#### **W&M ScholarWorks**

Dissertations, Theses, and Masters Projects

Theses, Dissertations, & Master Projects

2002

## Software and hardware methods for memory access latency reduction on ILP processors

Zhao Zhang College of William & Mary - Arts & Sciences

Follow this and additional works at: https://scholarworks.wm.edu/etd

Part of the Computer Sciences Commons

#### **Recommended Citation**

Zhang, Zhao, "Software and hardware methods for memory access latency reduction on ILP processors" (2002). Dissertations, Theses, and Masters Projects. Paper 1539623407. https://dx.doi.org/doi:10.21220/s2-97q8-0748

This Dissertation is brought to you for free and open access by the Theses, Dissertations, & Master Projects at W&M ScholarWorks. It has been accepted for inclusion in Dissertations, Theses, and Masters Projects by an authorized administrator of W&M ScholarWorks. For more information, please contact scholarworks@wm.edu.

# Software and Hardware Methods for Memory Access Latency Reduction on ILP Processors

\_\_\_\_

#### A Dissertation

Presented to

The Faculty of the Department of Computer Science

The College of William & Mary in Virginia

In Partial Fulfillment

Of the Requirements for the Degree of

Doctor of Philosophy

\_\_\_

by

Zhao Zhang

2002

### APPROVAL SHEET

This dissertation is submitted in partial fulfillment of the requirements for the degree of

**Doctor of Philosophy**

Zhao Zhang

Approved. June 2002

Xiaodong Zhang

Thesis Advisor

William Bynum

Phil Kearns

Evgenia Smirni

Andreas Stathopoulos

Mark Hinders

Department of Applied Science

## **Table of Contents**

| A | Acknowledgments |                                               |    |  |  |

|---|-----------------|-----------------------------------------------|----|--|--|

| A | bstra           | ct                                            | хi |  |  |

| 1 | Inti            | oduction                                      | 2  |  |  |

|   | 1.1             | Overview of Existing Studies                  | 3  |  |  |

|   | 1.2             | Our Contributions                             | 7  |  |  |

|   | 1.3             | Organization of the Dissertation              | 11 |  |  |

| 2 | Bac             | kground of Memory System Performance          | 12 |  |  |

|   | 2.1             | Cache Memories                                | 14 |  |  |

|   | 2.2             | DRAM Technology                               | 16 |  |  |

|   |                 | 2.2.1 DRAM Architecture and Operations        | 16 |  |  |

|   |                 | 2.2.2 Comparison of DRAM and SRAM             | 19 |  |  |

|   |                 | 2.2.3 DRAM Access Request and DRAM Operations | 19 |  |  |

|   |                 | 2.2.4 DRAM Variants                           | 21 |  |  |

|   |                 | 2.2.5 Memory Access Scheduling                | 23 |  |  |

|   | 2.3             | Dynamically Scheduled Superscalar Processors  | 26 |  |  |

| 3 | Eva  | luatio  | n Methodology: An Experimental Approach                   | 29 |

|---|------|---------|-----------------------------------------------------------|----|

|   | 3.1  | Archi   | tectural Simulations                                      | 30 |

|   | 3.2  | Simpl   | eScalar Tool Set                                          | 32 |

|   | 3.3  | Our S   | impleScalar Extensions                                    | 34 |

|   | 3.4  | SPEC    | and TPC-C Benchmarks                                      | 37 |

|   |      | 3.4.1   | SPEC CPU95 Benchmark                                      | 37 |

|   |      | 3.4.2   | SPEC CPU2000 Benchmark                                    | 37 |

|   |      | 3.4.3   | TPC-C Benchmark                                           | 40 |

| 4 | Fact | t Bit.l | Reversals on Uniprocessors and Shared-Memory Multiproces- | -  |

| • | sors |         | on Compression und Charles Incomory Industry              | 41 |

|   | 3013 | •       |                                                           |    |

|   | 4.1  | Block   | ing for Bit-reversals                                     | 46 |

|   | 4.2  | Blocki  | ing with Buffers                                          | 47 |

|   |      | 4.2.1   | Blocking With a Software Buffer and Its Limits            | 47 |

|   |      | 4.2.2   | Cache Structure Dependent Blocking                        | 48 |

|   |      | 4.2.3   | Victim-cache-aided Blocking                               | 51 |

|   | 4.3  | Blocki  | ng with Padding                                           | 52 |

|   | 4.4  | Blocki  | ng and Padding for a TLB                                  | 55 |

|   |      | 4.4.1   | Blocking for a Fully Associative TLB                      | 55 |

|   |      | 4.4.2   | Padding for a Set-associative TLB                         | 56 |

|   | 4.5  | Exper   | imental Results and Performance Evaluation                | 58 |

|   |      | 4.5.1   | Experimental Environment and Evaluation Methodology       | 58 |

|   |      | 4.5.2   | Effects of TLB and Virtual Memory                         | 60 |

|   |                   | 4.5.3                                                           | Performance of the Hybrid Method for Bit-reversals        | 63                                              |

|---|-------------------|-----------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------|

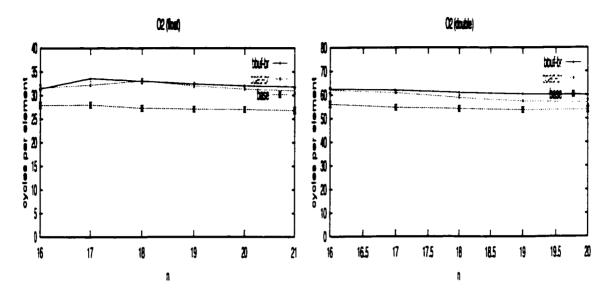

|   |                   | 4.5.4                                                           | Performance Comparisons on the SGI O2                     | 63                                              |

|   |                   | 4.5.5                                                           | Performance Comparisons on the Sun Ultra-5                | 65                                              |

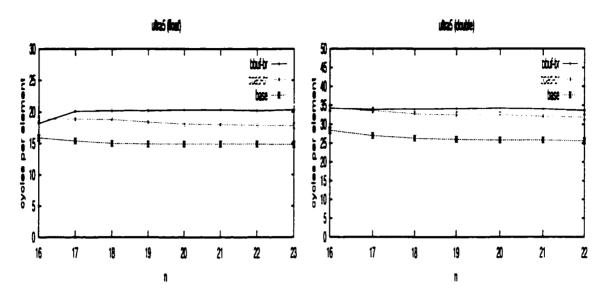

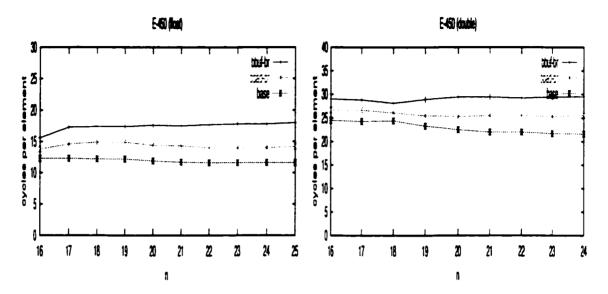

|   |                   | 4.5.6                                                           | Performance Comparisons on the Sun E-450                  | 65                                              |

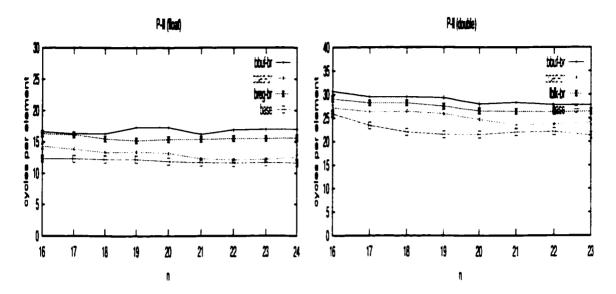

|   |                   | 4.5.7                                                           | Performance Comparisons on the Pentium-II 400             | 67                                              |

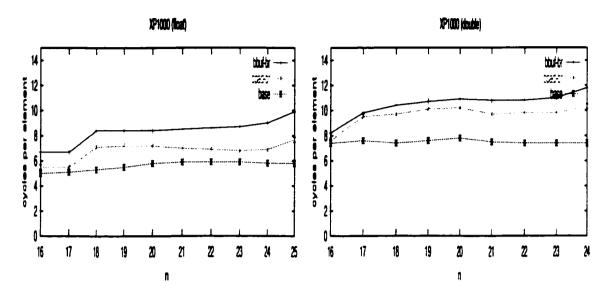

|   |                   | 4.5.8                                                           | Performance Comparisons on the Compaq XP-1000             | 68                                              |

|   | 4.6               | Perfor                                                          | mance Evaluation on SMP Multiprocessors                   | 69                                              |

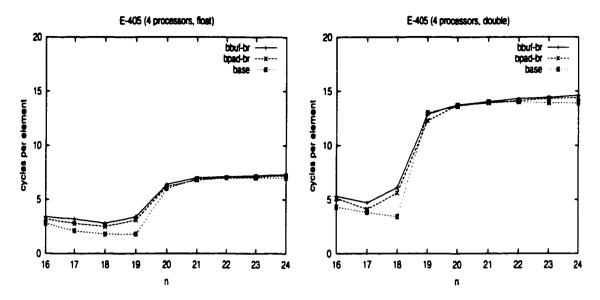

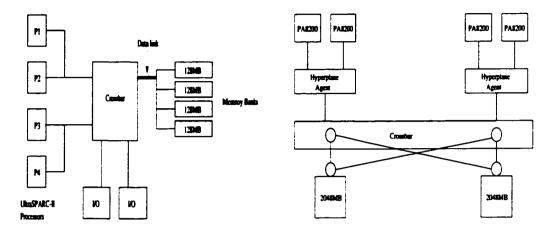

|   |                   | 4.6.1                                                           | Performance Comparisons on the Sun E-450                  | 70                                              |

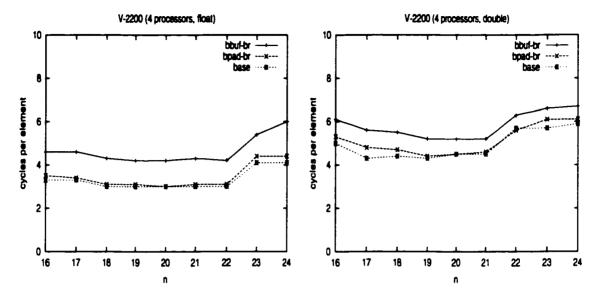

|   |                   | 4.6.2                                                           | Performance Comparisons on the HP 9000 V2200              | 73                                              |

|   | 4.7               | Summ                                                            | ary                                                       | 74                                              |

|   |                   | duce DRAM Row-buffer Conflicts by Breaking Address Mapping Sym- |                                                           |                                                 |

| 5 | Red               | luce Di                                                         | RAM Row-buffer Conflicts by Breaking Address Mapping Sym- | -                                               |

| 5 | Red               |                                                                 | RAM Row-buffer Conflicts by Breaking Address Mapping Sym- | -<br>76                                         |

| 5 |                   | ry                                                              | RAM Row-buffer Conflicts by Breaking Address Mapping Sym- |                                                 |

| 5 | met               | e <b>ry</b><br>Existir                                          |                                                           | 76                                              |

| 5 | met               | e <b>ry</b><br>Existir                                          | ng Address Mapping Schemes                                | <b>76</b>                                       |

| 5 | met               | Existir<br>Mappi                                                | ng Address Mapping Schemes                                | <b>76</b> 78 79                                 |

| 5 | met               | Existir<br>Mappi<br>5.2.1                                       | ng Address Mapping Schemes                                | 76<br>78<br>79<br>81                            |

| 5 | met               | Existin Mappi 5.2.1 5.2.2 5.2.3                                 | ng Address Mapping Schemes                                | 76<br>78<br>79<br>81                            |

| 5 | met<br>5.1<br>5.2 | Existin Mappi 5.2.1 5.2.2 5.2.3                                 | Ing Address Mapping Schemes                               | 76<br>78<br>79<br>81<br>81                      |

| 5 | met<br>5.1<br>5.2 | Existin Mappi 5.2.1 5.2.2 5.2.3 A Perr                          | ng Address Mapping Schemes                                | 766<br>78<br>79<br>81<br>81<br>83               |

| 5 | met<br>5.1<br>5.2 | Existin Mappi 5.2.1 5.2.2 5.2.3 A Perr 5.3.1 5.3.2              | Ing Address Mapping Schemes                               | 766<br>788<br>799<br>81<br>81<br>83<br>84<br>84 |

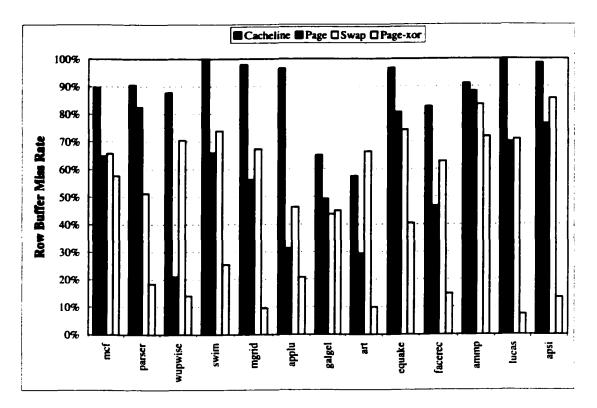

|                                        |                                                                 | 5.5.1                                 | Reductions of Row-buffer Miss Rates                           | 91          |  |  |

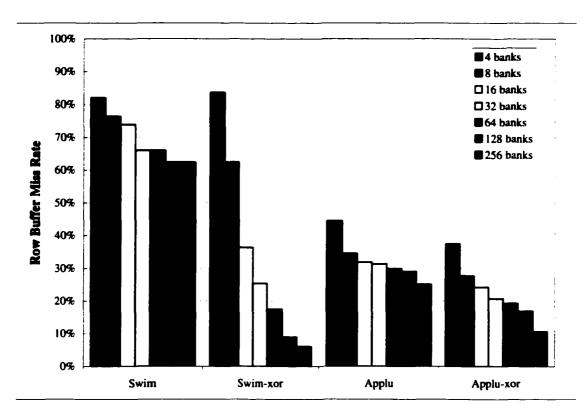

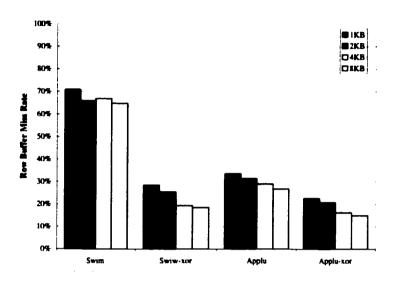

|----------------------------------------|-----------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------|-------------|--|--|

|                                        |                                                                 | 5.5.2                                 | Effects of Memory Organization Variations                     | 93          |  |  |

|                                        |                                                                 | 5.5.3                                 | Effects of Write Buffers                                      | 94          |  |  |

|                                        |                                                                 | 5.5.4                                 | Overall Performance Improvement                               | 96          |  |  |

|                                        | 5.6                                                             | Break                                 | ing Mapping Symmetry at Cache Level                           | 98          |  |  |

|                                        |                                                                 | 5.6.1                                 | Bitwise-XOR and Polynomial Mapping                            | 98          |  |  |

|                                        |                                                                 | 5.6.2                                 | Reduction of Miss Rates                                       | 99          |  |  |

|                                        |                                                                 | 5.6.3                                 | Comparisons of Overall Performance                            | 102         |  |  |

|                                        |                                                                 | 5.6.4                                 | Tradeoffs between Cache Mapping Schemes and DRAM Interleaving |             |  |  |

|                                        |                                                                 |                                       | Schemes                                                       | 103         |  |  |

|                                        | 5.7                                                             | Consid                                | derations of Large Cumulative Row Buffer Sizes                | 104         |  |  |

|                                        | 5.8                                                             | Other                                 | Related Work                                                  | 106         |  |  |

|                                        | 5.9                                                             | Concl                                 | usion                                                         | 109         |  |  |

| 6                                      | Cached DRAM: A Simple and Effective Technique for Memory Access |                                       |                                                               |             |  |  |

|                                        | Late                                                            | atency Reduction on ILP Processors 11 |                                                               |             |  |  |

|                                        | 6.1                                                             | Struct                                | ure and Operations of Cached DRAM                             | 114         |  |  |

|                                        | 6.2                                                             | Exper                                 | imental Environment                                           | Environment |  |  |

| 6.3 Comparisons of Overall Performance |                                                                 | arisons of Overall Performance        | 120                                                           |             |  |  |

|                                        |                                                                 | 6.3.1                                 | On-memory Cache Organizations                                 | 121         |  |  |

|                                        |                                                                 | 6.3.2                                 | Performance Improvement of Cached DRAM over SDRAM             | 122         |  |  |

|                                        |                                                                 | 6.3.3                                 | Performance Comparisons of Cached DRAM and Other DRAM Ar-     |             |  |  |

|                                        |                                                                 |                                       | chitectures                                                   | 124         |  |  |

|   | 6.4  | Cached DRAM with Increasing ILP Degree                            |     |  |  |  |

|---|------|-------------------------------------------------------------------|-----|--|--|--|

|   | 6.5  | Comparisons with Approaches Exploiting Row Buffer Locality        | 128 |  |  |  |

|   | 6.6  | Summary                                                           | 130 |  |  |  |

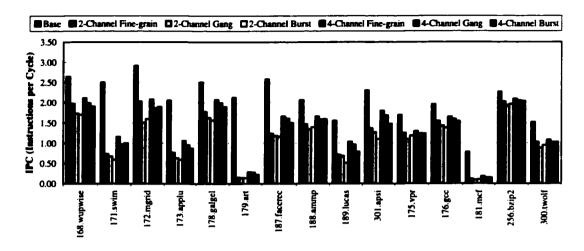

| 7 | Fin  | e-grain Priority Scheduling on Multi-channel Memory Systems       | 131 |  |  |  |

|   | 7.1  | Memory System Considerations                                      | 135 |  |  |  |

|   |      | 7.1.1 Multi-channel Memory Systems                                | 135 |  |  |  |

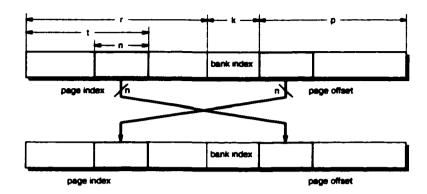

|   |      | 7.1.2 DRAM Mapping Scheme                                         | 136 |  |  |  |

|   | 7.2  | Fine-grain Priority Scheduling                                    | 138 |  |  |  |

|   |      | 7.2.1 Granularity of Scheduling                                   | 138 |  |  |  |

|   |      | 7.2.2 Scheduling Policies                                         | 139 |  |  |  |

|   | 7.3  | Complexity Analysis                                               | 141 |  |  |  |

|   |      | 7.3.1 Complexity inside Processor                                 | 141 |  |  |  |

|   |      | 7.3.2 Complexity in Memory Controller                             | 142 |  |  |  |

|   | 7.4  | Experimental Environment                                          | 144 |  |  |  |

|   | 7.5  | Experimental Results                                              | 145 |  |  |  |

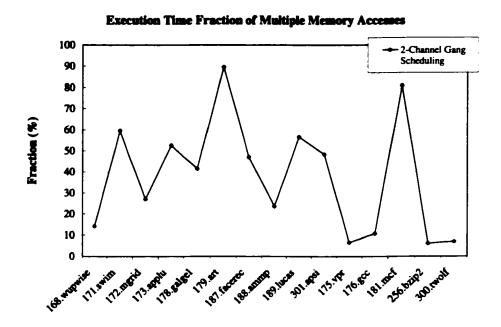

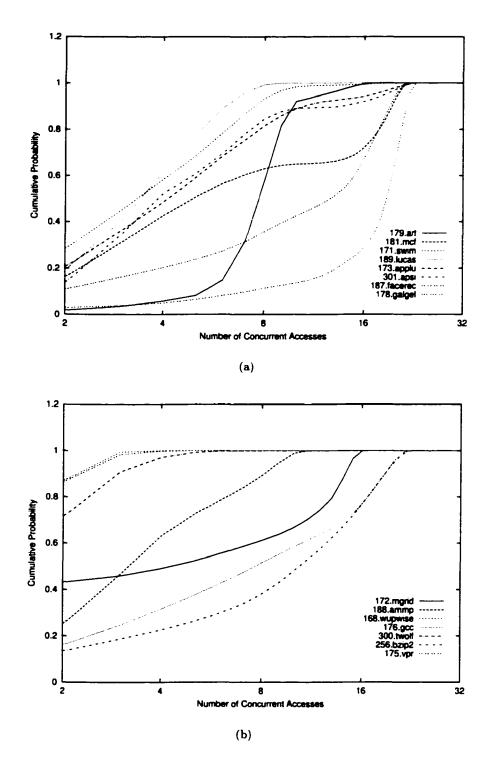

|   |      | 7.5.1 Burstiness in Miss Streams                                  | 145 |  |  |  |

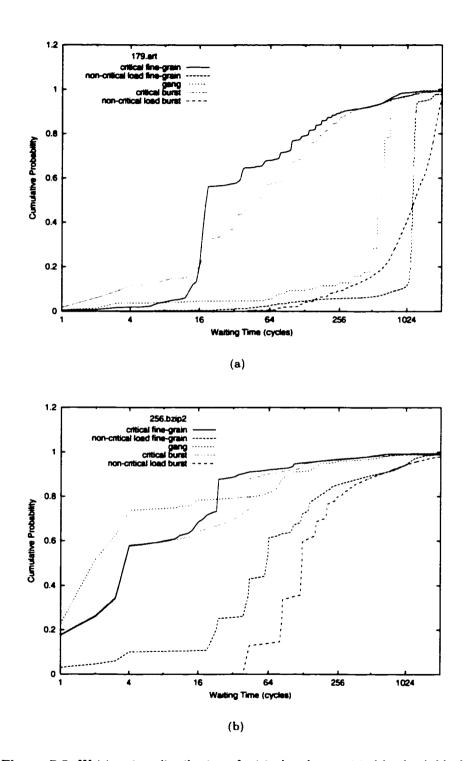

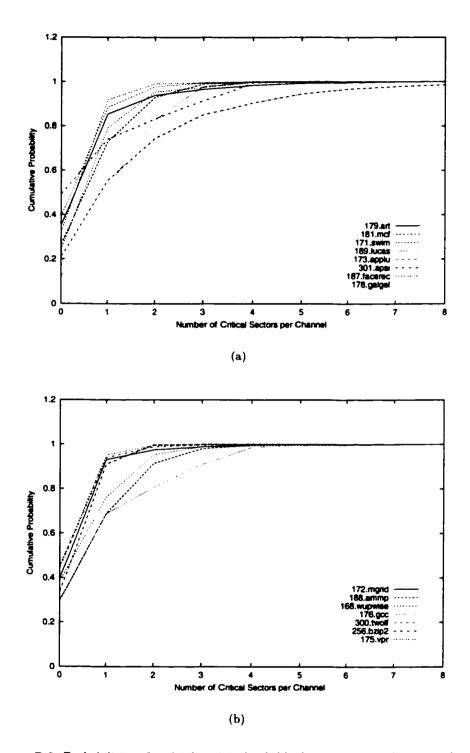

|   |      | 7.5.2 Potentials of Fine-grain Priority Scheduling                | 146 |  |  |  |

|   |      | 7.5.3 Performance Improvement of Fine-grain Priority Scheduling   | 151 |  |  |  |

|   | 7.6  | Other Related Work                                                | 154 |  |  |  |

|   | 7.7  | Summary                                                           | 156 |  |  |  |

| 0 | Carr | setmenting Lange Size and Law Overhand Off Chin Cooker has Cooked |     |  |  |  |

| 8 |      | nstructing Large Size and Low Overhead Off-Chip Caches by Cached  |     |  |  |  |

|   | DD   | D A N/I 157                                                       |     |  |  |  |

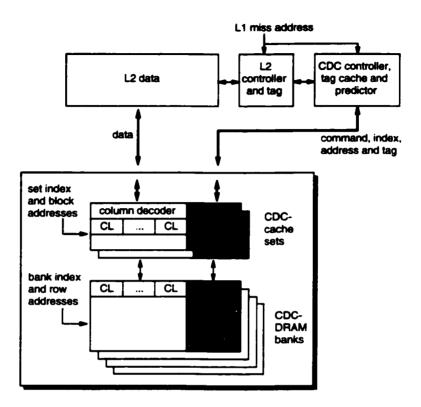

|   | 8.1 | The C  | CDC Design                                               | 16  |

|---|-----|--------|----------------------------------------------------------|-----|

|   |     | 8.1.1  | On-chip CDC Controller, Tag Cache, and Predictor         | 16  |

|   |     | 8.1.2  | CDC-DRAM Mapping                                         | 163 |

|   |     | 8.1.3  | CDC-cache Mapping                                        | 164 |

|   |     | 8.1.4  | The Predictor                                            | 16  |

|   |     | 8.1.5  | Write Policy                                             | 160 |

|   |     | 8.1.6  | Cache Coherence in Multiprocessor Environment            | 166 |

|   | 8.2 | Exper  | imental Setup                                            | 167 |

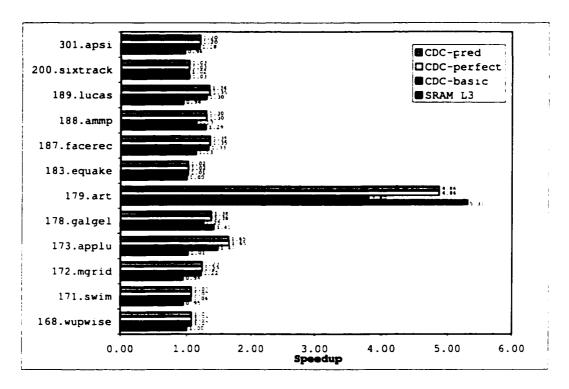

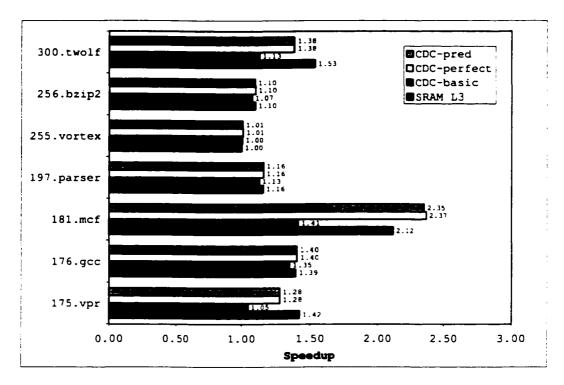

|   | 8.3 | Perfor | mance Results                                            | 169 |

|   |     | 8.3.1  | Performance of SRAM-L3                                   | 17  |

|   |     | 8.3.2  | Comparisons between CDC-predict and SRAM-L3              | 173 |

|   |     | 8.3.3  | Comparisons of the CDC Variants                          | 174 |

|   | 8.4 | Summ   | ary                                                      | 175 |

| 9 | Con | clusio | ns and Future Work                                       | 177 |

|   | 9.1 | Conclu | usions                                                   | 177 |

|   |     | 9.1.1  | Memory Latency Bottleneck                                | 177 |

|   |     | 9.1.2  | Our Approaches and Their Effectiveness                   | 179 |

|   | 9.2 | Future | e Work                                                   | 181 |

|   |     | 9.2.1  | Effective Memory Access Scheduling for Future Processors | 181 |

|   |     | 9.2.2  | Improving the Performance of CDC                         | 183 |

| A | The | Rit_re | eversal Program Using the Padding Method                 | 185 |

Bibliography 187

#### ACKNOWLEDGMENTS

This dissertation is a result of not only many years of efforts, but also the training, mentoring, educating, and support of many people. First of all, I would like to sincerely acknowledge Dr. Xiaodong Zhang, my advisor, for his mentoring and support for these five years. I am grateful for the numerous hours he have spent generously with me, which he spared from his heavy duties of research, service, and teaching. I appreciate his hard working and persistence, vast knowledge in many areas, and vision and determination to build up an excellent research team.

The Department of Computer Science at the College of William and Mary is a wonderful place for me to pursue my Doctoral degree. I would like to thank all faculty and staff in this department for their help in these years. I would like to acknowledge Dr. William Bynum, Dr. Phil Kearns, Dr. Evgenia Smirni, and Dr. Andreas Stathopoulos for serving the dissertation committee. I would like to thank Dr. Mark Hinders from the Department of Applied Science to take time from his busy schedule to serve as the external member of the committee. Especially, I thank Dr. William Bynum for his reviewing many of my manuscripts, and Dr. Evgenia Smirni and Dr. Bruce Lowekamp for their help in my career development. Dr. Bob Collins talked with me frequently in my first year in this department, obviously with the intention to help me in speaking English. I would also like to acknowledge Vanessa Godwin for the great help she has offered to me in my graduate study.

I would like to thank the members of the High Performance Computing and Software Lab, who have helped to create an environment full of stimulation. Dr. Yong Yan and Dr. Xing Du were great help to me, not only when we worked together but also after they have started their own careers. I would like to acknowledge Dr. Guangzhi Li. Zhichun Zhu, Li Xiao, Stefan Kubricht, Songqing Chen, Xin Chen, and Song Jiang for those wonderful discussions and arguments. With many of them I not only share the excitement of research,

but also enjoy a lot of fun as friends.

I would like to thank other graduate students in the department, including Lei Guo.

Aaron Hawkins, Zvezdan Petkovic, Alma Riska, Wei Sun, and Qi Zhang, but not exclusively,

for those interdisciplinary discussions and for their friendship.

I would like to acknowledge Dr. Yiming Hu of the Department of Electrical & Computer Engineering and Computer Science at University of Cincinnati, and Dr. Hong Wang in Intel Microprocessor Research Labs, for both their insightful comments on technical issues and their kind help in my career development.

I would also like to acknowledge the funding agencies that provided funds and equipment that supported my research: Sun Microsystems, for their donations of workstations and servers, and the National Science Foundation and the Air Force Office of Scientific Research. whose grants funded the majority of my graduate research.

I am deeply grateful to my parents, Guoxiang Zhang and Xiyin Wan, and my sisters, Qing Zhang and Xi Zhang, and my brother-in-law. Bin Feng, all of whom have given me the upbringing and education that allowed me to reach this point. A very special thanks goes out to my mother, who started my education early by teaching me Chinese language, arithmetic, and a little bit of English when I was only a few years old.

Most of all, I must acknowledge my wife, Zhichun Zhu, for her constant support, assistance, and encouragement through these years. She helped me survive tough times, meanwhile she suffered through my all kinds of pressure, loss of direction, and rotten moods. I could have never made it this far without her.

#### **ABSTRACT**

While microprocessors have doubled their speed every 18 months, performance improvement of memory systems has continued to lag behind. To address the speed gap between CPU and memory, a standard multi-level caching organization has been built for fast data accesses before the data have to be accessed in DRAM core. The existence of these caches in a computer system, such as L1, L2, L3, and DRAM row buffers, does not mean that data locality will be automatically exploited. The effective use of the memory hierarchy mainly depends on how data are allocated and how memory accesses are scheduled. In this dissertation, we propose several novel software and hardware techniques to effectively exploit the data locality and to significantly reduce memory access latency.

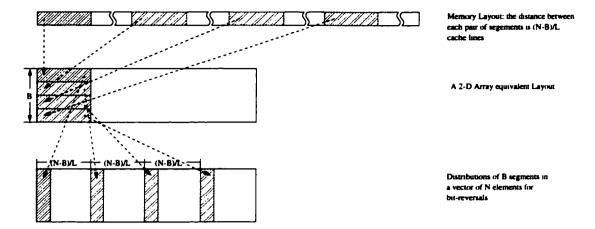

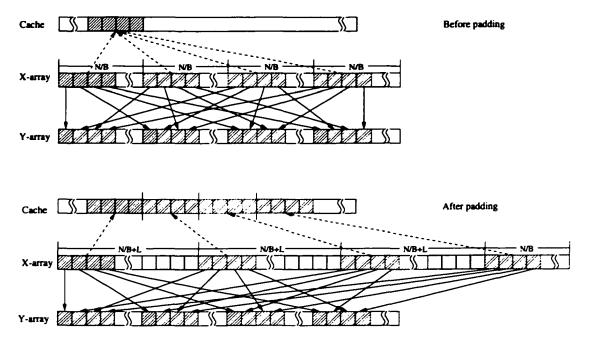

We first presented a case study at the application level that reconstructs memory-intensive programs by utilizing program-specific knowledge. The problem of bit-reversals, a set of data reordering operations extensively used in scientific computing program such as FFT, and an application with a special data access pattern that can cause severe cache conflicts, is identified in this study. We have proposed several software methods, including padding and blocking, to restructure the program to reduce those conflicts. Our methods outperform existing ones on both uniprocessor and multiprocessor systems.

The access latency to DRAM core has become increasingly long relative to CPU speed, causing memory accesses to be an execution bottleneck. In order to reduce the frequency of DRAM core accesses to effectively shorten the overall memory access latency, we have conducted three studies at this level of memory hierarchy. First, motivated by our evaluation of DRAM row buffer's performance roles and our findings of the reasons of its access conflicts, we propose a simple and effective memory interleaving scheme to reduce or even eliminate row buffer conflicts. Second, we propose a fine-grain priority scheduling scheme to reorder the sequence of data accesses on multi-channel memory systems, effectively exploiting the available bus bandwidth and access concurrency. In the final part of the dissertation, we first evaluate the design of cached DRAM and its organization alternatives associated with ILP processors. We then propose a new memory hierarchy integration that uses cached DRAM to construct a very large off-chip cache. We show that this structure outperforms a standard memory system with an off-level L3 cache for memory-intensive applications.

Memory access latency has become a major performance bottleneck for memory-intensive applications. As long as DRAM technology remains its most cost-effective position for making main memory, the memory performance problem will continue to exist. The studies conducted in this dissertation attempt to address this important issue. Our proposed software and hardware schemes are effective and applicable, which can be directly used in real-world memory system designs and implementations. Our studies also provide guidance for application programmers to understand memory performance implications, and for system architects to optimize memory hierarchies.

## Chapter 1

## Introduction

The performance of processors has been doubling every 18 months as predicted by Moore's Law for decades. This fast improvement comes from the advances in circuit design, fabrication technology, and architectural innovations. However, the improvement of memory systems has lagged far behind that rate. While the speed of high-end processors increases by 60% per year, the speed of DRAM increases by only 7% per year [44]. In other words, the speed gap between the CPU and the DRAM increases by more than 50% per year. Currently, the time cost of a DRAM access is equivalent to that of executing hundreds of instructions inside a processor. Without addressing the concern of the CPU-memory gap, further improvement of processor performance will eventually vanish because of the dominance of memory stall time.

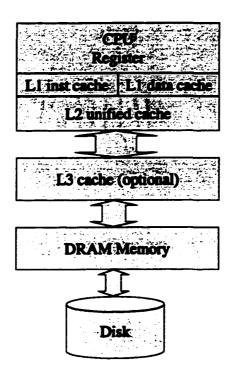

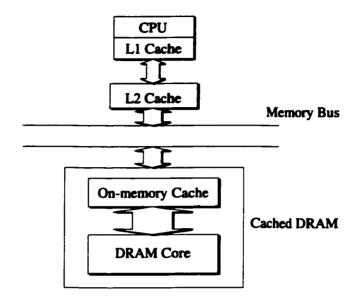

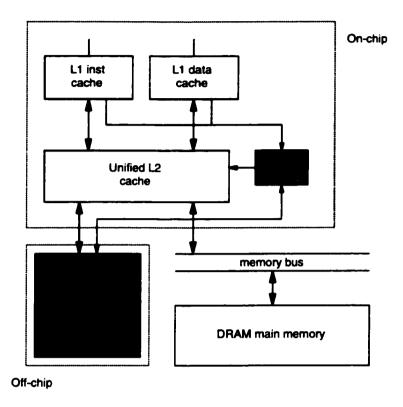

Traditionally, this issue has been addressed by constructing a memory hierarchy, as shown in Figure 1.1, where small and fast SRAM caches are at the top levels, and slow and large DRAM memory is at the bottom level. When working effectively, the top-level caches can serve most memory references, minimizing the number of accesses to the lower-level DRAM memory. However, as the speed gap between the CPU and DRAM memory continues to widen, even a small fraction of memory references falling into the DRAM

memory will make the memory stall times dominate in the total execution times of memoryintensive applications.

Figure 1.1: A typical memory hierarchy in high-end workstations.

#### 1.1 Overview of Existing Studies

Computer architecture research on memory hierarchy is focused on optimizing the hard-ware organization of caches [101, 76], especially on L1 instruction caches and L1 data caches. which satisfy more than 90 percent of memory references for most workloads. From computer architecture point of view, the cache performance is determined by the cache miss rates, cache access time, cache bandwidth, and miss penalty.

Increasing the cache size and using set-associative cache are effective methods to reduce cache miss rates. However, they usually cause an increase of access time, which increases either processor cycle time or pipeline length and delays the execution of all instructions. Many studies have been done to achieve the best trade-off between reducing cache miss rates and reducing cache access time. The study in [47] investigates the use of simple, direct mapped cache and the best balance between cache size and cache access time. New cache organizations (e.g. [76]) have been proposed to achieve the fast access times of direct mapped caches and the low cache miss rates of set associative caches, such as decoupled caches [103, 69, 98, 57, 77], multiple-access caches [2, 1, 123, 16, 78, 10], augmented caches [56, 87, 55], and multilevel caches [106, 5, 6, 116, 80, 110].

As processors aggressively exploit instruction-level parallelism (ILP), cache bandwidth becomes a serious limitation of processor performance. Issuing multiple instructions per cycle, processors need to fetch multiple instructions and data items per cycle. Wide instruction cache ports (outputting multiple consecutive instructions per access) and instruction buffers [41] exploit the spatial locality in the instruction fetch stream to increase cache bandwidth. Trace cache [92, 52, 36, 12] uses branch prediction information to concatenate non-contiguous instruction blocks separated by branch instructions into larger, contiguous blocks. In this way, more than one basic block (contiguous instructions without a branch) can be fetched in one cycle. Accesses to a data cache are less regular than those to an instruction cache. Thus, different techniques are needed to increase the bandwidth of data caches. Data caches with two interleaved banks [9, 120] allow two simultaneous accesses as long as they fall into different banks. A duplicating data cache [30] has two caches with identical contents, doubling the bandwidth with the cost of double-sized chip area. An-

other approach is phase-pipeline access [66], with which the cache outputs data on both clock edges. Although this technique saves chip area, the cache has to be as twice fast as the processor. As complexity-effective alternatives, authors in [88] propose locality-based interleaved cache that enhances the cache by adding a multi-ported single line buffer to each cache bank, and authors in [20] propose to use separate caches for program data, heap, and stack regions.

Software approaches, such as compiler ones, operating systems ones, and application-level ones also play an important role in reducing cache miss rate. Compiler approaches reduce cache miss rate by either improving program locality, optimizing data layout, or exploiting the opportunity of software prefetching. There are two types of locality optimization techniques: program transformation and data layout transformation. Program transformation [64, 72] tries to determine the best sequence of memory references that maximizes the reuse of cached data. Data layout transformation [53, 111] performs packing, padding, and aligning on data arrays and data structures to reduce data size and to avoid cache conflicts. Compilers can also insert prefetch instructions into programs [17, 74] to hide cache miss latency, effectively reducing cache miss rates. However, this approach is normally restricted to loop-based program code because the compiler must precisely predict memory access patterns.

Operating systems approaches reduce cache conflict misses by carefully mapping virtual memory pages onto physical memory pages. A static page mapping policy [60], such as page coloring, uses heuristics to select the mapping that is most likely to minimize cache conflict misses. A dynamic page mapping policy [11] employs special hardware to detect severe conflict miss conditions and dynamically changes the mapping of related pages to

avoid the conflicts.

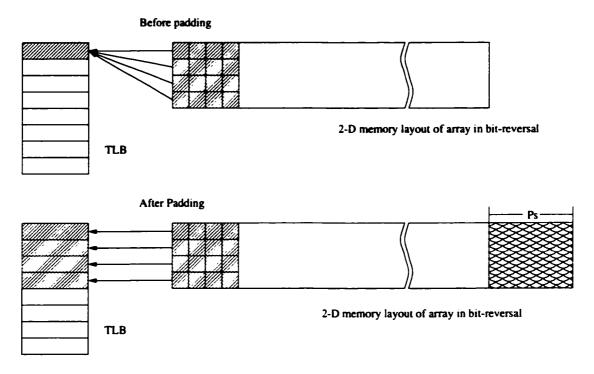

Application-level approaches improve cache locality or reduce cache conflict misses by exploiting the knowledge of application memory access patterns as well as the knowledge of the architecture on which the application is running. As in compiler approaches, the program access pattern or the data layout or both are reconstructed. Unlike compiler approaches, it is the application programmers who can make the changes because only the programmers, not the compilers, have the global knowledge about the interaction between the program and the underlying architecture. For example, a run-time method has been proposed in [119] to optimize the cache locality of a set of programs with dynamic memory access patterns running on shared-memory multiprocessors. Reconstructing the execution of programs into small computation threads and using a bin-space-based task partitioning method to assign those threads onto computing nodes, this method maximizes the reuse of cached data and achieves load balance among computing nodes. In this dissertation (Chapter 4), we also present a study of cache-optimal methods for bit-reversals, an application with severe cache conflicts on typical cache organizations. One method we propose is to reconstruct the layout of data arrays by inserting small padding spaces such that concurrently accessed data will not conflict in the cache.

Although numerous studies have been done to improve the effectiveness of memory hierarchy and many of the proposed cache techniques have been implemented, memory stall time will continue to increase due to the ever increasing CPU-memory speed gap. For applications with large working sets and irregular access patterns, the cache misses due to limited cache capacity can not be eliminated. For those applications, even if the cache misses rate is reduced to the minimum level, the memory stall time due to DRAM accesses can

easily dominate in the total execution time because of the very long DRAM access latency (relative to processor speed). For example, if a program has 0.5 misses per 100 instructions executed, and the cost of a DRAM access is equivalent to executing 200 instructions, (a 2GHz 2-way issue processor can execute up to two instructions in 0.5ns, while a typical DRAM access will take 50ns.) the memory stall time can be up to one half of the total execution time of the program.

#### 1.2 Our Contributions

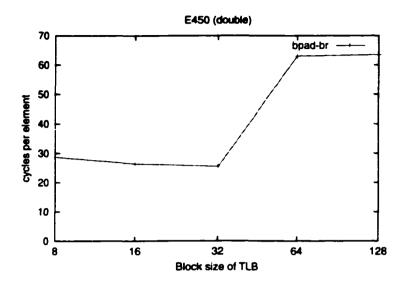

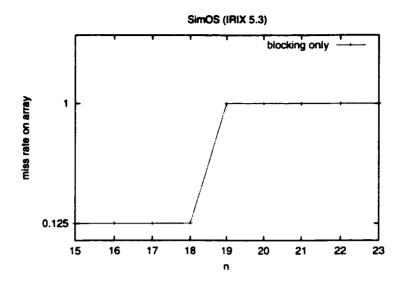

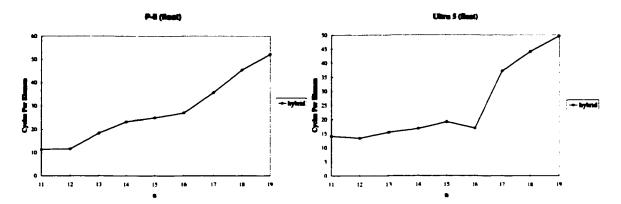

We have started our memory system study at the application level to reconstruct memory-intensive programs by utilizing program-specific knowledge. The problem of bit-reversals. a set of data reordering operations extensively used in scientific computing programs, such as FFT, is identified for such a study. This application has a special data access pattern [58] that can cause severe cache conflicts. In this study, we examine different methods using techniques of blocking, buffering, and padding for efficient implementations of bit-reversals. We evaluate the merits and limits of each technique and their applications and architecture-dependent conditions for developing cache-optimal methods. Besides testing the methods on different uniprocessors, we conducted both simulation and measurements on two commercial SMP multiprocessors to provide architectural insights into the methods and their implementations. We made two contributions in this study: (1) Our integrated blocking methods, which match cache associativity and TLB cache size and which fully use the available registers, are cache-optimal and fast. (2) We show that our padding methods outperform other software oriented methods, and believe they are the fastest in terms of

minimizing both CPU and memory access cycles. Since the padding methods are almost independent of hardware, they could be widely used on many uniprocessor workstations and multiprocessors.

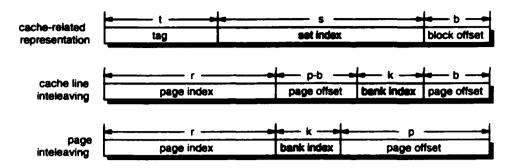

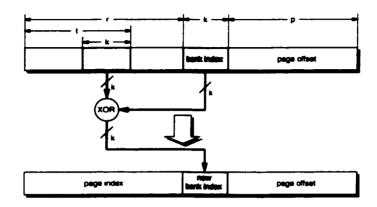

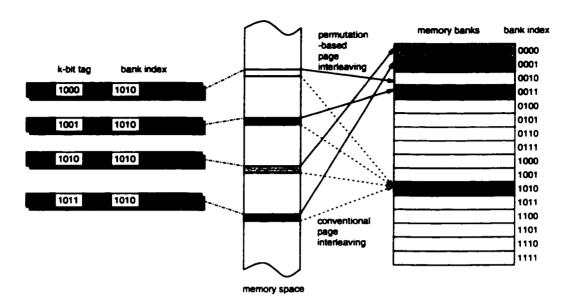

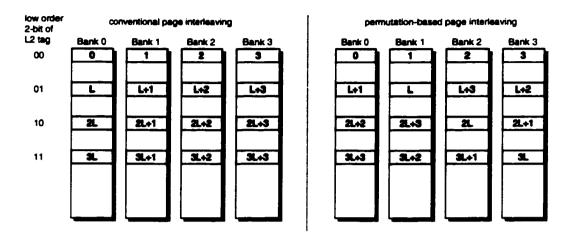

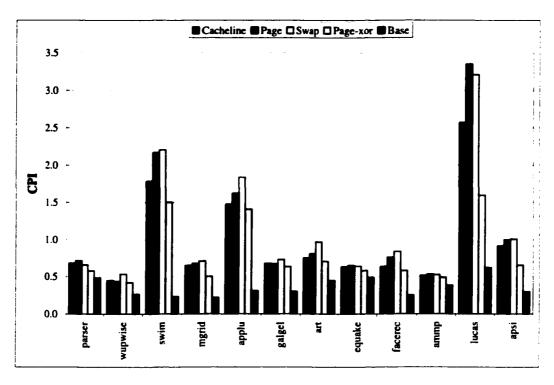

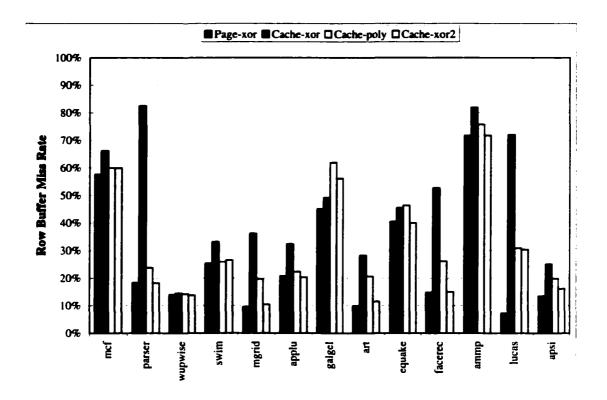

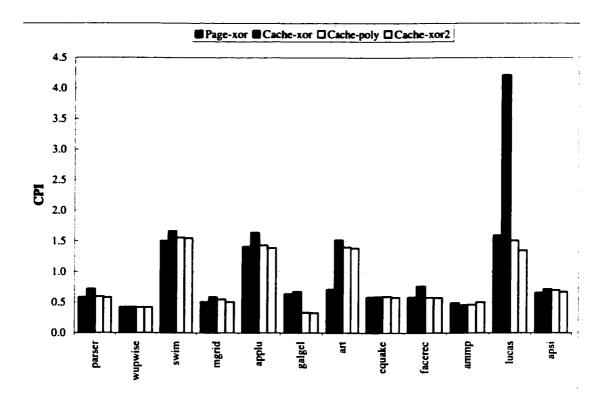

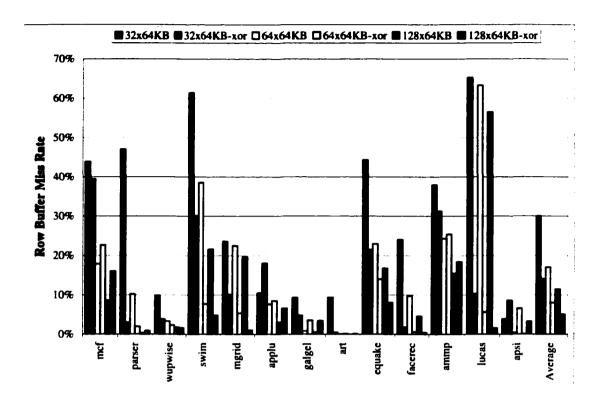

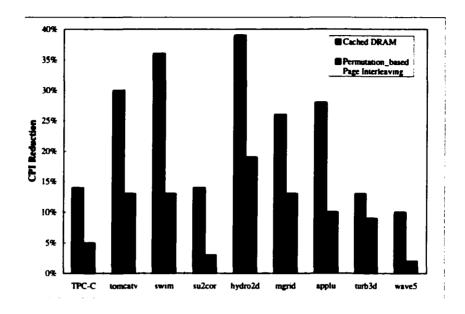

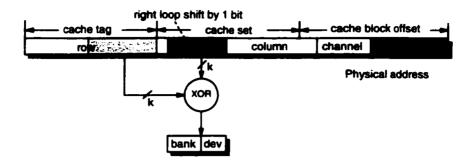

The main focus of this dissertation is on DRAM memory. The access latency to DRAM core has become increasingly long relatively to the CPU speed, causing DRAM accesses to be the performance bottleneck of many workloads. In order to exploit the potential of DRAM organizations to effectively shorten the overall memory access latency, we have conducted three studies at this level of the memory hierarchy. First, we investigate the potential of exploiting DRAM row buffer locality [124]. Each access to DRAM core must go through the row buffer, which has a shorter access latency than the DRAM core. DRAM row-buffer conflicts occur when a sequence of requests on different rows fall onto the same memory bank, causing a much higher memory access latency than requests to the same row or to different banks. We analyze the sources of row-buffer conflicts in the context of dynamically scheduled superscalar processors, and propose a permutation-based page interleaving scheme to reduce row-buffer conflicts and to exploit data access locality in the row buffer. Compared with several existing schemes, we show that the permutation-based scheme dramatically increases hit rates in DRAM row buffers and reduces memory stall time of SPEC2000 benchmark programs.

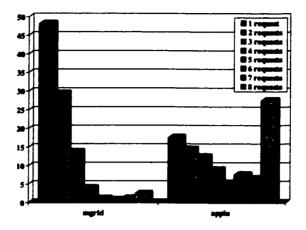

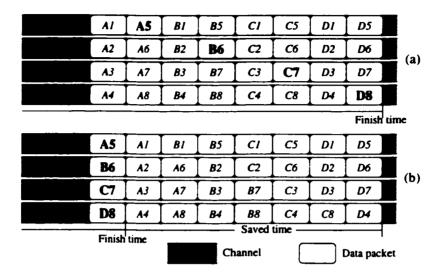

Second, we proposed a fine-grain priority scheduling scheme for recent multi-channel DRAM memory systems [126]. Configurations of contemporary DRAM memory systems become increasingly complex. A recent study shows that application performance is highly sensitive to DRAM memory configuration, and suggests that tuning burst sizes and channel configurations be an effective way to optimize the DRAM performance for a given memory-

intensive workload [24]. However, this approach is workload dependent. In this study, we show that by utilizing fine-grain priority access scheduling, we are able to find a workload independent configuration that achieves optimal performance on a multi-channel memory system. Our approach can well utilize the available high concurrency and high bandwidth on such memory systems, and can effectively reduce memory stall time.

In the final part of the dissertation, we first evaluate the performance of cached DRAM and its design alternatives in the context of ILP processors [124]. Then we propose a new memory hierarchy organization that uses cached DRAM to construct a very large off-chip cache. We show that this off-chip cache outperforms an off-chip SRAM cache in a standard memory system for memory-intensive applications.

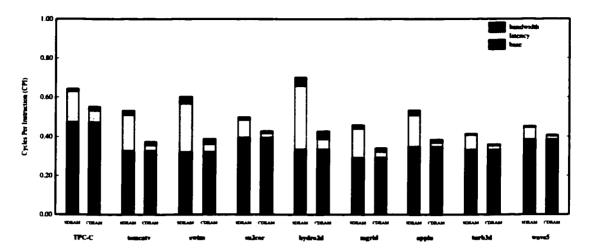

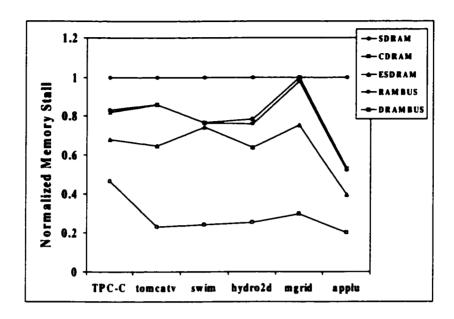

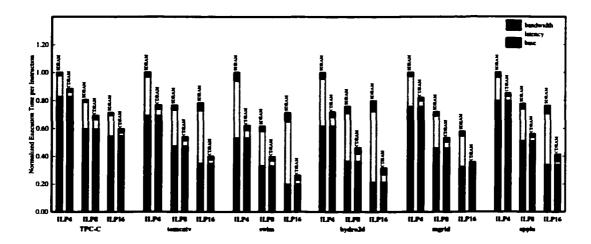

Cached DRAM is an existing technology that integrates a small cache into DRAM chip. By exploiting the spatial locality of memory access streams missing from the L2 cache, a cached DRAM can reduce the average DRAM access time. Previous studies have shown that cached DRAM is effective in a relatively simple processor model with small or even without data caches on the processor chip. Some recent studies have shown that this technique can be effective on modern ILP processors as well. Aiming at further investigating the ILP effects and comparing cached DRAM with other advanced DRAM organizations and interleaving techniques, we present a study of the design and optimization of cached DRAM in the context of processors with full ILP capabilities and large data caches. Conducting experiments on execution-driven simulation, we have evaluated its performance effectiveness using eight selected data-intensive SPECfp95 programs and TPC-C workload. Our study provides three new findings: (1) cached DRAM is able to consistently show its performance advantage as the ILP degree increases; (2) contemporary DRAM schemes.

such as SDRAM, Enhanced SDRAM, Rambus DRAM, and Direct Rambus DRAM, do not exploit memory access locality of memory-intensive workloads as effectively as cached DRAM does; and (3) compared with a highly effective permutation-based DRAM interleaving technique, cached DRAM can still gain substantial performance improvement, because its set-associative structure minimizes conflict misses in the on-memory caches.

Following the above study, we proposed a design that exploits the high density of cached DRAM to construct large off-chip L3 caches. Large off-chip L3 caches are beneficial to memory-intensive applications. However, there are two potential problems of using L3 caches: (1) The size of an SRAM cache is limited due to its low density and high cost, thus the working sets of many memory-intensive applications cannot fit into it. (2) Since the L3 tag checking overhead is significant for a cache miss, performance of some memory-intensive applications can be harmed by the existence of L3 cache due to increased memory access latency. To address these two problems, we present a new memory hierarchy organization that uses cached DRAM to construct a large size and low overhead off-chip cache. The high density DRAM in the cached DRAM can hold large data sets, while the small SRAM cache exploits the spatial locality that appears in L2 miss streams to reduce the access latency. A small on-chip tag cache is used to minimize the access overhead. Utilizing a prediction technique, the hit/miss status of an access to the cached DRAM can be accurately predicted. further reducing the access latency.

Memory access latency of application programs has become a major performance bottleneck. As long as DRAM technology remains its most cost-effective position for making main memory, the memory performance problem will continue to exist. The studies conducted in this dissertation attempt to address this important issue. The significance, potential impacts, and contributions of this dissertation are:

- Our performance studies on memory systems have provided insights into the effects

of application program interactions at different levels of the memory hierarchy, and

provide motivation and guidance for application programmers to understand memory

performance implications, and for system architects to optimize the memory hierarchy

and its system organization.

- Our proposed software and hardware schemes are effective and applicable, which can be directly used in the real-world memory system designs and implementations.

#### 1.3 Organization of the Dissertation

The rest of the dissertation is organized as follows. Chapter 2 presents the technical background of this dissertation. Chapter 3 presents the experimental performance evaluation methodology. Chapter 4 describes and evaluates the memory-effective algorithms and implementations of bit-reversals. Chapter 5 presents the permutation-based page interleaving scheme and its evaluation. Chapter 6 presents the evaluation of cached DRAM organization. Chapter 7 describes and evaluates the fine-grain priority access scheduling for multi-channel memory system. Chapter 8 discusses the cached-DRAM cache techniques. Finally, Chapter 9 concludes the dissertation and discusses the future work.

### Chapter 2

## **Background of Memory System**

## **Performance**

An ideal memory is infinitely large and meanwhile allows instantaneous access to every word stored in it. In practice, the access latency of a memory system increases with its capacity. Although the speed of small memories is able to catch up the speed of processor, the speed of large memories is many times slower due to technical limitations. To provide the illusion of an ideal memory system to programmers, architects have built memory hierarchies that contain fast, small memories at the top levels and large, slow memories at the bottom levels. A typical memory hierarchy in today's high performance computers has two-level on-chip caches that are integrated with the CPU, an optional off-chip cache, a DRAM memory system, and hard disks, as shown in Figure 1.1. (In this dissertation, we focus on applications that are memory-intensive but not I/O intensive, thus we do not consider the performance related to disk I/O.)

The effectiveness of the memory hierarchy is based on the principle of program locality.

There are two types of locality: temporal locality and spatial locality. Assume a memory word is accessed at a certain time during the execution of a program. The temporal locality

states that the memory word is likely to be accessed again in the near future, and the spatial locality states that the neighbor words are likely to be accessed soon. Thus, the word in use and its neighbor words should be stored at the top levels of the memory hierarchy to reduce the frequency of accessing slow memories. Both types of locality exist in the references to the program code and those to the program data. Most programs have good temporal locality and/or spatial locality so that the use of memory hierarchy can effectively hide the long latency of the slow memories.

The performance of memory hierarchy is highly dependent on program behavior. For programs that have small working sets, most memory references can be satisfied by the on-chip caches. The performance of those programs is then determined by the performance of the on-chip caches, whose access time is close to the processor cycle time. However, most real-world programs have large working sets that cannot be held by the on-chip caches. For those programs, on-chip caches can still filter out most memory references. However, as the performance of the processor increases, the performance loss in the DRAM memories increases dramatically.

The processor model has significant impacts on the design and optimization of caches and DRAM memories. Contemporary superscalar processors have the features of multiple issue, speculative execution, and non-blocking load to exploit ILP aggressively. The use of multiple issue increases the number of instructions that the processor can execute every cycle, thus increases the frequency of cache misses. Speculative execution and non-blocking load allows multiple outstanding cache misses, providing the opportunity of exploiting memory access concurrency.

The performance of a memory hierarchy can be measured by the increase of program

execution time due to memory access latency<sup>1</sup>. The shorter the increase, the better the performance of the memory hierarchy for the program. For simple processors, the performance of a memory hierarchy can be estimated by cache miss rates, cache hit latency, and cache miss latency (See [44] and Chapter 5). For dynamically scheduling processors, however, the insights of memory system performance must be discovered by detailed simulations. The experimental methodology will be discussed in the next chapter.

The rest of the chapter is organized as follows. Section 2.1 introduces the design issues and optimization of caches. Section 2.2 presents the details of DRAM technology. Finally, Section 2.3 discusses the processor model used in this dissertation.

#### 2.1 Cache Memories

A hardware cache buffers data contents that are likely to be accessed soon. A typical cache is divided into blocks, each of which stores multiple words that are continuous in the memory space. There are two common methods to map memory space onto the cache: direct mapped and set associative. A direct mapped cache maps a memory block onto a single location in the cache, while a set associative cache maps the block onto multiple locations. The replacement policy decides which block in the cache will be replaced when a cache miss happens. There is only one choice of replacement for direct mapped cache. For set associative cache, the least-recently used (LRU) policy is commonly used.

Cache misses can be divided into three categories: compulsory, capacity, and conflict [44].

Compulsory misses are those misses happening when data items are loaded into the cache

<sup>&</sup>lt;sup>1</sup>When comparing the performance of different configurations for the same program, *CPI* (cycle per instruction) is usually used as a substitute for execution time.

for the first time. Capacity misses are related to the limited capacity of cache. In other words, the capacity misses would not happen if the cache were infinitely large. Conflict misses happen when too many memory blocks are mapped onto some cache sets. Even if the cache is large enough to held the data items, only a small part of the cache can be effectively used, causing conflict misses.

For simple processors with a single level of cache, the performance of the cache is determined by cache miss rate, cache hit time, and cache miss penalty. The cache miss rate is the ratio of the number of cache misses to the number of memory references. Cache hit time is measured as the number of processor cycles that are needed to fetch data from the cache. Cache miss penalty is the time to fetch and access the data item from the lower level memory. Reducing the miss rate, the hit time, or the miss penalty will improve cache performance. High-performance superscalar processors require high-bandwidth instruction cache, high-bandwidth data cache, and non-blocking cache because of their multiple issue and dynamically scheduling features.

Increasing the cache capacity is an effective way to reduce the number of capacity misses. However, the cache hit time increases logarithmically as the cache capacity increases, which causes an increase of either the pipeline length or the processor cycle time. Thus, the best balance between the speed and the capacity must be determined by careful performance evaluations with realistic workloads [47]. As the transistor budget for building a cache increases, two-level or three-level caches are built to exploit the additional transistors without increasing the hit time of the first-level cache [5, 6, 116, 110]. Furthermore, more caches are integrated into the processor chip, which reduces the cache hit time effectively.

Increasing cache associativity is an effective method to reduce conflict misses. For

example, authors in [76] report that the miss rate of a direct mapped 16KB cache is about 50% higher than that of a four-way associative counterpart for a commercial workload. However, a set associative cache needs more tag storage, and has a longer hit time because its tag comparison is more complex. To address the long hit time, researchers have proposed a number of multiple-access cache techniques [2, 1, 16, 123, 78, 10], which allow fast accesses for most hits while avoiding the high miss rates of a direct mapped cache.

High-performance ILP processors run at a high frequency and issue multiple instructions per cycle, presenting new challenges for cache designs. Architects employ new techniques such as non-blocking cache, high-bandwidth design, and trace cache. With a non-blocking cache [63, 35, 34], the processor can issue other instructions even when a cache miss causes a load instruction to be suspended. MSHR [63] (Missing Status/information Holding Registers) is used to resume the execution of the load instruction when the missed data returns. A high-bandwidth data cache [30, 120, 66, 88, 20] can return more than one date item each cycle so that the processor can execute two or more load instructions simultaneously. Trace cache [92, 52, 36, 12] combines instruction cache with branch prediction unit to meet the demand for high instruction fetch bandwidth.

#### 2.2 DRAM Technology

#### 2.2.1 DRAM Architecture and Operations

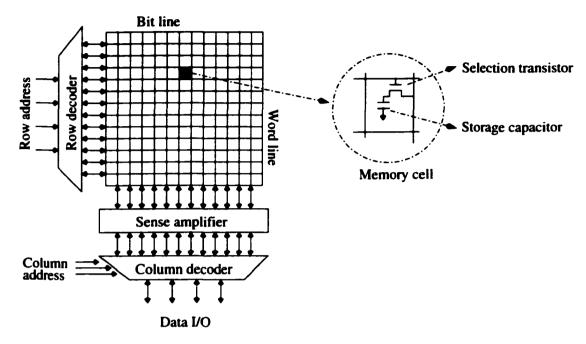

The basic structure of DRAM (Dynamic Random Access Memories) is an array of memory cells, as shown in Figure 2.1. Each cell consists of one transistor and one capacitor. The capacitor, called storage capacitor, stores one binary bit whose value is determined by the

Figure 2.1: The structure of a DRAM memory bank.

amount of charge carried by the capacitor. The transistor, called selection transistor, is used to control the input and output of the binary bit. Millions of memory cells form an array. attached to thousands of bit lines and word lines. Such a block, including its peripheral circuits, forms a memory bank. To read a word from a memory bank, the row decoder first activates a word line (a horizontal line in Figure 2.1) according to the row address. The charges carried by the memory cells on the word line propagate on the bit lines (a vertical line in Figure 2.1). The sense amplifier reads the signals on the bit lines and buffers the binary values in its own storage structure. The sense amplifier is also called row buffer. Then the column decoder selects a word in the row buffer according to the column address, and outputs it to the external world. This step is called column access operation. Reading a row of data to the row buffer is called row access operation.

Reading contents from DRAM memory cells is destructive. When the charges of a row of memory cells propagate on the bit lines, the capacitors in those cells lose the charges and the information they represent. Thus, the data stored in the row buffer must be written back into the memory cells after the row access. The process of writing data into memory cells also consists of row access and column access. The row access is the same as that of the read process. During the column access, a word stored in the row buffer is replaced by the input data, then all data stored in the row buffer is written back to the memory cells.

After a column access, a *precharge* operation must be performed to the memory bank before the next row access to the DRAM memory array can happen. The effect of precharge is to raise the voltage of bit lines, which is necessary for the sense amplifier to read signals from the memory cells.

The capacitors of the memory cells lose their charges gradually over time. Thus, a memory bank must be refreshed periodically. The process of *refresh* is just to read the data stored in a row of memory cells to the row buffer, and write the data back to the same memory cells. This process is done row by row.

The DRAM memory cell structure, which has only one selector transistor and one storage capacitor, is possibly the most compact structure allowed by current semiconductor technology. Because of the compactness of its memory cells and its array organization. DRAM memory has very high density and is relatively inexpensive. Unfortunately, those properties also limit the improvement of DRAM access latency. For contemporary DRAM memories, the precharge time is  $20\sim30ns$ , and the row access time and the column access time are around 20ns. For more details and discussions of DRAM memory technology, interested readers may refer to [81, 59, 27].

#### 2.2.2 Comparison of DRAM and SRAM

Compared with SRAMs (Static Random Access Memories), DRAMs have four major technical limitations. First, the simple cell structure with one capacitor and one transistor makes the row access latency longer than that of SRAMs, which use multiple transistors to facilitate a cell. Second, performing "read" operations on the DRAM cells is destructive to the original signals. The signals have to be written back to the selected memory cells. In contrast, the signals in SRAM cells are restored by themselves after read operations. Third, each DRAM cell must be refreshed periodically to charge the capacitor. In contrast, SRAMs hold their data bits using flip-flop gate circuits, where the memory contents are retained as long as the power is on. Finally, the DRAM memory array must be precharged for the next memory access.

SRAMs are fast, but expensive due to their low density. DRAMs are relatively slow, but have high density and low cost because of their one-transistor cell structure and other circuit characteristics. DRAMs have been widely used to construct the main memory for most computer systems. The only exception has been for some vector computer systems where expensive SRAMs are used for the main memory. This is because high speed is the first consideration for those vector computers. All contemporary workstations, multiprocessor servers, and PCs use DRAMs to build the main memory modules, and only use SRAMs to construct caches.

#### 2.2.3 DRAM Access Request and DRAM Operations

As discussed earlier, an access to a DRAM bank may involve three types of operations: precharge, row access, and column access. Those operations are not performed in a fixed

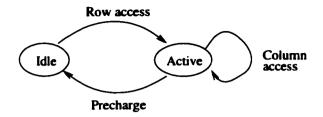

order, and some of them may not be necessary. The sequence of the operations to satisfy an access request depends on the bank state and the address to be accessed. From the viewpoint of scheduling, a memory bank can be in two states: active or idle [90]. When a bank is active, its row buffer contains valid data. When a bank is idle, it is precharged but the data in its row buffer is lost. Figure 2.2 shows how the bank state transits. We summarize the relationship between the operations and the bank states as following:

- Precharge can be performed when the bank state is active. After a precharge, the

data in the row buffer is lost, but the next row access can be performed. The bank

state will be idle after the operation.

- Row access can be performed when the bank state is idle. After a row access, a row

of data is read from the memory cell array to the row buffer. The bank state will be

active after the operation.

- Column access can be performed when the bank state is active. For a read request, a block of data is selected and read from the row buffer. For a write request, a block of data is selected and written to the row buffer. Only the data existing in the row buffer can be read or written. The bank keeps in the active state after the operation.

The sequence of operations that are necessary for an access request is dependent on the bank state and the data address. If the bank is active and the data to be accessed is already in the row buffer, only a column access is necessary. This type of access has the shortest latency. If the bank is active but the data to be accessed is not in the row buffer, then the sequence of operations is precharge, row access, and column access. This type of access has the longest latency. If the bank is idle, the sequence is always row access and column

Figure 2.2: Memory bank states.

access. Notice that precharge does not need a data address so it can be performed before a request arrives, and column access is always the last step for an access.

#### 2.2.4 DRAM Variants

There are a number of DRAM variants developed to improve DRAM latency and data transfer rate. Recent commercial examples include Synchronous DRAM (SDRAM), Enhanced SDRAM, Rambus DRAM, and Direct Rambus DRAM.

Synchronous DRAM (SDRAM): The data access operations of an SDRAM are synchronized with the processor by an external clock. The SDRAM technology improves upon the efficiency and the data transfer rate of DRAMs in three ways. First, SDRAM supports burst mode data access which reads or writes continuously allocated data blocks in the same row sequentially without idle intervals. The burst data access is defined by the starting address and the data length. Some asynchronous DRAMs also support burst mode data accesses, but require the memory controller to provide the column address for each data block. The burst mode in SDRAM significantly improves the data transfer rate. Second, the synchronous clock coordinates the processor and the main memory better, reducing processor idle time. Finally, SDRAMs

normally have two or four independent data banks, providing opportunity to overlap concurrent data accesses.

Enhanced SDRAM (ESDRAM): A small SRAM cache is integrated into the row buffer of each SDRAM memory bank. If an access is a hit in the buffer, the access time is equivalent to that of accessing the fast SRAM cache. The other advantage of ESDRAM is its ability of overlapping memory precharging and refreshing operations with cache accesses.

Rambus DRAM (RDRAM): A special high speed but narrow (one-byte wide) bus is designed to bridge between the processor and multiple memory banks. This bus is multiplexed for transferring address/command and data. Both edges of the bus clock signal are used for data transfer to double the data transfer rate. The memory banks in Rambus DRAM can be independently accessed, precharged, or refreshed to make accesses to different banks in a pipelining mode. Currently, Rambus DRAMs support eight or sixteen banks.

Direct Rambus DRAM (DRDRAM): This is an advanced version of RDRAM which provides a one-byte wide address bus and a two-byte wide data bus to connect a large number of memory banks (16 or 32). The number of row buffers is roughly an half of the number of memory banks, which makes each pair of adjacent banks share a row buffer. The buffer sharing reduces the hardware cost.

#### 2.2.5 Memory Access Scheduling

Today most DRAMs have multiple independent banks, and each bank can be operated independently. For example, one memory bank can be read when another memory bank is in precharge. Thus, contemporary DRAM memory systems can serve multiple accesses concurrently. Scheduling those concurrent requests can make a big difference in performance. Memory access scheduling can reduce access latency and improve bandwidth utilization by re-arranging the order and issue time of DRAM operations for a group of concurrent requests [75, 71, 48, 89, 90, 70].

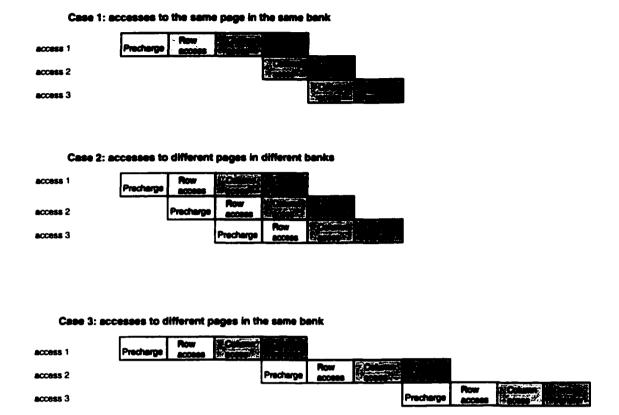

Concurrent memory accesses can be classified into one of the following three categories:

- Accesses to the same page in the same bank. These accesses not only fully exploit

the spatial data locality, but the corresponding operations can also be well pipelined.

Case 1 in Figure 2.3 shows the pipelined execution of three reads to the same page in

the same bank. Writes to the same page in the same bank can be well overlapped in

the same way. In both cases, the data bus is fully utilized during pipelined execution.

- 2. Accesses to different pages in different banks. Since the accesses can be done in parallel, the operations can also be well pipelined. Case 2 in Figure 2.3 shows the pipelined execution of three reads to different pages of different banks. Writes to different pages in different banks can be well pipelined in the same way. In both cases, the data bus is fully utilized during pipelined execution. Reads and writes can also be overlapped, except there is a small bus turn-around gap between a write and a following read.

- 3. Accesses to different pages in the same bank. These accesses not only have little data

Figure 2.3: Pipelined executions of three types of memory accesses. (This figure only shows the pipelining operations at a conceptual level.)

locality to exploit, the corresponding operations are difficult to pipeline as well. Case 3 in Figure 2.3 shows the pipelined execution of three reads to three different pages in the same bank. Precharge and row access are needed to initiate each access. The precharge of an access can be overlapped with the data transfer of another access. However, the DRAM row access of a request cannot start until the access ahead of it finishes. For each access in the pipelined execution, the idle time of the data bus can be the sum of a row access and a column. Similarly, write accesses to different pages in the same bank can not be effectively pipelined.

The more independent banks in a memory system, the larger the potential that page conflicts can be avoided (but a carefully designed memory address mapping is a necessity). Normally a memory system consists of a number of DRAM chips. Each DRAM chip has four or eight physically independent memory banks with current technique. The total number of independent banks depends on the organization of memory system, the number of chips. and the number of physical banks in a chip. Rambus DRAM systems tend to have more independent banks than a conventional SDRAM systems. For example, a Rambus DRAM system with 8 chips of 4 physical banks each have 32 independent banks. In comparison. a SDRAM system with 128-bit bus, 8 chips with 16-bit data output and 4 physical banks have only 4 banks; this is because the 8 chips must be operate together to supply 128-bit data to the bus.

Another scheduling issue is to decide the time to precharge a bank when it has no pending requests. There are two strategies: close page and open page. The close page strategy begins the precharge immediately after the current column access finishes. The next access to the bank will require a row activation and a column access. In contrast, the open page strategy delays the precharge, hoping that the next access is a row buffer hit, thus only the column access is needed. However, if the next access is a row buffer miss, all three operations will be required. Which strategy wins depends strongly on the page hit rate. If the hit rate is high, then the open page strategy is likely to reduce the memory stall time<sup>2</sup>. The row buffers are like a cache with a small number of blocks with very large cache size. It is well known that the performance of such a cache structure is comparable

<sup>&</sup>lt;sup>2</sup>The memory stall time is not decided only by the hit rate, especially for dynamically scheduled processors. In the general trend, however, the memory stall time decreases as the hit rate increases.

to large caches with small block size. There is a great potential to exploit this cache.

Recently, multi-channel memory systems have been used with high performance processors that require high bandwidth DRAM memories. Each channel can be scheduled independently. Direct Rambus DRAM is such a representative memory system. A Direct Rambus DRAM system generally consists of multiple channels, where each channel provides 1.6 GB/s bandwidth. Each channel has its own row control bus, column control bus, and two-byte wide data bus. The separation of row and column control buses eliminates the contention in the address bus between row operations (precharges and row activations) and column accesses. The bus clock rate is 400 MHz and the data is transferred on both edges of the clock. The row and column addresses/commands and the data are transferred in packets, each taking four bus cycles. The minimal data packet length is 16 bytes. Each channel can connect multiple devices (chips). Each device can have 32 banks and 33 half-page row buffers (this may vary according to the configuration). Those banks may be operated independently, which provides high concurrency at the bank level. The Intel Pentium 4 processor supports two channels, and the Compaq Alpha 21364 processor supports up to eight channels.

## 2.3 Dynamically Scheduled Superscalar Processors

The processor model has significant impact on the design and optimization of memory systems. The work in this dissertation is done in the context of dynamically scheduled superscalar processors with the following features:

- Dynamically scheduled [3]: The processor can *issue* (start the execution of) instructions out of program order. An instruction can be issued as long as previous instructions that provide its inputs have finished, and the hardware resources for the execution are available.

- Multiple issue: Multiple instructions can be issued every processor cycle. If the

processor is capable of issuing n instructions per cycle, it is called an n-way processor. Most contemporary processors are from 2-way to 8-way. The actual number of

instruction issued per cycle may be less than n.

- Speculative execution: The processor may issue instructions speculatively to exploit more instruction-level parallelism before their dependencies are fully examined.

In case the speculation is wrong, the execution of the related instructions is nullified.

- Non-blocking load: The processor may not stall when a cache miss happens upon

the execution of a load instruction. The execution of the load instruction must be

suspended, but the processor can issue other instructions that are not dependent on

the load instruction.

One would think that dynamic scheduling combined with a non-blocking load can eliminate the processor stall due to memory accesses. In fact, the processor can tolerate only the latency of L2 cache accesses. For a 2GHz processor, the latency of DRAM accesses is around one hundred processor cycles, while the processor can tolerate a delay of about ten cycles.

On the other hand, superscalar processors can reduce memory stall time from that of simple processors as they increase the concurrency of DRAM accesses. A processor can issue

dozens of instructions before it stalls for a cache miss, and is likely to find more cache misses during this period. This phenomena, called miss clustering, is widespread in the execution of realistic benchmark programs. Then, with proper hardware support, the processor can make multiple DRAM access requests to the DRAM memory system. An advanced DRAM memory system can serve those requests in parallel, reducing the average latency of DRAM accesses. Such an example has been shown in Figure 2.3.

## Chapter 3

# Evaluation Methodology: An

# **Experimental Approach**

We have extensively used architectural simulation and standard benchmarks to evaluate our software methods and hardware designs. We conduct almost all experiments using SimpleScalar [15], a set of simulation tools designed for program performance analysis and detailed microarchitectural modeling. To evaluate our hardware designs, we have incorporated new software modules in the simulator to simulate those hardware components. The only exception is the study in Chapter 4, in which we use direct measurements and SimOS [91] simulator to do performance evaluation. We have run SPEC95 [108] and SPEC2000 [45] benchmark programs and TPC-C [112] workload in the simulation environment to evaluate the performance of our designs.

This rest of this chapter is organized as follows. Section 3.1 discusses the background of architectural simulations. Section 3.2 introduces the SimpleScalar tool set. Section 3.3 describes our extension to SimpleScalar. Finally, Section 3.4 introduces SPEC95 and SPEC2000 benchmark programs and TPC-C workload.

#### 3.1 Architectural Simulations

Simulation is currently the predominant method for performance evaluation in computer architecture research, complemented by direct measurement and analytical modeling. For example, among 27 papers published in proceedings of the 29th International Symposium on Computer Architecture (ISCA-29, 2002), 24 papers use simulators as the major tool of performance evaluation. The authors come from both academia and computer industries such as Intel, IBM, HP, and Sun. (In fact, those companies have their own teams developing high-fidelity simulators to validate the design of their products.)

The use of simulation becomes popular as architects and researchers study advanced techniques to exploit instruction-level parallelism. Using analytical modeling to evaluate those techniques is extremely difficult, if not infeasible. The other alternative, direct measurement, is not available until a prototype can be made. Thus, simulation has become the only realistic choice in most cases. After years of development, today's architectural simulation has the following merits:

- Simulation of native ISA (Instruction Set Architecture): The simulators can emulate the execution of native binary codes (compiled on a real machines) without any alternation, and produce exactly the same results as on the real machine.

- Cycle-by-cycle accuracy: Detailed simulators model the status of processor components, including registers, instruction fetch with branch prediction, scheduling logic, functional units, L1/L2 caches, and memory. The status changes of those components are accurate cycle by cycle.

Modular design: A good simulation program consists of well designed modules. Architects and researchers, as users of the simulation program, can easily change existing modules or incorporate new modules to test and validate their ideas.

The three most popular collections of architectural simulation software are:

- SimpleScalar [15]: SimpleScalar is a tool set of simulation that contains several simulators providing different simulation detail levels. It was originally developed in the Computer Sciences Department at the University of Wisconsin-Madison. Now SimpleScalar can emulate four ISAs: Alpha. PISA, ARM, and x86. SimpleScalar is widely used in academia and industry and for both research and instruction. Section 3.2 describes SimpleScalar in more detail.

- SimOS [91]: SimOS is developed in the Department of Computer Science at Stanford

University. It is a complete machine simulation environment for both uniprocessors.

shared-memory multiprocessors, and a network of uniprocessors or multiprocessors.

It models the MIPS R4000 and R10000 and allows the IRIX 5.3 OS to run on the top

of the simulator. An extension of SimOS models the Digital Alpha processor families

and supports Digital Unix OS.

- RSIM [50]: RSIM (Rice Simulator for ILP Multiprocessor) is an architectural simulator for shared-memory multiprocessors based on dynamically scheduled processors.

It was developed at the Department of Electrical and Computer Engineering at Rice University.

Developers of those software tools have made the source code open and granted licenses to academic users free of charge. Nowadays, those tools have been widely used as simulation infrastructures on which researchers are able to make their own extensions. Proprietary simulation software has also been developed in industry, but those programs are normally not available for academic users.

Although architectural simulation is powerful, it has several limitations. First, the speed of high-fidelity simulation is much lower than that of real machines. The simulation slow-down, i.e., the time to finish the execution of a program on a simulator vs. that on a real machine, ranges from 3000 to 10000 for uniprocessor simulation. This fact limits the variety of workloads and the number of configurations that can be investigated, and incurs a high computation cost for running simulations. Second, the development and maintenance of high-performance simulation infrastructures have become very expensive, requiring extensive human and equipment support. Finally, validating simulation is a daunting task. Because of its complexity, identifying errors in simulation software is extremely difficult. Simulation developers did make efforts to validate simulation infrastructures against real machines [39, 28]. However, the results were not available until years after those simulation tools had been extensively used.

## 3.2 SimpleScalar Tool Set

The SimpleScalar tool set [15] is a suite of processor simulation tools containing both detailed and high-performance simulations. Ported to multiple instruction sets including Alpha, PISA (Portable Instruction Set Architecture), ARM, and x86. SimpleScalar has provided a powerful simulation infrastructure for both academic and industry users. Many extensions have been made to SimpleScalar, including value prediction, trace cache, multipro-

Figure 3.1: Processor pipeline in SimpleScalar. (from [15], reproduced with permission.)

cessor, and multithreaded processor. According to news on <a href="http://www.simplescalar.com/">http://www.simplescalar.com/</a>. the SimpleScalar web site, SimpleScalar is used by more than two out of five papers published in the 34th International Symposium on Microarchitecture (2001), more than one third of the papers in the 8th International Symposium on High-Performance Computer Architecture (2002), and more than one half of the papers in the 29th Annual International Symposium on Computer Architecture (2002).

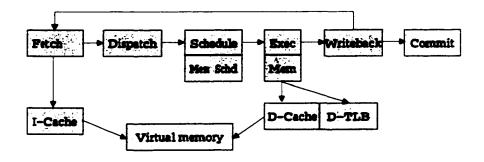

We have used the *sim-outorder* program in the SimpleScalar tool set to obtain most performance results reported in this dissertation. Sim-outorder simulates the full detail of a dynamically scheduling processor. It is a cycle-driven simulation: the simulator tracks the change of the processor status every cycle, including of pipeline, register, load/store queue, cache, TLB, and so on. The pipeline of the modeled processor has five stages: fetch, dispatch, exec/mem, writeback, and commit, as shown in Figure 3.1.

## 3.3 Our SimpleScalar Extensions

We have made a set of extensions to sim-outorder to model the main memory system in detail. The original sim-outorder implementation models a "perfect" main memory systems, of which the memory access latency is a constant for a cache fill request. Our extensions model the full detail of DRAM memory systems, including bus contention, bus synchronization, bank status, row access, column access, precharge, and refresh. We also model a writeback buffer and an MSHR unit.

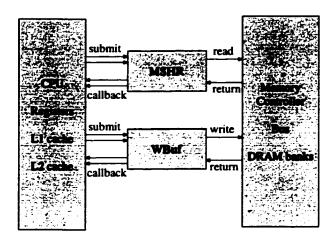

Figure 3.2 shows the overall structure of the extensions we have made. First, we modified the interface of the cache module in sim-outorder. The original cache module returns a fixed integer value of the access latency for both cache hit and miss. When a cache miss happens, the new cache module returns a negative value when it detects a cache miss. This change allows the miss latency be determined after the detection of a cache miss. The new module submits cache-related information to the MSHR module, and the processor module submits processor-related information to the MSHR module. The MSHR module records both sets of information and sends a message to the DRAM module. The DRAM module simulates the DRAM operations, determine the finish time, and send a message to the processor to inform it that the DRAM access has finished. Then the MSHR module find out the related miss information and make a requests to perform cache fill and to wake up the waiting instruction.

The interactions between the modules are based a message passing functionality that we added into SimpleScalar. With this functionality, a simulation module can send/receive messages to/from other modules. When sending a message, a module provides the des-

Figure 3.2: Diagram of our extension of DRAM memory simulation.

tination module, the message type, the time when the message should be delivered, and a flexible set of parameters. Upon receiving a message, the message-driven code of the destination module parses the message and processes accordingly.