### W&M ScholarWorks

Dissertations, Theses, and Masters Projects

Theses, Dissertations, & Master Projects

1992

### Code generation using a backtracking LR parser

Laurie Anne Smith King College of William & Mary - Arts & Sciences

Follow this and additional works at: https://scholarworks.wm.edu/etd

Part of the Computer Sciences Commons

#### **Recommended Citation**

King, Laurie Anne Smith, "Code generation using a backtracking LR parser" (1992). *Dissertations, Theses, and Masters Projects*. Paper 1539623820. https://dx.doi.org/doi:10.21220/s2-qkrj-qd04

This Dissertation is brought to you for free and open access by the Theses, Dissertations, & Master Projects at W&M ScholarWorks. It has been accepted for inclusion in Dissertations, Theses, and Masters Projects by an authorized administrator of W&M ScholarWorks. For more information, please contact scholarworks@wm.edu.

#### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

University Microfilms International A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 313/761-4700 800/521-0600

• • - --- •

Order Number 9804503

#### Code generation using a backtracking LR parser

King, Laurie Anne Smith, Ph.D. The College of William and Mary, 1992

Copyright ©1992 by King, Laurie Anne Smith. All rights reserved.

.

.

U·M·I 300 N. Zeeb Rd. Ann Arbor, MI 48106 .

·

#### CODE GENERATION USING A BACKTRACKING LR PARSER

A Dissertation

\_\_\_\_

Presented to

The Faculty of the Department of Computer Science

The College of William and Mary in Virginia

In Partial Fulfillment

Of the requirements for the Degree of

Doctor of Philosophy

bу

Laurie Anne Smith King

1992

Copyright © 1992 by Laurie Anne Smith King, All Rights Reserved

------

#### APPROVAL SHEET

This dissertation is submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy Laurie Anne Smith King

Approved, June 1992

Dr. William L. Bynum

Dr. Keith W. Miller

Dr. Larry J. Morell

Department of Computer Science, Hampton University

Kobert E

Dr. Robert E. Noonan

JC

Dr. J. C. Sanwal Department of Mathematics, The College of William and Mary

In memory of my grandmothers,

i

Hope Smith Shackson Focht and Gretchen Bergetta Smith Smith

## Table of Contents

|                  |                                                                                                                 | Lag  |

|------------------|-----------------------------------------------------------------------------------------------------------------|------|

| Acknowledgements |                                                                                                                 |      |

| List of Figures  | i de la companya de l | vi   |

| Abstract         |                                                                                                                 | viii |

| Chapter 1        | Introduction                                                                                                    | 2    |

| Chapter 2        | Blocking Problems in Parsing-based Code<br>Generators                                                           | 26   |

| Chapter 3        | A Backtracking LR Parser                                                                                        | 40   |

| Chapter 4        | Backing up over Semantic Actions                                                                                | 62   |

| Chapter 5        | Code Generation as Tree Transformations                                                                         | 69   |

| Chapter 6        | An Algorithm for Converting Tree<br>Transformations to an Affix Grammar                                         | 84   |

| Chapter 7        | Reparse Backup                                                                                                  | 95   |

| Chapter 8        | Conclusion                                                                                                      | 101  |

| Appendix A       | Peephole Optimization of the Intermediate Code                                                                  | 106  |

| Appendix B       | Computing Usage Counts                                                                                          | 111  |

| Appendix C       | Instruction Selection                                                                                           | 114  |

| Appendix D       | Selected Test Runs                                                                                              | 117  |

| Appendix E       | Reparse Backup Example Revisited                                                                                | 142  |

| Appendix F       | TTL and a Backtracking LR Parser Produce a Recognizer for any Recursively Enumerable                            |      |

|                  | Language                                                                                                        | 145  |

| Bibliography     |                                                                                                                 | 158  |

.

#### ACKNOWLEDGEMENTS

I wish to express my gratitude to the many people who helped me finish (finally) this dissertation.

To Bob Noonan, my advisor, for his unending patience and of course wise guidence. To the rest of my committee, Bill Bynum for his ability to put negative results in a positive light, Keith Miller for all those late night discussions, Larry Morell for his perennial flow of ideas, and JC Sanwal for teaching me all I know about circuit design and analysis. To Bob Collins who gave me the confidence to get started and keep going.

To my friends who stuck by me when I was so very hard to get along with, Tracy Camp for that graduate student comraderie, SueAnne Kyle Johnson for those long distance phone bills, Pat Meszaros for loving my daughter, Bob and Debbie Noonan for listening to my whining and great skiing, Karen and Louis Slothouber for awesome bridge games and great beach trips, and Glenda White for girl's night out.

To my relatives who encouraged me and kept me sane, my sister Kristen Smith, her fiance Todd Barnett, my cousin Charlie Viles and his wife Emily West.

To my grandfather, Clyde T. Smith, who was very generous in his financial support.

To my parents for their love and support, David Wm. Smith who pushed me to be the best and Beverly Smith who thought I was.

To my daughter, Madison Hope Lucas, who kept everything in perspective.

And finally to my husband and best friend, Stef Lucas, a true Renaissance man, without whose help I never would have finished my PhD.

## List of Figures

| Figure            |                                                                                                                                                  | Page          |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|

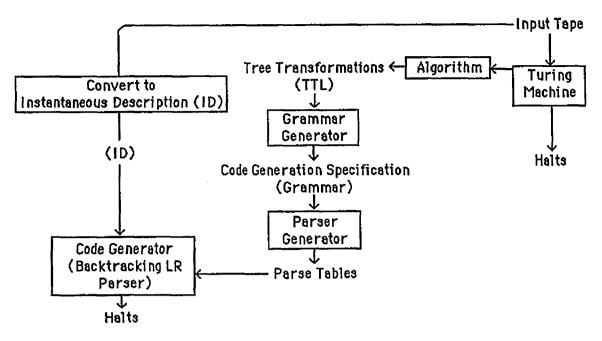

| 1.1<br>1.2<br>1.3 | Tree-Rewrite Rule for an Addition Instruction<br>Twig Specification for an Addition Instruction<br>Backtracking LR Parsing-based Code Generation | 9<br>10<br>24 |  |

|                   |                                                                                                                                                  |               |  |

| 2.1               | Intermediate Code Tree for $a := b + c$                                                                                                          | 27            |  |

| 2.2               | MD1: A Partial Code Generation Specification                                                                                                     | 28            |  |

| 2.3               | MD1-ambiguous                                                                                                                                    | 29            |  |

| 2.4               | MD2: Semantic Information Encoded Syntactically                                                                                                  | 30<br>30      |  |

| 2.5               | MD1-ambiguous with Semantic Restrictions<br>MD3 with Semantic Restrictions                                                                       | 36            |  |

| 2.6               | WD5 with Semantic Restrictions                                                                                                                   | 50            |  |

| 3.1               | Example Grammar MD4                                                                                                                              | 42            |  |

| 3.2               | •                                                                                                                                                | 43            |  |

| 3.3               | The Forward Parsing Algorithm                                                                                                                    | 45            |  |

| 3.4               | GetNextInput                                                                                                                                     | 46            |  |

| 3.5               | DoShift                                                                                                                                          | 46            |  |

|                   | DoReduce                                                                                                                                         | 46            |  |

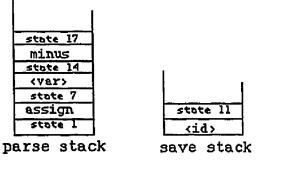

|                   | Parse Trace using Grammar MD4                                                                                                                    | 48            |  |

|                   | DoBacktrack Algorithm                                                                                                                            | 49            |  |

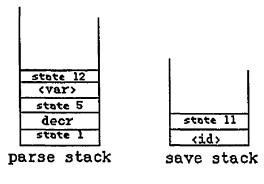

|                   | Another Parse Trace using Grammar MD4                                                                                                            | 53            |  |

|                   | Grammar MD5                                                                                                                                      | 54            |  |

|                   | The Parse Table for Grammar MD5                                                                                                                  | 54            |  |

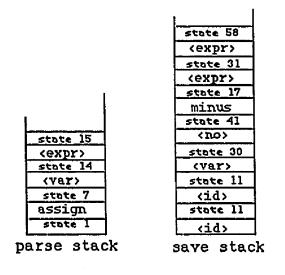

| 3.12              | Parse Trace using Grammar MD5                                                                                                                    | 60            |  |

| 4.1               | Grammar MD5 with Semantic Actions                                                                                                                | 64            |  |

| 4.2               | No Semantic Information Changed                                                                                                                  | 65            |  |

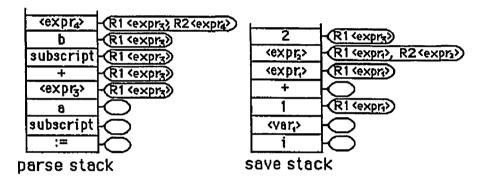

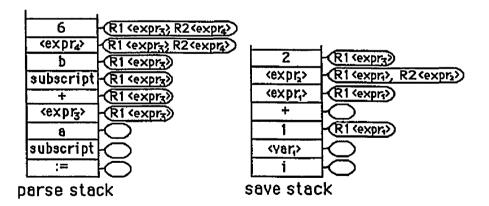

| 4.3               | Register 1 is Allocated                                                                                                                          | 65            |  |

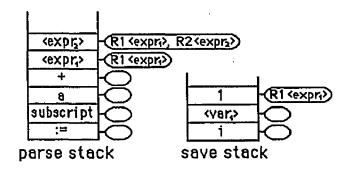

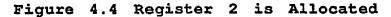

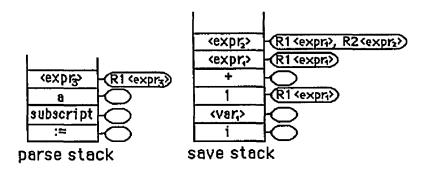

| 4.4               | Register 2 is Allocated                                                                                                                          | 66            |  |

| 4.5               | The Plus Operation is Performed                                                                                                                  | 66            |  |

| 4.6               | Trying the Shift Option                                                                                                                          | 67            |  |

| 4.7               | Register 2 is Reallocated                                                                                                                        | 67            |  |

| 4.8               | Block Trying to Apply Increment Instruction                                                                                                      | 67            |  |

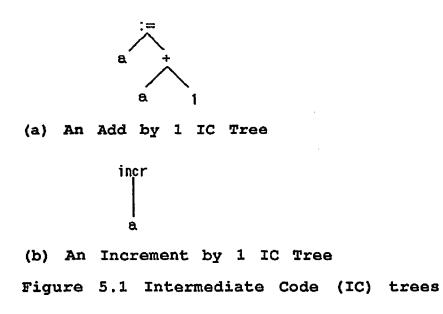

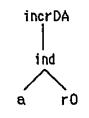

| 5.1               | Intermediate Code (IC) trees                                                                                                                     | 71            |  |

| 5.2               | A Machine Code Tree                                                                                                                              | 71            |  |

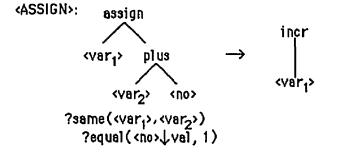

| 5.3               | Recognizing an Expression                                                                                                                        | 72            |  |

| 5.4               | A Rearrangement Tree Transformation                                                                                                              | 73            |  |

| 5.5               | A Replacement Tree Transformation                                                                                                                | 73            |  |

•

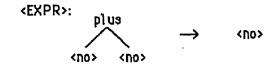

| 5.6  | A Conditional Tree Transformation                    | 73  |

|------|------------------------------------------------------|-----|

| 5.7  | Backtracking LR Parsing-based Code Generation        | 75  |

| 5.8  | Two Transformations to Machine Instructions          |     |

|      | for Addition                                         | 81  |

| 5.9  |                                                      | 82  |

|      | A Transformation to Machine Code for a Register Load | 82  |

| 0.10 |                                                      |     |

| 6.1  | TTL Syntax                                           | 84  |

| 6.2  | The Affix Grammar Rule Syntax for the                |     |

|      | TTL Rule of Figure 6.1                               | 85  |

| 6.3  | Tree Construction Procedures                         | 87  |

| 6.4  | Transformation Construction Algorithm                | 88  |

| 6.5  | Simple Reduction Transformation                      | 90  |

| 6.6  | Transformations with Conditions                      | 91  |

|      | Transformations with Actions                         | 92  |

| 6.8  | Rearrangement Transformations                        | 93  |

| 0.0  | Koarrangomont Transformations                        | 20  |

| 7.1  | Reparse Backup Algorithm                             | 97  |

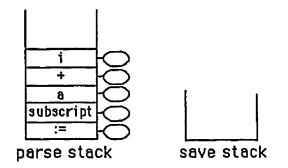

| 7.2  | IC for Assignment Statement                          | 98  |

| 7.3  | A Constant Folding Tree Transformation               | 98  |

| 7.4  | Parse State before Constant Folding                  | 98  |

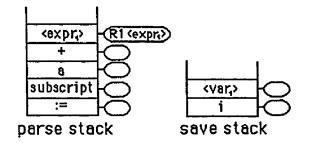

|      | Parse State after Constant Folding                   | 99  |

|      | Applying the Decr Tree Transformation                | 100 |

| 7.7  | Parse State after Parsing Decr Rewrite               | 100 |

|      |                                                      |     |

| E.1  | Parse State after Incorrect Reparse Backup over      |     |

| -    | Constant Folding Transformation                      | 143 |

| E.2  | Expression Transformations                           | 143 |

| E.3  | Parse State after Reduce by Rule 1                   | 144 |

| E.4  | Parse State after Reduce by Rule 2                   | 144 |

|      |                                                      |     |

| F.1  | Language Generators and Recognizers                  | 145 |

| F.2  | Turing Machine Simulation                            | 146 |

| F.3  | Turing Machine Simulation Using ID                   | 148 |

|      |                                                      |     |

· ·····

#### ABTRACT

Although the parsing phase of the modern compiler has been automated in a machine independent fashion, the diversity of computer architectures inhibits automating the code generation phase. During code generation, some intermediate representation of a source program is transformed into actual machine instructions. The need for portable compilers has driven research towards the automatic generation of code generators.

This research investigates the use of a backtracking LR parser that treats code generation as a series of tree transformations.

Code Generation Using A Backtracking LR Parser

-----

# Chapter 1 Introduction

"A compiler's primary function is to compile, organize the compilation, and go right back to compiling. It compiles basically only those things that require [sic] to be compiled, ignoring things that should not be compiled. The main way a compiler compiles, is to compile the things to be compiled until the compilation is complete." The definiton of a compiler given by a student in an Introductory Computer Science course. (1992)

#### **1.** Motivation and Goals

For the past two decades, a considerable amount of research has been devoted towards reducing effort required to construct quality compilers. The rapid pace with which new machine architectures become available, and the desire to port compilers to take advantage of these new architectures has motivated much of the research.

Design and implementation techniques for handcrafting compilers are ill-suited to the complexity of the complex clerical task performed by compilers. Despite the careful attention to the software design principles employed by early compiler writers, even compilers that had been in production for some time often have lingering bugs. Even if better techniques for writing compilers by hand were developed, the speed with which handcrafted compilers could be produced would be insufficient. Formal methods which would automate parts of the compiler creation task are required. Consequently, much research effort has been devoted towards the creation of *compiler-compilers*, systems that automatically generate a compiler or translator from a specification.

Applying a divide-and-conquer strategy, compilers are divided into a front-end and a back-end. The front-end recognizes and parses a source language, and ultimately produces intermediate code from a source program. The back-end translates the intermediate representation of a source program into object code specific to a given target machine.

Research of the 1960's and 1970's, while ignoring the semantic phase, has for the most part automated the front-end in a machine independent fashion. Advances in the use of grammars and parsing has made it possible for parsers to be automatically generated from a grammar-based description of the programming language. Now a substantial compiler front-end can be implemented in a one semester, undergraduate course using a compiler-compiler.

However, the diversity of computer architectures and complexity of the code generation task has inhibited automating the creation of code generators. For the most part, the back-end has been created manually; although high quality code generators can be created this way, hand generation is tedious and lacks the formalisms required to easily demonstrate the correctness of an implementation. In short, the creation of code generators suffers from the same problems that plagued the creation of compiler front-ends twenty years ago. A goal of recent research is to create code generators from machine descriptions or code generator specifications by developing a codegenerator-generator.

Using an algorithm to create code generators from machine descriptions or specifications is easier and faster. The algorithm can be implemented and verified once, and thereafter the user's responsibility consists only in providing an adequate machine description/specification. A further research goal is the automatic generation of code generators which produce "good" code, code that not only takes advantage of special use instructions and machine idiosyncracies but also which contains no dead code, i.e., code which has no effect.

#### 2. Background

This chapter reviews research on the automatic derivation of code generators from machine descriptions or code generation specifications. To date, the approach generally taken has been one of divide-and-conquer. Code generation has been conceptually carved into three main tasks: instruction selection, peephole optimization and register allocation/assignment. Instruction selection is the translation of intermediate code trees generated by the compiler front-end into object code, usually either assembler or machine code. Peephole optimization improves object code by correcting inefficient code sequences, selecting special case instructions, and eliminating redundant object code. Register allocation/assignment determines which values will reside in each register. Compiler back-ends are usually implemented by dividing these tasks into subphases.

Until recently, attempts to automate code generation have concentrated on a single task of code generation and so formalisms have been developed for each task separately. Even though the division between tasks is not strict, each can be automatically created as an independent phase that runs sequentially. For example, research which concentrates on instruction selection must consider the register allocation/assignment phase and vice versa because of its impact on optimal instruction selection.

In what follows, instruction selection, peephole optimization, and register allocation/assignment will be discussed in detail by reviewing relevant papers from the recent literature. Complexity is reduced by focusing on an individual phase, which poses sufficient challenges in itself. However, the phases are naturally interdependent and there are advantages to allowing all three phases to operate simultaneously in an integrated code generator. Armed with a better and more formal understanding of each individual phase, recent research has attempted to create integrated code generators from machine descriptions or code generation specifications. Consequently, we will first describe attempts to automate each phase as a relatively independent entity and then discuss the interdependence between the phases and review recent attempts to integrate the three phases.

#### 3. Instruction Selection

Many advances have been made in automating instruction selection. The instruction selector generators described herein consist of machine independent instruction selection algorithms which operate from a machine description or code generation specification.

The research described views instruction selection as a pattern matching operation. The code generation specification is encoded in a table and pattern matching algorithms match intermediate code trees to perform instruction selection. Three implementations of pattern matched instruction selection are presented: LR parsing approaches, an A.I. approach, and a dynamic tree-matching approach.

#### 3.1 Instruction Selection Via Parsing

The first practical automatic generation of a code generator was made by Glanville and Graham [GlGr78], who use an LR parser as the machine independent instruction selection algorithm. The grammar is the code generation specification because it describes how intermediate code trees are converted into machine instructions. Descriptive information about the target machine in the form of a grammar is used to create LR parser tables.

Productions are classified into three kinds [GaFi85]: address mode productions, instruction selection productions and transfer productions. Address mode productions map intermediate code addresses into machine addresses. An instruction selection production specifies an intermediate code tree pattern on the right hand side, with the left hand side specifying the result, typically a data type. Transfer productions allow the code generator to shift an operand's storage location, for example to perform data type conversions.

Grammar rules are ordered to create a table in which the cheapest/best instruction is tried first, described as a *locally greedy heuristic* [Hen84] or as a maximal munch strategy [Cat78]. Other approaches [SpTu87] have attempted to perform cost analysis during parsing beyond the simple ordering of the productions. Spector and Turner have implemented a dynamic programming algorithm that extends cost analysis by considering the actual time or space cost of selecting each nonterminal available in each state during parsing. Ganapathi and Fischer [GaFi85] extended the application of parsing techniques to instruction selection. They describe the instruction set of a target architecture using affix grammars in which attributes containing semantic information influence the construction of the parse tree.

The parsing approach for the automatic derivation of code generators has several advantages. Parsing is fast and provably correct with respect to the grammar, something ad hoc pattern matching algorithms cannot boast. A code generator built with this approach can benefit from any advances in parsing research. Furthermore, the code generator can be incrementally improved by adding new productions to the code generation specification. Another advantage of this approach is that the code generator can be retargeted quickly by modifying the code generation specification grammar.

Unfortunately, several problems arise from parsing using contextfree grammars. The machine language must be uniform<sup>1</sup> [GlGr78] for the conflict-resolution rules to recognize the whole language. The code generation specification is usually ambiguous because machines often have several ways of accomplishing the same task; naturally, code generation specification grammars reflect this ambiguity. Secondly, problems of syntactic or semantic blocking result from the locally greedy heuristic which resolves shift-reduce conflicts in favor of the shift, details of which are discussed in Chapter 2. Finally, the Achilles heel of the parsing method is a reliance on the non-trivial creation of hand-crafted grammars.

3.2 Cattell's Approach

Cattell's code generation algorithm [Cat80], operates directly off an ISP-style machine description. Heuristic searching and other A.I. techniques are used in the algorithm which is machine independent but uses machine dependent tables to select instructions.

Instruction selection is template driven; a new set of templates generates code for a different machine. The templates are patternmatched against intermediate code trees and each template

<sup>&</sup>lt;sup>1</sup>In a uniform language, the operands to an operator are valid independent of context so that if an operand is valid on the left of a binary operator, it is also valid on the right of the operator.

corresponds to a sequence of machine instructions. Instruction selection consists of emitting the machine code associated with a template when a match is found. The instruction selection algorithm is straightforward; the difficulty lies in creating the template table, called the MT. At code generator generation time, Cattell's method automatically selects both the possible templates and the instruction(s) associated with each template and thus creates the MT.

The code generator generator inputs a machine description and outputs the MT. An ISP machine description is manually transformed into a tree production machine description. Instruction function (such as addition for an ADD) is separated from operand addressing details (such as whether operands are registers or memory locations) which reduces the size of the machine description. The procedures SELECT and SEARCH build the template table, (MT), from the tree production machine description. SELECT chooses the special cases, trees, to be included in the MT and SEARCH finds code sequences that represent these trees. SELECT has a double duty because it also finds the best code sequence for each tree.

SELECT ensures that every intermediate code tree can be matched by a template in the MT. First, SELECT creates templates for all subtrees which map directly into machine instructions so that the MT includes all subtrees which can be matched by a single instruction. Second, some additional templates are added to generate more efficient code. Third, templates are included for subtrees of the form  $A \leftarrow B$  for every pair of distinct address modes A and B to enable data transfers Fourth, templates for every tree production operator are included and last, templates are included for control operators (e.g. loops and branches).

SEARCH cannot return all possible code sequences given a goal subtree, so two techniques are used to reduce the size of the search space: means-ends analysis and problem reduction. Means-ends analysis is used to explore nodes which are closer to the goal node first. Problem reduction decomposes a difficult problem into a set of smaller problems. SEARCH returns an instruction if the goal tree matches an instruction assertion exactly, otherwise it applies decomposition axioms and applies itself recursively to each new goal tree. If elements in a set of instructions are semantically close<sup>1</sup> to

<sup>&</sup>lt;sup>1</sup>As a heuristic measure of similarity, Cattell uses the primary operator of two trees.

the goal tree, then transformation axioms are applied recursively so that the transformed goal tree may be used as the goal tree.

The MT is used at code generation time by a pattern matching algorithm which matches templates in the MT against the intermediate code. The templates in the MT are ordered so that those which represent the least expensive instructions will be attempted first. If a template fails to match, the code generation algorithm continues by attempting a more expensive template. The code generator handles mismatches between the IC operands and the template, moving the operands to locations compatible with the template.

As with the parsing approaches, an advantage of Cattell's scheme is that much of the work is done at code generator generation time, rather than within the resulting code generator itself. SELECT and SEARCH operate at code generator generation time, when the MT table is created, but the final code generator just uses the MT. Cattell offers experimental evidence that his heuristic search for code sequences tends to find the optimal code sequences. Parsing approaches have difficulty with semantic blocking and Cattell's approach avoids semantic blocking because his method can "backtrack." Also, the size of the machine description and the number of instructions on the target machine have little effect on the speed of the resultant code generator. In comparison, parsing approaches only pattern match in the abstract sense, by wandering through the state tables, so they are inherently faster than Cattell's method, which really does pattern matching.

The translation of an ISP description into the initial tree production machine description is done manually and takes approximately one man-week according to Cattell. A drawback to this method is, SEARCH is not guaranteed to ever find an applicable code sequence for a given subtree, or even to terminate at all. Finally, Cattell acknowledges that more research is required to describe machine data types and other special architectural features like caches.

#### 3.2 A Tree Matching Approach

Another approach [AhGaTj89] to instruction selection views the intermediate code as an actual, versus a conceptual, tree and pattern-matches using tree patterns and tree rewrite rules. Central to this approach are two algorithms: an efficient tree matching

8

algorithm to recognize the intermediate code and a dynamic programming algorithm to attempt different combinations of tree matches in search of the one which generates the most efficient object code. Both algorithms must be fast in order to compete with LR parsing.

A special language, Twig, was developed for writing code generators. Efficient tree matching with dynamic programming are embedded as part of Twig. The compiler writer specifies the code generator by writing a Twig specification (program). The Twig compiler creates the desired code generator.

Twig code generator specifications consist of a list of tree-rewrite rules. Each rule has the form:

replacement

$$\leftarrow$$

template { cost } = { action }

where *replacement* is a single node, *template* is a tree, *cost* is a code fragment that computes the cost associated with the rule, and *action* is a code fragement. During code generation, templates are pattern matched against the IC. When a template matches, the IC subtree is reduced to the associated replacement node and the action part emits the corresponding machine code. The cost part measures the efficiency of the emitted code. Both the cost and action parts of the rule are code fragments supplied by the compiler writer.

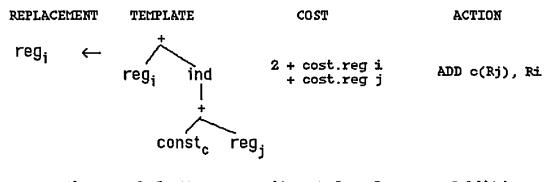

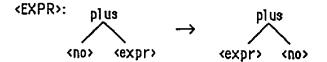

For example, Figure 1.1 depicts a rewrite rule for an addition instruction for a VAX-like target machine. The replacement node and IC tree template appears on the left, followed by the cost and and add instruction.

Figure 1.1 Tree-Rewrite Rule for an Addition Instruction.

The Twig specification for the rule in Figure 1.1 appears in Figure 1.2

```

reg:plus(reg, ind(plus(const, reg)))

{cost = 2 +$%1$^cost + $%3$^cost;}

{ emit(''ADD'', $2$, $1$, 0);

return($1$);

};

Figure 1.2 Twig Specification for an Addition

Instruction.

```

In the Twig specification, \$n\$ denotes the nth labeled leaf, \$n\$ denotes the nth child of the root of the template and it is assumed that the emit routine will convert ind(plus) into the correct machine addressing mode.

Instruction selection consists of three passes over the IC. The first pass attempts to pattern match all templates in the Twig specification, computing the cost associated with each match. The cost of each template match at a node can be computed independent of the node's parents so that a minimum cost cover can be computed in a single bottom up pass. Furthermore, a vector of costs is computed in which each vector entry corresponds to the cost of a template match for a given number of available registers. Hence register availability plays a role in instruction selection. The second pass performs register allocation based on the cost vector, and the third and final pass traverses the IC performing actions associated with each node to actually emit the chosen machine instructions.

Tree-based pattern matching is less formal than LR parsing and, in the current implementation, the resultant code generators are slower. Also, Twig does not do common subexpression elimination, algebraic simplification, or other high level optimizations. But the authors claim a number of advantages of tree patterns over LR parsing for instruction selection, most notably a simplified code generator specification, freedom to write rules in any order without regard for pattern matching conflicts, and the production of code that is optimal with respect the cost information provided.

#### 4. Peephole Optimization

Peephole optimization improves object code by correcting inefficient code sequences, selecting special-case instructions, and eliminating redundant or dead object code. Inefficient code most often arises as compilers generate intermediate code or object code in chunks or blocks. Peephole optimization allows the code on the edges of the blocks to be optimized. The classic example is the case of replacing a jump to another jump with a single jump instruction. An example of a special-case instruction is the substitution of an increment for an add by 1. Redundant or dead code is illustrated by an if statement immediately after a while. If the two have opposite conditions, testing the condition in the if statement is redundant and the code can be pruned. Conversely, if the two have the same conditions then the if statement is dead code and should be removed.

Peephole optimizations are necessary because often the optimizations are not apparent until after instruction selection. For example, the compiler cannot anticipate a priori that a jump will be to another jump. Secondly, performing peephole optimizations after the code is created is often more efficient than attempting optimizations during code emission. Case analysis, for instance, can be used to determine whether an add can be replaced with an increment, but only at the cost of complicating and slowing the code emission.

Fraser [Fra79] initially described a peephole optimizer, PO, which performs general optimizations that are both machine-independent and are not part of global optimizations performed before instruction selection. The input to PO, is an assembly language program and a symbolic machine description. Three passes over the input are made. The first is a backward scan that determines the effect of the instructions. Instructions with no effect are removed. The next pass is a forward pass that replaces pairs of adjacent instructions by a single instruction when possible. The final pass replaces each instruction with the cheapest possible equivalent. Besides the obvious drawback of a narrow optimization window, this implementation was slow.

Davidson and Fraser [DaFr79] extended this research by further refining the peephole optimizer, PO. As in the original, PO makes three passes to optimize the program. The first pass, a backward scan, generates the effect of register transfer patterns and finds all dead cells, i.e. variables that are immediately changed without being used or condition codes that are not tested before they are reset. The list of dead cells is kept so that useless effects are ignored. When a branch is encountered, the list of dead cells is cleared because the list of dead cells depends on the instruction's lexical successor and the destination of the branch is unknown. The second pass, a forward scan, considers the combined effect of two lexically adjacent instructions. When possible, PO replaces each variable instance in the second instruction with variable values from the first. PO can collapse branch chains by treating a branch and its target as a pair. PO also removes any unreferenced labels because any instruction pair with a label on the second instruction cannot be collapsed. The third and final pass translates register transfers back into assembly code.

This research suggested that a naive instruction selection phase can generate good code if used with PO. Sometimes a greater context than a two or three instruction window is needed, for example PO cannot collapse an otherwise reducible pair separated by a third, uncombined instruction. The optimization window is physical and a logical window is desired.

Davidson and Fraser [DaFr84] continued their research resulting in an expanded, modified version of PO. This new PO is inserted into a compiler. The entire compiler is divided into five programs. The FRONT END produces machine code for an abstract machine with a small and regular instruction set. The CODE EXPANDER converts intermediate code to register transfers and also flags cells that are obviously dead. The CACHER eliminates common subexpressions in basic blocks. The CACHER also marks the last use of each cell so that COMBINER can delete instructions which set unused cells. Each instruction is linked to the first instruction that uses one of its results, using a counting algorithm described by Frieburghouse [Fri74]. This allows COMBINER to combine logically adjacent instructions rather than physically adjacent ones, correcting a deficiency of earlier research. The ASSIGNER maps an unlimited number of pseudo registers onto hardware registers, spills<sup>1</sup> when necessary, and translates register transfers into assembly code.

CACHER and COMBINER consider some register allocation details to ease the burden on ASSIGNER. CACHER records and replaces references to common subexpressions with simpler register references. CACHER also calculates use-lists (links from instructions to particular expressions) for dead variable analysis. When an instruction is replaced by a cheaper one, the use-list shows if a value

<sup>&</sup>lt;sup>1</sup>An excess demand for registers causes the contents of one or more registers to be stored in memory (to be reloaded when the value is needed) so that the register demand can be met.

in a register is no longer needed. These use-lists also provide the information to remove redundant loads from memory. After peephole optimization, ASSIGNER performs register assignment and translates the register transfers to assembly code. If a register must be spilled, CACHER's use-lists are used once again to determine the most-distantly-used register in order to minimize the number of spills.

A shortcoming is that some expressions can be recomputed faster than they can be spilled and reloaded. Furthermore, some spills and loads could benefit from further peephole optimization. Davidson and Fraser state that this problem can be corrected by combining CACHER, COMBINER and ASSIGNER (originally developed separately to simplify development and accommodate a small address space). Once phases are combined, the COMBINER can identify common subexpressions too small for CACHER to catch, and to optimize the instructions that ASSIGNER introduces.

#### 5. Register Allocation/Assignment

Register allocation determines which variables are stored in registers. Register assignment determines which specific registers will be used to hold a given variable's value. Using registers effectively is important for the generation of shorter, faster Retrieving values from registers is much faster than instructions. getting values from memory, so a good code generator will retain values in registers as long as possible if the value can be used in several instructions. Retaining values in registers also shortens the code somewhat because specifying a register address is shorter than specifying a memory address. Register allocation/assignment is complicated by machine idiosyncrasies. Special-case instructions often require their operands to be in a specific register, like the accumulator, so assigning a variable to the correct register will allow the use of such instructions without the overhead of a register swap. Still other instructions require operands in an even/odd register pair, which further complicates register allocation/assignment.

Two common problems arise during register allocation/assignment: the value retention problem and the register demand problem. The value retention problem occurs because the code generator tries to hold values in a register to avoid recomputing them, but must also decide when a value is no longer needed. The register demand problem occurs when there is an excess demand for registers and the code generator must choose which register to spill and reload. Both these problems must be addressed by a good register allocator.

#### 5.1 Register Allocation/Assignment Strategies

There are three general strategies for register allocation/assignment (RAA) which describe when RAA is performed relative to the instruction selection phase: pre-allocation, on-the-fly allocation, and post-allocation.

In a pre-allocation strategy, instruction selection is simplified because the register assignments inherently rule out the use of certain instructions, thus limiting the choices the instruction selector must make. Simplification is a double-edged sword: it also constrains instruction selection. For example, some instructions require their operands to be in an even/odd pair of registers. If the operands are not in the register pair, the instruction selector cannot use the instruction and suboptimal code may result. Furthermore, preallocation RAA could over-constrain instruction selection by eliminating all possible instructions, requiring the instruction selector to generate needless moves in order to emit code. Pre-allocation works best when all registers are equivalent (interchangeable within instructions) which minimizes the constraints on instruction selection imposed by the RAA.

The concept of pre-allocation is fundamentally flawed because instruction selection and RAA cannot be cleanly separated. The RAA needs knowledge of the available instructions to assign registers intelligently but the knowledge requires doing instruction selection. On the other hand, intelligent instruction selection requires knowledge of possible register allocations/assignments.

An on-the-fly RAA strategy allows the instruction selector to make choices as it generates code. An advantage over pre-allocation is that the RAA can be chosen to fit the instruction. In the case of an instruction with operands in an even/odd pair of registers, the instruction selector can insure that the operands are assigned to the register pair. When registers are exhausted, a register-spill can be generated or a different instruction chosen. For instance, a memoryto-memory instruction will avoid the spill since no registers are required. The strategy complicates instruction selection by increasing the choices for the instruction selector. Naturally, register

14

spills are problematic when knowledge of a register's contents will be needed again is required to make the best register spill.

A post-allocation RAA operates with an instruction selector that assumes the existence of an infinite number of registers for use during instruction selection. The RAA's responsibility is the binding of the usually infinite number of psuedo registers to a fixed number of real machine registers. Binding occurs after instruction selection and/or peephole optimization. Because RAA occurs after instruction selection, the register allocator's task is simplified. The chosen instruction determines register assignments, so the allocator makes few decisions. When a register request cannot be satisfied, the allocator has no choice but to generate a spill. The generation of unecessary spills is a disadvantage of a post-allocation strategy.

#### 5.2 Global Versus Local RAA

RAA can be applied with either global or local strategies. Global register allocations are fixed across one or more basic blocks. Local register allocations are fixed within basic blocks but may change from one block to the next. A basic block is a sequential set of statements which contains no jumps or labels except at the beginning and/or end of the block.

Global RAA is illustrated best within loops, when the most frequently used variables within a loop are allocated to registers. In this way, the most frequently used variables are retrieved from memory only at the start of the loop and stored in memory only at the loop's end rather than at each loop iteration. Furthermore, the same variable might be used frequently in a series of loops. Global RAA would retrieve the variable from memory at the start of the first loop and retain the register allocation across the series of basic blocks. The variable would be stored in memory only at the end of the last loop.

In a local RAA scheme, registers are typically divided into groups for global and local use. Global registers are used as described above, whereas local registers are used for expression/address computations. In a complex expression, for example, intermediate results can be stored in local registers for later use. Such values are only stored in memory if enough local registers are not available. A potential inefficiency of local RAA results because registers are arbitrarily split into global and local groups before register usage is known. Too many registers may be devoted to local use when they would be better utilized as global registers and vice-versa. The optimal division cannot be determined a priori.

Global register allocation can be represented as a graph coloring problem, whereas local allocation can be done via usage counts. Both graph-coloring and usage counts are discussed below.

5.3 Local RAA via Usage Counts

Freiburghouse [Fre74] devised a simple and efficient method for register allocation implementing a local strategy. Glanville and Graham use this strategy to implement an on-the-fly RAA scheme within their instruction selector. Freiburghouse's algorithm provides an optimal solution to the value retention problem for each linear region. Freiburghouse shows the register demand problem is not solved by this algorithm, but is better than least recently used or least recently loaded strategies in terms of the number of loads generated in 2500 linear region test cases. An optimal solution is not feasible without lookahead.

In Freiburghouse's algorithm, a usage count is used to track the number of distinct references to a given value (variable or computation result) in a program. Algorithms that eliminate redundant computations calculate this. The usage count represents the number of times a value will be needed within the program. Every time a value is used, its usage count is decremented. Therefore a usage count of zero indicates the value will no longer be needed within the program. Usage counts are assigned before register allocation begins.

Registers are allocated to values as needed. When a value's usage count is zero, the associated register can be released since the value is no longer needed. If a register is needed and no spares are available, the register storing the value with the lowest usage count is released. If the register's value has not changed since loading spilling is unnecessary.

5.4 Global RAA via Graph Coloring

Chaitin, et al. [Cha81], discuss register allocation as a graph coloring problem. The idea of applying graph coloring to solve the register allocation problem is not new, but Chaitin describes the first attempt to actually implement this solution. This approach assumes global

1б

register allocation. Furthermore, this implementation uses a preallocation RAA (i.e. register allocation is performed before the instruction selection phase).

In their formulation of RAA, colors represent registers and graph nodes represent variables (names). Since variables are never placed in the stack frame pointer, it is reserved and is not represented with a color. A graph-coloring represents a legal register allocation in which each variable is in a different register. In coloring the graph, this method tries to keep as many values in registers as possible.

The first step in this register allocation solution is building the interference graph which describes when two variables cannot be in the same register (i.e. when two graph nodes cannot have the same color). Data-flow analysis is performed to determine which names (nodes in the graph) interfere. Two names interfere if one of them is live at the definition point of the other. To construct the interference graph, K edges are added to the graph when a new node (name) is defined, where K represents the number of live names at that point in the program. The goal is to put the non-interfering names into the same register (i.e. paint these graph nodes with the same color).

Next, RAA is performed by attempting to color the graph with N colors, where N is the number of registers. Nodes with less than N edges can be removed recursively, because such nodes can always be colored. If this reduces to an empty graph then the coloring, and RAA, is trivial. Reduction to an empty graph represents the situation in which more than enough registers are available. If an empty graph does not result, the paper describes an NP-complete algorithm which attempts to color the graph. If the graph cannot be colored, a node is removed from the graph. The removal of a node corresponds to introducing spill code to free a register. The cycle of attempted coloring and removal repeats until the graph is colored.

Chaitin describes a better method [Cha82] to insert spill code and eliminates the use of the NP-complete algorithm in a later paper. The old method, a recursive algorithm, blocks when all nodes have at least N edges. In the new method, the node with the least cost estimate is removed from the graph whenever the recursive algorithm blocks. Spill code for this register must be inserted into the intermediate code. The graph is then rebuilt and a N-coloring is again attempted. To get the least cost estimate the graph is supplemented with a table of cost estimates. This estimate is

17

derived from the cost to spill, which is the increase in execution time to spill, divided by the degree of the node. The cost to spill is calculated by adding the number of definition points and the number of uses where each is weighted by the estimated execution frequency. Chaitin also uses local knowledge to reload and spill once for a basic block, instead of many times during the block and accounts for allowing computations to be redone to avoid spilling and reloading.

Hennessy and Chow [ChHe84] implemented a post-allocation RAA based on graph coloring. The coloring process is driven according to cost and savings estimates computed for each live range or live range part, as live ranges are sometimes split. Live ranges are similar to Chaitin's definition-use chains. Coloring the graph assigns registers to each live range until all live ranges have registers or until the register supply is exhausted. Cost/Saving estimates prioritize variables so that variables which save the most time when in registers are assigned registers first, increasing the efficiency of the generated code. Not all registers are reserved for allocation by the graph-coloring scheme; some are allocated during a local register allocation phase using usage counts. By performing a local register allocation phase, the number of global registers (N) is reduced and the computation time of the NP-complete algorithm is also reduced.

The local allocation phase determines several parameters used to estimate variable priorities. The parameters are: the cost of moving a value from register to memory and vice versa, the execution time saved by referencing a variable in a register versus a variable in memory, and the execution time saved by each re-definition of a value in a register compared with a store to memory.

Hennessy and Chow's method has several advantages. First, the cost/saving estimates enable an informed choice of which register to spill. Second, their algorithm does not degrade (in time) when an N-coloring is unavailable. Third, the loop structure of a program is taken into account. For example, consider two variables which have similar occurrence frequencies, as determined by the local phase. If one variable is used across contiguous code segments, assigning that variable to the same register (color) across code segments will minimize register loads and stores. The global allocator can recognize this situation and make the more efficient allocation. Finally, it is not always desirable to allocate a register to a variable. A cost/saving estimate in which cost is greater than savings yields such a low

18

priority that the variable will never be assigned a register, hence this scheme does not fall prey to overallocation. Although these cost/saving estimate formulas are good, calculating the estimates adds extra phases to make the whole algorithm suboptimal [ChHe84].

#### 6. Integrated Approaches To Code Generation

So far instruction selection, peephole optimization, and register allocation have been discussed as independent tasks ordered sequentially as subphases. In reality, the tasks are interdependent and the division into independent phases is undesirable because of phase ordering problems, so named because often one phase introduces an inefficiency that can only be corrected by an earlier phase. For example, performing register allocation after instruction selection may introduce an inefficiency when creating register spills. It may be that a spill could be avoided by choosing a different instruction, or it might be cheaper to recompute a value rather than spill and reload. Neither alternative is available after instruction selection is complete. Another example occurs in the way the peephole optimizer and the register allocator are ordered. Performing peephole optimization first can reduce the need for registers by dead-variable analysis and common subexpression elimination. Allocating registers can introduce loads and stores for spilling and reloading values. This code should be further optimized by the peephole optimizer. Requiring the peephole optimizer and the register allocator to run sequentially can introduce inefficiencies no matter which goes first.

The phase ordering problem poses the dilemma that no matter how the phases are ordered, inefficiences result. The dilemma could be solved if the tasks were integrated into a single phase so that all three tasks operated cooperatively. For example, suppose an instruction requires its operands to be in adjacent registers. If the register allocator operates after instruction selection, it can insure that the operands for this instruction are placed in adjacent registers if possible. However, if the register allocator operates before instruction selection, it could influence the instruction selected. For the instruction selector to pick the best instruction, it must have knowledge about whether an instruction will cause a spill or extra moves to make its decision. Conversely, the register allocator needs information about the instruction selected to best allocate the registers. To minimize spills and extra moves the instruction selector and register allocator must make a mutual decision, which is not possible in phase-ordered code generation.

Other advantages are gained as a natural result of integrated code An advantage of combining two phases is that one generation. machine description or code generation specification can be used rather than two or three. Furthermore, when tasks are separate phases, each phase often duplicates the efforts of a previous phase thus making compile-time code generation 10-20% slower than if the phases were combined [HeGa86]. Peephole optimization can be performed on intermediate code to simplify instruction selection [TaVSSt82]. For example, additions of one can be replaced by increments at the intermediate code level. Case analysis during instruction selection is reduced because the instruction selector no longer considers this optimization. Both integrated and sequential code generation can use this form of peephole optimization. However to take advantage of machine dependencies, some peephole optimization can only be done after instruction selection. Thus performing peephole optimization on intermediate code alone is insufficient.

Because integration of instruction selection, peephole optimization and register allocation appears promising, some recent research has attempted the derivation of code generators in which phases are integrated (i.e. two or more phases are combined). In what follows, two attempts to extend earlier research to offer more integrated approaches to code generation are described. One approach, by Fraser and Wendt, attempts to integrate from the original perspective of peephole optimization. The second approach, by Ganapathi and Fischer, attempts to integrate from the original perspective of parsing-based instruction selection. Each is described in turn.

#### 6.1 Fraser and Wendt

Fraser and Wendt [FrWe86] describe how instruction selection and peephole optimization are performed by HOP, a single, general, rulebased system that matches and replaces register transfer patterns. One set of rules generates naive code, represented as register transfers; another set peephole optimizes these register transfers by combining juxtaposed instructions into a single instruction during generation; still other rules translate the optimized register transfers to assembly code.

20

Phase combination is accomplished as follows. When an instruction selection rule is executed, a register transfer is created instead of intermediate code so optimization rules can be applied. The register transfers are recycled through the rules until no more optimizations apply.

Combining instruction selection and peephole optimization is also faster because no time is wasted on I/O between phases. (The first phase no longer has to dismantle and output its structure only to have the next phase read and create a similar structure.) Furthermore, many optimization rules are generated at code generator generation time by PO and loaded into the compile-time optimizer HOP, thus the overall time for peephole optimizations is reduced.

Phase-ordering problems are not as likely to occur when instruction selection and peephole optimization are tightly integrated. The register allocator is part of the instruction selection phase; an infinite number of psuedo-registers are **not** used. The register allocator may naively generate more spills than needed, but as optimizations are applied unnecessary spills are removed. The spill code is not written unless it is actually needed (i.e. cannot be optimized away.) A "spill count" is used for each register to delay spill code emission until all optimization is complete to see if the code is actually ever needed. The code produced from this new compiler is not as good as the original compiler with separate phases but the authors attribute this to the fact that common subexpression elimination has not yet been implemented.

6.2 Ganapathi and Fischer

Ganapathi and Fischer's framework for integration works with attributed parsing code generators and builds on their earlier work on instruction selection [GaFi88]. Additional grammar productions (i.e. productions that describe special purpose instructions) are added to the instruction selection productions to perform peephole optimizations. Since attributes maintain contextual information, peephole optimizations on logically adjacent instructions are also possible. The structure is largely machine independent.

A peephole optimizing production is composed of the RHS of the leading logically adjacent instruction, a non-terminal 'V', and the RHS of the trailing logically adjacent instruction. Code that would have been emitted for the leading and trailing instructions (if they had not been logically adjacent) is buffered as an attribute of the LHS of the peephole production. When the peephole production is recognized, improved code is emitted instead of the original sequences. The code between the logically adjacent instructions is guaranteed to be emitted by the LHS attribute of the peephole production. The productions are ordered so that the peephole optimization productions come first. Adding peephole optimizing productions does not make the code generator any more likely to block. (If it did not block before these productions were added, it will not block now.) Thus if peephole productions can be applied, they will be.

Nested peephole optimizations are allowed; overlapped windows of peephole optimizations are not permitted (when two matches overlap and neither properly contains the other). The authors say that this restriction can be overcome with multiple buffers that emit code to different files that are then merged in correct sequence for final assembly but implementation of this solution may not be practical. Secondly, with a single-pass implementation it is not possible to iteratively apply peephole optimizations to improve the code quality. Here again the authors say that iterative peepholeoptimization opportunities do not appear frequent enough to cause serious degradation in code quality. A multi-pass attribute evaluation scheme could solve this problem.

#### 7. Backtracking LR-parsing for Code Generation

The goal of this thesis is to present a formal method of automatically deriving code generators from a code generation specification. We present the concept of a backtracking LR-parser, describe its use for the automatic creation of a code generator using a tree-based notation as the code generation specification (which is translated into an affix grammar), and give implementation details.

The backtracking LR parsing code generator described in subsequent chapters approaches the automatic derivation of code generators from the perspective of pattern matched instruction selection. This research is closely related to, and benefits from, earlier work by Glanville and Graham [GlGr78], Henry [Hen84], and Ganapthi and Fischer [GaFi85]. However, the introduction of backtracking gives our approach some of the flavor of Cattell's approach [Cat80], and our tree-based notation for machine descriptions has the flavor of Aho,

Ganapthi and Tjiang [AhGaTj89]. In this way, our research attempts to combine the best of our predecessors.

As compared with other parser based methods, a backtracking LR parsing code generator shares many of the same strengths. Because our code generator uses attributed grammars, it is more closely related to the affix grammar driven code generator of Ganapathi and Fischer [GaFi85] than the Glanville and Graham [GlGr78] and Henry [Hen84] code generators. Backtracking LR parsing also has the additional advantage of avoiding syntactic and semantic blocking problem via backtracking. In this sense backtracking LR parsing combines the flexibility of Cattell's approach [Cat80] with the formalism of parsing.

In comparsion with the dynamic tree pattern matching approach exemplified by Twig [AhGaTj89], backtracking LR parsing code generators can perform common subexpression elimination and other high level optimizations which Twig does not. Two advantages Twig claimed over other parser-based approaches are notational ease and avoidance of semantic blocking. Neither advantage holds over using tree transformations with a backtracking LR parser. As stated previously, the backtracking LR parsing code generator avoids blocking, and we have developed a new tree-based notation for writing code generation specifications that is comparable to Twig in terms of notation.

The effects gained from combining register transfers to perform peephole optimizations (and instruction selection in the case of Fraser and Wendt [FrWe86]) a la Davidson and Fraser [DaFr84] and Fraser and Wendt [FrWe86] can also be performed with a backtracking LR parser. The reparsing allowed by the backtracking would allow trees to be combined in much the same way that registers are combined. Although in this research, instead of combing two register transfers, two trees are collapsed and the result reparsed. In this way a logical window is available as well as the ability to handle overlapped and nested optimizations.

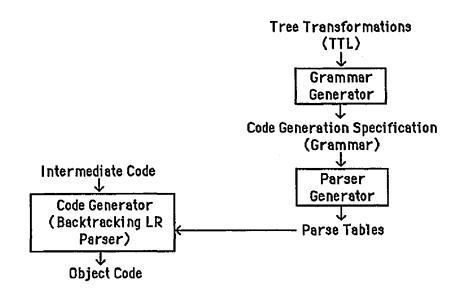

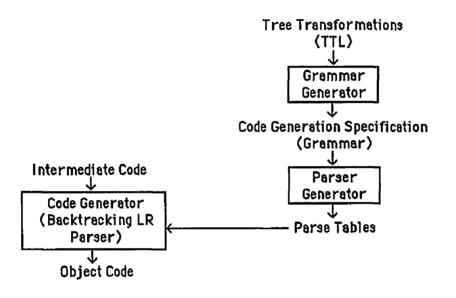

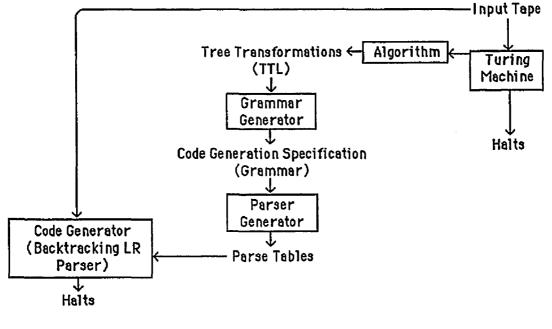

#### Figure 1.3 Backtracking LR Parsing-based Code Generation

Figure 1.3 depicts the use of a backtracking LR parser for the automatic derivation of a code generator from a TTL specification. There are four items this thesis discusses in detail:

- 1) The code generator produced from the code generation specification, represented by the box on the left of Figure 1.3.

- 2) The modified parse tables which enable backtracking LR parser depicted on the lower right of Figure 1.3, and to a lesser extent the parser generator shown directly above the parse tables in the figure.

- 3) The tree-based notation, written in the tree transformation language (TTL), is used for code generation specifications, labeled Tree Transformations in the upper right of Figure 1.3.

- 4) The grammar generator, shown in the box in the upper right of Figure 1.3, which transforms TTL code generation specifications into grammar-based specifications.

The remainder of this thesis is organized as follows. Chapter 2 reviews LR parser-based approaches to the automatic derivation of code generators with particular attention to the role of semantic actions for code generation and the problems of syntactic and

. . .

The context is established which motivatated our semantic blocking. investigation of the use of backtracking LR parsers for the automatic derivation of code generators. In Chapter 3, the modifications to the parser generator, to the parse tables, and to the parsing algorithm which enable backtracking are discussed. The problem of backing up in the presence of semantic actions performed during parsing is deferred until Chapter 4. Chapter 4 builds on the foundation provided in chapters 2 and 3, to discuss gathering, saving and restoring semantic information during the parse and backup over semantic actions. In Chapter 5 the concept of a tree transformation is introduced and a tree transformation language (TTL) for writing code generation specifications is described. In Chapter 6 an algorithm for a grammar generator which translates from TTL machine descriptions to an affix grammar representation is This algorithm was not implemented for this thesis, but presented. was executed manually. In Chapter 7 modifications to the code generator to allow for a specialized form of backup are discussed. These modifications were primarily caused by the need to reparse only the changed or new input created by a tree transformation. Chapter 8 summarizes the research and presents conclusions.

# Chapter 2

# Blocking Problems in Parsing-based Code Generators

"I went over my furniture and looked at each chair in turn, wondering whether the trouble lay there for it upsets me to see even one chair not in its usual place." from <u>White Nights</u> by Dostoyevsky (1848)

In this chapter, we discuss the problems caused by blocking, i.e. when the parse is in a state for which no action can be performed. We outline solutions previous researchers have used to avoid both syntactic and semantic blocking.

A compiler translates a machine-independent source language into a machine-dependent target language. Most compilers consist of a *front-end*, which recognizes the source language, and a *back-end* or code generator which produces the target machine language.

The front-end translates the source language into an equivalent representation using an intermediate code or IC. The code generator translates the IC into an equivalent representation in the target language.

Use of an intermediate representation has several benefits. A carefully designed IC permits the same front-end to be used with different code generators and vice-versa. This allows compilers, for the same language on different machines or for different languages on the same machine, to be implemented more easily and with less

duplication of effort. Second, the IC is a form of separation of concerns that simplifies both the front-end and the code generator. Information specific to the target machine is hidden from the frontend, and information specific to the source language is hidden from the code generator.

Glanville and Graham [GlGr78] identified the code generator's problem of recognizing the IC as a string pattern matching problem which can be solved using LR parsing technology. In their method, the code generator is a modified LR parser which accepts the IC as input, parses it and transforms it into the target machine language. This approach is summarized by Henry as follows:

"In the Graham-Glanville approach to code generation, a code generator is a pattern matcher/replacer built from pattern-replacement pairs. In our applications, the pattern models the computation that the instruction performs, and the replacement models the effect of the computation." [Hen84, p. 3].

The IC is viewed as a language that can be described by a grammar. Target machine instructions are associated with grammar productions to describe how the IC is translated into the target machine instructions. The association of grammar productions and target machine instructions forms the pattern-replacement pairs described by Henry. A Glanville-Graham style code generator is generated from the code generation specification grammar using an LR parser generator.

As the code generator parses the IC, target patterns represented by grammar rules are recognized and associated target machine instructions are emitted. For example, consider the IC tree in Figure 2.1 for an assignment statement.

Figure 2.1 Intermediate Code Tree for a:= b + c

Since parsers pattern match strings and this IC is represented with a tree, the IC must be *linearized* to allow parsing based pattern matching. The IC tree above can be represented in *linearized Polish prefix* form:

:= a + b c

In LR parsing-based code generation, the IC is described with a grammar. The following grammar will pattern match an IC of the form shown above:

| (1)    | $\langle assign \rangle \rightarrow := \langle var \rangle \langle expr \rangle$ |

|--------|----------------------------------------------------------------------------------|

| (2)    | $\langle var \rangle \rightarrow \langle id \rangle$                             |

| (3)    | $\langle expr \rangle \rightarrow + \langle expr \rangle \langle expr \rangle$   |

| (4)    | $\langle expr \rangle \rightarrow \langle var \rangle$                           |

| (5)    | $\langle expr \rangle \rightarrow \langle no \rangle$                            |

| Figure | 2.2 MD1: A Partial Code Generation<br>Specification                              |

The grammar MD1 in Figure 2.2 partially describes an assignment statement. An actual code generation specification would include many more productions to pattern match the IC. More productions are required to fully describe possible expressions (<expr>). When a production matches, an associated action emits machine instructions.

Machines have several possible instructions or sets of instructions to accomplish the same task, therefore there are many different translations possible for a given IC code sequence. All code generation specifications reflect this ambiguity.

An ambiguous grammar results from an inherently ambiguous code generation specification. Therefore there are a number of possible parse paths for a given linearized IC tree. For example, consider the partial code generation specification shown in Figure 2.3.

(1)  $\langle assign \rangle \rightarrow := \langle id \rangle + \langle id \rangle \langle no \rangle$ (2)  $\langle assign \rangle \rightarrow := \langle var \rangle \langle expr \rangle$ (3) <var>  $\rightarrow$  <id> (4) $\rightarrow$  + <expr> <expr> <expr> (5) <expr>  $\rightarrow$  <var> (6) <expr>  $\rightarrow$  <no> Figure 2.3 MD1-ambiguous

The first production is an optimizing production designed to generate an increment instruction. It would require both identifiers to be identical and a numeric operand with a value of one.

In Figure 2.3, MD1 is ambiguous. Both the first production:  $\langle assign \rangle \rightarrow := \langle id \rangle + \langle id \rangle \langle no \rangle$

and the production:

$\langle assign \rangle \rightarrow := \langle var \rangle \langle expr \rangle$

```

can derive := a + a 1.

```

This ambiguity results in a shift-reduce conflict during parsing. Once the input :=  $\langle id \rangle$  is on the stack, and the + symbol appears as the next input token, there is a conflict. Reducing  $\langle id \rangle$  to  $\langle var \rangle$  will eventually result in use of the production (2), while shifting the + token will eventually result in use of the production (1). Since shiftreduce conflict resolution occurs before the rest of the input is known, problems can result.

Grammar productions for target machine instructions also require semantic information as well as a syntactic description of the IC. For instance the production that represents an increment,  $<assign> \rightarrow :=$ <id> + <id> <no>, cannot be applied on most machines unless the number, <no>, is 1 and the two identifiers in the production represent the same location in memory.

Semantic information may be encoded in the grammar syntactically [GlGr78]. MD1-ambiguous is modified as shown in Figure 2.4.

| (1)    | $\langle assign \rangle \rightarrow := \langle id \rangle + \langle id \rangle \langle one \rangle$ |

|--------|-----------------------------------------------------------------------------------------------------|

| (2)    | $\langle assign \rangle \rightarrow := \langle var \rangle \langle expr \rangle$                    |

| (3)    | $\langle var \rangle \rightarrow \langle id \rangle$                                                |

| (4)    | $\langle expr \rangle \rightarrow + \langle expr \rangle \langle expr \rangle$                      |

| (5)    | $\langle expr \rangle \rightarrow \langle var \rangle$                                              |

| (6)    | $\langle expr \rangle \rightarrow \langle no \rangle$                                               |

| (7)    | $\langle expr \rangle \rightarrow \langle one \rangle$                                              |