### **W&M ScholarWorks**

Dissertations, Theses, and Masters Projects

Theses, Dissertations, & Master Projects

2006

## Real -time Retinex image enhancement: Algorithm and architecture optimizations

Glenn Derrick Hines College of William & Mary - Arts & Sciences

Follow this and additional works at: https://scholarworks.wm.edu/etd

Part of the Computer Sciences Commons

#### **Recommended Citation**

Hines, Glenn Derrick, "Real -time Retinex image enhancement: Algorithm and architecture optimizations" (2006). Dissertations, Theses, and Masters Projects. Paper 1539623490. https://dx.doi.org/doi:10.21220/s2-zgwv-7r76

This Dissertation is brought to you for free and open access by the Theses, Dissertations, & Master Projects at W&M ScholarWorks. It has been accepted for inclusion in Dissertations, Theses, and Masters Projects by an authorized administrator of W&M ScholarWorks. For more information, please contact scholarworks@wm.edu.

# REAL-TIME RETINEX IMAGE ENHANCEMENT: ALGORITHM AND ARCHITECTURE OPTIMIZATIONS

A Dissertation

Presented to

The Faculty of the Department of Computer Science

The College of William & Mary in Virginia

In Partial Fulfillment

Of the Requirements for the Degree of

Doctor of Philosophy

by

Glenn Derrick Hines

2006

### APPROVAL SHEET

This dissertation is submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Glenn Hines

Approved, January 2006

J. Philip Kearns

Dissertation Advisor

Zia-ur Rahman

Dissertation Co-Advisor

Weizhen Mao

Andreas Stathopoulos

Mark Hinders

Department of Applied Science

| To my lovely wife Sunita and our adorable children Jordan, Jada and Jamison |

|-----------------------------------------------------------------------------|

|                                                                             |

|                                                                             |

|                                                                             |

|                                                                             |

|                                                                             |

|                                                                             |

|                                                                             |

| •                                                                           |

| iii                                                                         |

## Table of Contents

| A  | cknov | wledgments             | viii |

|----|-------|------------------------|------|

| Li | st of | Tables                 | x    |

| Li | st of | Figures                | xv   |

| A  | bstra | et                     | xvi  |

| 1  | Intr  | roduction              | 2    |

| 2  | Ret   | inex Image Enhancement | 7    |

| 3  | Dig   | ital Signal Processors | 12   |

|    | 3.1   | TMS320C6711            | 13   |

|    | 3.2   | TMS320C6713            | 16   |

|    | 3.3   | TMS320DM642            | 17   |

|    | 3.4   | TMS320C6416            | 19   |

| 4  | Tes   | t Environment          | 21   |

|    | 4.1   | DSP Evaluation Modules | 21   |

|   |     | 4.1.1        | Video Capture and Display for C6711 and C6713 EVMs                     | 23  |

|---|-----|--------------|------------------------------------------------------------------------|-----|

|   |     | 4.1.2        | Video Capture and Display for DM642 and C6416 EVMs $\ \ldots \ \ldots$ | 26  |

|   | 4.2 | Develo       | opment Tools                                                           | 27  |

|   | 4.3 | Test-E       | ded Components and Operation                                           | 28  |

|   | 4.4 | Perfor       | mance Analysis                                                         | 30  |

|   | 4.5 | Real-t       | ime Parameter Updates                                                  | 31  |

|   | 4.6 | Retine       | ex Task Within DSP/BIOS                                                | 32  |

| 5 | Opt | imizat       | ions and Performance Results                                           | 33  |

|   | 5.1 | Single       | -Scale Monochrome Retinex Optimizations                                | 34  |

|   |     | 5.1.1        | Apply Convolution Equivalence                                          | 34  |

|   |     | 5.1.2        | Pre-Compute the Kernel                                                 | 36  |

|   | •   | 5.1.3        | Baseline Algorithm Performance                                         | 37  |

|   |     | 5.1.4        | Pre-Compute the Logarithm                                              | 39  |

|   |     | 5.1.5        | Use DMA to Transfer Columns                                            | 43  |

|   |     | 5.1.6        | Reduce Gaussian Kernel Computations                                    | 44  |

|   |     | 5.1.7        | Merge Algorithm Components                                             | 45  |

|   |     | 5.1.8        | Minimize Data Transfer Overhead                                        | 46  |

|   |     | 5.1.9        | Use Cache-optimized FFTs                                               | 48  |

|   | 5.2 | Map (        | Optimized SSMR to C6713                                                | 49  |

|   | 5.3 | Map (        | Optimized SSMR to DM642                                                | 50  |

|   |     | 5.3.1        | Apply Intrinsics                                                       | 52  |

|   |     | <b>=</b> 0.0 | N. 110 (1 A 11)                                                        | F ( |

|   | 5.4 | Multi-Spectral Multi-Scale Retinex Optimizations | 54 |

|---|-----|--------------------------------------------------|----|

|   |     | 5.4.1 Reuse Transformed Input Image              | 54 |

|   |     | 5.4.2 Reduce Computations                        | 55 |

|   |     | 5.4.3 Buffer Across Spectral Bands               | 58 |

|   |     | 5.4.4 Allocate Log Values in L2 Memory           | 59 |

|   |     | 5.4.5 MSR Performance Results                    | 59 |

| 6 | Enh | anced Vision System Case Study                   | 68 |

|   | 6.1 | Background                                       | 68 |

|   | 6.2 | Image Processing Functions                       | 70 |

|   | 6.3 | Additional Requirements                          | 73 |

|   | 6.4 | Results                                          | 76 |

| 7 | Fut | ure Research                                     | 82 |

|   | 7.1 | Luma-only Retinex                                | 82 |

|   | 7.2 | Improving Current Performance                    | 83 |

|   | 7.3 | Processing Larger Format Images                  | 84 |

|   | 7.4 | Migrating to a Multiprocessor Environment        | 88 |

| 8 | Con | aclusions                                        | 90 |

| A | Mu  | ti-Image Registration                            | 93 |

|   | A.1 | Background                                       | 94 |

|   | A.2 | Registration algorithms                          | 98 |

|   |     | A 2 1 CC algorithm                               | 00 |

|              |       | A.2.2  | MLR algorithm                   | 100 |

|--------------|-------|--------|---------------------------------|-----|

|              | A.3   | Result | s                               | 101 |

|              |       | A.3.1  | SS algorithm                    | 102 |

|              |       | A.3.2  | MLR algorithm                   | 104 |

|              |       | A.3.3  | Discussion                      | 106 |

|              | A.4   | Summ   | ary                             | 108 |

| В            | Fiel  | d Prog | grammable Gate Arrays           | 110 |

| $\mathbf{C}$ | DM    | 642 E  | VM Flash Programming Guidelines | 114 |

| Bi           | bliog | raphy  |                                 | 119 |

| Vi           | ta    |        |                                 | 127 |

#### ACKNOWLEDGMENTS

The list of people I wish to acknowlege would require another dissertation but I will point out a few. First, and foremost I thank my research advisor, Dr. Zia-ur Rahman for his guidance, patience, and great ideas. One day the world will know and value your genius. I also thank Daniel Jobson for his wonderful musings on image processing research, and Glenn Woodell for always lending a helping hand. The seeds of the Retinex that the three of you planted have grown into quite a tree. Thank you for allowing me to contribute to a branch.

I also thank my professors at William and Mary, Doctors Torczon, Bynum, Stockmeyer, Stathopoulos, Zhang, Noonan, Prosl, Rahman, and Kearns, for all of your enlightening classroom sessions, and patiently satisfying all of my "What if you tried this?" questions. In particular, special consideration is given to Professor Kearns for giving me the opportunity to continue my research in image processing and serving as my advisor.

Grateful acknowlegement is given to Vanessa Godwin. Your advice throughout my tenure as a student was invaluable. Thanks for "penetrating the bureaucracy" for me. I also sincerely thank my committee members Weizhen Mao, Andreas Stathopoulos, and Mark Hinders for all of your comments and suggestions, and for your willingness to take time out of your schedule for me.

The work contained in this dissertation was supported by funding from NASA Langley Research Center. Sincere appreciation is extended to my managers at NASA LaRC for giving me the opportunity to pursue my research dreams. This list spans many years now but includes Dr. Thomas Shull, Pam Rinsland, Steve Jurczyk, Steve Sandford, Randy Reagan, and Kathryn Stacy. Thanks also goes to Steven Harrah for project support, Cathryn Murray-Wooddell for working your magic with resources, and George Allison for keeping the Ph.D. pipeline going at NASA LaRC. Many thanks also go out to my colleagues at NASA but especially to my old lunch bunch including Duane, Cy, Danette, Michael, Marilee, Shelley, Felicia, and Lloyd who is no longer with us. We've solved many of the world's problems on napkins, now if only we can convince everyone else to listen.

I also wish to thank a few special people — My parents David and Helen Hines for raising me and my brothers, Ronnie and Brian, in a home that always valued knowledge and education, and for your good genes! Neville and Dorothy Etwaroo for doing the same for Sunita! My many extended family members for all of your words of encouragement and prayers, and my many friends including Roger Bailey, Charles Stump, Shawn Williams, Steve Green, Kenneth Arrington, Andres Alvarez, Levi Little, and Bruce Hornsby for keeping me laughing throughout the years.

And although I dedicated this document to my immediate family, I again give my utmost gratitude to my wife Sunita Etwaroo and our children Jordan Milan, Jada Nalini, and Jamison Glenn for all of your love and support. You are my air.

## List of Tables

| 3.1 | DSP Specifications                                                               | 20         |

|-----|----------------------------------------------------------------------------------|------------|

| 5.1 | Initial performance results from the first implementation of the SSMR            | 37         |

| 5.2 | Performance measurements after using logarithm tables and combining $\alpha$ and |            |

|     | β                                                                                | 41         |

| 5.3 | Performance results after using 2D DMA data transfers                            | 43         |

| 5.4 | Performance results after using 2D DMA data transfers                            | 45         |

| 5.5 | Performance results after merging algorithm stages. Since the forward and        |            |

|     | inverse column execution times are effectively merged together, the time to      |            |

|     | process columns is now in item "processcols"                                     | 47         |

| 5.6 | Final SSMR performance results using the C6711 DSP                               | <b>4</b> 9 |

| 5.7 | Measured Retinex performance on DM642 and C6416 processors. The 133              |            |

|     | and 200 refer to the clock speed of the EMIF bus. Measurement units are in       |            |

|     | both milliseconds, and frames per second in parentheses                          | 64         |

| 5.8 | Comparison of final SSMR performance using the C6711 and the C6416 DSPs.         | 64         |

| 5.9 | C6416 CPU Loading for different Retinex configurations                           | 65         |

| 6.1 | Sensor Specifications                                                       | 72  |

|-----|-----------------------------------------------------------------------------|-----|

| 7.1 | FFT Benchmarks for C6711, DM642 and C6416                                   | 85  |

| 7.2 | FFT Processing Time Benchmarks using C6711 and DM642 for various sized      |     |

|     | images                                                                      | 86  |

| 7.3 | FFT storage requirements and transfer times (based on row oriented data)    |     |

|     | for various sized images. Storage is based on complex image data stored as  |     |

|     | integers. Transfer times are based on a 64-bit EMIF bus clocked at 133 MHz. | 86  |

| A.1 | Sensor Specifications                                                       | 97  |

| A.2 | Updated Sensor Specifications                                               | 98  |

| A.3 | Visible to SWIR MLR Coefficients                                            | 104 |

| Δ 4 | LWIR to visible SWIR MLR Coefficients                                       | 105 |

## List of Figures

| 2.1 | The top row of images from left to right have simulated tungsten, fluorescent,    |    |

|-----|-----------------------------------------------------------------------------------|----|

|     | and sunlight illumination sources. The bottom row has the same images after       |    |

|     | Retinex processing. The effects of the different illumination sources is nearly   |    |

|     | completely removed                                                                | 8  |

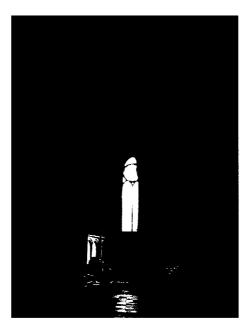

| 2.2 | Many image processing algorithms would either saturate the bright regions         |    |

|     | or clip the dark regions of the image on the left. The Retinex processed          |    |

|     | image on the right appears almost uniformly illuminated without exhibiting        |    |

|     | these effects.                                                                    | ę  |

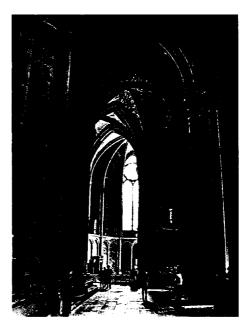

| 2.3 | On the left is a low contrast, dimly lit grayscale digital image; on the right is |    |

|     | the single-scale Retinex processed image — single-scale processing increases      |    |

|     | the contrast and sharpness                                                        | 10 |

| 3.1 | Primary DSP components include the CPU, L1 Data Cache, L1 Program                 |    |

|     | Cache, L2 memory (SRAM/Cache) and EDMA Controller                                 | 13 |

| 3.2 | General outline of 2-level internal memory architecture of C67x processors.       |    |

|     | The dashed boxes are user addressable memory                                      | 15 |

| 3 3 | Configuration modes for the C6711 L2 memory                                       | 16 |

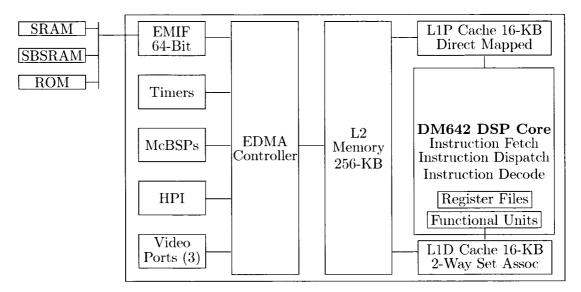

| 3.4 | Block diagram of primary DM642 components. The DM642 has special in-                       |    |

|-----|--------------------------------------------------------------------------------------------|----|

|     | struction extensions to accelerate video applications                                      | 17 |

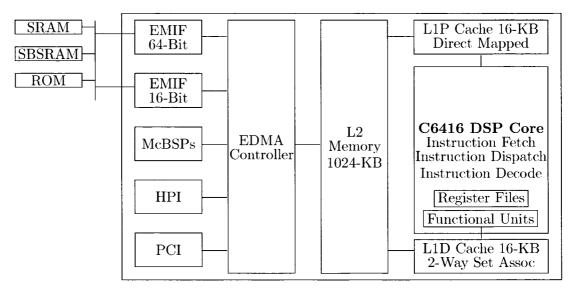

| 3.5 | Block diagram of primary C6416 Components. Note the larger L2 memory                       |    |

|     | and 64-bit EMIF bus                                                                        | 20 |

| 4.1 | Picture of DM642 EVM board. Numerous components are on the EVM                             |    |

|     | circuit board to support testing the DSP for a wide variety of applications.               |    |

|     | We primarily use the peripherals associated with video capture and display.                | 22 |

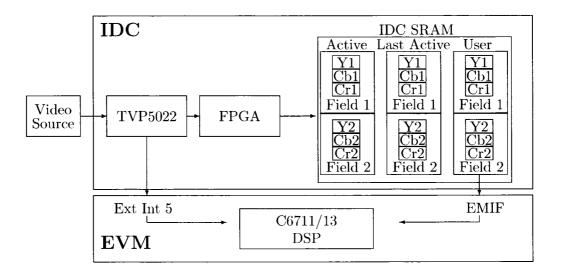

| 4.2 | IDC video capture subsystem                                                                | 24 |

| 4.3 | IDC video display subsystem                                                                | 25 |

| 4.4 | DM642 EVM block diagram                                                                    | 27 |

| 4.5 | C6416 EVM block diagram                                                                    | 28 |

| 4.6 | Block diagram of the test-bed — the Host PC only provides setup information                |    |

|     | to the EVM; after initiation, the DSP executes independently                               | 29 |

| 5.1 | Capture Video Frame with input from camera on the left, and Retinex output                 |    |

|     | on the right. Retinex parameters are $\alpha=175,\beta=135,\mathrm{and}\ \sigma=80$ — note |    |

|     | that we are nearly reaching the noise limit of the camera                                  | 50 |

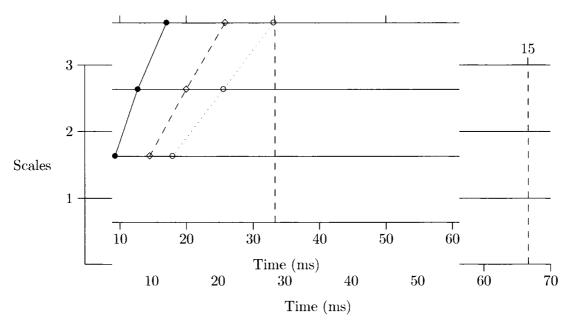

| 5.2 | Retinex performance in time (bottom axis) and frames per second (top axis)                 |    |

|     | to process 1 spectral band of image data on DM642 with 133 MHz EMIF $$                     |    |

|     | (dotted line), DM642 with 200 MHz EMIF (dashed line), and C6416 (full line).               | 61 |

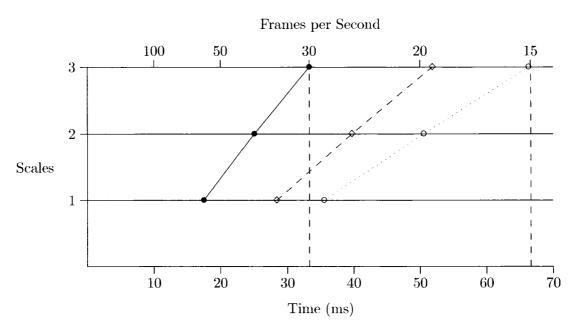

| 5.3 | Retinex performance in time (bottom axis) and frames per second (top axis)                 |    |

|     | to process 2 spectral bands of image data on DM642 with 133 MHz EMIF                       |    |

|     | (dotted line), DM642 with 200 MHz EMIF (dashed line), and C6416 (full line).               | 62 |

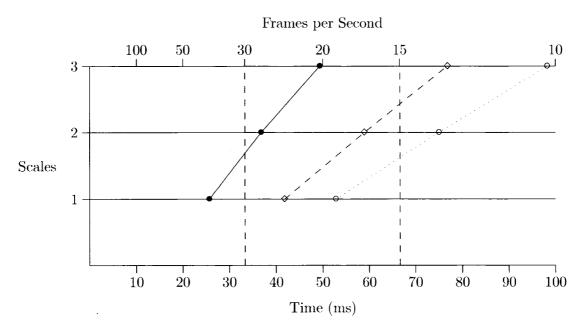

| 5.4 | Retinex performance in time (bottom axis) and frames per second (top axis)      |    |

|-----|---------------------------------------------------------------------------------|----|

|     | to process 3 spectral bands of image data on DM642 with 133 MHz EMIF $$         |    |

|     | (dotted line), DM642 with 200 MHz EMIF (dashed line), and C6416 (full line).    | 63 |

| 5.5 | First snapshot taken 40 seconds into the video recorded at NASA LaRC.           |    |

|     | The frame as captured by the camera is on the left and the real-time Retinex    |    |

|     | processed frame is on the right                                                 | 66 |

| 5.6 | Second snapshot taken 6 minutes and 28 seconds into the video. Colors are       |    |

|     | nearly completely indeterminable and objects are difficult to distinguish in    |    |

|     | the unprocessed image. Colors and objects are still clear in the processed      |    |

|     | frame                                                                           | 66 |

| 5.7 | Third snapshot taken 14 minutes 28 seconds into the video. The only dis-        |    |

|     | tinguishable object in the unprocessed frame is the tail-lights on the vehicle. |    |

|     | Although noisy, the real-time Retinex processed image still clearly shows       |    |

|     | most of the major objects in the first snapshot including spheres, tree lines,  |    |

|     | and parked vehicles                                                             | 67 |

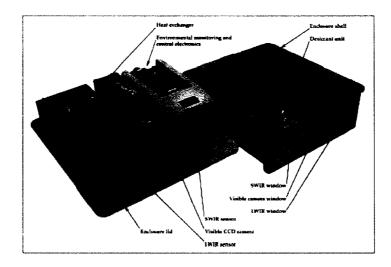

| 6.1 | The EVS LWIR, SWIR, and visible-band cameras mounted to a baseplate,            |    |

|     | and the enclosure shell. Inaccurate bore-sighting can cause image registration  |    |

|     | problems                                                                        | 69 |

| 6.2 | EVS camera enclosure mounted forward-looking underneath the NASA 757.           | 70 |

| 6.3 | The EVS acquires data during the entire flight but take-off and landing phases  |    |

|     | are critical. The simulated shaded area depicts the field of view (FOV) of      |    |

|     | the cameras                                                                     | 71 |

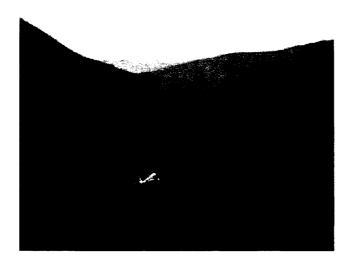

| 6.4  | Examples of the imagery generated by each camera in good weather condi-    |     |

|------|----------------------------------------------------------------------------|-----|

|      | tions. The images from cameras must be registered, enhanced, fused and     |     |

|      | displayed to the pilot in real-time                                        | 72  |

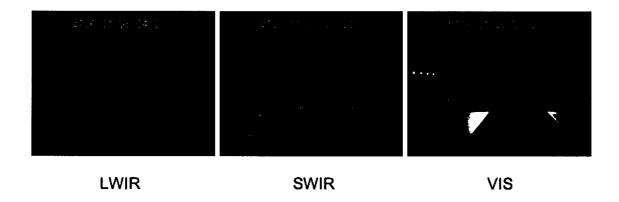

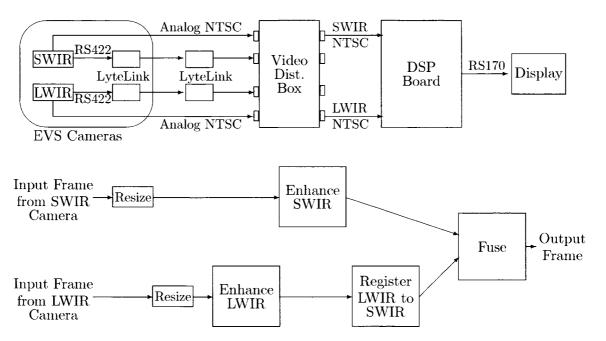

| 6.5  | Image processing architecture and functions of the EVS. Analog NTSC cam-   |     |

|      | era outputs are currently processed. The SWIR data is used as the baseline |     |

|      | for registration since it has the smallest field of view                   | 73  |

| 6.6  | DM642 EVM, signal splitter boards, and power supply in flight box          | 75  |

| 6.7  | Flight box in flight pallet on NASA 757                                    | 75  |

| 6.8  | A frame from the EVS SWIR camera before processing. The faint vertical     |     |

|      | lines were part of the input image and probably caused by subsampling in   |     |

|      | the video distribution system                                              | 78  |

| 6.9  | A frame from the EVS LWIR camera before processing. The LWIR camera        |     |

|      | output is actually rotated 180° from what is shown                         | 79  |

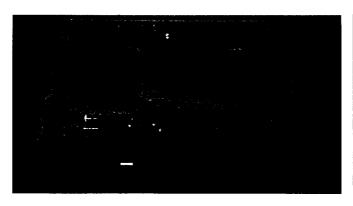

| 6.10 | SWIR frame after enhancement                                               | 80  |

| 6.11 | LWIR frame after enhancement and registration to the SWIR image            | 80  |

| 6.12 | Enhanced, registered and fused output image                                | 81  |

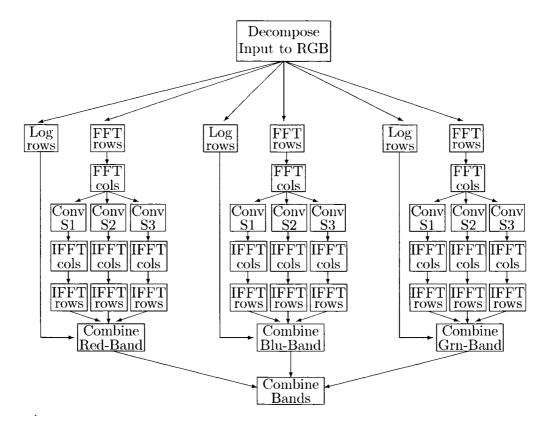

| 7.1  | Data flow diagram of MSR tasks                                             | 89  |

| A.1  | Original SWIR                                                              | 102 |

| A.2  | Original LWIR                                                              | 102 |

| A.3  | Original Visible                                                           | 102 |

| A.4  | Cropped SWIR                                                               | 103 |

| A 5  | SS Reg. LWIR                                                               | 109 |

| A.6  | SS Reg. visible                                         | 103 |

|------|---------------------------------------------------------|-----|

| A.7  | SWIR and SS Registered LWIR                             | 104 |

| A.8  | SS Registered LWIR and visible                          | 104 |

| A.9  | Repeated SWIR                                           | 105 |

| A.10 | MLR Reg. visible                                        | 105 |

| A.11 | SWIR and MLR Reg. visible                               | 105 |

| A.12 | Repeated MLR Registered visible                         | 106 |

| A.13 | MLR Reg. LWIR                                           | 106 |

| A.14 | MLR Reg. visible and LWIR                               | 106 |

| A.15 | Orig. SWIR at Time 26:14:28                             | 107 |

| A.16 | Orig. LWIR at Time 26:14:28                             | 107 |

| A.17 | Orig. visible at Time 26:14:28                          | 107 |

| A.18 | MLR Registered visible at Time 26:14:18                 | 107 |

| A.19 | SWIR and MLR Registered visible                         | 107 |

| A.20 | MLR Registered LWIR at Time 26:14:18                    | 108 |

| A.21 | MLR Registered visible and LWIR                         | 108 |

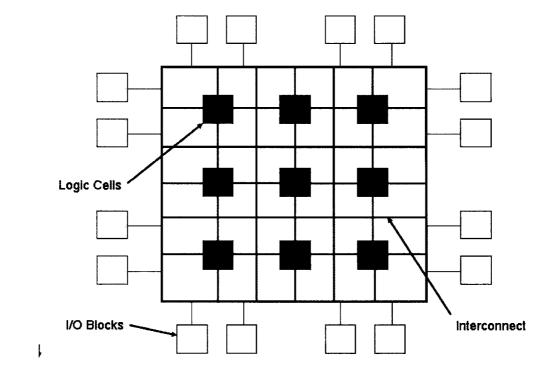

| B.1  | High-level block diagram of a typical FPGA Architecture | 111 |

### ABSTRACT

The field of digital image processing encompasses the study of algorithms applied to two-dimensional digital images, such as photographs, or three-dimensional signals, such as digital video. Digital image processing algorithms are generally divided into several distinct branches including image analysis, synthesis, segmentation, compression, restoration, and enhancement. One particular image enhancement algorithm that is rapidly gaining widespread acceptance as a near optimal solution for providing good visual representations of scenes is the Retinex.

The Retinex algorithm performs a non-linear transform that improves the brightness, contrast and sharpness of an image. It simultaneously provides dynamic range compression, color constancy, and color rendition. It has been successfully applied to still imagery captured from a wide variety of sources including medical radiometry, forensic investigations, and consumer photography. Many potential users require a real-time implementation of the algorithm. However, prior to this research effort, no real-time version of the algorithm had ever been achieved.

In this dissertation, we research and provide solutions to the issues associated with performing real-time Retinex image enhancement. We design, develop, test, and evaluate the algorithm and architecture optimizations that we developed to enable the implementation of the real-time Retinex specifically targeting specialized, embedded digital signal processors (DSPs). This includes optimization and mapping of the algorithm to different DSPs, and configuration of these architectures to support real-time processing.

First, we developed and implemented the single-scale monochrome Retinex on a Texas Instruments TMS320C6711 floating-point DSP and attained 21 frames per second (fps) performance. This design was then transferred to the faster TMS320C6713 floating-point DSP and ran at 28 fps. Then we modified our design for the fixed-point TMS320DM642 DSP and achieved an execution rate of 70 fps. Finally, we migrated this design to the fixed-point TMS320C6416 DSP. After making several additional optimizations and exploiting the enhanced architecture of the TMS320C6416, we achieved 108 fps and 20 fps performance for the single-scale, monochrome Retinex and three-scale, color Retinex, respectively. We also applied a version of our real-time Retinex in an Enhanced Vision System. This provides a general basis for using the algorithm in other applications.

### Chapter 1

## Introduction

Digital image processing encompasses the research and application of signal processing techniques applied to two-dimensional digital images, or three-dimensional signals such as digital video. The field originates from the confluence of large-scale digital computation and the requirement to improve the imagery generated by the U.S. space program in the mid-1960's [20]. Over the last 40 years computation technologies have experienced phenomenal growth and digital image processing has benefited from this progress to become a tool that is used in a wide variety of applications. There are now several branches of digital image processing, each representing different aspects of the field. These branches include image analysis, segmentation, compression, synthesis, restoration, and enhancement [20, 30]. One particular image enhancement algorithm that is rapidly gaining wide-spread acceptance as a near optimal solution for providing good visual representations of scenes is the Retinex.

The Retinex performs a computationally intensive, non-linear spatial/spectral transform that synthesizes strong local contrast enhancement and color constancy [33]. It is used to improve the brightness, contrast and sharpness of an image. It has been successfully applied to still imagery captured from a broad range of sources including aviation safety, medical radiometry, forensic investigations, military operations, homeland security, and consumer photography [103, 55]. It is offered in the commercially available software package PhotoFlair by TruView [99]. Several users require a real-time, embedded implementation of the Retinex, but prior to this research effort, no real-time version of the algorithm had ever been achieved. Real-time<sup>1</sup> is defined here as continuously capturing, processing and displaying 15-30,  $256 \times 256$  sized images<sup>2</sup> (frames) per second. Embedded implies a system or component that is, in general, relatively small, inexpensive, and consumes very little power [19].

One reason that a real-time version of the Retinex had not been achieved is because the Retinex is inherently computationally intensive due to the large volume of data that must be stored, processed, and transferred between processor and memory. The algorithm also entails performing multiple, large convolutions and requires orthogonal data accesses that exacerbate the problem. Another reason is the inefficiency of most general-purpose computing platforms for real-time Retinex processing — as well as for many other digital image processing algorithms. Today's general-purpose processors, such as 2.5 GHz Pentium 4s, possess sufficient computation power to provide reasonable processing rates for Retinex processing of small, still images. However, in general, they do not have the proper architecture, operating system, or development tools to effectively meet the time constraints required for real-time Retinex processing. In addition, many applications limit the processor selection to components that can be embedded into a system. Many general-purpose

A real-time system is one that satisfies explicit bounded response-time constraints to avoid failure [39].

$<sup>^2 \</sup>text{All}$  image sizes, such as 256  $\times$  256, in this dissertation are expressed using 8-bit pixels.

processors consume too much power or are too expensive to be used for these types of applications.

Several specialized, high-performance hardware architectures and technologies are suitable for this task. Application specific integrated circuits (ASICs) [62] are one-of-a-kind custom devices targeted towards a specific task and provide excellent performance at the expense of long development times and high cost. Field programmable gate arrays (FP-GAs) [58, 51] are an attractive alternative that offer relative ease of programming, high performance and reconfigurability to support custom applications. Digital signal processors (DSPs) [4] are inexpensive, easy to program — usually in common high level languages such as C — and offer good performance. DSPs are optimized for processing signals in real-time and offer some limited flexibility in architecture configuration. Several other esoteric technologies, such as array processors, are also available [36, 35]. However, for quick, low cost development, DSPs are a suitable and sufficient design choice.

In this dissertation, we examine and provide solutions for the issues associated with performing real-time Retinex image enhancement. We design, develop, test and evaluate the algorithm and architecture optimizations required to enable the implementation of the real-time Retinex specifically targeted for specialized, embedded DSPs. This includes optimization and mapping of the algorithm to different DSPs and configuration of these architectures to support real-time processing. We also develop and apply a particular instance of our research efforts for the real-time Retinex into an Enhanced Vision System [98]. This provides a general basis for using the algorithm in other applications or missions.

First, we developed and implemented the single-scale monochrome Retinex executing on a Texas Instruments TMS320C6711 floating-point DSP and attained 21 frames per second (fps) performance [24]. This design was later transferred to the slightly faster TMS320C6713 floating-point DSP and ran at 28 fps [25]. We then modified our design targeting the fixed-point TMS320DM642 DSP and initially achieved an execution rate of 34 fps [25]. Further refinements and optimizations improved our performance to nearly 70 fps. This design was implemented as part of an Enhanced Vision System (EVS) and demonstrated during EVS flight tests in August and September of 2005. Inputs from two single-band cameras were Retinex enhanced, registered, and fused. The system operated at over 34 fps. Finally, we migrated our design to a TMS320C6416 fixed-point DSP. After making several additional optimizations and exploiting the enhanced architecture of the TMS320C6416 we obtained 108 fps performance for the single-scale, single-band (monochrome) Retinex and 20 fps performance for the three-scale, three-band (color) Retinex.

Several different user communities will benefit from this enabling technology. The Aviation Safety Program Office at NASA LaRC will continue to support applying the real-time Retinex in future technology demonstrations on the NASA LaRC ARIES 757 (NASA 757) research aircraft. The Transportation Security Administration is interested in using the Retinex in applications to improve Homeland Security. The U.S. Army has provided funding to study using the real-time Retinex as part of a system to find improvised explosive devices (IEDs) from unmanned aerial vehicles (UAVs). The real-time Retinex also has been identified for potential use in future NASA space programs including lunar and planetary exploration missions and autonomous landing systems.

In Chapter 2 of this dissertation, we discuss the mathematics behind the Retinex algorithm. In Chapter 3 we give an overview of the architectures of our chosen DSP hardware.

In Chapter 4 we describe our test environment, and the software tools used to develop,

implement and measure the performance of the real-time Retinex. Chapter 5 is the heart of this dissertation. In it we discuss the optimization techniques we developed and applied to achieve real-time Retinex performance. In Chapter 6 we describe the EVS, and discuss how particular instances of the real-time Retinex were used in this context. In Chapter 7 we discuss future Retinex research issues and their potential solutions. This includes discussions of distributing the core structures developed for the DSP platforms into a multiprocessor environment, and the algorithm and architecture modifications required to process larger format images. Finally, in Chapter 8 we give our conclusions to this research.

## Chapter 2

## Retinex Image Enhancement

The Retinex is a general-purpose image enhancement algorithm that is used to produce good visual representations of scenes. The algorithm is derived from the last version of Edward Land's Retinex model [37] of the innate ability of human vision to perceive vivid color and detail across widely varying lighting conditions. In addition, this perception is relatively independent of the spectral characteristics of the illuminant. Jobson, et al. extended and improved Land's Retinex into a general-purpose enhancement algorithm that simultaneously provides dynamic range compression, color constancy, and color and lightness rendition. The first version of their work, the single-scale Retinex (SSR), provided good performance, but traded-off dynamic range compression for color rendition [33]. They improved their design by using multiple scales (multi-scale) within the Retinex (MSR) to address this tradeoff, and additionally added a method of color restoration to improve color rendition when gray-world violations occur within an image [32]. Other methods, such as post-processing using a white balance technique [56] have also been added. These additions extend the potential utility of the Retinex, but they also increase the computational require-

**Figure 2.1:** The top row of images from left to right have simulated tungsten, fluorescent, and sunlight illumination sources. The bottom row has the same images after Retinex processing. The effects of the different illumination sources is nearly completely removed.

ments of the algorithm. We concentrate on the SSR and MSR versions of the algorithm.

Figure 2.1 is an example that shows the color constancy property of the Retinex. The top row of images have simulated tungsten, fluorescent, and sunlight illumination sources from left to right respectively, and the bottom row is the image after Retinex enhancement. The Retinex processing has almost totally removed the effect of different illuminants on the scene. Figure 2.2 is a good visual illustration of the dynamic range compression property. Retinex processing of the image on the left dramatically brings out the details in the dark regions of the image without saturating the bright regions. Both of these examples are processed using the color version of the MSR. Figure 2.3 shows an example of monochrome SSR processing. The contrast and sharpness of the original is improved significantly.

**Figure 2.2**: Many image processing algorithms would either saturate the bright regions or clip the dark regions of the image on the left. The Retinex processed image on the right appears almost uniformly illuminated without exhibiting these effects.

The Retinex is a member of the class of center/surround functions which are similar to well known difference-of-Gaussian (DOG) functions [27, 54]. For the Retinex, the center is one pixel wide and its magnitude is the pixel value and the surround is a Gaussian. The single-scale Retinex is given by

$$R_i(x_1, x_2) = \log(I_i(x_1, x_2)) - \log(I_i(x_1, x_2) * F(x_1, x_2)), \qquad i = 1, \dots, S$$

(2.1)

where  $I_i$  and  $R_i$  are the *i*th spectral band of the input and output image, respectively. For a grayscale image S = 1 and for a standard color image S = 3. The log is the natural logarithm function and "\*" represents convolution. F is a Gaussian surround (or kernel) function defined by

$$F(x_1, x_2) = \kappa \exp[-(x_1^2 + x_2^2)/\sigma^2]$$

(2.2)

where  $\sigma$  controls the spatial extent of the surround, and  $\kappa = 1/\left(\sum_{x_1} \sum_{x_2} F(x_1, x_2)\right)$  is a

**Figure 2.3**: On the left is a low contrast, dimly lit grayscale digital image; on the right is the single-scale Retinex processed image — single-scale processing increases the contrast and sharpness.

normalization factor. Canonical gain,  $\alpha$ , and offset,  $\beta$ , values are applied to convert the Retinex output into the user display domain, so the final form of the single-scale Retinex is

$$R_i(x_1, x_2) = \alpha \left( \log(I_i(x_1, x_2)) - \log(I_i(x_1, x_2) * F(x_1, x_2)) \right) - \beta, \qquad i = 1, \dots, S$$

(2.3)

Values for  $\alpha$ ,  $\beta$ , and  $\sigma$  are application dependent and determined empirically. For example, in normal room light conditions values of 200, -120, 80 respectively produce good results.

The multi-scale Retinex is defined as the weighted sum of K SSR outputs, where K is the number of scales. Thus the MSR is given by

$$R_i(x_1, x_2) = \sum_{k=1}^K W_k \left( \log(I_i(x_1, x_2)) - \log(I_i(x_1, x_2) * F_k(x_1, x_2)) \right)$$

(2.4)

where the  $F_k$  are now defined as

$$F_k(x_1, x_2) = \kappa_k \exp[-(x_1^2 + x_2^2)/\sigma_k^2]. \tag{2.5}$$

The  $W_k$  are the weighting factors and the  $\kappa_k$  are the normalization factors associated with each scale. Jobson et al. [32] have shown, empirically, that three scales with reasonable local

to global coverage, and equal weights provide good performance for most images. Again a canonical gain  $\alpha$ , and offset,  $\beta$ , are applied thus the final form of the MSR is

$$R_i(x_1, x_2) = \alpha \sum_{k=1}^K W_k \left( \log(I_i(x_1, x_2)) - \log(I_i(x_1, x_2) * F_k(x_1, x_2)) \right) - \beta.$$

(2.6)

The derivation of the computational complexity of the Retinex is straightforward. Assume that the input image dimension size is  $N \times N$ , the extent of the surround, F, is  $M \times M$ , circular convolution is performed in the spatial domain, and ignore the operations involving  $\alpha$ ,  $\beta$ ,  $W_k$  and the computations required to generate  $F_k$ . We show in Section 5.1.2, that these are all valid assumptions. Then for the single-scale monochrome Retinex, there are  $M^2$  multiplies and  $M^2-1$  additions for every pixel. There are also  $2N^2$  logarithm operations — two logarithms for each pixel, and  $N^2$  subtractions. Thus, the running time of the algorithm is driven by the convolution operation and the complexity is  $O(N^2M^2)$ . As the extent of F approaches the size of the image, i.e.  $M \to N$ , the complexity becomes  $O(N^4)$ . For the one scale, multi-spectral case, the monochrome algorithm is performed S times, once for each spectral band. The complexity remains the same,  $O(N^2M^2)$ . For the multi-scale, multi-spectral case, the convolution and the other arithmetic operations are performed K times, once for each scale. This is subsequently repeated S times, once for each spectral band. Additionally, as discussed in Section 5.4, for any multi-spectral case, functions may be required to divide the spectrum into its individual component parts for processing, and to combine the processed components back together again. However, the complexity still remains the same  $-O(N^2M^2)$ . Methods to reduce the running time of the algorithm are discussed in Chapter 5.

## Chapter 3

## Digital Signal Processors

For our research we have selected four state-of-the-art Texas Instruments (TI) DSPs for implementation and performance evaluation of the real-time Retinex (RTR). TI processors were chosen because of their flexible and powerful architecture, good support tools, availability of the DSPs to the researchers, low cost of evaluation boards, and our past familiarity with using TI processors. Many other DSPs, such as Analog Devices SHARC processors, would also provide reasonable hardware platforms for implementation. All of the TI DSPs that were chosen are based on an advanced very-long-instruction-word (VLIW) [71] architecture. This type of architecture achieves high performance by exploiting instruction-level parallelism. Multiple execution units operate in parallel to execute multiple instructions during a single clock cycle. Our four target DSPs are the TMS320C6711, TMS320C6713, TMS320DM642, and TMS320C6416. In this chapter we discuss the relevant details of each of these processors.

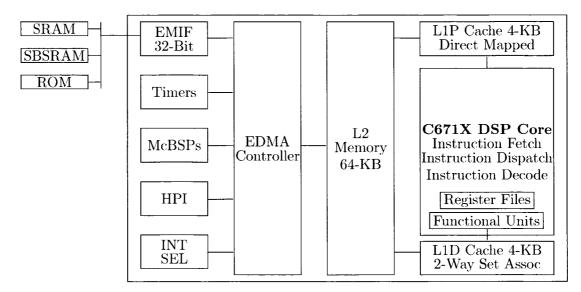

Figure 3.1: Primary DSP components include the CPU, L1 Data Cache, L1 Program Cache, L2 memory (SRAM/Cache) and EDMA Controller.

### 3.1 TMS320C6711

Our first target, the TMS320C6711B (C6711) DSP, is a 32-bit floating point processor that offers up to 1200 millions instructions per second (MIPS)/900 million floating point operations per second (MFLOPs) performance at a clock rate of 150 MHz (6.67 ns cycle time) [73]. As shown in Figure 3.1 the processor is divided into three main components: the CPU (or core), memory, and peripherals.

The CPU has eight independent functional units and a 256-bit wide instruction word that allows up to eight 32-bit instructions to be supplied to the units during every clock cycle. The functional units are mapped into two sets where each set contains four units and a register file. In total the eight functional units provide four fixed/floating point arithmetic logical units (ALUs), two fixed-point ALUs, and two fixed/floating-point multipliers. Two multiply-and-accumulate (MACs) per cycle can be performed for a total of up to 300 Million ... MACs (MMACs) per second. Each of the two register files contains sixteen 32-bit registers

for a total of 32 general-purpose registers. Six of the functional units have access to the register file on the opposite side via a cross path. Like a MIPS processor, the CPU uses a load/store architecture, where all instructions operate on registers. There are dual 64-bit load data paths and dual 32-bit store data paths.

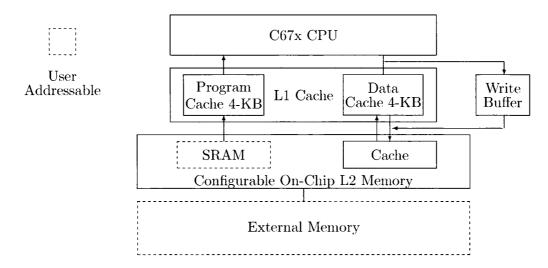

The DSP has a two-level memory architecture for both program and data [88]. Figure 3.2 is a general outline of the architecture. This hierarchical architecture is used to reduce the average memory access time by exploiting the temporal or spatial locality of data [87]. The Level 1 data cache (L1D) is a 32-Kbit 2-way set associative cache that services data accesses from the CPU. It has a 32-Byte line size and 64 sets. The L1D is implemented with a single bank of dual-ported 64-bit memory and can service up to two data accesses from the CPU on every cycle. The L1D is a read-allocate cache, but does not write-allocate<sup>1</sup>. A 32-bit by 4-entry write buffer between the L1D and the L2 memories is used to capture write misses. The Level 1 program cache (L1P) is a 32-Kbit direct-mapped, read-allocate cache that services program fetches from the CPU. It has a 64-Byte line size and 64 sets.

The Level 2 (L2) memory space is 64-KBytes that can be configured as all SRAM, all cache, or combinations of the two in 16-KByte increments. This memory services requests from the L1P, L1D, enhanced direct memory access (EDMA), or internal cache operations, with request priority from highest to lowest as listed. It is divided into four 64-bit banks that operate at the CPU's clock rate, 150 MHz, but pipelines accesses over two cycles. Any portion of L2 configured as cache (L2 Cache) is organized as 128 sets with 128-Byte line size. The associativity varies from 1-way for when the cache capacity is 16-KBytes, up

<sup>&</sup>lt;sup>1</sup>A read/write-allocate cache allocates space (i.e. selects a location in the cache) on a read/write miss according to the cache allocation policy.

**Figure 3.2**: General outline of 2-level internal memory architecture of C67x processors. The dashed boxes are user addressable memory.

to 4-way at 64-KBytes. The different configuration modes are shown in Figure 3.3. The operation of L2 Cache is similar to that of both the L1P and L1D caches. On a cache hit the L2 cache services the request directly. The L2 Cache is a writeback <sup>2</sup> cache so external memory is not updated until the line is either evicted or written back using cache control registers. Unlike the L1D, the L2 Cache is read-allocate and write-allocate. A least-recently used policy (LRU) is used for line selection.

Several peripherals are located within the processor. There is a multichannel EDMA controller that supports up to 16 channels of data transfers There is a host port interface (HPI) that allows a host processor to directly address the CPU's memory space. There is also a 32-bit external memory interface (EMIF) that provides an interface to external devices such as synchronous dynamic random access memory (SDRAM) and read-only memories (ROMs) [78].

<sup>&</sup>lt;sup>2</sup>Writeback is the process of writing data that has been modified from a valid, but now dirty cache line to lower-level memory. Write hits to a writeback cache are not immediately forwarded to lower-level memory.

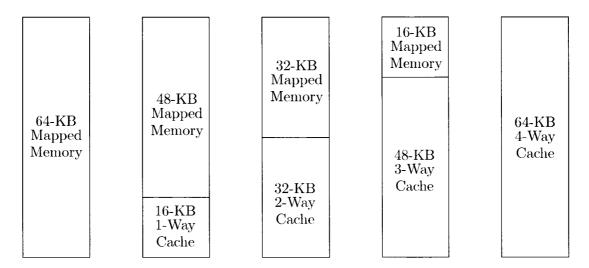

Figure 3.3: Configuration modes for the C6711 L2 memory.

#### 3.2 TMS320C6713

Our second target, the TMS320C6713 (C6713), is a 32-bit floating point processor that performs up to 1800 MIPS/1350 MFLOPS at a clock rate of 225 MHz (4.4 ns instruction cycle time) [84]. The architecture of the C6713 is very similar to the C6711, and code operating on one device directly ports over to the other [92]. The most relevant differences in the two devices are listed below.

- The C6713 operates at 225 MHz while the C6711 only operates at 150 MHz.

- The C6713 has a larger internal memory. The L1 caches are the same, but the C6713 has an additional 192-KBytes of SRAM in L2 that only functions as mapped memory.

- The C6713 has a software-configurable Phase-Lock Loop (PLL) controller that can be used to select different clock frequencies for the DSP core, peripherals and the EMIF [94]. Speeding up EMIF transfers can enable faster throughput.

**Figure 3.4**: Block diagram of primary DM642 components. The DM642 has special instruction extensions to accelerate video applications.

#### 3.3 TMS320DM642

Our third target is the TMS320DM642 (DM642). The DM642 is a 32-bit fixed-point processor that performs up to 4800 MIPS at a clock rate of 600 MHz (1.67 ns instruction cycle time) [86]. A block diagram of the processor is shown in Figure 3.4. The DM642 also has eight independent functional units consisting of six ALUs and two enhanced multipliers. In addition to standard multiplies, the multiply units include hardware that can perform bit-count, rotates, and bidirectional variable shifts. Four 32-bit MACs per cycle can be performed for a total of 2400 MMACs per second, or eight 8-bit MACs per cycle for a total of 4800 MMACS. There are new instruction extensions to accelerate video and imaging applications, and to improve the parallelism of the architecture [79]. This includes support for packed 8-bit and 64-bit data types, and instructions that perform non-aligned loads and stores of words or double words.

The DM642 also has a two-level cache [95]. The L1P is a 16-KByte direct-mapped

cache with 32-Byte line size and 512 sets. Multiple cache misses are pipelined. The L1D is 16-KBytes deep and is 2-way set associative with a 64-Byte line size and 128 sets. It is implemented as eight 32-bit wide banks of single-ported memory, as opposed to the single bank of dual-ported memory of the C671X devices. Each single-ported bank allows only one access per cycle. The L1D is a read-allocate only cache where new lines are allocated for L1D read misses but not write misses. The L1D implements a LRU line allocation policy for read misses and pipelines multiple misses. A 64-bit by 4-entry write buffer between L1D and L2 memory captures data from write misses. This buffer is an enhanced version of the one in the C671X in that the L2 can process a new request from the write buffer every cycle, as opposed to every 2 cycles on the C671X, provided that the L2 bank is not busy. Additionally, the DM642 write buffer allows merging of write requests, thus effectively increasing the write buffer capacity, reducing the stall penalty, and reducing the overall number of write operations the L2 must process.

The L2 memory is 256-KBytes that can be configured as local SRAM, cache or combinations of the two. This memory services cache misses from the L1P, the L1D, the EDMA controller and internal cache operations with request priority from highest to lowest as listed. It is divided into eight 64-bit banks that operate at the CPU's clock rate, 600 MHz, but pipelines accesses over two cycles. Four L2 Cache configuration modes are supported: 32-KByte capacity organized as 64 sets, 64-KByte capacity as 128 sets, 128-KByte capacity as 256 sets, and 256-KByte capacity as 512 sets. L2 Cache is always 4-way set associative with 128-Byte line sizes and operates as a write-back cache. A cache line is allocated for both read and write misses, and a LRU policy is used for line selection.

The DM642 also has many of the same peripherals as the C671X devices with several

extensions and additions including a 64-bit EMIF and three configurable video port peripherals [89]. The video ports provide a glue-less interface to common video decoder and encoder devices. Each video port can be configured for either video capture or display, and each port supports up to two channels with a 5120-Byte buffer that is shared between the two channels.

#### 3.4 TMS320C6416

Our fourth target is the TMS320C6416 (C6416). The C6416 is a 32-bit fixed-point processor that performs up to 8000 MIPS at a clock rate of 1000 MHz (1 ns instruction cycle time) [97]. A block diagram of the processor is shown in Figure 3.5. The C6416 has eight independent functional units consisting of six ALUs and two enhanced multipliers capable of performing four 16-bit × 16-bit multiplies every clock cycle with add/subtract operations. Four 32-bit MACs per cycle can be performed for a total of 4000 MMACs per second, or eight 8-bit MACs per cycle for a total of 8000 MMACS. The C6416 also includes support for packed 8-bit and 64-bit data types, and allows for non-aligned loads and stores of words/double words [79]. There are two register files, each containing 32, 32-bit registers for a total of 64 general-purpose registers. All eight of the functional units have access to the opposite register file and the dual load and store data paths are 64-bits wide.

The C6416 also has a two-level cache [97]. The L1P and L1D are the same size and operate the same as the respective memories on the DM642. The L2 memory has been increased to 1024-KBytes and can be configured as all mapped memory or combinations of cache (up to 256-KBytes) and mapped memory. Any portion of L2 memory partitioned

**Figure 3.5**: Block diagram of primary C6416 Components. Note the larger L2 memory and 64-bit EMIF bus.

as cache has the same modes as on the DM642. The C6416 has two EMIFs: one 64-Bits wide and one 16-Bits wide. The total external addressable memory space of 1280-MBytes. Table 3.1 summarizes the pertinent parameters of the DSPs.

| DSP   | Type        | Frequency | L1        | L2        | EMIF     | EMIF Clk |

|-------|-------------|-----------|-----------|-----------|----------|----------|

|       |             | (MHz)     | (K-Bytes) | (K-Bytes) | (Width)  | (MHz)    |

| C6711 | Floating-pt | 150       | 8         | 64        | 1 32-bit | 100      |

| C6713 | Floating-pt | 225       | 8         | 256       | 1 32-bit | 90       |

| DM642 | Fixed-pt    | 720       | 32        | 256       | 1 64-bit | 133      |

| C6416 | Fixed-pt    | 1000      | 32        | 1024      | 1 32-bit | 100      |

|       |             |           |           |           | 1 64-bit | 100      |

Table 3.1: DSP Specifications

# Chapter 4

# Test Environment

We now describe the platforms that support each DSP and the general hardware and software test environment. This environment will be used to test, analyze and evaluate our optimization techniques discussed in Chapter 5.

#### 4.1 DSP Evaluation Modules

Each DSP is embedded on a different printed circuit board for test and evaluation. The circuit boards are called EVMs (evaluation modules). Figure 4.1 shows the EVM for the DM642. The other EVMs look similar to this. As can be seen in the figure, each EVM has several components and interfaces to support the associated DSP. We will briefly describe the EVMs for each of our selected DSPs only defining the parts relevant to our discussion. We will then describe the tools used for software development, optimization, and performance analysis.

The C6711 EVM has 16-MBytes of SDRAM clocked at 100 MHz that is used as external memory for the chip. There are 128-KBytes of flash memory which is usually used to

Figure 4.1: Picture of DM642 EVM board. Numerous components are on the EVM circuit board to support testing the DSP for a wide variety of applications. We primarily use the peripherals associated with video capture and display.

hold application code and parameters when power is disconnected from the board. Communication to a host PC — primarily for downloading code and gathering statistics — is through a parallel port. An embedded Joint Test Action Group (JTAG) controller is used for emulation and debugging [28]. The board also has an expansion connector to support adding additional memory, peripherals, or daughter-cards [77].

The C6713 EVM has 8-MBytes of SDRAM clocked at a default rate of 90 MHz and 512-KBytes of flash memory. Communication to a host PC is performed through a Universal Serial Bus (USB) port. An embedded USB JTAG controller is provided for debugging [66]. The EVM also has an Intel LXT971 Ethernet port for data transfers to an external device.

The DM642 EVM has 32-MBytes of SDRAM clocked at 133 MHz, 4-MBytes of flash memory, an Intel LXT971 Ethernet interface, and a standard JTAG connector for external emulation [67]. The C6416 EVM has 256-MBytes of SDRAM on the 64-bit EMIF bus and 8-MBytes on the 32-bit wide EMIF bus. Both busses are clocked at 100 MHz. The

board also has 4-MBytes of flash memory, and a dedicated JTAG connector for external emulation [3].

#### 4.1.1 Video Capture and Display for C6711 and C6713 EVMs

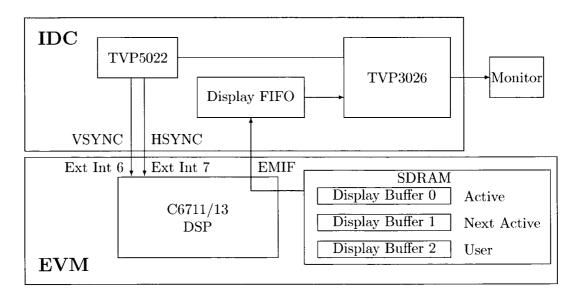

For the C6711 and C6713 EVMs, video capture, display, and data formatting are performed by an imaging daughter-card (IDC) [76] that connects to each board's expansion connectors. The main components of the IDC are a TI TVP5022 digital video decoder chip [74], a TI TVP3026 RAMDAC digital video encoder chip [70], a Xilinx FPGA for control, buffer management and interface logic, and 2-MBytes of SDRAM for capture frame memory. The IDC also has a female Radio Corporation of America (RCA) connector that is used to receive video, and a standard 15-pin female video graphics array (VGA) connector that is used to supply red, green, blue (RGB) [69] video output to a monitor.

Figure 4.2 is a block diagram of the video capture subsystem [72]. A video input signal from an NTSC (or Phase Alternating Line (PAL)) source is digitized by the TVP5022 decoder chip into a standard  $Y'C_BC_R$  4:2:2 format<sup>1</sup>. The  $Y'C_BC_R$  is a color space used to represent digital component video where color is represented by a luma component (Y'), and two chroma components ( $C_B$  and  $C_R$ ). The 4:2:2 notation<sup>2</sup> designates the ratio of Y',  $C_B$  and  $C_R$  signals where  $C_B$  and  $C_R$  are co-sited and subsampled at half the horizontal resolution of Y' [53].

<sup>&</sup>lt;sup>1</sup>The ITR-R BT.601 standard defines the Y'C<sub>B</sub>C<sub>R</sub> color space and the 4:2:2 sampling organization and resolutions. The BT.656 standard defines the serial and parallel interfaces for transmitting Y'C<sub>B</sub>C<sub>R</sub> 4:2:2 digital video [29, 100].

<sup>&</sup>lt;sup>2</sup>The number 4 originates from a multiplier of the BT.601 chosen baseline frequency of 3.375 MHz and corresponds to a sampling rate of 13.5 MHz, a standard frequency for digitizing NTSC or PAL; similarly the 2s correspond to 6.75 MHz [100]. Other common subsampling ratios include 4:4:4, 4:1:1 and 4:2:0 (where the chroma components are sited interstitially)

Figure 4.2: IDC video capture subsystem

The 8-bit wide  $Y'C_BC_R$  pixel stream — interleaved as  $C_B$ , Y',  $C_R$ , Y', ..., is fed into the FPGA. The FPGA separates and stores the stream into capture frame memory buffers as two separate fields (odd and even) in three separate blocks  $(Y', C_B, C_R)$  as shown in Figure 4.2. The TVP5022 chip also controls all video input timing including a vertical synchronization signal that generates a CPU interrupt once per frame, and a blanking signal that indicates the presence of data on the pixel bus to the FPGA.

The capture frame memory buffers are memory-mapped into the DSP address space as read-only and are accessed via the EMIF. A triple buffering scheme is used to allow an application to obtain a new buffer of the most recently captured data without waiting. The "active" buffer is currently receiving data from the TVP5022. The "last active" buffer is the last buffer that was filled by the TVP5022. The "user" buffer is owned and read by the user application. If the application can maintain a full 30 fps processing rate, the buffers are physically walked through in a circular sequence by the FPGA and user application. If the user application attempts to access the buffers faster than 30 Hz, then duplicate frames will

Figure 4.3: IDC video display subsystem

be returned. If the application executes slower, then captured frames will be overwritten.

Figure 4.3 is a block diagram of the video display subsystem [72]. Video display is limited to a max size of 800 × 600 pixels with 8-bits per pixel for grayscale or 16-bits per pixel for RGB 565 color<sup>3</sup>. A total output frame display buffer size of 2.88-MBytes (800 × 600 × 16-bits for 3 buffers) is allocated and linked into the DSP's external memory space. Timing signals for video readout include a vertical synchronization (VSYNC) signal and a horizontal synchronization (HSYNC) signal. The VSYNC signal triggers a CPU interrupt and the associated interrupt service routine posts a display semaphore which is used to wait for new frames. The HSYNC signal triggers an EDMA event to copy one line of display data from the display buffer to the IDC display first-in-first-out (FIFO) buffer. The TVP3026 RAMDAC chip then transmits this line to the output port.

Analogous to the video capture system, a triple buffering scheme is used for data transfers. The "user" buffer is owned by the user application. The "next active" buffer will be

<sup>&</sup>lt;sup>3</sup>RGB 565 represents color values using 5-bits for red, 6-bits for blue and 5-bits for green

returned on the next buffer request. The "active" buffer is being used for EDMA transfers. If the application attempts to access buffers too fast, frames will be dropped. If access is too slow, frames will be displayed repeatedly.

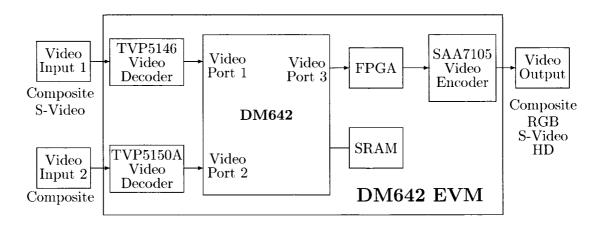

#### 4.1.2 Video Capture and Display for DM642 and C6416 EVMs

The DM642 has three on-chip video ports. On the EVM two of the ports are configured as capture ports (video ports 0 and 1) and one is configured as a display port (video port 2). The capture ports interface to TI TVP5146 [96] and TVP 5150A [91] video decoders. The TVP5146 supports composite<sup>4</sup> or Y/C format<sup>5</sup> inputs, and the TVP5150A supports composite inputs only on the EVM. The output of the display port is routed through an FPGA (for functions such as on-screen display or overlays) to a Phillips SAA7105 video encoder. The SAA7105 drives either NTSC/PAL composite video, S-video, RGB, or high-definition component video. Figure 4.4 is a block diagram of the system. Analog input video is digitized into planar  $Y'C_BC_R$  4:2:2 component video and buffered in external memory similar to the method used for the IDC.

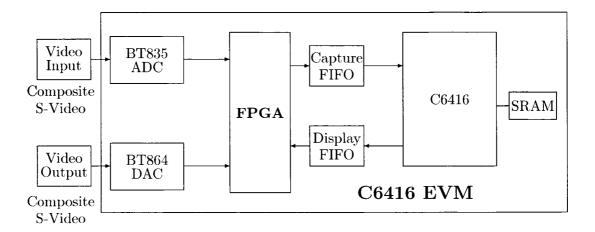

A block diagram of the C6416 EVM is shown in Figure 4.5. Analog video is digitized by a Conextant BT835 decoder into a  $Y'C_BC_R$  4:2:2 format and stored by the FPGA into the capture FIFO buffer. Instead of being written in planar form as on the C6711 EVM, the captured data is stored in  $C_R$ , Y',  $C_B$  ... interleaved order. The FIFO is memory-mapped into the address space of the DSP and accessed via the EMIF. Similarly, output data to be displayed is stored in  $Y'C_BC_R$  4:2:2 format and written using a EDMA channel into the

$<sup>^4</sup>$ Composite video combines luma, chroma and sync signals into a single waveform carried on a single wire pair.

<sup>&</sup>lt;sup>5</sup>Y/C has the luma and chroma components carried on separate signal wire pairs to reduce signal crosstalk. Y/C is often incorrectly referred to as S-video, a magnetic tape modulation format.

Figure 4.4: DM642 EVM block diagram

display FIFO by the DSP. The pixel stream is then transferred to a Conextant BT864 for digital-to-analog conversion (DAC) and NTSC/PAL encoding.

## 4.2 Development Tools

Several software development tools are used on all of the EVMs, including a C-compiler, assembly optimizer, and a debugger for visibility into source code execution. These tools are incorporated into TI's Code Composer Studio (CCS). Other rapid prototyping software tools used include a chip support library (CSL) [81] to configure and control on-chip peripherals, an image data manager (for the IDC) for DMA abstraction, and a C-callable DSP library (DSPLib) [90] that contains a collection of highly optimized functions such as the well-known Fast Fourier Transforms (FFT) [7, 49, 64]. A scalable real-time operating system (OS) kernel called DSP/BIOS (basic input output system) is used to provide preemptive multi-threading, hardware abstraction and real-time analysis [80].

Figure 4.5: C6416 EVM block diagram

Compiler options are used to control speculative loading, auto in-lining thresholds, data alignment/placement information, and advanced loop optimizations [82]. Significant performance improvements can be gained by using target-specific instructions called intrinsics [93]. Intrinsics are special functions that allow certain assembly statements to be easily embedded in application code. For example to find the maximum value of two variables x1 and x2 we simply use the optimized in-line intrinsic function call for max2 — max2(x1, x2).

## 4.3 Test-Bed Components and Operation

A test-bed is used to implement and analyze the real-time Retinex algorithm and to support testing the algorithm within the context of the EVS for our case study. The baseline test-bed is composed of

- a standard NTSC video source (for example a video camera, DVD player or VCR),

- a monitor that accepts a composite video input to display the processed output,

**Figure 4.6**: Block diagram of the test-bed — the Host PC only provides setup information to the EVM; after initiation, the DSP executes independently.

- a host personal computer (PC) running CCS for code development and analysis,

- a JTAG emulator for communication and debugging, and

- the target DSP on an EVM as discussed in Section 4.1.

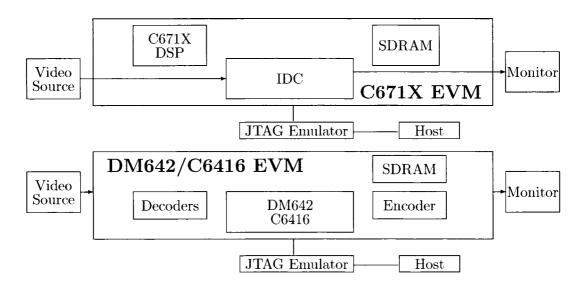

Figure 4.6 shows general outlines of the test-bed using the C6711 and C6713 EVMs with IDCs, and the DM642 and C6416 EVMs. The host PC is not part of the image processing chain.

General operation of the test-bed is as follows. C code to perform the Retinex is written on the PC using the CCS software. This code is compiled, assembled and linked into a common object file format (COFF) and is downloaded into the DSP on the EVM. Execution of the algorithm is then triggered from the PC. From this point on, the EVM operates totally independent of the PC. The functions for performance analysis are (1) video frames are captured from the source, (2) a  $256 \times 256$  pixel sized portion of the captured frame buffer is Retinex processed, and (3) the output product displayed.

#### 4.4 Performance Analysis

The execution time of the Retinex is measured by using the real-time analysis tools within DSP/BIOS. These tools are composed of instrumentation code that is integrated into the target application. The code is executed at run time, and the events of interest are stored in memory on the target. This information is transferred to the host PC for display, further processing, or post-execution analysis. All instrumentation operations have fixed, short execution times and communication between the target and host is performed in the background using a low priority idle thread thus minimizing the impact on performance and program behavior.

The instrumentation modules can be called explicitly by the application through application programmer interfaces (API)s or implicitly through the calls used internally by DSP/BIOS[80]. Explicit instrumentation API modules include a statistics (STS) object manager and a trace (TRC) manager. STS objects store statistics about data variables or system performance including capturing count, maximum, total, and average values in real-time. The TRC module provides a means to enable or disable data acquisition in real-time through querying a set of bits.

Implicit instrumentation is built into DSP/BIOS and allows the user to display several values including CPU loading. CPU loading is defined as the percentage of instruction cycles that the CPU spends performing application related work — running interrupts, tasks, periodic functions, performing I/O to the host, or running any other user routine. For the remaining time, the CPU is considered idle. CPU load is be expressed by

$$CPUload = (c_w/(c_w + c_i)) \times 100 \tag{4.1}$$

where  $c_w$  and  $c_i$  are work and idle instruction cycles, respectively. CPU loading can be viewed graphically in a window with continuous updates if the there are enough idle cycles to transfer this statistic to the host. Otherwise the values can be obtained after halting the target and retrieving the stored loading values.

#### 4.5 Real-time Parameter Updates

A useful capability to test the Retinex algorithm is to be able to update parameters in real-time. TI provides a mechanism to interact with an application in real-time called real-time data exchange (RTDX)[80]. RTDX plug-ins provide a means to transfer data between a host computer and DSP devices via the JTAG interface with minimal interference with the target application. A small RTDX library runs on the target DSP while another runs on the host. An application executing on the target makes function calls to the RTDX target library's API to send or receive data. The host library, working within CCS, provides a component object model (COM)<sup>6</sup> API for communication. Any object linking and embedding (OLE)<sup>7</sup> automation client on the host can be used for display or analysis. We developed our own OLE client using Visual Basic to update Retinex parameters  $(\alpha)$ , offset  $(\beta)$ , and the standard deviation of the Gaussian surround  $(\sigma)$ .

$<sup>^{6}\</sup>mathrm{COM}$  is a Microsoft developed technology that allows communication between software components.

<sup>&</sup>lt;sup>7</sup>OLE is a Microsoft developed standard enables the creation of an object in one application that can be linked or embedded in a second application.

## 4.6 Retinex Task Within DSP/BIOS

Our code for the Retinex is written to execute as a task within the DSP/BIOS environment. This allows explicit use of the real-time analysis tools. In general, two tasks, "main" and "video processing" are scheduled. First, "main" performs a few initializations, such as setting up the chip support library, configuring the cache, and opening up an EDMA channel, and then returns. The "video processing" task is then set to run automatically by the DSP/BIOS scheduler. The video processing task consists of the following steps:

- set up several video parameters such as capture and display frame sizes,

- receive a frame from the capture frame buffer,

- call (and waits on) the Retinex processing function,

- display the Retinex output and optionally displays the unprocessed frame,

- exchange capture and display buffers, and then returns to read another frame.

STS objects are coded within the "video processing" task to determine the overall execution time of the Retinex processing function. Several STS objects are also placed within the Retinex processing function to determine internal performance characteristics. This helps to isolate the primary time consumers or "tall-poles" within the algorithm. STS API calls to set the time on an STS object, and then to check the change in time after execution of some portion of code requires approximately 18 and 21 instructions respectively. These values can be removed for a more accurate measure of performance.

## Chapter 5

# Optimizations and Performance

# Results

We now describe the optimization techniques we developed and applied to implement the real-time Retinex. This discussion is the core of our research. Our discussion will focus on the major algorithm and architecture optimizations that significantly improved performance. Additionally, each optimization was developed under the basis that it would not cause any perceptible loss in image quality.

Our baseline algorithm and architecture targets are the single-scale monochrome version of the Retinex (SSMR) and the C6711 DSP on the C6711 EVM in our test-bed. The SSMR is the simplest form of the Retinex and the C6711 has the lowest performance of the processors in this study. However both allow us to establish our core algorithm and architecture techniques and provide a basis for future optimizations, extensions, and adaptation to other platforms. One change in the architecture at this point is to configure the L2 memory as 32-KBytes of cache and 32-KBytes of SRAM. The 32-KBytes of SRAM

are sufficient to store all the required variables in our first implementation.

#### 5.1 Single-Scale Monochrome Retinex Optimizations

#### 5.1.1 Apply Convolution Equivalence

A fundamental component of the Retinex computation is to convolve the input image with a Gaussian kernel. Good single-scale Retinex renditions are obtained with a large kernel  $(\sigma > 80)$ , so performing this operation in the spatial domain is extremely time consuming. The first, and most obvious, optimization then is to use the well-known equivalence between convolution in the spatial domain and multiplication in the spatial-frequency domain [7, 20]

$$f(x,y) * g(x,y) \Leftrightarrow F(\mu,\nu)G(\mu,\nu)$$

(5.1)

where F and G are the spatial frequency domain representations of f and g respectively. We apply this concept to convolve an input image with a Gaussian kernel by employing the 2-dimensional  $M \times N$  forward and inverse Discrete Fourier Transforms (DFTs) [20] defined by

$$\hat{F}(\mu,\nu) = \frac{1}{MN} \sum_{x=0}^{M-1} \sum_{x=0}^{N-1} f(x,y) \exp[-j2\pi(\mu x/M + \nu y/N)] \text{ and}$$

(5.2)

$$f(x,y) = \sum_{\mu=0}^{M-1} \sum_{\nu=0}^{N-1} \hat{F}(\mu,\nu) \exp[j2\pi(\mu x/M + \nu y/N)], \qquad (5.3)$$

respectively, to rewrite the SSMR equation as:

$$R(x_1, x_2) = \alpha(\log(I(x_1, x_2)) - \log[\mathcal{F}^{-1}(\hat{I}(\mu, \nu)\hat{F}(\mu, \nu))]) - \beta.$$

(5.4)

The  $\hat{I}(\mu,\nu)$  and  $\hat{F}(\mu,\nu)$  represent the DFTs of an input image  $I(x_1,x_2)$ , and a Gaussian kernel  $F(x_1,x_2)$ , respectively, and  $\mathcal{F}^{-1}$  represents the inverse DFT.

Exploiting the separability of the DFT and the computational efficiency of the FFT, we compute 2-dimensional transforms by applying 1-dimensional FFTs to first the rows and then the columns of the image. The computational complexity of the FFT for the 1-dimensional case is  $O((N/2)\log(N))$  where N is the size of the complex input [20]. Thus the computational complexity of the 2-dimensional case (where the input image dimensions are  $N \times N$ ) is reduced to  $O(N^2 \log(N))$ . The FFTs are computed using the optimized TI DSPLib. This library restricts the number of input points to a power of two so we have chosen to process a 256  $\times$  256 portion of each input frame to closely match the resolution of the cameras used in our case study as discussed in Chapter 6.

The specific FFT algorithm used is the floating-point radix-2 FFT [90]. TI benchmarks the number of cycles to compute this operation by

$$C = (2n\log_2 n) + 42\tag{5.5}$$

where C is the number of cycles,  $\log_2$  is the base 2 logarithm, and n is the length of the complex input array [90]. For a 256-point FFT this corresponds to 4138 execution cycles, thus the C6711 operating at 150 MHz performs this operation in 27.6 microseconds ( $\mu$ s) under ideal benchmark conditions. To forward transform the 256 rows of a 256  $\times$  256 image requires  $\approx$  7 milliseconds (ms). All of the 256 columns of the transformed image must then be forward transformed and later, both the rows and columns must be inverse transformed (IFFT) resulting in a total of 1024, 256-point forward and inverse transforms for the input image. The Gaussian kernel must also be forward transformed resulting in and

additional 512 FFTs, so the total number of transforms is 1,536. Prior to implementation, we felt that of all the calculations performed within the algorithm, performing the 1,536 FFTs would consume the majority of the execution time. However, experimental evidence showed otherwise as we discuss in Section 5.1.3.

#### 5.1.2 Pre-Compute the Kernel

To reduce the number of FFTs performed we developed our first optimization for the algorithm. As is commonly done in practice we pre-compute and store the coefficients (or "twiddle-factors" [61]) used to calculate the FFT/IFFT. Our basic idea then was to use a similar technique for the Gaussian surround functions. For the SSMR there is only one scale so we only had to generate one surround function. Two key concepts were implemented that not only reduced the number of FFTs, but also significantly reduced the amount of memory that must be used by the algorithm. First, the Gaussian kernel is directly generated and applied in the spatial frequency domain thus eliminating the requirement to perform the FFT of the kernel. Second, the Gaussian is separable and circularly symmetric [63], and is its own (scaled) Fourier transform so it can be expressed as the product of two 1-dimensional functions and can be decomposed into horizontal and vertical projections along these dimensions. Circular symmetry implies that the two projections are the same, and the left half of either projection is the same as the right half flipped about the halfway point. Thus we only need to keep a single 128-point array of surround values to multiply with the spatial frequency domain image data. In practice we used a 256-point array to simplify indexing. Using this array instead of the full spatial frequency domain representation of the kernel saves  $\approx 0.5$ -MBytes.

#### 5.1.3 Baseline Algorithm Performance

Using our ideas for the Gaussian kernel we implemented the first DSP version of the Retinex. Table 5.1 summarizes the actual measured execution time of the overall algorithm and selected components within the algorithm. These times were obtained by placing STS objects, discussed in Section 4.4, within the algorithm.

|                | Time (ms)          |

|----------------|--------------------|

| retinex        | 1333.42 (0.75 fps) |

| fwdprocessrows | 476.11             |

| fftrows        | 9.76               |

| logorig        | 461.72             |

| fwdprocesscols | 170.77             |

| multkernel     | 13.46              |

| invprocesscols | 157.83             |

| invprocessrows | 528.71             |

| rtxeq          | 507.80             |

Table 5.1: Initial performance results from the first implementation of the SSMR.