#### University of Texas at Tyler Scholar Works at UT Tyler

**Electrical Engineering Theses**

**Electrical Engineering**

Fall 8-2011

### A Study of Multiprocessor Systems using the Picoblaze 8-bit Microcontroller Implemented on Field Programmable Gate Arrays

Venkata Mandala

Follow this and additional works at: https://scholarworks.uttyler.edu/ee\_grad

Part of the Electrical and Computer Engineering Commons

#### Recommended Citation

Mandala, Venkata, "A Study of Multiprocessor Systems using the Picoblaze 8-bit Microcontroller Implemented on Field Programmable Gate Arrays" (2011). Electrical Engineering Theses. Paper 21. http://hdl.handle.net/10950/59

This Thesis is brought to you for free and open access by the Electrical Engineering at Scholar Works at UT Tyler. It has been accepted for inclusion in Electrical Engineering Theses by an authorized administrator of Scholar Works at UT Tyler. For more information, please contact tbianchi@uttyler.edu.

# A STUDY OF MULTIPROCESSOR SYSTEMS USING THE PICOBLAZE 8-BIT MICROCONTROLLER IMPLEMENTED ON FIELD PROGRAMMABLE GATE ARRAYS

by

#### VENKATA CHANDRA SEKHAR MANDALA

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering Department of Electrical Engineering

David H. K. Hoe, Ph.D., Committee Chair

College of Engineering and Computer Science

The University of Texas at Tyler August 2011

#### The University of Texas at Tyler Tyler, Texas

This is to certify that the Master's thesis of

#### VENKATA CHANDRA SEKHAR MANDALA

has been approved for the thesis requirements on July 13, 2011 for the Master of Science Degree in Electrical Engineering

Approvals:

Thesis Chair: David H K Hoe Ph D

Member: Mukul V Shirvaikar, Ph. D.

Member: Hector A. Ochoa, Ph.D.

Chair and Graduate Coordinator: Mukul V Shirvaikar, Ph. D.

Dr. James K. Nelson, Jr., Ph.D., P.E., Dean, College of Engineering and Computer Science, Brazzel Professor of Engineering

#### Acknowledgements

First of all, I am thankful to my father Mandala Maheswara Rao and mother Suguna Kumari and sister Geetha Devi for making my dream come true. I would like to thank Dr. David Hoe, my thesis advisor, for his support in my research in different areas of Electrical Engineering. I would also thank him for his encouragement, patience and supervision from the preliminary stages to the concluding level in my thesis. Without his guidance and persistent help this thesis would not have been possible.

I would like to thank my committee members, Dr. Hector A. Ochoa and Dr. Mukul V. Shirvaikar for taking the time to review my work. I am thankful to Dr. Mukul Shirvaikar for supporting and guiding me throughout my Master's degree. I would like to thank the entire Electrical Engineering department and the University of Texas at Tyler for supporting me throughout my Master's degree. Also, I would like to thank Chris Martinez, an undergraduate student in Electrical Engineering, for helping me in my thesis. Finally, I would like to thank all those who supported me in any respect during the completion of the thesis.

#### **Table of Contents**

| List of Figures                                                 | iv  |

|-----------------------------------------------------------------|-----|

| List of Tables                                                  | vi  |

| Abstract                                                        | vii |

| Chapter One: Introduction                                       | 1   |

| 1.1 Soft Processor Cores on FPGA                                | 1   |

| 1.2 Research Objectives                                         | 2   |

| 1.3 Research Method                                             | 3   |

| 1.4 Thesis Outline                                              | 3   |

| Chapter Two: Background                                         | 4   |

| 2.1 Trend Towards Multicore Processors                          | 4   |

| 2.1.1 Power Wall Problem                                        | 4   |

| 2.2 Multicore Processor                                         | 7   |

| 2.2.1 Array of Processors                                       | 8   |

| 2.2.2 Array of Functional Units                                 | 9   |

| 2.3 Reconfigurable Computing                                    | 11  |

| 2.3.1 Advantages of Reconfigurable Computing                    | 11  |

| 2.3.2 FPGAs                                                     | 11  |

| 2.3.2.1 Microcontroller within an FPGA                          | 11  |

| 2.3.3 Array of Soft Processors                                  | 12  |

| 2.3.4 PicoBlaze Microcontroller                                 | 13  |

| 2.4 Interprocessor Communication                                | 15  |

| 2.5 Summary                                                     | 16  |

| Chapter Three: FIFO Style Interprocessor Communication          | 17  |

| 3.1 FIFO Style Communication                                    | 17  |

| 3.1.1 FIFO                                                      | 17  |

| 3.1.2 PicoBlazes with a FIFO Buffer                             | 19  |

| 3.1.3 Experimental Verification of the FIFO with Two PicoBlazes | 20  |

| 3.2 Array of PicoBlazes                                                | 20   |

|------------------------------------------------------------------------|------|

| 3.2.1 The Wrapper                                                      | 20   |

| 3.2.2 Need for an Array of PicoBlaze Units                             | 24   |

| 3.2.3 Details of the Array                                             | 25   |

| 3.2.4 Routing/Logic Cell Resources Comparison                          | 26   |

| 3.3 Experiment with Array of PicoBlazes                                | 26   |

| 3.3.1 Counting Numbers Experiment                                      | 27   |

| 3.3.2 Status Signals and Read/Write Strobe Conditions Setup            | 27   |

| 3.3.3 Validation and Results                                           | 28   |

| 3.4 Application (A 4-tap FIR Filter)                                   | 29   |

| 3.4.1 Algorithm and Simulation of FIR                                  | 29   |

| 3.4.2 Array Structural Flow For FIR                                    | 29   |

| 3.4.3 Validation and Results                                           | 31   |

| 3.5 Summary                                                            | 33   |

| Chapter Four: Shared Memory Inter-Processor Communication              | 34   |

| 4.1 Shared Memory                                                      | 34   |

| 4.1.1 Shared Memory Mode of Communication                              | 34   |

| 4.1.2 Sharing BlockRAM Between Two PicoBlazes                          | 35   |

| 4.1.3 Shared Memory for Communication Between PicoBlaze Processors     | 36   |

| 4.2 Need for an Arbiter                                                | 36   |

| 4.2.1 Arbitration                                                      | 37   |

| 4.3 Round-Robin Arbiter                                                | 37   |

| 4.3.1 Implementation of a Round-Robin Bus Arbiter                      | 38   |

| 4.3.2 Round-Robin Arbiter with Four Processors                         | 39   |

| 4.4 PicoBlazes Using Round-Robin Arbiter                               | 40   |

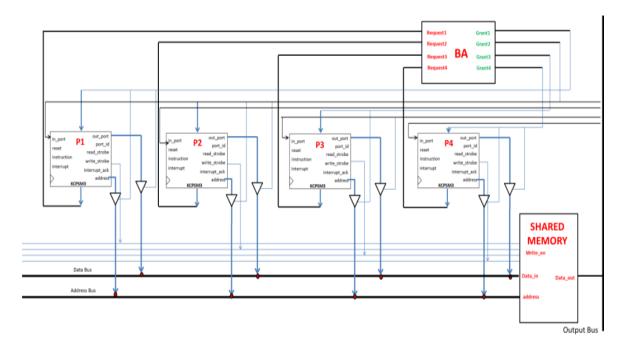

| 4.4.1 Four PicoBlazes Using Round-Robin Arbiter                        | 40   |

| 4.4.2 Implementation Description of Shared Memory with Round-robin Arb | iter |

|                                                                        | 40   |

| 4.4.3 Observations                                                     | 42   |

| 4.5 Summary                                                            | 43   |

| Chapter Fixe: Conclusions and Future Work                              | 1/   |

| 5.1 Conclusion                                                                                | . 44 |

|-----------------------------------------------------------------------------------------------|------|

| 5.2 Future Work                                                                               | . 44 |

| References                                                                                    | . 46 |

| Appendix A: Assembly Code for Button Press Experiment                                         | . 50 |

| A.1 PicoBlaze 1 to FIFO Assembly Code for Button Press Experiment                             | . 50 |

| A.2 FIFO to PicoBlaze 2 Assembly Code for Button Press Experiment                             | . 51 |

| Appendix B: Assembly Code for Counting Numbers Experiment                                     | . 53 |

| B.1 PicoBlaze 4 Assembly Code for Counting Numbers Experiment                                 | . 53 |

| B.2 PicoBlaze 1 (P1) Assembly Code for Counting Numbers Experiment                            | . 55 |

| B.3 PicoBlaze 2 Assembly Code for Counting Numbers Experiment                                 | . 56 |

| B.4 PicoBlaze 3 Assembly Code for Counting Numbers Experiment                                 | . 57 |

| B.5 PicoBlaze 5 Assembly Code for Counting Numbers Experiment                                 | . 58 |

| Appendix C: Code for 14 PicoBlazes FIR Filter Experiment                                      | . 59 |

| C.1 N-tap and T-input FIR Filter Code in C Language                                           | . 59 |

| C.2 PicoBlaze Array Code in VHDL for FIR Filter Design                                        | 60   |

| C.3 Four FIFO Wrapper Design Code in VHDL                                                     | . 79 |

| C.4 PicoBlaze 1 to PicoBlaze 10 Assembly Code for FIR Filter Design                           | . 83 |

| C.5 PicoBlazeU0 to PicoBlazeU3 Assembly Code for FIR filter Design                            | . 86 |

| Appendix D: Spartan 3E and Virtex 5 Statistics                                                | . 87 |

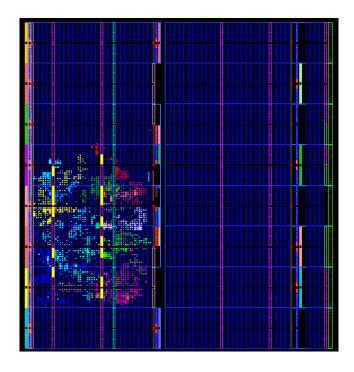

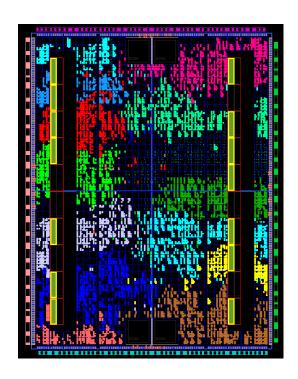

| D.1 Logic Cells LEGEND Color on Virtex 5 and Spartan 3E FPGA                                  | . 87 |

| D.2 Occupation of Logic Cell Resources on Virtex 5 FPGA                                       | . 87 |

| D.3 Occupation of Logic Cell Resources on Spartan 3E FPGA                                     | . 88 |

| D.4 Table Showing General Comparison of Virtex 5 and Spartan 3E FPGAs                         | . 88 |

| Appendix E: Arbitration Schemes                                                               | . 89 |

| E.1 Different Arbitration Schemes: (A Section from Chapter4)                                  | . 89 |

| Appendix F: Delay Statistics for Spartan 3E and Virtex 5                                      | . 91 |

| F.1 Place and Route Delay Statistics for Spartan 3E and Virtex 5 FPGAs                        | 91   |

| F.2 Synthesis (Pre-Routing) Report Statistics for <i>Spartan 3E</i> and <i>Virtex 5</i> FPGAs | 92   |

#### **List of Figures**

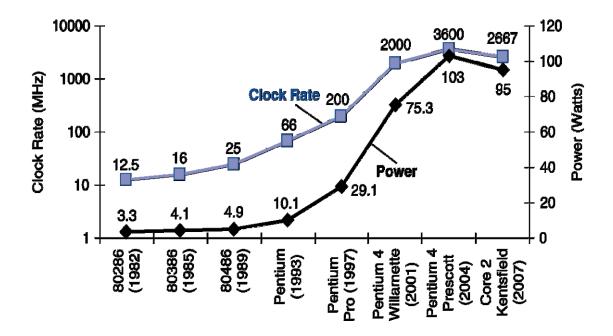

| Figure 2.1: Trend in clock rate and power for Intel uniprocessors (single core)             | 5  |

|---------------------------------------------------------------------------------------------|----|

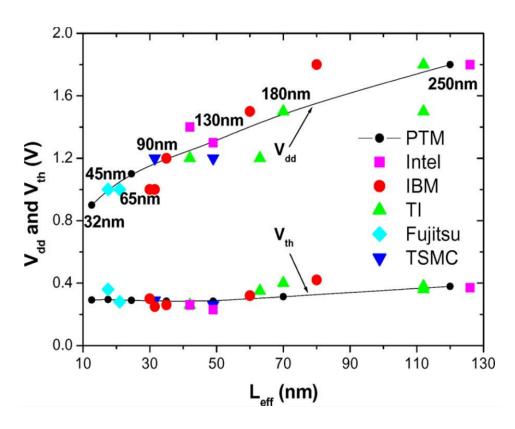

| Figure 2.2: Plot showing supply voltage $(V_{dd})$ and threshold voltage $(V_{th})$ scaling |    |

| transistor size $(L_{eff})$                                                                 | 7  |

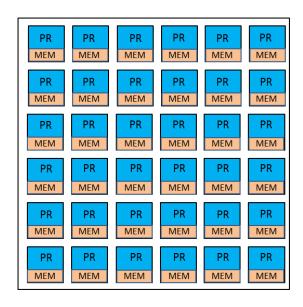

| Figure 2.3: Array of processors where PR is Processor and MEM is memory                     | 9  |

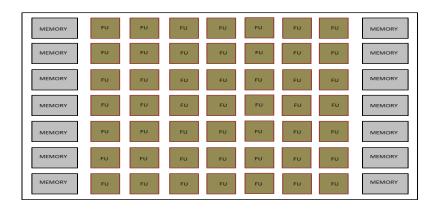

| Figure 2.4: Array of Functional Units (FU)                                                  | 10 |

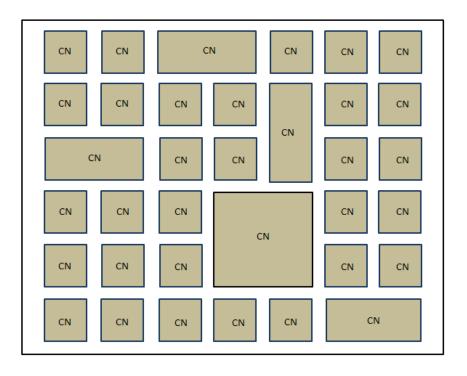

| Figure 2.5: Array of Soft Processors (CN stands for Computation Nodes)                      | 13 |

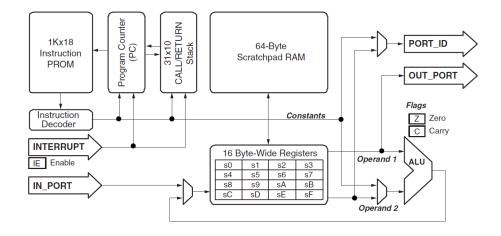

| Figure 2.6: PicoBlaze Microcontroller Block Diagram                                         | 14 |

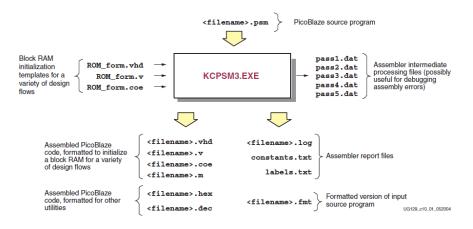

| Figure 2.7: KCPSM3 Assembler Files.                                                         | 15 |

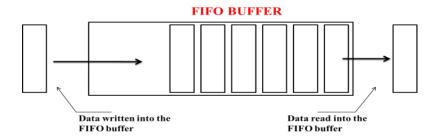

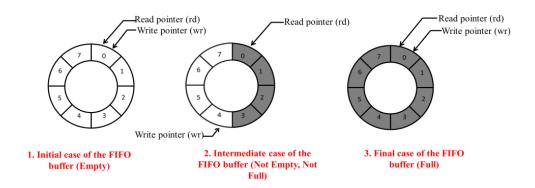

| Figure 3.1: Theoretical view of a FIFO Buffer                                               | 18 |

| Figure 3.2: Three Possible Cases of a circular FIFO Buffer                                  | 18 |

| Figure 3.3: Pseudo code for FIFO write and read cases                                       | 19 |

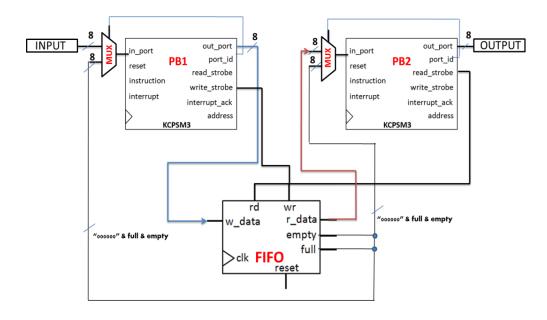

| Figure 3.4: Two PicoBlazes (PB1 and PB2) communicating through a FIFO Buffer                | 19 |

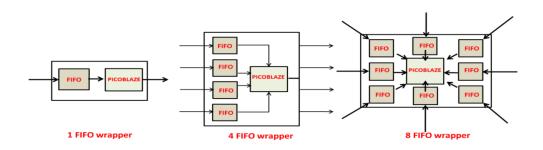

| Figure 3.5: Different topologies in designing a Wrapper                                     | 21 |

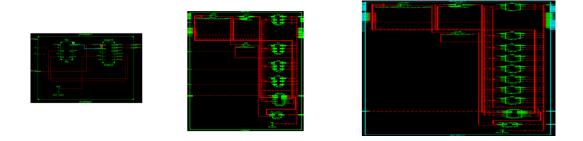

| Figure 3.6: Wrapper design view in schematic editor (1, 4 and 8 FIFOs from left)            | 21 |

| Figure 3.7: Detailed Wrapper with four FIFO buffers and a PicoBlaze Processor               | 22 |

| Figure 3.8: Port map for the Wrapper entity in VHDL                                         | 23 |

| Figure 3.9: Wrapper with port id coded in VHDL.                                             | 24 |

| Figure 3.10: A wrapper that connects to four neighboring Processors                         | 25 |

| Figure 3.11 Experiment setup with 5 PicoBlazes where PicoBlaze 4 is destination             | 27 |

| Figure 3.12: Destination PicoBlaze holding data in FIFOs.                                   | 28 |

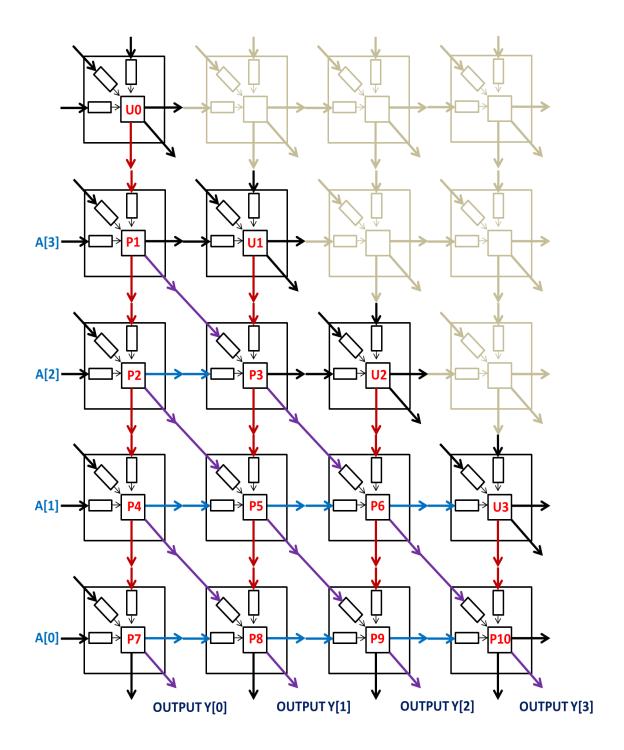

| Figure 3.13: A 4-tap FIR Filter Application on Array of PicoBlaze Units                     | 31 |

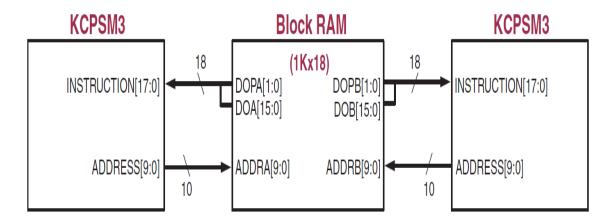

| Figure 4.1: Two PicoBlazes sharing one Block RAM                                            | 35 |

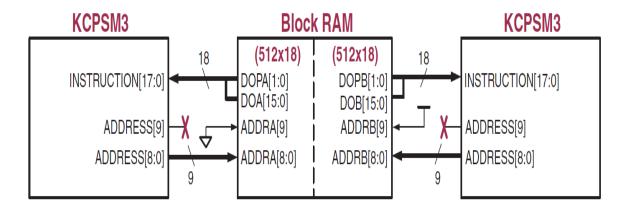

| Figure 4.2: Two PicoBlazes using two separate 512- instruction memory sections              |    |

| from BRAM                                                                                   | 36 |

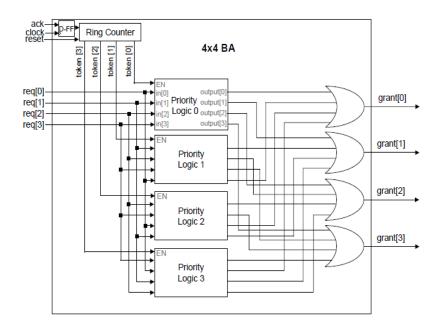

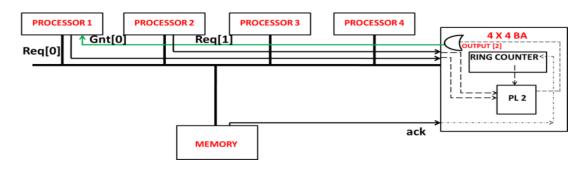

| Figure 4.3: Round-robin Arbiter.                                                            | 39 |

| Figure 4.4: Round-robin Arbiters with Four Processors                                       | 40 |

| Figure 4.5: Four PicoBlazes with Shared RAM mode communication using Bus                    |    |

| Arbiter                                                                           | 41 |

|-----------------------------------------------------------------------------------|----|

| Figure D-1: Legend colors for 14 PicoBlaze cores on FPGA                          | 87 |

| Figure D-2: Occupation of logic cells on <i>Virtex 5</i> FPGA                     | 87 |

| Figure D-3: Occupation of logic cells on <i>Spartan 3E</i> FPGA                   | 88 |

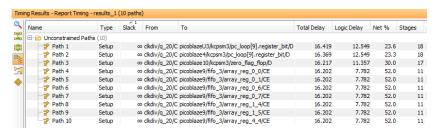

| Figure F-1: delay for <i>Spartan 3E</i> with 14 PicoBlazes (FIFO) setup           | 91 |

| Figure F-2: delay for <i>Virtex 5</i> with 14 PicoBlazes (FIFO) setup             | 91 |

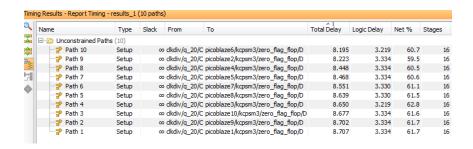

| Figure F-3: delay for <i>Spartan 3E</i> with 4 Picobalzes (shared memory) setup   | 91 |

| Figure F-4: delay for Virtex 5 with 4 PicoBlazes (shared memory) setup            | 91 |

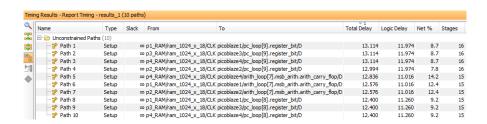

| Figure F-5: Synthesis delay report for <i>Spartan 3E</i> with 14 PicoBlaze setup  | 92 |

| Figure F-6: Synthesis delay report for <i>Virtex 5</i> with 14 PicoBlazes setup   | 92 |

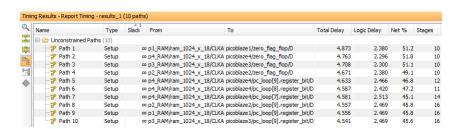

| Figure F-7: Synthesis delay report for <i>Spartan 3E</i> with Shared memory setup | 93 |

| Figure F-8: Synthesis delay report for <i>Virtex 5</i> with 4 Shared memory setup | 93 |

|                                                                                   |    |

#### **List of Tables**

| Table 3.1: Statistics for the 1, 4, and 8 FIFO Wrapper in Spartan 3E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Table 3.2: Statistics for the 1, 4, and 8 FIFO Wrapper in <i>Virtex 5</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26          |

| Table 3.3: Logic cell Statistics of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations of the Spartan 3E and Virtex 5 FPGAs implementations | enting an   |

| array of fourteen PicoBlazes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32          |

| Table 4.1: Logic cell Statistics of the Spartan 3E and Virtex 5 FPGAs implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | enting four |

| PicoBlaze processors and a shared memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 42          |

| Table D-1: Comparison of <i>Spartan 3E</i> and <i>Virtex 5</i> FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 88          |

#### **Abstract**

## A STUDY OF MULTIPROCESSOR SYSTEMS USING THE PICOBLAZE 8-BIT MICROCONTROLLER IMPLEMENTED ON FIELD PROGRAMMABLE GATE ARRAYS

Venkata Chandra Sekhar Mandala Thesis Chair: David H. K. Hoe, Ph.D.

The University of Texas at Tyler

August 2011

As Field Programmable Gate Arrays (FPGAs) are becoming more capable of implementing complex logic circuits, designers are increasingly choosing them over traditional microprocessor-based systems for implementing digital controllers and digital signal processing applications. Indeed, as FPGAs are being built using state-of-the-art deep submicron CMOS processes, the increased amount of logic and memory resources allows such FPGA-based implementations to compete in terms of speed, complexity, and power dissipation with most custom-built chips, but at a fraction of the development costs. The modern FPGA is now capable of implementing multiple instances of configurable processors that are completely specified by a high-level descriptor language. Such arrays of soft processor cores have opened up new design possibilities that include complex embedded systems applications that were previously implemented by custom multiprocessor chips. As the FPGA-based multiprocessor system is completely configurable by the user, it can be optimized for speed and power dissipation to fit a given application.

The goal of this thesis is to investigate design methods for implementing an array of soft processor cores using the Xilinx FPGA-based 8-bit microcontroller known as PicoBlaze. While development tools exist for the larger 32-bit processor from Xilinx known as MicroBlaze, no such resources are currently available for the PicoBlaze microcontroller. PicoBlaze benefits in applications that requires only less data bits (less than 8 bits). For example, consider the gene sequencing or DNA sequencing in which the processing requires only 2 to 5 bits. In such an application, PicoBlaze can be a simple processor to produce the results. Also, the PicoBlaze unit offers a finer level of granularity and hence consumes fewer resources than the larger 32-bit MicroBlaze processor. Hence, the former will find applications in embedded systems requiring a complex design to be partitioned over several processors but where only an 8-bit datapath is required.

The main challenge of this research is evaluating efficient schemes for interprocessor communication suitable for use with an 8-bit microcontroller. Two standard communication schemes were considered: the Mailbox method and Shared memory design. The former was found to be suitable for an array of PicoBlaze units that require nearest neighbor communication. This topology is sufficient for many signal processing applications. Various degrees of interconnect capability were considered for the Mailbox method and a wrapper that enables efficient array design was implemented. A simple Finite Impulse Response (FIR) filter was implemented to verify the design. For the Shared memory design, a round-robin arbiter design was considered, and four PicoBlaze units were connected to a single shared memory over a common bus.

This research provides some guidelines for implementing a multiprocessor system using the PicoBlaze processors. A comparison of logic and memory resource utilization indicates that a wrapper design using four FIFO (First In First Out) buffers provides a good tradeoff between interconnectivity and routing complexity, allowing many common signal processing applications to be implemented. The shared memory approach is more suited for designs where scaling to a large number of processors that need to transfer arbitrary and large blocks of data is required.

#### **Chapter One**

#### Introduction

Field Programmable Gate Arrays (FPGAs) are becoming a viable alternative for digital controllers and Digital Signal Processing (DSP) applications which were previously dominated by microprocessors and dedicated chips. The primary reason for the recent increased popularity of FPGA-based designs is that the modern FPGA chip now has the logic cell and memory resources implemented on advanced processes that allow them to realize many complex designs that can run more efficiently than regular microprocessor-based systems. This efficiency is seen in lower power consumption while maintaining the required clock speed. Also the growth in logic cell resources have allowed soft processor cores to be implemented on an FPGA.

Today, multiple soft processor cores can be implemented on an FPGA due to the increase of logic cells and memory unit resources. The ability to specify the hardware for implementing an array of processors through the use of a high-level descriptor language (HDL) allows a high-degree of flexibility for such FPGA-based designs. In general, Multiprocessor systems-on-a-chip (MPSoC) are being developed to support multiple applications on modern embedded systems. The ability to create an array of soft processor cores on a reconfigurable fabric with the associated advantages of flexibility and optimized run-time efficiency has made the idea of implementing complex embedded systems with FPGAs an attractive design option [1, 2].

#### 1.1 Soft Processor Cores on FPGA

MPSoC designs are required in applications that perform multiple operations (e.g. smart phones, PDAs, set-top boxes). The challenge for design occurs when hardware and software implementations are considered. Due to the increased number of logic cells, speed and performance, FPGAs can implement multiple soft processor cores. MPSoC is beneficial in terms of power consumption, as they can be clocked at lower speeds thereby

reducing the power consumed. Also, a high degree of parallelism can be maintained when using soft processor cores [3].

There have been several VLSI prototypes of arrays of simple processors developed at both the industrial and university level. Each simple processor in an array typically has local memory and specialized interconnections to communicate with neighboring processors. Some design examples include the PicoChip from PicoArray, the RAW processor developed at MIT, and the Am2045 core from Ambric [4, 5, 6]. Also, there has been recent research into an asynchronous array of simple processors (AsAP) chip consisting of processors with an array size of  $6 \times 6$  that is designed to compute DSP tasks efficiently [7]. Soft processor cores like MicroBlaze from Xilinx, Nios from Altera, and the Mitrion Virtual Processor from Mitrionics have been implemented as an array of soft processor cores for various applications [2, 4].

#### 1.2 Research Objectives

This thesis develops a methodology for implementing an array of soft processor cores using a simple 8-bit microcontroller known as PicoBlaze. While Xilinx provides a design flow for implementing an array of MicroBlaze processors (a 32-bit RISC-style processor), no such resources exist for the PicoBlaze processors. The tasks for this thesis include understanding the utilization of resources available on an FPGA and developing an application which involves programming the PicoBlaze processor using assembly language coding and specifying the hardware implementation using a high-level descriptor language. The templates of different topologies from different architectures will be examined and the best architecture for the design of an array of soft processor core will be determined. In summary, a systematic study of an array of soft processor cores using the PicoBlaze 8-bit microcontroller is undertaken. Unlike the Xilinx Microblaze processor, which has the resources for optimizing interprocessor communication, there is a need to build the necessary logic on an FPGA for communicating between arrayed PicoBlaze processors. A wrapper needs to be designed that should be flexible enough to be used for a wide range of signal processing applications.

#### 1.3 Research Method

The research method includes the following. Two Xilinx development boards (*Spartan* 3E and *Virtex* 5 – see Appendix D-4 for a specification of the two FPGAs) are chosen and a PicoBlaze microcontroller is studied and implemented using VHSIC (very high speed integrated) Hardware Description Language (VHDL) on the two FPGAs. Then, different architectures for an array of processors and different communication schemes are studied. A wrapper is designed that is used to produce an array as well used to keep the flow of resources constant for every unit. Then, an array of PicoBlazes is designed and implemented on the development boards. Finally, a simple FIR filter is implemented on the array to verify the functionality of the design. At all stages, the results are observed on the LEDs of the *Spartan* 3E and *Virtex* 5 boards.

#### 1.4 Thesis Outline

The flow of the thesis is as follows: Chapter 2 gives the background information on arrays built from simple processors, functional units, and soft processor cores. Details ofthe PicoBlaze soft processor core are also discussed in this chapter. In Chapter 3, communication between the Picoblaze processor cores is performed using FIFO buffers. Also, this chapter gives details of the wrapper and array of PicoBlaze units. In Chapter 4, the shared memory mode of communication for the PicoBlaze processor using an arbiter is described. Chapter 5 provides some conclusions and gives an overview of future work.

#### **Chapter Two**

#### **Background**

This chapter gives the background information on the need for multicore processors. The first section of the chapter describes the trend towards multicore processors. The second section is a discussion about an array of different processors in different categories. The next section gives the details of the PicoBlaze soft processor. And, the last section talks about the different modes of interprocessor communication for a PicoBlaze microcontroller. Finally, a summary is provided for this whole chapter.

#### 2.1 Trend Towards Multicore Processors

This section deals with the issues encountered with advanced processor design. First, the power wall problem is considered in which different factors and equations are discussed. This provides the basis for understanding the trend towards multicore processors.

#### 2.1.1 Power Wall Problem

Since the invention of the microprocessor in 1971, clock rates for processors have continued to increase until early in the 2000's. This was accomplished by technology scaling, where the decrease in integrated circuit (IC) feature sizes have made making Field effect transistors (FETs) faster and have allowed more transistors to be implemented on a single chip. In 1965, Gordan E. Moore predicted that the numbers of transistors on an IC will double every eighteen months. This has become known as "Moore's Law," and has held true to this point. Figure 2.1 illustrates the increase in clock rate with each succeeding generation of Intel single core processors. What is notable is the peak frequency of 3.6 GHz reached by the Pentium 4 in 2004. Intel had planned to implement a 4 GHz version of its Pentium 4 processor but ended up cancelling its release [8]. The problem is the increasing power dissipation that accompanies each increase in clock rate.

Figure 2.1: Trend in clock rate and power for Intel uniprocessors (single core) [9]

There is a limit to how much power can be dissipated by an integrated circuit due to the maximum rate of heat removal from an air-cooled micro-chip. This problem, known as the "power wall," can be modeled theoretically [10]. For CMOS circuits (currently the most common technology for implementing ICs), the primary source of power dissipation is the dynamic power, the power consumed during switching. The dynamic power dissipation depends on the capacitive loading of the logic gate, the voltage applied, and the frequency of operation:

$$P = C \cdot V_{dd}^2 \cdot f \tag{2.1}$$

where,

P = dynamic power of the circuit,

C =capacitive load of the circuit

$V_{dd}$  = supply voltage

f =frequency (clock rate)

As feature sizes decrease, the trend is to decrease the power supply voltage  $V_{dd}$  (see Figure 2.2). The main reason is to keep the electric field in the transistors to a manageable level. This also helps with minimizing the power dissipation. However, lowering the supply voltage also has a negative impact on circuit speed. This can be seen by the following sets of equations:

$$I_{DS} \propto (V_{dd} - V_T)^n \tag{2.2}$$

$$Delay \propto C \frac{V_{DD}}{I_{DS}} \tag{2.3}$$

where  $I_{DS}$  is the drain-to-source current of a MOSFET and  $V_T$  is its threshold voltage. To improve  $I_{DS}$  as the supply voltage is decreased, the threshold voltage can be decreased. However, lowering  $V_T$  below 0.5 V makes it increasingly difficult to turn the transistor off, especially for deep submicron transistors. Indeed, for circuits implemented on a process in the nanoscale regime, up to 40% of the power dissipation can be due to "leaky" transistors. The following equation summarizes the total power dissipation for a CMOS circuit:

$$P = \alpha \cdot C \cdot V_{dd}^{2} \cdot f + V_{dd} \cdot I_{st} + V_{dd} \cdot I_{leak}$$

(2.4)

where,

$\alpha$  = activity factor

$V_{dd}$ = supply voltage

$I_{st}$  = static current

$I_{leak}$  = leakage current

Power per transistor scales with frequency and also scales with  $V_{dd}$ . Lower  $V_{dd}$  can be compensated with increased pipelining to keep throughput constant. Power per transistor is not equal to power per area. Therefore, power density is a serious issue.

**Figure 2.2:** Plot showing supply voltage  $(V_{dd})$  and thresold voltage  $(V_{th})$  scaling with transistor size  $(L_{eff})$  [11]

There are two solutions to power wall. The first is to introduce high-performance cooling technologies as implemented by IBM on their z/10 and z/11 servers [12]. The second solution is to implement multiple processors per chip. Each processor can run at lower frequencies, but due to parallel processing, the overall performance is increased. These ICs that have multiple processors per chip are called "multicore" processors. Multicore designs have been implemented by Intel and AMD beginning in 2006. The following subsections review the trend towards multicore processor design.

#### 2.2 Multicore Processor

Intel's Many Integrated Core (MIC) design has many cores on a single chip which is used to run platforms at trillions of calculations per second. This architecture is designed to meet lower power dissipation and achieve higher levels of parallelism and is targeted for highly parallel applications [13]. Intel's Tera-scale computing program is researching methods to build processors with hundreds of cores [14].

In addition, Intel Labs is building a microprocessor called Single-chip Cloud Computer (SCC) that contains 48 cores (most Intel architecture cores) on a single silicon chip. Researchers have demonstrated message-passing and shared memory mode of communication using the SCC architecture [15]. The following section describes the arrays of different processors.

#### 2.2.1 Array of Processors

In this subsection, recent research into implementing an array of processors on a single chip is reviewed. An array of processors has simple processors with local memories and interconnect that helps inter-processor communication as shown in Figure 2.3.The Reconfigurable Architecture Workstation (RAW) from MIT has 16 tiles that are arranged in 2D-mesh in which each tile consists of a MIPS style compute processor (i.e., a pipelined RISC processor). Each RAW processor consists of a single-issue 8-stage pipeline, a 32-bit floating point unit, 32KB of instruction and data cache memory in a RAW processor [4].

The picoArray is a high performance communication processor developed by Picochip for wireless signal processing applications. PC102, one of the implementations of picoArray, consists of a heterogeneous array of 322 16-bit Reduced Instruction Set Computer (RISC) processor Array Elements (PAE) and 14 Functional Accelerator Units (FAU). Each processor has separate local instruction and data memories organized in a Harvard Architecture. The array elements in PC102 are arranged in a 2D grid and communicate over a network consisting of 32-bit buses and programmable bus switches. Application development for the picoArray involves specifying interactions between processes in the form of signal flows [4].

AMBRIC, from Ambric Inc. whose basic unit is called a bric. Each bric has two pairs of units, each pair consisting of a compute unit and a memory unit. The compute unit consists of two 32-bit Streaming RISC (SR) processors with 64 words of local memory, two 32-bit streaming RISC processors with DSP extensions, and a 32-bit channel interconnect for inter-processor and inter-compute unit communications. Each RAM unit consists of four banks of 1KB RAM and dynamic channel interconnect to communicate with these memories. The Am2045 core from Ambric consists of 45 brics

arranged in a 5 x 9 array. Since each bric has eight processors, the Am2045 encapsulates a total of 360 processors with 585 KB of on-chip memory [4].

#### Discussion:

In terms of granularity, the basic building block has one or many simple processors. RAW has an individual tile which is designed in a MIPS style processor, while, the picoArray consists of 16-bit RISC processor and Ambric's bric have two 32-bit Streaming RISC (SR) processors and two 32-bit SRD processors. Overall, Ambric gives more computational capacity.

In terms of interconnection network, RAW allows packet-oriented routing, while Ambric has circuit switch interconnect channels and picoArray has programmable switched buses. In all the above processors, communication patterns are found before compilation providing flexibility to the compiler for scheduling fine-grain parallelism. Optimization in terms of power consumption is done by keeping the units in sleep mode or by varying the clock frequency in different units to save energy [4].

**Figure 2.3:** Array of processors where PR is Processor and MEM is memory

#### 2.2.2 Array of Functional Units

An array of functional units architecture lacks an on-chip control processor and there is no central processing unit (see Figure 2.4). In this model, complex algorithms are

partitioned into a sequential flow of configurations to be dynamically configured into the functional units. The dynamic configuration is controlled by the configuration manager, which does not perform any computations by its own. Some examples include the following: Multiple ALU architecture with Reconfigurable Interconnect (MATRIX) from MIT, eXtreme Processing Platform (XPP) from PACT XPP Technologies, and the family of Field-Programmable Object Array (FPOA) from MathStar.

In all these examples, there is a basic unit called the functional unit (FU), consisting of a simplified ALU and a small amount of local memory. Each example has different strategies for configuring and managing the interconnections between functional units. MATRIX supports nearest neighbor connectivity as well as bypass connections. It also has the flexibility for arranging functions depending on the application requirement. The configuration sequencing of the processing array elements in XPP is done by a configuration manager. In FPOA, eight nearest neighbors can communicate with each other [4, 5, 6, 7].

#### Discussion:

In terms of architecture, MATRIX has local memory for each functional unit while XPP and FPOA have memory banks. In terms of interconnection network, MATRIX and FPOA uses nearest neighbor connectivity, while XPP communicates through buses.

**Figure 2.4:** Array of Functional Units (FU)

#### 2.3 Reconfigurable Computing

This section deals with reconfigurable computing, FPGAs and soft processor cores. PicoBlaze, a soft processor core from Xilinx Corporation is discussed. Finally, the interprocessor communication modes and schemes are reviewed.

#### 2.3.1 Advantages of Reconfigurable Computing

Reconfigurable computing has many advantages over Application Specific Integrated Circuits (ASICs) and software-programmed processors. The reasons include: they fill the gap between hardware and software; higher performance than software; and higher level of flexibility than hardware.

Reconfigurable computing allows users to write, download and run the program on a hardware chip. This kind of re-use is achieved by using a special hardware known as Field-Programmable Gate Arrays (FPGAs) which is discussed in the next section (section 2.3.2).

#### **2.3.2 FPGAs**

FPGAs were first introduced in 1986 by the Xilinx Corporation. As denoted by its name, FPGAs can be programmed in the "field" by the user based on the type of the application desired. FPGAs are preferred over application specific integrated circuits (ASICs) for several reasons: they are cost effective for low volume, high capacity and offer more flexibility than programmable logic devices (PLDs). The reason for selecting a FPGA over an ASIC is that complex designs can be implemented at lower engineering costs with FPGAs.

#### 2.3.2.1 Microcontroller within an FPGA

While both dedicated microcontrollers and FPGAs are able to successfully implement practically any digital logic function, the former have a fixed hardware configuration and can become obsolete with changing application requirements. On the other hand, as an FPGA-based microcontroller is described by VHDL code. It's architecture is flexible and can easily be modified by simply updating the code and reconfiguring the device. In addition, any support logic required by the microcontroller

can easily be added within the FPGA by simply adding the pertinent VHDL code [18] [19].

#### 2.3.3 Array of Soft Processors

An array of soft processors, often called soft instruction processors, consists of programmable instruction processors implemented in reconfigurable logic. As the cost and time to market for ASICs has increased, soft processors have found increased deployment in FPGA-based embedded systems. Even though the soft processors cannot meet the area, power and speed characteristics of their corresponding hardware solutions, they can make use of the reconfigurability option in FPGAs to match the complexity and implementation requirements of the application. Major FPGA vendors have provided their own soft processor cores that can be used on their own FPGA platforms. Xilinx FPGAs are widely used in soft multiprocessor implementations. It supplies three main processors: a 32-bit RISC soft processor core known as MicroBlaze, the 8-bit soft microcontroller known as PicoBlaze, and a hard processor core, which is a PowerPC processor. Soft processor cores can also be used as elements in larger processor arrays which gives solutions similar to the class of array of processors presented earlier, but in a more flexible way. A brief overview of the Mitrion platform, which is portable to a number of FPGA computer platforms, is given below.

The Mitrion virtual processor from Mitrionics has a cluster of soft computing nodes placed on the same FPGA. It differs from the conventional soft processor cores in the way it offers parallelism. The Mitrion-C programming language is used to extract parallelism based on data dependencies rather than on the order of execution. The optimizations in hardware are achieved by providing virtualized processor architecture in the form of soft IP cores that are configurable. Figure 2.5 shows an array of different computing nodes which are implemented as soft processor cores [4].

Figure 2.5: Array of Soft Processors (CN stands for Computation Nodes)

#### 2.3.4 PicoBlaze Microcontroller

There are dozens of 8-bit microcontroller architectures and instruction sets. Modern FPGAs can efficiently implement any 8-bit microcontroller, and available FPGA soft processor cores support popular instruction sets such as the PIC, 8051, AVR, 6502, 8080, and Z80 microcontrollers.

The PicoBlaze soft processor core is called the constant (K) coded Programmable State Machine (KCPSM3) also known as Ken Chapman's PSM, after its creator. The PicoBlaze microcontroller is specifically designed and optimized for the *Spartan 3* family. Versions also exist for the *Spartan 6* and *Virtex 6* family of FPGAs. Its compact architecture consumes considerably less FPGA resources than comparable 8-bit microcontroller architectures implemented on an FPGA. Also, the PicoBlaze microcontroller is provided as a free, source-level VHDL file with royalty-free reuse on Xilinx FPGAs [20].

The PicoBlaze microcontroller has many advantages over standalone microcontrollers. Since it is specified in VHDL code [21], the PicoBlaze microcontroller can be easily updated to allow the microcontroller to be retargeted for future generations

of Xilinx FPGAs, enabling future cost reductions and feature enhancements. Furthermore, the PicoBlaze microcontroller is expandable and extendable.

Before the advent of the PicoBlaze and MicroBlaze embedded processors, the microcontroller resided externally to the FPGA, limiting the connectivity to the other FPGA functions and restricting overall interface performance. By contrast, the PicoBlaze microcontroller is fully embedded in the FPGA allowing extensive on-chip connectivity to other FPGA resources. Signals remain within the FPGA, improving overall system performance. The PicoBlaze microcontroller reduces system cost because it offers a single-chip solution that is fully integrated within the FPGA [21].

The PicoBlaze architecture consists of an 8-bit datapath with a 64-byte scratchpad RAM, 16 registers and a 1K word (18 bits wide) Instruction PROM. A block diagram view of the PicoBlaze embedded microcontroller is shown in Figure 2.6 [20].

Figure 2.6: PicoBlaze Microcontroller Block Diagram [20]

The latest version of the PicoBlaze microcontroller is called KCPSM3 which can be downloaded from the Xilinx PicoBlaze lounge. The PicoBlaze design suite of tools consists of "KCPSM3.vhd" (the main VHDL microcontroller code) and an assembler folder containing "KCPSM3.exe", "ROM\_form.vhd", "ROM-form.coe" and "assemblycode.psm". The assembler is used to generate the VHDL code for the Block RAM from the psm code as shown in Figure 2.7.

Figure 2.7: KCPSM3 Assembler Files [20]

The PicoBlaze microcontroller is resource efficient allowing multiple PicoBlaze microcontrollers to be implemented on a single FPGA. Consequently, complex applications can be portioned across several PicoBlaze microcontrollers with each controller implementing a particular function (for example, keyboard and display control, and system management) [19].

#### 2.4 Interprocessor Communication

The key challenge for a multicore processor design is developing efficient means of communication among the cores. In a multiprocessor system, things get difficult when embedded designers encounter interprocessor connections designed to take advantage of a particular processor environment. On FPGA processors, the most common communication schemes are Shared Memory and Mailbox based message passing. Each interprocessor communication has its advantages and disadvantages. System designers must choose the most appropriate method for their application. The mailbox tends to be used to exchange smaller packets of information. It also provides synchronization between processors. The mailbox forms a channel through which messages are queued in a First in First Out (FIFO) mode from one end by the senders, and then dequeued at the other by the receiver [1, 18].

After multiple processors are connected to the interconnect infrastructure, the system designer is concerned with the primary modes of communication and synchronization between the processors. Mailboxes are used to pass messages between

senders and a receivers. Typical usage of a mailbox is to send actual data between processors. There are again two methods of communication in mailbox mode. One is the synchronous method in which the receiver actively keeps polling the mailbox for new data. The other method is an asynchronous method where the mailbox sends an interrupt to the receiver once the data is present in the mailbox. Xilinx provides the XPS Mailbox inter-processor communication core which has a pair of mailbox FIFOs in each mailbox. The recommended connection from Xilinx is to use a single mailbox between a pair of processors. FIFOs are implemented either using distributed Random Access Memory (RAM) or Block RAM (BRAM) resources [19].

Shared memory is the other mode of interprocessor communication between processing subsystems. Any processor can reference any shared memory location directly in a shared memory scheme. Data could be distributed across multiple processors, whose details could be abstracted by some particular software Application Program Interface. Shared memory can be built out of on-chip local memory or external memory. This scheme is more suitable for sharing large blocks of data between processors [19].

The following chapters will discuss in detail the implementation of the Mailbox and Shared Memory schemes suitable for communicating between multiple PicoBlaze microcontrollers implemented on a single Xilinx FPGA.

#### 2.5 Summary

Overall, this chapter provided background information of the problems and issues with various types of processor implementations. Also, this chapter explained PicoBlaze: a soft core processor. The discussion of the chapter ends with the different communication schemes available between processors. Different interprocessor communication mechanisms will be addressed in future chapters.

#### **Chapter Three**

#### **FIFO Style Interprocessor Communication**

Having discussed the need for multicore processors and various soft processor core implementations, the Mailbox scheme for interprocessor communication using the PicoBlaze microcontroller on Xilinx FPGAs is discussed in this chapter. First, the basic FIFO buffer is explained and then the implementation of two processors communicating with a single FIFO buffer is described. Then the wrapper with four FIFO's, one processor and four latches is discussed. Finally, two applications that demonstrate the working of the FIFO buffer and wrapper are described: the counting of numbers and an FIR filter.

#### 3.1 FIFO Style Communication

Mailboxes are used to send and receive data or messages between systems. Messages are queued in a FIFO fashion from the sender and then dequeued by the receiver. The mailbox can be taken as a simplified Transmission Control Protocol/Internal Protocol (TCP/IP)-like message channel between systems or processors. Message reception is addressed synchronously or asynchronously. In the synchronous method, a receiver continuously polls the mailbox for new data, while, in the asynchronous method, the mailbox sends an interrupt to the receiver once the data is present in the mailbox.

#### 3.1.1 FIFO

A FIFO buffer is an "elastic" storage between two subsystems (see Fig. 3.1). It typically has two control signals, *rd* and *wr*, for read and write operations, respectively. When *wr* is high, the input data is written into the buffer, while the *rd* signal is used to read data from the FIFO buffer or flush the data out from the FIFO buffer.

Figure 3.1: Theoretical view of a FIFO Buffer

In many applications the FIFO buffer is a critical component and the optimized implementation can be complex. In the next section, a simple circular-queue-based design is introduced. More efficient, device-specific implementations can be found in the Xilinx literature [22].

A FIFO buffer can be implemented in various ways. A straightforward approach is a circular queue-based implementation. In this method, a control circuit is added to a register file and the registers are arranged in a circular queue with read and write pointers (see Figure 3.2). The write pointer is at the head of the queue and the read pointer is at the tail of the queue. The pointer shifts one position for each operation, read or write.

Figure 3.2: Three Possible Cases of a circular FIFO Buffer

A FIFO buffer has full and empty status signals. A full signal indicates that the FIFO is full and that data cannot be written. An empty signal states that the FIFO is empty and data cannot be read from the FIFO [22].

The pseudo code listing algorithm for reading and writing to FIFO is given in Figure 3.3.

| Write to FIFO            | Read from FIFO            |

|--------------------------|---------------------------|

| • read full_flag;        | • read empty_flag ;       |

| • while full_flag = = 01 | • while empty_flag = = 01 |

| • read full_flag;        | • read empty_flag;        |

| • write data ;           | • read data ;             |

**Figure 3.3:** Pseudo code for FIFO *write* and *read* cases

#### 3.1.2 PicoBlazes with a FIFO Buffer

An initial implementation has two PicoBlazes that are communicated using a single FIFO buffer. The write signal of the FIFO is connected to the write strobe of the PicoBlaze 1 and the read signal of the FIFO is connected to the read strobe of the PicoBlaze 2. Also, the output of the PicoBlaze 1 unit is connected to the data input line of the FIFO buffer and the output of the FIFO buffer is connected to the input signal of the PicoBlaze 2 unit. Figure 3.4 shows the connections between the PicoBlazes and the FIFO.

Figure 3.4: Two PicoBlazes (PB1 and PB2) communicating through a FIFO Buffer

#### 3.1.3 Experimental Verification of the FIFO with Two PicoBlazes

The operation of the FIFO buffer is checked by implementing a small program on two processors. In the first processor, natural numbers are continuously produced and sent to the FIFO buffer and the status of the FIFO buffer is continuously verified. When the FIFO buffer is full, it sends a Full status signal to processor PB1. Then, the processor PB1 pauses at that point and waits until the data is read by processor PB2. The second processor is programmed so that when a button is pressed, it reads 16 bytes of data from the FIFO. Now, the first processor can send 16 more bytes of data into it as some data taken out by processor PB2. This experiment illustrates the working of FIFO as well as verifies the Mailbox method of interprocessor communication. This whole experiment is verified on the Xilinx *Spartan* 3E FPGA development boards. (See Appendix A for the assembly code.)

#### 3.2 Array of PicoBlazes

In this section, various nearest neighbor interconnection schemes are considered for an array of PicoBlazes. A wrapper is designed to allow different topologies. An experiment is performed to validate the wrapper and at last an array of PicoBlazes are produced and validated.

A wrapper is designed in order to allow repeated use of the same structure. The wrapper is coded in VHDL and its entity is called for *n* number of times in the top level file (main file). This facilitates saving time in code development and maintenance. For example, any change in the wrapper description will automatically makes changes in all the units of the array which are instances of this wrapper component.

#### 3.2.1 The Wrapper

Before designing the wrapper there are different topologies to be discussed. Consider the design of the wrapper with one, four and eight FIFOs, as shown in the Figure 3.5. The wrapper with one FIFO buffer can practically be used from one direction only as one wrapper can communicate with one PicoBlaze only. A wrapper with 8 FIFO buffers can communicate with eight neighboring processors. Analyzing data in Table 3.1 taken from *Spartan 3E* and Table 3.2 taken from *Virtex 5*, a wrapper designed with eight FIFO buffers occupies a lot of logic cell resources. The design of a wrapper with four FIFO

buffers provides a good balance between routing complexity and the ability to maintain adequate communication between processors for most signal processing applications. For example, in an FIR filter implementation [23], a topology which allows data to flow in the horizontal, vertical and diagonal directions through different blocks allows the filter to be easily partitioned into an efficient pipelined architecture [24]. Such a scheme will be described in detail at the end of this chapter. Shown below in Figure 3.6 is the screen shot of the wrapper in the schematic editor for three cases (1, 4 and 8 FIFO buffers).

Figure 3.5: Different topologies in designing a Wrapper

**Figure 3.6:** Wrapper design view in schematic editor (1, 4 and 8 FIFOs from left)

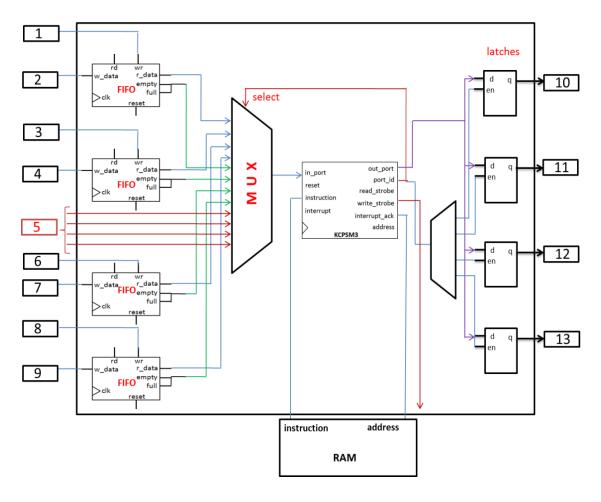

Hence, the design of a wrapper that can communicate with four PicoBlaze units around it is the focus of this work. The designed wrapper has four FIFO buffers for each of the four inputs and four latches for latching the data at the output. Different read and write signals are taken in and out of the wrapper to maintain communication with the other processors. Details of the wrapper are shown in the Figure 3.7.

Figure 3.7: Detailed wrapper with four FIFO buffers and a PicoBlaze Processor

The signals are defined as follows:

- 1, 3, 6, 8 are the write strobes from previous PicoBlaze processor

- 2, 4, 7, 9 are inputs to the current PicoBlaze processor

- 5 is the set of inputs of FIFO status signals from neighboring PicoBlaze processor

- 10, 11, 12, 13 are the outputs

Shown in Figure 3.8 are the input (IN) and output (OUT) ports for wrapper, described in a VHDL entity statement. For example, consider  $ws\_s$ ,  $ws\_e$ ,  $ws\_e$ ,  $ws\_d$  and  $ws\_w$  in the port map which are called as write strobe in south, write strobe in east, write strobe in southeast (called as 'diagonal' in the code) and write strobe in south directions respectively. Consider two PicoBlaze units, PB1 and PB2 where PB1 is writing data in

the south direction to PB2. Here, the PB2 south FIFO is written with PB1 south output and therefore, PB1 write strobe should be sent to PB2 in order to strobe the south FIFO of PB2. Hence, *ws\_s* is important for sending data from one Output of PB1 to input of PB2 south side FIFO. A similar flow occurs for the remaining directions as well.

```

entity PicoBlaze is

port(

-- IN

input_1: in std_logic_vector(7 downto 0);

input_2: in std_logic_vector(7 downto 0);

-- IN

-- IN

input_3: in std_logic_vector(7 downto 0);

input_4: in std_logic_vector(7 downto 0);

-- IN

output 1: out std logic vector(7 downto 0);

-- OUT

output_2: out std_logic_vector(7 downto 0);

-- OUT

output_3: out std_logic_vector(7 downto 0);

-- OUT

-- OUT

output_4: out std_logic_vector(7 downto 0);

-- IN

clk: in std_logic;

address : inout std_logic_vector(9 downto 0);

--INOUT

instruction: inout std_logic_vector(17 downto 0);

--INOUT

status1, status2, status3, status4: out std_logic_vector(7 downto 0);

-- OUT

status1 in, status2 in, status3 in, status4 in: in std logic vector(7 downto 0);

write_strobe_west_in, write_strobe_south_in, write_strobe_diagonal_in,

write_strobe_east_in: in std_logic;

-- IN

ws_s, ws_e, ws_d, ws_w: out std_logic;

-- OUT

-- IN

btn: in std_logic

);

end PicoBlaze;

```

Figure 3.8: Port map for the Wrapper entity in VHDL

Figure 3.9 contains a code snippet showing the selection of lines depending on the port id of the associated PicoBlaze processor. In the PicoBlaze assembly program, data is sent to a particular port and also received from a particular port. For example, if the

data is to be taken from FIFO3, *port\_id* of "0010" in binary notation or "2" in decimal notation should be called.

```

with port_id(3 downto 0) select

in_port <=

fifo_out1 when "0000",

-- data from FIFO1

fifo_out2 when "0001",

-- data from FIFO2

fifo_out3 when "0010",

-- data from FIFO3

-- data from FIFO4

fifo_out4 when "0011",

"000000" & full1 & empty1 when "0100", -- FIF01 empty/full status

"000000" & full2 & empty2 when "0101", -- FIFO2 empty/full status

"000000" & full3 & empty3 when "0110", -- FIFO3 empty/full status

"000000" & full4 & empty4 when "0111", -- FIFO4 empty/full status

status1_in when "1000",

-- status of FIFO1 of neighbor PicoBlaze

status2_in when "1001",

-- status of FIFO2 of neighbor PicoBlaze

status3_in when "1010",

-- status of FIFO3 of neighbor PicoBlaze

status4_in when "1011",

-- status of FIFO4 of neighbor PicoBlaze

"00000000" when others;

```

**Figure 3.9:** Wrapper with port id coded in VHDL

A multiplexer (MUX) is implemented in VHDL code taking port id as the select line. The PicoBlaze assembly level code uses the port ids defined here and thus sends the data to that particular port id.

#### 3.2.2 Need for an Array of PicoBlaze Units

The need for constructing an array comes when Digital Signal Processing (DSP) applications like an Infinite Impulse Response (IIR) filter or Finite Impulse Response (FIR) filter design are considered. An array of processors or subsystems is required for a filter design as the data is needed to be processed in different number of stages.

### 3.2.3 Details of the Array

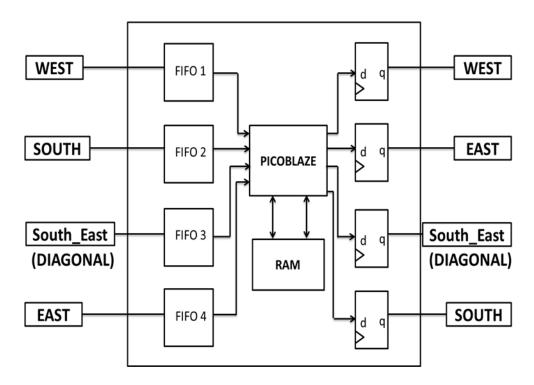

An array of PicoBlazes is arranged by using the wrapper designed with four FIFO buffers. The four FIFO buffers are sufficient to design an FIR filter. Four FIFO buffers (FIFO1, FIFO2, FIFO3 and FIFO4) are considered to take data coming from the four directions WEST, SOUTH, South\_East (DIAGONAL), and EAST, respectively. An array of PicoBlaze units is arranged as shown in Figure 3.10

**Figure 3.10:** A Wrapper that connects to four neighboring Processors

The data coming from the neighboring PicoBlaze in the south direction is connected to the FIFO buffer wired to the SOUTH input port. Similarly, the neighbors in the South\_East (DIAGONAL), WEST and EAST directions send the data into those FIFOs in those directions, respectively.

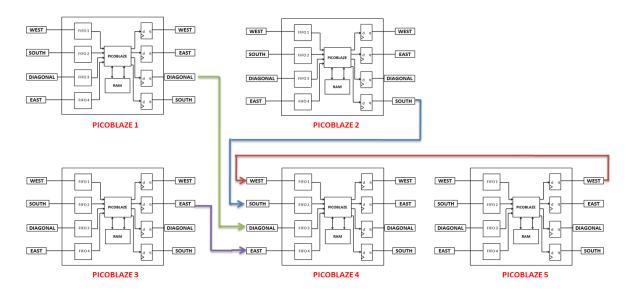

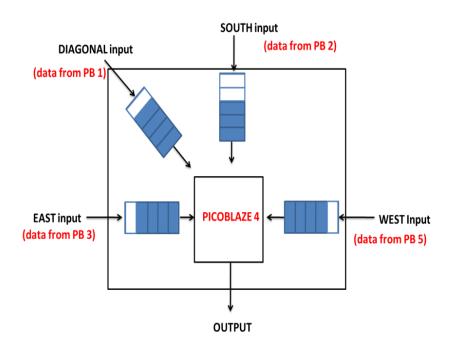

Each PicoBlaze has four inputs and four outputs. Four inputs are named as  $in\_west$ ,  $in\_south$ ,  $in\_diagonal$  and  $in\_east$  and, four outputs are named as  $out\_east$ ,  $out\_west$ ,  $out\_south$  and  $out\_diagonal$ . Connections between PicoBlazes depend on the direction of the data flow (see Figure 3.11 for details).

### 3.2.4 Routing/Logic Cell Resources Comparison

Table 3.1 and 3.2 below gives the statistics for 1-FIFO, 4-FIFOs and 8-FIFOs wrappers implemented on the *Spartan 3E* and *Virtex 5* FPGAs, respectively.

**Table 3.1:** Statistics for the 1, 4, and 8 FIFO Wrapper in *Spartan 3E*

| SPARTAN-<br>3E | Number of Slice<br>LUTS (= Logic +<br>Memory + route-<br>thru)<br>(Used/Available) | Number<br>used for<br>Logic | Number<br>used for<br>Memory | Number used for route-thru (Used/Available) |             | Number of Slices<br>(Used/Available) |

|----------------|------------------------------------------------------------------------------------|-----------------------------|------------------------------|---------------------------------------------|-------------|--------------------------------------|

| 1- FIFO        | 192 / 9,312<br>(2%)                                                                | 102                         | 68                           | 22                                          | 1 / 20 (5%) | 100 / 4,656<br>(2%)                  |

| 4 - FIFO       | 196 / 9,312<br>(2%)                                                                | 106                         | 68                           | 22                                          | 1 / 20 (5%) | 107 / 4,656<br>(2%)                  |

| 8 - FIFO       | 271 / 9,312<br>(3%)                                                                | 181                         | 68                           | 22                                          | 1 / 20 (5%) | 149 / 4,656<br>(3%)                  |

Table 3.2: Statistics for the 1, 4, and 8 FIFO Wrapper in Virtex 5

| VIRTEX -5 | Number of Slice<br>LUTS (= Logic +<br>Memory + route-<br>thru)<br>(Used/Available) | Number   Number   used for   Logic   Memory |    | Number<br>used for<br>route-thru | Number of Block<br>RAM<br>(Used/Available) | Number of Slices<br>(Used/Available) |  |

|-----------|------------------------------------------------------------------------------------|---------------------------------------------|----|----------------------------------|--------------------------------------------|--------------------------------------|--|

| 1-FIFO    | 145 / 69,120<br>(1%)                                                               | 116                                         | 26 | 3                                | 1 / 148 (1%)                               | 89 / 69,120<br>(1%)                  |  |

| 4 - FIFO  | 149 / 69,120<br>(1%)                                                               | 120                                         | 26 | 3                                | 1 / 148 (1%)                               | 98 / 69,120<br>(1%)                  |  |

| 8 - FIFO  | 199 / 69,120<br>(1%)                                                               | 170                                         | 26 | 3                                | 1 / 148 (1%)                               | 138 / 69,120<br>(1%)                 |  |

## 3.3 Experiment with Array of PicoBlazes

For the verification of consistency in the array as well as FIFO buffers inside the wrapper, a sample counting of numbers application is implemented on the Array of PicoBlaze.

#### 3.3.1 Counting Numbers Experiment

The goal of this experiment is to check the FIFO buffer usage and the control that the PicoBlazes have on FIFOs. The data is continuously fed into four FIFOs of one destination PicoBlaze wrapper and only eight bits of data at a time is chosen out of four FIFOs. The FIFOs are fed from four other PicoBlazes. Here, consistency in holding data by FIFO buffers and status signals are verified at different clock speeds.

#### 3.3.2 Status Signals and Read/Write Strobe Conditions Setup