# University of Texas at Tyler Scholar Works at UT Tyler

**Electrical Engineering Theses**

**Electrical Engineering**

Spring 4-27-2012

# Design and Implementation of Fault Tolerant Adders on Field Programmable Gate Arrays

Lakshmi Phani Deepthi Bollepalli

Follow this and additional works at: https://scholarworks.uttyler.edu/ee\_grad

Part of the Electrical and Computer Engineering Commons

#### Recommended Citation

Bollepalli, Lakshmi Phani Deepthi, "Design and Implementation of Fault Tolerant Adders on Field Programmable Gate Arrays" (2012). Electrical Engineering Theses. Paper 17. http://hdl.handle.net/10950/62

This Thesis is brought to you for free and open access by the Electrical Engineering at Scholar Works at UT Tyler. It has been accepted for inclusion in Electrical Engineering Theses by an authorized administrator of Scholar Works at UT Tyler. For more information, please contact tbianchi@uttyler.edu.

# DESIGN AND IMPLEMENTATION OF FAULT TOLERANT ADDERS ON FIELD PROGRAMMABLE GATE ARRAYS

by

Lakshmi Phani Deepthi Bollepalli

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering Department of Electrical Engineering

David H. K. Hoe, Ph.D., Committee Chair

College of Engineering and Computer Science

The University of Texas at Tyler May 2012

#### The University of Texas at Tyler Tyler, Texas

This is to certify that the Master's thesis of

## Lakshmi Phani Deepthi Bollepalli

has been approved for the thesis requirements on March 22<sup>nd</sup>, 2012 for the Master of Science Degree in Electrical Engineering

Approvals:

Thesis Chair: David H. K. Hoe, Ph.D.

Member: Mukul V. Shirvaikar, Ph. D.

Member: Ron N Pieper, Ph.D

Chair and Graduate Coordinator: Makul V. Shirvaikar, Ph. D.

Dr. James K. Nelson, Jr., Ph.D., P.E., Dean, College of Engineering and Computer Science, Brazzel Professor of Engineering

## Acknowledgements

Firstly, I sincerely thank my god for bestowing his divine blessings on me in successfully accomplishing this task. Secondly, my hearty thanks to my family members: my grandfather Purna Chandra Rao Ravi, mom Vijaya Kumari, uncle Rama Krishna Prasad Ravi and my loving sisters Gayathri and Hanumasri for their wholehearted support, love and encouragement for making my dream come true. I would like to express my honest and heartfelt gratitude to my advisor Dr. David Hoe for his encouragement, patience, supervision and constant support from the preliminary stages to the concluding level on me without whom this thesis would not have been possible. Also, I am grateful to my professor Dr. Hoe for encouraging me with the saying, "Give it the extra push." Without his support and encouragement from the very first day of my work, I cannot imagine my successful completion of this thesis. I am very grateful to my friend Chris Martinez for spending his valuable time throughout my research, working on late nights and weekends in the lab by encouraging me in completion of this task in every aspect. Also I would like to thank my seniors Venkata Chandra Sekhar Mandala and Rahul Jesuran and for making me active and supporting me throughout my Master's.

I would like to thank my committee members, Dr. Ron J. Piper and Dr. Mukul V. Shirvaikar for taking time and for reviewing my work. I still remember the precious words by Dr. Shirvaikar on the way home regarding my research with Dr. David Hoe which gave a million tons of encouragement and will power for a successful start. I would like to express my profound gratitude to him for his constant support and guidance throughout my Master's program. Finally I would like to thank the entire EE department and the University of Texas at Tyler for supporting me throughout my Master's. Finally, I would like to thank all those who supported me in any respect during the completion of the thesis.

# **Table of Contents**

| Chapter One                                             | 1  |

|---------------------------------------------------------|----|

| Introduction                                            | 1  |

| 1.1 Importance of Fault Tolerance in FPGAs              | 2  |

| 1.2 Review of the Relevant Literature:                  | 2  |

| 1.3 Research Objectives                                 | 3  |

| 1.4 Research Method                                     | 3  |

| 1.5 Thesis Outline                                      | 4  |

| Chapter Two                                             | 5  |

| Fault Tolerance on FPGAs.                               | 5  |

| 2.1 Introduction                                        | 5  |

| 2.2 Basic Adder Designs                                 | 5  |

| 2.2.1 Full Adder                                        | 5  |

| 2.3 Ripple Carry Adder                                  | 7  |

| 2.4 Kogge-Stone Adder                                   | 7  |

| 2.4.1 8-bit Kogge-Stone Adder                           | 8  |

| 2.5 Sparse Kogge-Stone Adder                            | 13 |

| 2.6. Basic Fault Tolerance - Hardware Redundancy        | 14 |

| 2.7 Advanced Fault Tolerant Methods                     | 15 |

| 2.7.1 Structural Design – Hybrid Approach               | 15 |

| 2.7.2 Roving                                            | 17 |

| 2.7.3 Graceful Degradation                              | 19 |

| Summary                                                 | 21 |

| Chapter 3                                               | 22 |

| Basic Fault Tolerant Implementation.                    | 22 |

| 3.1 Introduction                                        | 22 |

| 3.2 FPGA Implementation Method                          | 22 |

| 3.3 Triple Modular Redundancy-RCA                       | 22 |

| 3.4 Regular Kogge-Stone Adder Fault Correction Approach | 24 |

| 3.5 Lower Half Fault Tolerant Sparse Kogge-Stone Adder  | 25 |

| 3.5.1 Simulations of the S   | Sparse Kogge-Stone Adder                        | 27     |

|------------------------------|-------------------------------------------------|--------|

| Summary                      |                                                 | 28     |

| Chapter 4                    |                                                 | 29     |

| Advanced Fault Tolerance Con | ncepts                                          | 29     |

| 4.1 Introduction             |                                                 | 29     |

| 4.2 Upper Half Fault Tole    | erant Sparse Kogge-Stone Adder                  | 29     |

| 4.2.1 Simulation Results     |                                                 | 33     |

| 4.3 Graceful Degradation     |                                                 | 35     |

| 4.3.1 Implementation         |                                                 | 35     |

| 4.3.2 Simulation Results     |                                                 | 36     |

| 4.4 Synthesis Results        |                                                 | 38     |

| 4.5 Hardware Implementa      | ation                                           | 41     |

| Summary                      |                                                 | 44     |

| Chapter Five                 |                                                 | 46     |

| Conclusions and Future Work  |                                                 | 46     |

| 5.1 Conclusions              |                                                 | 46     |

| 5.2 Future Work              |                                                 | 46     |

| References                   |                                                 | 48     |

| Appendices                   |                                                 | 50     |

| Appendix: A                  |                                                 | 51     |

| A1. VHDL Code for 32-b       | oit TMR-RCA                                     | 51     |

| A2. VHDL Code for adde       | er1 in 32-bit TMR-RCA                           | 52     |

| A3. VHDL Code for adde       | er2 in 32-bit TMR-RCA                           | 53     |

| A4. VHDL Code for adde       | er3 in 32-bit TMR-RCA                           | 54     |

| A5. VHDL Code for com        | parator in 32-bit TMR-RCA                       | 54     |

| Appendix: B                  |                                                 | 56     |

| B1. VHDL Code for 8-bit      | t Kogge-Stone Fault Correcting Adder            | 56     |

| B2. VHDL Code for mux        | in 8-bit Kogge-Stone Fault Correcting Adder     | 62     |

| B3. VHDL Code for GPb        | lock in 8-bit Kogge-Stone Fault Correcting Add  | ler 62 |

| B4. VHDL Code for black      | kcell in 8-bit Kogge-Stone Fault Correcting Add | ler 63 |

| B5. VHDL Code for grav       | cell in 8-bit Kogge-Stone Fault Correcting Adde | er 63  |

| B6. VHDL Code for faultgraycell in 8-bit Kogge-Stone Fault Correcting Adder 64 |

|--------------------------------------------------------------------------------|

| B7. VHDL Code for buffer1 in 8-bit Kogge-Stone Fault Correcting Adder 64       |

| B8. VHDL Code for outmux in 8-bit Kogge-Stone Fault Correcting Adder 65        |

| B9. VHDL Code for sum in 8-bit Kogge-Stone Fault Correcting Adder              |

| B10. VHDL Code for CntlMuxs in 8-bit Kogge-Stone Fault Correcting Adder 66     |

| Appendix: C68                                                                  |

| C1. VHDL Code for 32-bit Kogge-Stone Adder (Lower half)                        |

| C2. VHDL Code for ConcatenationRCA in 32-bit Kogge-Stone Adder (Lower half)    |

| 77                                                                             |

| C3. VHDL Code for FaultyAdder1 in 32-bit Kogge-Stone Adder (Lower half) 78     |

| C4. VHDL Code for comparator1 in 32-bit Kogge-Stone Adder (Lower half) 78      |

| C5. VHDL Code for bitcounter1 in 32-bit Kogge-Stone Adder (Lower half) 80      |

| Appendix: D8                                                                   |

| D1. VHDL Code for 32-bit Kogge-Stone Adder (Upper half)                        |

| D2. VHDL Code for greengroup in 32-bit Kogge-Stone Adder (Upper half) 85       |

| D3. VHDL Code for purplegroup in 32-bit Kogge-Stone Adder (Upper half) 87      |

| D4. VHDL Code for bluegroup in 32-bit Kogge-Stone Adder (Upper half) 89        |

| D5. VHDL Code for ConcatenationRCA in 32-bit Kogge-Stone Adder (Upper half)    |

| D6. VHDL Code for faultgraycell in 32-bit Kogge-Stone Adder (Upper half) 92    |

| D7. VHDL Code for faultblackcell in 32-bit Kogge-Stone Adder (Upper half) 92   |

| Appendix: E94                                                                  |

| E1. VHDL Code for 32-bit Graceful Degradation94                                |

| E2. VHDL Code for comparator2 in 32-bit Graceful Degradation 104               |

| Appendix: F                                                                    |

| F1. VHDL code for 32-bit TMR-RCA Implemented on Hardware                       |

| F2. VHDL code for 32-bit Sparse Kogge-Stone Lower Half Implemented on Hardware |

| F3. VHDL code for 32-bit Graceful Degradation Implemented on Hardware 110      |

| Appendix G113                                                                  |

| G.1 Other Fault Combinations for Upper Half Fault Tolerant Sparse Kogge-Stone  |

| Adder113                                                                       |

| Appendix H                                                | 115 |

|-----------------------------------------------------------|-----|

| H1 Spartan-3E                                             | 115 |

| H2 Virtex-5                                               | 116 |

| Appendix I                                                | 118 |

| I1. Delay Calculation of TMR_RCA on Logic Analyzer        | 118 |

| I2. Observing Worst Case Transition for Kogge Stone Adder | 124 |

| Appendix J                                                | 133 |

# **List of Figures**

| Figure 2.1 Block diagram of a full adder                                                          | 6   |

|---------------------------------------------------------------------------------------------------|-----|

| Figure 2.2 4-bit ripple carry adder                                                               | 7   |

| Figure 2.3 Generate-Propagate block                                                               | 9   |

| Figure 2.4(a) Black cell                                                                          | 9   |

| Figure 2.4(a) Gray cell                                                                           | 9   |

| Figure 2.5 Buffer                                                                                 | 10  |

| Figure 2.6 8-bit Kogge-Stone adder                                                                | 11  |

| Figure 2.7 16-bit Kogge-Stone adder                                                               | 12  |

| Figure 2.8 Sparse Kogge-Stone adder                                                               | 13  |

| Figure 2.9 General Triple Modular Redundancy                                                      | 14  |

| Figure 2.10 TMR adder circuit using ripple carry                                                  | 15  |

| Figure 2.11 8-bit Kogge-Stone carry tree illustrating the mutually exclusive even and carry trees |     |

| Figure 2.12 Timing diagram for three adders in execution unit (Tc is the clock period)            | )17 |

| Figure 2.13 Block diagram for the proposed 8-bit fault tolerant Kogge-Stone adder                 | 18  |

| Figure 2.14 Roving area under test across the chip                                                | 18  |

| Figure 2.15 General block diagram of graceful degradation                                         | 19  |

| Figure 2.16 General view of the graceful degradation process                                      | 20  |

| Figure 3.1 General design flow.                                                                   | 23  |

| Figure 3.2 Simulation results for the 64-bit TMR-RCA                                              | 24  |

| Figure 3.3 Simulation results for the 64-bit error correcting Kogge-Stone adder                   | 25  |

| Figure 3.4 Block diagram of fault tolerant sparse Kogge-Stone adder                               | 26  |

| Figure 3.5 Timing diagram for the lower half fault tolerant Kogge-Stone                           | 27  |

| Figure 3.6 Simulation results for the 64-bit lower half FT sparse Kogge-Stone adder               | 28  |

| Figure 4.1 Upper half detection scheme for 16-bit sparse Kogge-Stone adder           | 30  |

|--------------------------------------------------------------------------------------|-----|

| Figure 4.2 Upper half detection truth table                                          | 30  |

| Figure 4.3 Upper half detection scheme with fault free carry comparisions            | 31  |

| Figure 4.4 Truth table for upper half error detection with fault free comparisions   | 32  |

| Figure 4.5 Upper half detection scheme for a 32-bit sparse Kogge-Stone adder         | 33  |

| Figure 4.6 (a) Normal adder operation of the sparse Kogge-Stone upper half           | 34  |

| Figure 4.6 (b) Fault tolerant adder operation of the sparse Kogge-Stone upper half   | 34  |

| Figure 4.7 Block diagram of graceful degradation approach on sparse Kogge-Stone a    |     |

| Figure 4.8 (a) Normal adder operation of the graceful degradation adder              | 37  |

| Figure 4.8 (b) Fault tolerant adder operation of the graceful degradation adder      | 37  |

| Figure 4.9 Estimation of resources used from FPGA synthesis                          | 38  |

| Figure 4.10 Corresponding delays for the sparse KS on Sparatn 3E FPGA                | 39  |

| Figure 4.11 Delay of FT adders on Spartan 3E FPGA                                    | 40  |

| Figure 4.12 Delay of FT adders on Virtex 5 FPGA                                      | 41  |

| Figure 4.13 Measured delay for the 64-bit TMR-RCA                                    | 42  |

| Figure 4.14: Implemented procedure for simulating the worst-case delay on the sparse | e   |

| Kogge-Stone lower half approach                                                      | 43  |

| Figure 4.15 Measured delay for the 64-bit sparse Kogge-Stone Adder                   | 43  |

| Figure 4.16 Measured delay for the 64-bit graceful degradation adder                 | 44  |

| Figure 4.17 Summary of adder delays on Spartan 3E                                    | 45  |

| Figure G: Fault tolerant adder operation for multiple fault combinations             | 114 |

| Figure H-1: Spartan-3E FPGA                                                          | 115 |

| Figure H-2: Virtex-5 FPGA                                                            | 116 |

| Figure I-1: Adder delay including ROM and multiplexer                                | 118 |

| Figure I-2: Logic cell of Spartan 3E                                                 | 120 |

| Figure I-3 Adder delay excluding ROM and multiplexer | 123 |

|------------------------------------------------------|-----|

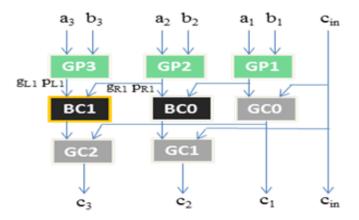

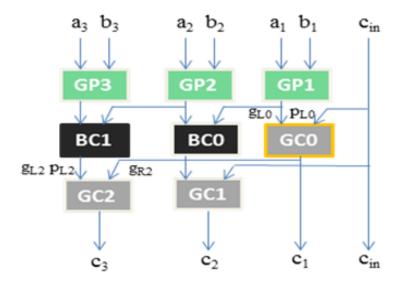

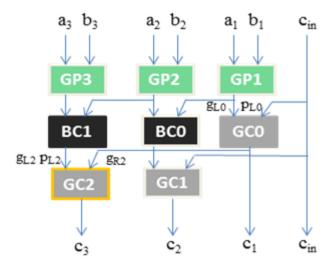

| Figure I-4: Kogge-Stone adder with selected BC1      | 126 |

| Figure I-5: Kogge-Stone adder with selected GC0      | 127 |

| Figure I.6: Kogge-Stone adder with selected GC2      | 128 |

# **List of Tables**

| Table 2.1: Truth table of full adder                                            | 6   |

|---------------------------------------------------------------------------------|-----|

| Table 2.6: Kogge-Stone adders of different bit-widths                           | 11  |

| Table I-1: Input pattern chosen for testing TMR-RCA                             | 119 |

| Table I-2: Worst case carry and sum delays                                      | 121 |

| Table I-3: Worst case input delays                                              | 123 |

| Table I-4: Subset of (g, p) relations used for testing                          | 125 |

| Table I-5: Black cell 1 outputs for high inputs                                 | 126 |

| Table I-6: Gray cell 0 outputs for high inputs                                  | 127 |

| Table I-7: Gray cell 2 outputs for high inputs                                  | 128 |

| Table I-8: Black cell 1 outputs for one low input                               | 129 |

| Table I-9: Gray cell 0 outputs for one low input                                | 130 |

| Table I-10: Gray cell 2 outputs for one low input                               | 131 |

| Table J-1: Delay summary for lower half fault tolerant sparse Kogge-Stone adder | 133 |

#### **Abstract**

# DESIGN AND IMPLEMENTATION OF FAULT TOLERANT ADDERS ON FIELD PROGRAMMABLE GATE ARRAYS

Lakshmi Phani Deepthi Bollepalli

Thesis chair: David H. K. Hoe, Ph.D.

The University of Texas at Tyler

May 2012

Fault tolerant systems play a very prominent role in many digital systems especially for those implemented with nanoscale technologies because of their susceptibility to electromagnetic interference and transient errors due to cosmic rays. Arithmetic logic circuits play a vital role in all digital signal processing systems and also in microprocessors. Keeping this in mind, this research is concerned with achieving fault tolerance on various adder architectures on Field Programmable Gate Arrays (FPGAs).

The research method involves implementing error detection and correction techniques for the sparse Kogge-Stone adder and comparing it with Triple Modular Redundancy (TMR) techniques. Fault tolerance is implemented on a Kogge-Stone adder by taking the advantage of inherent redundancy in the carry tree. On a sparse Kogge-Stone adder, fault tolerance is implemented by introducing additional ripple carry adders into the design. Implementing this fault tolerance approach on the sparse Kogge-Stone adder is successfully completed and verified by introducing faults either on the ripple carry adder or in the carry tree. The adder designs are specified using a high-level descriptor language called "Very High Speed Integrated Circuit Hardware Description Language" (VHDL) and implemented on an FPGA. Two types of Xilinx FPGAs were

used in this study: the Spartan 3E and Virtex 5. The fault tolerant adders were analyzed in terms of their delay and resource utilization as a function of their bit-widths.

The results of this research provide important design guidelines for the implementation of fault tolerant adders on FPGAs. The Triple Modular Redundancy-Ripple Carry Adder (TMR-RCA) is the most efficient approach for fault tolerant design on an FPGA in terms of its resources, due to its simplicity and the ability to take advantage of the fast-carry chain. However, for very large bit widths, there are indications that the sparse Kogge-Stone adder offers superior performance over an RCA when implemented on an FPGA. Two fault tolerant approaches were implemented using a sparse Kogge-Stone architecture. First, a fault tolerant sparse Kogge-Stone adder is designed by taking advantage of the existing ripple carry adders in the architecture and adopting a similar approach to the TMR-RCA by inserting two additional ripple carry adders into the design. Second, a graceful degradation approach is implemented with the sparse Kogge-Stone adder. In this approach, a faulty block is permanently replaced with a spare block. As the spare block is initially used for fault checking, the fault tolerant capability of the circuit is degraded in order to continue fault-free operation. The adder delay is smaller for graceful degradation by approximately 1 ns from measured results and 2 ns from the synthesis results independent of the bit widths when compared with the fault tolerant Kogge-Stone adder. However, the resource utilization is similar for both adders.

#### **Chapter One**

#### Introduction

Fault tolerance plays a very important role in modern systems where immediate human intervention is not possible and system failure can have disastrous consequences. A fault tolerant system has the ability to detect and then correct the occurrence of a hardware failure. In order to detect the fault, the system must be able to sense any deviations from its normal operation. A fully fault tolerant system also has the ability to correct the fault in order to return the system to its normal functionality. An optimal design will minimize the amount of extra logic required to detect and then correct the occurrence of the fault. An extreme temperature change is one of the reasons in which fault tolerance is necessary for devices operating in harsh operating environments, as found, for example, in space and military applications. Fault tolerance will also be necessary in nanoelectronic systems, as small device dimensions make the system more susceptible to outside interference, such as cosmic radiation.

This thesis will study methods to implement fault tolerant arithmetic circuits on Field Programmable Gate Arrays (FPGAs). FPGAs are integrated circuits (ICs) that can be configured to implement a specific function after the chip has been manufactured. The first FPGAs were put on the market by Xilinx Corporation in 1985 and by the late 1990's FPGAs were becoming more popular than Application Specific Integrated Circuits (ASICs). The advantages of using FPGAs are their reprogrammable nature, ease of prototyping, rapid time to market, and minimal non-recurring engineering (NRE) cost compared to custom IC designs. Most modern electronic systems contain some high performance digital chips known as Digital Signal Processors (DSPs). DSP designs are commonly used in electronic systems such as avionics, communication systems and also in portable electronics. DSP chips transform and manipulate digitally encoded signals according to some specified system design goal. Various algorithms such as the Fast Fourier Transforms are used to analyze the signals which are in digital form. The main components of a DSP chip are the adder and multiplier along with memory elements. The

performance of the system is based on the speed at which arithmetic operations are performed. Hence the adder plays a vital role in DSPs for carrying out all the required arithmetic operations.

#### 1.1 Importance of Fault Tolerance in FPGAs

A large portion of an FPGA chip consists of its configuration memory. The logic stored in the memory of the system can be altered by Single-Event Upsets (SEUs). SEUs can occur due to cosmic radiation or a high energy neutron striking the substrate of the device silicon. As SEUs can cause single-bit errors within the configuration memory, a fault tolerant system that uses FPGAs must guard against these occurrences. Fault tolerant systems are also important for circuits implemented on nanoscale technologies as external influences such as electromagnetic interference and cosmic rays can cause transient errors which in turn affect the operation of the devices and can degrade the system reliability. State-of-the-art FPGAs are designed with very fine geometrics making them susceptible to faults due to such electrical interference. For example, Xilinx's Virtex-6 FPGA uses 40 nm technology and the Virtex-7 uses 28 nm technology. The silicon processing technology is at the 22 nm mode at the time this thesis was written. Degradation mechanisms of the devices become more severe with the shrinking of the process geometry. For example, hot-carrier effects due to the increasing electric field strength in the transistor's channel causes a gradual degradation in the device performance through threshold voltage shifts.

#### 1.2 Review of the Relevant Literature:

Previous studies have investigated fault tolerant methods implemented on FPGAs [1]. The basic fault tolerant approach is Triple Modular Redundancy (TMR) which is used as a point of reference to compare with advanced fault approach considered in this thesis [2]. TMR is a common solution for hardening digital logic against SEUs and is widely adopted in ASIC designs [3]. Hardware is essentially replicated in triplicate with a voter circuit used to pass the majority rule signals to the output.

Roving fault detection and graceful degradation are some of the fault tolerant approaches used for ensuring reliable FPGA designs [4]. Roving fault detection performs a progressive scan of an FPGA structure by swapping blocks with the same functionality

with a block carrying out the test function. Graceful degradation is an approach in which the faulty block is replaced with a spare block. A fault correction approach for a parallel prefix, *N* bit Kogge-Stone adder, which consists of two independent *N*/2 bit Han-Carlson (HC) adders, is implemented [5]. In addition, fault tolerance can be implemented by using self-testing areas (STARs) on an FPGA, which allows fault checking to occur without disturbing the normal system operation [6].

#### 1.3 Research Objectives

As the adder plays a vital role in digital signal processing systems and microprocessors, the main objective of this research is to design and implement fault tolerant adders on FPGAs. Existing fault tolerant approaches will be applied to adders of varying bit widths for implementation on FPGAs.

#### 1.4 Research Method

To meet the research objectives three adder topologies, namely the ripple carry adder, Kogge-Stone adder, and the sparse Kogge-Stone adder are studied. The ripple carry adder in a TMR configuration is used as the reference design. The Kogge-Stone adder, which is classified as a parallel prefix adder, has a critical path on the order of  $log_2N$  (where N is the width of the adder in bits). The regularity of its structure makes it suitable for VLSI designs as well as FPGA implementations. This research is performed in two parts. First is to evaluate the previous work of K. Roy's group on fault tolerant adders meant for VLSI design [5] and by implementing this approach on FPGAs. Second is to investigate and design fully fault tolerant Kogge-Stone adders on FPGAs. The fault tolerant adders which are coded in VHDL are synthesized and implemented on the FPGAs. The functionality of the designed fault tolerant adders are studied and then compared with the base reference TMR adder in terms of delay and usage of resources as a function of their bit-widths. An optimal fault tolerant design adds little overhead to the system. The method of study for this research involves designing carry tree adders of varying widths up to 256 bits. The designs are synthesized by coding with VHDL using Xilinx's ISE 12.4 software. The performance metrics of timing delay and operational cost are observed from the synthesis reports. The functionality of the designed adders are

verified and simulating with ISIM. The critical delays of the designed adders are measured using a high-speed logic analyzer.

#### 1.5 Thesis Outline

An outline of the thesis is as follows. Chapter Two describes the background work on fault tolerance in FPGAs. Chapter Three discusses the results of simulations of the basic fault tolerance adders using ISIM. Chapter Four introduces advanced fault tolerant concepts and then analyzes the performance metrics like timing (speed-adder delay) and the functionality based on the results obtained from the logic analyzer. Finally Chapter Five provides the conclusions and describes potential future work in this area.

## **Chapter Two**

#### **Fault Tolerance on FPGAs**

#### 2.1 Introduction

An adder plays a vital role in many digital circuit designs including Digital Signal Processors (DSPs) and microprocessors. The fault tolerant techniques for high speed adder designs are considered in this chapter. Triple Modular Redundancy (TMR), which is a common fault tolerance approach, is used as the base reference design. Advanced concepts for fault tolerant adders on FPGAs include roving, and graceful degradation. This chapter describes the design of the ripple carry adder, parallel prefix adders and then the fault tolerant concepts that can be applied to these designs.

#### 2.2 Basic Adder Designs

This section describes the basic adders used in this thesis. The adders implemented on FPGAs are the ripple carry adder, Kogge-Stone adder, and sparse Kogge-Stone adders. The ripple carry adder is one of the simplest adder designs. The Kogge-Stone adder is an example of a parallel prefix adder. The internal blocks used in the adder designs are described in detail in this section.

#### 2.2.1 Full Adder

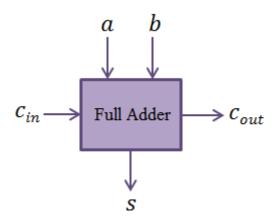

A full adder is a circuit which adds three one bit binary numbers and outputs two one bit binary numbers. The block diagram is shown in Figure 2.1. Here, a and b are the two adder inputs and  $c_{in}$  is the carry input. The two outputs produced are the sum s and carry  $c_{out}$ . Table 2.1 depicts the truth table of the full adder. The following are the Boolean expressions for the full adder.

$$s = a \oplus b \oplus c_{in}$$

$$c_{out} = a \cdot b + b \cdot c_{in} + a \cdot c_{in} = a \cdot b + (a \oplus b) \cdot c_{in}$$

$$(2.1)$$

Figure 2.1: Block diagram of a full adder

For prefix adders, it is convenient to define the intermediate signals generate, propagate, and delete given by g, p, and d, respectively,

$$g = a \cdot b$$

$$p = a \oplus b$$

$$d = \overline{ab}$$

(2.2)

The sum and carry out are then given by,

$$s = p \oplus c_{in}$$

$$c_{out} = g + p \cdot c_{in}$$

(2.3)

Table 2.1. Truth table of a full adder

| a | b | $c_{in}$ | S | $c_{out}$ | Carry Status |

|---|---|----------|---|-----------|--------------|

| 0 | 0 | 0        | 0 | 0         | delete       |

| 0 | 0 | 1        | 1 | 0         | delete       |

| 0 | 1 | 0        | 1 | 0         | propagate    |

| 0 | 1 | 1        | 0 | 1         | propagate    |

| 1 | 0 | 0        | 1 | 0         | propagate    |

| 1 | 0 | 1        | 0 | 1         | propagate    |

| 1 | 1 | 0        | 0 | 1         | generate     |

| 1 | 1 | 1        | 1 | 1         | generate     |

#### 2.3 Ripple Carry Adder

The ripple carry adder is one of the simplest adders. It consists of a cascaded series of full adders. For example, a 4-bit adder can be constructed by cascading four full adders together as shown in Figure 2.2. The ripple carry adder is relatively slow as each full adder must wait for the carry bit to be calculated from the previous full adder.

The worst case delay of a ripple carry adder occurs when  $c_{in}$  propagates from the first stage to the most significant bit position. The delay for an N-bit adder is given by,

$$t_{adder} = (N-1)t_{carry} + t_{sum} (2.4)$$

where,  $t_{carry}$  is the carry propagation delay for one stage and  $t_{sum}$  is the time required to compute the sum bit for one stage. Hence, the delay of the ripple carry adder is of order N.

**Figure 2.2:** 4-bit ripple carry adder

#### 2.4 Kogge-Stone Adder

The Kogge-Stone adder is classified as a parallel prefix adder since the generate and the propagate signals are precomputed. In a tree-based adder, carries are generated in tree and fast computation is obtained at the expense of increased area and power. The main advantage of this design is that the carry tree reduces the logic depth of the adder by essentially generating the carries in parallel. The parallel-prefix adder becomes more favorable in terms of speed due to the  $O(log_2n)$  delay through the carry path compared to O(n) for the RCA. The Kogge-Stone adder is widely used in high-performance 32-bit,

64-bit, and 128-bit adders as it reduces the critical path to a great extent compared to the ripple carry adder.

The operation of the tree-based adder can be understood using the concept of the fundamental carry operation (*fco*). This operator works on the generate and propagate pairs as defined by,

$$(g_L, p_L) \circ (g_R, p_R) = (g_L + p_L \cdot g_R, p_L \cdot p_R)$$

(2.5)

where  $g_L$ ,  $p_L$  are the left input generate and propagate pairs and  $g_R$ ,  $p_R$  are the right input generate and propagate pairs to the cell. For example, in a 4-bit carry lookahead adder, the carry combination equation can be expressed as,

$$c_{4} = (g_{4}, p_{4}) \circ [(g_{3}, p_{3}) \circ [(g_{2}, p_{2}) \circ (g_{1}, p_{1})]]$$

$$= (g_{4}, p_{4}) \circ [(g_{3}, p_{3}) \circ [(g_{2} + p_{2} \cdot g_{1}, p_{2} \cdot p_{1})]]$$

$$\vdots$$

$$= g_{4} + p_{4} \cdot g_{3} + p_{4} \cdot p_{3} \cdot g_{2} + p_{4} \cdot p_{3} \cdot p_{2} \cdot g_{1}$$

$$(2.6)$$

Since the *fco* obeys the associativity property, the expression can be reordered to yield parallel computations in a tree based structure [7],

$$c_4 = [(g_4, p_4) \circ (g_3, p_3)] \circ [(g_2, p_2) \circ (g_1, p_1)]$$

(2.7)

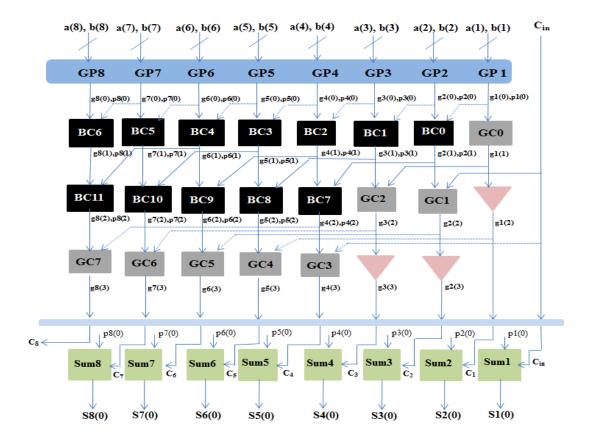

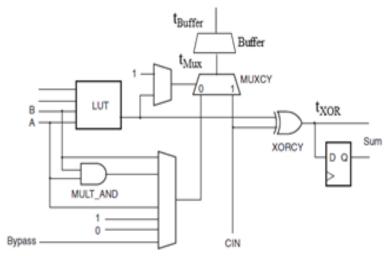

#### 2.4.1 8-bit Kogge-Stone Adder

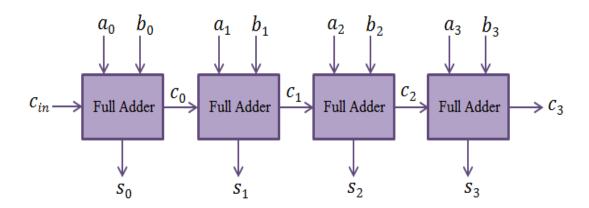

The 8-bit Kogge stone adder will be explained in detail in this subsection. An 8-bit Kogge-Stone adder is built from eight generate and propagate (GP) blocks, eight black cells (BC) blocks, eight gray cell (GC) blocks, and nine sum blocks as shown in the Figure 2.3. The details of the various blocks used in the structure of Kogge-Stone adder are discussed below.

#### 1) GP block

The generate and propagate block takes a pair of operand bits (a, b) as inputs and computes a pair of generate and propagate signals (g, p) as output, as depicted in Figure 2.3. The output from the GP block is given by the equation (2.2).

Figure 2.3: Generate-Propagate block

#### 2) BC block

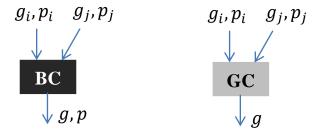

The black cell takes two pairs of generate and propagate signals  $(g_i, p_i)$  and  $(g_j, p_j)$  as input and computes a pair of generate and propagate signals (g, p) as output. It is shown in the Figure 2.4(a).

Figure 2.4 (a): Black cell Figure 2.4 (b): Gray cell

The expressions for the output signals g, p generated by the black cell are given by

$$g = g_i + p_i \cdot g_j$$

$$p = p_i \cdot p_j$$

(2.8)

#### 3) GC block:

The gray cell takes two pairs of generate and propagate signals  $(g_i, p_i)$  and  $(g_j, p_j)$  as inputs and computes a generate signal g as output which is shown in Figure 2.4(b).

The expressions for the output signal g obtained by the gray cell is given a

$$g = g_i + p_i \cdot g_i \tag{2.9}$$

#### 4) Buffer

The buffer takes a pair of the generate and propagate signals  $(p_i, g_i)$  as input and passes the same signals to the output. It is shown in Figure 2.5.

Figure 2.5: Buffer

The expressions for the output signals g, p obtained by the buffer block are given as

$$g = g_i (2.10)$$

$$p = p_i$$

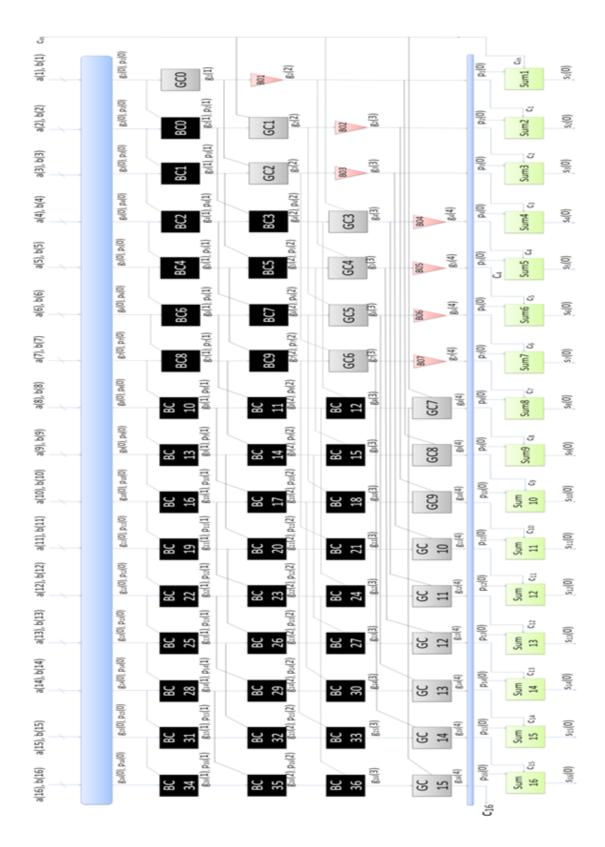

The complete schematic for the 8-bit Kogge-Stone adder is shown in Figure 2.6. An 8-bit Kogge-Stone adder is built from eight generate and propagate (GP) blocks, twelve black cell (BC) blocks, eight gray cell (GC) blocks, and eight sum blocks. To be aesthetic, an extra column has been added in our design to show the computation of  $c_8$ . In practice,  $c_8$  is generated by just adding an extra gray cell in the last column.

Figure 2.6: 8-bit Kogge-Stone adder

### **Higher Order Kogge-Stone Adders**

Table 2.6. summarizes the various types of cells required for the Kogge-Stone adders with larger bit widths.

**Table 2.6.** Kogge-Stone adders of different bit widths

| Bit Width of Kogge- | No. of GP | No. of      | No. of Gray | No. of Sum |

|---------------------|-----------|-------------|-------------|------------|

| Stone Adder         | Blocks    | Black Cells | Cells       | blocks     |

| 16-bit              | 16        | 37          | 16          | 16         |

| 64-bit              | 64        | 257         | 64          | 64         |

| 128-bit             | 128       | 641         | 128         | 128        |

| 256-bit             | 256       | 1537        | 256         | 256        |

**Figure 2.7:** 16-bit Kogge-Stone adder [8]

#### 2.5 Sparse Kogge-Stone Adder

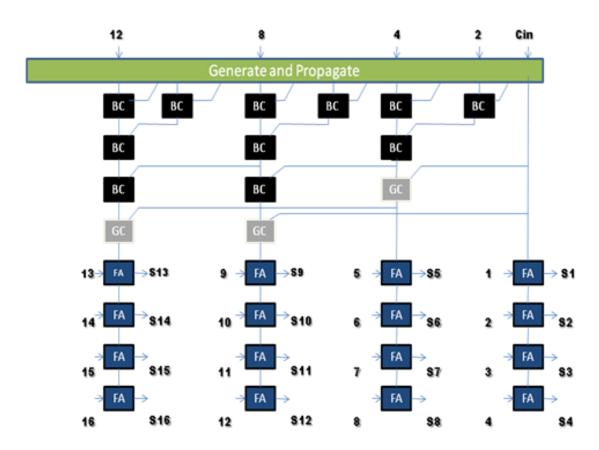

The sparse Kogge-Stone adder consists of several smaller ripple carry adders (RCAs) on its lower half and a carry tree on its upper half. Thus, the sparse Kogge-Stone adder terminates with RCAs. The number of carries generated is less in a sparse Kogge-Stone adder compared to the regular Kogge-Stone adder. The functionality of the GP block, black cell and the gray cell remains exactly the same as in the regular Kogge-Stone adder. The schematic for a 16-bit sparse Kogge-Stone adder is shown in Figure 2.8. Sparse and regular Kogge-Stone adders have essentially the same delay when implemented on an FPGA although the former utilizes much less resources [9].

Figure 2.8: Sparse Kogge-Stone adder.

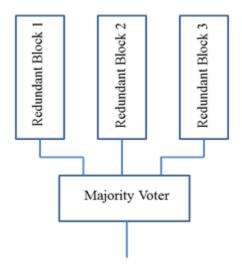

#### 2.6. Basic Fault Tolerance - Hardware Redundancy

Basic fault tolerance can be achieved by N-module redundancy (NMR) where N refers to the degree of redundancy used in the design. This approach is easy to apply but results in high area overhead. For example, Triple Modular Redundancy (TMR) is a fault tolerant method where the hardware is essentially replicated in triplicate with a voter circuit used to pass the majority rule signals to the output. TMR is one of the most common methods used to create fault tolerant designs in both ASIC and FPGA implementations.

The general TMR is shown in Figure 2.9. Three copies of the same circuit are connected to a majority voter which is used to obtain the fault free output. This method works as long as all the faults are confined to one of the redundant blocks. The latency will be increased because of the voter in the circuit's critical path. The triple modular redundant ripple carry adder (TMR-RCA) is used as the reference design for this thesis. This adder is the simplest approach for both detecting and correcting faults. The block diagram of the TMR adder circuit using the ripple carry adders is shown in Figure 2.10.

**Figure 2.9:** General Triple Modular Redundancy

**Figure 2.10:** TMR adder circuit using ripple carry

#### 2.7 Advanced Fault Tolerant Methods

Compared to the basic TMR-RCA, more advanced fault tolerant methods exist including roving and graceful degradation approaches. Allowing fault tolerance to operate at different levels of abstraction might facilitate a more cost-effective design [10]. Fault tolerance can be classified into three categories, namely information redundancy, time redundancy, and a hybrid approach. The technique involved in information redundancy includes the use of error-correcting codes. Time redundancy tradeoffs area for time of the available time slot and recomputes in a different time slot resulting in low overhead but longer delay [11]. Hybrid approaches make use of several types of the available tree [5] for redundancy to achieve fault tolerance. This section focuses on a hybrid approach to achieve fault tolerance. For example, a fault tolerant design can be implemented by taking advantage of the inherent redundancy of a parallel prefix adder like the Kogge-Stone adder which is described next.

#### 2.7.1 Structural Design – Hybrid Approach

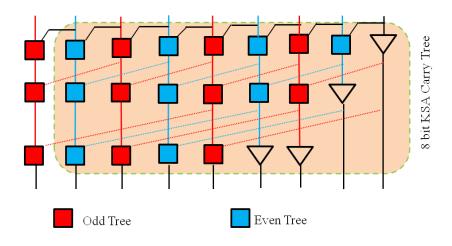

A fault tolerant parallel prefix adder can be implemented using a Kogge-Stone adder due to the inherent redundancy in the carry-tree [5]. The even and the odd carry trees present in the adder are mutually exclusive as shown in the Figure 2.11. An extra

column is added to make sure that if any fault occurs at the last sum bit then it can be restored. This approach falls under the hybrid category due to its inherent structural redundancy and use of time redundancy since two clock cycles are required to correct a

**Figure 2.11:** An 8 bit Kogge-Stone carry tree illustrating the mutually exclusive even and odd carry trees.

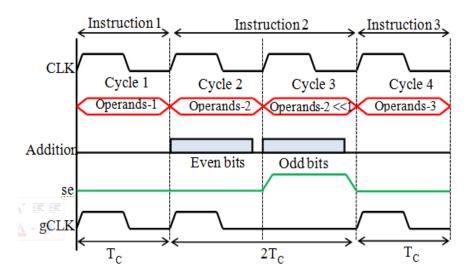

fault. Due to the mutual exclusive nature, if a defect is present in the one-half of the carry tree, the other half can be utilized to compute the carries for both the even and odd carries. The timing diagram for this design is illustrated in Figure 2.12. In the scenario depicted, three instructions are scheduled on three different adders present in the execution unit. The second adder is defective and is evaluated in two clock cycles whereas the fault free adders are evaluated in a single-clock cycle, assuming that the defect is in the odd bits. In the timing diagram adaptive clocking is performed during the execution of the second instruction for correct functionality of the pipeline. In cycle-3 the odd bits are computed correctly and stored as the operands are left shifted by one bit. The even bits are discarded in cycle-3. As the second adder which is scheduled for instruction 2 is faulty, it will be completely evaluated only at the end of cycle-3 even though it is initiated at cycle-2. The even bits are computed in cycle-2 and registered while the odd bits are discarded.

Thus the output will be produced only after two clock cycles. In cycle-1, one of the correct set of bits which are either even or odd are computed and stored at the output registers. The operands are shifted by one bit and the remaining sets of bits are computed and stored in cycle-2. The trade-off in time may be acceptable in some circumstances using proper scheduling and micro-architectural changes, as detailed in [5]. The design for the error correcting 8-bit Kogge-Stone adder is shown in Figure 2.13. The multiplexers at the inputs are used for shifting the operands left by one bit whereas the multiplexers at the output are used for shifting the partially correct sums to the right by one bit.

**Figure 2.12:** Timing diagram for three adders in execution unit (T<sub>C</sub> is the clock period)

#### **2.7.2 Roving**

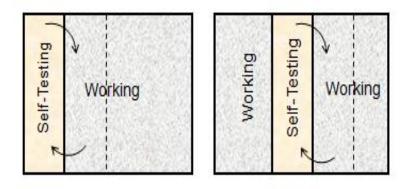

Roving is one of the fault detection methods detailed in [4]. An important work in this area is described by Emmert, Stroud and Abramovici in which the testing and the diagnostic process takes place in designated Self-Testing Areas (STARs) of an FPGA, without disturbing the normal operation of the system [12]. Roving performs a progressive scan of the FPGA structure by swapping blocks of equivalent functionality for testing. In the roving detection of faults, the FPGA is split into equal-sized regions in which one region is configured to perform self-test, while the remaining areas carry out the designed function of the FPGA. An important advantage is that the detected fault does not affect the working logic of the system [6]. As a result, the operation does not have to be interrupted for fault diagnosis. It relies on incremental run-time configuration, which is the ability to dynamically reconfigure part of an FPGA without actually disturbing the operation performed in the rest of the device.

Figure 2.13: Block diagram for the proposed 8-bit fault tolerant Kogge-Stone adder [5].

The overhead will be less in roving compared to other redundancy methods as the overhead consists of one-self test region and a controller which manages the reconfiguration process. A disadvantage is that roving results in longer signal delays and may force a reduction in the system clock speed as the connections of the adjacent functional areas are stretched [12]. Roving spares and fault scanning is illustrated in Figure 2.14.

Figure 2.14: Roving area under test across the chip.

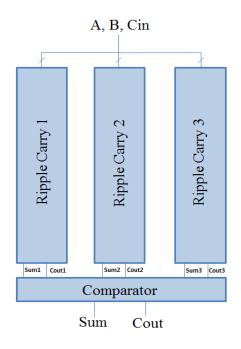

#### 2.7.3 Graceful Degradation

This method involves the use of redundant hardware for both the detection and recovery from faults. Graceful degradation occurs when one of the spare hardware blocks is used to replace a faulty one, resulting in a degradation of system functionality.

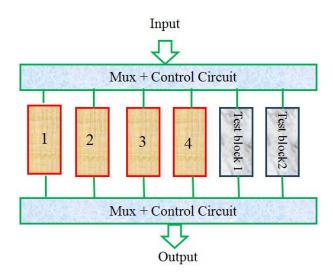

During fault detection, each block is checked with the voter circuit against two identical blocks used as spares. If there is any error then the faulty block will be replaced with one of the spare blocks. Figure 2.15 shows the general description of a system that exhibits graceful degradation. In this example, there are four operational blocks with two test blocks.

Figure 2.15: General block diagram of graceful degradation

In this scheme, blocks 1 to 4 and the two test blocks have identical functionality. Two redundant blocks, labeled Test block 1 and 2 are used to check the blocks labeled 1 to 4 in sequence. A TMR-like checking scheme is utilized in this example. If an error is found, then the faulty block is replaced with one of the test blocks. Thus, the system remains operational but the fault checking capability is degraded.

Figure 2.16 provides a detailed example. Consider the case where the fault is present in block 4. Figure 2.16(a) shows the first block being checked with the test blocks. As no error is found in block 1, the fault checking now proceeds to block 2, shown in Figure 2.16(b). There is no error in block 2. Block 3 is then compared with the test blocks shown in the Figure 2.16(c). Finally checking goes to the block 4 as no fault is

present in block 3 (see Figure 2.16(d)). As block 4 is faulty, the entire block is replaced with one of the test blocks, shown in Figure 2.16(e). The system remains functional, but the ability to detect existing faults has been degraded, since a TMR-like fault checking scheme can no longer be utilized.

**Figure 2.16:** General view of the graceful degradation process.

### **Summary**

In this chapter, the general fault tolerance methods implemented on electronic systems like Triple Modular Redundancy (TMR) were discussed. Also advanced fault tolerant methods like the hybrid approach with structural redundancy, the roving concept and the graceful degradation approach were explained. In the next chapter, the methods of implementation on an FPGA, including TMR-RCA, and the error correcting structural approach [5] are discussed. A proposed fault tolerant sparse Kogge-Stone adder is also introduced.

#### Chapter 3

#### **Basic Fault Tolerant Implementation**

#### 3.1 Introduction

Some basic methods for implementing fault tolerant adder designs are described in this chapter. First the FPGA implementation method using Xilinx's Integrated Software Environment (ISE) software is described. The simulation results for the Triple Modular Redundancy-Ripple Carry adder (TMR-RCA) and the error correcting regular Kogge-Stone adder are detailed next. Then the design used for creating a partially fault tolerant lower half sparse Kogge-Stone adder which includes the use of ripple carry adders is described.

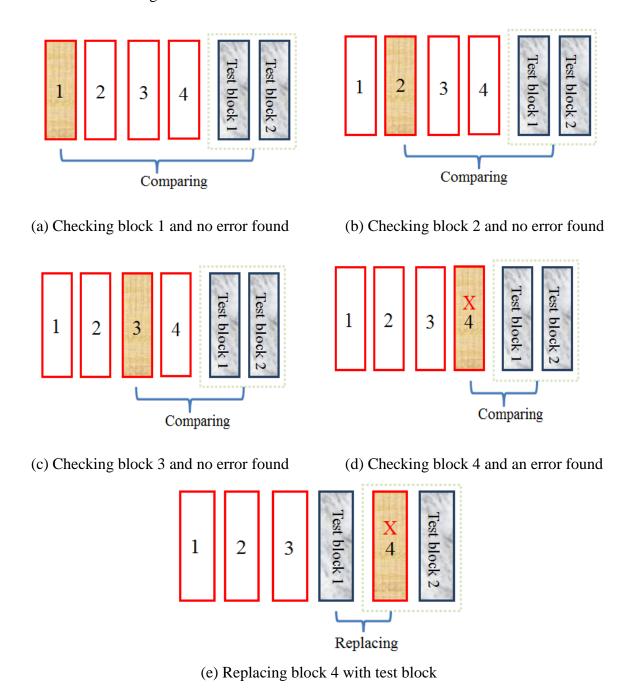

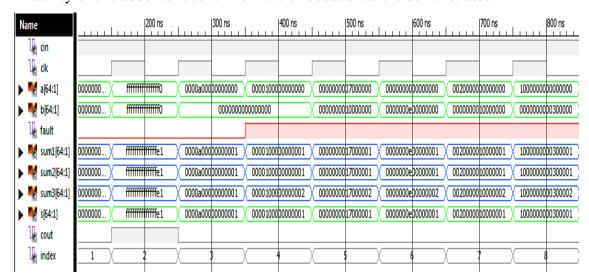

#### 3.2 FPGA Implementation Method

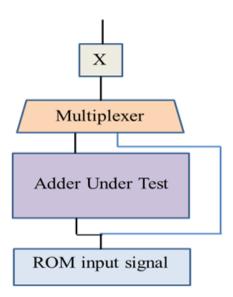

Xilinx's ISE Design Suite 12.4 software is used to implement all the fault tolerant adder designs on the Spartan 3E FPGA. The design flow is outlined in Figure 3.1. A project navigator helps to manage the entire design process which includes design entry, simulation, synthesis and implementation by downloading the configuration onto the FPGA device.

First, the design flow begins by creating a new project in Xilinx's ISE, followed by coding the model in VHDL. The VHDL code for the select fault tolerant adders is given in the Appendices. The code is then synthesized using the ISE software. The functionality of the designs are verified by creating a test bench in VHDL and then simulating with the ISIM tool. Finally, the functionality of the implemented adder is verified using a TLA 7012 Logic Analyzer.

#### 3.3 Triple Modular Redundancy-RCA

The simulation results for the TMR-RCA structure discussed in Chapter Two are described in this section. Input stimuli were carefully selected to demonstrate the functionality of each adder. Specific cases are discussed for each adder approach. The VHDL code for the 32-bit TMR-RCA and higher bit widths implemented on hardware

are given in Appendix A. A signal named fault is used to inject a fault into one of the RCAs and the signal error goes high when a fault is detected.

Figure 3.1: General design flow

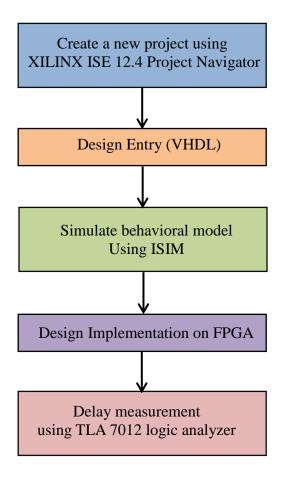

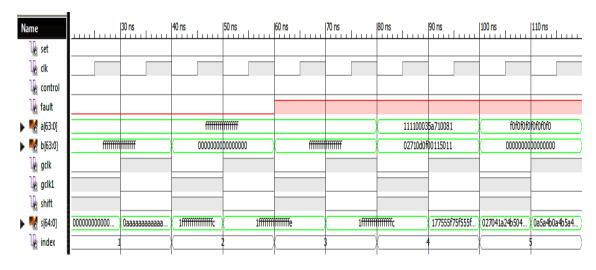

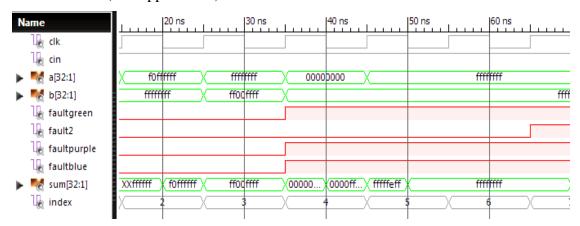

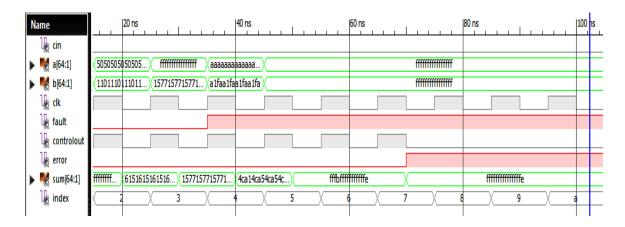

The simulation results for the adders of widths up to 256 bits are observed in this thesis. The simulation results for the 64-bit TMR-RCA are shown in the Figure 3.2 as an example. The simulation results are shown in two parts: (a) the actual functionality of the adder and (b) the fault tolerant operation.

(b) Consider the case where a fault is injected into one of the ripple carry adders at index = 5. The inputs are  $c_{in} = 1$ , a = '0000000070000000' and b = '0000000100000000'. The resulting output sum s equals '0000000170000001' which is chosen from the majority of the redundant RCA blocks, sum1 or sum2, as sum3 is incorrect. Hence the ability of this adder to recover from the embedded fault is demonstrated.

**Figure 3.2:** Simulation results for the 64-bit TMR-RCA

### 3.4 Regular Kogge-Stone Adder Fault Correction Approach

The simulation results for the regular Kogge-Stone adder error correcting approach discussed in chapter 2 is described in this section. For the 64-bit Kogge-Stone adder, different values are assigned to the inputs a, b and  $c_{in}$  for each clock cycle by synthesizing a test bench. The VHDL code for error correction on a Kogge-Stone adder with a width of 64 bits is given in Appendix B.

The simulation results of the error correcting 64-bit regular Kogge-Stone adder are shown in the Figure 3.3. The simulation results are depicted in two parts: (a) the actual functionality of the adder and (b) fault tolerant operation.

**Figure 3.3:** Simulation results for the 64-bit error correcting Kogge-Stone adder.

## 3.5 Lower Half Fault Tolerant Sparse Kogge-Stone Adder

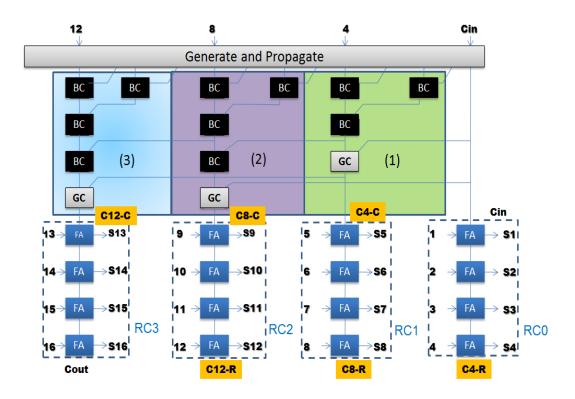

This section describes the design of a Sparse Kogge-Stone adder which is both fault detecting and fault correcting. In the sparse Kogge-Stone adder, ripple carry adders are required at the output, whose length is dependent on the degree of the sparseness in the carry tree. Figure 2.9 in chapter two illustrates a sparse Kogge-Stone adder with a factor of four reduction in the carry tree. Thus, it needs four ripple carry adders in its lower half.

Fully fault tolerant designs for the sparse Kogge-Stone adder have been achieved in two steps. First a fault tolerant design for the lower half (i.e., the ripple carry adder chains) is implemented. Then the design is extended to make the upper half (i.e, the carry tree) fault tolerant. This is discussed in Chapter Four.

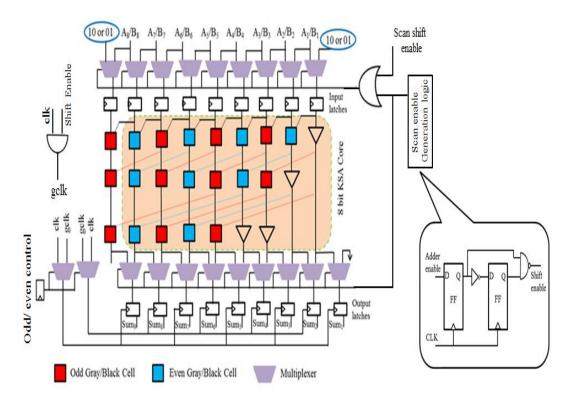

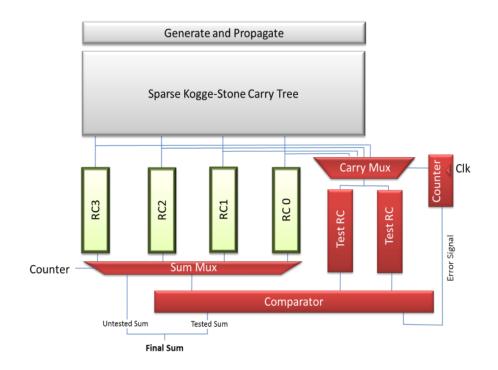

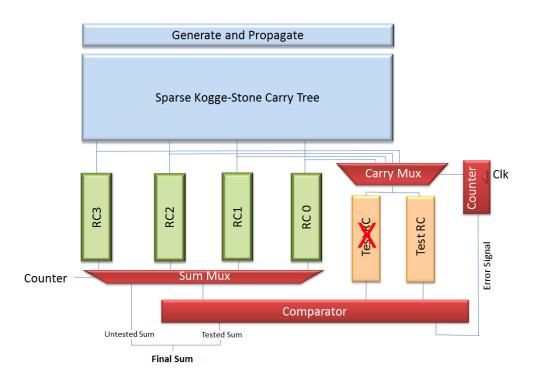

As the design contains the addition of the ripple carry adders in the sparse Kogge-Stone adder, a similar testing methodology can be used as with the TMR-RC adder to detect and correct errors found in any of the ripple carry adders. An illustration of the design for the fault tolerant sparse Kogge-Stone adder is shown in Figure 3.4.

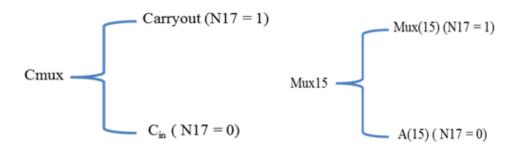

Figure 3.4: Block diagram of fault tolerant sparse Kogge-Stone adder

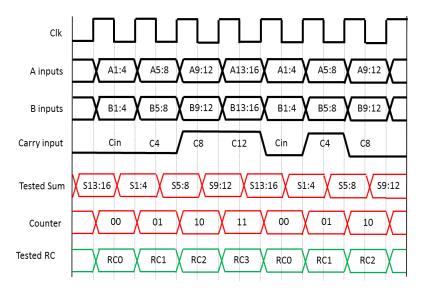

The highlighted portion in red in Figure 3.4 is the error correction and detecting logic. Two extra ripple carry adders must be added to the design for testing (Test RC) which is similar to the TMR-RCA. Also, some multiplexers and a bit counter are required. During each clock cycle, one of the four ripple carry adders is selected for testing. The corresponding carry-in and A and B operands are routed through the multiplexer denoted as Carry Mux to the TestRCs. The selections of these inputs are controlled by a counter which is driven by the clock. The final evaluation is performed by a comparator in which the outputs of the tested RCA branch (one of RCO to RC3) are switched simultaneously. The final sum is obtained at the falling edge as the valid output has been passed through the tested sum.

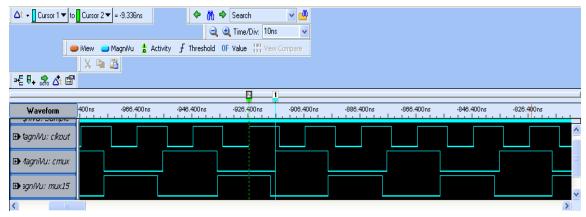

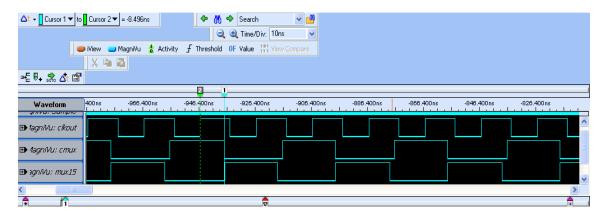

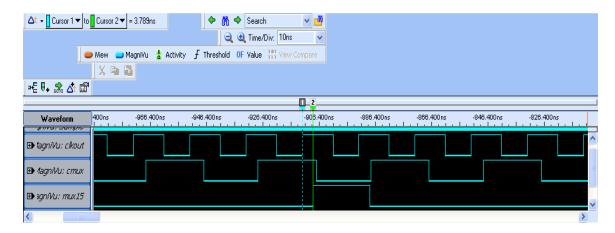

The timing diagram for this design is illustrated in Figure 3.5. Once an error is detected, the clock operating the bit counter is stopped at the RCA branch where the error was detected and will continue correcting the faulty RCA branch until the error has been removed.

Figure 3.5: Timing diagram for the lower half fault tolerant Kogge-Stone adder

## 3.5.1 Simulations of the Sparse Kogge-Stone Adder

The design is coded in VHDL and simulated using ISIM. The following simulation results illustrate the successful detection and the correction of the fault in the adder. A signal named fault is used to inject a fault into one of the RCAs and the signal error goes high when a fault is detected. The synthesis results for the lower half fault tolerant sparse Kogge-Stone approach are obtained for the Spartan 3E FPGA. The VHDL code for a 32-bit lower half sparse Kogge-Stone adder is given in Appendix C.

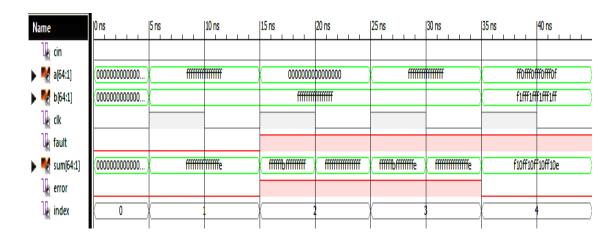

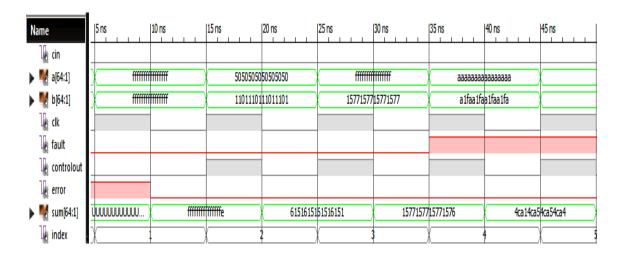

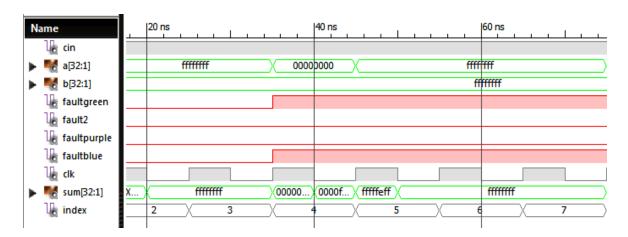

The simulation results for the 64-bit sparse Kogge-Stone adder are shown in Figure 3.6. The simulation results are depict in two parts: (a) the functionality of the adder and (b) the fault tolerant operation.

- (a) Consider the case where the index = 1. The corresponding assigned inputs are a = 'fffffffffffff, and b = 'ffffffffffffff. The final sum obtained at that clock cycle is correctly given as sum = 'ffffffffffffff.

- (b) Consider the case where the fault is introduced at index =2. The corresponding assigned inputs are a = `0000000000000000 and b = `fffffffffffff. As described

earlier, the error is detected and the correct sum is obtained at the falling edge of index = 2. Thus the final sum obtained at the given inputs is *sum* = 'fffffffffffffff.'. Hence the ability of this adder to recover from the embedded fault is demonstrated.

**Figure 3.6:** Simulation results for the 64-bit lower half FT sparse Kogge-Stone adder.

## **Summary**

In this chapter, the simulation results for some basic fault tolerance techniques suitable for implementation on FPGAs were discussed. The inherent redundancy in the carry tree of the Kogge-Stone adder is used for error correction. Also by introducing additional ripple carry adders in the lower half of the sparse Kogge-Stone adder, fault tolerance can be achieved. In the next chapter, more advanced concepts for implementing fault tolerant adders on FPGAs are described. In addition, performance metrics like timing (speed-adder delay) and resource utilization for the different methods are compared. The functionality of the various fault tolerant adder designs is verified using a logic analyzer for testing these implementations.

## Chapter 4

## **Advanced Fault Tolerance Concepts**

#### 4.1 Introduction

Having discussed the simulation results for basic fault tolerant adders, this chapter will describe the architectures for implementing advanced fault tolerant sparse Kogge-Stone adders. First, a fault tolerant carry tree which is designated as the upper half of the sparse Kogge-Stone adder is designed. Second, the permanent replacement of a faulty block with a spare block is implemented for the ripple carry adders present on the lower half of the Sparse Kogge-Stone adder. As this results in reduced fault checking ability, this process is known as graceful degradation. The design of these proposed fault tolerant approaches with their simulation results are detailed in this chapter.

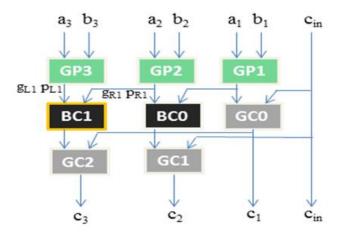

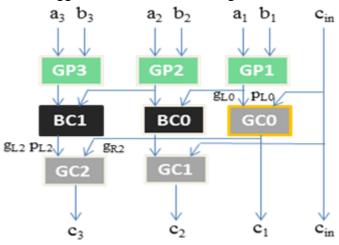

## 4.2 Upper Half Fault Tolerant Sparse Kogge-Stone Adder

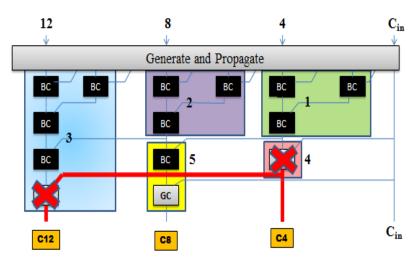

The fault tolerant design for the lower half of the sparse Kogge-Stone adder which consists of the ripple carry adder chains, was explained in Chapter Three. This section focuses on making the carry tree of the sparse Kogge-Stone adder, designated as the upper half, fault tolerant. In this design, the carry tree of the sparse Kogge-Stone adder is split into three sections, which are depicted by the following colors: (1) green, (2) purple and (3) blue in Figure 4.1. The testing methodology developed makes use of redundant carries generated by the carry tree (Ci-C) and the ripple carry adders (Ci-R). For example, for a 16-bit sparse Kogge-Stone adder with 4-bit RCAs, there are two sets of carries generated for C4, C8, and C12 (i.e., i = 4, 8, 12). The complete schematic for the upper half error detection scheme for the 16-bit sparse Kogge-Stone adder is shown in Figure 4.1.

The technique for detecting a fault is now explained in detail. For example, if carry C4-C does not match carry C4-R, the error must be located in the first section assuming the first ripple carry adder (RC0) is fault free. If the result obtained is fault free, a fault free carry C4 will enter the second ripple carry adder (RC1).

Figure 4.1: Upper half error detection scheme for 16-bit sparse Kogge-Stone

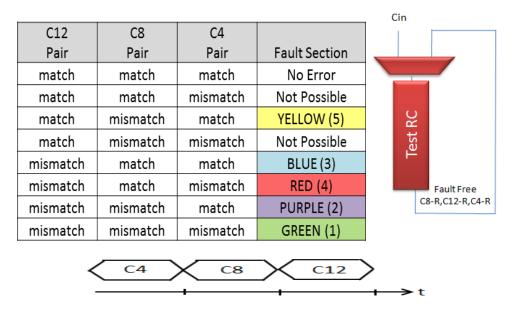

Next, if a mismatch is found in the C8-R and C8-C pair, there exists a fault in the second section. Finally, if the carries C8 and C4 are fault free, the error can be in the third section if a mismatch is found in the C12 pair. The fault detection mechanism is summarized in Figure 4.2. A mismatch in a carry pair is indicated by '1' in Figure 4.2. If there are multiple faults at the same time this approach is still able to correct at its corresponding clock cycle.

| C12 | C8 | C4 | Fault selection |

|-----|----|----|-----------------|

| X   | X  | 1  | Green (1)       |

| X   | 1  | 0  | Purple (2)      |

| 1   | 0  | 0  | Blue (3)        |

| 0   | 0  | 0  | No Error        |

**Figure 4.2:** Upper half detection truth table

Spares for each section can be made available to replace a faulty section by using multiplexers to reroute the carry tree from the faulty branches to the spare section. A

method for increasing the number of sections detectable is possible with the adoption of a time redundant ripple carry adder which is already in the bottom-half test circuit. By feeding the carry out produced by the first ripple carry (C4-RCO) into the test ripple carry adders (Test RCs), the adder produces completely fault free values for comparison over the course of three clock cycles. These fault free carries can then be compared to the carry tree's output for fault detection in the five sections as illustrated in the Figure 4.3. An example depicted in Figure 4.3 shows the fault originating in the red section (4) and passing through C12 and C4. As C8 shows no signs of a fault in this example, the only possible case for this error combination can be traced back to a fault in section (4). Similarly, with this scheme a list of possible combinations was developed into a truth table as shown in Figure 4.4. The figure also includes an example of a time redundancy ripple carry circuit capable of producing the fault free carries necessary for the comparison. It takes three clock cycles to produce C12 as shown in Figure 4.4. If an error has been successfully isolated to a specific section of the adder, the faulty section can be replaced using a decoder and multiplexer, which reroutes the signals to the replacement sections built into the design.

**Figure 4.3:** Upper half detection scheme with fault free carry comparisons.

The fault can only be corrected after a faulty sum value has been allowed to pass. Once the rerouting of the replacement section has completed, the adder will perform normally as seen in the simulation results in the next section.

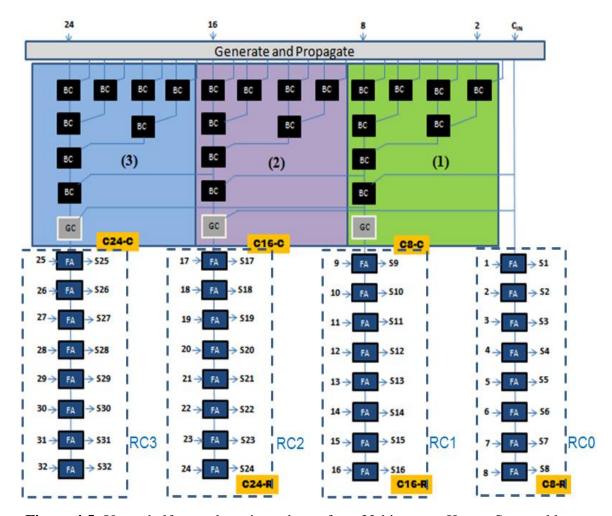

**Figure 4.4:** Truth table for upper half error detection with fault free comparisons

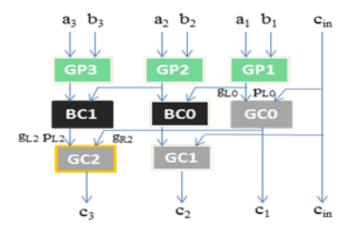

A similar fault detection scheme is applied for the sparse Kogge-Stone adder of higher bit widths. The complete schematic for the proposed upper half error detection scheme for a 32-bit sparse Kogge-Stone adder is shown in Figure 4.5. For example, for a 32-bit sparse Kogge-Stone adder with 4-bit RCAs, there are two sets of carries generated for C8, C16, and C24. The same technique for detecting a fault as in the 16-bit sparse Kogge-Stone is now explained for this 32-bit adder. For example, if carry C8-C does not match carry C8-R, the error must be located in the first section assuming the first ripple carry adder (RC0) is fault free. If the result obtained is fault free, a fault free carry C8 will enter the second ripple carry adder (RC1). Next, if a mismatch is found in the C16-R and C16-C pair, there exists a fault in the second section. Finally, if the carries C16 and C8 are fault free, the error can be in the third section if a mismatch is found in the C24 pair.

This illustrates the proposed scheme for implementing fault tolerance in the carry tree and can easily be extended to higher bit width sparse Kogge-Stone adders.

**Figure 4.5:** Upper half error detection scheme for a 32-bit sparse Kogge-Stone adder

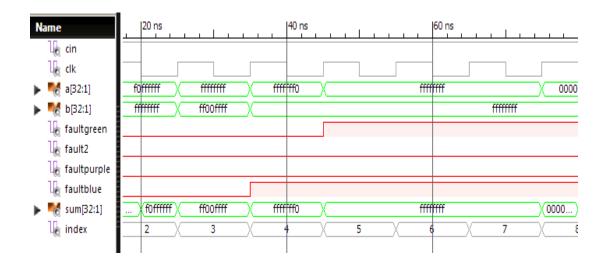

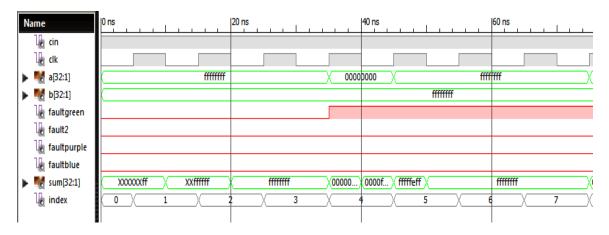

#### 4.2.1 Simulation Results

The final design is coded in VHDL and simulated using ISIM. The VHDL code for a 32-bit sparse Kogge-Stone upper half approach is given in Appendix D. A signal named faultgreen is used to inject a fault into the section (1) and a signal named fault2 is injected into the backup of section (3) colored in blue in Figure 4.5. The synthesis results for the 32-bit fault tolerant sparse Kogge-Stone upper half approach are obtained for the Spartan 3E FPGA and its simulation results are shown in Figure 4.6.

The simulation results are shown in two parts: (a) functionality of the adder and (b) fault tolerant performance.

(a) Consider the cycle with index = 3 shown in Figure 4.6 (a). The inputs are  $c_{in} = 1$ , a = 'fffffffff', and b = 'ff00ffff'. The correct output sum = 'ff00ffff' is obtained.

- (b) Consider the cycle with index = 4 shown in Figure 4.6 (b). The chosen inputs are  $c_{in}$  = 1, a = 'fffffff0', and b = 'ffffffff'. The signal named faultblue is introduced in section (3) of the design. This tests the adders ability to detect and correct the fault. The obtained output sum is correctly computed as 'fffffff0'.

- (c) Consider the cycle with index = 5 shown in Figure 4.6 (b). The chosen inputs are  $c_{in}$  = 1, a = 'ffffffff', and b = 'ffffffff'. In this case signals, named faultblue and faultgreen are used to inject a fault into sections (3) and (1), respectively. The obtained output sum is correctly computed as 'ffffffff'.

The simulations results are also checked and verified for various other fault combinations (see Appendix G).

**4.6** (a): Normal adder operation of the sparse Kogge-Stone upper half

**4.6** (b): Fault tolerant adder operation of the sparse Kogge-Stone upper half

**Figure 4.6:** Simulation results for 32-bit sparse Kogge-Stone upper half approach

#### 4.3 Graceful Degradation

Graceful degradation is a process of permanently replacing the faulty block with the test block, thus degrading the fault tolerant capability of the circuit in order to continue its primary function. The generic example with a complete block diagram was explained in Chapter Two.

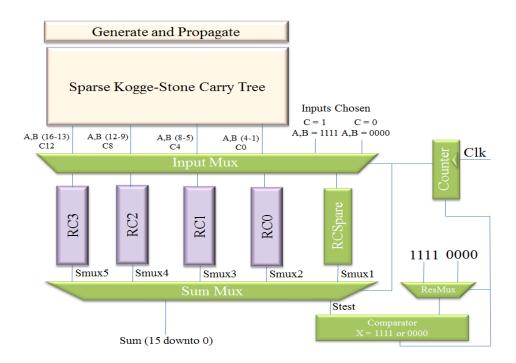

## 4.3.1 Implementation

This section describes the proposed graceful degradation approach for the sparse Kogge-Stone adder. Multiplexers and a bit counter are added to this design. An illustration of this design can be seen in Figure 4.7, where the error correction and the detection logic is highlighted in green. In this design, RC0 to RC3 are the ripple carry adders present on the lower half of the sparse Kogge-Stone adder and an extra ripple carry adder called RCSpare, is added for replacement of a faulty RCA.

Figure 4.7: Block diagram of graceful degradation on the sparse Kogge-Stone adder

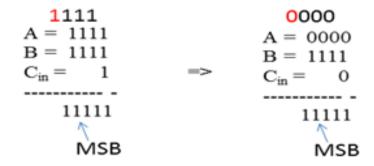

During each clock cycle, one of the four ripple carry adders, RC0 to RC3 (highlighted in purple in Fig. 4.7) is selected for testing. Two test input cases are chosen

for testing the selected adder, and while it is being tested its corresponding inputs are routed to RCSpare. The results obtained for the given inputs are expected earlier and fed to the multiplexer called ResMux. Thus ResMux selects one of the expected results for the test inputs. The output obtained from the ripple carry adder which is under test is then compared with the expected output from the ResMux using a comparator. If there is no error while comparing then the checking continues to the other inputs chosen, i.e. operands A, B = 0000 and C =0. Thus the expected outputs for the two chosen cases are compared with the obtained output from the selected ripple carry adder under test. The test inputs are chosen for testing the ripple carry adder based on the popular *Stuck-At* fault model [13]. A stuck-at 0 fault is tested using inputs of 1111 and a stuck-at 1 fault is tested by setting the inputs to 0000. If the selected ripple carry adder passes the two test cases it is considered to be fault free.

The counter is driven by a clock and controls the selection of these inputs. The checking then continues to the next ripple carry adder. Once an error is detected, the clock operating the bit counter is stopped and the block is permanently replaced with the replacement block RCSpare while the adder can continue to function correctly. As further checking is not possible, fault tolerant capability is lost. However this can be remedied by adding more replacement blocks. This is a tradeoff between fault tolerant capability and area.

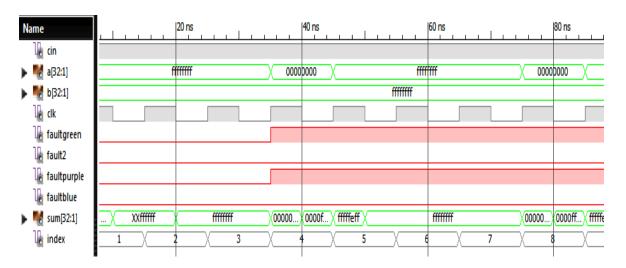

#### **4.3.2 Simulation Results**

The final designs are coded in VHDL and simulated using ISIM. The VHDL code for a 32-bit TMR-RCA and graceful degradation implemented on hardware are given in Appendix E. A signal named fault is used to inject a fault into one of the RCAs and the signal error goes high when a fault is detected. The synthesis results for fault tolerant sparse Kogge-Stone lower half approach are obtained for the Spartan 3E FPGA.

The simulation results of the 64-bit graceful degradation on a sparse Kogge-Stone adder are shown in the Figure 4.8. The simulation results are shown in two parts: (a) functionality of the adder and (b) the fault tolerant performance.

(a) Consider the cycle with index = 1 shown in Figure 4.8 (a). The inputs are  $c_{in} = 0$ , a = 'fffffffffff, and b = 'fffffffffffff.' The resulting output is sum = 'fffffffffffffff.'

**4.8** (a): Normal adder operation of the graceful degradation adder

**4.8** (b): Fault tolerant adder operation of the graceful degradation adder

**Figure 4.8:** Simulation results for a 64-bit graceful degradation sparse Kogge-Stone adder

## **4.4 Synthesis Results**

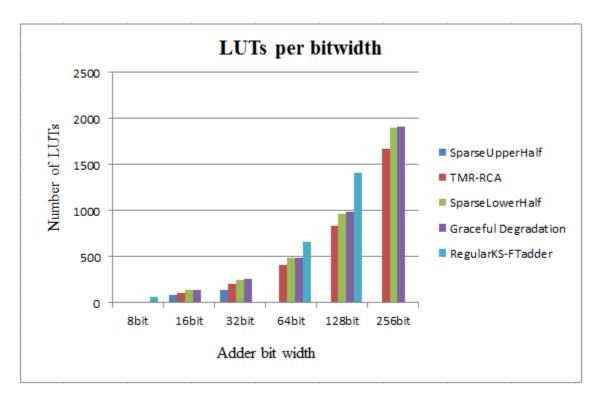

The synthesis results for a TMR-RCA, regular Kogge-Stone fault tolerant adder, proposed fault tolerant sparse Kogge-Stone for both lower half and upper half, and graceful degradation are obtained for a Spartan 3E FPGA. Design statistics are obtained by synthesizing the adders using Xilinx *ISE* software in two ways. First, the number of resources in terms of look up tables (LUTs) is observed. The results obtained are shown in Figure 4.9 which gives an estimation of the number of the look up tables (LUTs) used by each design. The sparse Kogge-Stone upper half approach was implemented for 16 and 32 bits, thus demonstrating it can be scaled to wider bit widths. However, partitioning the sections of the sparse Kogge-Stone adder to higher order bit widths is quite a challenging task.

Figure 4.9: Estimation of resources used from FPGA synthesis

Second, the simulated delays for the fault tolerant adders are observed. The TMR adders seems to be the most efficient approach in terms of resources for fault tolerant design on FPGA due to its simplicity and the ability to take the advantage of the fast-carry chain.

The graphs are plotted for delay versus the bit width of the adders. The delay of each TMR-RCA is compared to the delay of the fault tolerant sparse Kogge-Stone adder for widths varying from 16 to 256 bits.

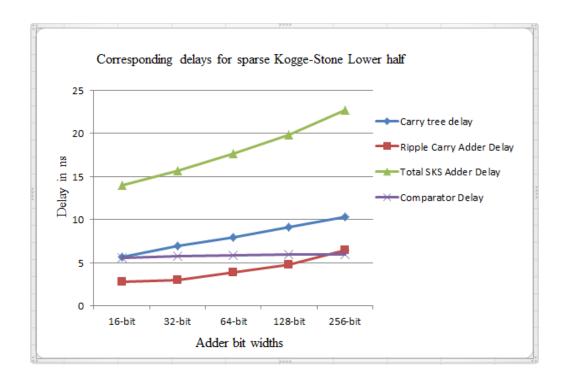

Figure 4.10 depicts the graph for the total adder delay taking each component into consideration. The comparator delay is constant for all bit widths. The carry tree delay has logarithmic characteristics whereas the ripple carry delay is linear as expected. Thus the overall total delay of the fault tolerant lower half sparse Kogge-Stone is the summation of all the individual component delays. Hence the obtained plot is logarithmic as expected for the sparse Kogge-Stone adder as shown in Figure 4.10.

Figure 4.10: Corresponding delays for the sparse KS on Spartan 3E FPGA

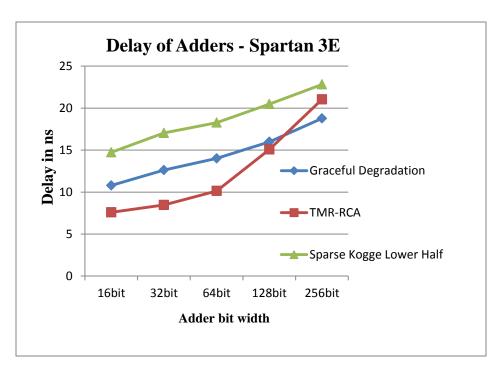

Figure 4.11 depicts the graph for the delay of the adders on Spartan 3E FPGA. In the figure, the delay of the fault tolerant adders for different bit widths is shown. It can be observed from the graph that the delay is small for the TMR-RCA. Thus the TMR-RCA is still the best approach for an FPGA fault tolerant implementation at bitwidth of 128 and less due to its simple design of the approach and the use of the fast carry chain. At

widths of 256 bits, a graceful degradation approach that uses a sparse Kogge-Stone adder has smaller delay.

From the FPGA synthesis results shown in Figure 4.9, it is observed that the regular Kogge-Stone fault tolerant adder requires a lot more resources compared with the proposed fault tolerant approach on the sparse Kogge-Stone lower half and the graceful degradation adder. This tradeoff comes at the expense of a higher logic depth resulting in a longer critical path in the graceful degradation on the sparse Kogge-Stone adder than the regular Kogge-Stone fault tolerant adder. The tradeoffs for the proposed fault tolerant adders can be observed by looking at the delay plots. At 256 bits, the graceful degradation is better than the TMR-RCA due to its use of a sparse Kogge-Stone adder configuration.

Figure 4.11: Delay of FT adders on Spartan 3E FPGA

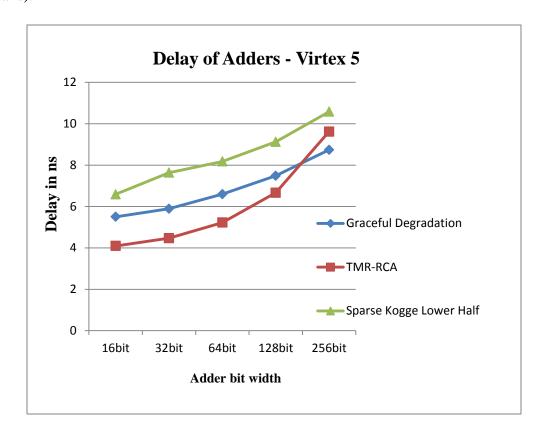

The delays for the adders synthesized on Virtex-5 FPGA are shown in Figure 4.12. It can be observed that the overall delay of all the adders is roughly half that compared to the Spartan 3E FPGA. This is expect since the Virtex 5 FPGA is built using a more advanced process than the Spartan 3E FPGA. In addition, the each Virtex 5 logic cell uses 6-input look-up tables (LUTs) compared to the 4 input LUTs of the Spartan 3E

FPGA, resulting in a more efficient implementation overall. (See Appendix H for details).

**Figure 4.12:** Delay of FT adders on the Virtex 5 FPGA

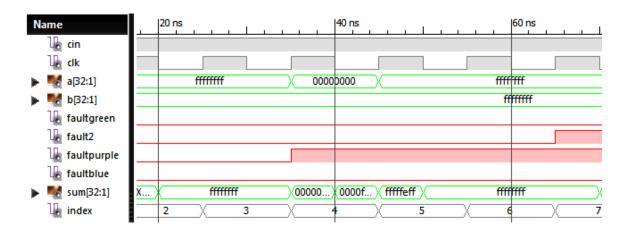

#### 4.5 Hardware Implementation

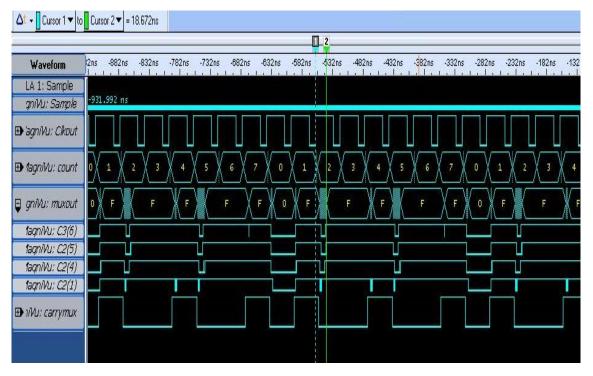

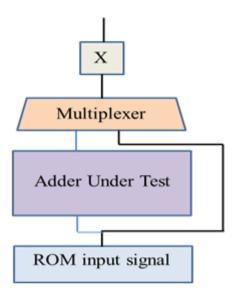

After synthesizing all the designs using the Xilinx ISE software, the proposed fault tolerant adders TMR-RCA, sparse Kogge-Stone adder (lower half), and graceful degradation are then implemented on the Spartan 3E FPGA. The functional verification and the delays of all the structures are performed by using a high speed Tektronix Logic Analyzer (TLA). The VHDL code for a 32-bit adder implemented on hardware is given in Appendix F to keep it to a manageable size and all delay measurements here are shown for 64 bits. The resulting waveforms obtained by implementing a 64-bit TMR-RCA on Spartan 3E FPGA are shown in Figure 4.13.

For the TMR-RCA, different values are assigned for the inputs a, b and  $c_{in}$  for each clock cycle by synthesizing a test circuit along with the fault tolerant adder on the FPGA. These waveforms show how the critical adder delay is measured at every output

transition with respect to a clock signal on the logic analyzer. The corresponding delay obtained at particular transition is shown in Figure 4.13 which is highlighted in red (see Appendix I for the detailed procedure for measuring adder delay).

Figure 4.13: Measured delay for the 64-bit TMR-RCA

For obtaining the worst case delay for the fault tolerant lower half sparse Kogge-Stone adder, the fault has been introduced to one of the TestRC blocks as shown in Figure 4.14. This ensures that a comparison is made between one of the RCA blocks (RCA0 to RCA3) and the fault free TestRC block. The resulting waveforms obtained by implementing a 64-bit sparse Kogge-Stone lower half on the Spartan 3E FPGA are shown in Figure 4.15.

**Figure 4.14:** Implemented procedure for simulating the worst-case delay on the sparse Kogge-Stone lower half approach

Figure 4.15: Measured delay for the 64-bit sparse Kogge-Stone adder

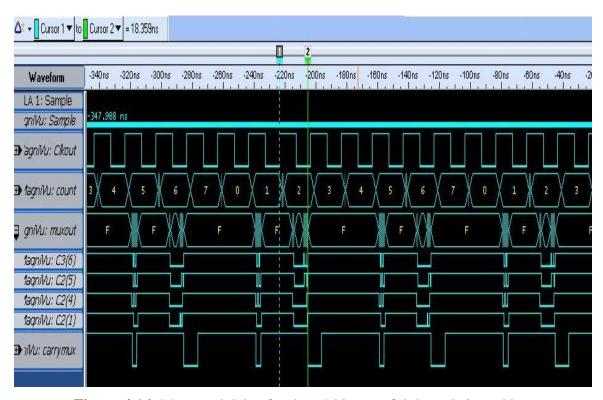

The resulting waveforms obtained by implementing a 64-bit sparse graceful degradation on Spartan 3E FPGA are shown in Figure 4.16.

Figure 4.16: Measured delay for the 64-bit graceful degradation adder

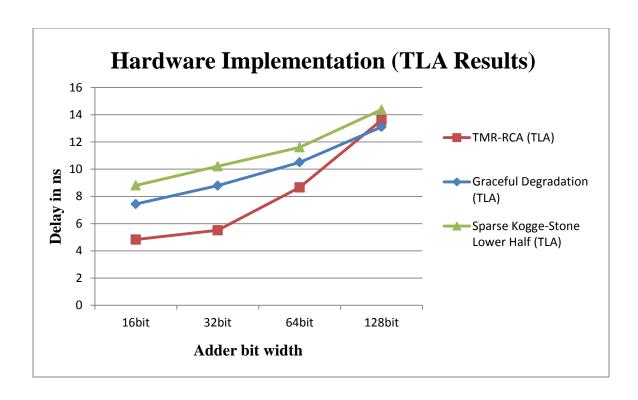

The worst case delays are obtained from the logic analyzer for TMR-RCA, sparse Kogge-Stone adder (Lower Half), and graceful degradation for the corresponding chosen input patterns for the adders of different bit widths. Figure 4.17 summarizes the test results, showing that the measured results are faster but the overall relative delay between the adders is comparable to the results obtained from the synthesis reports.

### **Summary**

This chapter has discussed the advanced techniques for implementing fault tolerant adders with its simulation results. By introducing backup sections in the upper half of the sparse Kogge-Stone adder, fault tolerance can be achieved. The key results are summarized in terms of utilization of resources and the corresponding adder delays.

**Figure 4.17:** Summary of adder delays on Spartan 3E.

The functionality of the designs implemented on the hardware has been verified by viewing the output signals on a logic analyzer and then measuring the resulting adder delays. The results indicate that the TMR-RCA is the best approach for an FPGA fault tolerant implementation at bit widths up to 128 due to its simple design and the use of the fast carry chain. At higher bit widths of 256, the sparse Kogge-Stone adder using a graceful degradation approach proves to be superior to the TMR-RCA in terms of delay. The next chapter will summarize and conclude the thesis work that has been completed and discuss some possibilities for future work.

## **Chapter Five**

## **Conclusions and Future Work**

#### 5.1 Conclusions

The fault tolerant adders implemented on FPGAs have been characterized with respect to their delay performance and logic complexity as a function of bit width. Basic fault tolerant adder designs like the Triple Modular Redundancy-Ripple Carry Adder (TMR-RCA) and error correcting regular Kogge-Stone adder were analyzed. A sparse Kogge-Stone adder which is fully fault tolerant in its lower half (i.e., in the ripple carry adders) was proposed. Simulation results demonstrate that this design is able to detect and correct errors in its RCA chains.

Architectures for implementing advanced fault tolerance techniques on the sparse Kogge-Stone adders were proposed. This includes the upper half fault tolerant sparse Kogge-Stone adder and a graceful degradation concept. Simulation and synthesis using FPGA design tools have validated the performance of the lower-half and upper-half sparse Kogge-Stone adders for both fault detection and correction. In this analysis, the TMR-RCA seems to be the most efficient approach for fault tolerant design on an FPGA in terms of its resources due to its simplicity and the ability to take the advantage of the fast-carry chain. However, for very large bit widths, there are indications that the Kogge-Stone adder offers superior performance over a ripple carry adder when implemented on an FPGA. A fault tolerant sparse Kogge-Stone adder is designed by taking advantage of the existing ripple carry adders in the architecture and adopting a similar approach to the TMR-RCA by inserting two additional ripple carry adders into the design. A graceful degradation approach is implemented with the sparse Kogge-Stone adder. In this approach, a faulty block is permanently replaced with a spare block. As the spare block is initially used for fault checking, the fault tolerant capability of the circuit is degraded in order to continue fault-free operation. The adder delay is faster for graceful degradation with an overhead of 1 ns from measured results and an overhead of 2 ns from the synthesis results independent of the bit widths when compared with the fault tolerant Kogge-Stone adder even though the resource utilization is similar.

#### **5.2 Future Work**