## University of Texas at Tyler Scholar Works at UT Tyler

**Electrical Engineering Theses**

**Electrical Engineering**

Spring 5-1-2012

# Optimization of Short-Channel RF CMOS Low Noise Amplifiers by Geometric Programming

Xiaoyu Jin

Follow this and additional works at: https://scholarworks.uttyler.edu/ee\_grad Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Jin, Xiaoyu, "Optimization of Short-Channel RF CMOS Low Noise Amplifiers by Geometric Programming" (2012). *Electrical Engineering Theses*. Paper 15. http://hdl.handle.net/10950/75

This Thesis is brought to you for free and open access by the Electrical Engineering at Scholar Works at UT Tyler. It has been accepted for inclusion in Electrical Engineering Theses by an authorized administrator of Scholar Works at UT Tyler. For more information, please contact tbianchi@uttyler.edu.

# OPTIMIZATION OF SHORT-CHANNEL RF CMOS LOW NOISE AMPLIFIERS BY GEOMETRIC PROGRAMMING

by

## XIAOYU JIN

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering Department of Electrical Engineering

David H. K. Hoe, Ph.D., Committee Chair

College of Engineering and Computer Science

The University of Texas at Tyler May 2012 The University of Texas at Tyler Tyler, Texas

This is to certify that the Master's thesis of

### XIAOYU JIN

has been approved for the thesis requirements on March 29<sup>th</sup>, 2012 for the Master of Science Degree in Electrical Engineering

Approvals:

Thesis Chair: David H. K. Hoe, Ph.D.

Member: Mukul V. Shirvaikar, Ph.D.

Member: David M. Beams, Ph.D.

Chair and Graduate Coordinator: Vaukul V. Shirvaikar, Ph.D.

Dr. James K. Nelson, Jr., Ph.D., P.E., Dean, College of Engineering and Computer Science, Brazzel Professor of Engineering

### Acknowledgements

I would like to thank everyone who has helped and inspired me during my Master's study at The University of Texas at Tyler. This thesis study would never been possible without their help and support.

First of all, I especially want to thank my advisor, Dr. David H. K. Hoe, for his guidance during my research and study. His perpetual energy and enthusiasm in research has motivated all his advisees, including me. In addition, he was always accessible and willing to help his students with their research. Second, I would like to thank my committee members, Dr. Mukul V. Shirvaikar and Dr. David M. Beams, for taking their time to review my thesis and give constructive criticisms. I would also want to express my gratitude to my friendly and cheerful fellow students. I'm blessed to have them around during daily work. I would like to thank the entire Electrical Engineering department for supporting me throughout my study here at The University of Texas at Tyler.

Last but not least, my deepest gratitude goes to my parents and my sister for their unconditional love and support throughout my life. I'm so grateful to have my husband and my daughter. They are always there cheering me up and stood by me through the good times and the bad times.

## **Table of Contents**

| List of Figures iv                                       |

|----------------------------------------------------------|

| List of Tables                                           |

| Abstractviii                                             |

| Chapter One 1                                            |

| Introduction                                             |

| 1.1 RF CMOS                                              |

| 1.1.1 Bipolar vs. CMOS for RF Circuits                   |

| 1.1.2 RF CMOS LNA Topologies                             |

| 1.2 Submicron CMOS Technology                            |

| 1.2.1 Submicron Effects                                  |

| 1.2.2 Effect of CMOS Downscaling on Noise Model Analysis |

| 1.3 Optimization in Design of RF CMOS LNA7               |

| 1.3.1 Optimization Methods7                              |

| 1.3.2 Geometric Programming                              |

| 1.4 Objective of the Thesis                              |

| Chapter Two 10                                           |

| Noise Modeling in CMOS 10                                |

| 2.1 RF Noise                                             |

| 2.2 Thermal Noise                                        |

| 2.2.1 Thermal Noise in MOSFETs 12                        |

| 2.2.2 Analytical Compact Thermal Noise Models 12         |

| 2.2.2.1 The Model of Klaassen-Prins                      |

| 2.2.2.2 The Model of Albert van der Ziel 15              |

| 2.2.2.3 The Model of Tsividis17                          |

| 2.2.2.4 The Model of Scholten et al                      |

| 2.2.2.5 The Model of Han et al                           |

| 2.2.2.6 The Model of Deen et al                          |

| 2.2.2.7 The Model of Jeon et al                                                  |

|----------------------------------------------------------------------------------|

| 2.2.2.8 White Noise Factor Formula21                                             |

| 2.3 Noise Parameters                                                             |

| Chapter Three                                                                    |

| Formulation of Geometric Programming for Short-channel CMOS LNAs                 |

| 3.1 Geometric Programming                                                        |

| 3.2 Design Considerations for a Short-channel CMOS LNAs                          |

| 3.2.1 Objective Function                                                         |

| 3.2.2 Monomial Expressions of $g_m$ for Short-channel CMOS Devices               |

| 3.2.3 Monomial Expressions of the $g_{d0}$ for Short-channel CMOS Transistors 37 |

| 3.2.4 Dimensional Constraints                                                    |

| 3.2.5 Input Impedance                                                            |

| 3.2.6 Power Dissipation Constraint                                               |

| 3.2.7 Other Constraints                                                          |

| Chapter Four 41                                                                  |

| Application of Geometric Programming to 90 nm and 180 nm CMOS LNAs 41            |

| 4.1 Extraction of $\gamma$ , $\beta$ , and <i>c</i>                              |

| 4.2 Formulation of GP-compatible Objective Functions and Design Constraints 45   |

| 4.3 A MATLAB-based Software Package for Geometric Programming                    |

| 4.4 GP Optimization Design Results                                               |

| 4.5 Trade-off Analyses 55                                                        |

| 4.5.1 Effect of Input Circuit Quality Factor on the Design of LNAs               |

| 4.5.2 Effect of Drain Current and Operational Frequency on the Noise Figure 57   |

| Chapter Five61                                                                   |

| Conclusions and Future Work61                                                    |

| References                                                                       |

| Appendix A                                                                       |

| Appendix B                                                                       |

| Appendix C70                                                                     |

| Appendix D72                                                                     |

| D.1 Contribution of Input Source Resistance72                                    |

| D.2 Contribution of the Channel Thermal Noise Current                              |

|------------------------------------------------------------------------------------|

| D.3 Contribution of the Induced Gate Noise Current75                               |

| D.4 Contribution of the Output Resistance                                          |

| Appendix E                                                                         |

| Appendix F                                                                         |

| F.1 Derivations of $g_{d0}$ and $g_m$ for Long-channel Devices                     |

| F.2 Derivations of $g_{d0}$ and $g_m$ for Short-channel Devices                    |

| F.3 Calculations of Body Effect Factor <i>m</i>                                    |

| Appendix G                                                                         |

| G.1 MATLAB Script for Monomial Curve Fitting of the Transconductance $g_m$ 86      |

| G.2 MATLAB Script for Monomial Curve Fitting of the Output Conductance $g_{d0}$ 87 |

| Appendix H                                                                         |

| H.1 BSIM3 Model Card for 90 nm from Predictive Technology Model                    |

| H.2 BSIM3 Model Card for 180 nm from MOSIS92                                       |

| Appendix I                                                                         |

| Appendix J                                                                         |

| Appendix K                                                                         |

| Appendix L                                                                         |

| L.1 Effect of Input Circuit Quality Factor on the Design of LNAs                   |

| L.2 Effect of Input Circuit Quality Factor on the Noise Figure and Gate Width 99   |

| L.3 Effect of Drain Current and Operational Frequency on the Noise Figure 101      |

# List of Figures

| Figure 1.1: Common-source amplifier with resistive termination                                 | 3  |

|------------------------------------------------------------------------------------------------|----|

| Figure 1.2: Shunt-series feedback amplifier                                                    | 4  |

| Figure 1.3: Common-gate amplifier                                                              | 4  |

| Figure 1.4: Narrowband LNA with inductive source degeneration                                  | 5  |

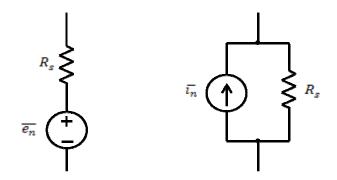

| Figure 2.1: Thermal noise models for resistors                                                 | 11 |

| Figure 2.2: Gradual channel approximation                                                      | 13 |

| Figure 2.3: Schematic representation of an n-channel MOSFET transistor                         | 14 |

| Figure 2.4: (a) Induced gate noise, (b) Standard representation, (c) Equivalent                |    |

| Thévenin representation                                                                        | 16 |

| Figure 2.5: Thermal noise comparison of different analytical noise models                      | 23 |

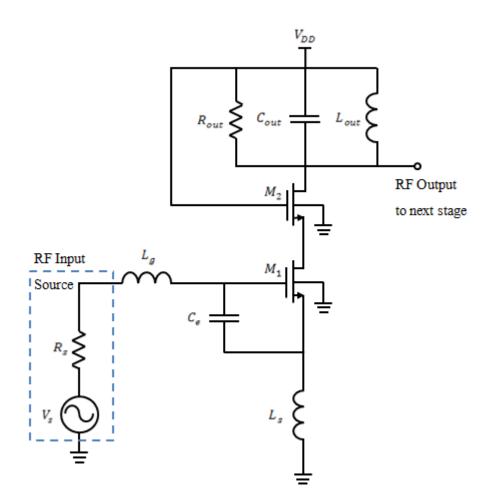

| Figure 3.1: Schematic of CMOS cascode LNA with inductive source degeneration                   | 27 |

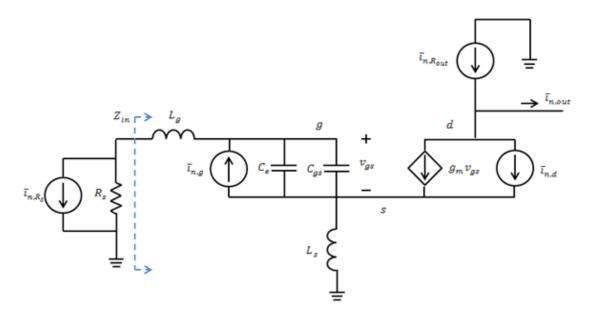

| Figure 3.2: Small-signal circuit for noise analysis                                            | 28 |

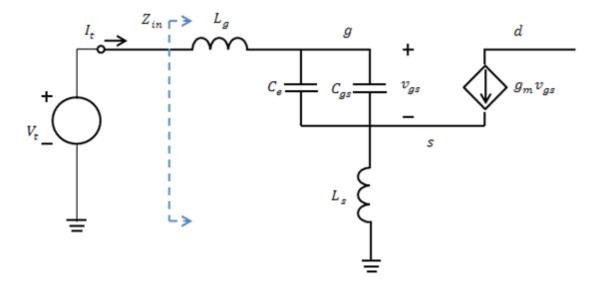

| Figure 3.3: Equivalent circuit for the input impedance calculation                             | 29 |

| Figure 3.4: Small-signal circuit of the calculation of output noise due to input source        |    |

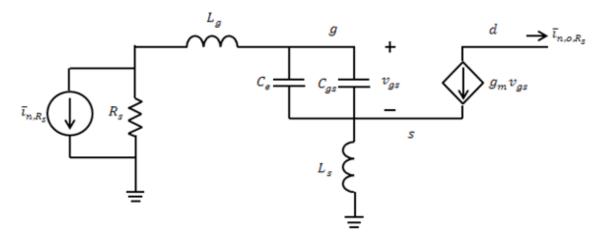

| resistance noise                                                                               | 33 |

| Figure 4.1: Experimental (markers) and model prediction (solid lines) results of the           |    |

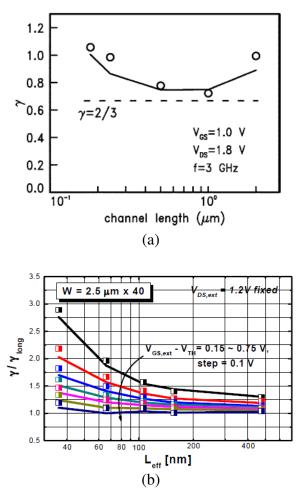

| white noise factor from (a) Scholten <i>et al.</i> and (b) Jeon <i>et al.</i>                  | 42 |

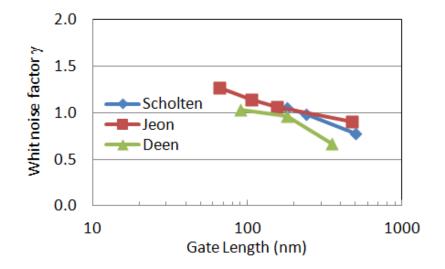

| Figure 4.2: White noise factor $\gamma$ versus gate length                                     | 43 |

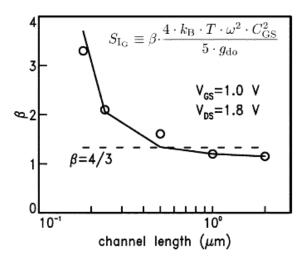

| Figure 4.3: Beta factor versus gate channel length                                             | 44 |

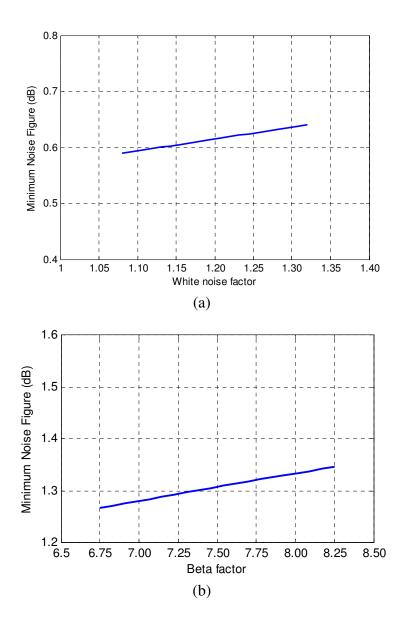

| Figure 4.4: (a) Variation of $\gamma$ factor on minimum noise figure, (b) Variation of $\beta$ |    |

| factor on minimum noise figure                                                                 | 45 |

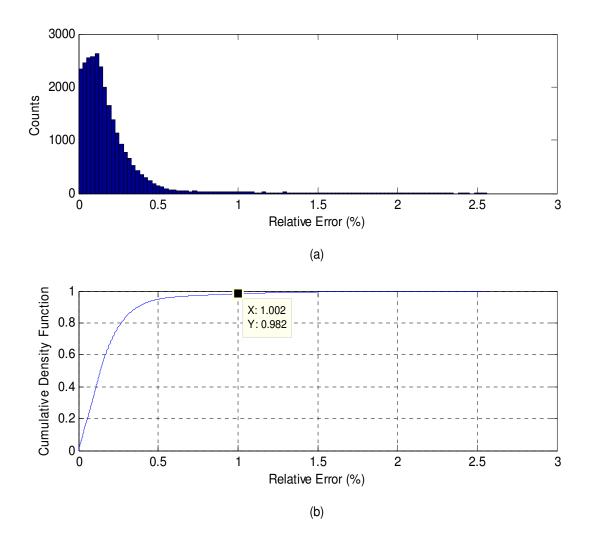

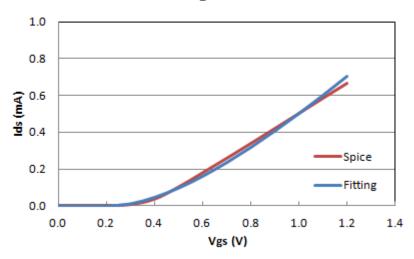

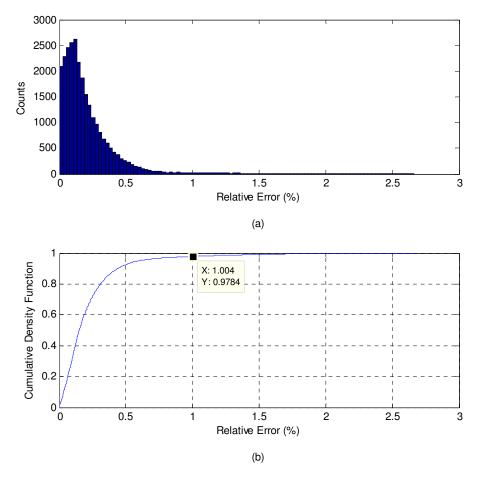

| Figure 4.5: (a) Histogram of relative error for curve fitting of $g_m$ for 90 nm,              |    |

| (b) Cumulative density function of relative error for curve fitting of $g_m$                   |    |

| for 90 nm                                                                                      | 48 |

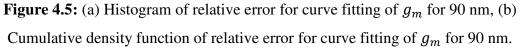

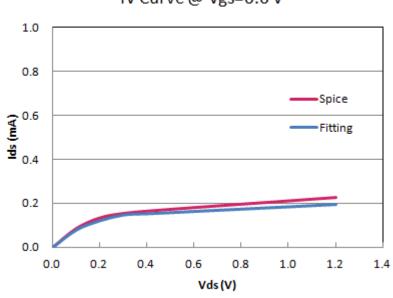

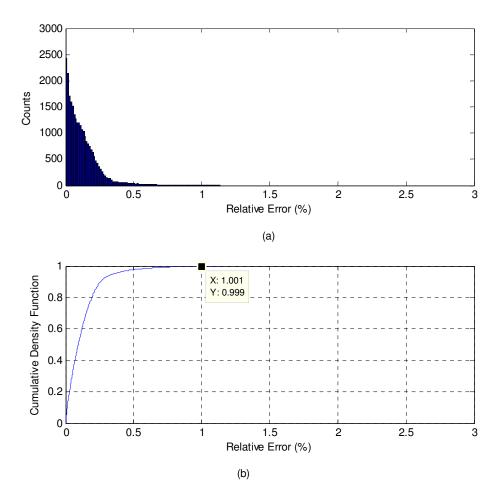

| Figure 4.6: (a) Histogram of relative error for curve fitting of $g_{d0}$ for 90 nm,           |    |

| (b) Cumulative density function of relative error for curve fitting of $g_{d0}$                |    |

| for 90 nm                                                                                 | 49 |  |  |  |

|-------------------------------------------------------------------------------------------|----|--|--|--|

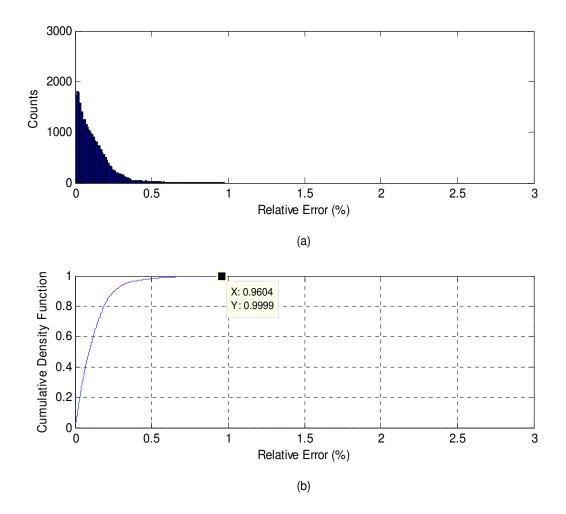

| Figure 4.7: Schematic of a CMOS LNA for 90 nm process                                     |    |  |  |  |

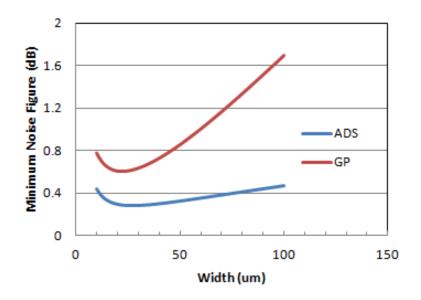

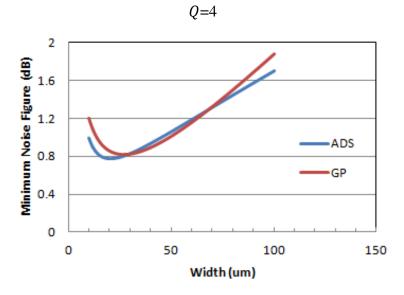

| Figure 4.8: Variation of noise figure with different gate width for 90 nm design          |    |  |  |  |

| when <i>Q</i> =4                                                                          | 53 |  |  |  |

| Figure 4.9: Variation of noise figure with different gate width for 180 nm design         |    |  |  |  |

| when Q=4                                                                                  | 53 |  |  |  |

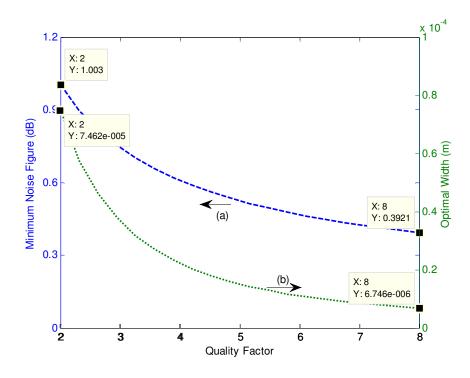

| Figure 4.10: (a) Variation of minimum noise figure with different quality factors for     |    |  |  |  |

| 90 nm design, (b) Variation of optimal width with different quality                       |    |  |  |  |

| factors for 90 nm design                                                                  | 54 |  |  |  |

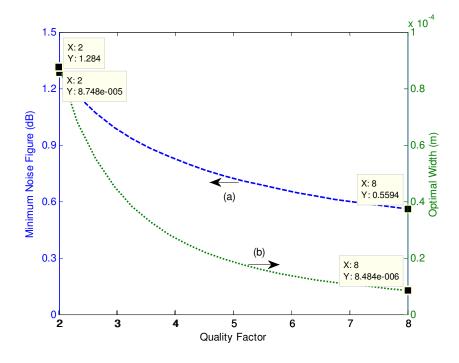

| Figure 4.11: (a) Variation of minimum noise figure with different quality factors for     |    |  |  |  |

| 180 nm design, (b) Variation of optimal width with different quality                      |    |  |  |  |

| factors for 180 nm design                                                                 | 54 |  |  |  |

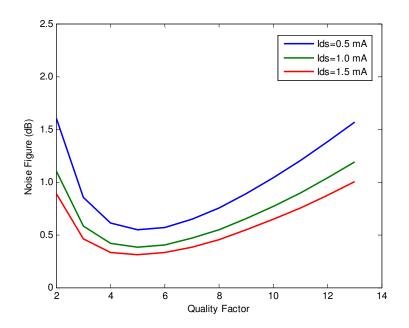

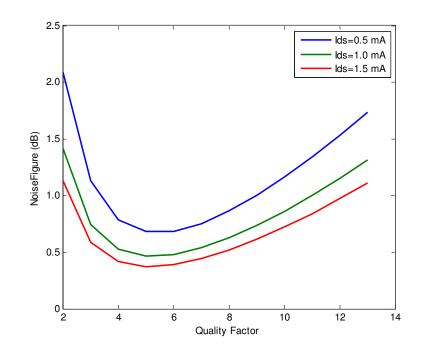

| Figure 4.12: Effect of input circuit quality factor on noise figure at different dc drain |    |  |  |  |

| current ( $W$ =20 µm, $L$ =90 nm)                                                         | 56 |  |  |  |

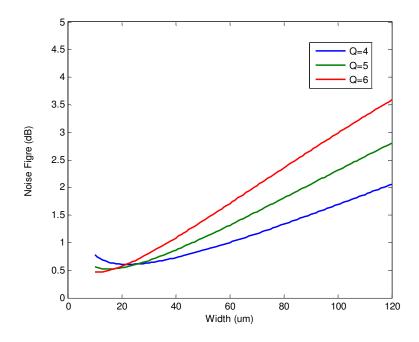

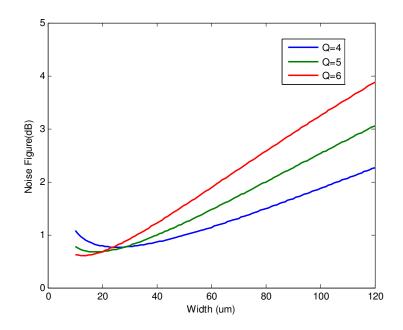

| Figure 4.13: Effect of channel width on the noise figure at different input circuit       |    |  |  |  |

| quality factors                                                                           | 56 |  |  |  |

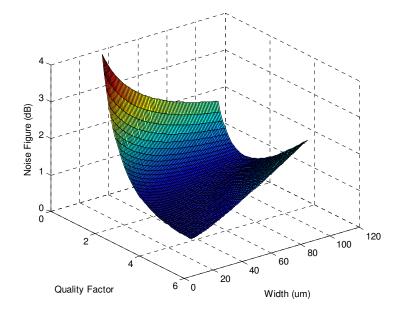

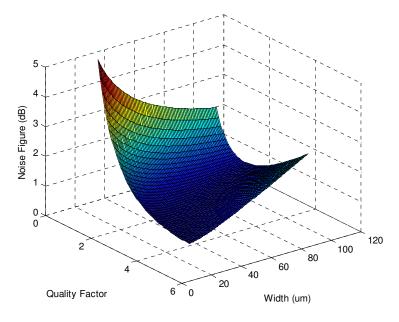

| Figure 4.14: Effect of input circuit quality factor and channel width on the noise        |    |  |  |  |

| figure in 3D                                                                              | 57 |  |  |  |

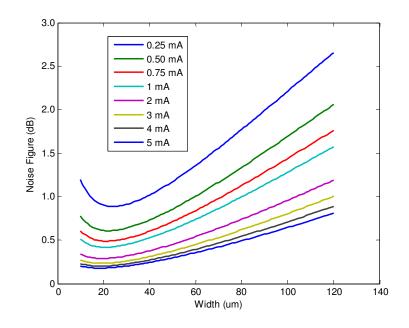

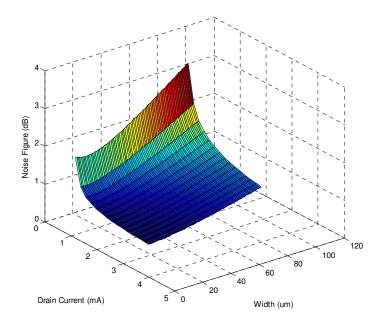

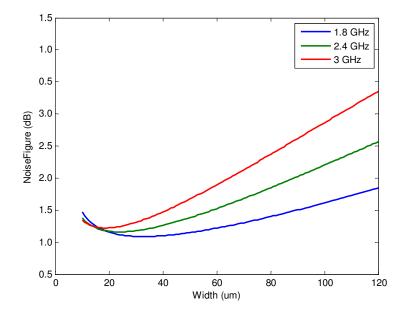

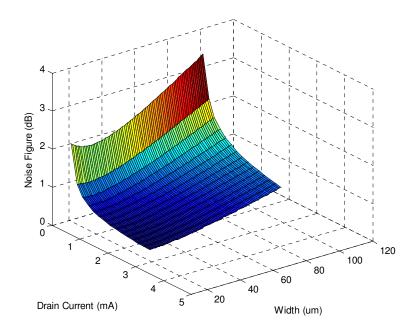

| Figure 4.15: Effect of channel width on the noise figure at different drain currents      | 58 |  |  |  |

| Figure 4.16: Effect of drain current and channel width on the noise figure in 3D          | 58 |  |  |  |

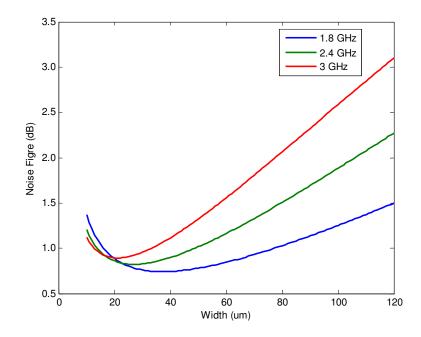

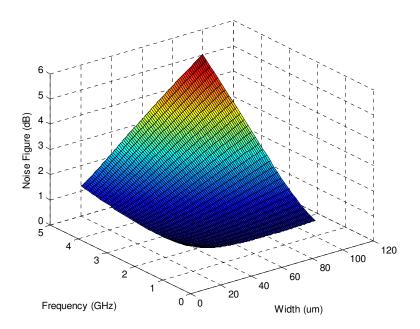

| Figure 4.17: Effect of channel width on the noise figure at different frequencies         | 59 |  |  |  |

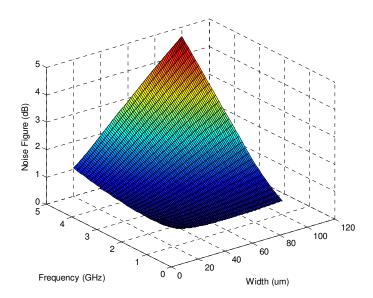

| Figure 4.18: Effect of operational frequency and channel width on the noise figure in     |    |  |  |  |

| 3D                                                                                        | 59 |  |  |  |

| Figure C-1: Equivalent circuit of input impedance calculation                             | 70 |  |  |  |

| Figure D-1: Small-signal circuit for calculating output noise due to the noise current    |    |  |  |  |

| of input source resistance                                                                | 72 |  |  |  |

| Figure D-2: Small-signal circuit for calculating output noise due to channel thermal      |    |  |  |  |

| noise current                                                                             | 73 |  |  |  |

| Figure D-3: Small-signal circuit for calculating output noise due to induced gate         |    |  |  |  |

| noise current                                                                             | 75 |  |  |  |

| Figure D-4: Small-signal circuit for calculating output noise due to the noise current    |    |  |  |  |

| of the output resistance                                                                  | 76  |

|-------------------------------------------------------------------------------------------|-----|

| Figure I-1: Curve fitting for estimation of $\theta$                                      | 94  |

| Figure I-2: Curve fitting for estimation of channel-length modulation parameter $\lambda$ | 94  |

| Figure J-1: (a) Histogram of relative error for curve fitting of $g_m$ for 180 nm,        |     |

| (b) Cumulative density function of relative error for curve fitting of $g_m$              |     |

| for 180 nm                                                                                | 95  |

| Figure J-2: (a) Histogram of relative error for curve fitting of $g_{d0}$ for 180 nm,     |     |

| (b) Cumulative density function of relative error for curve fitting                       |     |

| of $g_{d0}$ for 180 nm                                                                    | 96  |

| Figure L-1: Effect of input circuit quality factor on the noise figure at different dc    |     |

| drain current ( $W$ =20 µm, $L$ =180 nm)                                                  | 99  |

| Figure L-2: Effect of channel width on the noise figure at different input circuit        |     |

| quality factors                                                                           | 100 |

| Figure L-3: Effect of input circuit quality factor and channel width on the noise         |     |

| figure in 3D                                                                              | 100 |

| Figure L-4: Effect of channel width on the noise figure at different drain currents       | 101 |

| Figure L-5: Effect of drain current and channel width on the noise figure in 3D           | 101 |

| Figure L-6: Effect of channel width on the noise figure at different frequencies          | 102 |

| Figure L-7: Effect of operational frequency and channel width on the noise figure in      |     |

| 3D                                                                                        | 102 |

## List of Tables

### Abstract

## OPTIMIZATION OF SHORT-CHANNEL RF CMOS LOW NOISE AMPLIFIERS BY GEOMETRIC PROGRAMMING

Xiaoyu Jin Thesis Chair: David H. K. Hoe, Ph.D. The University of Texas at Tyler May 2012

Geometric programming (GP) is an optimization method to produce globally optimal circuit parameters with high computational efficiency. Such a method has been applied to short-channel (90 nm and 180 nm) CMOS Low Noise Amplifiers (LNAs) with common-source inductive degeneration to obtain optimal design parameters by minimizing the noise figure. An extensive survey of analytical models and experimental results reported in the literature was carried out to quantify the issue of excessive thermal noise for short-channel MOSFETs. Geometric programming compatible functions have been determined to calculate the noise figure of short-channel CMOS devices by taking into consideration channel-length modulation and velocity saturation effects.

Optimal design parameters (e.g., channel width and noise figure) from geometric programming optimization are validated by comparing them with numerical simulations using Agilent's Advanced Design Systems (ADS) software. Furthermore, tradeoff analyses have been performed to examine the influence of various design parameters such as quality factors and drain current on the optimization of CMOS LNAs. In particular, it is found that the optimal input quality factor is slightly higher for LNAs using short-channel devices compared with the analysis reported for long-channel designs. With the continuous downscaling of CMOS technologies nowadays, geometric programming offers high performance advantages in the optimal design of short-channel CMOS LNAs.

## Chapter One Introduction

Radio frequency (RF) devices receive and transmit signals from 3 kHz to 300 GHz, covering a variety of wireless applications [1]. For example, broadcasting at radio frequencies has been established on technique for almost a century. Cellular phones have been used for decades. New generations of cellular phones (4G) have just been available for a couple of years. Moreover, wireless local area network (Wi-Fi) is gaining popularity for laptop, tablet and smartphone users, since Wi-Fi can provide access to the Internet via an access point (hotspot). Campus-wide Wi-Fi and city-wide Wi-Fi are further providing convenience for these users. Other applications of RF include global positioning system (GPS), phased array RF systems, radio frequency identification devices (RFIDs) and smart handheld devices [2]. Since wireless communication enables voice, data, image and video to be transferred to anywhere almost instantaneously, the impact of RF on people's daily lives has become significant.

The design of RF applications involves an important component known as the low-noise amplifier (LNA). The LNA is an essential component located at the first stage of a radio receiver circuit. The major function of an LNA is to amplify very weak signals (e.g., electrical signals received by an antenna) while adding as little noise and distortion as possible [3]. This is particularly true for applications in wireless and mobile communications with high frequency receivers. The optimization of low-noise amplifiers will minimize noise under power constraints, which is extremely important for mobile communications.

#### 1.1 RF CMOS

Since there is a wide range of applications for RF, the implementation of LNAs depends on the specifics of each application. Historically, bipolar transistors have been

used for the design of high-power amplifiers in audio equipment and radio receivers [4]. Recently, submicron CMOS has become viable for the implementation of LNAs in wireless communication (e.g., cellular phones, Wi-Fi) due to its high integration feature and improvements in unity-gain frequency ( $\omega_T$ ) of MOS devices [5]. Four commonly used topologies are briefly described to satisfy the design requirements of low-noise amplifiers.

#### 1.1.1 Bipolar vs. CMOS for RF Circuits

Classic devices in RF receivers consist of bipolar transistors and CMOS. For RF receiver applications, an optimal solution can be achieved by taking considerations of gain, noise, linearity, power consumption and cost.

One of the semiconductor devices commonly used for amplification is a bipolar transistor. Two major types of bipolar transistors are PNP and NPN. Bipolar transistors have pros and cons compared with CMOS. Bipolar devices can switch signals at high speeds, and can be manufactured to handle large currents so that they can serve as high-power amplifiers in audio equipment and in radio receivers. However, bipolar devices are not especially effective for low power design and are not suitable for high-integration applications, especially when integration with CMOS digital circuits is required.

The advantages of CMOS implementations for RF circuits are high integration density, low cost and exceptional speed performance when the devices are implemented in nanoscale technologies [2]. With the increasing popularity of system-on-chip (SoC) designs for increasing integration density and reducing system cost, CMOS implementations are very attractive for the realization of mixed-signal and RF designs [6]. Significant improvements for transit time and maximum oscillation frequency have been achieved when the CMOS gate length is scaled below 100 nm [7]. CMOS technology remains the major player for the market of low cost and less performancedemanding applications such as GPS, Bluetooth and Wi-Fi [2].

The shortcomings of CMOS in RF circuits are that the noise/gain performance and breakdown voltage of MOSFETs are not as good as that of bipolar devices. Nevertheless, such limitations can be overcome with appropriate circuit architectures.

2

Consequently, CMOS RF circuits have been used in 3G and 4G cellular applications, such as GSM/GPRS/EDGE [8].

#### 1.1.2 RF CMOS LNA Topologies

The design of RF CMOS low-noise amplifiers typically involves a critical requirement to provide a specific impedance (i.e., 50  $\Omega$ ) to the input source. Several topologies are available [3], including resistive termination, shunt-series feedback,  $1/g_m$  termination, and inductive degeneration.

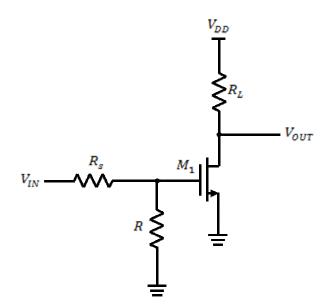

In resistive termination topology, a 50  $\Omega$  resistor (*R*) is simply placed across the input terminals of a common-source amplifier (Figure 1.1) with a source resistance  $R_s$  and an output resistance  $R_L$ . However, this additional resistor introduces thermal noise and attenuates the signal before the transistor, resulting in unacceptably high noise.

Figure 1.1: Common-source amplifier with resistive termination

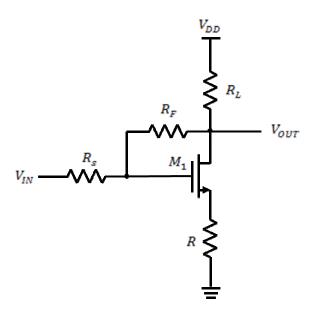

In a shunt-series feedback topology (Figure 1.2), the resistor R does not cause attenuation of signals before amplification. It is expected that the noise figure in a shuntseries feedback amplifier is an improvement over that of a resistive termination amplifier. On the other hand, the resistor feedback network remains a source of thermal noise. Consequently, the noise performance of this topology is still not optimum.

Figure 1.2: Shunt-series feedback amplifier

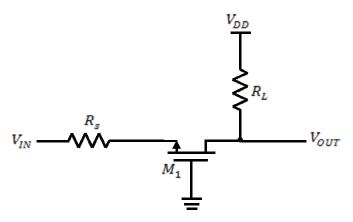

The common-gate topology  $(1/g_m)$  is another circuit implementing a resistive input impedance (Figure 1.3). One of characteristics of the common-gate topology is that the resistance looking into the source terminal equals  $1/g_m$ .

Figure 1.3: Common-gate amplifier

The aforementioned topologies do not have attractive noise performance due to the presence of a noisy resistance along the signal path. If a resistive input impedance can be provided without using an actual resistor, the noise performance of amplifiers can be significantly improved.

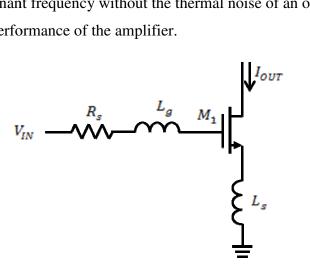

To create a resistive input impedance without the noise of real resistors, an inductive source degeneration topology (Figure 1.4) is commonly used. The key point of

this topology is that the input impedance has a resistive component. Conceptually this happens because a phase lag occurs at the potential of the bottom plate of the gate, which varies along the channel and depends on the signal at the gate. The additions of the source inductor  $L_s$  and the gate inductor  $L_g$  enhance this effect and provide control over the value of the input impedance [3]. Therefore, this topology provides a resistive input impedance at the resonant frequency without the thermal noise of an ordinary resistor and degrading the noise performance of the amplifier.

Figure 1.4: Narrowband LNA with inductive source degeneration

#### **1.2 Submicron CMOS Technology**

In the past three decades, the downscaling of CMOS technologies has continued to change the speed, complexity, and power consumption of many applications [9]. The introduction of submicron CMOS technology has posed new challenges to the design of analog circuits such as RF low-noise amplifiers due to various submicron effects [6].

#### **1.2.1 Submicron Effects**

The evolution of CMOS from the micron level to the submicron level contributes to new challenges in the design of analog circuits [10]. The first concern with downscaling of CMOS technology is the reduction in power supply voltage. Another problem is short-channel effects, such as velocity saturation and channel-length modulation, which have posed more difficulties for the modeling of short-channel MOSFETs.

Decreases in power supply voltage may result in lower performance of analog circuits. The drop of power supply voltages from 5 V to 1.2 V in submicron CMOS

technology may not pose serious problems in the design of analog circuits. However, further reduction of power supply voltages may cause technical challenges. For example, the reduction of power supply voltages results in analog circuits with lower performance since biasing at lower voltages causes the degradation of transistor properties [10]. Another problem with the reduction of power supply voltages is the loss of headroom required to employ cascoded load devices for high-gain amplifiers. This can cause a significant reduction in the output swing of the CMOS amplifier resulting in an amplifier with degraded performance [10].

When device geometries shrink down to the submicron level and beyond, various second order effects become prominent [3]. The velocity saturation of the carriers in the channel is a prime concern. Velocity saturation occurs when the electric field in the channel reaches a critical value which causes the carrier velocities to reach a maximum value. This means the drain current saturates sooner for short-channel devices when compared with long-channel devices. Channel-length modulation is another concern. For long-channel devices, a constant saturation drain current is assumed. However, this is not the case for short-channel devices. The extent of the depletion region close to the drain increases with the increasing drain to source voltage [3]. Drain current increases with the increasing drain to source voltage for short-channel devices. Thus, the modeling of MOSFETs needs to be reconsidered for short-channel devices.

#### 1.2.2 Effect of CMOS Downscaling on Noise Model Analysis

The continuous downscaling of CMOS technologies requires that accurate modeling of noise be established when applied to the design of RF CMOS low-noise amplifiers. Thermal noise is the dominant source of noise for CMOS circuits at RF frequencies. The classical theory of thermal noise is still valid at the submicron level if short-channel effects are properly taken into account. Velocity saturation, channel-length modulation and hot carrier effects need special attention for submicron CMOS technologies.

The effect of velocity saturation on the noise performance of CMOS transistors becomes noticeable when the size of CMOS device scales down to the submicron level. Due to scattering by high-energy phonons, carrier velocities saturate and stop increasing with increasing electrical field. The electron drift velocity finally saturates at a value of about  $10^5$  m/s when the electrical field reaches about  $10^6$  V/m in CMOS devices [3]. The drain current for calculating long-channel devices can be modified to reflect the effect of velocity saturation in short-channel devices. Details of such modification are available in the literature [11]. The drain current of short-channel devices becomes saturated and has a linear relationship, rather than a square-law relationship, with the gate-source voltage. Thus, thermal noise due to the drain current can be appropriately revised for short-channel devices by taking into consideration the effects of velocity saturation.

#### 1.3 Optimization in Design of RF CMOS LNA

Wireless and mobile communication systems today are very complex and the time to market requirements create a short turnaround time, especially in today's competitive marketplace. Simulation becomes a critical tool to discover and correct problems before fabrication. Without such a tool, refabrication of an integrated circuit (IC) due to design miscalculations is very expensive and time consuming. Optimization techniques are a central component for the simulation tool to find the optimum design parameters to achieve the best performance. The optimization of CMOS LNA designs focuses on minimizing the noise figure in CMOS devices for a set of specifics, such as power dissipation, and transistor dimensions.

#### **1.3.1 Optimization Methods**

The design parameters in LNAs consist of transistor dimensions (e.g., transistor gate length L and gate width W) and other passive component values such as inductance and capacitance. The objective of optimization methods for low-noise amplifiers is to minimize the noise figure while optimizing other performance parameters. Various approaches are available for achieve this design optimization.

General-purpose classical optimization methods are extensively used in the computer aided design of analog circuits [12]. These classical methods include steepest descent, sequential quadratic programming, and Lagrange multiplier methods. The advantage of these classical methods is the ability to handle a large variety of problems. The disadvantage of these classical methods is that only a locally optimal design is found. The locally optimal design does not guarantee the design is the best design available

globally. As an analogy, someone walking in the mountains may see only the nearest peak, not the highest peak in the mountain range.

Another approach for design optimization is based on knowledge and expert systems [12]. The advantage is that it can be used anywhere with even fewer limitations than the classical optimization methods. The disadvantages of this approach include a locally optimum design, no detection of feasibility, and substantial human intervention.

Global optimization methods have the ability to find the globally optimal design and have been widely used in the computer aided design of analog circuits [13]. Two well-known methods of global optimization are branch and bound and simulated annealing. The advantages of global optimization methods are unambiguously achieving a global optimum and handling a wide variety of performance measures and objectives. The disadvantage is that global optimization methods can be very slow.

Convex optimization and geometric programming methods have started to gain attention in the computer aided design of analog circuits in recent years [13]. The advantages of convex optimization are efficiency of solving large problems with thousands of variables and tens of thousands of constraints, globally optimum solutions, and unambiguous detection of infeasibility. The disadvantage of convex optimization is that there are more limitations on the types of problems to be solved than the aforementioned methods for optimization. However, this is a compromise to achieve efficiency in solving large problems.

#### **1.3.2 Geometric Programming**

A geometric programming is an optimization problem of the form with the objective function as posynomial function and constraints of posynomial inequality and monomial equality. All design parameters are non-negative variables. A geometric programming problem can be converted to a convex optimization problem.

Geometric programming has been used in many problems in analog circuit and digital design [14]. For example, component values and transistor dimensions of CMOS operational amplifiers have been optimized by formulating geometric programming to meet the competing performance measures such as power, open-loop gain and bandwidth

8

[13]. Additional applications of geometric programming include RF circuit design [15, 16].

More importantly, geometric programming has recently been utilized for the design of RF CMOS low-noise amplifiers [17]. A low-noise amplifier with a topology of source inductive degeneration [18] using standard 0.35  $\mu$ m CMOS process was optimized with the noise figure as the objective function and design constraints such as input circuit quality factor and input impedance matching. Globally optimum solutions were obtained with an extremely small computational cost.

This implementation of geometric programming focused on the intermediate channel length regime of the CMOS process. With the downscaling of CMOS technologies to submicron and nanoscale levels, the complexity of noise models for short channels poses challenges to formulate the objective function and design constraints in the form of geometric programming.

#### **1.4 Objective of the Thesis**

The objective of this thesis is to obtain the globally optimal design of RF CMOS low-noise amplifiers with short-channel devices by implementing geometric programming for minimizing the noise figure and for satisfying design constraints such as input circuit quality factor, power consumption, and input impedance matching.

A framework for noise modeling of short-channel RF CMOS transistors is first established by taking into consideration the velocity saturation effect. Then, the objective function of the noise figure is formulated in the form of a posynomial function and design constraints are described in the form of a posynomial inequality and monomial equality. After that, geometric programming is applied to obtain the globally-optimal solution. Design parameters from the optimal solution are compared with simulation results. Finally, the implication of geometric programming for short-channel CMOS designs is discussed and future work in this area is described.

# Chapter Two Noise Modeling in CMOS

In this chapter, major thermal noise models for MOSFETs in the literature are discussed, taking short-channel effects into consideration, such as velocity saturation, channel-length modulation, and the effect of mobility degradation. Most of these noise models are good for short-channel devices. A noise model suitable for geometric programming has been chosen for this study.

### 2.1 RF Noise

In general, noise means any unwanted signal. It is the opposite phrase to signal in electronics. Therefore, it can be defined as "everything except the desired signal" [3]. There are noise sources called artificial noise that can be reduced or removed using a good shielding system. An example is the interference between two adjacent cables transmitting voice or data information. On the other hand, noise sources that are inherent and irreducible in the system or devices are known as fundamental noise, for example, the snowy pictures in analog TV sets. The mystery of fundamental noise was unfolded by a series of papers written by H. Nyquist, J.B. Johnson and W. Schottky [19-21] with explanations of the origins of different noise sources and numerous analyses. In general, there are several types of fundamental noise.

In MOSFETs, thermal noise and shot noise are the major noise sources. Flicker noise is known for its 1/f characteristic, which suggests that the power spectral density of flicker noise increases as frequency decreases. Therefore, flicker noise is insignificant in RF noise modeling but it is dominant at the low frequency range. Generationrecombination noise can be generally neglected since it is even much smaller than flicker noise. In RF MOSFET transistors, shot noise plays the main role in the noise characteristics only when the device is in the subthreshold region [3]. For low-noise

10

amplifier design, transistors are operating in the saturation region where shot noise can be neglected. Therefore, thermal noise is the focus for the noise analysis in this thesis.

#### 2.2 Thermal Noise

Thermal noise, also known as Johnson-Nyquist noise, can be considered as a phenomenon of Brownian motion [21]. Thermally-excited carriers (usually electrons) generate a randomly varying current in a conductor. Because of the randomness of the noise process, it is impossible and meaningless to identify an exact value for the noise voltage at a particular time. In order to characterize the thermal noise, statistical measures are commonly used in noise analysis. Due to the thermal origin, the noise mean square value of a conductor is dependent on the absolute temperature [19]. Therefore, the thermal noise mean square value for a resistor is determined only by the temperature T and electrical resistance R at thermal equilibrium [3]:

$$\overline{e_n^2} = S_{e_n} \Delta f = 4kTR\Delta f \tag{2.1}$$

$$\overline{\iota_n^2} = \frac{\overline{e_n^2}}{R^2} = \frac{4kTR\Delta f}{R^2} = \frac{4kT\Delta f}{R} = S_{i_n}\Delta f$$

(2.2)

where  $S_{e_n}$  and  $S_{i_n}$  are the spectral densities of  $\overline{e_n^2}$  and  $\overline{\iota_n^2}$  for 1  $\Omega$  resistor respectively, k is Boltzmann's constant (1.38×10<sup>-23</sup> V·C/K),  $\Delta f$  is the noise bandwidth in Hertz, and T is the absolute temperature in Kelvin. Thermal noise is also called white noise, because its mean square value is independent of frequency [22], as it is shown in aforementioned formulas. The two noise models for a resistor are depicted in Figure 2.1.

Figure 2.1: Thermal noise models for resistors [3]

The polarity signs for the noise voltage source and the noise current source do not indicate the noise has a particular polarity because noise has a zero mean voltage. They are simply references.

#### 2.2.1 Thermal Noise in MOSFETs

MOSFETs behave basically as voltage-controlled resistors. Therefore, thermal noise is present in MOSFETs, which is the result of random potential fluctuations in the channel [23]. These fluctuations in the channel lead to one source of thermal noise, which is the drain current noise. In addition, through the oxide capacitance of the gate terminal, the fluctuations are introduced to the gate and cause a gate noise current, also known as induced gate thermal noise. The drain current noise and the gate noise are correlated because they both are agitated by the thermal noise sources in the channel. Since noise characteristics are one of the main concerns in the LNA design, it is very important for circuit designers to be able to predict and calculate the noise of MOS devices with reasonable accuracy and also to recognize the noise dependence on the geometry and biasing conditions of the device. Modeling of the thermal noise generated in the channel of MOSFETs started a few decades ago and much research on the compact modeling of thermal noise has been done [24].

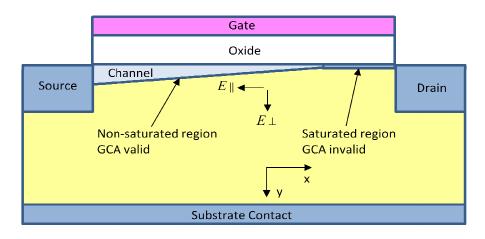

#### 2.2.2 Analytical Compact Thermal Noise Models

The fundamental assumption for most analytical and semi analytical MOSFET thermal noise models is the so-called gradual channel approximation (GCA). For the ideal two-terminal MOS device, the charge density profile is defined by a one-dimensional Poisson's equation, as it is described in the structure of a MOS capacitor. As for three-terminal or four-terminal MOSFET devices, they generally pose a two-dimensional electrostatic problem due to the geometric effects and the drain-source bias [25]. This approximation states that the rate of variation of the lateral field within the channel  $(dE_{\parallel}/dx)$  is much smaller than the rate of variation of the vertical field  $(dE_{\perp}/dy)$ , as illustrated in Figure 2.2, and the channel potential is a gradually changing function of position along the channel from the drain to the source, which varies very little along the channel over a distance of the order of the gate oxide insulator thickness [11, 25, 26].

The GCA is valid for long-channel MOSFETs, where the aspect ratio between the gate length and the vertical distance of the space charge region from the gate electrode is large. Unfortunately, if the MOSFET is biased in strong inversion, which is in the saturation region, the GCA always becomes invalid beyond the pinch-off region due to the large lateral field gradient that develops in this region [22, 25]. Under the assumption of the GCA, a couple of noise models have been developed for long-channel MOSFETs.

Figure 2.2: Gradual channel approximation [25]

#### 2.2.2.1 The Model of Klaassen-Prins

Klaassen and Prins [27] were among the first researchers to develop equations for calculating the power spectral density of the thermal noise of a MOSFET. Their work is based on the relationship between the channel current and the local channel conductivity of the MOSFET. It has been widely used to calculate the channel thermal noise for long-channel MOSFETs [3, 22, 23]. The drain current of a MOSFET can be expressed in the following equation [23, 27] as

$$I_d = g(V(x)) \cdot \frac{dV(x)}{dx}$$

(2.3)

where V(x) is the channel potential at x, dV(x) is the dc voltage difference in the electron quasi-Fermi level in the inversion layer and the hole quasi-Fermi level in the substrate at position x (e.g. n-channel), and g is the local channel conductivity. A schematic representation is shown in Figure 2.3. For a simple long-channel MOSFET using the gradual channel approximation [23], the following can be written,

$$g(V(x)) = \mu C_{ox} W(V_{od} - V(x))$$

(2.4)

where  $V_{od}$  is the overdrive voltage and it equals  $V_{gs} - V_{th}$  ( $V_{gs}$  is the gate-source voltage,  $V_{th}$  is the threshold voltage), V(x) is the channel potential at x, W is the width of the MOSFET,  $\mu$  is the mobility, and  $C_{ox}$  is the oxide capacitance per unit area. Assuming a differential segment  $\Delta x$  of the channel, a small noise voltage contribution v(x) across the segment  $\Delta x$  is observed, which is added to the dc voltage V(x). This voltage can cause noise in the drain current, which leads to a change in the dc current through the MOSFET. There are some assumptions throughout the following analysis. First, noise sources of the different channel segments are local and not correlated. Second, the charge carriers are in thermal equilibrium. The boundary conditions of the small voltage contribution v(x) are  $v(x)|_{x=0,L} = 0$  [23, 27]. Therefore, the Klaassen-Prins equation for the power spectral density  $S_{id}$  of thermal noise of a long-channel MOSFET is

$$S_{i_d} = \frac{4kT}{L^2 I_d} \int_0^{V_{ds}} g^2(V) \cdot dV$$

(2.5)

where  $I_d$  is the drain current, *L* is the gate length and g(V) is the local output conductivity. This equation can be developed into another commonly used expression, which is the so-called white noise gamma factor formula discussed in the following section. The details for this derivation can be found in Appendix A.

Figure 2.3: Schematic representation of an n-channel MOSFET transistor [27]

#### 2.2.2.2 The Model of Albert van der Ziel

After Klaassen and Prins introduced their model for channel thermal noise in MOSFETs, Albert van der Ziel included hot electron effects in his model by substituting the lattice temperature with carrier temperature,  $T_e(x)$ , and modified the model to [23]

$$S_{i_d} = \frac{4kT}{L^2 I_d} \int_0^{V_{ds}} \frac{T_e(x)}{T} g^2(V) \cdot dV$$

(2.6)

Once  $\frac{T_e(x)}{T}$  and g(V) are known,  $S_{i_d}$  can be easily calculated. In order to treat a MOSFET as resistor element, van der Ziel presented a convenient expression [23]:

$$S_{i_d} = 4kT\gamma g_{d0} \tag{2.7}$$

where

$$\gamma = \frac{1}{g_0 I_d L} \int_0^{V_{ds}} \frac{T_e(x)}{T} g^2(V) \cdot dV$$

(2.8)

In Eq. (2.8),  $g_0$  is the channel conductance per unit length at the source and  $g_{d0}$  is the channel conductance at zero drain bias. The parameter  $\gamma$  is often called the white noise gamma factor and the expression in Eq. (2.8) is commonly used to calculate and demonstrate the channel thermal noise in long-channel MOSFETs and the excess channel thermal noise in short-channel transistors. The parameter  $\gamma$  relates the thermal noise power spectral density with the output conductance at different bias conditions. However, it is very practical and continues to be used to allow experimental or theoretical results to be compared from different research groups [28]. The value of  $\gamma$  is unity for zero drain bias, in long-channel devices, and decreases toward 2/3 in saturation.

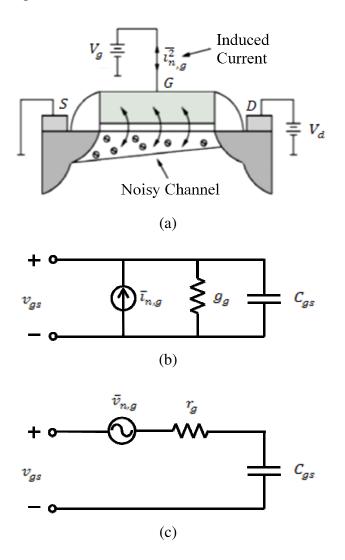

In addition, a MOSFET can be described as an RC network at high frequencies, with the oxide capacitance of the gate terminal and the resistance due to the channel itself. The fluctuations in the channel are introduced to the gate and cause a gate noise current, also known as induced gate thermal noise (Figure 2.4 (a)). Van der Ziel has shown the induced gate noise can be expressed as [23]

$$S_{i_g} = 4kT\beta g_g \tag{2.9}$$

where  $\beta$  is basically independent of the substrate conductivity, and its value is 4/3 in the saturation region for long-channel MOSFETs. The conductance  $g_g$  has the form as

$$g_g = \frac{\omega^2 C_{gs}^2}{5g_{d0}}$$

(2.10)

In Eq. (2.10), the intrinsic gate capacitance of transistor  $C_{gs} = \frac{2}{3}C_{ox}WL$  where  $C_{ox}$  is the oxide capacitance per unit area, W is the channel width and L is the channel length. A circuit model for gate noise has been illustrated in [3], which describes the induced gate noise in the form of Eq. (2.9).

Figure 2.4: (a) Induced gate noise, (b) Standard representation, (c) Equivalent Thévenin representation [29]

In the circuit model representation, the conductance  $g_g$  is connected between the gate and source shunted by the gate noise current. An equivalent Thévenin representation seems more intuitive with  $r_g = \frac{1}{5g_{d0}}$  [3]. As shown in Eq. (2.10), the conductance  $g_g$  increases with frequency, indicating that the induced gate noise can dominate at radio frequencies. The conductance  $g_g$  is also proportional to the square of  $C_{gs}$ , so a small value of  $C_{gs}$  will favor a lower induced gate noise. This is discussed further in the following chapter.

Since the induced gate noise is correlated with the drain thermal noise, the correlation coefficient is defined as [23]

$$c = \frac{\overline{\iota_{ng} \cdot \iota_{nd}^*}}{\sqrt{\overline{\iota_{ng}^2} \cdot \overline{\iota_{nd}^2}}}$$

(2.11)

where  $\overline{\iota_{ng} \cdot \iota_{nd}^*}$  is the spectrum of the crosscorrelation of the drain thermal noise and the induced gate noise. The complex correlation coefficient *c* is theoretically 0.395j for long-channel MOSFETs (see Appendix B).

#### 2.2.2.3 The Model of Tsividis

Another frequently used equation for the channel thermal noise proposed by Tsividis is given by [22]

$$S_{i_d} = 4kT \frac{\mu}{L^2} (-Q_{inv})$$

(2.12)

where  $\mu$  is the carrier mobility and  $Q_{inv}$  is the total inversion layer charge.

The aforementioned models are developed and valid for long-channel MOSFETs, where short-channel effects were not taken into account. The short-channel effects, such as velocity saturation, enhanced channel-length modulation and mobility degradation, are basically caused by the high longitudinal field due to the short gate length of the MOSFET. Meanwhile, the GCA assumption becomes invalid due to the velocity saturation for short-channel MOSFETs. Additionally, considerable increase in the drain current noise of short-channel MOSFETs has been observed and becomes significant while MOSFETs geometries shrink down to the submicron level [11, 22, 24, 25, 30, 31]. Therefore, several models have been developed to explain this enhanced thermal noise present in short-channel MOSFETs.

#### 2.2.2.4 The Model of Scholten et al.

In the Klaassen-Prins model shown in Eq. (2.5), *L* is the MOSFET gate length and *g* is the local channel conductivity. This model is suitable for long-channel MOSFETs. Unfortunately, for submicron channel lengths, short-channel effects become more significant. Scholten and his colleagues developed a nonquasi-static RF MOSFET model based on the concept of channel segmentation [22, 30]. This was implemented in the so-called MOS Model 11 [32], where every channel segment is taken into account.

An improved Klaassen-Prins model including the effect of channel-length modulation and the effect of velocity saturation is presented in [28, 30, 33]. The noise power spectral density is

$$S_{i_d} = \frac{4kT}{L_{elec}^2 I_d} \int_0^{V_{ds}} g_c^2(V) \cdot dV$$

(2.13)

where  $L_{elec}$  is the electrical channel length of the MOSFET, replacing the effective channel length  $L_{eff}$  in the original Klaassen-Prins expression. The parameter  $L_{elec}$  is defined as  $L_{elec} = L_{eff} - \Delta L$  where  $\Delta L$  is the length of the velocity saturated region. The parameter  $g_c$  is the revised conductivity taking velocity saturation into consideration. The noise contribution of the pinch-off region is assumed to be negligible due to insignificant dependence of channel thermal noise on the drain-to-source voltage beyond the saturation voltage [30].

#### 2.2.2.5 The Model of Han et al.

In Han's approach [31, 34], the effect of velocity saturation and the effect of carrier heating are taken into account. In long-channel MOSFETs, the carrier mobility is considered independent of the bias conditions and is usually modeled as a constant. However, the carrier mobility in short-channel MOSFETs is degraded due to the high lateral electric field from drain to source [11] and is thus dependent on the bias conditions. The impedance field method [35] was used to recalculate the thermal noise for short-channel MOSFETs. The drain current of a MOSFET with the effect of mobility degradation is given in [34] as

$$I_d = g_0(V) \frac{\left(\frac{dV}{dx}\right)}{1 + \left(\frac{dV}{dx}\right)/E_C}$$

(2.14)

where the local channel conductance  $g_0(V) = \mu_{eff} W C_{ox}(V_{od} - \alpha V)$ . The parameter  $E_C = 2v_{sat}/\mu_{eff}$  is the critical field at which velocity saturation occurs,  $v_{sat}$  is the saturation velocity of carriers,  $\mu_{eff}$  is the effective mobility,  $C_{ox}$  is the gate oxide capacitance per unit area,  $V_{od}$  is the gate overdrive voltage  $(V_{gs} - V_{th})$ , V is the source-referenced channel potential at x, and  $\alpha$  is a coefficient describing the bulk-charge effect. The bulk-charge effect is the variation of threshold voltage caused by non-uniform channel depletion and the dependence of the threshold voltage on the channel potential. The impact of the carriers in the velocity saturation region on the drain thermal noise current is ignored in this analysis. Applying a similar procedure and method as Scholten, the channel noise of the MOSFET takes the form of

$$S_{i_d} = \frac{4kT}{L_{elec}^2 I_d (1 + \frac{V_{ds}}{L_{elec}E_c})^2} \int_0^{V_{ds}} g_0^2(V) (1 + \frac{E}{E_c}) \cdot dV$$

(2.15)

where the electrical channel length of the MOSFET is  $L_{elec} = L_{eff} - \Delta L$ .

In order to obtain a compact analytical equation, a closed-form expression is given [34] as

$$S_{i_d} \approx 4kTg_{d0} \frac{1 - u + \frac{u^2}{3}}{1 - \frac{u}{2}}$$

(2.16)

where  $g_{d0}$  is the drain conductance at  $V_{ds} = 0$  V,  $u = \alpha V_{ds}/V_{od}$  and  $\alpha$  is the coefficient of the bulk charge effect. The parameter  $\alpha$  has a typical value of 1.2 [36]. The parameter  $V_{od}$  is the gate overdrive voltage, which equals  $(V_{gs} - V_{th})$ .

#### 2.2.2.6 The Model of Deen et al.

Based on Han's model, the longitudinal electric field (E) along the channel was examined by Deen's group [24]. They claimed that the longitudinal electric field (E) is a function of the position x along the channel instead of a constant along the channel, and is given by

$$E(x) = \frac{E_C V_d}{\left[(2V_{od} - V_d)^2 - 4\alpha E_C V_d x\right]^{\frac{1}{2}}}$$

(2.17)

where  $V_d = I_d/(WC_{OX}v_{sat})$ . The revised total channel charge can be obtained by integrating the drain current from 0 to  $L_{elec}$  with the expression of E(x) in Eq. (2.17). The total drain-current noise power spectral density is then obtained,

$$S_{id} = 4kT \frac{4V_{od}^2 + V_d^2 + V_{od}V_d}{3V_{od}^2(V_{od} - V_d)} \alpha I_d$$

(2.18)

#### 2.2.2.7 The Model of Jeon et al.

Jeon and his colleagues also have developed an analytical channel thermal noise model for deep-submicron MOSFETs with short-channel effects [37]. By following Tsividis' method [22], they derived an analytical noise model. In their analytical channel thermal noise model, short-channel effects, such as channel-length modulation, velocity saturation, and hot carrier effects, have been taken into account.

The ac conductance  $g_{ac}$  is a small-signal conductance with the consideration of velocity saturation. It was used to express the current noise source spectrum of a small segment  $\Delta x$  of channel length, and it is given as

$$\overline{\Delta \iota_n^2} = 4kT_c g_{ac} \Delta f \tag{2.19}$$

where  $T_c$  is the carrier effective temperature. The carrier temperature has shown a dependency on the electric field when a high electric field is present in short-channel MOSFETs. The relation of  $T_c$  and the electric field is given as

$$\frac{T_c}{T_0} = \left(1 + \frac{E}{E_c}\right)^n \tag{2.20}$$

where  $T_0$  is the lattice temperature, and when n = 0 the carrier is in thermal equilibrium without carrier heating effect. The heating effect is considered for n = 1 or n = 2 [23].

This small noise source will be added on the top of the drain current  $I_{ds}$ , which already includes the velocity saturation effect in this model [37]. By integrating the new drain current over the channel, the total drain-current noise power spectral density for different values of n is given as

$$S_{id} = 4kT_0 \frac{4V_{od}^2 + 10V_0^2 + 7V_{od}V_0 + \frac{3}{2} \frac{V_0^3}{V_{od} - V_0 ln \frac{|2V_{od} - V_0|}{V_0}}}{3(V_{od} - V_0)(V_{od} + V_0)^2} mI_d$$

$$with n = 2$$

$$S_{id} = 4kT_0 \frac{4V_{od}^2 + 4V_0^2 + 4V_{od}V_0}{3(V_{od} - V_0)(V_{od} + V_0)^2} mI_d$$

(2.21a)

with

$$n = 1$$

(2.21b)

$$S_{id} = 4kT_0 \frac{4V_{od}^2 + V_0^2 + V_{od}V_0}{3(V_{od} - V_0)(V_{od} + V_0)^2} mI_d$$

with  $n = 0$  (2.21c)

where  $V_{od}$  is equal to  $(V_{gs} - V_{th})$ , and  $V_0 = I_d / (W C_{ox} v_{sat})$ , which is the same as  $V_d$  in Deen's model. The parameter *m* is body effect factor [11]. These models show great similarity with Han's model and Deen's model, and were validated with measurement results by Jeon's group.

#### 2.2.2.8 White Noise Factor Formula

The aforementioned models all included some of the short-channel effects based on different perspectives of the researchers, such as the effect of velocity saturation, the effect of channel-length modulation, and the effect of mobility degradation. However, the expressions in Eq. (2.13) and Eq. (2.15) are not suitable for hand analysis. Particularly, they are not practical for use in geometric programming, which is the special optimization method adapted in this thesis. A simpler noise formula would be a better choice. As mentioned in the discussion of van der Ziel's model, the channel thermal noise can be conveniently expressed using the so-called white noise gamma factor formula given in Eq. (2.7), where  $\gamma$  is the thermal noise factor. Since this expression is a simple closed-form equation, it has been widely used for noise analysis by circuit designers, and it is also used in this thesis. For long-channel MOSFETs, the theoretical values of  $\gamma$  are well known. It is equal to unity at zero drain bias and 2/3 in the saturation region. However, when the size of MOSFETs approaches the submicron and even smaller level, it is observed that the values of  $\gamma$  are not the same as in long-channel MOSFETs under the same bias conditions. There are some reports regarding the modeling of  $\gamma$  in shortchannel MOSFETs [30, 34, 38]. Since excess thermal noise has been observed in shortchannel MOSFETs, an increase of the value  $\gamma$  is expected for short-channel MOSFETs.

In the work of Scholten and his group [30], measurements and modeling had been carried out. Short-channel effects, such as effect of velocity saturation and effect of channel-length modulation, have been taken into account in their noise modeling, which has been described in the previous section. Based on their results, both the channel thermal noise constant  $\gamma$  and the induced gate current noise constant  $\beta$  are independent of the operating frequencies within moderate frequencies (for example, 10 GHz or less), and they are not very sensitive to bias conditions for high bias voltages. However, they do vary with the channel lengths, which agreed with the fact that larger thermal noise was present in short-channel MOSFETs than long-channel MOSFETs. The values of  $\gamma$  are expected to be larger than their theoretical long-channel values. Because of the same origin of channel thermal noise and induced gate noise, a similar trend of increase in  $\beta$  has been observed at short channel lengths.

Jeon and his group recently have also investigated and measured the white noise factor  $\gamma$  [38], which is an extension of their previous work. The channel thermal noise power spectral density can still be expressed as Eq. (2.7), the well-known white noise gamma factor formula. However, the white noise factor  $\gamma$  for short-channel MOSFETs takes the form of

$$\gamma = \frac{g_{ds}}{g_{d0}} \left( 1 + \frac{\bar{E}}{E_C} \right) \tag{2.22}$$

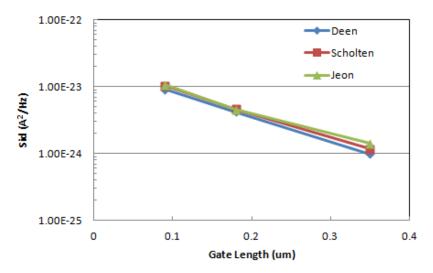

where  $g_{ds}$  is the conductance of the channel,  $\overline{E}$  is the average longitudinal electric field which is equal to  $V_{ds}/L_{elec}$ . The parameter  $E_c$  is the critical electric field, which is equal to  $2v_{sat}/\mu_{eff}$ . Based on the model of Eq. (2.22),  $\gamma$  is a function of the drain bias for different channel length. A comparison between Deen's analytical model of the channel thermal noise in Eq. (2.18), and the thermal noise calculation using the two  $\gamma$  models from Scholten's and Jeon's results have been made. As it is shown in Figure 2.5, their results are comparable with a similar trend regarding different channel lengths. Since Scholten and Jeon have completed a relatively in depth study of the noise parameters and there is relatively good agreement of their work with Deen's analytical model, the noise calculations in this thesis are carried out based upon the results of Scholten and Jeon.

**Figure 2.5:** Thermal noise comparison of different analytical noise models The numerical results for Figure 2.5 are shown in Table 2.1.

Table 2.1: Thermal noise comparison of different analytical noise models

| Gate Length | Power spectral d       | spectral density of channel thermal noise (A <sup>2</sup> /Hz) |                        |  |

|-------------|------------------------|----------------------------------------------------------------|------------------------|--|

| Guie Length | Deen                   | Scholten                                                       | Jeon                   |  |

| 90 nm       | 9.07×10 <sup>-24</sup> | $1.04 \times 10^{-23}$                                         | 1.07×10 <sup>-23</sup> |  |

| 180 nm      | 4.22×10 <sup>-24</sup> | 4.63×10 <sup>-24</sup>                                         | 4.54×10 <sup>-24</sup> |  |

| 350 nm      | 9.86×10 <sup>-25</sup> | $1.17 \times 10^{-24}$                                         | 1.41×10 <sup>-24</sup> |  |

#### **2.3 Noise Parameters**

Noise parameters are used to measure and evaluate the noise performance of a given system. The noise factor is a useful and important one among the noise parameters, which is usually denoted as F. If only the overall input-output behavior of a system is concerned, all the internal noise sources can be represented by a pair of external sources: a noise current and a noise voltage. The noise factor F is then defined as

$$F = \frac{\text{total output noise power}}{\text{output noise due to input source}}$$

(2.23)

where the source temperature is at 290 K by convention [3]. The noise factor gives a quantitative evaluation of the degradation in the signal-to-noise ratio due to the system noise sources, which means the larger noise factor would be expected if the larger degradation in signal-to-noise occurs. Since the lower signal-to-noise ratio is always desired, the smaller noise factor is the optimum goal for LNA circuit designs. An alternative expression of the noise factor is the noise figure, which is commonly used and simply the noise factor expressed in decibels as

$$NF = 10\log_{10}(F) \tag{2.24}$$

In summary, different short-channel noise models have been reviewed and discussed in this chapter. The experimental results from Scholten's and Jeon's groups, which both take into account short-channel effects, have shown good agreement with Deen's analytical model. Therefore, an excess thermal noise model with elevated white noise gamma parameter following Scholten and Jeon has been chosen for the noise analysis in this study. In the next chapter, the derivation of the noise figure and the design considerations for low-noise amplifier optimization will be presented and discussed in detail.

# **Chapter Three**

# Formulation of Geometric Programming for Short-channel CMOS LNAs

Geometric programming is proposed as the method to optimize the design of short-channel CMOS LNAs. The objective function for geometric programming is to minimize the noise figure of the CMOS LNA subject to design constraints. The noise figure for short-channel devices is placed in the form of posynomial functions, which are compatible with geometric programming. In addition, design constraints, such as output conductance, transconductance, dimensional constraints, input impedance, and power dissipation are expressed either as a posynomial function or a monomial function.

# **3.1 Geometric Programming**

A geometric optimization problem has an objective function in the form of a posynomial function with inequality constraints expressed as posynomial functions and equality constraints as monomial functions [14].

A monomial function has the following form:

$$g(x_i) = c x_1^{a_1} x_2^{a_2} x_3^{a_3} \dots x_n^{a_n}$$

(3.1)

where *c* is a positive constant (c > 0);  $x_1, x_2, ...,$  and  $x_n$  are real positive variables;  $a_1$ ,  $a_1$ , ..., and  $a_1$  are constants known as the exponents of the monomial. Any positive constant is a monomial. Monomials are closed under multiplication and division.

A posynomial function is a sum of one or more monomial functions as shown in the following equation,

$$f(x_i) = \sum_{k=1}^{K} c_k x_1^{a_{1k}} x_2^{a_{2k}} x_3^{a_{3k}} \dots x_n^{a_{nk}}$$

(3.2)

where  $c_k > 0$ . Note that posynomial functions are also closed under addition and multiplication.

With the introduction of the basic concepts for monomial and posynomial functions, a standard form for a geometric programming can be defined as an optimization problem with the following form

Minimize an objective function:  $f_0(x)$

Subject to constraints:

$$f_i(x) \le 1, \ i = 1, \cdots, m$$

(3.3)

$g_i(x) = 1, \ i = 1, \cdots, p$

where  $x = (x_1, ..., x_n)$  a vector with components  $x_i$ ,  $f_0(x)$  is an objective function with the form of a posynomial function;  $f_1(x)$ ,  $f_2(x)$ , ...,  $f_m(x)$  are posynomial functions;  $g_1(x)$ ,  $g_2(x)$ , ...,  $g_p(x)$  are monomial functions; and  $x_i$  are the optimization variables ( $x_i$  are always greater than zero).

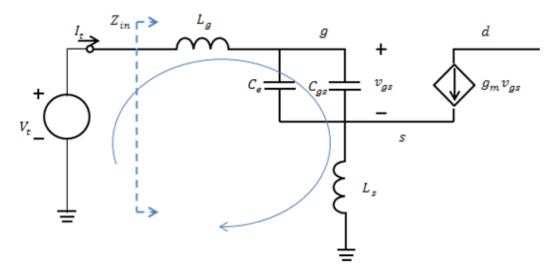

As a global optimization method, geometric programming has provided a very efficient method for designing CMOS operational amplifiers [13] and RF CMOS lownoise amplifiers using long-channel MOSFETs [17]. In this thesis, geometric programming was applied to the design optimization of a short-channel CMOS narrowband low-noise amplifier. The frequency of operation was chosen to be 2.4 GHz, which is the operating frequency for widely-used Bluetooth applications. For narrowband operation, which is the focus of this thesis, inductive source degeneration offers the best noise performance compared to other topologies discussed previously in Chapter Two. Therefore, an LNA with inductive source degeneration, as shown in Figure 3.1, is selected for design optimization in this thesis. A cascode device  $M_2$  is added to improve the isolation between the tuned input and tuned output circuits and also to reduce the effect of the gate-to-drain capacitance of transistor  $M_1$  [3]. An additional capacitance  $C_e$ across the gate and source is introduced into the circuit, which is in parallel to the intrinsic gate capacitance  $C_{gs}$  of the transistor  $M_1$ . By adding this capacitor, a relatively high quality factor can be obtained without very high values of the on-chip inductors ( $L_q$ and  $L_s$ ), which is very important for high-integration density circuit implementations.

This additional capacitance also gives the freedom to choose small intrinsic gate capacitance  $C_{gs}$ . Since the induced gate noise is proportional to the square of  $C_{gs}$ , smaller  $C_{gs}$  will result in a lower induced gate noise, which has been found to be more significant in short-channel devices [18]. The formulation of such a design problem as a geometric programming is shown in detail in this chapter.

Figure 3.1: Schematic of CMOS cascode LNA with inductive source degeneration

# 3.2 Design Considerations for a Short-channel CMOS LNAs

The major goal of an LNA is to provide a reasonable gain with a small noise level. The noise performance is the most crucial issue for a front-end amplifier. Therefore, minimizing the noise figure is the main objective of the CMOS LNA design in this thesis. To achieve the best noise performance, design variables such as channel width (W) and channel length (L) need to be optimized. In addition, design constraints, such as quality factor of the input circuit, maximum allowed power dissipation, and input impedance matching, need to be satisfied during the optimization process.

#### **3.2.1 Objective Function**

The objective of LNA design in this thesis is to minimize the noise figure. Consequently, the noise figure is considered as the objective function for geometric programming. By small-signal analysis, the equation for the noise figure is described in the following section.

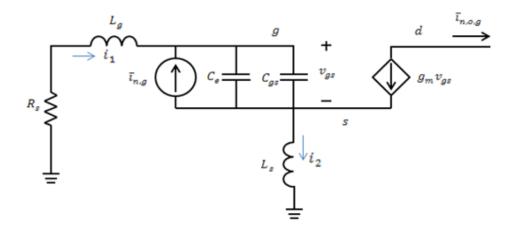

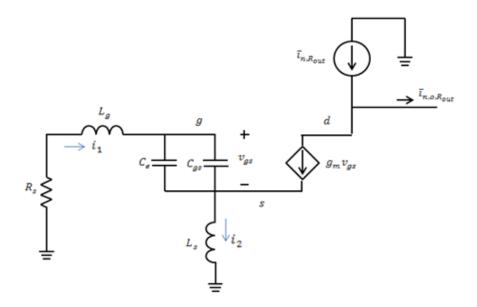

Assuming the output impedance of transistor  $M_1$  ( $r_{o1}$ ) is large, transistor  $M_2$  has an insignificant influence on the noise performance of the low-noise amplifier. Therefore, its contribution to the total noise is neglected in the noise analysis. In addition, the contribution of the substrate noise is also neglected as well for simplicity [18]. Therefore, the noise figure will be minimized for the given design constraints. Based on the previous discussion of noise sources in RF CMOS, the thermal noise is the main concern at RF intermediate frequencies (i.e., the carrier frequency) for MOSFETs, where 1/f noise is no longer significant. Therefore, four noise sources have been considered in the design, which are the thermal noise of the source resistance ( $\bar{\iota}_{n,R_s}$ ), the channel thermal noise ( $\bar{\iota}_{n,d}$ ), the gate induced current noise ( $\bar{\iota}_{n,g}$ ), and the thermal noise of the output resistance ( $\bar{\iota}_{n,R_{out}}$ ).

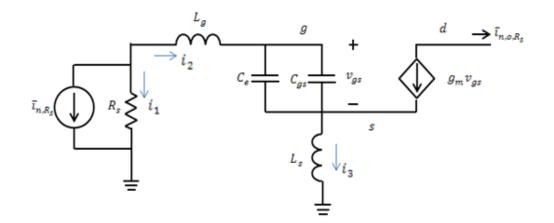

Figure 3.2: Small-signal circuit for noise analysis

Before the discussion of the noise analysis, the input impedance needs to be calculated in order to determine the noise contributions of the input referred noise in the following derivations. All the passive components in the circuit are considered to be lossless except the output load, which is represented by an LC tank including a parasitic resistance, as shown in Figure 3.1. To compute the input impedance of the circuit in Figure 3.2, the small-signal MOSFET is modeled only with a transconductance ( $g_m$ ) and a gate-source capacitance ( $C_{gs}$ ). The equivalent circuit to calculate the input impedance of the circuit is shown in Figure 3.3.

Figure 3.3: Equivalent circuit for the input impedance calculation

Therefore, the input impedance is (see Appendix C for the full derivation)

$$Z_{in} = \frac{V_t}{I_t}$$

$$= \frac{1}{j\omega(C_e + C_{gs})} + j\omega(L_g + L_s) + \frac{g_m}{(C_e + C_{gs})}L_s$$

$$= \frac{g_m}{(C_e + C_{gs})}L_s + j\left[\omega(L_g + L_s) - \frac{1}{\omega(C_e + C_{gs})}\right]$$

(3.4)

At the resonant frequency  $\omega_0$ , which is the operating frequency of the circuit, the input impedance should be resistive and equal to the source resistance for the maximum

power delivery. In this case, the input resistance is  $R_s$ , which gives the following relation regarding the input impedance,

$$\omega_0(L_g + L_s) - \frac{1}{\omega_0(C_e + C_{gs})} = 0$$

(3.5)

$$\frac{g_m}{(C_e + C_{gs})}L_s = R_s \tag{3.6}$$

After applying some simple algebra, the final equations required to obtain an input impedance match at the resonant frequency are

$$\omega_0 = \frac{1}{\sqrt{(L_g + L_s)(C_e + C_{gs})}} = \frac{1}{\sqrt{L_{tot} \cdot C_{tot}}}$$

(3.7)

$$R_s = \frac{g_m}{\left(C_e + C_{gs}\right)} L_s = \frac{g_m}{C_{tot}} L_s \tag{3.8}$$

where  $L_{tot} = (L_g + L_s)$  and  $C_{tot} = (C_e + C_{gs})$ .

Since the focus is on the resonant behavior of the circuit, a commonly used parameter Q, which is called the quality factor, is introduced into the analysis. By definition,

$$Q = \omega \frac{energy \ stored}{average \ power \ dissipated} \tag{3.9}$$

The quality factor of a series RLC circuit is given as  $Q = \frac{\sqrt{L/C}}{R}$  [3]. Therefore, the quality factor of the input circuit at resonant frequency  $\omega_0$  is described as

$$Q = \frac{\sqrt{L_{tot}/C_{tot}}}{R_{tot}} \tag{3.10}$$

where  $R_{tot} = R_s + \frac{g_m}{c_{tot}}L_s$ . Making use of Eq. (3.7) and Eq. (3.8), the quality factor of the input circuit at resonant frequency  $\omega_0$  has the form of

$$Q = \frac{1}{R_{tot}\omega_0 C_{tot}} = \frac{1}{2R_s\omega_0 C_{tot}}$$

(3.11)

The quality factor of a parallel RLC circuit is given as  $Q = \frac{R}{\sqrt{L/C}}$  [3]. Therefore, the quality factor of the output circuit at resonant frequency  $\omega_0$  is described as

$$Q_{out} = R_{out} C_{out} \omega_0 \tag{3.12}$$

where  $R_{out}$  is the parasitic output resistance and  $C_{out}$  is the capacitance of the output load. The resonant frequency  $\omega_0$  can be expressed in terms of the output capacitance and conductance as

$$\omega_0 = \frac{1}{\sqrt{L_{out}C_{out}}} \tag{3.13}$$

An inductance value of 10 nH and a quality factor of 5 have been used for the output circuit [18].

The definition of noise factor from the previous chapter was given in Eq. (2.23) as

$$F = \frac{\text{total output noise power}}{\text{output noise due to input source}}$$

In order to find the expression of the noise factor and noise figure, two steps are required. First, all four noise sources need to be identified using thermal noise theory analysis. Second, the contributions of all four noise sources to the output noise power must be computed by using small-signal analysis.

Considering the thermal noise in resistors given by Eq.(2.2), the contributions due to resistor  $R_s$  and  $R_{out}$  are given by

$$\overline{\iota_{n_{r_{R_s}}}^2} = 4kT \frac{1}{R_s} \Delta f \tag{3.14}$$

$$\overline{u_{n_{R_{out}}}^2} = 4kT \frac{1}{R_{out}} \Delta f$$

(3.15)

The channel thermal noise mean square value and the induced gate noise mean square value are given according to Eq. (2.7) and Eq. (2.9). Therefore

$$\overline{\iota_{n,d}^2} = 4kT\gamma_{short}g_{d0}\Delta f \tag{3.16}$$

$$\overline{\iota_{n,g}^2} = 4kT\beta_{short}g_g\Delta f \tag{3.17}$$

The significant differences of Eqs. (3.16) and (3.17) from Eqs. (2.7) and (2.9) are that short-channel effects have been taken into account in the expressions in Eqs. (3.16) and (3.17). The parameters  $\gamma_{short}$  and  $\beta_{short}$  are extracted from the noise analysis of short-channel models [30, 38]. Additionally, the conductance of  $g_{d0}$  and  $g_g$  are also formulated with the contribution of short-channel effects taken into account, which will be discussed in a later section.

With the noise sources calculated, transfer functions using small-signal analysis may be used to find the total output noise power. Once the output noise power is known, the noise figure can be readily expressed. The calculation of the output noise power is based on the small-signal circuit in Figure 3.2. Detailed derivations can be found in Appendix D. In small-signal noise analyses,  $\bar{\iota}_{n,R_s}$  is the source resistance thermal noise,  $\bar{\iota}_{n,d}$  is the channel thermal noise,  $\bar{\iota}_{n,g}$  is the induced gate noise, and  $\bar{\iota}_{n,R_{out}}$  is the output resistance thermal noise. The contributions of these four noise sources to the output noise are denoted by  $\bar{\iota}_{n,o,R_s}$ ,  $\bar{\iota}_{n,o,d}$ ,  $\bar{\iota}_{n,o,g}$  and  $\bar{\iota}_{n,o,R_{out}}$ , respectively.

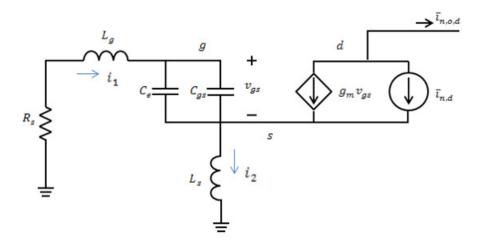

For example, when the output noise due to the input source resistance noise is calculated, other noise sources are removed. The resulting small-signal circuit with only the input source resistance noise is shown in Figure 3.4. The share of the output noise current due to the input source resistance noise can be expressed as,

$$\bar{\iota}_{n,o,R_s} = \frac{g_m}{j2\omega_0 C_{tot}} \bar{\iota}_{n,R_s}$$

(3.18)

Figure 3.4: Small-signal circuit of the calculation of output noise due to input source resistance noise

Following a similar procedure, the contributions of the other three noise sources to the output noise current are

$$\bar{\iota}_{n,o,d} = -\frac{1}{2}\bar{\iota}_{n,d} \tag{3.19}$$

$$\bar{\iota}_{n,o,g} = \frac{g_m}{j\omega_0 C_{tot}} \frac{1 - jR_s\omega_0 C_{tot}}{j2R_s\omega_0 C_{tot}} \bar{\iota}_{n,g}$$

(3.20)

$$\bar{\iota}_{n,o,R_{out}} = \bar{\iota}_{n,R_{out}} \tag{3.21}$$

There is one more component in the output noise current, which is the contribution due to the correlation between the drain current  $(\bar{\iota}_{n,d})$  and the induced gate current  $(\bar{\iota}_{n,g})$ . Calculating the correlation is straightforward because these two noise currents share a common thermal noise origin. The correlation coefficient *c* is defined by Eq. (2.11). The output noise due to the correlation can be represented as [18]

$$\overline{\iota^2}_{n,o,correlation} = \frac{g_m c}{2\omega_0 C_{tot}} \sqrt{\overline{\iota^2}_{n,g} \cdot \overline{\iota^2}_{n,d}}$$

(3.22)

Therefore, the noise factor of the LNA can be rewritten as

$$F = \frac{\overline{\iota^2}_{n,o,R_s} + \overline{\iota^2}_{n,o,d} + \overline{\iota^2}_{n,o,g} + \overline{\iota^2}_{n,o,correlation} + \overline{\iota^2}_{n,o,R_{out}}}{\overline{\iota^2}_{n,o,R_s}}$$

(3.23)

By using Eq. (3.14)-(3.22), Eq. (2.10) and Eq. (3.11), the noise factor at resonance is obtained as (see Appendix E)