## JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY

Special issue edited by Andrzej Jakubowski, Aleksander Werbowy, and Lidia Łukasiak

### Part II

| SiGe field effect transistors - performance and applications                                                            |               |      |

|-------------------------------------------------------------------------------------------------------------------------|---------------|------|

| T. E. Whall and E. H. C. Parker                                                                                         | Invited paper | 3    |

| Reliability of deep submicron MOSFETs                                                                                   |               |      |

| F. Balestra                                                                                                             | Invited paper | 12   |

| High-temperature instability processes in SOI structures<br>and MOSFETs                                                 |               |      |

| A. N. Nazarov, V. I. Kilchytska, J. N. Vovk, and J. P. Colinge                                                          | Invited paper | 18   |

| Challenges in ultrathin oxide layers formation                                                                          |               |      |

| R. B. Beck, A. Jakubowski, L. Lukasiak, and M. Korwin-Pawłowski                                                         | Invited paper | 27   |

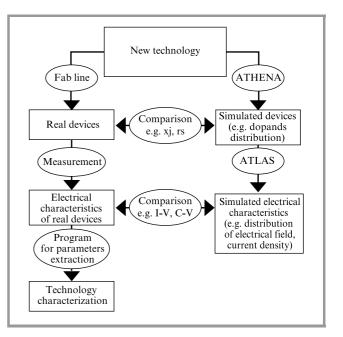

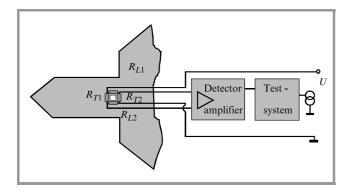

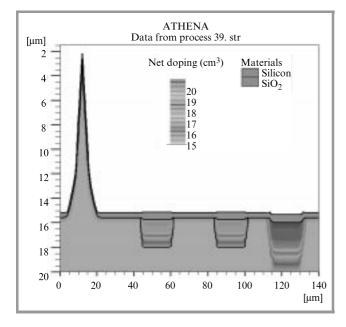

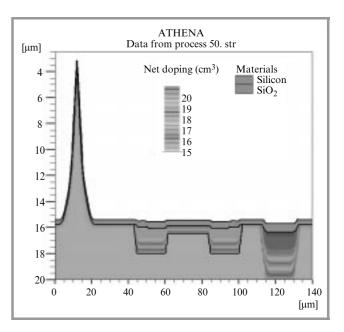

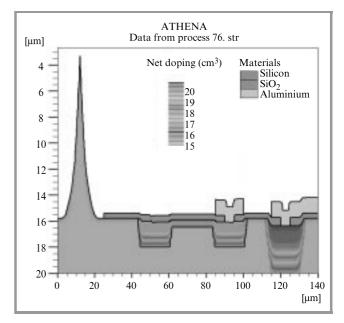

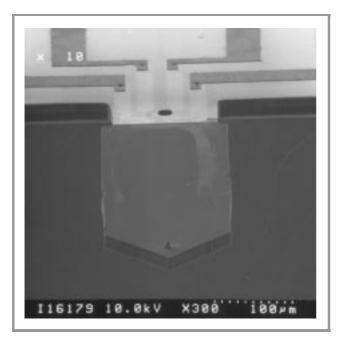

| Piezoresistive sensors for atomic force microscopy – numerical simulations by means of virtual wafer fab                |               |      |

| T. Dębski et al.                                                                                                        | Paper         | - 35 |

| On possibility to extend the operation temperature range of SOI sensors with polysilicon piezoresistors                 |               |      |

| A. Druzhinin et al.                                                                                                     | Paper         | - 40 |

| Grain boundary effect on the anisotropy piezoresistance<br>of laser-recrystallized polysilicon layers in SOI-structures |               |      |

| Y. Pankov and A. Druzhinin                                                                                              | Paper         | - 46 |

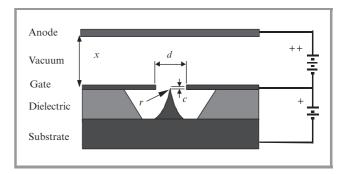

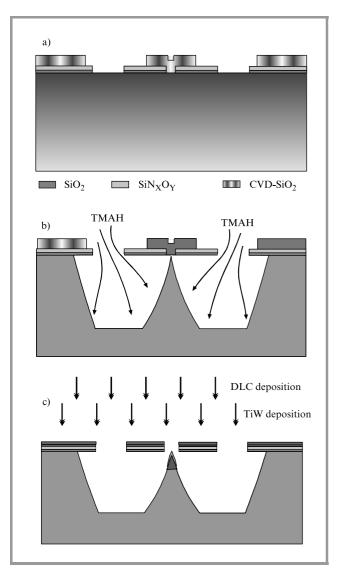

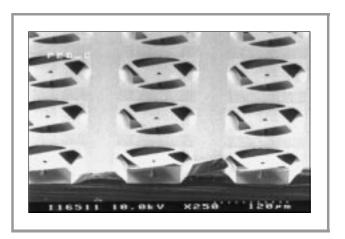

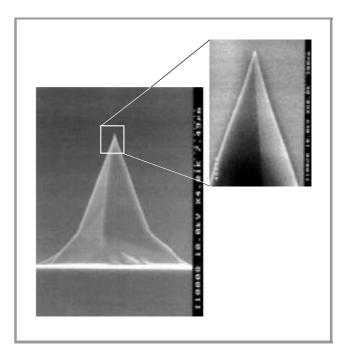

| Fabrication and properties of the field emission array<br>with self-alignment gate electrode                            |               |      |

| W. Barth et al.                                                                                                         | Paper         | 49   |

### Editorial Board

| Editor-in Chief:   | . Pawel Szczepański                            |

|--------------------|------------------------------------------------|

| Associate Editors: | . Elżbieta Andrukiewicz<br>Aleksander Orłowski |

| Managing Editor:   | . Maria Lopuszniak                             |

| Technical Editor:  | Anna Tyszka-Zawadzka                           |

### Editorial Advisory Board

....

| Chairman: | . Andrzej Jajszczyk       |

|-----------|---------------------------|

|           | Marek Amanowicz           |

|           | Daniel Bem                |

|           | Andrzej Hildebrandt       |

|           | Witold Holubowicz         |

|           | Andrzej Jakubowski        |

|           | Alina Karwowska-Lamparska |

|           | Marian Kowalewski         |

|           | Andrzej Kowalski          |

|           | Józef Lubacz              |

|           | Władysław Majewski        |

|           | Krzysztof Malinowski      |

|           | Marian Marciniak          |

|           | Józef Modelski            |

|           | Ewa Orlowska              |

|           | Andrzej Pach              |

|           | Zdzisław Papir            |

|           | Janusz Stoklosa           |

|           | Wiesław Traczyk           |

|           | Andrzej P. Wierzbicki     |

|           | Tadeusz Więckowski        |

|           | Tadeusz A. Wysocki        |

|           | Jan Zabrodzki             |

|           | Andrzej Zieliński         |

|           |                           |

|           |                           |

## JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY

### Preface

Rumors about forthcoming twilight of silicon-based microelectronics seem to be exaggerated. Microelectronics has been continuously developing for the past three decades – for instance every three years a new generation of memories becomes available on the market with the capacity four times larger than that of the previous generation. The current "official" development forecast published by SIA (Semiconductor Industry Association) reaches ahead to the years 2012-2015. There are, however, more aggressive forecasts available that reach even as far as the year 2020.

While the development of silicon microelectronics in the past could be attributed mostly to the reduction of the feature size (progress in lithography), today it relies more on new material solutions, such as SOI, SiGe or SiC. The combination of this trend with continuous miniaturization provides the opportunity of moving into the range of very high frequencies.

Silicon microelectronics for fast analog and RF circuits, as well as for mainstream wireless and computational applications – these are the new application areas in telecommunications, which is one of the most powerful drivers of microelectronics product development. It is clear that with the anticipated  $f_{max} \approx 50$  GHz and  $f_T = 40$  GHz to be reached by RF transistors in 2005, according to the International Technology Roadmap for Semiconductors (SIA, 1999), a lot of effort must be put into the development of appropriate material, processing, characterization and modeling. However, such an outstanding progress will not happen without increased speed offered by new material solutions. As is generally known, carrier mobility in SiGe is several times higher than in silicon due to internal strain. On the other hand, higher speed of operation in SOI devices is achieved mainly due to the reduction of parasitic capacitances.

High-speed is, however, not everything. Portable wireless products push, for obvious reasons, for lowpower solutions. This trend, too, requires new material, such as SOI where current drivability is higher than in conventional devices due to reduced thickness of the active region.

In this volume the Reader will find a selection of papers and lectures (part II of two parts) presented during the conference "Advanced Silicon Devices and Technologies for ULSI Era", which took place in Museum of Earth, Warsaw, Poland on 28–30 June 2000. A number of these papers are devoted to the performance of state-of-the-art semiconductor devices and sensors, in certain cases intended for highly-specialized applications, e.g. Atomic Force Microscopy. A lot of attention is also paid to the studies of the physical properties of such materials as e.g. porous silicon or amorphous silicon. The much-investigated subject of ultrathin gate dielectrics is covered, too. Finally, there are several papers devoted to device modeling.

We hope that Readers will find these Proceedings useful and interesting.

Guest editors: Andrzej Jakubowski, Aleksander Werbowy, Lidia Łukasiak

# SiGe field effect transistors – performance and applications

Terrence E. Whall and Evan H. C. Parker

Abstract — Recent and encouraging developments in Schottky and MOS gated Si/SiGe field effect transistors are surveyed. Circuit applications are now beginning to be investigated. The authors discuss some of this work and consider future prospects for the role of SiGe field effect devices in mobile communications.

Keywords — SiGe, FETs, epitaxy, circuits.

### 1. Introduction

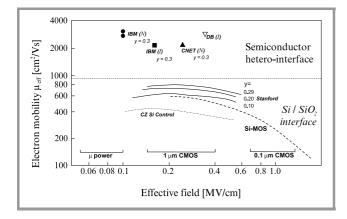

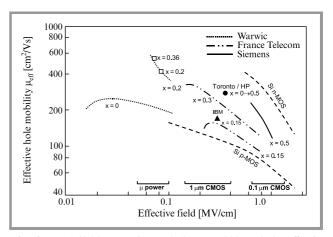

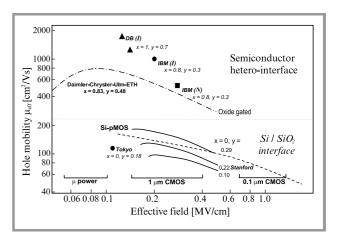

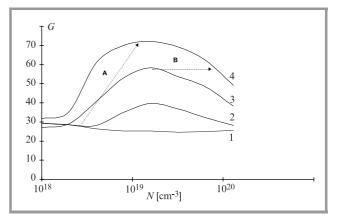

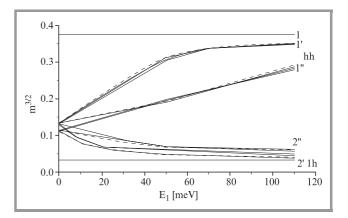

SiGe heterostructures are now firmly established in bipolar technologies, with a current market value of £30M per annum rising to £1.83B by 2005, driven by the wireless and optical communications sector [1]. SiGe also offers the exciting prospect of similar or even bigger commercial benefits in Si field effect transistors. The reasons for this optimism are based on the substantial gains in room temperature effective mobilities, shown in Figs. 1, 2 and 3, which accrue from strain-induced band structure modifications [2–4] in silicon, SiGe alloy and germanium epilayers. In this article, we examine the resulting performance gains in a number of devices based on these heterostructures, discuss some other potential benefits of a SiGe technology, and briefly survey some circuit applications.

Fig. 1. Available experimental data on 300 K electron mobilities in strained Si grown on virtual substrates with terminating composition Si<sub>1-x</sub>Ge<sub>y</sub> versus the effective field  $E_{eff}$  [2, 3].  $E_{eff} = \frac{e}{\epsilon_s} [N_{depl} + \frac{1}{\beta}n_s]$  where  $\epsilon_s$  is the absolute permittivity of Si,  $N_{depl}$  is the depletion charge density, and  $n_s$  is the carrier density. The upper section shows mobilities at remote doped hetero-interfaces and the lower section refers to oxide-gate/(tensile strained) Si interfaces. *I* denotes "inverted" modulation-doped structure (doping supply layer below strained silicon) and *N* denotes "normal" interface case (doping above silicon). The oxidegated structures are operated in the inversion mode. Here  $\beta = 2$ .

Fig. 2. Available experimental data on 300 K hole effective mobilities obtained in pseudomorphic  $\text{Si/Si}_{1-x}\text{Ge}_y/\text{Si}$  structures plotted against effective field  $(E_{eff})$ , all data refer to buried SiGe channels except for the IBM sample where the gate dielectric was produced by plasma oxidation. The alloy composition in the Toronto/HP sample was graded. The squares refer to modulation-doped structures. The bars indicate the range of  $E_{eff}$  values present in micropower, 1 and 0.1  $\mu$ m CMOS technologies.  $\beta$  is usually taken as 3 for holes [6], in order to obtain an universal curve independent of doping specifications. That practice is followed here, but we note that this tends to over-emphasise the superiority of the electron channel where  $\beta$  is chosen as 2.

*Fig. 3.* Available experimental data on 300 K hole mobilities obtained in compressively strained Si<sub>1-x</sub>Ge<sub>y</sub> and tensile strained Si grown on virtual substrates with terminating composition structures Si<sub>1-x</sub>Ge<sub>y</sub>. The upper section shows mobilities for remote doped hetero-interfaces and the lower section refers to oxide-gate/(tensile strained) Si interfaces. *I* denotes "inverted" and *N* denotes "inverted" interface. The oxide-gated data refer to inversion layers.  $\beta = 3$ .

### 2. Strained silicon n-channel devices

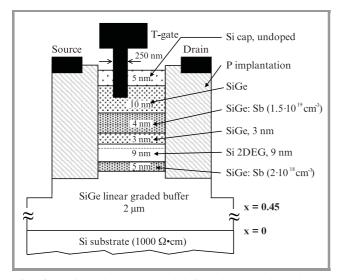

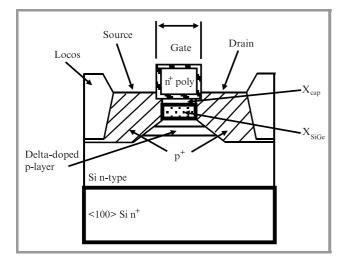

Ismail et al [5] have fabricated an 0.4  $\mu$ m gate length Schottky gated modulation doped FET or n-MODFET with a peak transconductance of 420 mSmm<sup>-1</sup>, an  $f_T$  of 40 GHz and an  $f_{max}$  of 56 GHz, comparable to GaAs/AlGaAs HEMTs of the same gate length. Figure 4 shows a typical Si/SiGe n-MODFET, designed and fabricated by the Daimler-Chrysler group [6]. The strained Si is supplied

*Fig. 4.* Schottky gated modulation doped n-channel FET (n-MODFET). The conduction band offset in the strained Si layer confines electrons. The T gate recess determines the threshold voltage, allowing either d-mode or e-mode operation (*after Glück et al. [6]*).

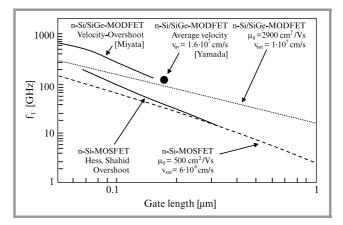

with carriers by SiGe:Sb doped layers above and below the quantum well. The device can operate in either depletion or enhancement mode depending on the depth of the Pt/Au Schottky gate recess, with a deeper recess in the latter case. An 0.25  $\mu$ m d-mode device gives a measured  $f_T$  of 70 GHz and an  $f_{max}$  of 120 GHz (U. König, private communication). Simulations [7] suggest transconductances up to 1000 mSmm<sup>-1</sup> and transit frequencies  $f_T$  above 200 GHz in self aligned layouts with gate lengths < 0.1  $\mu$ m. Figure 5 shows the simulations of  $f_T$ . It is apparent that velocity overshoot plays an important role at gate lengths of 0.1  $\mu$ m and below, particularly in the heterostructure.

Fig. 5. Simulated transit frequencies of SiGe n-MODFETs compared to ordinary SiGe n-MOS (after König et al. [7]).

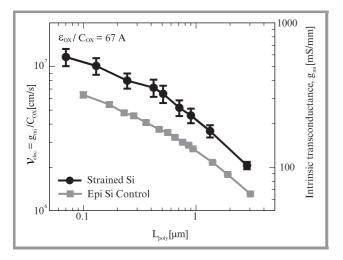

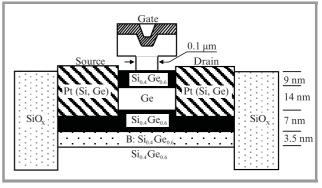

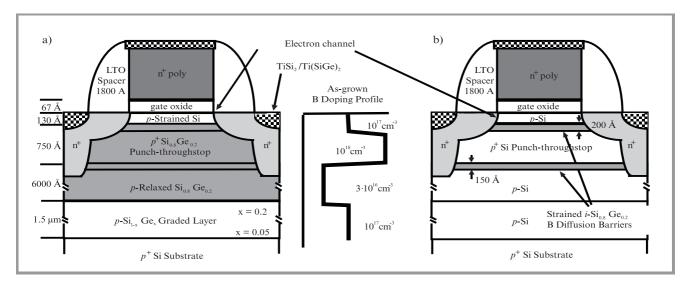

The Stanford group have used CVD at 750°C to grow a strained Si channel on a relaxed Si<sub>0.8</sub>Ge<sub>0.2</sub> strain-tuning virtual substrate (VS), and have fabricated an n-MOSFET of channel length 0.1  $\mu$ m [8]. This is illustrated in Fig. 6a. The VS is in-situ boron-doped to create a punchthrough stopper doping profile surrounded by Si<sub>0.8</sub>Ge<sub>0.2</sub> of lower doping. A very steep profile is possible because the boron diffusivity in both strained and relaxed Si<sub>0.8</sub>Ge<sub>0.2</sub> is 8 times lower than in bulk Si. In the unstrained Si control sample SiGe boron diffusion barriers are placed either side of the p-layer, as shown in Fig. 6b. The doping profiles obtained

give comparable short channel behaviour in heterostructure and control with a DIBL value of approx 0.8, threshold voltage shift of approx 0.1 V and subthreshold slope of  $103 \div 110$  mV per decade. Transconductance enhancement in the heterostructure device is 60%, and average velocity (a measure of  $f_T$ ) 67% as shown in Fig. 7. This improved performance [9] corresponds to a mobility enhancement of 70% at an effective field as high as 1 MV/cm and substantial velocity overshoot associated with a 100% increase in the energy relaxation time.

*Fig. 7.* Average channel velocities and intrinsic transconductances of the devices shown in Fig. 6 (*after Rim et al.* [8]).

### 3. Strained $\text{Si}_{1-x}\text{Ge}_x$ ( $0 \le \text{and} \le 1$ ) p-channel devices

Modern circuits for analogue and digital performance demand both n- and p-channel devices but the poor performance of the latter is an impediment to even better circuitry. Indeed, a major theme at the recent (December 1999) *International Electronic Devices Meeting (IEDM)* concerned the Si p-MOS device, which is the Achilles heel of Si CMOS. Factors of two or more reduction in current drive or transconductance as compared to Si n-MOS were reported in about a dozen papers concerned with deep submicron devices (50 nm <  $L_{eff} \leq 100$  nm) and theoretical work [10] indicated that the factor of two represented a lower limit. SiGe offers a unique opportunity to obtain matching n- and p-channel performance for the first time.

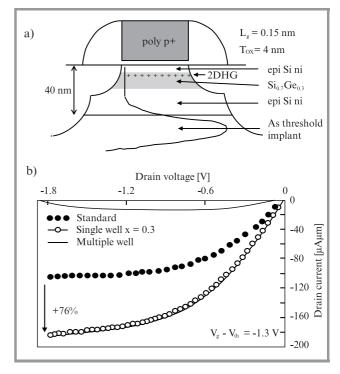

The fully pseudomorphic Si/SiGe/Si sandwich structure, because of its simplicity, has received a lot of attention for enhanced p-channel performance. It is a relatively defect-free structure which avoids the problems associated with the Si<sub>1-y</sub>Ge<sub>y</sub> virtual substrate of long growth times and comparatively poor thermal conductivity. The CNET group have fabricated [11] such a device within an 0.15  $\mu$ m CMOS process and this is sketched in Fig. 8a. It uses a p<sup>+</sup> poly-gate with a 4 nm gate oxide, and In or As implants for threshold voltage adjustment. They obtain a 76% improve-

*Fig. 8.* Device architecture (a) and current drive capability (b) of fully pseudomorphic  $Si/Si_{0.7}Ge_{0.3}/Si$  p-MOSFET. The valence band offset relative to silicon confines the carriers in the alloy. Also shown is the current drive enhancement as compared to silicon for a Si/SiGe multi quantum well structure (*after Alieu et al. [11]*).

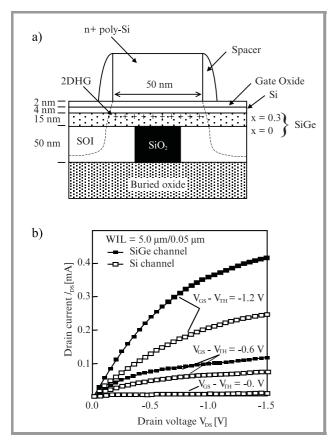

ment in current drive compared to a bulk silicon standard, as shown in Fig. 8b. The Cornell group report an  $f_T$  of 23 GHz and an  $f_{max}$  of 35 GHz in Si/Si<sub>0.6</sub>Ge<sub>0.4</sub>/Si 0.2  $\mu$ m gate length p-MOS device [12]. They compare their  $f_T$ value with measurements on a bulk Si n-MOSFET of similar geometry, which gave 32 GHz. A novel solid-phase epitaxy process has been used [13] to form an ultra thin body SOI p-channel Si/Si<sub>0.7</sub>Ge<sub>0.3</sub> MOSFET, which is shown in Fig. 9a. Negligible threshold voltage roll-off and a subthreshold slope of 100 mV/dec is obtained for a channel length of 50 nm. The incorporation of SiGe in the channel (graded from 0 at the bottom to 30% at the top) results in a 70% enhancement in drive current, Fig. 9b. The authors note that further increases in drain current can be expected if the series resistance is reduced by process optimisation.

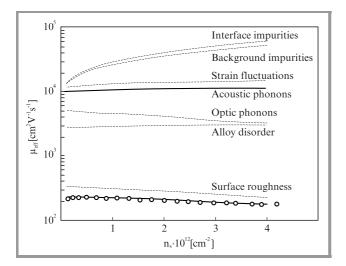

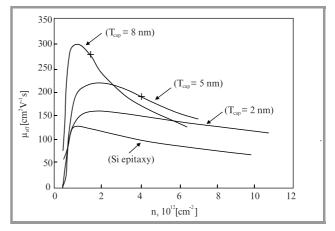

A Glasgow/Loughborough/Warwick team have been investigating the factors which limit current drive and transconductance in SiGe p-MOS devices. Measurements on an x = 0.5 structure of uniform composition, fabricated at Infineon (Munich), Fig. 10, have been compared with theory by Kearney et al. [14] and it is concluded that interface roughness rather than alloy scattering dominates the mobility at both 4 K and 300 K. Further arguments in favour of this viewpoint are given by Whall and Parker [15]. Figure 11 shows measurements of effective mobility by Palmer

*Fig. 9.* (a) Ultra-thin-body silicon on insulator MOSFET incorporating SiGe strained layer. A trench is formed in the SOI wafer,  $SiO_2$  is deposited by low-pressure CVD and then SiGe is deposited and crystallised by solid-phase epitaxy. The broken lines indicate the boundaries of the source and drain islands. (b) Showing 70% enhancement in current drive as compared to silicon (*after Yee Chia Yeo et al. [13]*).

*Fig. 10.* Room temperature effective mobility of a Si/Si<sub>0.5</sub>Ge<sub>0.5</sub>/Si p-MOSFET versus carrier density. O experiment: broken lines theory, continuous line resultant theoretical mobility (*after Kearney et al.* [14]).

*Fig. 11.* Measurements of effective mobility versus carrier density in  $Si/Si_{0.64}Ge_{0.36}/Si$  p-MOSFETs of various Si cap thicknesses, compared with a Si control. The crosses indicate the onset of parasitic conduction in the Si cap (*after Palmer et al. [16]*).

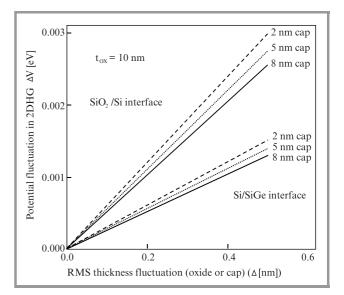

*Fig. 12.* Coulomb potential fluctuations in the Si<sub>0.64</sub>Ge<sub>0.36</sub> quantum well due to random thickness variations in the oxide and Si cap layers, giving rise to interface roughness scattering. A carrier density of  $1 \cdot 10^{12}$  cm<sup>-2</sup> is chosen to avoid the complication of parasitic conduction in the silicon cap (*after Palmer et al. [16]*).

et al. [16] on x = 0.36 devices of various Silicon cap thicknesses. They argue that, for the devices in question, the potential fluctuations in the SiGe channel which limit the mobility, Fig. 12, are associated mainly with Si0<sub>2</sub>/Si as opposed to Si/SiGe interface roughness, in contrast to what is usually claimed. Ge segregation during growth and/or diffusion during processing degrades the Si/Si0<sub>2</sub> interface, presumably because of snowploughing of the Ge during oxidation, leading to increased roughness scattering. Thicker silicon caps lead to better Si0<sub>2</sub>/Si interfaces and higher peak mobilities. At high carrier densities, however, the thicker Si caps are populated, leading to a fall in effective mobility. A device configuration which has merit, is shown in Fig. 13. It uses an n<sup>+</sup> poly-Si gate and a B doping layer beneath the SiGe channel to suppress parallel conduction

*Fig. 13.* p-channel Si/SiGe/Si e-mode MOSFET with  $n^+$  poly Si gate and Si:B doping layer to reduce effective (vertical) field and allow thicker Si cap.

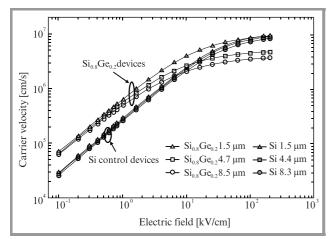

in the cap while maintaining a low threshold voltage for enhancement mode operation. Because a thicker silicon cap becomes possible, it should be more tolerant of any Ge segregation. The B doping layer reduces the vertical effective field  $E_{eff}$ , which should give higher mobilities. Co-evaporation of C is being used by the Warwick group to stabilise the B against segregation and also diffusion. The velocity field characteristics reported by Kaya et al. [17] on an x = 0.2 SiGe p-MOS device, and reproduced in Fig. 14, are consistent with the view that, although the bulk saturation velocity in SiGe is less than that in Si, velocity overshoot affects dominate at short channel lengths and are responsible for the enhanced device performances discussed above. Zhao et al. [18] confirm this behaviour and also report that the observed velocity overshoot effects increase with mobility. Further improvements in device performance should be possible by engineering the doping

*Fig. 14.* Carrier velocity versus horizontal field, extracted from measurements on thick oxide (140 nm)  $Si_{0.8}Ge_{0.2}$  p-MOSFETs and by comparison with a drift diffusion model (*after Kaya et al.* [17]).

distributions to increase the velocity at the source end of the channel.

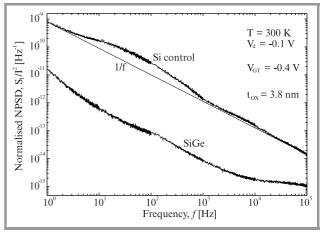

A number of other factors could tip the scales in favour of SiGe. The increased solid solubility and low diffusivity of B in SiGe promises shallow low resistance source and drain contacts [19]. SiGe sources have been demonstrated to suppress parasitic bipolar action and punchthrough [20, 21]. Poly SiGe gates [22] exhibit reduced gate-depletion, reduced boron penetration and give increased current through reduction of  $E_{eff}$ . Measurements by the Warwick group on a Siemens Si/Si<sub>0.5</sub>Ge<sub>0.5</sub>/Si p-MOSFET give two orders of magnitude improvement in the relative 1/f noise, as shown in Fig. 15, which may be associated with the displacement of the Fermi level in the heterostructure [23].

*Fig. 15.* Showing two orders of magnitude improvement in relative noise power spectral density (NPSD) in a Si/Si<sub>0.5</sub>Ge<sub>0.5</sub>/Si MOSFET as compared to a Si control (*after Prest et al. [23]*).

Fig. 16. 0.1  $\mu$ m gate length strained Ge p-MODFET. Contact pad metallisation not shown (*after Hammond et al.* [26]).

Even more dramatic performance enhancements might be expected in high Ge content and pure Ge strained layers on VS. The Daimler-Chrysler group et al. [24] have fabricated strained Si<sub>0.3</sub>Ge<sub>0.7</sub> and Ge p-MOS and p-MODFETs on VS. A novel Ge p-MOS device yielded an  $f_T$  of 59 GHz and an  $f_{max}$  of 126 GHz at a gate length of 0.1  $\mu$ m (*U. König, private communication*). The  $f_T$  value is close to that in ordinary Si n-MOS [25]. A recent IBM 0.1  $\mu$ m Ge p-MODFET is shown in Fig. 16. Transconductances of up to 488 mS/mm at a drain source voltage as low 0.6 V were obtained [26]. For comparison ordinary 0.1  $\mu$ m Si p-MOS exhibits a transconductance of 320 mS/mm at 1.5 V [25]. An 0.15  $\mu$ m self aligned Si<sub>0.2</sub>Ge<sub>0.8</sub> p-MOS structure, using SiN for the gate dielectric [27], displayed a maximum transconductance of 305 mS/mm an  $f_T$  of 62 GHz at low drain source voltage of 0.75 V (compared to approximately 30 GHz at 1.5 V in Si [25]) and an  $f_{max}$  of 68 GHz. We have omitted to mention strained p-channel FETs in

We have omitted to mention strained p-channel FETs in this article, which have also shown promise. The reader is referred to the review of Maiti and co-workers [29].

### 4. Some potential circuit applications

n-type Si/SiGe MODFETs promise improved performances comparable to III-V based circuits in analogue RF circuits and could play an important role in communication systems where they might be used as, for example, front and photoreceivers or low noise amplifiers. Saxarra et al. [29] have fabricated a transimpedance amplifier, based on the n-MODFET described in Section 2, the circuit of which is shown in Fig. 17. It consists of two stages, the input common-source stage having drain to gate feedback to

*Fig. 17.* Two stage transimpedance amplifier using n-MODFETs sketched in Fig. 4.

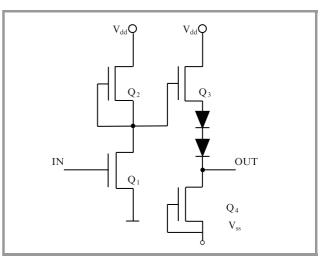

transform current to voltage. The second stage amplifiers the output voltage of the first stage and uses two transistors to increase the gain. Spice simulations suggest a 3 dB  $\Omega$  bandwidth of 4.84 GHz with a gain of 64.7 dB  $\Omega$  for a power supply voltage of 5 V and for a feedback resistor of 1.5 k $\Omega$ , assuming ideal impedance matching. On the other hand, using a feedback resistor of 540  $\Omega$ , the maximum bandwidth measured is 1.8 GHz and the gain is 56 dB  $\Omega$ . The performance shortfall is attributed in part to non-optimum oxide passivation and non-ideal impedance matching. A similar device has been used by Ostermann et al. [30] to fabricate an inverter circuit, Fig. 18.  $Q_1$  is a common source amplifier which feeds on active load  $Q_2$ . The gate delay is 28 ps for 180 nm gate length, 100  $\mu$ m gate width, and power supply voltage  $V_{DD} = 2$  V.

SiGe CMOS offers for the first time the possibility of speeds to approach and match that of GaAs technology while at

Fig. 18. Inverter circuit with source follower, using n-MODFETs sketched in Fig. 4.  $Q_2$  and  $Q_4$  are active loads.

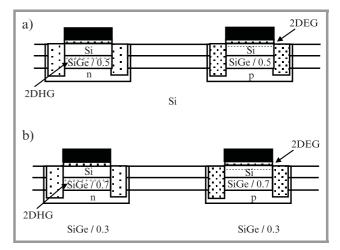

*Fig. 19.* Si/SiGe CMOS process options: (a) giving enhanced p-channel performance, (b) giving enhanced n-channel performance and further enhancement of p-channel performance.

the same time offering p-channel and enhancement mode devices, not available in GaAs, simplifying circuit design. Figures 19a and 19b show, respectively, two process options for (a) a fully pseudomorphic CMOS technology of enhanced p-channel performance and (b) a VS one having both improved n and p-channel performance. A CNET group [11] and a Southampton/Warwick Group [32] have independently attempted the fabrication of a CMOS configuration of type (a). Whereas enhanced p-channel performance was demonstrated in the CNET device, Ge segregation and/or diffusion degraded the performance of the surface n-channel. Similarly, the Southampton p-channel showed enhanced transconductance but the n-channel device properties were poor due to unsuccessful attempts to find a low thermal budget oxide. Nevertheless, these are first attempts and the outlook is promising. As far as we are aware no work has yet been carried out on configuration (b).

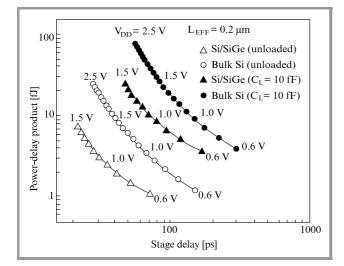

*Fig. 20.* Simulated power delay product versus stage delay for a Si/SiGe CMOS configuration, based on strained silicon and strained SiGe alloy layers, given enhancements in both n- and p-channel current drive (*after Armstrong et al. [34]*).

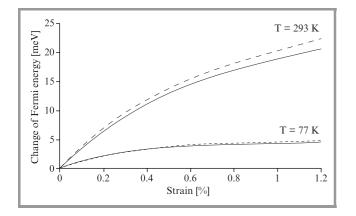

Voinigescu et al. [33] have calculated the 3-stage ring oscillator delay for a fully pseudomorphic Si/SiGe 0.25  $\mu$ m CMOS technology, and for a supply voltage of 2.5 V. Their calculations are based on a fully graded SiGe channel, the Ge fraction varying from 0 at the bottom to 0.5 at the top of the structure, the effective mobility [34] of which is shown in Fig. 2. They obtain a delay of 33 ps per stage compared to 50 ps for the Si CMOS circuit. The power delay products have been calculated by Armstrong et al. [35] for a VS based Si/SiGe CMOS configuration similar to that shown in Fig. 19b and for bulk Si CMOS, and are compared in Fig. 20. The authors assume channel lengths of 0.2  $\mu$ m, gate oxide thicknesses of 5 nm and low field mobilities of 2500  $\text{cm}^2 \text{V}^{-1} \text{s}^{-1}$  and 800  $\text{cm}^2 \text{V}^{-1} \text{s}^{-1}$  for SiGe n-MOS and p-MOS. Factors of 1.23 and 2.25 increases are predicted for n-MOS and p-MOS current drive respectively. The drain current saturates at a low drain bias of 0.4 V for SiGe n-MOS and 0.8 V for SiGe p-MOS. This cuts down the power consumption by up to a factor of 3 or 4! The high carrier mobilities result in a factor of 6.4 improvement in power delay product for the unloaded case and a factor of 4.6 improvement at a delay of 55 ps for the loaded case compared to bulk Si. It is noted that the performance advantage derives largely from the increased current drive of the SiGe p-MOS channel.

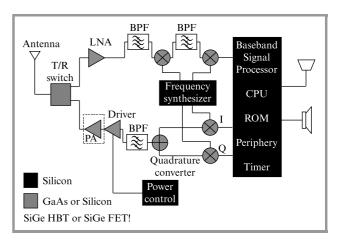

The huge and wide ranging markets in wireless and optical communications offer plenty of opportunities for a SiGe FET technology. The digital wireless handset [36] shown in Fig. 21 may be used to illustrate the potential advantages of SiGe MOS technology, since it contains numerous important building blocks in mobile communications. GaAs currently predominates in the RF section containing the power amplifier (PA), driver amplifier, low noise amplifier (LNA) and transmit/receive (T/R) switch, and competes with silicon in the mixer sections. It is currently being challenged by the SiGe HBT in all these areas. A preferred solution,

*Fig. 21.* Building blocks of a digital handset (*after Costa [35]*). The areas where SiGe FETs could compete are shown shaded.

capable of giving higher levels of integration and lower power consumption is Si CMOS [37]. The incorporation of SiGe into CMOS may be what is needed for this to happen. As the technology matures we might expect that SiGe will bring the high  $f_T$ ,  $f_{max}$ , better linearity and HF noise needed by the LNA. Switched capacitor circuits are promising candidates for band pass filters (BPF). Here the faster switching speed and low power consumption of SiGe CMOS could be of benefit. The good 1/f noise properties referred to in Section 3 could lead the development of low-phase noise local oscillators for the frequency synthesiser. The transmitter power amplifier places particularly onerous demands on Si CMOS. However, good progress is being made in this respect with ordinary Si. For example, an 0.4  $\mu m$  Si n-MOS 2 GHz amplifier has been demonstrated with 1 W output power, 50% PAE at 3.6 V, with satisfactory linearity and a breakdown voltage of 15 V [38]. SiGe should, in principle, be able to significantly improve on these figures.

### 5. Conclusions

The current performance indicators for Si/Ge are such that it offers serious prospects of making significant inroads into, or even displacing, the more mature bulk silicon technology. An example of an early application would be in mobile telephony. Much work is still needed on design, growth and processing before this can happen.

### Acknowledgements

The authors have had stimulating and valuable discussions with A. Asenov, J. Barker, A. Evans, K. Fobelets, M. J. Kearney, U. König, A. O'Neill and C. Pappavasilou.

### References

- R. Dixon, "Silicon germanium", Compound Semicond., vol. 7(1), p. 72, 2000.

- [2] E. H. C. Parker and T. E. Whall, "SiGe heterostructure CMOS circuits and applications", *Solid State Electron.*, vol. 43, p. 1497, 1999.

- [3] T. E. Whall and E. H. C. Parker, "SiGe heterostructures for FET applications", J. Phys. D. Appl. Phys., vol. 31, p. 1397, 1998.

- [4] G. Hock, E. Kohn, C. Rosenblad, H. von Känel, H.-J. Herzog, and U. König, "High hole mobility in Si<sub>0.17</sub>Ge<sub>0.83</sub> channel metal-oxidesemiconductor field-effect transistors grown by plasma-enhanced chemical vapour deposition", *Appl. Phys. Lett.*, vol. 76(26), p. 3920, 2000.

- [5] K. Ismail, "Si/SiGe high speed field-effect transistors", *IEDM Tech. Dig.*, vol. 95, p. 509.

- [6] M. Glück, T. Hackbarth, M. Birk, A. Haas, E. Kohn, and U. König, "Design and fabrication of SiGe n-type MODFETs Physica E: Low Dimensional Systems and Nanostructures", vol. 763, 1998.

- [7] U. König, M. Glück, A. Grable, G. Hock, E. Kohn, B. Bozon, D. Nuernbergk, T. Ostermann, and R. Hagelauer, "Design rules for n-type SiGe hetero FETs", *Solid State Electron.*, vol. 41(10), p. 1541, 1997.

- [8] K. Rim, J. L. Hoyt, and J. F. Gibbons, "Transconductance enhancement in deep submicron strained Si n-MOSFETs", *IEDM Tech. Dig.*, vol. 98, p. 707.

- [9] K. Rim, J. L. Hoyt, and J. F. Gibbons, "Fabrication and analysis of deep submicron strained Si n-MOSFETs", *IEEE Trans. Electron Dev.*, vol. 47(7), pp. 1406–1415, 2000.

- [10] F. Assad, Z. Ren, S. Datta, and M. Lundstrom, "Performance limits of silicon MOSFETS", *IEDM Tech. Dig.*, 1999 (to be published).

- [11] J. Alieu, T. Skotnikii, J. L. Regolini, and G. Bremond, "Multiple SiGe quantum, wells – novel channel architecture for 0.12 μm CMOS", in *Proc. 29th Eur. Solid State Dev. Res. Conf.*, Leuven, Belgium, Sept. 1999, p. 292.

- [12] K. Bhaumik, Y. Shacham-Diamand, J. P. Noel, J. Bevk, and L. C. Feldman, "23 GHz f<sub>T</sub> room temperature SiGe quantum well p-MOSFETs", in *Proc. NRC IMS Epit. Meet.*, Ottawa, March 1994, p. 349.

- [13] Yee Chia Yeo, Vivek Sabramanian, J. Kedzierski, Peiqi Xuan, Tsu-Jae King, Jeffrey Bokor, and Chenning Hu, "Nanoscale ultra-thinbody silicon-on-insulator p-MOSFET with SiGe/Si heterostructure channel", *IEEE Electron Dev. Lett.*, vol. 21, p. 161, 2000.

- [14] M. J. Kearney, A. I. Horrell, H. Fischer, L. Risch, E. H. C. Parker, and T. E. Whall, "Improved room temperature mobility in a coherently strained Si/Si<sub>0.5</sub>/Ge<sub>0.5</sub>/Si p-channel field effect structure", *Appl. Phys. Lett.* (submitted, Sept. 2000).

- [15] T. E. Whall and E. H. C. Parker, "Si/SiGe/Si pMOS performance alloy scattering and other considerations", *Thin Solid Films*, vol. 368, pp. 297–305, 2000.

- [16] M. J. Palmer, G. Braithwaite, T. Grasby, P. J. Phillips, M. J. Prest, E. H. C. Parker, T. E. Whall, C. P. Parry, A. M. Waite, A. G. R. Evans, S. Roy, J. R. Watling, S. Kaya, and A. Asenov, "Effective mobilities in pseudomorphic SiGe p-channel MOSFETs with thin silicon capping layers", *Appl. Phys. Lett.* (submitted, Sept. 2000).

- [17] S. Kaya, Y.-P. Zhao, J. R. Watling, A. Asenov, J. R. Barker, G. Ansaripour, G. Braithwaite, E. H. C. Parker, and T. E. Whall, "Indication of velocity overshoot in strained Si<sub>0.8</sub>Ge<sub>0.2</sub> p-channel MOSFETs", *Semicond. Sci. Technol.*, vol. 15, p. 573, 2000.

- [18] Y.-P. Zhao, S. Kaya, J. R. Watling, A. Asenov, J. R. Barker, M. Palmer, G. Braithwaite, E. H. C. Parker, T. E. Whall, A. Waite, and A. G. R. Evans, "Indication of non-equilibrium transport in SiGe p-MOSFETs", in *Proc. 30th Eur. Solid State Dev. Res. Conf.* (*ESSDERC*), Cork, 2000, pp. 224–227.

- [19] Hideki Takeuchi, Wen-Chin Lee, Pushkar Ranade, and Tsu-Jae King, "Improved pMOSFET short-channel performance using ultra-shallow Si<sub>0.8</sub>Ge<sub>0.2</sub> source/drain extensions", *IEDM Tech. Dig.*, 1999 (to be published).

- [20] Z. Y. Wu, S. Hall, and W. Eccleston, "Suppression of parasitic bipolar action in deep submicron MOSFETs by the use of a narrow band gap source", in *Proc. 25th ESSDERC*, Sept. 1995.

- [21] R. M. Sidek, A. G. R. Evans, and R. A. Kubiak, "Reduction of parasitic bipolar action and punchthrough in MOSFETs using Si/SiGe sources and drains", *Electron Lett.*, vol. 32, p. 269, 1996.

- [22] Wen-Chin Lee, B. Watson, Tsu-Jae King, and Chenning-Hu, "Enhancement of pMOS device performance with poly-SiGe gate", *IEEE Electron Dev. Lett.*, vol. 20, p. 232, 1999.

- [23] M. Prest, C. Brown, H. Fischer, L. Risch, B. Jones, E. H. C. Parker, and T. E. Whall, "Low 1/f noise in a Si/Si<sub>0.5</sub>Ge<sub>0.5</sub>/Si pMOSFET", *Electron Dev. Lett.* (submitted, Sept. 2000).

- [24] M. Glück, T. Hackbarth, U. König, A. Haas, G. Hock, and E. Kohn, "High fmax n-type Si/SiGe MODFETs", IEEE Electron. Lett., vol. 33(4), p. 355, 1997.

- [25] Yuan Taur, A. Buchanan, W. Chen, D. J. Frank, K. E. Ismail, S.-H. Lo, G. A. Sai-Halasz, R. G. Viswanathan, H.-J. C. Wann, S. J. Wind, and H.-S. Wong, "CMOS scaling into the nanometre regime", *Proc. IEEE*, vol. 85(4), p. 486, 1997.

- [26] R. Hammond, S. J. Koester, and J. O. Chu, "Extremely high transconductance Ge/Si<sub>0.4</sub>Ge<sub>0.6</sub> pMOSFETs grown by UHV-CVD", *IEEE Electron Dev. Lett.* (to be published).

- [27] W. Lu, R. Hammond, S. J. Koester, X. W. Wang, J. D. Chu, T. P. Na, and I. Adesida, "High performance 0.15 self aligned SiGe p-MOS-MODFETs with SiN gate dielectric", *IEDM Tech. Dig.*, 1999 (to be published).

- [28] C. K. Maiti, L. K. Bera, and S. Chattopadhyay, "Strained-Si heterostructure field-effect transistors", *Semicond. Sci.Tech.*, vol. 13, p. 1225, 1998.

- [29] M. Saxarra, M. Glück, J. N. Albers, D. Behammer, U. Langmann, and U. König, "Transimpedance amplifiers based on Si/SiGe MODFETs", *Electron Lett.*, vol. 34(5), p. 49, 1998.

- [30] T. Ostermann, M. Glück, R. Hagelauer, U. König, M. Dobersberger, M. Birk, and F. Vehler, "Inverter circuits with Si/SiGe n-type MODFETs", in *Proc. Int. Semi. Dev. Res. Symp.*, Charlottesville, Va, 1997.

- [31] R. M. Sidek, U. N. Straube, A. M. Waite, A. G. R. Evans, C. Parry, P. Philips, T. E. Whall, and E. H. C. Parker, "SiGe CMOS fabrication using SiGe MBE and an anodic/LTO gate oxide", *Semicond. Sci. Tech.*, vol. 15, p. 135, 2000.

- [32] S. Voinigescu, P. Rabkin, C. A. T. Salama, A. Tcherniaev, R. Cottle, and P. Blakey, "Submicron Si/SiGe CMOS circuit potential determined using mixed-mode device-circuit simulation", *Simulat. Standard*, vol. 4(5), 1993.

- [33] S. Voinigescu, C. A. T. Salama, J. P. Noel, and T. I. Kamins, "Si/SiGe heterostructure pMOSFET with triangular Ge channel profiles", *IEDM Tech. Dig.*, vol. 94, p. 369.

- [34] M. A. Armstrong, D. A. Antoniadis, A. Sadek, K. Ismail, and F. Stern, "Design of Si/SiGe heterostructure complementary metaloxide-semiconductor transistors", *IEDM Tech. Dig.*, vol. 95, p. 7861.

- [35] J. C. Costa, "Heterostructure FETs for digital wireless communications", *Compound Semicond.*, vol. 5(4), p. 42, 1999.

- [36] B. Razavi, "Challenges in portable RF transceiver design", *IEEE Trans. Circ. Dev.*, vol. 2, p. 12, 1996.

- [37] Isao Yoshida, "2 GHz Si power MOSFET technology", IEDM Tech. Dig., vol. 97, p. 51.

**Terrence E. Whall** – BSc(Hons), City University 1964, D Phil, University of Sussex 1969; Research Fellow London University 1969–71, Lecturer/Senior Lecturer Portsmouth University 1971–87, Lecturer 1987–89, Senior Lecturer 1989–95, Reader 1995–98, Personal Chair 1998-, Department of Physics, University of Warwick. Research Profile: Research career devoted to experimental investigations of the synthesis and electrical properties of a wide range of materials. Since 1987 has lead the electrical characterisation and device physics work in the Semiconductor Group at Warwick. Along with Professor Parker spearheaded the UK consortium research activity (involving seven universities, UK/German industry) evaluating the prospects for SiGe MOS technologies. Has given numerous invited talks and has produced over 200 publications. e-mail: T.E.Whall@warwick.ac.uk Department of Physics University of Warwick

Coventry CV4 7AL, UK

**Evan H. C. Parker** – Dip. Tech(Hons), City University 1964, D Phil University of Sussex 1968; Research Scientist – Zenith Radio Research Corporation 1968–1971; Lecturer (1971, Senior Lecturer 1976), Sir John Cass Reader 1984–86, Sir John Cass College of Science and Technology,

London. Professor of Semiconductor Physics 1986-present, Department of Physics, University of Warwick. Leader: Semiconductor Research Group (currently 20 personnel). Research Profile: Since 1978 have worked on thin semiconducting layers - PbTe, InGa, GaAs, and since 1980 Si, SiGe and SiGeC. The work of the semiconductor group is concerned with the study of MBE growth and the physics and device properties of Si-SiGe-SiGeC heterostructures. Along with Professor Whall he spearheaded a consortium research activity (involving nine universities, UK/German industry) evaluating the prospects for SiGe MOS technologies. AVS Prize 1983. Chaired/co-chaired several of the international symposia on Si-MBE, given numerous invited talks, produced over 250 publications (including two books and several Editorships) and has acted as a consultant for UK, German and Japanese industry.

e-mail: E.H.C.Parker@warwick.ac.uk Department of Physics University of Warwick

Coventry CV4 7AL, UK

*Fig. 6.* Showing (a) strained Si n-MOSFET and (b) unstrained Si control device structures. Boron profile control is aided by  $Si_{0.8}Ge_{0.2}$  diffusion barriers in each case (*after Rim et al. [8]*).

Invited paper

## Reliability of deep submicron MOSFETs

Francis Balestra

Abstract — In this work, a review of the reliability of n- and p-channel Si and SOI MOSFETs as a function of gate length and temperature is given. The main hot carrier effects and degradations are compared for bulk and SOI devices in a wide range of gate length, down to deep submicron. The worst case aging, device lifetime and maximum drain bias that can be applied are addressed. The physical mechanisms and the emergence of new phenomena at the origin of the degradation are studied for advanced MOS transistors. The impact of the substrate bias is also outlined.

Keywords — bulk MOSFETs, SOI devices, deep submicron transistors, reliability.

### 1. Introduction

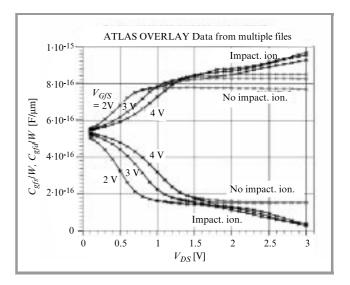

It is well known that hot-carrier-induced device degradation (creation of interface states and/or positive and negative trapped charges by electron or hole injection) can limit the long-term reliability of deep submicron MOSFETs (reduction of transconductance and drain current, shift of the threshold voltage). The impact ionization phenomenon is one of the main hot carrier effects  $[1 \div 6]$ . We can distinguish two stress regimes, which depend on the electron energy. The first one corresponds to the primary impact ionization in maximal substrate current condition ( $V_g \cong V_{d/2}$ ). The second stress regime corresponds to the secondary impact ionization in maximal gate current condition  $(V_g \cong V_d)$ . The longitudinal electric field responsible for the primary impact ionization produces hot carriers with energy around 1.5 eV [3]. Monte Carlo simulations have shown that the secondary ionization generates hot carriers with energy values higher than  $3 \div 3.5$  eV after a secondary heating in the drain/substrate junction. These energies correspond to the interface state threshold energy [4, 5]. The interface state creation is one of the major causes of device degradation. Nevertheless, several issues are still not clear up to now:

- 1. What is the worst case aging condition (maximum substrate or gate currents) as a function of gate length and temperature?

- 2. Which physical mechanisms are at the origin of the main degradation for advanced devices?

- 3. Is there some differences for the aging of bulk Si and SOI MOSFETs?

- 4. What are the lifetime and maximum drain bias which can be applied as a function of device architecture?

In this work, the hot carrier phenomena and degradation in various regimes of n- and p-channel bulk silicon and silicon-on-insulator MOSFETs are studied in a wide range of gate length down to deep submicron as a function of temperature.

### 2. Results and discussion

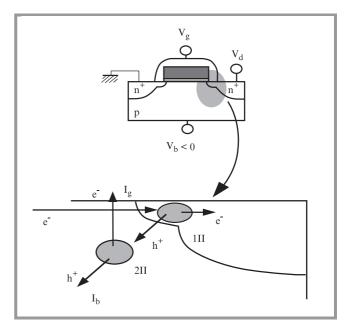

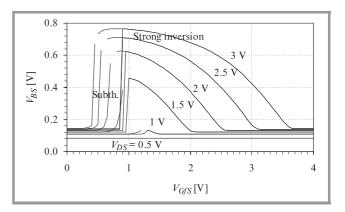

### 2.1. Bulk Si MOSFETs

Figure 1 shows the secondary impact ionization mechanisms. The first ionization leads to electron/hole pairs. The electrons flows towards the drain for a n-channel MOS-FET and the holes are heated in the drain substrate junction where high electric fields exist for advanced MOSFETs due to high substrate doping. These holes gain high energies and can induce a second impact ionization leading to electrons/holes pairs. The holes constitute the substrate current and the electrons can be injected into the gate in particular for deep submicron devices realized with ultra-thin gate oxides leading to high transverse electric field. These electrons are at the origin of the gate current or can be trapped in this oxide.

Fig. 1. Secondary impact ionization mechanisms.

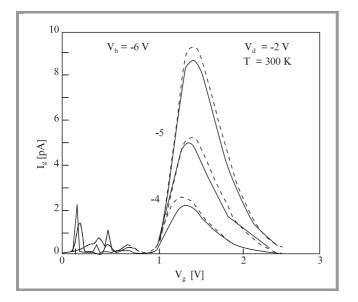

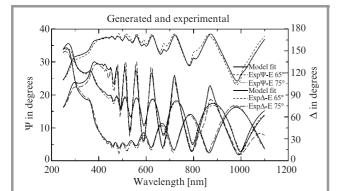

Figure 2 exemplifies the gate current as a function of the substrate bias for a 0.45  $\mu$ m MOSFET of a 0.1  $\mu$ m technology with a 3.5 nm gate oxide [7]. The substrate bias is used in this experiment in order to enhance the electric field at the drain/substrate junction leading to a higher secondary impact ionization. The gate current induced by

this secondary heating obtained with a model based on the lucky electron concept is also shown in this figure. The good agreement observed between theory and experiment confirms the origin of this gate current. Therefore these additional hot carrier effects will play a major role for determining the worst case degradation and the reliability of advanced MOS transistors.

**Fig. 2.** Comparison between model and experimental data for the gate current of advanced bulk Si devices (0.45  $\mu$ m N-MOSFET of a 0.1  $\mu$ m technology with a 3.5 nm gate oxide) taking into account the secondary impact ionization.

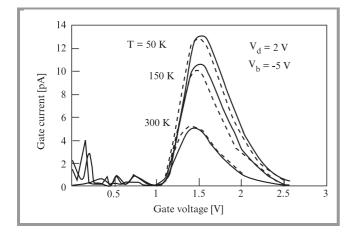

Figure 3 is a plot of the impact of temperature on the gate current characteristics.  $I_g$  is substantially increased at low temperature even for a low drain voltage (2 V). The model taking into account the secondary impact ionization is also in good agreement with the experimental data.

**Fig. 3.** Impact of temperature (experiment and modeling) on the  $I_g(V_g)$  characteristics for a 0.45  $\mu$ m bulk N-MOSFET of a 0.1  $\mu$ m technology with a 3.5 nm gate oxide.

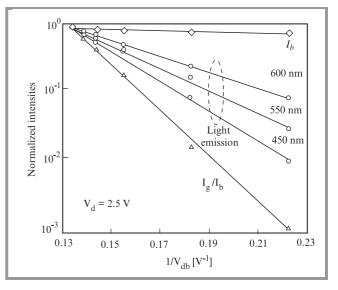

The number of emitted photons due to hot electrons as a function of energy is plotted in Fig. 4. The impact of the substrate bias on the light emission is also shown. For small energies  $(1 \div 1.5 \text{ eV})$  the substrate voltage has a very small impact. However, for high energies  $(2 \div 3 \text{ eV})$ , the number of emitted photons substantially increases at high  $V_b$  due to the secondary heating at the drain/substrate junction. These hot carriers can lead to significant device degradation.

**Fig. 4.** Impact of the substrate bias on the light emission for deep submicron bulk MOSFETs.

**Fig. 5.** Correlation between the normalized gate and substrate currents and the wavelength of emitted photons for bulk silicon n-channel MOSFETs.

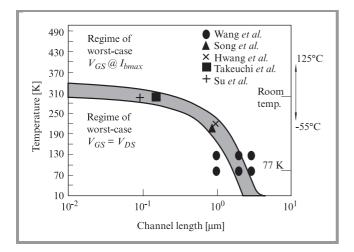

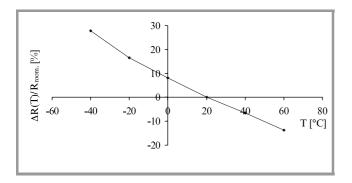

Figure 5 presents the correlation between the light emission and the normalized gate and substrate currents. For long wavelengths, the variation of the light emission is similar to that of the substrate current (first heating), and for small wavelengths it is correlated with the gate current (second heating). The impact of both the channel length and temperature on the worst case aging is exemplified in Fig. 6 [8]. For long devices, the worst case corresponds to the maximum substrate current  $(V_g \cong V_{d/2})$  except for very low temperatures. However, for deep submicron devices  $(0.1 \ \mu\text{m} \text{ range})$  the limit between the two worst case regimes  $(V_g = V_{d/2} \text{ or } V_d)$ is observed in the room temperature range. Therefore, the maximum gate current  $(V_g \cong V_d)$  could become the worst case degradation even at 300 K. Furthermore, in the traditional operating range (between  $-50^{\circ}\text{C}$  and  $100^{\circ}\text{C}$ ) the worst case can shift from a regime to another one for advanced MOSFETs.

**Fig. 6.** Impact of channel length and temperature on the worst case degradation (bulk NMOS).

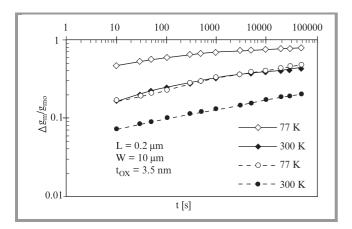

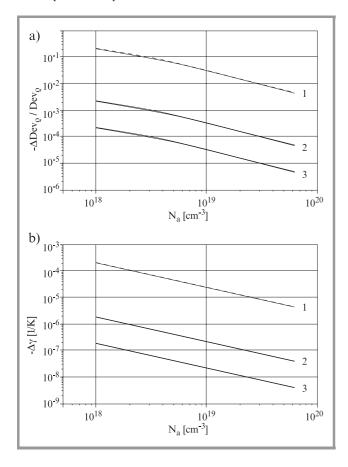

The influence of the substrate voltage for various temperatures is exemplified in Fig. 7. The significant impact of the substrate bias on the transconductance degradation both at 300 and 77 K demonstrates that the secondary heating plays a major role in the reliability of the devices. The maximum drain bias which can be applied in order to obtain a ten years lifetime (criterion: 10% transconductance

**Fig. 7.** Impact of substrate bias for bulk N-MOSFET devices on transconductance degradation for  $I_{g \max}$  stress ( $V_b = -3$  V full lines,  $V_b = 0$  V dashed lines).

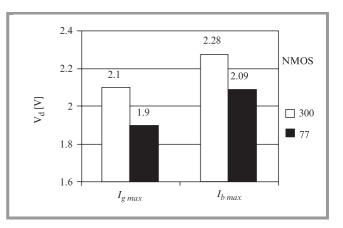

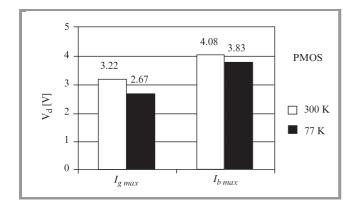

degradation under static stress) is analyzed for 0.2  $\mu$ m MOS transistors. The worst case aging leading to the minimum  $V_{d \max}$  is obtained for a stress in  $I_{g \max}$  condition both at room and liquid nitrogen temperatures (Fig. 8). In addition, a stronger degradation is always observed at 77 K as compared to 300 K, even in the case of  $I_{b \max}$  stress (Fig. 8). In this regime, a smaller substrate current and impact ionization rate have been previously shown, but the enhancement of carrier trapping and the larger influence of a given degradation on the electrical properties at low temperature could explain this special behavior.

**Fig. 8.** Maximal drain voltage in order to obtain 10% transconductance degradation after 10 years for bulk N-MOSFET (W/L = 10/0.2,  $t_{ox} = 3.5$  nm); static stress.

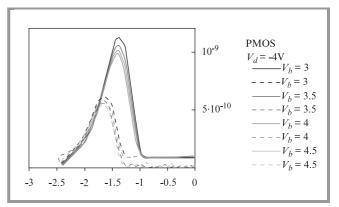

**Fig. 9.** Typical  $I_g(V_g)$  characteristics obtained at  $V_d = -4$  V for different substrate voltages at 300 K (full lines) and 77 K (dashed lines) (bulk PMOS, W/L = 10/0.2,  $t_{ox} = 3.5$  nm).

Therefore, the impact of the secondary hot carrier effects is clearly demonstrated at room and low temperature for advanced n-channel MOSFETs.

Figure 9 exemplifies the typical gate current characteristics for a  $0.2 \,\mu\text{m}$  p-channel bulk Si MOSFET. An electron current is found whatever the substrate and drain biases are. The substrate voltage has only a very low influence on the gate current level (small reduction with increasing the substrate bias). These results show that the influence of the secondary impact ionization is negligible for PMOS devices. Furthermore, contrary to the case of n-channel MOSFETs,  $I_g$  is reduced for lower temperatures (Fig. 9).

**Fig. 10.** Maximal drain voltage in order to obtain 10% transconductance degradation after ten years (static stress) (bulk PMOS, W/L = 10/0.2,  $t_{ox} = 3.5$  nm).

**Fig. 11.** Maximal drain voltage in order to obtain 100 mV threshold voltage degradation after ten years (static stress) (bulk PMOS, W/L = 10/0.2,  $t_{ox} = 3.5$  nm).

**Fig. 12.** Maximal substrate voltage in order to obtain 10% transconductance degradation after ten years (static stress) (bulk NMOS, W/L = 10/0.2,  $t_{ox} = 3.5$  nm,  $V_d = 2$  V).

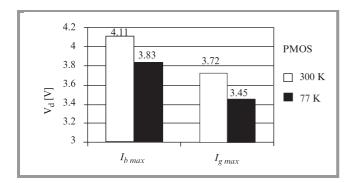

The maximum drain bias which can be applied in order to obtain a ten years lifetime (criterion: 10% transconductance degradation under static stress) is shown in Fig. 10. The worst case aging is obtained for a stress performed at  $V_g = V_d$  (noted ,, $I_{gmax}$ "). However, it is worth noting that the maximum gate current is reached for a gate voltage substantially lower than the drain bias in the case of P-MOSFETs (see Fig. 9). The drain voltage  $V_{dmax}$  for a 10 years lifetime is also reduced at 77 K as compared to room temperature operation, even if the substrate and gate currents are smaller at liquid nitrogen temperature. Therefore, for deep submicron devices, a stress at  $V_g = V_d$  for a 77 K operation is always the worst case for PMOS and NMOS. A similar trend is observed for the threshold voltage degradation (Fig. 11).

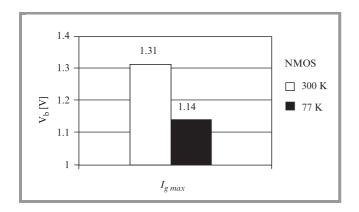

The maximum substrate bias, which can be applied in order to obtain a 10 years lifetime for a  $0.2 \,\mu\text{m}$  bulk Si N-MOSFET, is illustrated in Fig. 12. A nominal bias (2 V) is applied for this  $0.2 \,\mu\text{m}$  technology.  $V_{b\,\text{max}}$  is around 1.3 V at 300 K and 1.1 V at 77 K, which shows that the applied substrate bias could become a limitation in some applications.

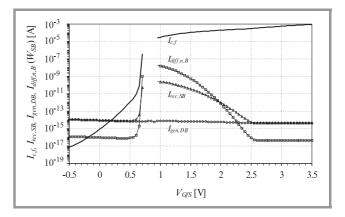

### 2.2. SOI MOSFETs

The SOI technology is well known for its advantages as compared to bulk devices, in particular in the field of low voltage/low power and high frequency applications [9, 10]. However, SOI MOSFETs can suffer from possible degradation of the front and the buried silicon/oxide interfaces. Furthermore, another hot carrier regime associated with the parasitic bipolar transistor triggered at high  $V_d$  can be harmful for deep submicron SOI devices. Therefore, it is necessary to perform a thorough evaluation of these effects as function of the SOI transistor architecture.

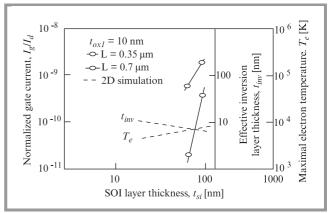

**Fig. 13.** Comparison between the variations of the normalized gate current, the inversion layer thickness and the electron temperature versus Si film thickness for fully depleted SOI MOSFETs.

In Fig. 13 the dependence of the normalized gate current versus the silicon film thickness is plotted [11]. The gate current is reduced for thinner films whatever the gate length is. This interesting behavior is partially attributed to the increase of the inversion layer thickness in fully depleted SOI films which is induced by the reduction of the transverse electric field. This phenomenon leads to a reduction of carrier temperature. However, another possible effect in order to explain the decrease of hot carrier effects is the lowering of the secondary impact ionization. Indeed, in thin film SOI, the area of the drain/substrate junction decreases as compared to thick Si layers or bulk MOSFETs, and therefore a reduction of the number of high energy carrier is obtained. Moreover, the reduction of the transverse electric field also leads to a smaller injection probability into the gate.

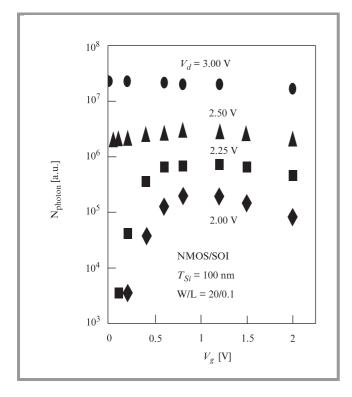

Fig. 14. Number of emitted photons in  $0.1 \,\mu\text{m}$  n-channel SOI MOSFET versus gate and drain biases.

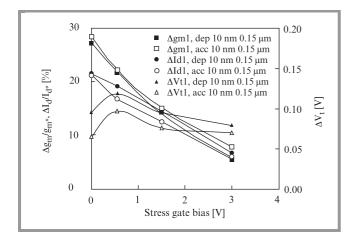

**Fig. 15.** Device parameter degradation as a function of gate bias for 0.15  $\mu$ m n-channel SOI MOSFETs realized on an ultra-thin (10 nm) Si film thickness measured with accumulated or depleted opposite interface.

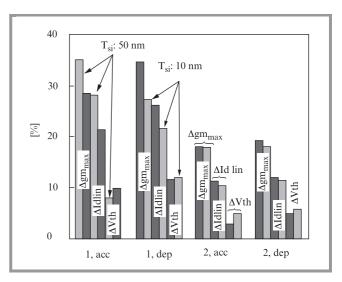

However, another typical SOI mechanism associated with the floating body has to be taken into account for long term device reliability. Figure 14 shows the number of emitted photons for a 0.1  $\mu$ m SOI MOSFET versus gate and drain biases [12]. For small gate and high drain voltages, a large increase of the photon number is observed due to the parasitic bipolar transistor (PBT) action inducing high energy carriers. Contrary to the case of bulk Si MOSFETs, as illustrated in Fig. 15 for a 0.15  $\mu$ m fully depleted SOI device fabricated on a 10 nm Si layer thickness, the worst case aging is obtained for small gate biases (0 ÷ *V*<sub>*t*</sub>) due to this PBT action [13].

**Fig. 16.** Device degradation  $(I_d, gm, V_t)$  at the front (1) and back (2) interfaces as a function of Si layer thickness (10 and 50 nm) measured with accumulated or depleted opposite interface for n-channel fully depleted SOI MOSFETs.

**Fig. 17.** Maximum drain bias that can be applied in order to obtain 10 years device lifetime (static stress) versus gate length for partially depleted (100 nm Si film thickness) n-channel SOI MOSFETs.

Figure 16 presents the impact of the Si film thickness on fully depleted SOI device degradation in the PBT regime [13]. It is clear that a reduction of the transconductance and drain current degradation is obtained with reducing the SOI layer thickness. In particular, a significant decrease of the front interface aging is observed, while similar degradations are observed for the back interface due to larger interface coupling in ultra-thin films.

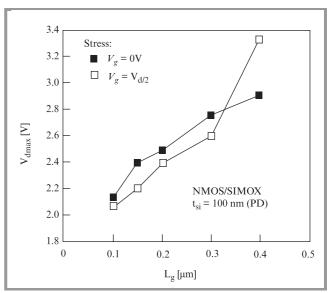

The reliability of partially depleted SOI MOSFETs is exemplified in Fig. 17 [12]. The maximum drain bias which can be applied in order to obtain a 10 years lifetime is shown. For this device architecture, the worst case aging with a minimum  $V_{d \text{ max}}$  is observed in the maximum substrate current condition  $(V_g = V_{d/2})$  in the deep submicron range. Therefore, contrary to the case of bulk devices, the worst case aging is obtained for low gate voltages  $(0 \div V_{d/2})$ in n-channel SOI MOSFETs whatever the device architecture is.

### 3. Conclusion

A review of the reliability of n- and p-channel bulk Si and SOI MOSFETs as a function of gate length and temperature has been given. The worst case aging, device lifetime and maximum drain bias that can be applied have been addressed. The impact of the substrate bias has also been outlined. The worst case degradation has been found at  $V_g = V_d$  (which corresponds to the maximum gate current condition for n-channel) for deep submicron bulk Si MOS-FETs whatever the temperature is and for long channel transistors at low temperature. The substantial influence of the secondary impact ionization on the degradation has been clearly demonstrated for very short channel N-MOSFETs. The interest of using ultra-thin film SOI MOS transistors for reducing the secondary impact ionization and device aging has also been pointed out. Contrary to the case of bulk MOSFETs, the worst case aging has been found for small gate biases  $(0 \div V_{d/2})$  in all the n-channel SOI devices.

### References

C. Hu, S. Tam *et al.*, *IEEE TED*, vol. ED-32, no. 2, p. 375, 1985.

A. Raychaudhuri *et al.*, *IEEE TED*, vol. 43, no.7, p. 1114, 1996.

- J. D. Bude and M. Matrapasqua, *IEEE Elec. Dev. Lett.*, vol. 16, no. 10, p. 439, 1995.

- 4) Masunaga et al, Jap. J. Appl. Phys., vol. 19, suppl. 19-1, p. 93, 1980.

- 5) D. Bude, IEDM Tech Dig., p. 865, 1996.

- Takeda et al., "Hot carrier effects in MOS devices", Ac. Press, p. 123, 1995.

- B. Marchand, B. Cretu, G. Ghibaudo, F. Balestra, D. Blachier, C. Leroux, S. Deleonibus, G. Guegan, G. Reimbold, S. Kubicek, and K. De-Meyer, in *Proc. ULIS'2000*, Grenoble, France, Jan. 2000, p. 9.

- 8) J. Wang Ratkovic et al., in Proc. ESREF'97, p. 1747.

- 9) J. P. Colinge, *Silicon-on-Insulator Technology: Materials to VLSI*. Kluwer Academic Publishers, 1991.

- S. Cristoloveanu and S. S. Li, *Electrical Characterization of Silicon*on-Insulator Materials and Devices. Kluwer Academic Publishers, 1995.

- Y. Omura, "An improved analytical solution of energy balance equation for short-channel SOI MOSFET's and transverse-field-induced carrier heating", *IEEE Trans. Electron Dev.*, vol. ED-42, p. 301, 1995.

- S. H. Renn, J. L. Pelloie, and F. Balestra, "Hot carrier effects in deep submicron thin film SOI MOSFETs", *IEDM Tech. Dig.*, p. 877, 1996.

- O. Potavin, S. Haendler, C. Raynaud, J. Jomaah, and F. Balestra, in Proc. ULIS'2000, Grenoble, France, Jan. 2000, p. 43.

**Francis Balestra** received the B.Sc. degree from the University of Provence, France in 1981 and the M.Sc. and Ph.D. degrees in electronics from the Institut National Polytechnique, France, in 1982 and 1985, respectively. Currently he is with the Laboratoire de Physique de Composants a Semiconducteurs (LPCS), which he has been heading since 1999. His research interests include deep submicron CMOS, SOI devices, low temperature electronics and polysilicon emitter bipolar transistors for BiCMOS technology. Dr. Balestra has co-authored over 80 publications in international scientific journals and 120 communications at national and international conferences (20 invited papers and review articles).

e-mail: balestra@enserg.fr LPCS (CNRS/INPG), ENSERG 23 Av. des Martyrs, BP 257 38106 Grenoble, France

## High-temperature instability processes in SOI structures and MOSFETs

Alexei N. Nazarov, V. I. Kilchytska, Ja. N. Vovk, and J. P. Colinge

Abstract — The paper reviews the problems related to BOX high-temperature instability in SOI structures and MOSFETs. The methods of bias-temperature research applied to SOI structures and SOI MOSFETs are analysed and the results of combined electrical studies of ZMR, and SIMOX SOI structures are presented. The studies are focused mainly on electrical discharging processes in the BOX at high temperature and its link with new instability phenomena such as high-temperature kink effects in SOI MOSFETs.

Keywords — SOI, MOSFET, high-temperature instability, ZMR, SIMOX.

### 1. Introduction

Devices fabricated on silicon-on-insulator (SOI) structures are very promising for high-temperature microelectronics [1]. Consequently, the high-temperature stability of SOI structures is the necessary condition for proper device operation. From this point of view, the main weakness of SOI structures is thick buried oxide (BOX), which can effectively accumulate a positive and a negative charge during the application of sufficiently low electric fields to SOI structures [2, 3].

Thus, the paper is devoted to review high-temperature instability phenomena in SOI structures and devices especially with respect to bias-temperature (BT) processes in the BOX.

### 2. Methods for electrical characterization of high-temperature instability processes

### 2.1. Capacitance-voltage method for SOI structures

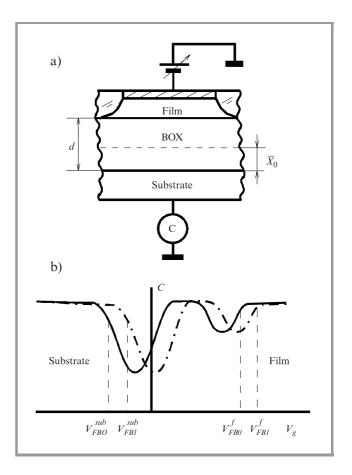

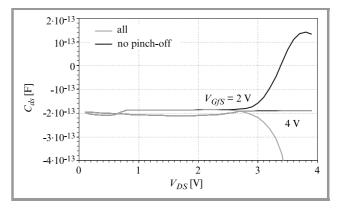

The most widely used method to study the BT instability is the analysis of capacitance-voltage (C-V) curves. In this method measurements are performed at room temperature before and after application of the bias to the gate of SOI structure at high temperature. For SOI structures the C-V method is very useful, since it permits the potentials at BOX/substrate and at BOX/film interfaces (Fig. 1a) and, consequently, the total net charge,  $Q_{tn}$ , in the BOX and its centroid,  $X_0$ , to be determined. As it was proposed in [4, 5]

$$Q_{tn} = Q_f + Q_{sub} = \frac{C_d \left( V_{FB}^f - V_{FB}^{sub} \right)}{qS} , \qquad (1)$$

$$X_{0} = \frac{\int_{0}^{d} \rho(x) x dx}{\int_{0}^{d} \rho(x) x dx} = \frac{\left| V_{FB}^{f} \right| d}{V_{FB}^{f} - V_{FB}^{sub}},$$

(2)

where  $V_{FB}^{f}$ ,  $V_{FB}^{sub}$  are flat-band voltages related to the film/BOX and the substrate/BOX interfaces, respectively,  $\rho(x)$  is the charge distribution in the BOX, *d* is the BOX thickness,  $C_d$  is the buried insulator capacitance. The centroid is determined with respect to the BOX/substrate interface (Fig. 1b).

*Fig. 1.* A schematic diagram of a SOI capacitor (a) and low-frequency C-V characteristics before (bold line) and after (dotted line) BT stress (b).

The amount of the mobile charge related to the BOX/film interface,  $\Delta Q_m^f$ , and to the BOX/substrate interface,  $\Delta Q_m^{sub}$ , after BT stress can be calculated as

$$\Delta Q_m^f = \frac{C_d \left( V_{FB1}^f - V_{FB0}^f \right)}{qS} = \frac{C_d \Delta V_{FB}^f}{qS} \tag{3}$$

and

$$\Delta Q_m^{sub} = \frac{C_d \,\Delta V_{FB}^{sub}}{qS} \,, \tag{4}$$

where  $V_{FB1}$ ,  $V_{FB0}$  are flat-band voltages after and before BT stress, respectively (see Fig. 1a). Thus, the change of the charge in the BOX is

$$\Delta Q_{tr} = \Delta Q_m^f - \Delta Q_m^{sub} \,. \tag{5}$$

If  $\Delta Q_{tr} = 0$ , we can consider the BOX/semiconductor interfaces as electrically blocking ones, if  $\Delta Q_{tr} \neq 0$ , interfaces are electrically unblocking.

### 2.2. Thermally stimulated polarization/depolarization currents

Thermally stimulated polarization/depolarization (TSP/ TSD) current method is used to investigate the charge transfer processes in a dielectric during linear heating of the structure, holding a fixed voltage across the capacitors and measuring the resulting current (Fig. 2).

It has been shown that charge moving in the outer circuit during the polarization or depolarization processes,

*Fig. 2.* Schematic time diagrams of temperature (a) and applied voltage (b), and TSP/TSD current (c).

$Q_{TSP/TSD}$ , is equal to the mirror charge at the blocking electrode [6]. Therefore:

$$Q_{TSP/TSD} = \frac{1}{\beta S} \int_{T_0}^T I(T) dT = \Delta Q_m^f , \qquad (6)$$

if the BOX/film interface is blocking, or

$$Q_{TSP/TSD} = \Delta Q_m^{sub} \tag{7}$$

if the BOX/substrate interface is blocking, where  $\beta$  is the heating rate.

Thus, the comparison of C-V with TSP/TSD data allows to identify the electrically blocking interfaces and to determine the degree of blocking.

In addition, the TSP/TSD method gives the possibility of determination the activation energies of the polarization/depolarization processes and the frequency factor or capture cross section for traps involved in the processes (see, for instance [7]). In the case of energy distributed traps the fractional thermally cleaning method can be used in order to calculate the trap parameters [8].

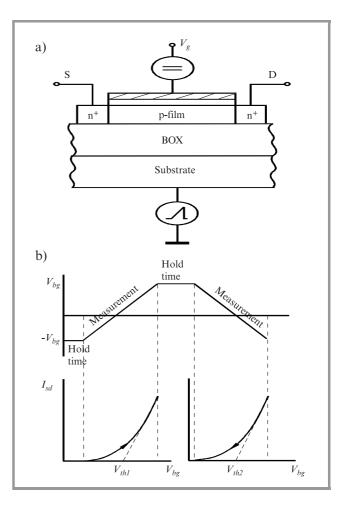

*Fig. 3.* A schematic diagram of a SOI MOSFET (a) and the applied voltage at the back-gate (b) for BT instability measurements using the drain-gate characteristic technique.

### 2.3. Source-drain current – gate voltage characteristics of MOSFETs

Source-drain current  $I_{sd}$  – gate voltage  $V_g$ , characteristics at high temperature enable the polarization parameters to be determined and the operation stability of the devices to be analysed. Measurement of the source-drain current,  $I_{sd}$ , in the back channel SOI MOSFET at high temperature, after holding the back-gate voltage positive or negative (Fig. 3), permits the change in the charge in the BOX layer relative to the BOX/film interface to be determined:

$$\Delta Q_m^f = C_d \frac{V_{th1} - V_{th2}}{qS} = \frac{C_d \Delta V_{th}}{qS} , \qquad (8)$$

where  $V_{th1}$ ,  $V_{th2}$  are back-channel threshold voltages after negative and positive applied voltage to the back-gate, respectively.

Investigation of the threshold voltage shift as a function of temperature and hold time permits all main parameters of high temperature instability processes to be calculated.

### 2.4. Source-drain current relaxation

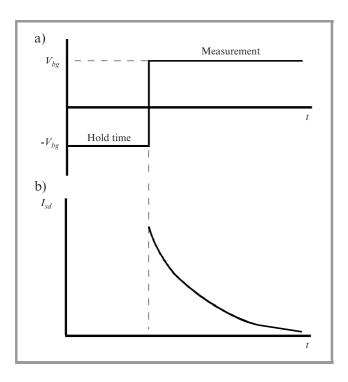

If at high temperature the polarity of the back-gate voltage is reversed and, as result, relaxation of the source-drain current occurs it is possible to determine the relaxation time of the processes, that links with the relaxation time of the charge changing in the BOX. This phenomenon is depicted

*Fig. 4.* A schematic diagram for (a) back-gate voltage switching and (b) measurement of the relaxation current.

schematically in Fig. 4. Indeed, as it was shown in [9] in the linear regime of the inversion mode (IM) SOI n-MOSFET operation, the source-drain current can be given by

$$I_{sd}(t,T) = \left(\frac{W}{L}\right) \mu_e C_d \left[V_{bg} - V_{thb}^* + Q_{BOX}(t,T)/C_d\right] V_{sd} ,$$

(9)

where W, L are the width and the length of the channel,  $\mu_e$  is the electron mobility in the inversion channel,  $V_{bg}$  is the back-gate voltage,  $V_{thb}^*$  is constant with weak temperature dependence,  $Q_{BOX}$  is the total buried oxide charge,  $V_{sd}$  is source-drain voltage. That is, the source-drain current relaxation is directly linked with buried oxide charge changing.

If the BOX charge depends on the time and temperature as:

$$Q_{BOX}(t,T) = Q_{BOX}(t=0) \exp\left[-\frac{t}{\tau(T)}\right]$$

(10)

the relaxation time,  $\tau(T)$ , can be calculated from slope angle tangent of the following dependence:

$$\ln \frac{I_{sd}(t) - I_{sd}(\infty)}{I_{sd}(0) - I_{sd}(\infty)} = -\frac{t}{\tau} , \qquad (11)$$

where  $I_{sd}(0)$  and  $I_{sd}(\infty)$  are the source-drain current at first and at final moment, respectively.

The measurement of source-drain current relaxation at different temperature allows the activation energy of the instability processes to be determined.

Thus, a combination of the C-V and the TSP/TSD current methods with  $I_{sd}$ - $V_{bg}$  characteristics of MOSFETs fabricated on the same SOI wafer opens a wide range of possibilities for the study of high-temperature instability processes in the BOX.

## 3. High-temperature instability in buried oxide of SOI structures

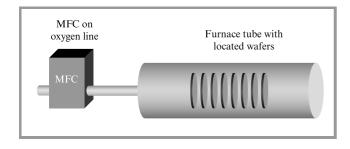

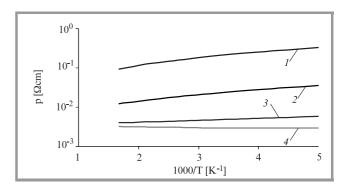

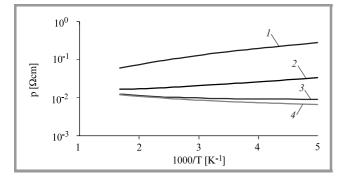

### 3.1. Structure fabricated by zone-melting recrystallization technique

The SOI structures used in this study have been fabricated by the laser zone-melting recrystallization (LZMR) technique [10]. A linear melted zone was formed by a highpower CW YAG:Nd laser. A circular laser beam was transformed into a linear spot with thickness of 0.1 mm using special cylindrical lenses. In order to provide a low thermal gradient regime the wafer was heated up to  $1300^{\circ}$ C from the back side by a set of halogen lamps. Recrystallized structure was composed of a 400 nm thick poly-Si film deposited on silicon wafer thermally oxidized at high pressure ( $d_{BOX} = 360$  nm) and covered by a SiO<sub>2</sub> cap layer to prevent agglomeration of the molten zone. SOI capacitors (Al-Si-SiO<sub>2</sub>-Si-Al) were fabricated by LOCOS technique after recrystallization of polysilicon film. Measurements of the C-V characteristics of LZMR SOI capacitors before and after TSP and TSD processes up to 400°C has led to the conclusion that the BOX/semiconductor interfaces in this material are almost blocking (Table 1) [11]. Bias application to the SOI structure at high temperature leads to charge movement from one interface to the other. During this movement only 10% of the charge is lost. Comparison of the total net charge in the BOX, obtained by C-V method, with moving charge in the BOX, obtained by TSP/TSD current method, helps us to conclude that almost all of the positive charge, which is trapped in the BOX, participated in the observed movement of charge.

#### Table 1

Total,  $Q_{tn}$  and mobile charges,  $Q_{TSP}$  and  $Q_{TSD}$ , and charge centroid in buried SiO<sub>2</sub> in ZMR SOI structures

| $Q_{tn}  [\rm cm^{-2}]  (\rm C-V)$ |                    |                    | $\overline{X}_0$ [Å] (C-V) |           |           | $Q_{TSP}$        | $Q_{TSD}$            |

|------------------------------------|--------------------|--------------------|----------------------------|-----------|-----------|------------------|----------------------|

| initial                            | after TSP          | after TSD          | initial                    | after TSP | after TSD | $[cm^{-2}]$      | $[\mathrm{cm}^{-2}]$ |

| $1\cdot 10^{12}$                   | $8.3\cdot 10^{11}$ | $9.4\cdot 10^{11}$ | 1070                       | 1900      | 380       | $5\cdot 10^{11}$ | $7\cdot 10^{11}$     |

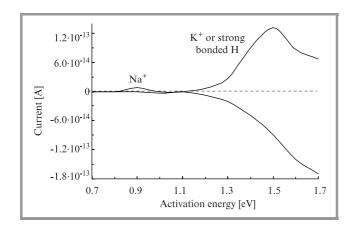

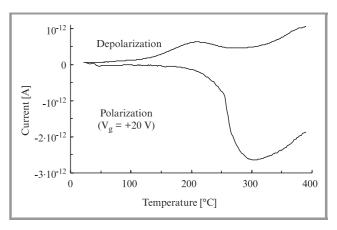

*Fig. 5.* TSP/TSD current spectra measured in ZMR mesa structures ( $\beta = 0.3^{\circ}$ C/s).

Investigation of thermal polarization/depolarization processes (Fig. 5) [11] makes it possible to suggest that a small low-temperature current peak (located in temperature range from 50 to 100°C) with activation energy ranging from 0.75 to 0.9 eV can be related to Na<sup>+</sup> ions whilst the hightemperature current peak, located in the temperature range from 200 to 400°C with the activation energy from 1.2 to 1.7 eV is due to the movement of K<sup>+</sup> ions or to strongly bonded hydrogen.

### 3.2. SOI structures fabricated by single implanted SIMOX technique

The SOI structure used in this study has been fabricated by the standard single implanted SIMOX technique. The implanted dose was  $1.8 \cdot 10^{18} \text{ O}^+/\text{cm}^2$ , the energy of implantation was 200 keV, and the temperature of implantation was 600°C. Post-implantation annealing was performed at  $1320^{\circ}$ C in Ar + 2% O<sub>2</sub> for 6 hours. After wafer processing the thickness of the BOX was 360 nm.

Investigation of the high-temperature stability of the charge in the BOX layer in SIMOX SOI structures using C-V and TSP/TSD current methods has shown [12] considerable distinction of this material from LZMR SOI one.

It should be noted that at first measurement of TSP and TSD processes there is a significant difference between the values of the polarization and depolarization current in SIMOX samples which is greater than a factor of 5 (Fig. 6). Next, the current peaks are completely asymmetric, from which it is concluded that different processes are involved during polarization and depolarization. In addition, after thermal polarization when a negative voltage is applied to the substrate a positive charge buildup in the BOX is observed; whilst a positive voltage applied to the substrate leads to negative charge accumulation, which compensates the positive charge close to the BOX/substrate interface is observed whilst a very small charge change occurs near the BOX/silicon film interface (Table 2).

*Fig. 6.* The TSP/TSD current spectra measured in SIMOX mesa structures.

The important point is similar changing of total charge in the BOX obtained from C-V ( $\Delta Q_m^{sub}$ ,  $\Delta Q_m^f$ ) and TSP ( $Q_{TSP}$ ) measurements at polarization up to 250°C, that can be considered as the BOX/semiconductor interfaces in SIMOX structure are almost electrically blocking in this temperature range. After thermal polarization up to 400°C the charge measured from TSP current is considerably higher than the transported charge determined from C-V measurements. This may be an evidence of electrical unblocking properties of the BOX/semiconductor interfaces in SIMOX structures at temperatures ranging from 250 to 400°C.

The activation energy of the main polarization process (observed at a negative bias applied to the substrate), determined by the fractional thermal cleaning method, is 1.2 eV. Charge movement during this polarization process at first measurement may reach the value of  $1.1 \cdot 10^{12}$  cm<sup>-2</sup> (see Table 2). In the case of depolarization at zero applied voltage we observed two small current peaks from which the activation energy can be only roughly estimated.

|                         | Parameters             |                        |                      |                  |                        |                        |                      |                        |

|-------------------------|------------------------|------------------------|----------------------|------------------|------------------------|------------------------|----------------------|------------------------|

| Kind of                 | $\Delta Q_{sub}$       | $\Delta Q_f$           | $\Delta Q_{tn}$      | $\overline{X}_0$ | $Q_{TSP}$              | $\Delta Q_m^s$         | $\Delta Q_m^f$       | $\Delta Q_{tr}$        |

| treatment               | $[cm^{-2}]$            | [cm <sup>-2</sup> ]    | $[cm^{-2}]$          | [Å]              | $[cm^{-2}]$            | $[cm^{-2}]$            | $[cm^{-2}]$          | $[cm^{-2}]$            |

| Initial                 | $-3 \cdot 10^{10}$     | $6.8\cdot 10^{11}$     | $6.5 \cdot 10^{11}$  | 3600             |                        |                        |                      |                        |

| Polarization<br>(250°C) | 1.4 · 10 <sup>11</sup> | 6.2 · 10 <sup>11</sup> | 7.6 10 <sup>11</sup> | 2680             | 1.8 · 10 <sup>11</sup> | $1.7 \cdot 10^{11}$    | $-5.8 \cdot 10^{10}$ | 1.1 · 10 <sup>11</sup> |

| Polarization<br>(400°C) | 9 · 10 <sup>10</sup>   | $7.4 \cdot 10^{11}$    | 8.3 10 <sup>11</sup> | 3270             | 1.1.10 <sup>12</sup>   | 1.2 · 10 <sup>11</sup> | 6 · 10 <sup>10</sup> | $1.8 \cdot 10^{11}$    |

Table 2The charges, obtained from C-V characteristics and from TSP current technique  $(Q_{TSP})$ and charge centroid for SIMOX structures

We think that the thermal polarization process at negative voltage applied to the substrate of SOI structure is associated with electron emission from traps located near the BOX/substrate interface. The capture cross section for these traps determined from TSP current peak is  $8 \cdot 10^{-18}$  cm<sup>-2</sup>. It should be noted that the flat-band voltage at the BOX/substrate interface is about zero, which is attributed to the complete compensation of the electrical charge located near this interface.

## 4. High-temperature instability of SOI MOSFETs

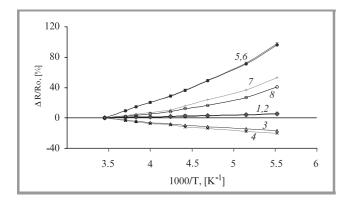

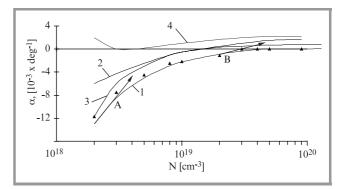

### 4.1. High-temperature kink-effect of back-channel SOI n-MOSFETs

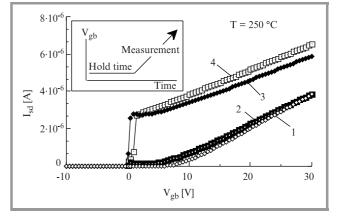

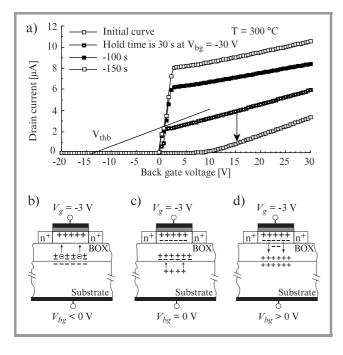

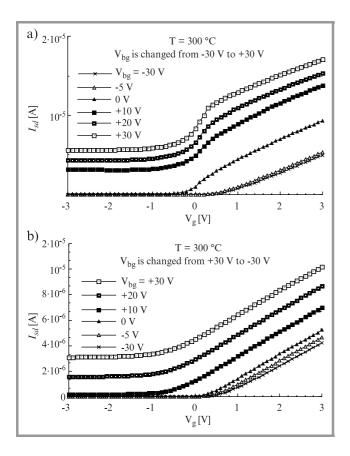

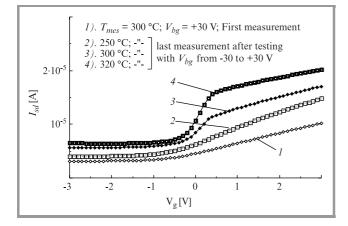

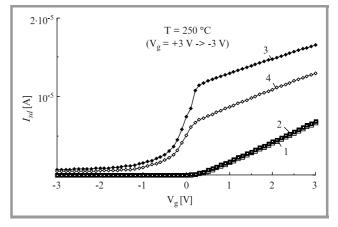

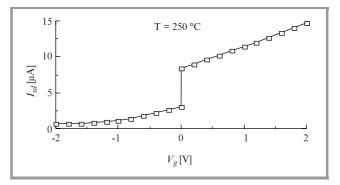

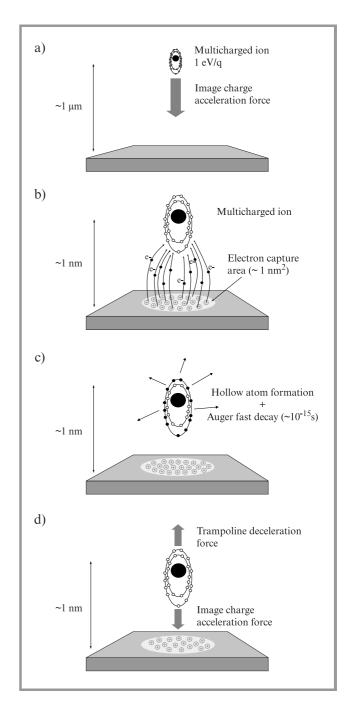

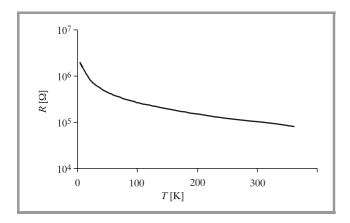

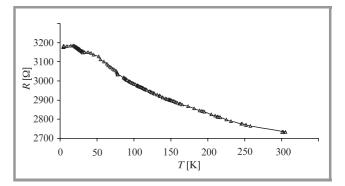

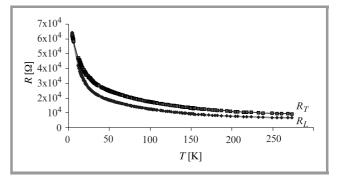

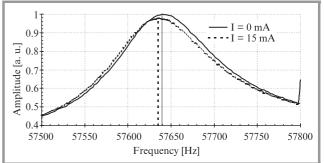

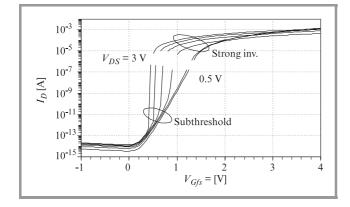

The processes of charging and discharging in the BOX at high temperature can lead to some unusual effects in the MOSFETs. In the paper [3] a new high-temperature effect in the SIMOX SOI n-MOSFET named the hightemperature back-channel kink-effect has been described. This effect appears in fully depleted (FD) inversion mode (IM) n-MOSFETs, fabricated on single implanted SIMOX SOI wafer, when a negative voltage is applied to the substrate at a temperature above 200°C and thereafter the backgate (substrate) voltage,  $V_{bg}$ , is rapidly swept to a positive value. Under these conditions and with a bias at back gate about zero it was observed that a jump occurs in the source-drain current (Fig. 7). This current jump increases with increasing temperature and hold time of negative voltage applied to the substrate prior to the back-gate voltage sweeping and tends to saturation for high-temperature measurements and for long hold times (Fig. 8a).

The current jump cannot be related to the floating-body effects in the SOI MOSFET because the drain voltage is low during the measurements (0.1 V) and the measurements are performed at high temperature, when the floating body effects have to be suppressed [13, 14]. In order to check that special experiments on the SOI MOSFETs with contact to silicon film have been performed. The source-drain current jump near zero back-gate voltage have been observed be-

*Fig.* 7. Drain current versus back-gate voltage for different sweep rates: initial characteristic (sweep rate is 50 V/s) (*1*); the characteristics measured after keeping back gate at -30 V during 150 s and when a sweep rate equals to 1.7 V/s (2), 5 V/s (3) and 50 V/s (4).

ginning from 200°C and have not disappeared when silicon film was grounded. Thus, it is believed that charging and discharging processes in the BOX of the SOI structure are responsible for the observed phenomenon [15, 16].

The drain-current jump has been explained by the following processes taking place in the BOX of the SOI MOS-FET. Firstly, when negative voltage is applied to the substrate at high temperature, a positive charge is accumulated in the BOX. Since this positive charge does not result in an increase of the channel current in the MOSFET, it has been concluded that this positive charge is compensated by a negative electron charge easily injected from the substrate (Fig. 8b). Accumulation of the positive charge has been suggested to be associated with electron extraction from traps located near the BOX/substrate interface. Secondly, when the back-gate voltage approaches to zero, the electrons, located in the vicinity of the BOX/substrate interface, recombine with the thermally generated holes in this region and cannot further compensate the positive charge in the BOX (Fig. 8c). Thus, a sharp increase of the drain current is observed. Thirdly, when a positive voltage is

*Fig. 8.* Drain current versus substrate voltage for different hold times at -15 V (arrow signifies the direction of current relaxation) (a), schematic illustration of the positive charge accumulation in the BOX at  $V_{bg} < 0$  V (b), electron recombination at  $V_{bg} = 0$  V (c) and the neutralization of the positive charge at  $V_{bg} > 0$  V (d).

applied to the substrate, the positively charged traps in the BOX are compensated by electrons injected from the channel of the MOSFET (Fig. 8d). In this case a change in the slope of the  $I_{sd}$ - $V_{bg}$  – characteristic in dependence of the back-gate voltage sweep rate (Fig. 7) and of the magnitude of the current jump (that is the value of a positive charge accumulated in the BOX) (Fig. 8a) has to be observed. Using the above considered model and studying the processes of positive charge accumulation (charging) and relaxation (discharging) in the BOX, the parameters of traps associated with these processes have been estimated.

### 4.2. BOX trap parameters extraction from high-temperature kink-effect of back-channel SOI n-MOSFET

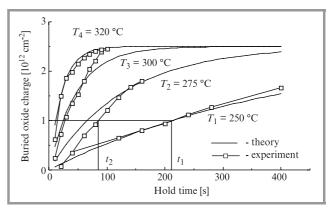

It was shown [15], that the positive charge accumulation in the BOX can be investigated by measuring the magnitude of a drain current jump at different temperatures and hold times of a negative voltage applied to the substrate.