### JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY

### Preface

Despite the fact that a range of limitations are beginning to appear as CMOS technology is being raised to ever higher levels of perfection, it is anticipated that silicon will be the dominant material of the semiconductor industry for at least the first half of the 21st century. The forecast for microelectronics development published in 2006 by Semiconductor Industry Association (SIA) reaches ahead to the years 2014–2020. Moreover, a comparison with former SIA forecasts indicates that they become more aggressive (that is more optimistic) with time.

While the development of silicon microelectronics in the past could be attributed mostly to the reduction of the feature size (progress in lithography), today it relies more on new material solutions, such as SOI, SON, SiGe or SiC. The combination of this trend with continuous miniaturization provides the opportunity of improving IC functionality and speed of operation.

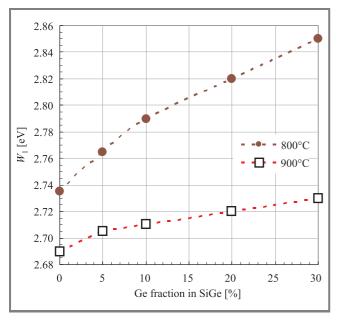

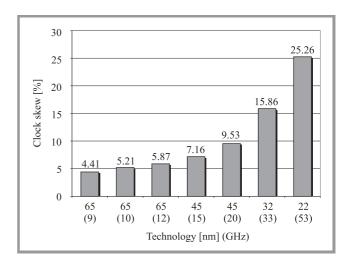

Telecommunications and information technology are arguably the most powerful drivers behind microelectronics product development nowadays. Plenty of new applications are being created for fast analog and rf circuits, as well as for information processing ones. It is clear that with the anticipated peak  $f_{\rm max}=425$  GHz and  $f_T=385$  GHz to be reached by rf SiGe-base bipolar transistors in 2011, according to the 2006 issue of ITRS, a lot of effort must be put into the development of appropriate material, processing, characterization and modeling. While progress in the bipolar technology is impressive, the increase of MOSFET speed is even more so. The same issue of ITRS predicts on-chip clock of 73 GHz for 2020, which will require MOSFET internal switching speed of 12 500 GHz.

High-speed isn't, however, everything. Portable wireless products push, for obvious reasons, for low-power solutions. This trend requires new architectural solutions (e.g., channel thinning), and in consequence, new material, such as SOI (or its possible successor SON), where current driveability is considerably higher than in conventional MOSFETs.

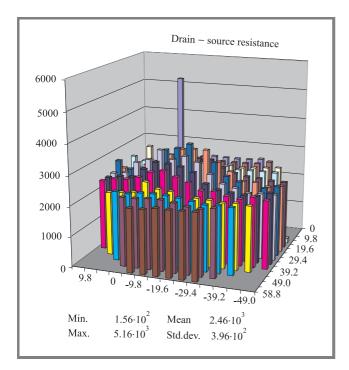

In this issue the Reader will find papers devoted to fabrication (ultra-thin gate dielectrics, DLC and BN layers), characterization (influence of strain on the optical properties of the Si-SiO<sub>2</sub> system, non-uniformity of MOSFET electrical parameters over the gate area,

quality of the dielectric-semiconductor interface) and modeling (strained-Si, SiC MOSFETs) of semiconductor devices. Statistical modeling of process (Monte Carlo) and IC reliability is also addressed, as well as optical interconnects in future ICs.

We hope the Readers will find this issue of the *Journal of Telecommunications and Information Technology* useful and interesting.

Andrzej Jakubowski Lidia Łukasiak Guest Editors

## Applying shallow nitrogen implantation from rf plasma for dual gate oxide technology

Tomasz Bieniek, Romuald B. Beck, Andrzej Jakubowski, Grzegorz Głuszko, Piotr Konarski, and Michał Ćwil

Abstract—The goal of this work was to study nitrogen implantation from plasma with the aim of applying it in dual gate oxide technology and to examine the influence of the rf power of plasma and that of oxidation type. The obtained structures were examined by means of ellipsometry, SIMS and electrical characterization methods.

Keywords—CMOS, dual gate oxide, gate stack, oxynitride, plasma implantation.

### 1. Introduction

According to the ITRS roadmap [1] the reduction of the gate dielectric thickness is one of the ways to ensure the increasing level of packing and performance of silicon integrated circuits. In mixed logic/memory circuits manufactured as system on a chip, two different thicknesses of dielectric layers are required. The most advanced solution would be to form both dielectric layers simultaneously, in a single process. This may be possible if oxidation of a silicon layer is preceded with local nitrogen implantation, since the rate of oxidation depends on the nitrogen implantation dose and its profile (e.g., [2, 3]).

The experiments presented in this work are a part of a broader study that examines the possibility of fabricating very thin dielectric layers using ultrashallow nitrogen implantation from rf plasma. As opposed to the methods presented in the literature so far, where classical implanters or the IIIP technique were used for ultrashallow implantation, our process is performed in a typical Oxford plasma technology plasma enhanced chemical vapour deposition (PECVD) planar plasma reactor. The choice of nitrogen source and process parameters for plasma implantation was based on the results of previous studies [4–6].

In this work nitrogen implantation carried out from NH<sub>3</sub> plasma has been immediately followed by either thermal or plasma oxidation process. In this way the influence of oxidation type could be examined.

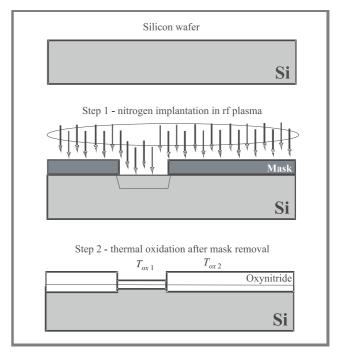

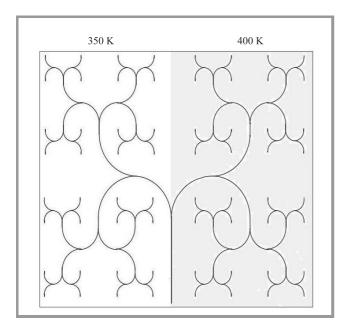

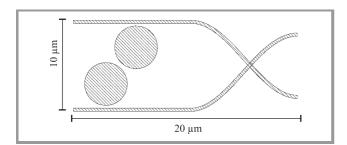

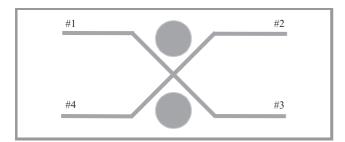

The aim of this work was to study the feasibility of dual gate oxide technology (Fig. 1) based on rf plasma implantation, as well as to investigate the influence of rf power during implantation and that of oxidation type (conventional versus plasma).

The thickness and nitrogen profile of the obtained layers were investigated by means of ellipsometry and secondary ion mass spectrometry (SIMS) measurements. Test

*Fig. 1.* Dual gate oxide technology – two oxynitride layers with different thickness obtained in a single oxidation process.

structures were fabricated using NMOS technology with Al gate and electrical characterization was performed to determine selected electrophysical parameters, such as: effective charge and interface trap density, insulating properties and breakdown behavior.

### 2. Experimental

The experiments in this study were carried out in two steps. In the first one, the process of nitrogen implantation from ammonia (NH<sub>3</sub>) plasma was performed at 350°C in a PECVD system. The rf power was varied between 100 W, 200 W and 300 W. In the second step, the samples were oxidized either thermally or using a plasma process. Thermal oxidation was performed in dry oxygen diluted in argon (50 ml/min  $O_2$  in 1 l/min Ar) at 1000°C (samples 2–4 in Table 1). Low temperature (350°C) plasma oxidation was performed in oxygen at rf power of 100 W (sample 6 in Table 1). The parameters of thermal and plasma oxidation were chosen based on the results of previous studies [4–6].

Table 1 Summary of process parameters

| Parameters         | Only<br>thermal<br>oxidation                                      | 100 W implanta-<br>tion + thermal<br>oxidation | 200 W implanta-<br>tion + thermal<br>oxidation | 300 W implanta-<br>tion + thermal<br>oxidation | Only<br>plasma<br>oxidation | 100 W implantation + plasma oxidation |  |  |

|--------------------|-------------------------------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|-----------------------------|---------------------------------------|--|--|

| Sample no.         | 1                                                                 | 2                                              | 3                                              | 4                                              | 5                           | 6                                     |  |  |

|                    | Step 1 – nitrogen plasma ion implantation, 350°C, NH <sub>3</sub> |                                                |                                                |                                                |                             |                                       |  |  |

| Implantation       | no                                                                | yes                                            | yes                                            | yes                                            | no                          | yes                                   |  |  |

| Rf power [W]       | no                                                                | 100                                            | 200                                            | 300                                            | no                          | 100                                   |  |  |

| Step 2 – oxidation |                                                                   |                                                |                                                |                                                |                             |                                       |  |  |

| Туре               | Thermal, dry oxygen diluted in Ar, 1000°C                         |                                                |                                                |                                                |                             | sma, 350°C                            |  |  |

Table 2

Results of electrical characterization of NMOS test structures

| Parameters                                        | Only<br>thermal<br>oxidation | 100 W implantation + thermal oxidation | 200 W implanta-<br>tion + thermal<br>oxidation | 300 W implanta-<br>tion + thermal<br>oxidation | Only<br>plasma<br>oxidation | 100 W implantation + plasma oxidation |

|---------------------------------------------------|------------------------------|----------------------------------------|------------------------------------------------|------------------------------------------------|-----------------------------|---------------------------------------|

| Sample no.                                        | 1                            | 2                                      | 3                                              | 4                                              | 5                           | 6                                     |

| Optical thickness $D_{ox\_opt}$ [Å]               | 93                           | 55                                     | 49                                             | 53                                             | 40                          | 40                                    |

| EOT from <i>C-V</i> (@1 MHz)                      | 104                          | 60                                     | 38                                             | 89                                             | 46                          | 75                                    |

| Effective dielectric constant $\varepsilon_{eff}$ | 3.4                          | 3.4                                    | 4.6                                            | 2.2                                            | 3.3                         | 2.0                                   |

| $D_{itmb}$ [1/eV cm <sup>2</sup> ]                | $3.21 \cdot 10^{12}$         | $4.93 \cdot 10^{12}$                   | $8.93 \cdot 10^{12}$                           | $4.11 \cdot 10^{12}$                           | $6.19 \cdot 10^{12}$        | $3.12 \cdot 10^{12}$                  |

| $Q_{eff}/q~\mathrm{[cm^{-2}]}$                    | $4.82 \cdot 10^{11}$         | $9.35 \cdot 10^{11}$                   | $3.12 \cdot 10^{12}$                           | $1.64 \cdot 10^{12}$                           | $1.34 \cdot 10^{12}$        | $6.93 \cdot 10^{12}$                  |

| $Q_{eff}/q/D_{ox\_opt}$ [1/cm <sup>2</sup> Å]     | $5.35 \cdot 10^9$            | $1.70 \cdot 10^{10}$                   | $6.37 \cdot 10^{10}$                           | $3.10 \cdot 10^{10}$                           | $3.36 \cdot 10^{10}$        | $1.73 \cdot 10^{11}$                  |

| $Q_{eff}$ [C/cm <sup>2</sup> ]                    | $7.71 \cdot 10^{-8}$         | $1.50 \cdot 10^{-7}$                   | $5.00 \cdot 10^{-7}$                           | $2.63 \cdot 10^{-7}$                           | $2.15 \cdot 10^{-7}$        | $1.11 \cdot 10^{-6}$                  |

| $U_{FB}$ [V]                                      | -1.15                        | -1.20                                  | -1.48                                          | -1.60                                          | -1.21                       | -3.34                                 |

| $E_{BR} [MV/cm] (50\%)$                           | 13.2                         | 11.3                                   | 12.0                                           | 19.2                                           | 13.8                        | 13.8                                  |

To have the necessary reference data, two samples were subjected to either thermal (sample 1) or plasma (sample 5) oxidation only (no nitrogen implantation). The technological experiments performed in the course of this study are summarized in Table 1.

Thickness and composition of the obtained layers were then studied by means of ellipsometry, and ULE-SIMS (ultra-low-energy-SIMS), while electrophysical properties were evaluated based on electrical characterization (*C-V* and *I-V* characteristics analysis) of NMOS test structures with the investigated ultra-thin silicon oxynitride layers as gate dielectric.

### 3. Results

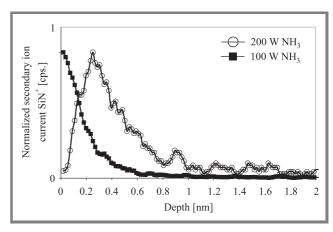

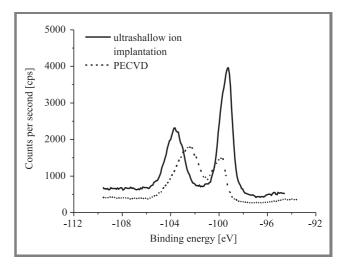

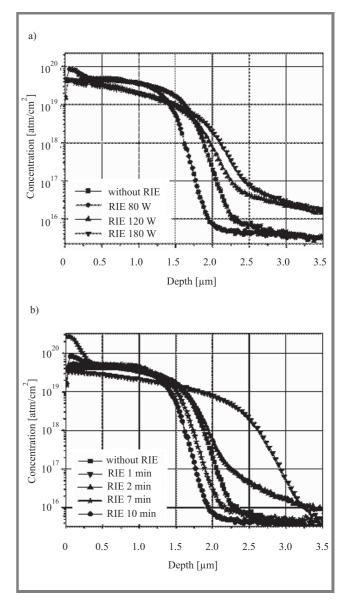

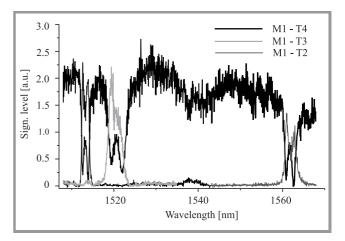

The results obtained in this work and summarized in Tables 1 and 2 confirm that nitrogen implantation does takes place even at very low rf plasma energies (even at 100 W – see Fig. 2). Subsequent thermal oxidation

formed ultra-thin oxynitride layers with the composition and thickness dependent on the conditions of the implantation process.

*Fig. 2.* Examples of nitrogen profiles of the layers formed by means of nitrogen implantation at different levels of rf power followed by plasma oxidation as obtained from ULE-SIMS [7].

During oxynitride layer formation two contradictory effects have significant influence upon the composition and final thickness of the layer.

Nitrogen implantation results in a significant decrease of the thermal oxidation rate, as can be seen in Table 2 (compare the thickness of all nitrogen implanted and thermally oxidized samples with that of sample 1).

Results obtained by ULE – SIMS (see Fig. 2) demonstrate that both, nitrogen profile and content may be controlled by rf plasma power used for implantation. Depending on this power the maximum of the nitrogen profile may be located just at the top surface of the layer or still within the layer – no further than 1.0 nm from its top (see Fig. 2).

A profile of this depth is difficult (if not impossible) to obtain by other techniques. The depth correlates well with the desired final thickness of the oxynitride layer. This means that when the formation of ultra-thin oxynitride layer is finished (that is after oxidation) the nitrogen profile will not extend into the device channel region.

Analysis of electrical characteristics of NMOS test structures indicates correlation between rf power used for nitrogen implantation and electrical properties of the  $Si/SiO_xN_y$  system.

Ellipsometric measurements indicate crucial difference between the thermal and plasma oxidation. For plasma oxidation no difference between the implanted and non-implanted samples was observed (see Table 2) while for thermal oxidation big difference between the implanted and non-implanted samples can be noticed. Almost no difference may, however, be noticed between the implanted samples despite varying rf power used. The whole picture changes if the electrical thickness is taken into consideration.

The equivalent oxide thickness (EOT) values (electrical thickness evaluated from the high frequency *C-V* characteristics assuming the dielectric permittivity is that of silicon dioxide) depend on rf power during implantation. The obvious and intuitive explanation to this observation is that this reflects the dependence of the efficiency of the nitrogen implantation (thus, the composition of the layer) on implantation conditions. In fact a comparison of the optical thickness and EOT leads to the conclusion that the effective dielectric constant of the layer is higher than that of thermal oxide only in one case (implantation at 200 W), which can be attributed to the significant presence of nitrogen in the layer (see Table 2). For the other cases, i.e., 100 W and 300 W, as well as the reference one, the effective dielectric constant values are lower than that of thermal oxide.

The case of thermal oxide proves that one should treat this comparison with highest care<sup>1</sup>. It is our strong belief that

<sup>1</sup>The optical thickness is evaluated from the ellipsometric measurements assuming silicon dioxide refractive index value, due to the low sensitivity of the ellipsometric curves for very low layer thickness. EOT, on the other hand, is evaluated assuming the dielectric constant of thick film thermal silicon dioxide. Neither of the two assumptions is true in the case of the examined samples, even for the reference sample 1 (this is only 10 nm layer). In fact, the significant decrease in the sensitivity of ellipsometric curves makes the former assumption certainly less critical than the latter. One should also keep in mind that for ultra-thin layers optical thickness tends to differ (is usually smaller) from electrical thickness (evaluated from *C-V* curves).

we should refer in our discussion to the observed trends in the effective dielectric constant values, rather than to the absolute values.

Following this approach one notices that the effective dielectric constant reaches maximum in the 200 W case. The dramatic drop of this parameter for 300 W could be interpreted as too much damage caused by nitrogen implantation during the first stage of layer formation. It is interesting, however, to realize that sample 4 has proved to be overall superior (as will be shown below) to all the other samples in terms of electrical properties (the lowest leakage current, highest critical electric field, well defined *C-V* curve and relatively low charge densities). The reason of this discrepancy is not yet known.

For plasma oxidized samples the situation is different. Although, as mentioned above, the optical thickness of the layer is the same, the EOT values differ significantly. Remembering the discussion presented above we may still state that some changes in the layer composition must take place as a result of nitrogen plasma implantation prior to plasma oxidation. Although such a drastic change in EOT would certainly be good enough to obtain satisfactory dual gate oxide technology, its value decreases instead of its required rise. Thus, instead of relaxing technological problems with formation of ultra-thin gate dielectric layer, application of this method to perform dual gate oxide technology would create even more serious difficulties.

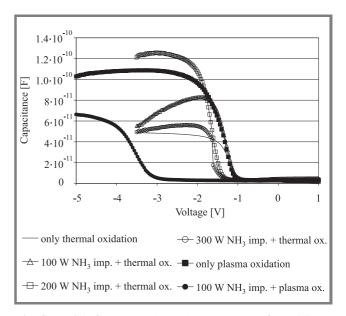

Typical electrical characteristics of NMOS test devices manufactured for the purpose of this study are presented in Figs. 3–5. High frequency C-V curves are shown in Fig. 3. In general, the differences in maximum capacitance are the obvious consequence of different thickness and composition of the studied oxynitride layers and - to a certain extent - of different leakage currents. In order to

*Fig. 3.* High frequency (1 MHz) *C-V* curves of NMOS test structures with the gate dielectric layers produced under different plasma parameters (varied rf power and oxidation type – see Table 1).

prevent the errors in EOT and all other electrical parameter calculations we used the estimation method of  $C_{\rm max}$  as presented in [8]. A simple and intuitively obvious dependence has also been found between rf plasma power and the densities of the effective charge  $Q_{eff}$  interface traps at midgap  $D_{itmb}$ . Both parameters show maximum at 200 W. In fact, sample 4 (rf during plasma implantation 300 W) has superior trapping and effective charge density to all other samples subjected to the plasma implantation and only marginally worse than those of the reference thermal oxide. This result is promising for the dual gate oxide technology.

For plasma oxidation case, the situation is more complicated. Although the systems resulting from plasma nitrogen implantation and plasma oxidation are on a par with reference thermal oxide in terms of trapping properties, the effective charge density is certainly the highest among all samples studied (more than one order of magnitude higher than in the reference thermally oxidized gate oxide).

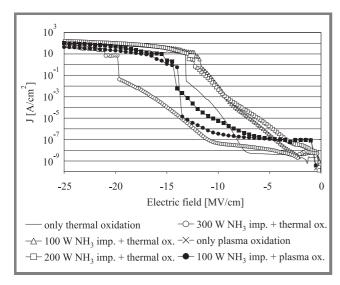

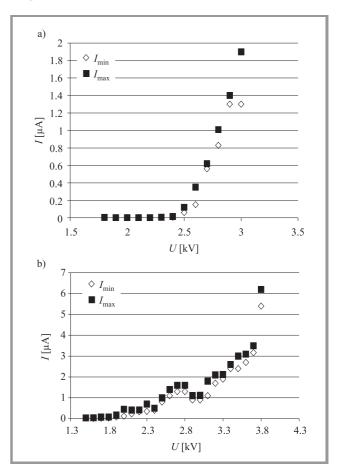

Typical *I-V* curves of individual samples studied in this work are shown in Fig. 4. The analysis of *I-V* curves yields a surprising result. Samples implanted at the highest rf power (300 W; sample 4) have the best insulating properties, better even than the reference thermal oxide (especially for high electric fields). Samples prepared using only plasma processes, that is plasma oxidation only (sample 5) or plasma implantation followed by plasma oxidation (sample 6) exhibit comparable *I-V* behavior, similar also to that of sample 1 (thermal oxidation only) for medium and higher electric fields, although their current is almost two orders of magnitude higher for low electric fields. Samples 2 and 3, implanted at 100 W and 200 W of rf power exhibit the highest leakage currents.

*Fig. 4.* The *I-V* curves of NMOS test structures; gate dielectric layers were produced with different process parameters (varied rf power and oxidation type – see Table 1).

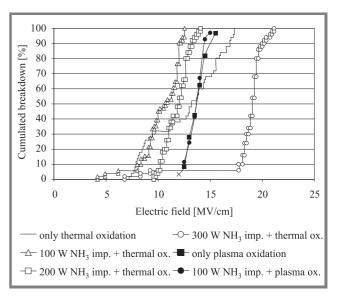

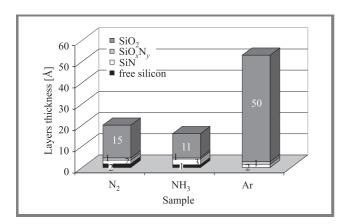

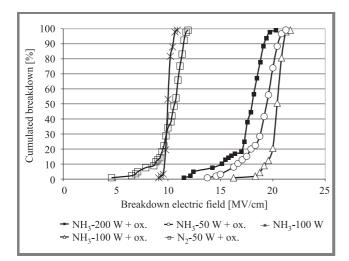

In all studied samples breakdown events were well defined, thus the Weibull plots could be created for each sample (see Fig. 5). Oxynitride layer formed by means of implantation from NH<sub>3</sub> at 300 W and subsequent thermal oxidation (sample 4) was the best in terms of critical electric field with  $E_{BR}$  as high as 19 MV/cm.  $E_{BR}$  values of other samples vary between 11 MV/cm and 14 MV/cm (see Table 2). This means that in each case, the breakdown properties of the obtained SiON layers are superior to the defect free thermal oxides (10 MV/cm). It is interesting to realize that the plots for samples that underwent plasma oxidation are almost identical, whether they were or not subjected to nitrogen implantation.

*Fig. 5.* Weibull plots of NMOS test structures; gate dielectric layers were produced with different process parameters (varied rf power and oxidation type – see Table 1).

Another interesting feature of the presented Weibull plots is their abruptness indicating that for each layer type all breakdowns took place under similar stressing voltage conditions. Therefore, it may be concluded, that we are dealing with intrinsic breakdown (characteristic of layers with almost no defects) or with one caused by one type of defects only (in the case where the intrinsic breakdown field is even higher for this type of material).

### 4. Summary

The experiments performed indicate that dual gate oxide technology based on ultrashallow implantation of nitrogen is feasible. From the two approaches to dual gate oxide technology studied in this work, the combination of nitrogen implantation with thermal oxidation is definitely more promising, because significant reduction of the final oxynitride layer thickness due to plasma implantation was observed.

Variation of rf power indicates that the highest investigated value of this parameter (300 W) results in a superior quality of the ultra-thin gate dielectric layer, comparable with that of non-implanted samples (trapping and effective charge density) and in certain aspects – leakage currents and critical electric field – even much better.

Although the plasma implantation does not degrade the properties in plasma oxidized samples (leakage currents, critical electric field, trapping) except for the effective charge density, the observed decrease in EOT seems to eliminate this method from the list of candidates for implementation for dual gate oxide technology in the future. On the basis of the results obtained in this study, it may be concluded that effective plasma implantation reduces the leakage current, especially at medium and high electric field, leading to significant improvement in breakdown properties ( $E_{BR}$  reaching 19 MV/cm). This effect may be of great value for future CMOS technologies, which suffer a lot from the leakage and reliability issues.

### Acknowledgements

This work has been funded partly by the European Commission under the frame of the Network of Excellence SINANO (Silicon-based nanodevices, IST-506844) and partly by Polish Ministry of Science and Higher Education under the contract no. 3T11B 020 30.

### References

- International Technology Roadmap for Semiconductor, http://public.itrs.net

- [2] T. Chevolleau, A. Szekeres, and S. Alexandrova, "Oxidation of N implanted silicon: optical and structural properties", *Surf. Coat. Technol.*, vol. 151–152, pp. 281–284, 2002.

- [3] R. Rajkumer, M. Kumar, P. J. George, S. Mukherjee, and K. S. Chari, "Effects of nitrogen and argon plasma – immersion ion implantation on silicon and its oxidation", *Surf. Coat. Technol.*, vol. 156, no. 1–3, pp. 253–257, 2002.

- [4] T. Bieniek, R. B. Beck, A. Jakubowski, and A. Kudła, "Formation of ultra-thin oxide layers by low temperature oxidation in r.f. plasma", *Elektronika*, vol. 10, pp. 6–7, 2004.

- [5] T. Bieniek, R. B. Beck, A. Jakubowski, and A. Kudła, "Study of extremely shallow nitrogen ions implantation in planar r.f. plasma reactors", *Elektronika*, vol. 2–3, pp. 9–10, 2005.

- [6] T. Bieniek, A. Wojtkiewicz, L. Łukasiak, and R. B. Beck, "Silicon dioxide as passivating, ultrathin layer in MOSFET gate stacks", J. Wide Bandgap Mater., vol. 8, no. 3–4, pp. 201–209, 2002.

- [7] T. Bieniek, R. Beck, A. Jakubowski, P. Hoffmann, D. Schmeisser, P. Konarski, and M. Cwil, "Formation of pedestal oxynitride layer by extremely shallow nitrogen implantation in planar r.f. plasma reactor", ECS Trans., vol. 1, no. 5, pp. 407–419, 2006.

- [8] B. Majkusiak and A. Jakubowski, "A technical formula for determining the insulator capacitance in a MOS structure", *Solid State Electron.*, vol. 35, no. 2, pp. 223–224, 1992.

Tomasz Bieniek was born in Warsaw, Poland, in 1977. He received the M.Sc. degree from Warsaw University Technology in 2002 and Ph.D. degree in 2007. His research area concentrates on plasma processes for CMOS-VLSI technology, especially in very thin and ultra-thin dielectric layers.

Since 2006 he is working in Institute of Electron Technol-

e-mail: tbieniek@elka.pw.edu.pl

Institute of Microelectronics and Optoelectronics

Warsaw University of Technology

Koszykowa st 75

00-662 Warsaw, Poland

e-mail: tbieniek@ite.waw.pl Institute of Electron Technology

Lotników av. 32/46 02-669 Warsaw, Poland

Romuald B. Beck received the M.Sc. degree in electronics from the Faculty of Electronics, Warsaw University of Technology, Poland, in 1976. From the same university, he received the Ph.D. and D.Sc. degrees in 1982 and 1996, respectively. Since 2000 he occupies the post of Professor. Since 2005 he has been heading Mi-

croelectronic and Nanoelectronic Devices Division. His research activities have been concentrated in the area of modeling, diagnostics and technology of the metal-insulator-semiconductor devices with very thin and ultrathin oxides, dielectric layers formation methods, their kinetics and the relations between the process kinetics and the electrophysical properties of the devices, their yield and their reliability, dry etching methods and their implementation to modern ICs technology.

e-mail: r.beck@elka.pw.edu.pl Institute of Microelectronics and Optoelectronics Warsaw University of Technology Koszykowa st 75 00-662 Warsaw, Poland

Andrzej Jakubowski received the M.Sc., Ph.D. and D.Sc. degrees in electrical engineering from the Warsaw University of Technology (WUT), Poland. At present Professor Jakubowski is the Head of the Institute of Microelectronics and Optoelectronics (WUT). His main research interests include modeling and characterization of

semiconductor devices and integrated circuits. He is author and co-author of more than 300 papers, several books and textbooks.

e-mail: jakubowski@imio.pw.edu.pl Institute of Microelectronics and Optoelectronics Warsaw University of Technology Koszykowa st 75 00-662 Warsaw, Poland

JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY

3/2007

Grzegorz Głuszko was born in Biłgoraj, Poland, in 1976. He received the B.Sc. and M.Sc. degrees in microelectronics from Warsaw University of Technology, Poland, in 2002 and 2004, respectively. Since then he has been working on a Ph.D. thesis concerning characterization of novel MOS devices. His research interests in-

clude charge pumping studies of the quality of siliconsilicon dioxide interface, as well as modeling of MOS devices.

ggluszko@elka.pw.edu.pl Institute of Microelectronics and Optoelectronics Warsaw University of Technology Koszykowa st 75 00-662 Warsaw, Poland

Piotr Konarski received the M.Sc. degree from the Chemistry Department of Warsaw University in 1976 and Ph.D. degree from the Institute of Electron Technology, Poland, in 1997. He is the Head of Vacuum Instruments Laboratory at Industrial Institute of Electronics in Warsaw. He performs applied research in the areas

relating to: vacuum technology, surface physics, secondary ion mass spectrometry, glow discharge mass spectrometry and depth profile analysis. He is a member of The Polish Fulbright Alumni Association and Polish Vacuum Society.

e-mail: piotr.konarski@pie.edu.pl Industrial Institute of Electronics Długa st 44/50 00-241 Warsaw, Poland

Michał Ćwil was born in Warsaw, Poland, in 1979. He received the M.Sc. degree in physics from the Faculty of Physics, Warsaw University of Technology in 2003, where he is currently working on his Ph.D. degree in the field of electrical characterization of CIGS solar cells. He is also a specialist in secondary ion mass spec-

trometry. Currently he is an Assistant at the Industrial Institute of Electronics in Warsaw.

e-mail: cwil@if.pw.edu.pl Industrial Institute of Electronics Długa st 44/50 00-241 Warsaw, Poland Faculty of Physics Warsaw University of Technology Koszykowa st 75 00-662 Warsaw, Poland

### Composition and electrical properties of ultra-thin $SiO_xN_y$ layers formed by rf plasma nitrogen implantation/plasma oxidation processes

Tomasz Bieniek, Romuald B. Beck, Andrzej Jakubowski, Piotr Konarski, Michał Ćwil, Patrick Hoffmann, and Dieter Schmeißer

Abstract-Experiments presented in this work are a summary of the study that examines the possibility of fabrication of oxynitride layers for Si structures by nitrogen implantation from rf plasma only or nitrogen implantation from rf plasma followed immediately by plasma oxidation process. The obtained layers were characterized by means of: ellipsometry, XPS and ULE-SIMS. The results of electrical characterization of NMOS Al-gate test structures fabricated with the investigated layers used as gate dielectric, are also discussed.

Keywords—CMOS, gate stack, oxynitride, plasma implantation.

### 1. Introduction

According to the ITRS roadmap [1] the thickness of the gate dielectric layer will be dramatically reduced in the near future to 6-8 Å in 2011. Such extremely thin layers generate, however, a lot of problems in terms of processing repeatability and reliability. This, in turn, creates a pressure to substitute silicon dioxide with a single layer of high-k material or - more probably - with a gate stack (a combination of high-k material and pedestal layer passivating silicon-dielectric interface).

Oxynitride layers seem to be very promising in this respect. This is mostly due to the fact that silicon nitride layers are known to be very resistant to diffusion and thus oxidation (vide their application for LOCOS), while oxide is undisputedly the best possible passivating layer for silicon surface.

Oxynitride layers can be produced with number of methods. The experiments presented in this work are a summary of the study that examines the possibility of fabrication of oxynitride layers for Si structures by nitrogen implantation from rf plasma (denoted hereafter as "as-implanted") or nitrogen implantation from rf plasma followed immediately by plasma oxidation process.

In contrast to the methods presented in the literature so far (e.g., [2, 3]), where the classical implanters or the ion immersion implantation in plasma (IIIP) technique were used for implantation, in this work we used a typical rf plasma planar reactor, usually applied for plasma enhanced chemical vapour deposition (PECVD) - Oxford plasma technology - PlasmaLab 80+.

### 2. Experimental

In this work ultra-thin oxynitride layers were formed during plasma processes. Ultrashallow plasma implantation of nitrogen ions and low temperature plasma oxidation were used to form the layers. Both these processes were performed, as already mentioned above, in a PECVD reactor. For the purpose of this study, the layers were formed under different conditions. The variable process parameters were: implantation time, rf power, nitrogen source gases, and temperature. A detailed process description may be found in [4-6].

Two-stage analysis of the studied ultra-thin oxynitride layers was performed. In the first stage, the layers formed using nitrogen plasma implantation only (as implanted) were characterized in order to understand the state of the silicon substrate right after plasma implantation. In the second stage, the layers formed using nitrogen implantation followed by plasma oxidation underwent similar analysis, to understand the consequences of the complex process.

Each stage included structural (i.e., optical - ellipsometry, chemical and physical X-ray photoelectron spectroscopy (XPS), secondary ion mass spectroscopy (SIMS) and electrical (electrical measurements of NMOS test structures with investigated layer used like a gate dielectrics) analysis. Structural analysis was aimed at independent determination of the chemical composition and thickness of the layers [7-9]. In order to perform electrical characterization of the layers, NMOS Al-gate test structures with ultra-thin dielectric layers formed using the studied method were fabricated. Al gate was chosen to avoid any thermal treatment after the gate dielectric was formed.

The NMOS test structures were then electrically characterized by means of C-V and I-V measurements in order to evaluate: leakage currents, effective charge density and trapping and breakdown behavior.

### 3. Results

### 3.1. Samples with nitrogen plasma implantation only (as-implanted)

In the first step, analysis of the correlation between the ultrashallow plasma implantation and composition and thickness of the affected silicon layer was studied. The following parameters of plasma implantation were of interest: type of nitrogen source gas, rf plasma power, implantation time and sample temperature during implantation.

The XPS studies have revealed that despite using either nitrogen or ammonia plasma during implantation, the implanted substrate region consists mostly of silicon dioxide. This must be the result of a spontaneous oxidation upon the exposure of the samples to the atmosphere when removing them from the plasma reactor. Even though the implantation temperature is only 200°C or 350°C – the results prove that the implantation leaves the silicon surface very prone to oxidation even in such usually unfavorable conditions.

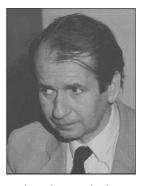

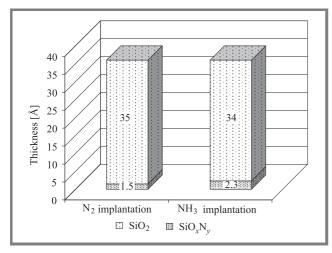

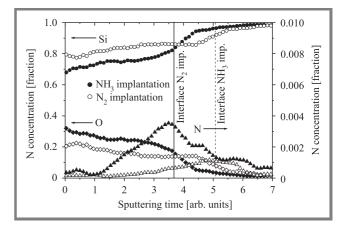

There are, however, small differences in the composition of the studied layers depending on the nitrogen source (see Fig. 1). Marginally higher content of nitrogen is observed for nitrogen implantation from ammonia plasma. Different nitrogen content and/or damage caused to the silicon surface during nitrogen implantation result in significantly different overall layer thickness – lower for implantation from ammonia than from nitrogen plasma. Thus, it seams reasonable to choose ammonia plasma for the purpose investigated in this paper and this choice has been adopted for the subsequent investigation.

*Fig. 1.* Chemical composition and thickness obtained from XPS for layers formed in different plasmas  $(NH_3, N_2, Ar)$  – normalized to the optical thickness.

From the reference experiment in which the silicon sample was subjected to Ar plasma bombardment (for the same as in case of nitrogen and ammonia plasmas rf power – 100 W) one can evaluate the influence of substrate damage caused by bombarding ions. Comparison of the thickness of spontaneously oxidized layers after exposure to either Ar or nitrogen plasma clearly proves that the nitrogen presence in the surface silicon layer significantly slows down the oxidation rate.

This in turn proves that the presence of nitrogen-rich oxide at the silicon surface may be effectively used to prevent or at least to reduce oxide growth at the silicon interface during high-*k* dielectric deposition and/or source and drain dopant activation annealing.

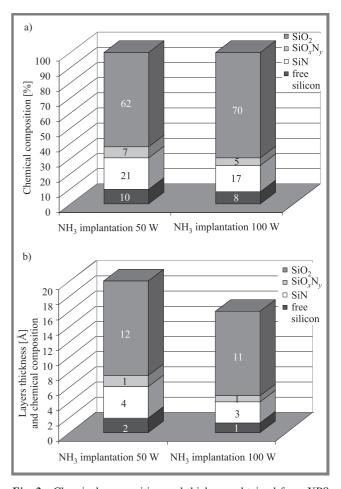

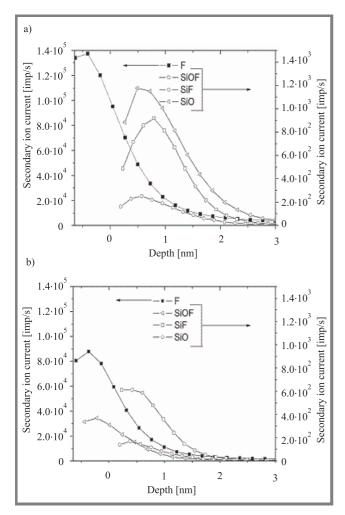

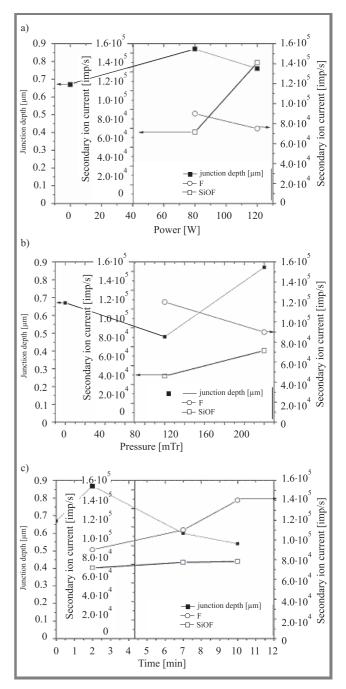

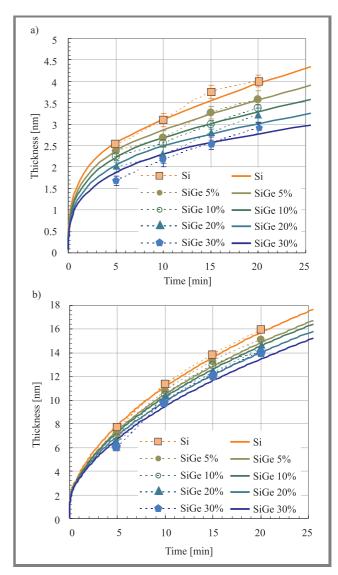

The next correlation to investigate was the influence of implantation rf power. The analysis based on the example of NH<sub>3</sub> samples shows that rf power is a very important process parameter (see Figs. 2 and 3). Increasing implantation power results in a decrease of the layer thickness and in minor changes of its chemical composition (see Figs. 2a and 2b). It is not obvious if these changes are sufficient to cause the observed reduction of the layer thickness. The other possibility is that changing rf power affects the density of the plasma and thus also the implantation and substrate damage efficiency, which in turn can lead to a change in spontaneous oxidation rate. Additional data for this analysis may be obtained from ultra-low energy SIMS (ULE-SIMS).

*Fig. 2.* Chemical composition and thickness obtained from XPS for layers formed in  $NH_3$  plasma for two different levels of rf implantation power (50 W and 100 W) normalized to: (a) 100%; (b) to the layer thickness.

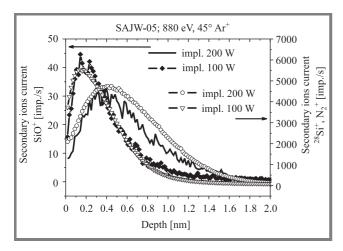

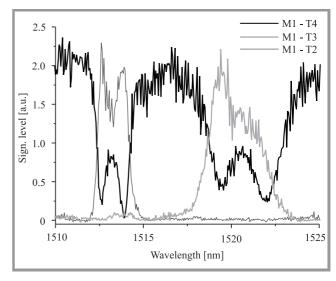

Analysis of ULE-SIMS data yielded similar results to the ones obtained from XPS. They prove that rf power used for nitrogen implantation is a crucial process parameter. Depending on rf power used, the maximum of the nitrogen profile may be located just at the top surface of the layers (for power not higher than 100 W) or within up to 1.0 nm from it (see Fig. 3). It seems, therefore, that the nitro-

*Fig. 3.* Examples of ULE-SIMS results – secondary ion current for  $SiO^+$ ,  $Si^+$ ,  $N_2^+$  for the samples implanted from NH<sub>3</sub> for two different rf power levels (100 W and 200 W).

gen profile may be optimized by choosing the appropriate rf power for nitrogen implantation.

A profile of this depth is difficult (if not impossible) to obtain by other techniques. The depth correlates well with the desired final thickness of the oxynitride layer. This means that when the formation of ultra-thin oxynitride layer is finished (that is after oxidation) the nitrogen profile will not extend into the device channel region.

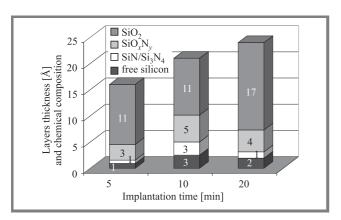

The XPS study of the samples exposed to plasma implantation of nitrogen for different time (see Fig. 4) demonstrates that the amount of nitrogen rich phases (oxynitrides and nitrides) reaches a maximum at a certain implantation time. For the studied cases the highest content of nitrogen was observed in layers obtained by 10 min implantation. In practice, however, it may be difficult to use this parameter to optimize nitrogen content since the layer thickness is also dependent on implantation time.

*Fig. 4.* Chemical composition and thickness obtained from XPS for different times of implantation (5 min, 10 min, 20 min) – normalized to the optical thickness.

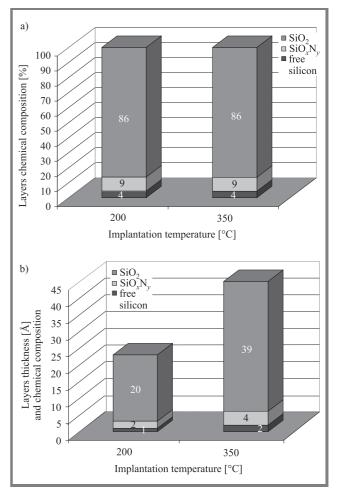

The last parameter of nitrogen implantation to be studied was the temperature of the silicon substrate. The surprising result obtained in this study can be seen in Fig. 5a, which demonstrates that no differences in the chemical content are observed between the layer obtained at temperatures ranging from 200°C to 350°C. Interestingly enough higher temperatures promote layer growth (23 Å versus 45 Å for 200°C and 350°C, respectively – see Fig. 5b). The nature of this dependence is not clear. One might speculate

Fig. 5. Chemical composition and thickness obtained from XPS for layers formed at different implantation temperatures ( $200^{\circ}$ C and  $350^{\circ}$ C) – normalized: (a) to 100%; (b) to the optical thickness.

that higher temperatures allow easier (and faster) formation of nitride bonds, which in turn increases the silicon substrate oxidation rate. Such an explanation would be, however, only true if silicon oxidation took place during implantation and not, as believed until now, exclusively during the exposure to the clean-room atmosphere.

### 3.2. Samples with nitrogen implantation followed by plasma oxidation

The next stage of analysis refers to the structural investigations of the layers formed using plasma implantation of nitrogen followed by plasma oxidation. Introduction of the second process step – plasma oxidation – has created new parameters to be decided upon. From previous studies

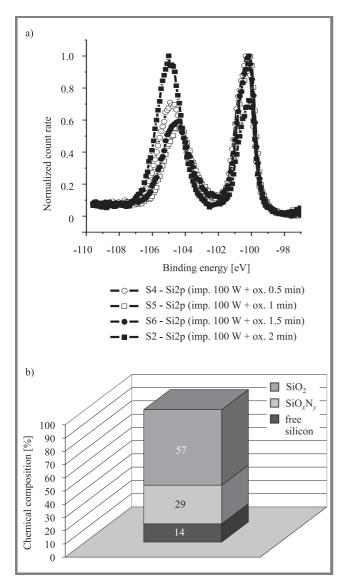

on plasma oxidation alone we have chosen the rf power of 50 W and oxygen pressure of 0.5 Tr for this process. Oxidation time was studied using XPS, similarly to the previous case. From the spectra presented in Fig. 6 we can clearly see that even half minute oxidation after nitrogen implantation is enough to form an oxynitride layer with high silicon dioxide content. Any oxidation, longer than 0.5 min, gives  $\mathrm{SiO}_x\mathrm{N}_y$  layer with similar oxygen content and profile. For the sake of this study, the plasma oxidation time was set to 2 min. The following experiments aimed at checking the influence of plasma oxidation on the composition of the final layer.

*Fig. 6.* Results of XPS measurements: (a) Si2p peaks for the samples implanted from NH<sub>3</sub> plasma at 100 W and plasma oxidized for different oxidation times (0.5; 1; 1.5, 2 min); (b) composition of the layer plasma oxidized for 2 min.

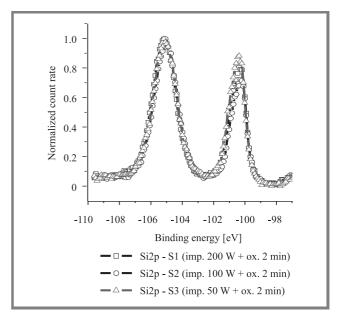

The XPS spectra shown in Fig. 7 prove that as a result of plasma oxidation we obtain almost the same composition of the oxynitride layer (as shown in Fig. 6b) regardless of the rf power used for nitrogen implantation.

*Fig.* 7. Si2p peak for samples implanted from NH<sub>3</sub> plasma at three different levels of rf power (50 W, 100 W and 200 W) and oxidized in oxygen plasma for 2 min.

### 3.3. Electrical characterization

The test structures for the analysis of electrophysical properties were fabricated using different nitrogen implantation conditions. In order to establish the most sensitive relations between the properties of the layers and plasma process parameters the test structures were fabricated using different rf plasma power for plasma implantation. It should be remembered here that this parameter appeared to have the greatest influence on the properties of the layers directly after implantation. Two samples were fabricated using NH $_3$  as nitrogen source at different levels of rf power (sample 5–100 W and sample 6–50 W). For the sake of comparison, one sample was also produced with the layer formed using N $_2$  plasma (sample 4). Process parameters and characterization results are summarized in Table 1.

Analysis of electrical characteristics of NMOS test structures has shown strong correlation between plasma process parameters and electrical properties of the layers. This result was rather surprising since XPS analysis revealed that layer composition after plasma oxidation was the same regardless of the initial state after nitrogen implantation.

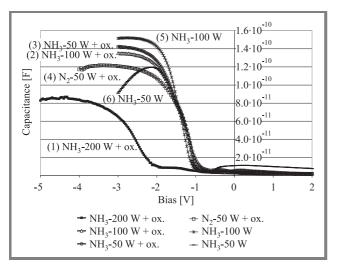

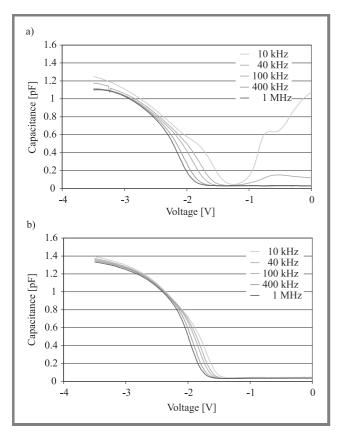

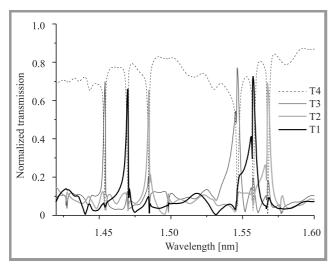

High frequency C-V curves shown in Fig. 8 form two clearly distinguishable groups. One curve (sample 1) is shifted towards negative voltage with respect to all the other curves (including also those obtained from as implanted samples 5 and 6). This voltage shift is the consequence of much higher effective charge concentration  $Q_{eff}/q$  (see Table 1). This confirms the results of the XPS analysis, which indicated that implantation at 200 W from NH<sub>3</sub> plasma created significantly more damage than processes carried out at lower values of rf power [4–6].

The differences in maximum capacitance  $C_{\text{max}}$  are the obvious consequence of the variation in layer thicknesses,

3/2007

Table 1

The technological process parameters of oxynitride layer formation and the results of optical and electrical characteristics evaluation for NMOS test structures manufactured in this study

| Domomotore                                           |                     |                     | Sam                 | ples                |                     |                     |  |  |

|------------------------------------------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|--|--|

| Parameters                                           | 1                   | 2                   | 3                   | 4                   | 5                   | 6                   |  |  |

| Step 1 – nitrogen ions implantation (350°C)          |                     |                     |                     |                     |                     |                     |  |  |

| Power [W]                                            | 200                 | 100                 | 50                  | 50                  | 100                 | 50                  |  |  |

| Gas/plasma                                           | NH <sub>3</sub>     | NH <sub>3</sub>     | NH <sub>3</sub>     | N <sub>2</sub>      | NH <sub>3</sub>     | NH <sub>3</sub>     |  |  |

| Ste                                                  | ep 2 – plasma       | oxidation (3:       | 50°C, 50 W, 0       | $O_2)$              |                     |                     |  |  |

| Optical characterization                             |                     |                     |                     |                     |                     |                     |  |  |

| Layer thickness [Å]                                  | 33                  | 24                  | 24                  | 52                  | 45                  | 32                  |  |  |

| El                                                   | ectrical chara      | cterization (fr     | om C-V curve        | es)                 |                     |                     |  |  |

| EOT [Å]                                              | 59                  | 37                  | 35                  | 41                  | 33                  | 40                  |  |  |

| $U_{fb}  [{ m V}]$                                   | -2.2                | -1.1                | -1.0                | -1.1                | -1.2                | -1.2                |  |  |

| $Q_{eff}/q~[{ m cm}^{-2}]$                           | $4.7 \cdot 10^{12}$ | $9.0 \cdot 10^{12}$ | $4.9 \cdot 10^{11}$ | $7.0 \cdot 10^{11}$ | $1.8 \cdot 10^{12}$ | $1.1 \cdot 10^{12}$ |  |  |

| $Q_{eff}/q$ /optical thickness [cm <sup>-2</sup> /Å] | $1.4 \cdot 10^{11}$ | $3.8 \cdot 10^{10}$ | $2.0 \cdot 10^{10}$ | $1.3 \cdot 10^{10}$ | $4.0 \cdot 10^{10}$ | $3.4 \cdot 10^{10}$ |  |  |

| $D_{itmb}$ 1/eV cm <sup>2</sup>                      | $1.8 \cdot 10^{13}$ | $1.5 \cdot 10^{13}$ | $8.0 \cdot 10^{12}$ | $1.2 \cdot 10^{13}$ | $9.8 \cdot 10^{13}$ | $7.7 \cdot 10^{12}$ |  |  |

| Electrical characterization (from <i>I-V</i> curves) |                     |                     |                     |                     |                     |                     |  |  |

| E <sub>breakdown</sub>                               | 17.8                | 20.4                | 19.6                | 10.6                | 10                  | _*                  |  |  |

| * No catastrophic physical breakdown                 | could be dete       | ected for these     | e devices.          |                     |                     |                     |  |  |

compositions, as well as in leakage current for particular wafers. Leakage is related with oxide structure integrity, therefore should also be reflected in the effective dielectric constant of the studied oxynitride layers. These values obtained from  $C_{\rm max}$  (oxynitride thickness was determined independently by ellipsometry) have confirmed the above mentioned relations between samples.

Fig. 8. Typical high frequency C-V curves for the studied NMOS test structures with the gate dielectric layers produced with different plasma parameters (varied rf power and nitrogen gas source) [6].

The *C-V* behavior of as implanted samples proves that a dielectric film (identified by XPS as oxynitride layer) is

formed on top of the silicon substrate already after nitrogen implantation. This observation confirms that the exposure of the as-implanted silicon surface (please, keep in mind that the wafer temperature is 350°C before the plasma reactor is vented) to the atmosphere is enough to form an oxynitride layer. The quality of such layers (as-implanted) expressed in terms of charge and trap densities in the studied system is, amazingly, comparable to those formed by plasma oxidation only. The significant difference between these two groups (as-implanted and oxidized), as it will be shown below, exists in leakage currents and breakdown properties, which suggests that the main difference between them lays in the integrity of the dielectric layer.

Simple and intuitively obvious dependence between rf plasma power and the densities of the effective charge  $Q_{eff}$  and traps  $D_{itmb}$  has also been confirmed. The values of both of these parameters rise with the increase of rf power. Taking into consideration different final thickness of the oxynitride layers obtained under different conditions makes this dependence even stronger (see  $Q_{eff}/q$  normalized to the layer thickness in Table 1).

It is interesting to realize that although  $N_2$  implanted samples exhibit relatively low  $Q_{eff}/q$  values (especially when normalized to the layer thickness) – their interface properties (expressed in  $D_{itmb}$ ) are worse than those of the 50 W, NH<sub>3</sub>-implanted sample.

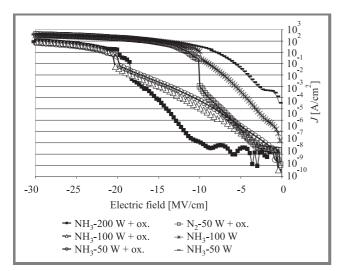

The typical *I-V* curves (for the purpose of easier comparison drawn in the *J-E* scale) for individual samples studied in this work are presented in Fig. 9. In all of the examined cases (except of sample 6) the breakdown events were

well defined, thus, the Weibull plots could be constructed (see Fig. 10).

Fig. 9. Typical *J-E* curves for the studied NMOS test structures; gate dielectric layers were produced with different plasma parameters (rf power and nitrogen source gas) [6].

*Fig. 10.* Weibull's plots for the studied NMOS test structures; gate dielectric layers were produced with different plasma parameters (rf power and nitrogen gas source) [6].

The as-implanted samples (without plasma oxidation) exhibit obviously the highest leakage currents. In the case of the sample implanted at 50 W this current is approximately two orders of magnitude higher than that of the sample implanted at 100 W.

Among the samples which underwent plasma oxidation,  $N_2$  implanted sample proves again to be inferior to the rest. Although its critical electric field is comparable to that typically achieved by thermal  $SiO_2$  layers ( $\sim 10$  MV/cm), other samples exhibited much higher values. The best result (20 MV/cm) was observed in the oxynitride sample formed by implantation from  $NH_3$  at 100 W.

It is interesting to realize that the lowest leakage current is observed for the sample implanted from NH<sub>3</sub> at 200 W, which is the worst among implanted and oxidized samples

in terms of charge and trap density In the high electric field region the current for this sample was even a few (up to three) orders of magnitude lower than that for the samples implanted from NH<sub>3</sub> at lower rf power (100 W and 50 W).

The Weibull plots created from the results of *I-V* measurements are shown in Fig. 10. It is interesting to realize that all of them are very steep, proving practically single mode breakdown properties and no (or very little) early, defect related breakdowns.

### 4. Summary

The nitrogen implantation from rf plasma either alone or followed by plasma oxidation was studied as a potential method to fabricate ultra-thin oxynitrides layers.

It has been proved that nitrogen implantation from  $NH_3$  can be more effective than from  $N_2$ . The rf power can be successfully used to control both, the thickness and composition of an ultra-thin oxynitride layer. It can also be used to control the nitrogen profile within the oxynitride layer. The nitrogen penetration depth can be less than 1.0 nm. Thus, no degradation of MOSFET carrier mobility in the device channel should be observed.

The implantation temperature and time are not sensitive parameters, therefore this method offers significant flexibility in this respect.

Plasma oxidation rebuilds the oxynitride layer, the final composition is practically the same regardless of the parameters of the preceding nitrogen implantation. The electrophysical properties of these layers are, however, different (implantation – parameter dependent).

The effective charge and interface trap densities are, so far, hardly acceptable, but no annealing has been used in this study. The breakdown properties of the studied layers are excellent and, hence, give hope for uniform and reliable gate stacks with pedestal oxynitrides formed by this method.

### Acknowledgements

This work has been partly funded by the European Commission under the frame of the Network of Excellence SINANO (Silicon-based nanodevices, IST-506844) and partly by Polish Ministry of Science and Higher Education under the contract no. 3T11B 020 30.

### References

International Technology Roadmap for Semiconductor, http://public.itrs.net

3/2007

- [2] T. Chevolleau, A. Szekeres, and S. Alexandrova, "Oxidation of N implanted silicon: optical and structural properties", *Surf. Coat. Technol.*, vol. 151–152, pp. 281–284, 2002.

- [3] R. Rajkumer, M. Kumar, P. J. George, S. Mukherjee, and K. S. Chari, "Effects of nitrogen and argon plasma – immersion ion implantation on silicon and its oxidation", *Surf. Coat. Technol.*, vol. 156, iss. 1–3, pp. 253–257, 2002.

- [4] T. Bieniek, R. B. Beck, A. Jakubowski, and A. Kudła, "Formation of ultrathin oxide layers by low temperature oxidation in r.f. plasma", *Elektronika*, vol. 10, pp. 6–7, 2004.

- [5] T. Bieniek, R. B. Beck, A. Jakubowski, and A. Kudła, "Study of extremely shallow nitrogen ions implantation in planar r.f. plasma reactors", *Elektronika*, vol. 2-3, pp. 9–10, 2005.

- [6] T. Bieniek, R. Beck, A. Jakubowski, P. Hoffmann, D. Schmeisser, P. Konarski, and M. Cwil, "Formation of pedestal oxynitride layer by extremely shallow nitrogen implantation in planar r.f. plasma reactor", ECS Trans., vol. 1, no. 5, pp. 407–419, 2006.

- [7] J. R. Shallenberger, M. J. Edgell, S. P. Smith, C. J. Hitzman, J. F. Kirchhoff, E. Principe, S. Biswas, R. J. Bleiler, W. Nieveen, and K. Jones, "Oxide thickness determination by XPS, AES, SIMS, RBS and TEM", in *Int. Conf. Ion Impl. Technol. Proc.*, Kyoto, Japan, 1998, vol. 1, pp. 79–82.

- [8] S. Tanuma, C. J. Powell, and D. R. Penn, "Calculations of electron inelastic mean free paths", *Surf. Interf. Anal.*, vol. 17, pp. 927–939, 1991

- [9] J. F. Moulder, W. F. Stickle, P. E. Sobol, and K. D. Bomben, *Hand-book of X-ray Photoelectrons Spectroscopy*. Eden Prairie: Perkin-Elmer Corp., 1992.

Patrick Hoffmann received his diploma in physics from the Brandenburg Technical University (BTU) in Cottbus, Germany, in 1998. He was investigating interface properties of oxynitrides on silicon, and finished his Ph.D. work in 2003 at the Brandenburg Technical University in Cottbus. Later his research was expanded to oxyni-

trides on SiC. Presently, Doctor Hoffmann is working at the Hahn-Meitner-Institute in Berlin on the nitrogen incorporation into zinc oxide.

e-mail: Patrick.Hoffmann@tu-cottbus.de or patrick.hoffmann@hmi.de

Department of Applied Physics II

Brandenburg Technical University

Universitätsplatz 3-4

03-044 Cottbus, Germany

Dieter Schmeißer is Head of the Chair of Applied Physics at the Brandenburg Technical University (BTU) in Cottbus, Germany, since 1996. He studied physics at the University of Erlangen and got his Ph.D. at the Fritz-Haber Institute (Berlin) and the habilitation at the University of Tübingen. Former appointments as a research fellow

were at the Hahn-Meitner-Institut (Berlin), IBM (Yorktown Heights, USA), and at the University of Tübingen. His research activities are the field of photoelectron spectroscopy to analyze interface reactions. The systems of interest are organic materials, materials for semiconductor devices, and functional oxides. They include applications as organic FET, Fe-DRAMS, and high-k dielectrics, as well as chemical and bio-sensors. Professor Schmeißer currently is a member of DeMaWiG, member of the German, European, and American Physical and Materials societies. He is elected to join the scientific advisory board of the Institut for Kristallzüchtung (IKZ) in Berlin, of the Institut für Halbleiterphysik (IHP) in Frankfurt/Oder, and of the Brandenburg Polymer Center of Excellence in Schwarzheide. Further activities include the organization of national summer schools and international symposia at the E-MRS meetings.

e-mail: dsch@tu-cottbus.de Department of Applied Physics II Brandenburg Technical University Universitätsplatz 3-4 03-044 Cottbus, Germany

**Tomasz Bieniek**, **Romuald B. Beck**, and **Andrzej Jakubowski** – for biographies, see this issue, p. 7.

**Piotr Konarski** and **Michał Ćwil** – for biographies, see this issue, p. 8.

## The influence of annealing (900°C) of ultra-thin PECVD silicon oxynitride layers

Robert Mroczyński, Grzegorz Głuszko, Romuald B. Beck, Andrzej Jakubowski, Michał Ćwil, Piotr Konarski, Patrick Hoffmann, and Dieter Schmeißer

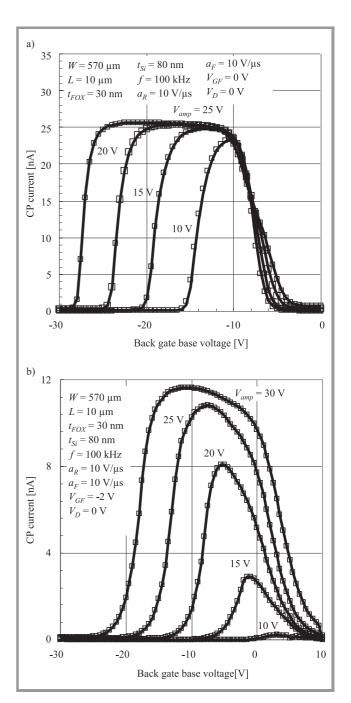

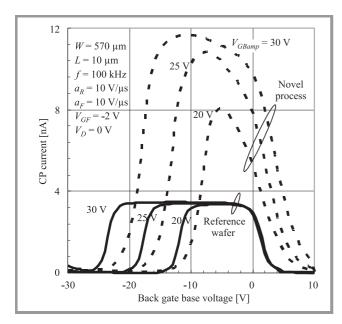

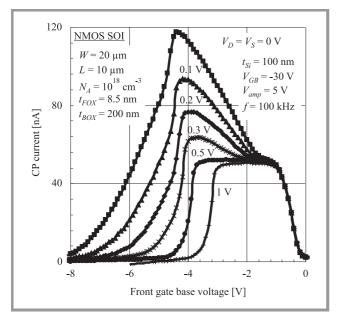

Abstract—This work reports on changes in the properties of ultra-thin PECVD silicon oxynitride layers after hightemperature treatment. Possible changes in the structure, composition and electrophysical properties were investigated by means of spectroscopic ellipsometry, XPS, SIMS and electrical characterization methods (C-V, I-V and chargepumping). The XPS measurements show that  $SiO_xN_y$  is the dominant phase in the ultra-thin layer and high-temperature annealing results in further increase of the oxynitride phase up to 70% of the whole layer. Despite comparable thickness, SIMS measurement indicates a densification of the annealed layer, because sputtering time is increased. It suggests complex changes of physical and chemical properties of the investigated layers taking place during high-temperature annealing. The C-V curves of annealed layers exhibit less frequency dispersion, their leakage and charge-pumping currents are lower when compared to those of as-deposited layers, proving improvement in the gate structure trapping properties due to the annealing process.

Keywords—ultra-thin dielectrics, silicon oxynitride, PECVD, CMOS.

### 1. Introduction

According to the ITRS roadmap [1]  $SiO_2$  gate dielectric will have to be replaced with by layers exhibiting higher dielectric constants. Ultra-thin silicon oxynitride ( $SiO_xN_y$ ) seems to be a promising candidate as gate dielectric in future CMOS IC's (e.g., [2, 3]).

However, during standard CMOS self-aligned technology the implantation of source/drain regions is followed by a high-temperature annealing aiming at electrical activation of the implanted dopants. These processes occur after gate dielectric fabrication and may obviously influence its electrophysical properties.

This work reports on changes in properties of ultra-thin plasma enhanced chemical vapour deposition (PECVD) silicon oxynitride layers after high-temperature treatment. Possible changes in the structure, composition and electrophysical properties were investigated by means of spectroscopic ellipsometry, XPS, SIMS and electrical characterization.

### 2. Experimental

Non-self-aligned Al gate NMOS technology was used to fabricate test structures on 2" p-type  $\langle 100 \rangle$  Si wafers.

Oxynitride layers were deposited in a PlasmaLab System 80+ of Oxford plasma technology. The parameters of the PECVD process were optimized to allow repeatable formation of gate dielectrics. Split experiments with annealing of the obtained layers in argon at 900°C for 30 minutes were done. Process parameters are shown in Table 1.

Table 1 Process parameters allowing formation of ultra-thin silicon oxynitride layers

| Parameters                                   | Values |

|----------------------------------------------|--------|

| SiH <sub>4</sub> (2%): N <sub>2</sub> [sccm] | 150    |

| N <sub>2</sub> O [seem]                      | 16     |

| NH <sub>3</sub> [seem]                       | 32     |

| Pressure [mTr]                               | 500    |

| Power [W]                                    | 10     |

| Time [s]                                     | 20     |

| Temperature [°C]                             | 350    |

| Time of annealing [min]                      | 30     |

| Temperature of annealing [°C]                | 900    |

The properties of the obtained layers were examined by means of: optical, electrical, XPS and SIMS measurements.

The thickness of the oxynitride layers was measured using a J. A. Wollam spectroscopic ellipsometer.

The X-ray photoelectron spectroscopy (XPS) analysis and ultra-low-energy-secondary ion mass spectroscopy (ULE-SIMS) profiles were used to observe the changes in chemical composition and component profiles due to the high-temperature treatment.

The XPS measurements were performed at the undulator beamline U49/2-PGM-2 supplying photons in the energy range of 80 eV – 1500 eV with a resolution above 7000 ( $E/\Delta E$ ). An EA125 electron analyser (Omicron NanoTechnology GmbH) with a resolution of  $\sim$ 200 meV was used.

The SIMS measurements were done using SAJW-05 system equipped with 06-350E Physical Electronics  $Ar^+$  gun (ultra-low energy 880 eV  $Ar^+$  beam) and Balzers QMA-410 quadrupole mass spectrometer. Quantitative atomic concentration of nitrogen and oxygen was calculated based on  $\mathrm{Si}_2N^+,\,\mathrm{Si}_2O^+$  and  $\mathrm{Si}_2^+$  secondary ion currents.

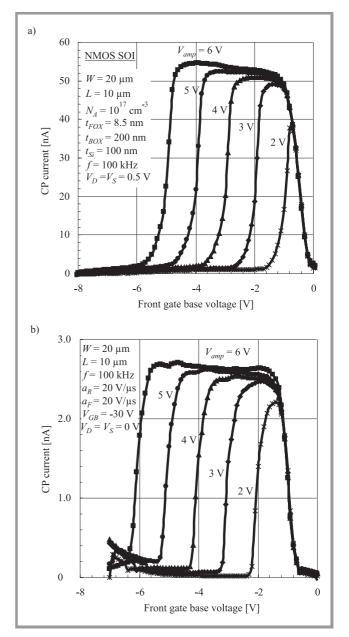

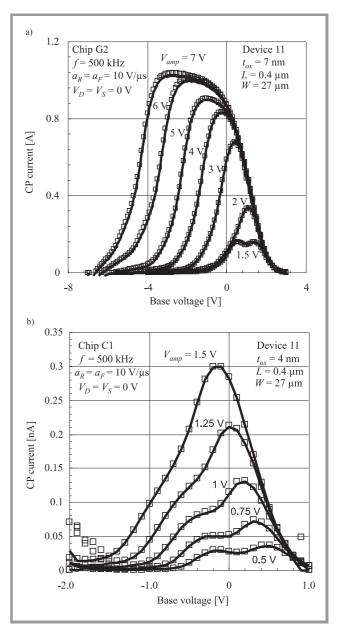

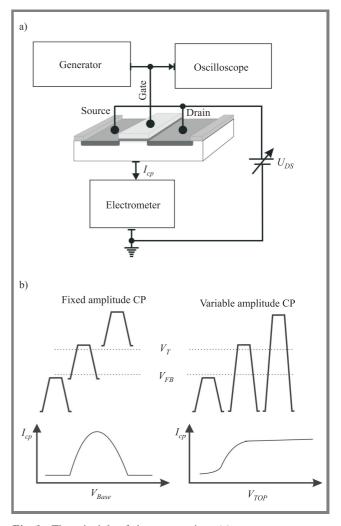

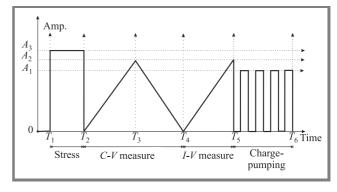

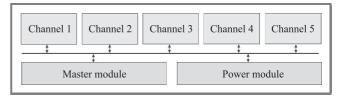

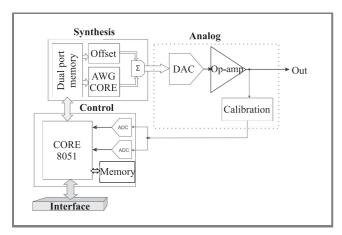

Electrical measurements were performed with Hewlett-Packard 4061A Semiconductor Component Test System (*C-V* characteristics) and Keithley SMU (*I-V* characteristics). The metal-insulator-semiconductor (MIS) capacitors with gate area of  $A=1.7\cdot 10^{-5}$  cm² were used to determine the basic electrophysical properties of the investigated layers. Moreover, charge-pumping currents of MIS-FETs ( $W \times L = 10~\mu\text{m} \times 10~\mu\text{m}$ ) were measured to evaluate interface-trap density.

### 3. Results and discussion

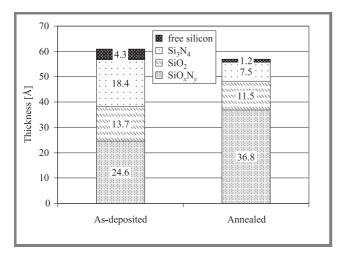

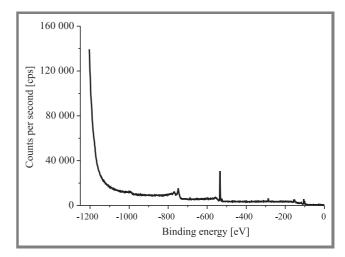

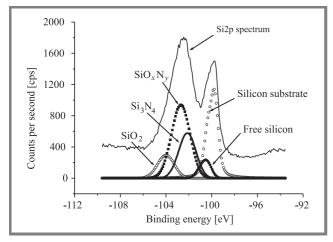

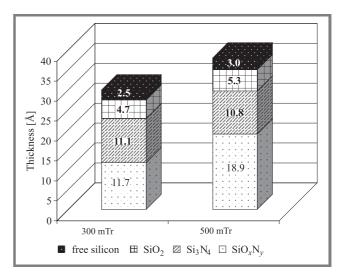

Changes in the structure and composition of PECVD silicon oxynitride layers due to high-temperature annealing were studied by XPS measurements. To get the information about chemical bonds present in  $\mathrm{SiO}_x\mathrm{N}_y$  the measured spectra were analysed using line deconvolution. Every single line was attributed to the particular compound, due to its unique binding energy in the ultra-thin dielectric layer. Figure 1 shows a comparison of the chemical composition of the dielectric layers before and after annealing (expressed in terms of thickness and referred to the thickness obtained from the ellipsometric measurements) as determined from the Si2p line.

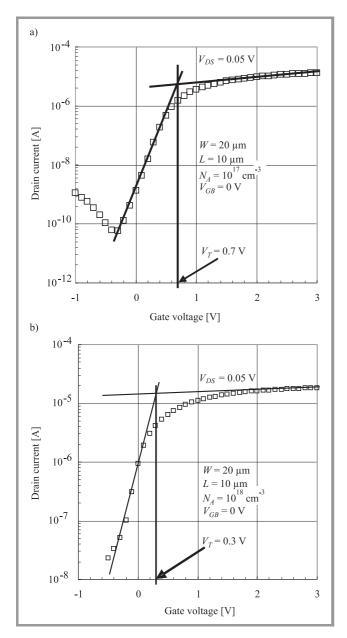

Fig. 1. Composition of PECVD ultra-thin silicon oxynitride layers (expressed as thickness), as determined from the Si2p line analysis.

From Fig. 1 a number of conclusions can be drawn. First –  $SiO_xN_y$  is the dominant phase in both as-deposited and annealed layers. Second – high-temperature annealing causes the amount of all phases other than oxynitride to decrease. These phases include oxide, silicon and, particularly significant, nitride (decreasing by almost 60%). It seems reasonable to expect that the growth of oxynitride takes place at the expense of nitride and oxide, while the decrease of the amount of free silicon resulting from annealing is probably due to the saturation of silicon dangling bonds during this high-temperature process. Third – the ultra-thin oxynitride layer can be considered thermally stable in terms of the total layer thickness, as no significant change in this parameter

is observed after annealing at high temperatures. This is very important for application of such oxynitride layers in the self-aligned CMOS technology since post implantation high-temperature annealing must not result in any significant changes of the layer thickness. Such changes would obviously be detrimental to the overall integrity of the gate stack.

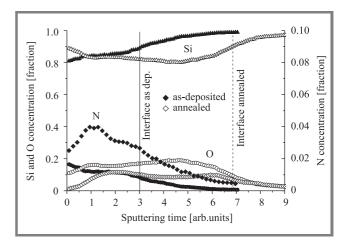

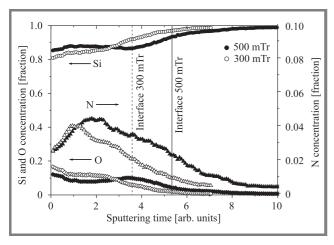

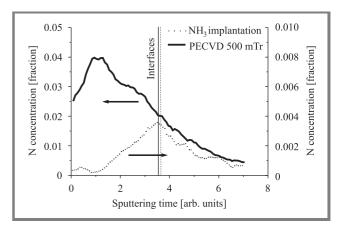

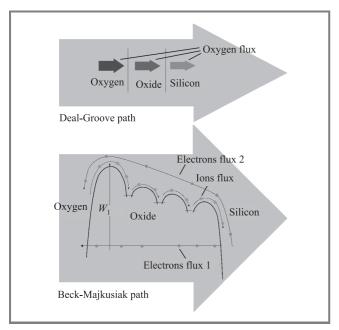

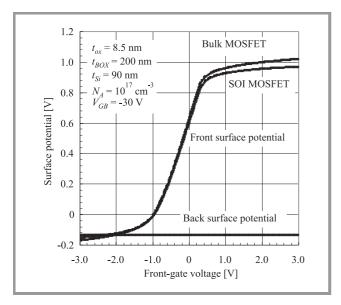

The SIMS profiles obtained for the same layers are shown in Fig. 2. It should be noticed that despite comparable physical thickness (as determined by ellipsometric measurements), sputtering of annealed dielectric layers during the measurement is much slower than that of as-deposited ones. Consequently, the location of the silicon/layer interface on the sputtering time scale is quite different for as-deposited and annealed layers (see Fig. 2). This difference in etching

Fig. 2. The SIMS profiles of as-deposited and annealed silicon oxynitride layers.

rate has to be attributed to changes in physical and chemical properties (e.g., saturation of dangling bonds, densification of the layer) that must have taken place during high-temperature annealing of the oxynitride layers. A similar result has been observed during wet etching of ultra-thin oxynitride layers during formation of transistor gate. The wet etching time increased 18 times (from 10 seconds for as-deposited layers to 3 minutes for annealed ones)!

These observations indicate that annealed layers should exhibit better electrophysical properties than as-deposited ones. In fact, these expectations have been confirmed by the analysis of electrical properties of the studied ultra-thin dielectric/silicon system. The results of this analysis are presented below.

Another observation resulting from SIMS profiles is that nitrogen and oxygen are distributed more homogeneously in annealed layers than in as-deposited ones. In the case of the latter the maximum nitrogen concentration is located well within the layer (neither close to the top surface, nor to the interface).

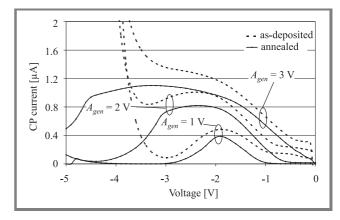

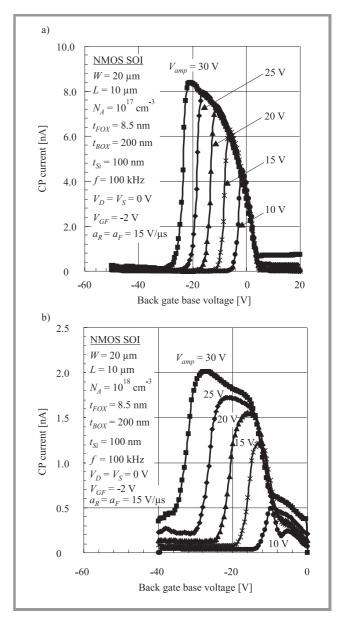

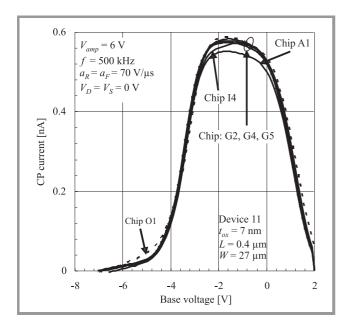

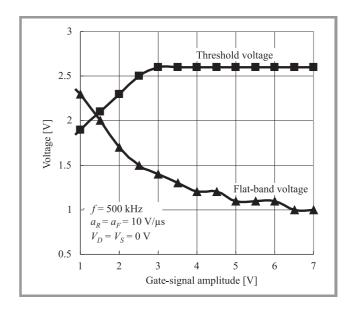

The capacitance-voltage characteristics obtained from the test structures are shown in Fig. 3. It is clear that *C-V* curves of MIS capacitors with annealed oxynitrides exhibit smaller frequency dispersion in all regions (inversion,

*Fig. 3.* Comparison of *C-V* characteristics of MIS structures with (a) as-deposited and (b) annealed silicon oxynitride layers.

depletion and accumulation). Moreover, the maximum capacitance  $C_{\rm max}$  is higher in annealed structures. Since the total layer thickness (determined by ellipsometric measurements) is comparable for both annealed and as-deposited layers and  $C_{\rm max}$  is stable over a wide voltage range we can conclude that the dielectric constant is increased as a result of annealing. The parameters presented in Table 2 confirm this assumption.

Table 2 Optical thickness and basic electrophysical properties of PECVD  $SiO_xN_y$  layers

| Parameters                                    | As-deposited         | Annealed             |

|-----------------------------------------------|----------------------|----------------------|

| Thickness [A]                                 | 61                   | 57                   |

| EOT [Å]*                                      | 50                   | 42                   |

| $Q_{eff}/q~\mathrm{[cm^{-2}]^{**}}$           | $4.75 \cdot 10^{12}$ | $4.82 \cdot 10^{12}$ |

| $D_{it} [\text{cm}^{-2}\text{ev}^{-1}]^{***}$ | $1.2\cdot 10^{13}$   | $7.2 \cdot 10^{12}$  |

\* EOT stands for equivalend oxide thickness (determined from *C-V* measurements), \*\* evaluated from *C-V* measurements, \*\*\* evaluated from *C-P* measurements.

Table 2 compares the thickness and basic electrophysical parameters of the oxynitride layers, determined by means of spectroscopic ellipsometry, *C-V* and charge-pumping (CP).

The equivalent oxide thickness (EOT) is lower than physical thickness by 16% in the case of as-deposited layers and by 26% in the case of annealed ones. This is due to the fact that the dielectric constant of annealed layers is higher than that of as-deposited ones. The effective charge (as determined from *C-V* measurements) does not seem to be affected by annealing but the trap density determined from CP measurements is almost twice lower for annealed layers. It may be thus concluded that annealed oxynitride exhibits better electrophysical properties.

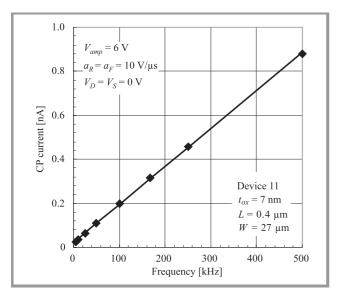

Fig. 4. Comparison of CP currents of MISFETs ( $W \times L = 10 \ \mu \text{m} \times 10 \ \mu \text{m}$ ).

As seen in Fig. 4 only CP characteristics of MISFETs with annealed layers demonstrate classical behavior. Significantly higher CP currents of MISFETs with as-deposited layers at higher gate voltages are probably caused by higher leakage current (see Fig. 5) [4]. Additionally, CP currents of the MISFETs with annealed gate dielectric are clearly lower than these of as-deposited layers. This indicates that annealed layers have lower trap density (see Table 2).

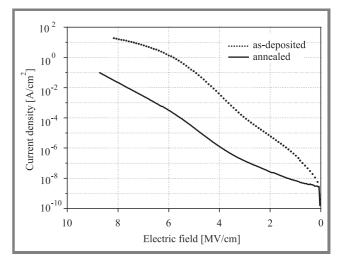

Fig. 5. Current density versus mean electric field within the dielectric layer.

The current-voltage characteristics were also measured in this study. To facilitate a comparison of the insulating properties of the investigated layers, these characteristics are

3/2007

presented in Fig. 5 as current density versus mean electric field within the  $SiO_xN_y$  layer. It is clear that oxynitride layers exposed to high-temperature treatment show much better insulating properties – at intermediate electric fields current density of as-deposited layers is almost four orders of magnitude higher than that of annealed ones.

### 4. Conclusions

Ultra-thin PECVD silicon oxynitride layers were investigated by means of spectroscopic ellipsometry, XPS, SIMS and electrical characterization.

Ultra-thin PECVD silicon oxynitrides undergo complex changes in chemical composition due to thermal treatment (e.g., decreasing amount of oxide and nitride and increasing amount of  $SiO_xN_y$ ). The amount of free silicon is lower in annealed layers – probably due to the saturation of free dangling bonds caused by annealing.

Oxygen and nitrogen are distributed more homogenously throughout annealed layers than as-deposited ones. In asdeposited oxynitride layers a maximum of nitrogen concentration is visible between the two interfaces.

Annealed silicon oxynitrides have better insulating properties (as evidenced by significantly lower leakage current). Additionally, annealed  $SiO_xN_y/Si$  system has better electrical parameters – lower frequency dispersion and lower interface traps density.

In view of all these results it is justified to conclude that high-temperature annealing improves electrophysical properties of silicon oxynitride layers. Moreover, oxynitride is thermally stable in terms of the total layer thickness, therefore high-temperature annealing may be applied (e.g., dopant activation after the implantation process) following the formation of the gate dielectric in self-aligned CMOS technology.

### Acknowledgements

This work was partly supported by the 6th Framework Programme of the European Union under contract no. 506844 SINANO (Silicon-based nanodevices) and partly by the Polish Ministry of Science and Higher Education under grant no. 4 T11B 023 25.

### References

- International Technology Roadmap for Semiconductors, http://www.itrs.net/

- [2] G. D. Wilk, R. M. Wallace, and J. M. Anthony, "High-k dielectrics current status and materials considerations", J. Appl. Phys., vol. 89, no. 10, pp. 5243–5275, 2001.

- [3] M. L. Green, E. P. Gusev, R. Degraeve, and E. L. Garfunkel, "Ultrathin (< 4 nm) SiO<sub>2</sub> and Si-O-N gate dielectric layers for silicon microelectronics: understanding the processing, structure and physical and electrical limits", *J. Appl. Phys.*, vol. 90, no. 5, pp. 2057–2121, 2001.

- [4] J. Hee-Hwan et al., "On-chip charge pumping method for characterization of interface states of ultra thin gate oxides in nano-CMOS technology", in *IEDM 2005 Conf.*, Washington, USA, 2005.

Robert Mroczyński was born in Warsaw, Poland, in 1978. He received the M.Sc. degree in microelectronics from the Faculty of Electronics and Information Technology, Warsaw University of Technology in 2003, where he is currently working towards a Ph.D. degree. His research concentrates on fabrication, characterization, process-

ing and application of ultra-thin dielectric layers (e.g., silicon oxynitride) in CMOS-ULSI devices.

e-mail: rmroczyn@elka.pw.edu.pl Institute of Microelectronics and Optoelectronics Warsaw University of Technology Koszykowa st 75 00-662 Warsaw, Poland

**Romuald B. Beck** and **Andrzej Jakubowski** – for biographies, see this issue, p. 7.

Grzegorz Głuszko, Michał Ćwil, and Piotr Konarski – for biographies, see this issue, p. 8.

**Patrick Hoffmann** and **Dieter Schmeißer** – for biographies, see this issue, p. 15.

# Comparison of composition of ultra-thin silicon oxynitride layers' fabricated by PECVD and ultrashallow rf plasma ion implantation

Robert Mroczyński, Tomasz Bieniek, Romuald B. Beck, Michał Ćwil, Piotr Konarski, Patrick Hoffmann, and Dieter Schmeißer

Abstract—In this paper differences in chemical composition of ultra-thin silicon oxynitride layers fabricated in planar rf plasma reactor are studied. The ultra-thin dielectric layers were obtained in the same reactor by two different methods: ultrashallow nitrogen implantation followed by plasma oxidation and plasma enhanced chemical vapour deposition (PECVD). Chemical composition of silicon oxynitride layers was investigated by means of X-ray photoelectron spectroscopy (XPS) and secondary ion mass spectrometry (SIMS). The spectroscopic ellipsometry was used to determine both the thickness and refractive index of the obtained layers. The XPS measurements show considerable differences between the composition of the fabricated layers using each of the above mentioned methods. The SIMS analysis confirms XPS results and indicates differences in nitrogen distribution.

Keywords—ultra-thin dielectrics, oxynitride, SIMS, XPS, PECVD.

### 1. Introduction

Silicon oxynitride has been investigated extensively for several years as an alternative for silicon dioxide (e.g., [1]). This is mainly due to the fact that the dielectric constant of oxynitride is slightly higher than that of SiO<sub>2</sub>, the reliability of the oxynitride/silicon system is better and boron and phosphorus diffusion is reduced. Moreover, the diffusion of atomic hydrogen is also suppressed by silicon oxynitride (e.g., [2]).

Nowadays, as the thickness of the gate dielectric layers has reached the scale of a few nanometers, understanding the chemical composition of such thin layers is of extreme importance. For appropriate characterization of such ultra-thin layers ultra-low energy secondary ion mass spectroscopy (ULE-SIMS) and XPS can be used [3, 4].

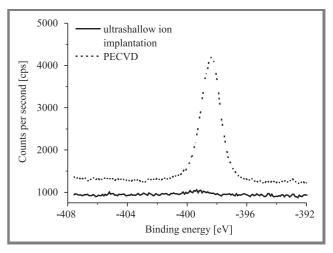

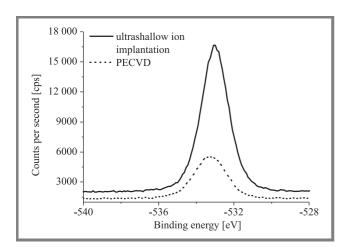

In this paper ultra-thin silicon oxynitride layers were fabricated in a planar rf plasma reactor. The dielectric layers were obtained in the same reactor using two different methods: ultrashallow nitrogen implantation followed by plasma oxidation (referred to hereafter as implantation/oxidation) and plasma enhanced chemical vapour deposition (PECVD). The source of plasma used during nitrogen implantation was either ammonia (NH<sub>3</sub>) or pure nitrogen (N<sub>2</sub>).

Chemical composition of silicon oxynitride layers was investigated by means of XPS and ULE-SIMS. Spectroscopic ellipsometry was used to determine the thickness and refractive index of the obtained layers.

### 2. Experimental

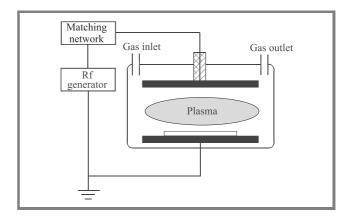

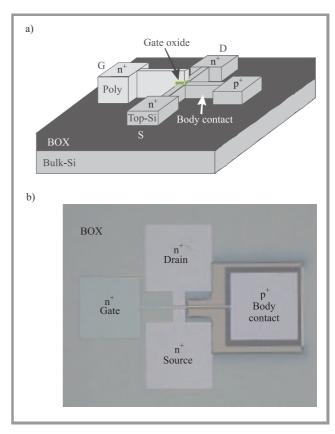

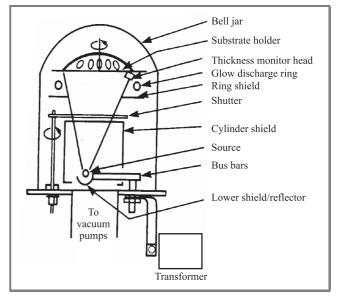

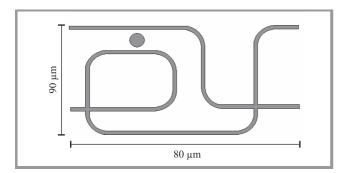

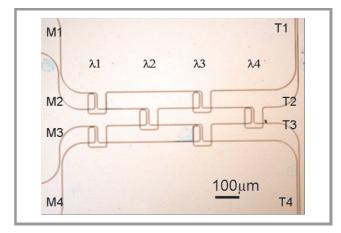

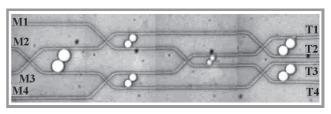

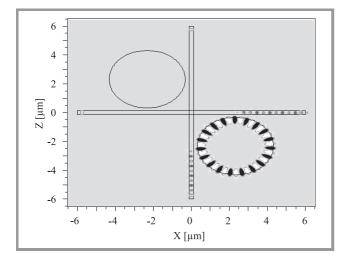

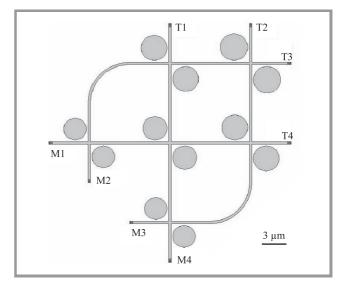

Two-inch  $\langle 100 \rangle$  p type silicon substrates of the resistivity 4–7  $\Omega$ cm were used in this study. The silicon oxynitride films were fabricated in an Oxford plasma technology PlasmaLab 80+ system. The silicon substrates were cleaned using the standard RCA method. A schematic view of the equipment used is shown in Fig. 1.

Fig. 1. Schematic view of the parallel plate reactor.

Process parameters necessary for ultra-thin oxynitride to be formed are presented in Table 1.

The properties of the obtained layers were studied by ellipsometric, XPS and ULE-SIMS analysis. A J.A. Woollam Co. ellipsometer allowing measurements at different angles with the wavelength ranging from 250 nm to 1400 nm was used to determine the thickness and refractive index of the investigated layers.

The XPS and ULE-SIMS measurements were used to investigate differences in the chemical composition and profiles of  $SiO_xN_y$  layers. XPS measurements were performed at 1254 eV at the Brandenburg University of Technology in Cottbus. SIMS measurements were done at the Industrial Institute of Electronics in Warsaw using

SAJW-05 system equipped with 06-350E Physical Electronics Ar+ gun (ultra-low energy 880 eV Ar<sup>+</sup> beam) and Balzers QMA-410 quadrupole mass spectrometer. Ar<sup>+</sup> beam (100  $\mu$ m in diameter) was rastered over an area of 2 mm  $\times$  2 mm in order to get low ion current density and appropriate sputtering rate during ion bombardment. With this high in-depth resolution could be obtained.

Table 1

Process parameters allowing formation of ultra-thin dielectric layers

|                                                   | Ultrashal<br>implan         |                           |       |    |

|---------------------------------------------------|-----------------------------|---------------------------|-------|----|

| Parameters                                        | Step 1 – plasma nitridation | Step 2 – plasma oxidation | PECVD |    |

| Power [W]                                         | 50                          | 1                         | 0     |    |