# JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY

1/2010

| History of Semiconductors                                                                                                                                                                 |               |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----|

| L. Lukasiak and A. Jakubowski                                                                                                                                                             | Invited Paper | 3  |

| Charging Phenomena at the Interface Between High-k Dielectrics and SiO <sub>x</sub> Interlayers                                                                                           |               |    |

| O. Engström et al.                                                                                                                                                                        | Invited Paper | 10 |

| Novel Method of Improving Electrical Properties of Thin PECVD Oxide Films by Fluorination of Silicon Surface Region by RIE in RF CF <sub>4</sub> Plasma                                   |               |    |

| M. Kalisz, G. Głuszko, and R. B. Beck                                                                                                                                                     | Paper         | 20 |

| The Effect of High Temperature Annealing on Fluorine Distribution Profile and Electro-Physical Properties of Thin Gate Oxide Fluorinated by Silicon Dioxide RIE in CF <sub>4</sub> Plasma |               |    |

| M. Kalisz, G. Gluszko, and R. B. Beck                                                                                                                                                     | Paper         | 25 |

| Large-Signal RF Modeling with the EKV3 MOSFET Model                                                                                                                                       |               |    |

| MA. Chalkiadaki and M. Bucher                                                                                                                                                             | Paper         | 29 |

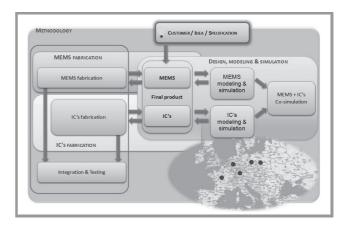

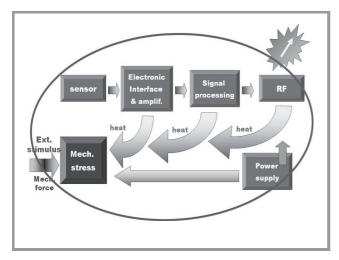

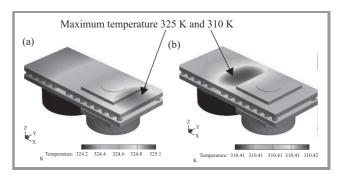

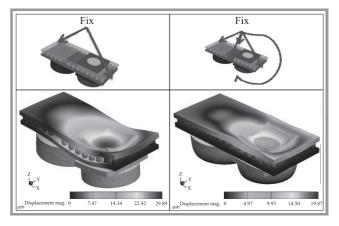

| Multi-Domain Modeling and Simulations of the Heterogeneous Systems                                                                                                                        |               |    |

| T. Bieniek et al.                                                                                                                                                                         | Paper         | 34 |

| Frequency Offset Compensation for OFDM Systems Using a Combined Autocorrelation and Wiener Filtering Scheme                                                                               |               |    |

| A. Ramadan Ali, T. J. Khanzada, and A. Omar                                                                                                                                               | Paper         | 40 |

|                                                                                                                                                                                           |               |    |

(Contents Continued on Back Cover)

#### Editorial Board

| Editor-in Chief:   | Paweł Szczepański                    |

|--------------------|--------------------------------------|

| Associate Editors: | Krzysztof Borzycki<br>Marek Jaworski |

| Managing Editor:   | Maria Łopuszniak                     |

| Technical Editor:  | Ewa Kapuściarek                      |

### Editorial Advisory Board

Marek Amanowicz

Daniel Bem

Wojciech Burakowski

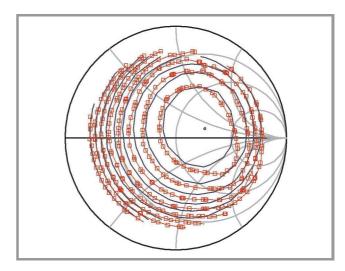

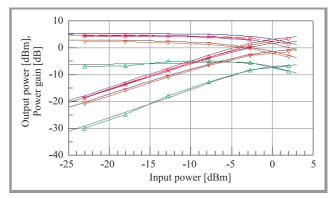

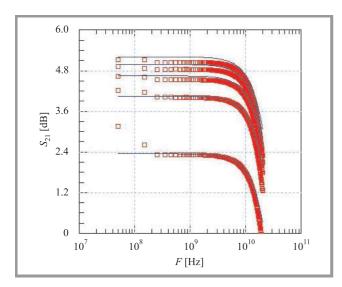

Andrzej Dąbrowski

Andrzej Hildebrandt

Witold Holubowicz

Andrzej Jakubowski

Alina Karwowska-Lamparska

Marian Kowalewski

Andrzej Kowalski

Józef Lubacz

Tadeusz Łuba

Krzysztof Malinowski

Marian Marciniak

Józef Modelski

Ewa Orłowska

Andrzej Pach

Zdzisław Papir

Michał Pióro

Janusz Stokłosa

Wiesław Traczyk

Andrzej P. Wierzbicki

Tadeusz Więckowski

Józef Woźniak

Tadeusz A. Wysocki

Jan Zabrodzki

Andrzej Zieliński

ISSN 1509-4553 on-line: ISSN 1899-8852 © Copyright by National Institute of Telecommunications

Warsaw 2010

Circulation: 300 copies

Sowa - Druk na życzenie, www.sowadruk.pl, tel. 022 431-81-40

# JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY

## Preface

Despite the fact that a range of limitations are beginning to appear as CMOS technology is being raised to ever higher levels of perfection, it is anticipated that silicon will be the dominant material of the semiconductor industry for at least the first half of the 21st century. The forecast for microelectronics development updated in 2008 by SIA (Semiconductor Industry Association) reaches ahead to the years 2016–2022. Unfortunately, comparison with former SIA forecasts indicates that in certain aspects they become less aggressive (that is less optimistic) with time.

While the development of silicon microelectronics in the past could be attributed mostly to the reduction of the feature size (progress in lithography), today it relies more on new material (SOI, SON, SiGe or SiC) and architecture (ultra-thin body, double-gate, multiplegate) solutions. The combination of this trend with continuous miniaturization provides the opportunity of improving IC functionality and speed of operation.

Telecommunications and information technology are arguably the most powerful drivers behind microelectronics product development nowadays. Plenty of new applications are being created for fast analog and RF circuits, as well as for information processing ones. It is clear that with the anticipated peak  $f_{\rm max}=425$  GHz and  $f_T=395$  GHz to be reached by RF SiGe-base bipolar transistors in 2014, according to the 2008 update of ITRS, a lot of efforts must be put into the development of appropriate material, processing, characterization and modeling. While progress in the bipolar technology is impressive, the increase of MOSFET speed is even more so. The same issue of ITRS predicts on-chip clock of  $\sim$ 14 GHz for 2022.

High-speed isn't, however, everything. Portable wireless products push, for obvious reasons, for low-power solutions. This trend requires new architectural solutions (e.g., channel thinning), and in consequence, new materials, such as SOI (or its possible successor SON – silicon-on-nothing), where current driveability is considerably higher than in conventional MOSFETs.

In this issue the Reader will find papers devoted to the history of semiconductors, charging effects at the interfaces between high-k dielectrics and  $\mathrm{SiO}_2$ , the influence of fluorine on the quality of the  $\mathrm{Si-SiO}_2$  interface, large-signal RF modeling, as well as modeling and simulation of heterogeneous systems.

Wireless applications in challenging environments require improved modulation schemes and signal processing. One example is dealing with frequency offset and phase noise in orthogonal frequency division multiplexing (OFDM) systems. In a novel scheme the frequency offset is first estimated using an autocorrelation method, and then refined by applying an iterative phase correction by means of pilot-based Wiener filtering; the method was tested in a multipath indoor environment.

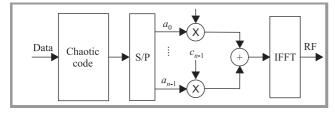

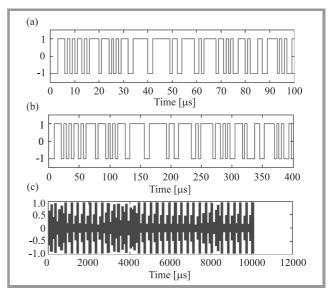

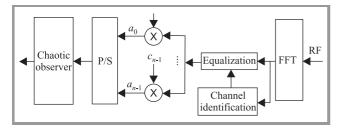

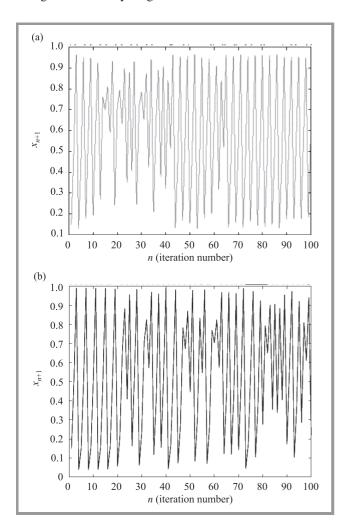

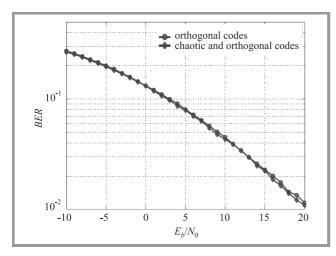

The next study devoted to radio systems included in this issue found that use of chaotic spreading sequence in a multicarrier code division multiple access system (MC-CDMA) to spread spectrum and estimate the transmission channel system significantly outperforms the Walsh-Hadamard code spreading in MC-CDMA system with respect to channel identification. The proposed scheme uses a chaotic sequence generated by a logistic map as a training signal and estimate channel parameters according to dynamics of the chaotic sequence.

Global satellite-based positioning systems enable to build new telematic systems for applications and services in many branches of economy, in particular applied to mobile objects like vehicles, called mobile telematic services. A paper include in this issue presents features of such services, with a special emphasis on services foreseen in Galileo satellite positioning system, including a necessity of complementary communications between a positioned object and related surroundings.

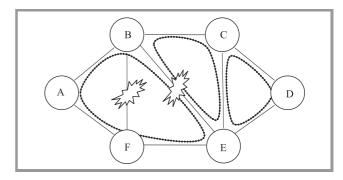

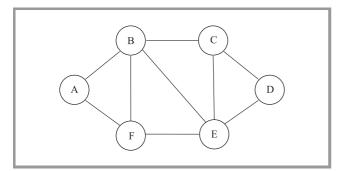

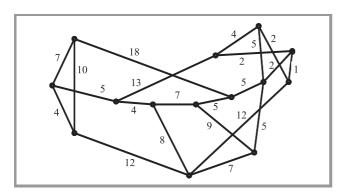

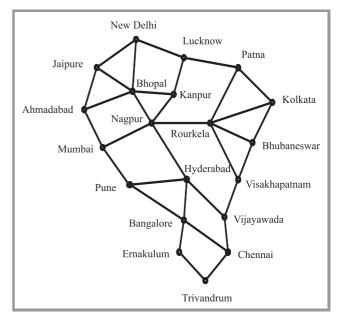

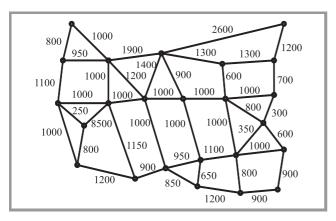

In the age of fast internet, core and metro networks widely employ wavelength division multiplexing (WDM) in optical fiber transmission to satisfy the growing need for bandwidth. While capacity of WDM networks is adequate, failure (e.g., a cable cut) potentially leads to enormous data and revenue loss, and protection is one of the key techniques used in "survivable" WDM networks. The study compares the performance of protection schemes such as dedicated path protection (DPP), shared path protection (SPP) and shared link protection (SLP), taking into account capacity utilization, switching time and blocking probability.

The last subject covered is different: optimization of the multi-threaded interval algorithm for the Pareto-set computation, and the possibility of applying interval methods to seek the Pareto-front of a multicriterial nonlinear problem. An efficient algorithm has been proposed and tested before, the current paper presents its optimization in order to increase the speedup of multi-threaded variant, and to extend the algorithm to compute not only the Pareto-front (in the criteria space), but also the Pareto-set (in the decision space).

We hope the Readers will find this issue of the *Journal of Telecommunications and Information Technology* useful and interesting.

Andrzej Jakubowski Lidia Łukasiak Guest Editors

Paweł Szczepański Editor-in-Chief Invited paper

## **History of Semiconductors**

Lidia Łukasiak and Andrzej Jakubowski

Abstract—The history of semiconductors is presented beginning with the first documented observation of a semiconductor effect (Faraday), through the development of the first devices (point-contact rectifiers and transistors, early field-effect transistors) and the theory of semiconductors up to the contemporary devices (SOI and multigate devices).

Keywords—band theory, laser, Moore's law, semiconductor, transistor.

#### 1. Introduction

There is no doubt that semiconductors changed the world beyond anything that could have been imagined before them. Although people have probably always needed to communicate and process data, it is thanks to the semiconductors that these two important tasks have become easy and take up infinitely less time than, e.g., at the time of vacuum tubes.

The history of semiconductors is long and complicated. Obviously, one cannot expect it to fit one short paper. Given this limitation the authors concentrated on the facts they considered the most important and this choice is never fully impartial. Therefore, we apologize in advance to all those Readers who will find that some vital moments of the semiconductor history are missing in this paper.

The rest of this paper is organized in four sections devoted to early history of semiconductors, theory of their operation, the actual devices and a short summary.

#### 2. Early History of Semiconductors

According to G. Busch [1] the term "semiconducting" was used for the first time by Alessandro Volta in 1782. The first documented observation of a semiconductor effect is that of Michael Faraday (1833), who noticed that the resistance of silver sulfide decreased with temperature, which was different than the dependence observed in metals [2]. An extensive quantitative analysis of the temperature dependence of the electrical conductivity of Ag<sub>2</sub>S and Cu<sub>2</sub>S was published in 1851 by Johann Hittorf [1].

For some years to come the history of semiconductors focused around two important properties, i.e., rectification of metal-semiconductor junction and sensitivity of semiconductors to light and is briefly described in Subsections 2.1 and 2.2.

#### 2.1. Rectification

In 1874 Karl Ferdinand Braun observed conduction and rectification in metal sulfides probed with a metal point

(whisker) [3]. Although Braun's discovery was not immediately appreciated, later it played a significant role in the development of the radio and detection of microwave radiation in WWII radar systems [4] (in 1909 Braun shared a Nobel Prize in physics with Marconi). In 1874 rectification was observed by Arthur Schuster in a circuit made of copper wires bound by screws [4]. Schuster noticed that the effect appeared only after the circuit was not used for some time. As soon as he cleaned the ends of the wires (that is removed copper oxide), the rectification was gone. In this way he discovered copper oxide as a new semiconductor [5]. In 1929 Walter Schottky experimentally confirmed the presence of a barrier in a metal-semiconductor junction [5].

#### 2.2. Photoconductivity and Photovoltaics

In 1839 Alexander Edmund Becquerel (the father of a great scientist Henri Becquerel) discovered the photovoltaic effect at a junction between a semiconductor and an electrolyte [6]. The photoconductivity in solids was discovered by Willoughby Smith in 1873 during his work on submarine cable testing that required reliable resistors with high resistance [7]. Smith experimented with selenium resistors and observed that light caused a dramatic decrease of their resistance. Adams and Day were the first to discover the photovoltaic effect in a solid material (1876). They noticed that the presence of light could change the direction of the current flowing through the selenium connected to a battery [8]. The first working solar cell was constructed by Charles Fritts in 1883. It consisted of a metal plate and a thin layer of selenium covered with a very thin layer of gold [8]. The efficiency of this cell was below 1% [9].

#### 3. Theory

In 1878 Edwin Herbert Hall discovered that charge carriers in solids are deflected in magnetic field (Hall effect). This phenomenon was later used to study the properties of semiconductors [10]. Shortly after the discovery of the electron by J. J. Thomson several scientists proposed theories of electron-based conduction in metals. The theory of Eduard Riecke (1899) is particularly interesting, because he assumed the presence of both negative and positive charge carriers with different concentrations and mobilities [1]. Around 1908 Karl Baedeker observed the dependence of the conductivity of copper iodide on the stoichiometry (iodine content). He also measured the Hall effect in this material, which indicated carriers with positive charge [1]. In 1914 Johan Koenigsberger divided solid-state materials into three groups with respected to their conductivity: metals,

insulators and "variable conductors" [1]. In 1928 Ferdinand Bloch developed the theory of electrons in lattices [10]. In 1930 Bernhard Gudden reported that the observed properties of semiconductors were due exclusively to the presence of impurities and that chemically pure semiconductor did not exist [1].

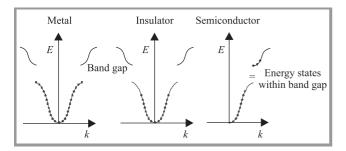

Fig. 1. Alan Wilson's theory of bands in solids.

In 1930 Rudolf Peierls presented the concept of forbidden gaps that was applied to realistic solids by Brillouin the same year. Also in 1930 Kronig and Penney developed a simple, analytical model of periodic potential. In 1931 Alan Wilson developed the band theory of solids based on the idea of empty and filled energy bands (Fig. 1). Wilson also confirmed that the conductivity of semiconductors was due to impurities [10]. In the same year Heisenberg developed the concept of hole (which was implicit in the works of Rudolf Peierls [10]). In 1938 Walter Schottky and Neville F. Mott (Nobel Prize in 1977) independently developed models of the potential barrier and current flow through a metal-semiconductor junction. A year later Schottky improved his model including the presence of space charge. In 1938 Boris Davydov presented a theory of a copper-oxide rectifier including the presence of a p-n junction in the oxide, excess carriers and recombination. He also understood the importance of surface states [11]. In 1942 Hans Bethe developed the theory of thermionic emission (Nobel Prize in 1967).

#### 4. Devices

#### 4.1. Point-Contact Rectifiers

In 1904 J. C. Bose obtained a patent for PbS point-contact rectifiers [12]. G. Pickard was the first to show that silicon point-contact rectifiers were useful in detection of radio waves (patent in 1906) [10]. The selenium and copper oxide rectifiers were developed, respectively, in 1925 by E. Presser and 1926 by L. O. Grondahl [10]. The selenium rectifiers were heavily used in the WWII in military communications and radar equipment [10].

#### 4.2. The p-n Junction

During his work on the detection of radio waves Russel Ohl realized that the problems with cat's whisker detectors were caused by bad quality of the semiconductor. Therefore he melted the silicon in quartz tubes and then let it cool down. The obtained material was still polycrystalline but the electrical tests demonstrated that the properties were much more uniform. Ohl identified the impurities that created the p-n junction that he accidentally obtained during his technological experiments. He held four patents on silicon detectors and p-n junction [13].

#### 4.3. Bipolar Transistor

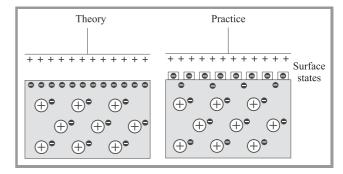

In 1945 William Shockley put forward a concept of a semiconductor amplifier operating by means of the field-effect principle. The idea was that the application of a transverse electric field would change the conductance of a semiconductor layer. Unfortunately this effect was not observed experimentally. John Bardeen thought that this was due to surface states screening the bulk of the material from the field (Fig. 2). His surface-theory was published in 1947 [14].

Fig. 2. The idea of surface states.

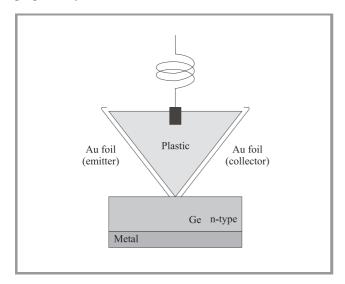

While working on the field-effect devices, in December 1947 John Bardeen and Walter Brattain built a germanium point-contact transistor (Fig. 3) and demonstrated that this device exhibited a power gain. There was, however, an uncertainty concerning the mechanism responsible for the transistor action [13]. Bardeen and Brattain were convinced that surface-related phenomena had the dominant role in the operation of the new device while Shockley favoured bulk conduction of minority carriers. About one month later he developed a theory of a p-n junction and a junction transistor [15]. Shockley, Bardeen and Brattain received the Nobel Prize in physics in 1956 (John Bardeen received another one in 1972 for his theory of superconductivity). In February 1948 John Shive demonstrated a correctly operating point-contact transistor with the emitter and collector placed on the opposite sides of a very thin slice of germanium (0.01 cm). This configuration indicated that the conduction was indeed taking place in the bulk, not along the surface (the distance between the emitter and collector along the surface would be much longer) [15]. It was only then that Shockley presented his theory of transistor operation to the coworkers [15], [16].

It is worth remembering that the crucial properties of semiconductors at the time were "structure sensitive" (as Bardeen put it in [14]), that is they were strongly dependent on the purity of the sample. The semiconductor material with which Bardeen and Brattain worked was prepared using a technique developed by Gordon K. Teal and John B. Little based on the Czochralski method. The crystal was then purified using the zone refining method proposed by William G. Pfann [11].

Fig. 3. The first point-contact transistor [16].

Point-contact transistors were the first to be produced, but they were extremely unstable and the electrical characteristics were hard to control. The first grown junction transistors were manufactured in 1952. They were much better when compared to their point-contact predecessor, but the production was much more difficult. As a result of a complicated doping procedure the grown crystal consisted of three regions forming an n-p-n structure. It had to be cut into individual devices and contacts had to be made. The process was difficult and could not be automated easily. Moreover, a lot of semiconductor material was wasted. In 1952 alloyed junction transistor was reported (two pellets of indium were alloyed on the opposite sides of a slice of silicon). Its production was simpler and less material-consuming and could be automated at least partially. The obtained base width was around 10  $\mu$ m, which let the device operate up to a few MHz only. The first diffused Ge transistor (diffusion was used to form the base region, while the emitter was alloyed) with a characteristic "mesa" shape was reported in 1954. The base width was 1  $\mu$ m and the cut-off frequency 500 MHz. It was generally understood that for most applications silicon transistors would be better than germanium ones due to lower reverse currents. The first commercially available silicon devices (grown junction) were manufactured in 1954 by Gordon Teal. The first diffused Si transistor appeared in 1955. To reduce the resistivity of the collector that limited the operation speed without lowering the breakdown voltage too much John Early thought of a collector consisting of two layers, i.e., high-resistivity one on top of a highly doped one. A transistor with epitaxial layer added was reported in 1960. In the same year Jean Hoerni proposed the planar transistor (both base and emitter regions diffused). The oxide that served as a mask was not removed and acted as a passivating layer [15].

Further improvement of speed was proposed by Herbert Kroemer. A built-in electric field could be introduced into the base by means of graded doping. Another way of introducing the electric field in the base he thought of was grading the composition of the semiconductor material itself, which resulted in graded band gap. This heterostructure concept could not be put to practice easily because of fabrication problems [17].

#### 4.4. Integrated Circuit

The transistor was much more reliable, worked faster and generated less heat when compared to the vacuum tubes [18]. Thus it was anticipated that large systems could be built using these devices. The distance between them had, however, to be as short as possible to minimize delays caused by interconnects. In 1958 Jack Kilby demonstrated the first integrated circuit where several devices were fabricated in one silicon substrate and connected by means of wire bonding. Kilby realized that this would be a disadvantage therefore in his patent he proposed formation of interconnects by means of deposition of aluminum on a layer of SiO<sub>2</sub> covering the semiconductor material [15]. This has been achieved independently by Robert Noyce in 1959. In 2000 Jack Kilby received a Noble Prize in physics for his achievements.

#### 4.5. Tunnel Diode

Leo Esaki studied heavily doped junctions to find out how high the base of a bipolar transistor could be doped before the injection at the emitter junction became inadequate. He was aware that in very narrow junctions tunneling could take place. He obtained the first Ge tunneling diode in 1957 and a silicon one in 1958. Esaki's presentation at the International Conference of Solid State Physics in Electrons and Telecommunications in 1958 was highly appreciated by Shockley [19]. Unfortunately, Shockley exhibited a complete lack of interest when Robert Noyce came to him to present his idea of a tunnel diode two years earlier. As a result Noyce moved to other projects [20]. The tunnel diode was extremely resistant to the environmental conditions due to the fact that conduction was not based on minority carriers or thermal effects. Moreover, its switching times were much shorter than those of the transistor. Leo Esaki received a Nobel Prize in physics in 1973 for his work on tunneling and superlattices [21], [22].

## 4.6. Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET)

In 1930 and 1933 Julius Lilienfeld obtained patents for devices resembling today's MESFET and MOSFET, respec-

tively. In 1934 Oskar Heil applied for a patent for his theoretical work on capacitive control in field-effect transistors [3].

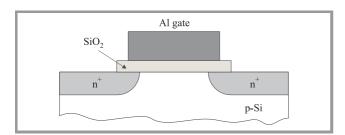

The first bipolar transistors were quite unreliable because semiconductor surface was not properly passivated. A group directed by M. M. Atalla worked on this problem and found out that a layer of silicon dioxide could be the answer [23]. During the course of this work a new concept of a field-effect transistor was developed and the actual device manufactured [24]. Unfortunately, the device could not match the performance of bipolar transistors at the time and was largely forgotten [15]. Several years before Bell Laboratories demonstrated an MOS transistor Paul Weimer and Torkel Wallmark of RCA did work on such devices. Weimer made transistors of cadmium sulfide and cadmium selenide [11]. In 1963 Steven Hofstein and Fredric Heiman published a paper on a silicon MOSFET [25] (Fig. 4). In the same year the first CMOS circuit was proposed by Frank Wanlass [26]. In 1970 Willard Boyle and George Smith presented the concept of charge-coupled devices (CCD) – a semiconductor equivalent of magnetic bubbles [27]. Both scientists received a Nobel Prize in physics in 2009 for their work on CCD.

Fig. 4. A cross section of a metal-oxide-semiconductor transistor.

Early MOSFETs had aluminum gate. Development of a poly-Si gate [28] led to a self-aligned device, where the gate itself constitutes the mask for source and drain diffusion. In this way parasitic gate-to-source and gate-to-drain capacitances associated with gate overlap could be controlled. Since polysilicon had relatively high resistance, gates made of silicides of refractory metals were proposed (e.g., [29], [30]).

Reduction of the size of the device led to the so-called short-channel effects (SCE) including threshold voltage roll-off and drain-induced barrier lowering. The ways to cope with this problem include a reduction of the depth of source and drain [31] combined with efforts to avoid increased resistance (e.g., lightly doped drain [32], elevated source/drain (S/D) [33] or possibly Schottky barrier S/D [34]). Threshold voltage and punchthrough are controlled by means of the appropriate doping profile of the channel that makes it possible to maintain relatively good surface mobility (e.g., [35]). Short-channel effects are considerably reduced when gate oxide is thin. As a result of decreased thickness, gate leakage current obviously grows, increasing power consumption of the entire chip, which is an undesirable effect for battery-powered mobile systems.

It is estimated that gate leakage current increases approximately 30 times every technology generation, as opposed to 3–5 times increase of channel leakage current [36]. Apart from leakage current, the reduction of gate-oxide thickness increases the susceptibility of the device to boron penetration from the poly-Si gate into the channel. A number of different high-k materials are extensively investigated.

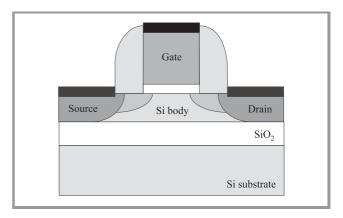

Fig. 5. A cross section of a SOI MOSFET.

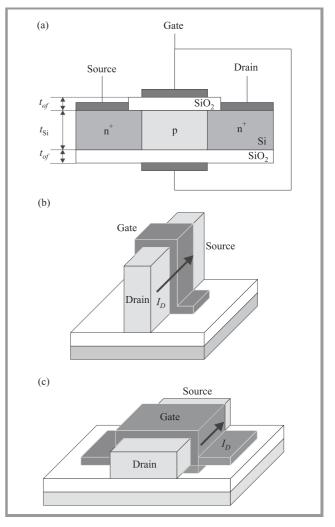

Fig. 6. Mutigate transistors: (a) double gate; (b) FinFET; (c) surrounding gate.

1/2010

An interesting extension of the classical bulk MOSFET is silicon-on-insulator (SOI) – see Fig. 5 [37]. The advantage of SOI is the ease of electrical isolation of a device from the rest of the integrated circuit, which increases packing density. Moreover, the area of source and drain junctions is significantly reduced, thus decreasing parasitic capacitances. Finally, the depletion width is limited by the Si body thickness, therefore it is widely believed that SOI helps reduce short channel effects unless source-to-drain coupling through channel and BOX cannot be neglected. The properties of SOI devices are improved with the reduction of body thickness. It is believed that fully depleted ultra-thin-body SOI (FD UTB SOI) is one of the best scaling solutions. Due to excellent gate control of the channel these devices may be undoped or very lightly doped. In this way mobility is not degraded and threshold voltage is less dependent on the fluctuations of doping concentration [38]. Another advantage of SOI is that it facilitates development of new device concepts [39] (Fig. 6), but this is another story.

#### 4.7. Semiconductor Lasers

Semiconductors are widely used for emission and detection of radiation. The first report on light emitted by a semiconductor appeared in 1907 in a note by H. J. Round. Fundamental work in this area was conducted, among other, by Losev. A very interesting description of the development of light-emitting diodes may be found in [40] while the history of photovoltaics is discussed in [8]. In this section only semiconductor lasers are mentioned briefly.

The first semiconductor lasers were developed around 1962 by four American research teams [41]. Further research in this area went in two directions, i.e., wider spectrum of materials to obtain wider wavelength range and concepts of new device structures. Herbert Kroemer and Zhores Alferov have independently come up with the idea that semiconductor lasers should be built on heterostructures. Zhores Alferov was a member of the team that created the first Soviet p-n junction transistor in 1953. He was directly involved in research aimed at development of specialized semiconductor devices for Russian nuclear submarines. The matter was of such importance for the Soviet authorities that he used to receive phone calls from very high government officials who wanted the work done faster. To fulfill those requests Alferov had to move to the lab and literally live there [42]. Later he worked on power devices and became familiar with p-i-n and p-n-n structures. When the first report on semiconductor lasers appeared, he realized that double heterostructures of the p-i-n type should be used in these devices [41]. He obtained the first practical heterostructure devices and the first heterostructure laser [42]. In 2000 Alferov and Kroemer (mentioned in Subsection 4.4) received a Nobel Prize in physics for their achievements in the area of semiconductor heterostructures used in high-speed- and optoelectronics.

Significant progress in semiconductor lasers is associated, among other, with the use of quantum wells and new materials, especially gallium nitride.

#### 5. Summary

Silicon may be considered as the information carrier of our times. In the history of information there were two revolutions (approximately 500 years apart). The first was that of Johan Gutenberg who made information available to many, the other is the invention of the transistor. Currently the global amount of information doubles every year. Many things we are taking for granted (such as, e.g., computers, Internet and mobile phones) would not be possible without silicon microelectronics. Electronic circuits are also present in cars, home appliances, machinery, etc. Optoelectronic devices are equally important in everyday life, e.g., fiberoptic communications for data transfer, data storage (CD and DVD recorders), digital cameras, etc.

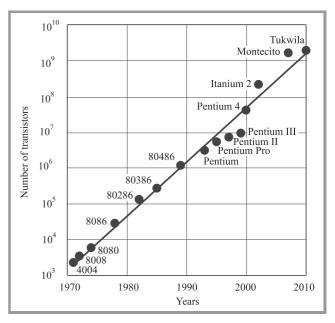

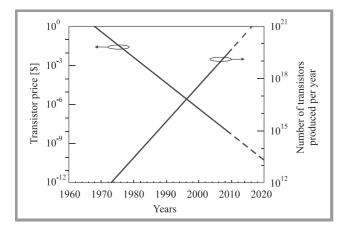

Since the beginning of semiconductor electronics the number of transistors in an integrated circuit has been increasing exponentially with time. This trend had been first noticed by Gordon Moore [43] and is called Moore's law. This law is illustrated in Fig. 7, where the number of transistors in successive Intel processors is plotted as a function of time (data after [44]).

*Fig.* 7. Number of transistors in successive Intel processors as a function of time (data after [44]).

Even though the bipolar technology was largely replaced by CMOS (more than 90 percent of integrated circuits are manufactured in CMOS technology), Moore's law is still true in many aspects of the development trends of silicon microelectronics (obviously, with the appropriate time constant). The MOS transistor has been improved countless times but above everything else it has been miniaturized

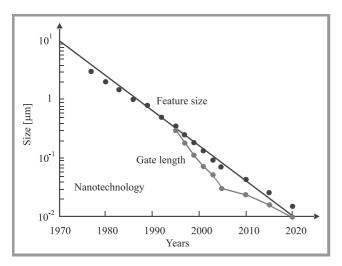

Fig. 8. Feature size as a function of time (data after [45]).

beyond imagination. The reduction of the feature size, presented in Fig. 8, is more or less exponential. The number of transistors produced per year and the average price are shown as a function of time in Fig. 9 (again the change is exponential). It is being anticipated that in 2010 approximately one billion transistors will be produced for every person living on the Earth.

Fig. 9. Number of transistors produced per year and transistor price as a function of time (data after [46]).

We are pretty sure the future still holds a few surprises. Extensive research is being carried out on graphene, organic electronics, quantum devices, microsystems, integration of silicon with other materials and many other issues, but that is another story...

#### References

- [1] G. Busch, "Early history of the physics and chemistry of semiconductors from doubts to fact in a hundred years", Eur. J. Phys., vol. 10, no. 4, pp. 254–263, 1989.

- [2] F. Laeri, F. Schüth, U. Simon, and M. Wark, Host-Guest-Systems Based on Nanoporous Crystals. Weinheim: Wiley, 2003, pp. 435–436.

- [3] T. K. Sarkar, R. Mailloux, A. A. Oliner, M. Salazar-Palma, and D. L. Sengupta, *The History of Wireless*. Hoboken: Wiley, 2006.

- [4] J. Orton, Semiconductors and the Information Revolution: Magic Crystals that Made IT Happen. Amsterdam: Academic Press/Elsevier, 2009, pp. 35–36

- [5] W. Mönch, Semiconductor Surfaces and Interfaces. Berlin-Heidelberg: Springer, 2001.

- [6] Z. A. Smith and K. D. Taylor, Renewable and Alternative Energy Sources: A Reference Handbook. Santa Barbara: ABC-CLIO Inc., 2008, p. 157.

- [7] J. Orton, *The Story of Semiconductors*. Oxford: Oxford University Press, 2004, p. 359.

- [8] J. Perlin, From Space to Earth: The Story of Solar Electricity. Cambridge: Harvard University Press, 2002, p. 17.

- [9] M. Grundman, The Physics of Semiconductors. Berlin-Heidelberg: Springer, 2006.

- [10] L. Hoddeson, E. Braun, J. Teichmann, and S. Weart, Out of the Crystal Maze: Chapters in the History of Solid State Physics. New York: Oxford University Press, 1992.

- [11] B. Lojek, History of Semiconductor Engineering. Berlin-Heidelberg: Springer, 2007.

- [12] P. K. Bondyopathyay, "Sir J. C. Bose's diode detector received Marconi's first transatlantic wireless signal of December 1901 (the "Italian navy coherer" scandal revisited)", *Proc. IEEE*, vol. 86, no. 1, pp. 259–285, 1998.

- [13] M. Riordan and L. Hoddeson, "The origins of the p-n junction", IEEE Spectrum, vol. 34, no. 6, p. 46, 1997.

- [14] J. Bardeen, "Solid state physics 1947", Solid State Technol., vol. 30, no. 12, pp. 69–71, 1987.

- [15] I. M. Ross, "The invention of the transistor", *Proc. IEEE*, vol. 86, no. 1, pp. 7–27, 1998.

- [16] M. Riordan, L. Hoddeson, and C. Herring, "The invention of the transistor", Rev. Mod. Phys., vol. 71, no. 2, pp. S336–S345, 1999.

- [17] T. S. Perry, "Not just blue sky", *IEEE Spectrum*, vol. 39, no. 6, pp. 33–37, 2002.

- [18] J. A. Armstrong, "Solid state technology and the computer: 40 years later small is still beautiful", *Solid State Technol.*, vol. 30, no. 12, pp. 81–83, 1987.

- [19] L. Esaki, "Discovery of the tunnel diode", IEEE Trans. Electron Dev., vol. 23, no. 7, pp. 644–647, 1976.

- [20] L. Berlin and H. Casey, Jr., "Robert Noyce and the tunnel diode", IEEE Spectrum, vol. 42, no. 5, pp. 49–53, 2005.

- [21] L. Esaki and R. Tsu, "Superlattice and negative conductivity in semiconductors", IBM Res. Note, RC-2418, March 1969.

- [22] L. Esaki and R. Tsu, "Superlattice and negative differential conductivity in semiconductors", *IBM J. Res. Develop.*, vol. 14, pp. 61–65, Jan. 1970.

- [23] M. M. Atalla, E. Tannenbaum, and E. J. Scheibner, "Stabilization of silicon surfaces by thermally grown oxides", *Bell. Syst. Tech. J.*, vol. 38, no. 3, pp. 749–783, 1959.

- [24] D. Kahng and M. M. Atalla, "Silicon-silicon dioxide field induced surface devices", in *Solid State Res. Conf.*, Pittsburgh, USA, 1960.

- [25] S. R. Hofstein and F. P. Heiman, "Silicon insulated-gate field-effect transistor", *Proc. IEEE*, vol. 51, no. 9, pp. 1190–1202, 1963.

- [26] F. M. Wanlass and C. T. Sah, "Nanowatt logic using field-effect metal-oxide semiconductor triodes", in *Proc. Techn. Dig. IEEE 1963*, *Int. Solid-State Circ. Conf.*, Philadelphia, USA, 1963, pp. 32–33.

- [27] W. S. Boyle and G. E. Smith, "The inception of charge-coupled devices", *IEEE Trans. Electron Dev.*, vol. 23, no. 7, pp. 661–663, 1976

- [28] R. E Kerwin, D. L. Klein, and J. C. Sarace, "Method for making MIS structures", US Patent 3 475 234, filed March 27, 1967, issued Oct. 28, 1969.

- [29] T. Mochizuki, K. Shibata, T. Inoue, K. Obuchi, and M. Kashiwogi, "A new gate material for MOS devices molybdenum silicide (MoSi<sub>2</sub>)", in *Proc. ECS Conf.*, Atlanta, USA, 1977, vol. 72–2, pp. 331–332.

- [30] K. C. Saraswat, F. Mohammedi, and J. D. Meindl, "WSi<sub>2</sub> gate MOS devices", in *Proc. IEDM Tech. Dig.*, Washington, USA, 1979, pp. 462–464.

1/2010

- [31] J. R. Brews, W. Fichtner, E. H. Nicollian, and S. N. Sze, "Generalized guide for MOSFET miniaturization", *IEEE Electron Dev. Lett.*, vol. 1, no. 1, pp. 2–4, 1980.

- [32] W. R. Hunter, T. C. Holloway, P. K. Chatterjee, and A. F. Tasch, "New edge-defined vertical-etch approaches for submicrometer MOSFET fabrication", in *Proc. IEDM Tech. Dig.*, Washington, USA, 1980, pp. 764–767.

- [33] S. S. Wong, D. R. Bradbury, D. C. Chen, and K. Y. Chiu, "Elevated source/drain MOSFET", in *Proc. IEDM Tech. Dig.*, San Francisco, USA, 1984, pp. 634–637.

- [34] T. Mochizuki and K. D. Wise, "An n-channel MOSFET with Schottky source and drain", *IEEE Electron Dev. Lett.*, vol. 5, no. 4, pp. 108–110, 1984.

- [35] H. Tian, R. B. Hulfachor, J. J. Ellis-Monaghan, K. W. Kim, M. A. Littlejohn, J. R. Hauser, and N. A. Masnari, "An evaluation of super-steep-retrograde channel doping for deep-submicron MOSFT applications", *IEEE Trans. Electron Dev.*, vol. 41, no. 10, pp. 1880–1882, 1994.

- [36] C.-T. Chuang, K. Bernstein, R. V. Joshi, R. Puri, K. Kim, E. J. Nowak, T. Ludwig, and I. Aller, "Focusing on planar device structures and strained silicon for handling silicon scaling issues in the deep sub-100 nm regime", *IEEE Circ. Dev. Mag.*, vol. 20, no. 1, pp. 6–19, 2004.

- [37] J.-P. Collinge, Silicon-on-Insulator Technology: Materials to VLSI. Boston/Dordrecht/London: Kluwer, 2004.

- [38] T. Skotnicki, J. A. Hutchby, T.-J. King, H.-S. P. Wong, and F. Boeuf, "The end of CMOS scaling", *IEEE Circ. Dev. Mag.*, vol. 21, no. 1, pp. 16–26, 2005.

- [39] J.-P. Colinge, "Multiple-gate SOI MOSFETs", Solid-State Electron., vol. 48, no. 6, pp. 897–905, 2004.

- [40] E. E. Loebner, "Subhistories of the light emitting diode", IEEE Trans. Electron Dev., vol. 23, no. 7, pp. 675–698, 1976.

- [41] N. Holonyak, "The semiconductor laser: a thirty-five year perspective", *Proc. IEEE*, vol. 85, no. 11, pp. 1678–1693, 1997.

- [42] Z. I. Alferov, "Autobiography", http://nobelprize.org/ nobel\_prizes/physics/laureates/2000/alferov-autobio.html

- [43] G. E. Moore, "Progress in digital integrated electronics", in *Proc. IEDM Tech. Dig.*, Washington, USA, 1975, p. 103.

- [44] Hardware components, Intel processor history, http://www.interfacebus.com/intel-processor-types-release-date.html

- [45] International Technology Roadmap for Semiconductors, 2008, http://www.itrs.net/Links/2008ITRS/home2008.htm

- [46] The singularity is near, http://singularity.com/charts

Lidia Łukasiak graduated from the Faculty of Electronics, Warsaw University of Technology, Poland, in 1988 and joined the Institute of Microelectronics and Optoelectronics the same year. She received the Ph.D. and D.Sc. degrees from the same university in 1994 and 2002, respectively. Since 2004 she has been the Vice-Director for

Teaching of the Institute of Microelectronics and Optoelectronics. Her research interests include modeling and characterization of semiconductor devices and microprocessor systems.

e-mail: lukasiak@imio.pw.edu.pl Institute of Microelectronics and Optoelectronics Warsaw University of Technology Koszykowa st 75 00-662 Warsaw, Poland

Andrzej Jakubowski received the M.Sc., Ph.D. and D.Sc. degrees in electrical engineering from the Warsaw University of Technology (WUT), Poland. In the years 1984–1990 and 1993–2001 the Head of the Division of Microelectronics of the Institute of Microelectronics and Optoelectronics (IMiO) and in the years 2001–2004 the Head

of the Division of Microelectronics and Nanoelectronics Devices of IMiO. He was the Director of the Institute of Electron Technology (ITE) in the years 1989–1992 and Director of IMiO from 2004 till 2008. Between 1990 and 1991 he was the Chairman of the Committee of Applied Research and a member of the Prime Minister's Committee of Science and Technical Progress. He was the Vicechairman of the Committee of Electronics and Telecommunications of Polish Academy of Sciences between 1989 and 2007. He was also the Chairman of the Microelectronics Section of this Committee from 1988 till 2003. He was the editor-in-chief of "Electron Technology" between 1990 and 1994. He is the author or co-author of more than 600 publications (journal and conference papers, monographs) and several textbooks for students, as well as popular-science papers. He delivered many invited lectures at foreign universities and international conferences in Europe, United States and Asia. He supervised 23 Ph.D. theses and more than 150 B.Sc., and M.Sc. theses. He received 5 Awards of the Minister of National Education. The main areas of his research are modeling, characterization and fabrication of semiconductor structures (e.g., MOS, SOI MOS, HBT, SiGe MOS).

e-mail: jakubowski@imio.pw.edu.pl Institute of Microelectronics and Optoelectronics Warsaw University of Technology Koszykowa st 75 00-662 Warsaw, Poland Invited paper

# **Charging Phenomena** at the Interface Between High-k Dielectrics and SiO<sub>x</sub> Interlayers

Olof Engström, Bahman Raeissi, Johan Piscator, Ivona Z. Mitrovic, Stephen Hall, Heinrich D. B. Gottlob, Mathias Schmidt, Paul K. Hurley, and Karim Cherkaoui

Abstract—The transition regions of GdSiO/SiO<sub>x</sub> and HfO<sub>2</sub>/ SiO<sub>r</sub> interfaces have been studied with the high-k layers deposited on silicon substrates. The existence of transition regions was verified by medium energy ion scattering (MEIS) data and transmission electron microscopy (TEM). From measurements of thermally stimulated current (TSC), electron states were found in the transition region of the HfO<sub>2</sub>/SiO<sub>x</sub> structures, exhibiting instability attributed to the flexible structural molecular network expected to surround the trap volumes. The investigations were focused especially on whether the trap states belong to an agglomeration consisting of a single charge polarity or of a dipole constellation. We found that flat-band voltage shifts of MOS structures, that reach constant values for increasing oxide thickness, cannot be taken as unique evidence for the existence of dipole layers.

Keywords—defects, dielectrics, high-k, metal oxide semiconductor.

#### 1. Introduction

The gate function of future metal oxide semiconductor (MOS) transistors has attracted a large scientific community to an expedition into the periodic system for tracking the Dielectric Grail. Wanted is a material with acceptable energy offset values,  $\Delta E$ , between the energy bands of the dielectric and the silicon crystal while, in addition, having a high enough dielectric constant, k. Yet, to fulfill the demands of low current leakage and high capacitive coupling between gate metal and transistor channel, the crucial property is the product  $k \times \Delta E$  of these two quantities [1]. So far, for CMOS applications most of the efforts have been limited to metal oxides. The change from the extremely well mastered thermal SiO<sub>2</sub> material, to an oxide based on metals among the transition or rare earth series, has disclosed obstacles that were unnoticeable for traditional technology. Beside the problems of chemical stability between these new "high-k" oxides and the silicon substrate, crystallization, sensitivity to humid environment, higher concentrations of oxide traps and interface states are properties, not uncommon among these materials. Driven by technology, this has given rise to needs for understanding their microscopic properties from chemical, physical and electrical point of view.

A common attribute of high-k oxide films deposited on silicon is the occurrence of an  $SiO_x$  interlayer between the high-k material and the silicon crystal. This evokes interface electron state properties similar to those at thermal SiO<sub>2</sub>/Si interfaces [2], [3]. Even if the interlayer lowers the effective k value of the film, it often gives better conditions for a transistor channel than those offered by a direct interface due to lower charge carrier scattering by the former. However, it must be paid for by an extra interface occurring between  $SiO_x$  and the high-k material [4]. As the total physical thickness of the film is in the range of 5 nm or smaller, on this length scale the transition from  $SiO_x$  to the high-k material can hardly be considered abrupt. It is found to include a transition region with undefined stoichiometry and thus with possible structural instabilities [5]-[11]. Recently, the occurrence of traps either singular or in dipole configurations have been noticed as the potential origin of charge sources decreasing the quality of presumptive gate insulators [11]-[16]. In the present paper, we will describe the physical and electrical properties of transition regions at GdSiO/SiO<sub>x</sub> and HfO<sub>2</sub>/SiO<sub>x</sub> interfaces and demonstrate how charge carrier traffic at such positions can be interpreted in order to characterize the trap properties. Based on this reasoning, the possible existence of a dipole layer in the transition region will be addressed.

#### 2. Properties of Transition Regions

The dominating defect causing charge carrier traps in the bulk of transition and rare-earth metal oxides is commonly considered to be the oxygen vacancy. It has similar properties as the E' center in SiO<sub>2</sub> and has been the object of a rich theoretical [15], [16] and experimental [10], [11] literature. In HfO<sub>2</sub> it has been predicted to be an amphoteric center with four [15] or five [16] charge states ranging from double donor to double acceptor behavior with the latter states positioned in the range 1-2 eV from the HfO<sub>2</sub> conduction band edge. Furthermore, the double acceptor level is argued to be connected with large lattice relaxation [16]. It has even been proposed that the double negatively charged energy level falls below the single negatively charged level, thus exhibiting negative-U property [17]. These trap properties will be further discussed below in relation to the results from electrical measurements.

As one example of the complex high-k oxide/SiO<sub>x</sub> interface, we will discuss data from GdSiO. This dielectric was

1/2010

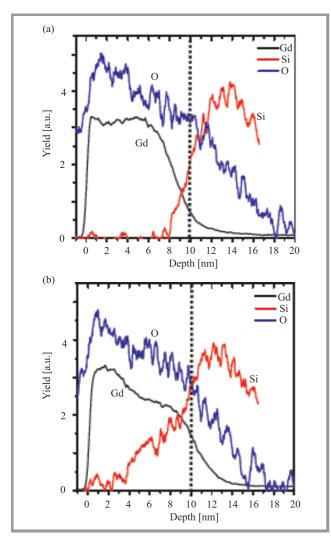

*Fig. 1.* MEIS data for samples with GdSiO evaporated on top of a 4 nm thermal oxide: (a) as deposited and (b) after RTA at  $900^{\circ}$ C for 1 s.

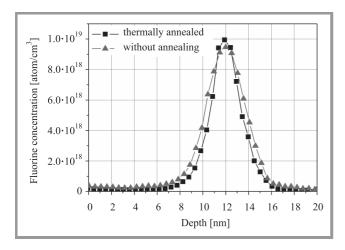

prepared by evaporating Gd<sub>2</sub>O<sub>3</sub> on a 4 nm thick thermal SiO<sub>2</sub> layer on silicon [18]–[21]. The double layer was partly transformed into GdSiO by rapid thermal anneal (RTA) for 1 s at 900°C. The depth distribution of elements before and after the thermal anneal is shown by medium energy ion scattering (MEIS) data in Fig. 1. A steeply decreasing silicon concentration from the silicon side into the oxide directly after deposition (Fig. 1(a)), reflects a complicated diffusion process taking place already at this stage. At the 10 nm mark, the concentration of oxygen is a factor of 2 higher than the concentration of silicon. This indicates a reminiscence of SiO<sub>2</sub> which quickly becomes a suboxide at larger distances from this interface, where a nearly stoichiometric Gd<sub>2</sub>O<sub>3</sub> takes over. The extremely high gradient of Si at the 10 nm point would be expected to stage structural instability. After the RTA at 900°C, silicon has penetrated the whole oxide layer (Fig. 1(b)) creating a GdSiO with varying concentration of Si. This structure has been demonstrated to fulfill the industrial target for low standby power, 22 nm double gate SOI transistors [18].

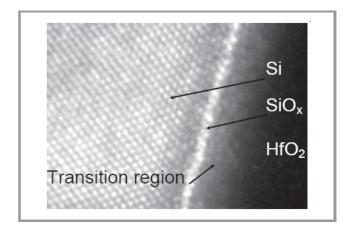

A second example is given by a transmission electron microscopy (TEM) picture showing the interface between  $HfO_2$  and  $SiO_x$  in Fig. 2. This sample was prepared by reactive sputtering of Hf and  $O_2$  followed by an anneal at  $800^{\circ}$ C for 10 min [12]. Between the white string showing the  $SiO_x$  layer and  $HfO_2$ , appearing as a black area,

*Fig.* 2. TEM graph from a cross section of  $Si/SiO_x/HfO_2$ , where the  $HfO_2$  layer was deposited by reactive sputtering.

a milky band is shown with a width of about 2 nm. Here, one may expect the same type of diffusion taking place as in the case of GdSiO above. As will be shown below, traps formed in this region consequently have an unusual electric behavior.

# 3. Charge Carrier Traffic at Transition Regions

#### 3.1. Energy Relations and Charge Exchange

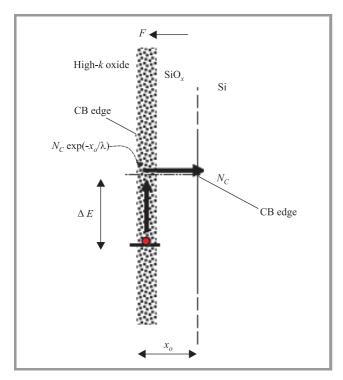

We consider an interface between a high-k oxide and an  $SiO_x$  interlayer on silicon as schematically shown in Fig. 3. The transition region is marked by a wide patterned band and includes a trap level at an energy distance  $\Delta E$  below the silicon conduction band edge. A negative net charge is present in the interlayer, such that an electric field F is directed from the silicon crystal towards the high-k oxide. Assuming that the thickness of the interlayer is about 1 nm, tunneling through this layer is non-negligible and can be described as assisted by a decay of the effective density of states,  $N_C$ , from the silicon conduction band determined by  $N_C \exp[-x_0/\lambda]$ , where  $x_0$  is the distance from the SiO<sub>x</sub>/Si interface to the trap and  $\lambda$  is a damping factor. A captured electron can be transferred into the Si bulk by a two step process, starting with a thermally driven mechanism to the tunneling states at the energy level of the silicon conduction band edge. As long as the electric field is high enough, this process is followed by tunneling into the silicon conduction band as depicted in Fig. 3. Emitting electrons from the trap position will lower the electric field. The system

Fig. 3. Two step emission path of electrons captured in traps positioned in the transition region. The first step is thermal, to decaying states from the silicon conduction band followed by tunneling to the silicon.

may, therefore, reach a situation where the electric field becomes too low for the second transfer step to occur, which means that the emission process stops. As the tunneling probability is very sensitive to the magnitude of the electric field, this termination may be very abrupt as we will see in the experimental data following.

As long as the tunneling rate dominates, the bottleneck of this process is the thermal electron emission rate,  $e_n$ , from the trap to an effective density of states decreased by the tunneling probability

$$e_n = \sigma_n v_{th} N_C \exp\left(-\frac{x_0}{\lambda}\right) \exp\left(-\frac{\Delta E}{k_B T}\right),$$

(1)

where  $\sigma_n$  is the capture cross section representing a local transition from the tunneling state to the trap state,  $v_{th}$  is the average thermal velocity of electrons in the silicon conduction band,  $k_B$  is Boltzmann's constant and T is absolute temperature. As will be described in detail below, using thermally stimulated current (TSC) technique to determine the emission rate, the temperature is linearly increased with time during the measurement cycle. As the electric field, F, decreases due to the decrease of negative charge in the  $SiO_x$ layer, the energy distance  $\Delta E$  will increase. In addition, the temperature increase will move the Fermi level in the silicon bulk to deeper energy in the band gap. For a given applied voltage across the structure, this will lower the position of the silicon conduction band edge at the SiO<sub>x</sub>/Si interface which will increase the voltage drop across the interlayer and tend to decrease  $\Delta E$ . Assuming, as a first order approximation, that both these processes are linear with temperature, we write

$$\Delta E = \Delta E_0 - \alpha T \,, \tag{2}$$

where  $\Delta E_0$  is the energy distance between the silicon conduction band edge and the trap level extrapolated to  $T=0~{\rm K}$  and  $\alpha$  is a constant determined by the two competing processes described above. Using Eq. (2) in (1), we get

$$e_n = \sigma_e v_{th} N_C \exp\left(-\frac{\Delta E_0}{k_B T}\right),$$

(3)

where

$$\sigma_e = \sigma_n \exp\left(\frac{\alpha}{k_B}\right) \exp\left(-\frac{x_0}{\lambda}\right)$$

(4)

can be considered as an effective capture cross section, influenced by the changing energy level position and the tunneling probability. We notice that, measuring the emission rate as a function of temperature and plotting this quantity in an Arrhenius graph would give an activation energy corresponding to an extrapolation of  $\Delta E$  to T=0 K under the assumption of linear conditions. However, this reasoning does not take into account the properties related to local molecular dynamics of the trap volume.

For a case like the oxygen vacancy, where the transition is argued to be connected with a strong lattice relaxation [16], the emission process would be influenced also by the vibronic properties of the trap [21] and characterized by "hysteretic tunneling", adding a simultaneous trap relaxation and tunneling into the picture [22]. This would lead to two additional pre-exponential factors in the expressions for the thermal emission rate one originating from a possible thermally activated  $\sigma_n$ :

$$\sigma_n = \sigma_0 \exp\left(-\frac{\Delta U}{k_B T}\right),$$

(5)

where  $\sigma_0$  depends on a combination of matrix elements including electronic and atomic wave functions involved in the process while  $\Delta U$  is an activation energy originating from the vibrational properties of the trap system [21], [23]. The second effect comes from the entropy factor [21], [23], [24]:

$$X_n = \exp\left(\frac{\Delta S}{k_B}\right),\tag{6}$$

where  $\Delta S$  is the change in entropy due to the change in vibrational frequency of the ionic part of the trap when the electron is released. Hence, combining the effects of the change in  $\Delta E$  due to de-charging and those of a vibrating electron-ion trap system, we find from Eqs. (1)–(6):

$$e_n = \sigma_0 \exp\left(-\frac{\Delta U}{k_B T}\right) \exp\left(\frac{\Delta S}{k_B}\right) \exp\left(\frac{\alpha}{k_B}\right) \times \exp\left(-\frac{x_0}{\lambda}\right) v_{th} N_C \exp\left(-\frac{\Delta H_0}{k_B T}\right), \tag{7}$$

where the activation energy now is represented by an enthalpy,  $\Delta H_0 = \Delta E_0 + \Delta ST$ , including the heat,  $\Delta ST$ , stored by the local vibrational modes [21], [23], [24].

For this case the first factors in Eq. (7) make up an "effective" capture cross section,  $\sigma_e$ , which would be obtained from an Arrhenius plot of the thermal emission rate,  $e_n$ :

$$\sigma_e = \sigma_0 \exp\left(-\frac{\Delta U}{k_B T}\right) \exp\left(\frac{\Delta S}{k_B}\right) \exp\left(\frac{\alpha}{k_B}\right) \exp\left(-\frac{x_0}{\lambda}\right). \quad (8)$$

As will be shown below, TSC results demonstrate instabilities among the traps investigated in the  $HfO_2/SiO_x$  transition region. This is most probably originating from restructuring of the molecular arrangement around the trap volume, thus changing the matrix elements for charge carrier transition involved in  $\sigma_0$  as well as quantities of the vibrational properties reflected by  $\Delta U$ ,  $\Delta S$ , and  $\Delta H_0$  in Eqs. (7) and (8).

#### 3.2. Thermally Stimulated Current

When measuring TSC from traps in a MOS system [12], the sample is first brought into accumulation at room temperature followed by a temperature decrease to about 50 K. During this procedure, traps at the interface and in the oxide are filled by charge carriers. At the low temperature point, the system is biased into deep depletion and a temperature increase, linear as a function of time, is applied. For an n-type semiconductor this gate bias is negative. As long as the temperature is lower than about 200 K and the total scanning time up to that temperature is shorter than

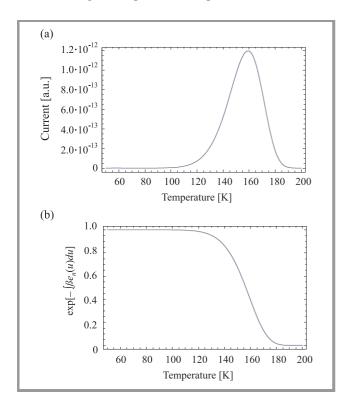

*Fig. 4.* (a) Theoretical plot of thermally stimulated current for an activation energy of 0.13 eV, an effective capture cross section of  $10^{-24}$  cm<sup>2</sup> and a temperature scan rate of 20 K/minute. (b) The integral factor in Eq. (9) as a function of temperature. This function is close to 1 for the initial part of the curve in (a).

about 10 min, it should be noticed that, due to the low temperature, an extremely low concentration of holes is expected in the valence band of the silicon crystal. Therefore, all de-charging processes observed as a TSC can be expected to originate from electron exchange at the insulator/silicon interface. The current created by emitted electrons is expressed by [12]

$$i(T) = \frac{C_{ox}}{C_S + C_{ox}} q N_T e_n \exp\left[-\int_{T_0}^{T_1} \beta e_n(u) dU\right], \quad (9)$$

where  $C_{ox}$  and  $C_s$  are the capacitances of the oxide and the depleted semiconductor, respectively,  $N_T$  is the surface concentration of captured carriers and  $\beta$  is the scanning rate of the temperature, linear in time, t, such that  $T = \beta t$ . The function given by Eq. (9) is plotted in Fig. 4(a) for an activation energy of 0.13 eV and an effective capture cross section of  $10^{-24}~\rm cm^2$ . Using the rather complicated expression in Eq. (8) for parameter extraction from experimental data is not practical. However, calculating the integral factor in this equation as a function of temperature, for the same input data as used above, one finds the graph shown in Fig. 4(b). It is noticed that the integral takes a value close to 1 for the initial part of the TSC curve in Fig. 4(a). Furthermore, as  $C_{ox} \gg C_s$  for the deep depletion conditions used in the experiment, this part of the experimental data is proportional to the thermal emission rate  $e_n$ . Estimating the total concentration,  $N_T$ , of trap levels from the area under the TSC peak, therefore, gives a possibility to find effective capture cross sections from Arrhenius plots of  $e_n$  [12].

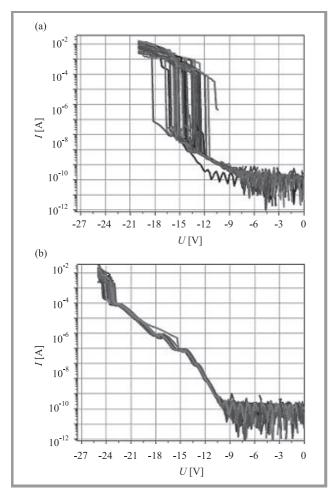

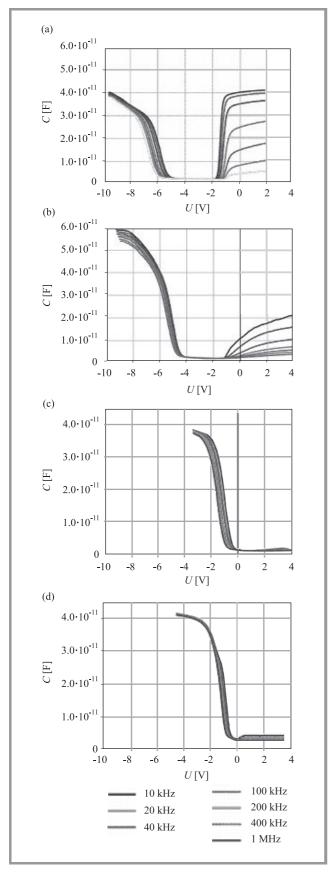

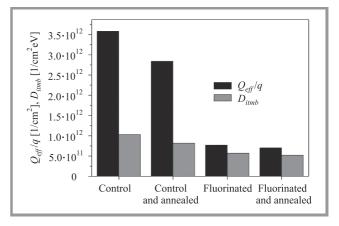

#### 3.3. Experimental TSC Results on the $HfO_2/SiO_x$ Interface

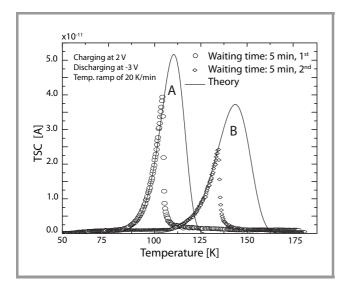

Figure 5 shows experimental TSC data from electron emission at the transition region of an MOS capacitor with an Al/HfO<sub>2</sub>/SiO<sub>x</sub>/Si structure like the one shown by TEM in Fig. 2. Two important features can be observed in Fig. 5:

- repeated measurement gives a different TSC peak position on the temperature scale;

- 2) the TSC curves are terminated before they reach the maximum point of the theoretical curves (solid curves) fitted to the experimental data.

These results are typical and occur for a large majority of the present samples with HfO<sub>2</sub> prepared by reactive sputtering as well as for samples prepared by atomic layer deposition (ALD) [25]. The observation (1), reveals an instability of the traps as mentioned above in relation to Eq. (9). Such instability after voltage stress under similar conditions as in the present experiment, was observed also by Bersuker *et al.* in [10]. The observation (2), can be interpreted as a result of the tunneling process involved in the electron emission. During the emission process, the negative charge in the transition region, born by the captured

*Fig. 5.* Experimental TSC data (points) for MOS structures with HfO<sub>2</sub> prepared by reactive sputtering compared with theoretical calculations (solid curves) calculated from Eq. (9). Repeated measurement gave rise to a shift of the TSC peak along the temperature axis, reflecting structural changes of the emitting electron traps. The activation energy for the curves A and B is 0.13 eV and 0.16 eV, respectively, and the corresponding capture cross sections are  $6 \cdot 10^{-22}$  cm<sup>2</sup> and  $9 \cdot 10^{-21}$  cm<sup>2</sup>, respectively.

electrons, will decrease. This will decrease the electric field driving the tunneling until the field strength is too weak for continued emission. As the tunneling probability is very sensitive to a change in electric field, the TSC will get an abrupt termination as shown for the two curves in Fig. 5.

#### 4. Single Charge Versus Dipole Charge

The recent increasing interest in the properties of high-k/ SiO<sub>x</sub> transition layers includes novel ideas about a possible occurrence of closely separated charge planes with different polarities within this region [13]. It has been described as dipole planes occurring as a result of oxygen transfer across the interface between the high-k and the  $SiO_x$  material [14]. According to an idea proposed in [14], such transition would take place from the material with the highest surface density of oxygen atoms to that with lower density. For transition metal oxides, like HfO2, this would imply that oxygen is transferred from this material into  $SiO_x$ , creating interstitials and leaving oxygen vacancies behind. As the relation between oxygen surface densities of rare-earth metal oxides, like  $Gd_2O_3$  and  $SiO_x$  is the opposite, such transfer would instead go from the  $SiO_x$  to the high-k side.

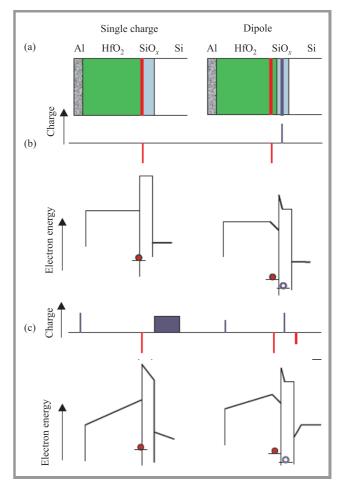

The influence of a single negative charge and a dipole surface on the conduction band relations for the metal/ HfO<sub>2</sub>/SiO<sub>x</sub>/n-type Si structure is depicted in Fig. 6. The geometries are shown in Fig. 6(a), while Fig. 6(b) and Fig. 6(c) show the charge relations and the conduction band relations for an open circuit case and a short circuit case, respectively. In order to demonstrate the specific influences of these charge planes, we assume that no other charges

are present in the structure. Considering first the single charge case in the left column of Fig. 6 for an open circuit case in Fig. 6(b), where the opposite positive charge is assumed to exist at a long distance, the electron energy of the whole structure is lifted in parallel in relation to an earth plane. Short circuiting, as shown in Fig. 6(c), will cause positive charge to appear at the metal gate and in the depletion region occurring in the n-type semiconductor. Compared with an ideal structure without charge, an increased positive voltage,  $V_{FB}$ , on the gate would be needed to obtain flat-band condition for this case. Furthermore,  $V_{FB}$  would increase linearly with increasing thickness of the HfO<sub>2</sub> layer.

*Fig. 6.* Illustration of (a) charge configuration, and conduction band relations for (b) open circuit and (c) short circuit conditions of a metal/high-k/SiO<sub>x</sub>/Si structure. The columns demonstrate the conditions for a single charge plane (left) and a dipole plane (right), respectively.

For a dipole layer at the  $HfO_2/SiO_x$  interface, as shown in the right column of Fig. 6, under open-circuit conditions, one would expect an electric field between the two charge planes only (Fig. 6(b)). This would create a potential drop in that domain, while constant potentials would occur outside the two planes separated by a voltage created inside the dipole. Short-circuiting this structure gives rise to a positive charge on the gate and a negative charge in

1/2010

the semiconductor, forcing the latter into accumulation condition. These two charges are exactly equal and vary depending on the  $HfO_2$  thickness in such a way that the sum of the energy drops in  $HfO_2$  and in the semiconductor is constant and equal to  $qV_{FB}$ . In this case a negative  $V_{FB}$ , equal to the potential drop inside the dipole, is needed to obtain flat-band conditions. However, contrary to the situation with a single negative charge, the dipole combination would give a  $V_{FB}$  which is independent of the thickness of  $HfO_2$ . Such a behavior was indicated in [14] for  $HfO_x/Si_x$  interfaces.

The single charge case demonstrated by Fig. 6(a) offers a model for straightforward explanation of the anomalous TSC data as discussed in Section 3. The dipole case in Fig. 6(b) likewise gives rise to an energy relation of the conduction bands supporting electron injection into the silicon and thus a TSC with similar behavior as that from a single negative charge plane. Therefore, TSC does not give direct information on which of these two charge constellations is the source of current.

#### 5. Discussion

In order to explain the saturating flat-band voltage and its positive sign as observed in [12] when increasing the thickness of HfO<sub>2</sub>, the idea put forward in [13] requires injection of negatively charged traps from the high-k side into SiO<sub>r</sub>. This would give rise to a dipole directed in the opposite way to that discussed in relation to Fig. 6. Such a model is not completely unproblematic. First, injecting an oxygen ion from the HfO2 into the SiOx layer might be expected to give rise to an interstitial, leaving behind a vacancy in the HfO<sub>2</sub>. According to recent theoretical results [15], [16], vacancies are amphoteric and act as acceptors with energy levels at about 1.5 eV from the HfO<sub>2</sub> conduction band. They may therefore tend to be filled by electrons from the silicon conduction band and thus become negatively charged. On the other hand, the donor levels connected with oxygen vacancies are expected close to the middle of the bandgap of HfO2 and are most probably occupied by electrons and neutral at voltages of the flat-band values at about 0.5 V in [13]. The origin of positive charge required on the HfO2 side, therefore, is

A second problem with a dipole model may be the quantity of charge needed to obtain  $V_{FB}$  shifts in the range of 0.3-0.5 V as observed in [13]. As the thickness of the  $SiO_x$  layer normally is about 1 nm, the maximum value for the distance between the two charge sheets of an assumed dipole would be about that value. In order to achieve a shift of 0.3 V, this requires a charge density of more than  $5 \cdot 10^{15} q$  As cm<sup>-2</sup>. It can be compared with the charge contained in the TSC curves of Fig. 5, which is in the range of  $10^{13} q$  As cm<sup>-2</sup>. Finally, the strongest argument for a dipole model might be the saturating flat-band voltage. However, this result does not uniquely lead to a dipole configuration as shown in the following. Taking into account the continuous character of the transition region, a satu-

rating  $V_{FB}$  may result also from single charge condition. Contrary to the assumption made in [13], the transition from  $HfO_2$  to  $SiO_x$  cannot be considered abrupt on length scales in the range of a few nm. As noticed in Fig. 1, the oxygen concentration increases with distance from the silicon side due to diffusion into the silicon crystal. Similar behavior of oxygen concentration has been observed by elastic recoil detection analysis (ERDA) studies on HfPrO samples [26]. Therefore, it is reasonable to assume that the concentration of oxygen vacancies decreases with distance from the silicon side. Furthermore, assuming that thinner  $HfO_2$  layers, due to the out-diffusion of oxygen to the surface, also as observed in Fig. 1, have a lower decay of vacancies, it is probable that they have a smaller decay in concentration.

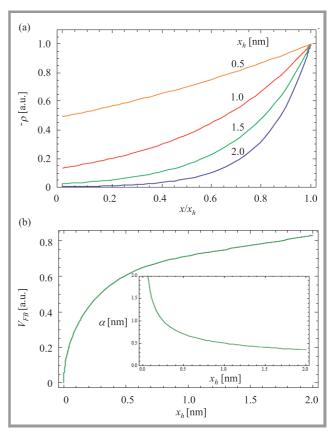

*Fig.* 7. (a) Assumed depth distribution of acceptor state volume concentrations in the transition region for  $HfO_2$  with thicknesses of 0.5, 1.0, 1.5 and 2.0 nm. The point x = 0 is at the  $HfO_2$  surface, while  $x = x_h$  is at a reference point where  $SiO_2$  transfers to suboxides. (b) The flat-band voltage as a function of  $HfO_2$  thickness for acceptor concentrations as shown in (a) with the decay constant, α, varying as a function of  $x_h$  as shown in the inset of (b).

A theoretical example is shown in Fig. 7(a), where the concentration of traps is plotted for different thicknesses as a function of normalized distance from a defined reference point in the transition region. Such a point could be the one, where  $SiO_2$  transfers to suboxides. For simplicity, the curves in Fig. 7(a) are exponential functions with decay factors,  $\alpha$ , decreasing with the thickness  $x_h$  of  $HfO_2$ , as

shown in the inset of Fig. 7(b). Solving Poisson's equation for the functions in Fig. 7(a):

$$\frac{d^2V}{dx^2} = -\frac{\rho_0}{k\varepsilon_0} \exp\left(-\frac{x_h - x}{\alpha}\right),\tag{10}$$

where V is electrical potential,  $\rho_0$  is the volume charge density at the reference point,  $x_h$ ,  $\varepsilon_0$  is the dielectric permittivity of vacuum and x is distance from the HfO<sub>2</sub> surface, we find  $V_{FB}$  from the potential at x=0 as

$$\frac{k\varepsilon_0}{\rho_0}V_{FB} = -\alpha \left\{ x_h + \alpha \left[ 1 - \exp\left(-\frac{x_h}{\alpha}\right) \right] \right\}. \tag{11}$$

The  $V_{FB}$  normalized by the pre-factor in Eq. (11) is plotted in Fig. 7(b) as a function of HfO<sub>2</sub> thickness,  $x_h$ . The shape of this curve, with a tendency to saturate for increasing,  $x_h$ , was interpreted in [12] as a result of a dipole layer. Figure 7(b) demonstrates that under assumptions based on MEIS data, it is possible to obtain similar behavior from a singly charged layer.

#### 6. Conclusions

The theoretical TSC curves shown in Fig. 5 were calculated assuming an ensemble of electron states with one common discrete energy level. The agreement between the initial curvature of these graphs and the experimental data indicates that the majority of traps observed by TSC have similar properties of their charge carrier statistics and are positioned with limited spread in distance from the silicon/SiO $_x$  interface. This excludes bulk traps in the HfO<sub>2</sub> as candidates and suggests a trap distribution concentrated at the HfO<sub>2</sub>/SiO<sub>x</sub> interface as depicted in Fig. 7(a) for delivering electrons to the TSC. Also, TSC peaks from states at the Si/SiOx interface are ruled out by earlier experiments as they have been demonstrated to occur at temperatures above 200 K, outside the scale of Fig. 5 [12]. The extremely low values of capture cross sections in the range  $10^{-26} - 10^{-19}$  cm<sup>-2</sup>, normally found by TSC for this kind of experiments [11], [27], are explained by the tunneling process needed for carrier injection into the silicon substrate and the thermally activated process expected for carrier capture into oxygen vacancies [16]. Also, taking into account the flexible structural network anticipated in the transition region, the shift of the TSC peaks as shown in Fig. 5 may be assigned to the restructuring of oxygen vacancy defects as discussed in Section 2.

The argument in [13], for the existence of a dipole plane at the interface between  $HfO_2$  and  $SiO_2$  layers, was based on the observation of flat-band voltage as a function of the thickness of  $HfO_2$ . It was shown that  $V_{FB}$  saturated to a near constant value when this thickness increases as expected for a dipole charge and discussed above in connection with Fig. 6. However, such a result is not unique for a dipole. By assuming an oxygen vacancy distribution in the high-k layer as estimated from MEIS data, we have demonstrated in the present work that similar  $V_{FB}$  dependence may be the result of a single charge distribution. We conclude, therefore, that more evidence is necessary before

the existence of a dipole layer occurring in high- $k/SiO_x$  transition regions is confirmed.

#### Acknowledgment

The authors collaborate under the banner of the "High-*k*-Gang" (http://www.high-k-gang.eu/). The work has benefited from funding provided by the European Network of Excellence NANOSIL within FP7 (ICT-216171).

#### References

- [1] O. Engström, B. Raeissi, S. Hall, O. Buiu, M. C. Lemme, H. D. B. Gottlob, P. K. Hurley, and K. Cherkaoui, "Navigation aids in the search for future high-k dielectrics: physical and electrical trends", *Solid-State Electron.*, vol. 51, iss. 4, pp. 622–626, 2007.

- [2] B. Raeissi, J. Piscator, O. Engström, S. Hall, O. Buiu, M. C. Lemme, H. D. B. Gottlob, P. K. Hurley, K. Cherkaoui, and H. J. Osten, "High-k-oxide/silicon interfaces characterized by capacitance frequency spectroscopy", *Solid-State Electron.*, vol. 52, iss. 9, pp. 1274–1279, 2008.

- [3] P. K. Hurley, K. Cherkaoui, E. O'Connor, M. C. Lemme, H. D. B. Gottlob, M. Schmidt, S. Hall, Y. Lu, O. Buiu, B. Raeissi, J. Piscator, O. Engström, and S. B. Newcomb, "Interface defects in HfO<sub>2</sub>, LaSiO<sub>x</sub> and Gd<sub>2</sub>O<sub>3</sub> high-k-metal-gate structures on silicon", J. Electrochem. Soc., vol. 155, no. 2, pp. G13–G20, 2008.

- [4] M. A. Quevedo-Lopez, P. D. Kirsch, S. Krishnan, H. N. Alshareef, J. Barnett, H. R. Harris, A. Neugroschel, F. S. Aguirre-Tostado, B. E. Gnade, M. J. Kim, R. M. Wallace, and B. H. Lee, "Systematic gate stack optimization to maximize mobility with HfSiON EOT scaling", in *Proc. ESSDERC 2006 Conf.*, Montreux, Switzerland, 2006, pp. 113–116.

- [5] G. Lucovsky, Y. Wu, H. Niimi, V. Misra, and J. C. Phillips, "Bonding constraints and defect formation at interfaces between crystalline silicon and advanced single layer composite gate dielectrics", *Appl. Phys. Lett.*, vol. 74, no. 14, pp. 2005–2007, 1999.

- [6] G. Lucovsky, J. P. Maria, and J. C. Phillips, "Interfacial strain induced self-organization in semiconductor dielectric gate stacks. II. Strain relief at internal dielectric interfaces between SiO<sub>2</sub> and alternative dielectrics", J. Vac. Sci. Technol. B, vol. 22, iss. 4, pp. 2097–2104, 2004.

- [7] G. Lucovsky and J. C. Phillips, "Defects and defect relaxation at internal interfaces between high-k transition metal and rare earth dielectrics and interfacial native oxides in metal oxide semiconductor (MOS) structures", *Thin Solid Films*, vol. 486, iss. 1–2, pp. 200–204, 2005.

- [8] F. Giustino, A. Bongiorna, and A. Pasquarello, "Equivalent thickness of thin oxide interlayer in gate insulator stacks on silicon", *Appl. Phys. Lett.*, vol. 86, iss. 19, pp. 192901-1--3, 2005.

- [9] P. Broqvist and A. Pasquarello, "Band gaps and dielectric constants of amorphous hafnium silicates: a first principle calculation", *Appl. Phys. Lett.*, vol. 90, iss. 8, pp. 082907-1--3, 2007.

- [10] G. Bersuker, C. S. Park, J. Barnett, P. S. Lysaght, P. D. Kirsch, C. D. Young, R. Choi, B. H. Lee, B. Foran, K. van Benthem, S. J. Pennycook, P. M. Lenahan, and J. T. Ryan, "The effect of interfacial layer properties on the performance of Hf-based gate stack devices", J. Appl. Phys., vol. 100, p. 094108, 2006.

- [11] J. T. Ryan, P. M. Lenahan, G. Bersuker, and P. Lysaght, "Electron spin resonance observations of oxygen deficient silicon atoms in the interfacial layer of hafnium oxide based metal-oxide-silicon structures", Appl. Phys. Lett., vol. 90, p. 173513, 2007.

- [12] B. Raeissi, Y. Y. Chen, J. Piscator, Z. H. Lai, and O. Engström, "Electron traps at HfO<sub>2</sub>/SiO<sub>x</sub> interfaces", in *Proc. ESSDERC 2008 Conf.*, Edinburgh, Scotland, 2008, pp. 130–133.

- [13] K. Iwamoto, Y. Kamimuta, A. Ogawa, Y. Watanabe, S. Migita, W. Mizubayashi, Y. Morita, M. Takahashi, H. Ota, T. Nabatame, and A. Toriumi, "Experimental evidence for the flatband voltage shift of high-k metal-oxide-semiconductor devices due to the dipole formation at the high-k/SiO<sub>2</sub> interface", Appl. Phys. Lett., vol. 92, iss. 13, pp. 132907-1--3, 2008.

- [14] K. Kita and A. Toriumi, "Origin of electric dipoles formed at highk/SiO<sub>2</sub> interface", Appl. Phys. Lett., vol. 94, iss. 13, pp. 132902-1--3, 2009.

- [15] K. Xiong, J. Robertson, M. C. Gibson, and S. J. Clark, "Defect energy levels in HfO<sub>2</sub> high-dielectric constant gate oxide", *Appl. Phys. Lett.*, vol. 87, iss. 18, pp. 183505-1--3, 2005.

- [16] J. L. Gavartin, D. Muñoz Ramo, A. L. Shluger, G. Bersuker, and B. H. Lee, "Negative oxygen vacancies in HfO<sub>2</sub> as charge traps in high-k stacks", *Appl. Phys. Lett.*, vol. 89, iss. 8, pp. 082908-1--3, 2006.

- [17] Y. P. Feng, A. T. Lim, and M. F. Li, "Negative-U property of oxygen vacancy in cubic HfO<sub>2</sub>", *Appl. Phys. Lett.*, vol. 87, iss. 6, pp. 062105-1--3, 2005.

- [18] H. D. B. Gottlob, M. Schmidt, A. Stefani, M. C. Lemme, H. Kurz, I. Z. Mitrovic, W. M. Davey, S. Hall, M. Werner, P. R. Chalker, K. Cherkaoui, P. K. Hurley, J. Piscator, O. Engström, and S. B. Newcomb, "Scaling potential and MOSFET integration of thermally stable Gd silicate dielectrics", *Microelectron. Eng.*, vol. 86, iss. 7–9, pp. 1642–1645, 2009.

- [19] H. D. B. Gottlob, A. Stefani, M. Schmidt, M. C. Lemme, H. Kurz, I. Z. Mitrovic, M. Werner, W. M. Davey, S. Hall, P. R. Chalker, K. Cherkaoui, P. K. Hurley, J. Piscator, O. Engström, and S. B. Newcomb, "Gd silicate: a high-k dielectric compatible with high temperature annealing", J. Vac. Sci. Technol. B, vol. 27, iss. 1, pp. 249–252, 2009.

- [20] I. Z. Mitrovic and S. Hall, "Rare earth silicate formation a route towards high-k for the 22 nm node and beyond", J. Telecommun. Inform. Technol., no. 4, pp. 51–60, 2009.

- [21] O. Engström and A. Alm, "Energy concepts of insulator-semiconductor interface traps", *J. Appl. Phys.*, vol. 54, no. 9, pp. 5240–5244, 1983.

- [22] W. B. Fowler, J. K. Rudra, M. E. Zvanut, and F. J. Fiegl, "Hysteresis and Franck-Condon relaxation in insulator-semiconductor tunnelling", *Phys. Rev. B*, vol. 41, no. 12, pp. 8313–8317, 1990.

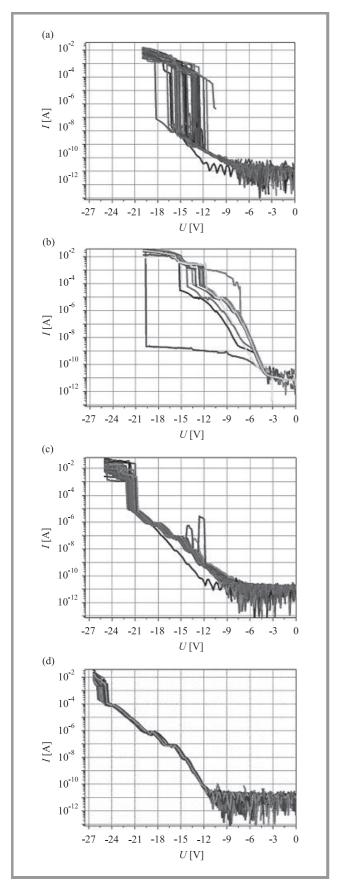

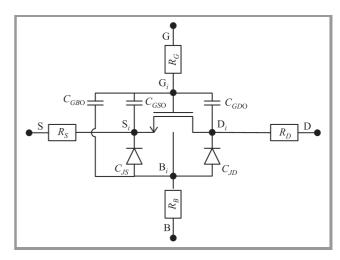

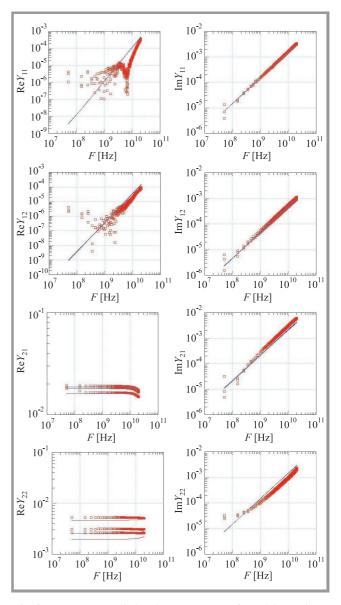

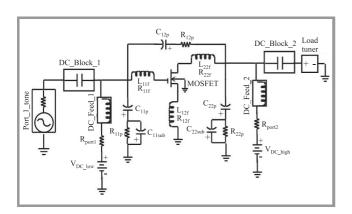

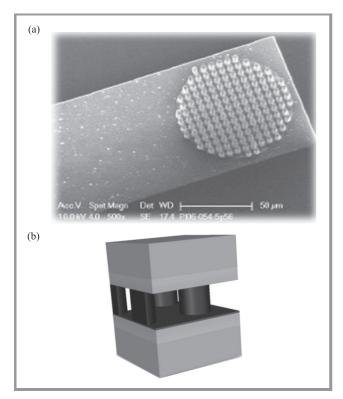

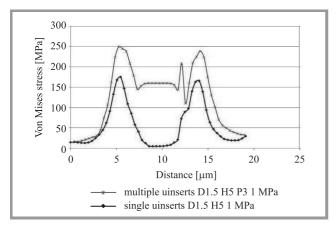

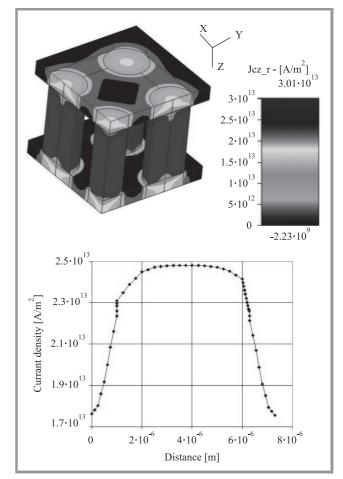

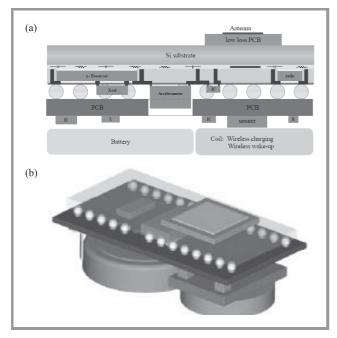

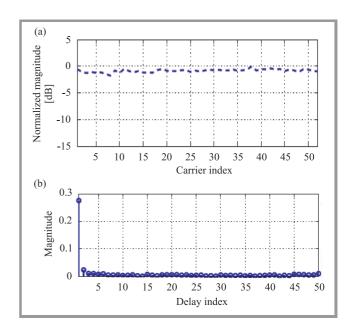

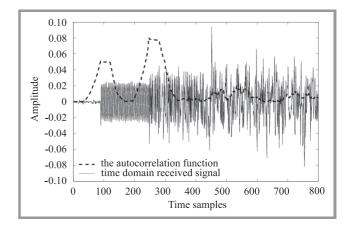

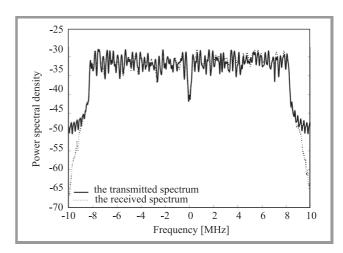

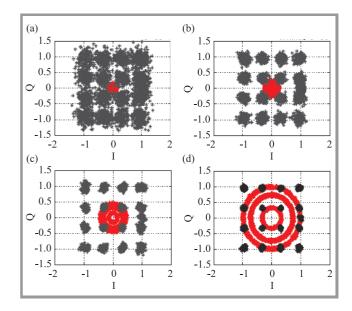

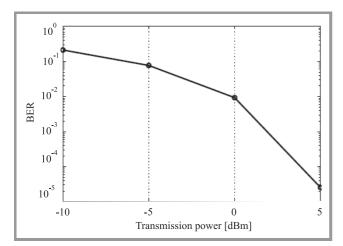

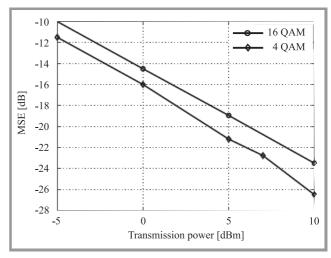

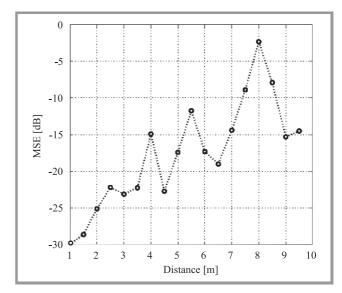

- [23] O. Engström and H. G. Grimmeiss, "Vibronic states of silicon dioxide interface traps", Semicond. Sci. Technol., vol. 4, no. 12, pp. 1106–1115, 1989.