## <sup>Paper</sup> LPT and SLPT Measurement Methods of Flat-Band Voltage (V<sub>FB</sub>) in MOS Devices

Krzysztof Piskorski and Henryk M. Przewłocki

Abstract— The photoelectric techniques are often used for the measurements of metal oxide semiconductor (MOS) structure parameters. These methods, which consist in illuminating the MOS structure with a semitransparent metal gate by a UV light beam, are often competitive for typical electric measurements. The results obtained by different photoelectric methods are, in many cases, more accurate and reproducible than the results of other measurements. The flat-band voltage  $V_{FB}$ is an important parameter of any MOS structure since its value influences the threshold voltage  $V_T$ , which decides for example about power consumption of MOS transistors. One of the methods to measure the  $V_{FB}$  value is the electric method of C(V) characteristic. This method involves certain calculations and requires the knowledge about parameters of the investigated sample. The accuracy of this method is rarely better than  $\pm 100$  mV (for higher doping of the substrates the accuracy is worse). The other method of  $V_{FB}$  value determination, outlined in this article, is the photoelectric light pulse technique (LPT) method. This method based on the idea proposed by Yun is currently being optimized and verified experimentally.

Keywords— flat-band voltage, light pulse technique, MOS system, photoelectric methods, scanned light pulse technique.

### 1. Introduction

The light pulse technique (LPT) and the scanning light pulse technique (SLPT) are photoelectric methods used to determine electrical parameters of metal oxide semiconductor (MOS) structures. In this article, determination of the flat-band voltage  $V_{FB}$  of MOS structures using these two methods will be discussed. The LPT method may be used to determine the  $V_{FB}$  value of the entire MOS device, while the SLPT method allows determination of the distribution of local  $V_{FB}$  values over the gate area. In the latter case this is done by scanning the gate area with a light beam of small diameter (small in comparison with gate dimensions).

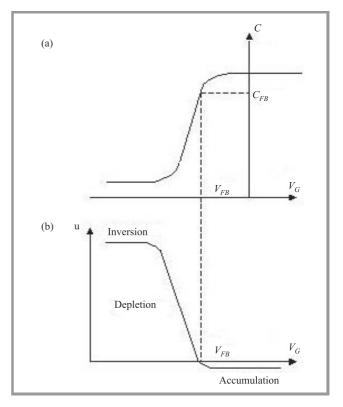

At present, the best results of LPT and SLPT measurements are experimentally obtained making use of a digital lockin amplifier. The DC signal u at the output of the lock-in amplifier is a function of the potential  $V_G$  applied to the gate of the MOS device under investigation. This is illustrated in Fig. 1(b), where the dependence of the signal u on the gate voltage  $V_G$  is shown. In Fig. 1(a) the capacitancevoltage  $C(V_G)$  curve of the same structure is shown for comparison. As will be shown later, the gate voltage  $V_G$  at which u changes sign is the flat-band voltage of the MOS structure under investigation. Hence, by adjusting gate voltage  $V_G$  to obtain u = 0 the  $V_{FB}$  value can be determined. The main difficulty in practical application of the LPT and SLPT measurement methods results from the fact that the signal |u| in the accumulation range is in most of the cases several orders of magnitude smaller than in inversion and depletion (as schematically shown in Fig. 1). Hence, very high sensitivity of the measurement setup is required to correctly determine the  $V_G$  value corresponding to u = 0.

Fig. 1. (a) The  $C(V_G)$  curve of a MOS device and (b) the  $u = f(V_G)$  characteristic of the same device. The  $V_G$  value at which *u* changes sign is the flat-band voltage  $V_{FB}$ .

The idea of using the LPT method to determine the flatband voltage  $V_{FB}$  was first proposed by Yun [1]. Using the oscilloscope, he observed the dependence of the current pulses resulting from light pulses illuminating the MOS device under investigation on the gate voltage  $V_G$ . He correctly concluded, that by changing the gate bias  $V_G$  from inversion and depletion towards accumulation of the MOS structure, one observes diminishing current pulses that disappear at  $V_G = V_{FB}$ . Incorrectly, however, he stated that at  $V_G$  values corresponding to accumulation, the MOS structure does not respond with any electrical signal to the excitation by the light pulses.

A more rigorous and comprehensive treatment of the problems related with the LPT method of  $V_{FB}$  determination was given by Jakubowski and Krawczyk [2], [3]. These authors proved, both theoretically and experimentally, that the electrical signal with which the MOS structure responds to the light pulses, changes sign at  $V_G = V_{FB}$  and that there exists a finite and measurable electrical response of the MOS structure in the state of accumulation. The polarity of this response is opposite to the polarity observed in the inversion and depletion ranges, as shown in Fig. 1.

The authors of [3] used the lock-in amplifier in their experimental work, which allowed them to obtain  $u(V_G)$  characteristics similar to the one shown in Fig. 1. However, they did not try to take full advantage of this technique as a  $V_{FB}$  determination method.

It is the purpose of this work to improve the understanding and the experimental implementation of this measurement technique, to make it more sensitive, more precise and more accurate than the commonly used method of  $C(V_G)$  characteristics.

### 2. Physical Background of the Method

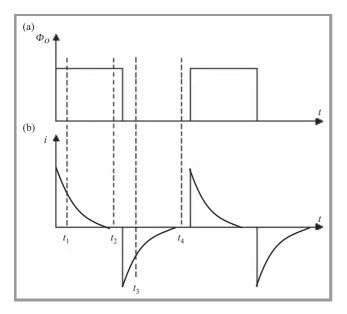

Consider an MOS structure illuminated by a series of light pulses as shown in Fig. 2(a). The photon energy of this light hv should be larger that the band gap  $E_G$  of the semiconductor substrate (to generate electron-hole pairs), but smaller than the barrier heights at gate-dielectric and

*Fig. 2.* (a) The intensity of photon flux  $\Phi_0$  versus time *t* and (b) the current *i* versus time *t*.

JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY 4/2009 dielectric-semiconductor interfaces (not to generate current flow across the dielectric).

As a result of such pulsed illumination, a series of current pulses can be detected in the external circuit of the investigated structure (Fig. 2(b)). The magnitude of these pulses depends on the semiconductor surface potential  $\phi_S$  and the pulses disappear when  $\phi_S = 0$ , as shown in [3].

Hence, by finding the dependence of the magnitude of these current peaks on the gate bias  $V_G$  one may find the flat-band voltage value  $V_{FB}$ , at which the current peaks disappear.

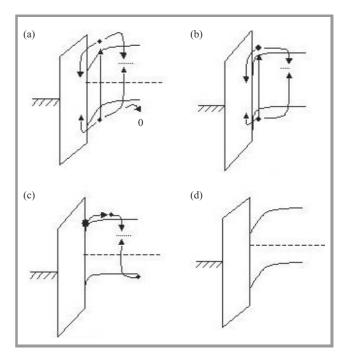

Following [4] in Fig. 3 the movement of charges is illustrated in different time intervals  $t = t_1, t_2, t_3$  and  $t_4$ , marked both in Figs. 2 and 3.

*Fig. 3.* Band diagrams of the MOS system for different times illustrating the current flux at the dielectric-semiconductor interface: (a)  $t = t_1$ ; (b)  $t = t_2$ ; (c)  $t = t_3$ ; (d)  $t = t_4$ .

At  $t = t_1$ , the light beam causes increased generation of carriers in the semiconductor. The photo-generated electrons may either recombine through the interface states, or in the semiconductor bulk, or they may accumulate in the potential well at the semiconductor-dielectric interface. At the same time, the photo-generated holes can either recombine with the electrons, at the interface or in the bulk, or they can leave the semiconductor through the back contact, causing current flow in the external circuit and accumulate in the MOS gate. After some time, electrons and holes are accumulated on both sides of the dielectric, thus, increasing the voltage drop in the dielectric. Such an increase of this voltage drop must be balanced by a decrease of the semiconductor surface potential  $\phi_S$ , which causes a decrease of the width w of the space charge region at the semiconductor surface. As a result, the carrier generation rate decreases, leading to the situation in which the carrier generation is

balanced by recombination and the current in the external circuit disappears, as illustrated in Figs. 2 and 3(b) for  $t = t_2$ .

When illumination disappears, electrons accumulated at the semiconductor surface are emitted into the semiconductor bulk where they recombine with the holes "returning" from the gate through the external circuit, as illustrated in Fig. 3(c). These "returning" holes create a negative current pulse in the external circuit, as shown in Fig. 2, at  $t = t_3$ . This process continues until thermal equilibrium is reached at the semiconductor surface, as illustrated in Fig. 3(d) and the current in the external circuit disappears, as shown in Fig. 2, at  $t = t_4$ .

### 3. Calculation of the $u = f(V_G)$ Characteristics

In an attempt to fully exploit the advantages of LPT and SLPT methods of flat-band voltage determination in MOS structures we have developed a method which allows the dependence of the DC signal u at the output of the lockin amplifier to be calculated as a function of the potential  $V_G$  applied to the gate of the MOS structure under investigation. This method is based on the theory developed in [2], [3].

The effective light generation level is defined as

$$\xi = \frac{\Delta n}{n_i} = \frac{\Delta p}{n_i},\tag{1}$$

where:  $\Delta n$ ,  $\Delta p$  are the excess electron and hole concentrations generated by light and  $n_i$  is the intrinsic concentration. As shown in [2], [3] the main parameters of MOS structures under illumination (in quasi-equilibrium) may be expressed by the same expressions that apply in equilibrium if the Fermi potential  $u_F = \frac{q\phi_F}{kT}$  is replaced by  $u_F^* = \frac{q\phi_F}{kT}$ , and the intrinsic concentration  $n_i$  is replaced by  $n_i^*$ , where:

$$u_F^* = \frac{1}{2} \ln \frac{\xi + e^{u_F}}{\xi + e^{-u_F}}$$

(2)

and

$$n_i^* = n_i \sqrt{\left(\xi + e^{u_F}\right) \left(\xi + e^{-u_F}\right)}.$$

(3)

The DC signal at the output of lock-in amplifier is proportional to the difference  $\Delta Q_S$  of the semiconductor surface charge in equilibrium  $Q_S$  and under illumination  $Q_S^*$ :

$$u \sim \Delta Q_S = Q_S - Q_S^*,\tag{4}$$

where  $Q_S$  is given by [5]

$$Q_S = \sqrt{2\,\mathrm{k}\,T\,\varepsilon_{Si}\,\varepsilon_0\,n_i}\cdot F_S,\tag{5}$$

which under illumination becomes:

$$Q_S^* = \sqrt{2\,\mathrm{k}\,T\,\varepsilon_{Si}\,\varepsilon_0\,n_i^*}\cdot F_S^*,\tag{5a}$$

where: k – Boltzmann's constant, T – absolute temperature,  $\varepsilon_{Si}$  – relative electrical permittivity of the semiconductor,  $\varepsilon_0$  – permittivity of free space and  $F_S$  is the Kingston function, given by

$$F_{S} = -\frac{u_{S}}{|u_{S}|} \sqrt{e^{u_{F}} (e^{-u_{S}} + u_{S} - 1) + e^{-u_{F}} (e^{u_{S}} - u_{S} - 1)}, \quad (6)$$

which under illumination becomes:

$$F_{S}^{*} = -\frac{u_{S}^{*}}{|u_{S}^{*}|} \sqrt{e^{u_{F}^{*}} \left(e^{-u_{S}^{*}} + u_{S}^{*} - 1\right) + e^{-u_{F}^{*}} \left(e^{u_{S}^{*}} - u_{S}^{*} - 1\right)}, \quad (6a)$$

where:  $u_s$  is the normalized surface potential in equilibrium:

$$u_S = \frac{q\phi_S}{\mathbf{k}T},\tag{7}$$

becoming:

$$u_S^* = \frac{q\phi_S^*}{kT} \tag{7a}$$

under illumination.

The gate voltage  $V_G$  is the same when the MOS structure is in equilibrium and when it is illuminated. In the case of equilibrium,  $V_G$  may be expressed as [5]

$$V_G - V_{FB} = \phi_S - \frac{Q_S}{C_I},\tag{8}$$

which under illumination becomes:

$$V_G - V_{FB} = \phi_S^* - \frac{Q_S^*}{C_I},$$

(8a)

where:  $C_I$  is the capacitance of the dielectric.

Since  $Q_S(Q_S^*)$  are the functions of  $u_S(u_S^*)$  and  $\phi_S(\phi_S^*)$  given above one may calculate  $\phi_S$ ,  $\phi_S^*$ ,  $Q_S$  and  $Q_S^*$  values for any  $V_G$  value, if the effective light generation level  $\xi$  is known. Hence, for any  $\xi$  value the  $\Delta Q_S = f(V_G)$  characteristics may be calculated. These characteristics should have the same shape as the experimental  $u = f(V_G)$  characteristics.

For given experimental conditions the value of  $\xi$  may be determined by taking the  $C(V_G)$  characteristics of the MOS structure in the darkness, as well as, under illumination and by calculating the  $u_F^*$  value using the expression [2], [3]:

$$u_{F}^{*} = u_{F} \left[ \frac{C_{INV} \left( C_{I} - C_{INV}^{*} \right)}{C_{INV}^{*} \left( C_{I} - C_{INV} \right)} \right]^{2}, \tag{9}$$

where:  $C_{INV}$ ,  $C_{INV}^*$  are the inversion capacitance values in the darkness and under illumination, respectively.

| 4/2009 | JOUR | RNAL | OF 1 | ELE  | CON | MUN | VICAT | IONS |

|--------|------|------|------|------|-----|-----|-------|------|

|        | AND  | INF  | ORM  | ATIO | DN  | TEC | INOL  | OGY  |

Once the value of  $u_F^*$  is known,  $\xi$  may be calculated using:

$$\xi = e^{-u_F} \frac{e^{2u_F} - e^{2u_F^*}}{e^{2u_F^*} - 1}.$$

(10)

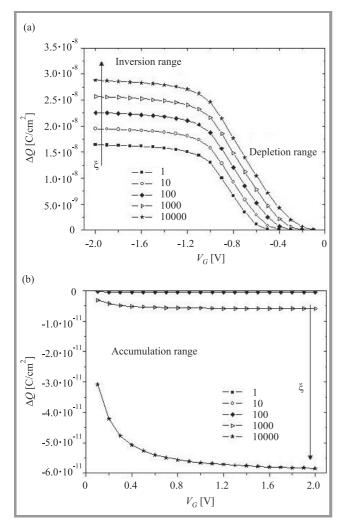

The calculated  $u(V_G)$  characteristics in inversion/depletion and accumulation are presented in Figs. 4(a) and 4(b), respectively. An ideal n-type MOS structure with the following parameters:  $t_{OX} = 63.2$  nm,  $N_D = 1.487 \cdot 10^{15}$  cm<sup>-3</sup>,  $C_I = 5.4637 \cdot 10^{-8}$  F/cm<sup>2</sup> was assumed.

*Fig. 4.* Calculated  $\Delta Q_S = f(V_G)$  characteristics for different  $\xi$  values in: (a) inversion/depletion and (b) accumulation.

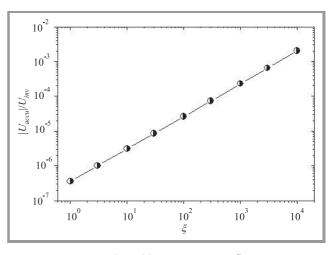

The influence of  $\xi$  on the calculated  $\Delta Q$  (hence also on the *u* signal) is much stronger in accumulation than in inversion/depletion, as clearly seen in Fig. 4. The ratio of the signal in accumulation to the signal in inversion  $(|u_{accu}|/u_{inv})$  is shown in Fig. 5 as a function of  $\xi$ .

Hence, the  $\xi$  value may be directly determined from the  $|u_{accu}|/u_{inv} = f(\xi)$  plot:

$$\xi = 10^{\frac{m}{n}} \left( \frac{|u_{accu}|}{u_{inv}} \right)^{\frac{1}{n}},\tag{11}$$

where: *m*, *n* are the parameters of the interpolation line y = mx + n approximating the  $|u_{accu}|/u_{inv}$  dependence.

JOURNAL OF TELECOMMUNICATIONS 4/2009

Hence, having the measured  $u(V_G)$  characteristics and comparing the  $|u_{accu}|/u_{inv}$  ratio with the calculated depen-

*Fig.* 5. The ratio of  $|u_{accu}|/u_{inv}$  for different  $\xi$ . In the range of 1 to 10<sup>4</sup> the ratio shows the linear dependence of log  $|u_{accu}|/u_{inv}$  on log  $\xi$ .

dence of  $|u_{accu}|/u_{inv}$  on  $\xi$  (for the same structure parameters) one may determine the effective light generation level  $\xi$ .

# 4. Implementation of the Measurement Method

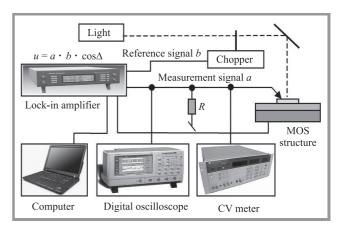

The measurement setup for the flat-band voltage  $V_{FB}$  determination is shown in Fig. 6. The light beam is chopped and reflected onto the gate of MOS structure by the mirror.

*Fig. 6.* The measurement setup for the flat-band  $V_{FB}$  voltage determination.

The measured signal a from the structure is detected by a digital oscilloscope and a lock-in amplifier, which allows very small signals to be measured, even if they are below the noise level. The reference signal b from the chopper is also fed into the lock-in amplifier. The output signal uof the lock-in amplifier is a product of a and b signals and cosine of the phase difference between these signals  $(\cos \Delta)$ . Changing the phase of signal *b* allows the maximum value of the output signal  $(\cos(0, 180^\circ) = 1)$  to be obtained.

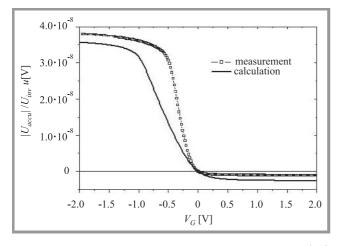

The comparison of the measured and calculated characteristics is shown in Fig. 7. The parameters used in the calculation model ( $N_D = 1.354 \cdot 10^{15} \text{ cm}^{-3}$ ,  $t_{OX} = 61.83 \text{ nm}$ ) were determined by  $C(V_G)$  measurements. The  $\xi$  value is assumed to be  $10^4$ . The measured  $u(V_G)$  characteristics are shifted along the horizontal axis so that the signal *u* reaches zero at zero gate voltage.

*Fig.* 7. The comparison between measured and calculated  $u(V_G)$  characteristics.

The differences between both (measured and calculated) characteristics are clearly seen, although the shape of these curves is quite similar. The inaccuracies (e.g., different slope in depletion range, different level in accumulation and inversion ranges) are probably caused by the fact that calculations were done assuming an ideal MOS structure, by the errors in measuring the structure parameters and, possibly, by the inaccuracy of the determination of the zero level of the signal u.

### 5. Results

The measurements of  $u = f(V_G)$  characteristics made on dozens of MOS structures with different parameters (e.g., different  $t_{OX}$ , different annealing time  $t(N_2)$ ) confirmed, that the photoelectric LPT method is a very promising technique of the flat-band voltage  $V_{FB}$  determination. Numerous measurements made on the same structure show excellent reproducibility. The spread of points, at which  $u(V_G)$  characteristics change sign ( $V_{FB}$  values), is not greater than  $\pm 5$  mV in this case. The sensitivity of the LPT method is very good. Due to the use of a lock-in amplifier high precision measurements of very small signal values ( $\sim$  nV) in accumulation may be performed. Hence, the LPT method seems to allow much more accurate  $V_{FB}$ determination than the method of  $C(V_G)$  characteristics. Despite many advantages of the LPT method the determination of its absolute accuracy is still problematic. In accordance with our present knowledge and assuming for the moment, that all the measurements of  $u(V_G)$  characteristics are taken at the same temperature T, the  $u(V_G)$  characteristics taken at different values of the light beam power Pshould have one common point at which they intersect one another. This point corresponds to  $\phi_S = 0$  and  $V_G = V_{FB}$ . Hence, this point of intersection is expected to lie at the u = 0 axis.

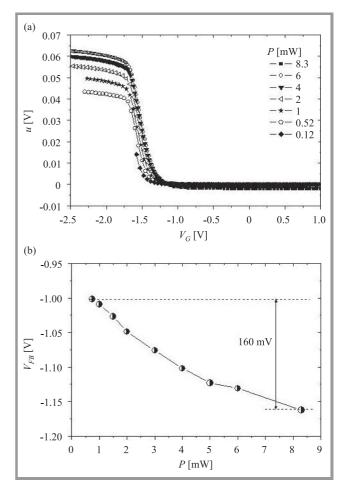

*Fig. 8.* (a) The  $u(V_G)$  characteristics measured at different light power *P* and (b)  $V_{FB}$  values shifted by 0.11 mV along vertical axis as a function of light power.

Our measurement results show, however, that this "point", or rather a spot of final dimensions, where the family of  $u(V_G)$  characteristics taken at different *P* values is very narrow (< 200 mV), lies not at the u = 0 axis, but a little (~ 0.1 mV) above it. This may result in considerable differences in  $V_G$  values at which these characteristics intersect the u = 0 axis. This effect results probably from the zeroing accuracy of our lock-in amplifier, which is insufficient for this application.

Therefore it is assumed further that the position of the minimum width of the band of  $u(V_G)$  characteristics and not the point of intersection with the u = 0 axis determines the  $V_{FB}$  value. The fact that the  $u(V_G)$  characteristics taken over a wide range of light power P do not cross one another at one point, but rather at a spot of finite dimensions, may be explained by the differences of the temperature Tof the structure, resulting from illumination with different light beam power P.

The  $u(V_G)$  characteristics measured at different P are presented in Fig. 8(a). The influence of T on the  $V_{FB}$  value is illustrated in Fig. 8b, by the  $V_{FB}$  versus P characteristics. In Fig. 8(b) the amplitude (difference between highest and lowest  $V_{FB}$  values) is approximately equal to 160 mV. The  $V_{FB}$  value measured on the same MOS structure by  $C(V_G)$ characteristics method is equal to -0.955 V, so it is clearly seen that in in the case of LPT photoelectric measurements the  $V_{FB}$  values obtained at different power of light are more negative than those obtained from the the  $C(V_G)$  measurements. Moreover a decreasing tendency of  $V_{FB} = f(P)$  for P > 0.75 mW is observed. This phenomenon may be explained by the increasing temperature caused by the high power of the light beam illuminating the sample [6], [7]. Further investigations will be focused on detailed understanding of this problem.

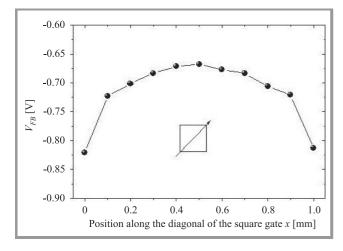

Although, the absolute accuracy of the LPT method is not satisfactory yet, the SLPT method which is a modification of the LPT method was used to measure local  $V_{FB}$  values. By scanning the gate area with a light beam of small diameter the spatial distribution of the local  $V_{FB}$  values may be determined. Using this method a series of local  $V_{FB}$  values was determined along the diagonal of a square gate, as shown in Fig. 9.

*Fig. 9.* One-dimensional distributions of local  $V_{FB}$  values in a MOS structure.

Although high absolute accuracy of each local  $V_{FB}$  value, represented by a point in Fig. 9, may not be guaranteed, there is no doubt that the shape of the  $V_{FB}$  distribution over the gate area is correctly represented. This shape of  $V_{FB}$  distribution is not surprising taking into account the previously determined distributions over the gate area of the effective contact potential difference  $\phi_{MS}$  [8]–[11] and of the barrier height  $E_{BG}$  at the gate-dielectric in-

JOURNAL OF TELECOMMUNICATIONS AND INFORMATION TECHNOLOGY 4/2009 terface [12]–[15]. Local values of all these parameters have "dome-like" distributions over gate areas of metal gate MOS structures. It is our hypothesis that this shape of distributions of electrical parameters is caused by the non uniform distribution of the mechanical stress at the metal-dielectric interface [16]–[20].

### 6. Conclusions

A new, high precision photoelectric measurement method of the flat-band  $V_{FB}$  voltage in MOS structures is studied. This method, called light pulse technique (LPT) consists in illuminating a semitransparent gate of a MOS structure by a series of light pulses and measuring the output current signal which is a function of the potential  $V_G$  applied to the investigated structure. The magnitude of these current pulses depends on semiconductor surface potential  $\phi_S$  and when  $\phi_S = 0$  the pulses disappear. This situation defines the flat-band state in semiconductor.

The measurement results of  $V_{FB}$  values confirmed that the LPT method is characterized by a good precision and good reproducibility. The problem of the absolute accuracy of this method has not been solved yet and it is going to be the main purpose of our further investigations.

The SLPT method which is a modification of the LPT method allows to the local values of  $V_{FB}$  at different points over the gate of the MOS structure to be measured. It was proved that, as expected, the  $V_{FB}$  values have a characteristic dome-like distribution over the gate area. This shape is similar to those of  $\phi_{MS}$  and  $E_{BG}$  distributions measured previously and is characterized by the highest values in the middle of the gate and lower values at the gate corners. It is our hypothesis that the mechanical stress existing in the oxide under the metal gate has a dominant influence on the shape of the distribution of the above mentioned electrical parameters.

#### References

- B. H. Yun, "Direct measurement of flat-band voltage in MOS by infrared excitation", *Appl. Phys. Lett.*, vol. 21, no. 5, pp. 194–195, 1972.

- [2] A. Jakubowski and S. Krawczyk, "Electrical properties of the MIS capacitor under illumination", *Electron Technol.*, vol. 11, no. 1/2, pp. 3–22, 1978.

- [3] A. Jakubowski and S. Krawczyk, "Photoelectric method of the MIS flat-band voltage determination", *Electron Technol.*, vol. 11, no. 1/2, pp. 23–35, 1978.

- [4] O. Engstrom and A. Carlsson, "Scanned light pulse technique for the investigation of insulator – semiconductor interfaces", J. Appl. Phys., vol. 54, no. 9, pp. 5245–5251, 1983.

- [5] E. H. Nicollian and J. R. Brews, MOS (Metal Oxide Semiconductor) Physics and Technology. New York: Wiley, 1982.

- [6] M. Leśko and H. M. Przewłocki, "Badanie wpływu temperatury na parametry elektryczne struktur MOS", *Elektronika*, no. 2–3, pp. 56–57, 2005 (in Polish).

- [7] M. Leśko, "Badanie wpływu temperatury na parametry i charakterystyki C(V) struktur MOS". M.Sc. thesis, Warsaw University of Technology, Institute of Electron Technology, Warsaw, 2004 (in Polish).

- [8] H. M. Przewłocki *et al.*, "The lateral distribution of the effective contact potential difference over the gate area of MOS structures", *Internet J. Electron Technol.*, vol. 35, no. 6, pp. 1–6, 2003.

- [9] H. M. Przewłocki *et al.*, "Distribution of the contact potential local values over the gate area of MOS structures", *Microelectron. Eng.*, vol. 72, pp. 165–173, 2004.

- [10] A. Kudła *et al.*, "Photoelectric measurements of the local value of the contact potential difference in the metal-insulator-semiconductor MIS structures", *Thin Solid Films*, vol. 450, pp. 203–206, 2004.

- [11] H. M. Przewłocki *et al.*, "Variability of the local \u03c6<sub>MS</sub> values over the gate area of MOS devices", *J. Telecommun. Inform. Technol.*, no. 1, pp. 34–39, 2005.

- [12] K. Piskorski and H. M. Przewłocki, "Distribution of potential barrier height local values at Al-SiO<sub>2</sub> and Si-SiO<sub>2</sub> interfaces of the metal-oxide-semiconductor (MOS) structures", *Internet J. Electron Technol.*, vol. 36, no. 5, pp. 1–5, 2004.

- [13] K. Piskorski and H. M. Przewłocki, "Distribution of potential barrier height local values at Al-SiO<sub>2</sub> and Si-SiO<sub>2</sub> interfaces of the metal-oxide-semiconductor (MOS) structures", *Bull. Polish Acad. Sci.*, vol. 54, no. 4, pp. 461–468, 2006.

- [14] K. Piskorski and H. M. Przewłocki, "Investigation of barrier height distributions over the gate area of Al-SiO<sub>2</sub>-Si structures", J. Telecommun. Inform. Technol., no. 3, pp. 49–54, 2007.

- [15] H. M. Przewłocki, K. Piskorski, A. Kudła, and D. Brzezińska, "Distributions of barrier heights, difference of effective contact potential, and local values of flat-band voltage in Al-SiO<sub>2</sub>-Si and poly-Si-SiO<sub>2</sub>-Si structures", *Thin Solid Films*, vol. 516, pp. 4184–4189, 2008.

- [16] C. H. Bjorkman, J. T. Fitch, and G. Lucovsky, "Correlation between midgap interface state density and thickness-averaged oxide stress and strain at Si/SiO<sub>2</sub> interfaces formed by thermal oxidation of Si", *Appl. Phys. Lett.*, vol. 56, no. 20, pp. 1983–1986, 1990.

- [17] S. M. Hu, "Stress-related problems in silicon technology", J. Appl. Phys., vol. 70, no. 6, pp. 53–80, 1991.

- [18] I. De Wolf, H. E. Maes, and S. K. Jones, "Micro-Raman study of stress distribution in local isolation structures and correlation with transmission electron microscopy", *J. Appl. Phys.*, vol. 71, no. 2, pp. 898–906, 1991.

- [19] I. De Wolf, H. E. Maes, and S. K. Jones, "Stress measurements in silicon devices through Raman spectroscopy: bridging the gap between theory and experiment", *J. Appl. Phys.*, vol. 79, no. 9, pp. 7148–7156, 1996.

- [20] K. F. Dombrowski, I. De Wolf, and B. Dietrich, "Stress measurements using ultraviolet micro-Raman spectroscopy", J. Appl. Phys., vol. 75, no. 16, pp. 2450–2451, 1999.

**Krzysztof Piskorski** was born in Zgierz, Poland, in 1976. He received the M.Sc. degree from the Technical University of Łódź, Poland, in 2002. His Masters project in "Dry etching of  $A_{III}$ – $B_V$  nitrides" was carried out at the Ecole Centrale de Lyon, France, in 2001. He is currently working as a Research Assistant at the Institute

of Electron Technology (IET) in Warsaw, Poland, with the Department of MOS System Studies. His research interests include photoelectric measurements for MOS structures.

e-mail: kpisk@ite.waw.pl Institute of Electron Technology Lotników av. 32/46 02-668 Warsaw, Poland

Henryk M. Przewłocki obtained the M.Sc., Ph.D., and D.Sc. degrees in 1959, 1969, and 2001, respectively, specializing in physics, technology, and measurements of MOS structures. In the period of 1965–1983, he also taught various courses to graduate and undergraduate students of the Technical University of Warsaw.

At present he is Head of a research group at the Institute of Electron Technology (IET) in Warsaw, specializing in photoelectric properties and measurement methods of MOS structures. He has served as consultant and committeeman to numerous scientific, industrial and educational organizations in Poland and worldwide and has received a number of prestigious awards, including the highest Polish award, the National Award for Outstanding Achievements in Technical Sciences.

e-mail: hmp@ite.waw.pl Institute of Electron Technology Lotników av. 32/46 02-668 Warsaw, Poland