International Journal of Science Engineering and Advance Technology

Low Complex And Reconfigurable Fir Filter Using Low Power Architecture

Medisetti Mahalakshmi\*<sup>1</sup>, P Naga Raju<sup>2</sup> M.Tech Scholar, Department of ECE.<sup>1</sup> Assist.Prof, Department of ECE, Kakinada Institute of Engineering &Technology East Godavari Dist., AP, India.<sup>2</sup>

Abstract—Coefficient multipliers are the hindrances exhibit in programmable finite impulse response (FIR) advanced channels. As the channel coefficients change either powerfully or occasionally, the scan for basic sub articulations for multiplier less execution should be performed over the whole extent of numbers of the coveted exactness, and the measure of movements related with each recognized basic sub articulation should be retained. The multifaceted nature of a quality inquiry is in this manner past the current outline calculations in light of ordinary double and marked digit portrayals. Another plan worldview for the programmable FIR channels by misusing the expanded twofold base number framework (EDBNS). Because of its sparsity and intrinsic reflection of the whole of parallel moved fractional items, the sharing of adders in the time-multiplexed various consistent increase pieces of the programmable FIR channels can be boosted by an immediate mapping from the semi least EDBNS. The multiplexing cost can be further reduced by merging double base terms. In this, power is reduced by using modified booth encoding algorithm. Partial products generation stage is optimized by using Radix8 modified booth encoding algorithm.

Keywords: Extended Double Base Number System (EDBNS), Product of b generation (POBG), Finite Impulse Response (FIR).

# I. INTRODUCTION

Filter is a frequency particular system. It passes a band of frequencies while constricting the others. Channels are delegated simple and computerized relying upon nature of sources of info and yields. Channels are additionally delegated limited motivation reaction and endless drive reaction channels relying upon motivation reaction. This part gives a brief about the sorts of channels.

Advanced channels are utilized broadly in every aspect of electronic industry. This is on account of advanced channels can possibly accomplish much preferable flag to commotion proportions over simple channels and at each middle of the road arrange the simple channel adds more clamor to the flag, the computerized channel performs quiet scientific operations at each moderate stride in the change. The computerized channels have risen as a solid alternative for evacuating commotion, forming range, and limiting between image impedance in correspondence designs. These channels have turned out to be prominent in light of the fact that their exact reproducibility permits configuration architects to accomplish execution levels that are hard to get with simple channels

Computerized Filters can be developed from 3 crucial numerical operations.

- Addition (or subtraction)

- Multiplication (ordinarily of a flag by a steady)

• Time Delay i.e. deferring a computerized motion by at least one specimen periods

Multipliers are key parts of numerous superior frameworks, for example, FIR channels, chip, advanced flag processors, and so forth. A framework's execution is for the most part controlled by the execution of the multiplier in light of the fact that the multiplier is by and large the slowest forgiving in the framework. Moreover, it is by and large the most region devouring. Consequently, upgrading the speed and territory of the multiplier is a noteworthy outline issue. Be that as it may, zone and speed are generally clashing limitations with the goal that enhancing speed comes about for the most part in bigger ranges. Subsequently, entire ranges of multipliers with various zone speed requirements are composed with completely parallel handling. In the middle of are digit serial multipliers where single digits comprising of a few bits are worked on. These multipliers have direct execution in both speed and range. Be that as it may, existing digit

serial multipliers have been tormented by entangled exchanging frameworks as well as anomalies in plan. Radix 2<sup>n</sup> multipliers which work on digits in a parallel mold rather than bits convey the pipelining to the digit level and evade a large portion of the above issues. They were presented by M. K. Ibrahim in 1993. These structures are iterative and secluded. The pipelining done at the digit level brings the advantage of steady operation speed independent of the extent of the multiplier. The clock speed is just controlled by the digit estimate which is now settled before the outline is actualized.

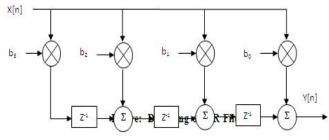

Y[n]=b0x[n]+b1x[n-1]+b2x[n-2]+b3x[n-3]

**Figure 2: Designing of FIR Filter**

• In electronics, an adder or summer is a digital circuit that performs addition of numbers. In numerous PCs and different sorts of processors, adders are utilized in the number-crunching rationale unit(s), as well as in different parts of the processor, where they are utilized to figure addresses, table records, and comparable operations. In spite of the fact that adders can be developed for some numerical portrayals, for example, paired coded decimal orexcess-3, the most widely recognized adders work on double numbers. In situations where two's supplement or ones' supplement is being utilized to speak to negative numbers.

• We can see a full viper as a 3:2 misfortune compressor: it aggregates three one-piece data sources, and returns the outcome as a solitary good for nothing number; that is, it maps 8 input esteems to 4 yield esteems. Hence, for instance, a parallel contribution of 101results out of a yield of 1+0+1=10 (decimal number '2'). The do speaks to bit one of the outcomes, while the aggregate speaks to bit zero. In like manner, a half viper can be utilized as a 2:2 misfortune compressor, compacting four conceivable contributions to three conceivable yields. Such compressors can be utilized to accelerate the summation of at least three addends. On the off chance that the addends are precisely three, the design is known as the convey spare viper. On the off chance that the addends are

at least four, more than one layer of compressors is essential and there is different conceivable outlines for the circuit. The most widely recognized are Wallace trees. This sort of circuit is most eminently utilized as a part of multipliers, which is the reason these circuits are otherwise called Wallace multipliers.

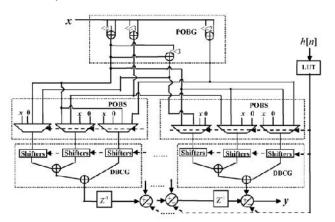

• Minimization of POBS by EDBNS Reduction Properties and Exponential Diophantine Equation (EDE):

Each of the POBS pieces comprises of a bank of multiplexers with inputs nourishing from the POBG. The results of each energy of-numbers and the info motion from the POBG are steered to the contributions of these multiplexers as indicated by their frequencies of events in the EDBNS portrayal of the coefficient. A similar fractional item may show up in the contributions of a few multiplexers of similar POBS square in the event that it happens more than once in the EDBNS portrayal of a similar coefficient. The execution cost of a POBS piece is dictated by the quantity of multiplexers and the multifaceted nature of every multiplexer. The many-sided quality of a multiplexer is roughly relative to its number of information sources and the bit width of the data sources. In this manner, one approach to decrease the equipment cost of a POBS piece is to limit the aggregate number of info lines to the multiplexers. In spite of the fact that has been compelled in general in the era of the EDBNS portrayals for all - bit coefficients, the EDBNS portrayals of a few coefficients may have less than terms. Accordingly, a few components in don't need to be associated with the contributions of all multiplexers. Advance decrease in the aggregate number of contributions to the multiplexers of a POBS piece can be accomplished with the assistance of the accompanying two diminishment rules [35] for DBNS. The second property is additionally substantial for of EDBNS.

8-bit programmable FIR filter designed by proposed algorithm

Step 1) Compute and for all -bit coefficients. Generate the EDBNS array for all the -bit coeffi- cients using the search algorithm.

Step 2) Implement the POBG block by producing all power-of- integers in using the method

Step 3) Design the POBS block with multiplexers. Each power-of- integer from the POBG block is first connected to an input of different multiplexers, where is the maximum number of times that power-of- value can appear in the EDBNS representation of any coefficient. Then, minimize the number of input lines to the multiplexers of POBS block by the algorithm presented in above figure.

Step 4) Design programmable shifters for the DBCG block. Extract the amount of shifts for each powerof- integer and store it in the LUT addressable by the fundamentals.

Step 5) Sum the double base terms in DBCG by a carry save adder (CSA) tree to reduce the delay.

#### II. DOUBLE BASE NUMBER SYSTEM:

Twofold base number framework (DBNS) is an option number framework other than the double framework. Its portrayal is like the radix number framework together with two bases, generally be two and three. DBNS jelly the two essential properties: excess and scantiness. The excess is the property obliging with the parallelism. In this examination, we are occupied with parallel expansion calculation on DBNS. Our hypothetical outcome demonstrates that parallel expansion in DBNS can be performed

•

#### RADIX-8 MODIFIED BOOTH ALGORITHM:

- •

- Stall's calculation includes more than once including one of two foreordained esteems to an item P, and afterward playing out a rightward number juggling shift on P.

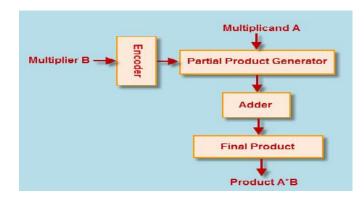

- Multiplier engineering contain two designs, i.e., Modified Booth. In view of the investigation of different multiplier designs, we locate that Modified Booth builds the speed since it diminishes incomplete items to half. Further, the postponement in multiplier can be diminished by utilizing Wallace tree. Power utilization of Wallace tree multiplier is additionally less when contrasted with corner and exhibit. Elements of the two multipliers can be consolidated to create rapid and low power multiplier. Adjusted Booth multiplier comprises of Modified Booth Recorder

(MBR). MBR have two sections, i.e., Booth Encoder (BE) and Booth Selector (BS). The fundamental operation of BE is to decipher the multiplier flag and yield will be utilized by BS to create the halfway item. The incomplete items are at that point, included with the Wallace tree adders, like the convey spare snake approach. The last line of convey and aggregate yield is included via convey look-ahead viper with the convey skewed to one side by position.

•

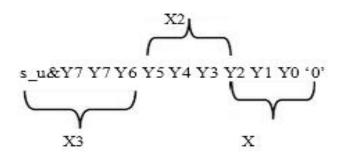

Radix-8 Booth encoding is frequently used to keep away from variable size halfway item exhibits. Before planning Radix-8 BE, the multiplier must be changed over into a Radix-8 number by partitioning them into four digits separately as indicated by Booth Encoder Table given after wards. Preceding believer the multiplier, a zero is added into the Least Significant Bit (LSB) of the multiplier.

Radix 8 Booth recoding applies the same algorithm as that of Radix 4, but now we take quartets of bits instead of triplets. Each quartet is codified as a signed digit using below

Table. Radix 8 algorithm reduces the number of partial products to n/3, where n is the number of multiplier bit s. Thus it allows a ti me gain in the partial products summation Radix-8 recoding applies the same algorithm as radix-4, but now we take quartets of bits instead of triplets. Each quartet is codified as a signed-digit using the table

| Quartet value | Signed-digit value |

|---------------|--------------------|

| 0000          | 0                  |

| 0001          | +1                 |

| 0010          | +1                 |

| 0011          | +2                 |

| 0100          | +2                 |

| 0101          | +3                 |

| 0110          | +3                 |

| 0111          | +4                 |

| 1000          | -4                 |

| 1001          | -3                 |

| 1010          | -3                 |

| 1011          | -2                 |

| 1100          | -2                 |

| 1101          | -1                 |

| 1110          | -1                 |

| 1111          | 0                  |

Here we have an odd multiple of the multiplicand, 3Y, which is not immediately available. To: generate it we need to perform this previous add:2Y+Y=3Y. But we are designing a multiplier for specific purpose and thereby the multiplicand belongs to a previously known set of numbers which are stored in a memory chip. We have tried to take advantage of this fact, to ease the bottleneck of the radix-8 architecture, that is, the generation of 3Y. In this manner we try to attain a better overall multiplication time, or at least comparable to the time we could obtain using a radix-4 architecture (with the additional advantage of using a less number of transistors). To generate 3Y with 21bit words we only have to add 2Y+Y, that is, to add the number with the same number shifted one position to the left.

A product formed by multiplying the multiplicand by one digit of the multiplier when the multiplier has more than one digit. Partial products are used as intermediate steps in calculating larger products.

Partial product generator is designed to produce the product by multiplying the multiplicand A by 0, 1, -1, 2, -2,-3,-4, 3, 4. For product generator, multiply by zero means the multiplicand is multiplied by "0".Multiply by "1" means the product still remains the same as the multiplicand value. Multiply by "-1" means that the product is the two's complement form of the number. Multiply by "-2" is to shift left one bit the two's complement of the multiplicand value and multiply by "2" means just shift left the multiplicand by one place. Multiply by "-4" is to shift left two bit

the two's complement of the multiplicand value and multiply by "2" means just shift left the multiplicand by two place. Here we have an odd multiple of the multiplicand, 3Y, which is not immediately available. To generate it we need to perform this previous add: 2Y+Y=3Y. But we are designing a multiplier for specific purpose and thereby the multiplicand belongs to a previously known set of numbers which are stored in a memory chip. We have tried to take advantage of this fact, to ease the bottleneck of the radix-8 architecture, that is, the generation of 3Y. In this manner we try to attain a better overall multiplication time, or at least comparable to the time we could obtain using radix-4 architecture (with the additional advantage of using a less number of transistors). To generate 3Y with 8-bit words we only have to add 2Y+Y, that is, to add the number with the same number shifted one position to the left.

#### **III. RESULTS**

Figure 6: Experimental Result

# **IV. CONCLUSION**

Design methodologies aiming at minimizing their implementation cost have been intensively studied by many researchers. This paper presents a radically different approach to this problem for the minimization of the TMMCM block of programmable FIR digital filters based on the extended form of DBNS. An algorithm for the generation of quasi-minimum EDBNS has been proposed. The obtained EDBNS can be directly mapped to an efficient TM-MCM architecture. Further, this is enhanced by using radix-8 modified booth encoding algorithm for improvement architecture.

### V. REFERENCES

[1] A. G. Dempster and M. D. Macleod, "Use of minimumadder multiplier blocks in FIR digital filters," IEEE Trans. Circuits Syst. II, AnalogDigit. Signal Process., vol. 42, no. 9, pp. 569–577, Sep. 1995.

[2] Y. Wang and K. Roy, "CSDC: A new complexity reduction technique for multiplierless implementation of digital FIR filters," IEEE Trans.Circuits Syst. I, Reg Papers, vol. 52, no. 9, pp. 1845–1853, Sep. 2005.

[3] C. Y. Yao, W. C. Hsia, and Y. H. Ho, "Designing hardware-efficient fixed-point FIR filters in an expanding subexpression space," IEEETrans. Circuits Syst. I, Reg Papers, vol. 61, no. 1, pp. 202–212, Jan. 2014.

[4] Y. Pan and P. K. Meher, "Bit-level optimization of adder-trees for multiple constant multiplications for efficient FIR filter implementation," IEEE Trans. Circuits Syst. I, Reg Papers, vol. 61, no. 2, pp. 455–462, Feb. 2014.

[5] J. Park, W. Jeong, H. M. Meimand, Y. Wang, H. Choo, and K. Roy, "Computation sharing programmable FIR filter for low-power and high-performance applications," IEEE J. Solid-State Circuits, vol. 39, no. 2, pp. 348–357, Feb. 2004.

[6] E. Grayver and B. Daneshrad, "Low power, area efficient programmable filter and variable rate decimator," in Proc. IEEE Int.Symp. Circuits Syst., Geneva, Switzerland, May 2000, pp. 341–344.

[7] S. S. Demirsoy, R. Beck, A. G. Dempster, and I. Kale, "Reconfigurable implementation of recursive DCT kernels for reduced quantization noise," in Proc. IEEE Int. Symp. Circuits Syst., Bangkok, decimator," in Proc. IEEE Int.Symp. Circuits Syst., Geneva, Switzerland, May 2000, pp. 341–344.

[8] J. Chen and C. H. Chang, "High-level synthesis algorithm for the design of reconfigurable constant multiplier," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 28, no. 12, pp. 1844–1856, Dec. 2009.

[9] R. Mahesh and A. P. Vinod, "Reconfigurable low area complexity filter bank architecture based on frequency response masking for nonuniform channelization in software radio receivers," IEEE Trans. Aerosp. Electron. Syst., vol. 47, no. 2, pp. 1241–1255, Apr. 2011. [10] T. Chen, Y. V. Zakharow, and C. Liu, "Lowcomplexity channel-estimate based adaptive linear equalizer," IEEE Signal Process. Lett., vol. 18, no. 7, pp. 427–430, Jul. 2011.

[11] I. Hautala, J. Boutellier, and J. Hannuksela, "Programmable lowpower implementation of the HEVC adaptive loop filter," in IEEE Int. Conf. Acous., Speech, Signal Process., Vancouver, BC, Canada, May 2013, pp. 2664–2668.

[12] E. J. Norberg, R. S. Guzzon, J. S. Parker, L. A. Johansson, and L. A. Coldren, "Programmable photonic microwave filters monolithically integerated in InP-InGaAsP," J. Lightwave Technol., vol. 29, no. 11, pp. 1611–1619, Jun. 2011.