brought to you by 🗓 CORE

IJSEAT, Vol 3, Issue 9, SEPTEMBER - 2015

# International Journal of Science Engineering and Advance Technology

Carbon Nanotube based approach on FETs using Ternary Comparator

M.Koti Reddy,

Asst Proff, in Department of Electronics & Communication Engineering,

kakinada institute of engineering and technology-II,

Email:kotikiet@Gmail.Com

Abstract:A Carbon Nanotube Field Effect Transistor (CNFET) is referred to as a FET that utilizes a single Carbon Nanotube or an array of carbon nanotubes as the channel material instead of bulk silicon in the traditional MOSFET structure. New approach of ternary magnitude comparator based on the CNFET ternary logic gates. These gates are promising alternative to conventional logic design because of its energy efficiency, it can accomplish by the reduced circuit on ternary logic. Ternary comparator implementation is based on prefix based design and combines ternary and binary logic gates for optimized implementation. A novel approach of a comparator has been implemented and simulated using SPICE. A design response indicates that the 1-bit comparator consumes less power say 0.65µW and has a delay of 21ps. The simulation results for comparators with versatile lengths of operands.

*Keywords:* Comparator, CNFET, Ternery logic. **I. Introduction**

In ternary logic, a three-valued logic is any of several many-valued logic systems in which there are three truth values indicating true, false and some indeterminate third value. This is contrasted with the more commonly known bivalent logics which provide only for true and false. Early research on design of ternary logic using CMOS can be found in literature [2] [3]. Carbon nanotube based multilevel voltage mode logic design was presented in [4]. It has been shown that the performance of CMOS technologies can be enhanced by adding MVL blocks to binary ICs [5]. There are two kinds of MVL circuits which are based on MOS technology. One is current mode MVL circuit and the other is voltage mode MVL circuit. Voltage mode MVL is achieved by multithreshold CMOS design [6]. Multiple threshold values in CMOS can be achieved by using different bias voltages to the bulk terminal of the transistors. The CNFET is a promising alternative to silicon transistor for achieving low power and high performance [7] [8]. The other advantage of CNFET over CMOS is that the threshold voltage of CNFET is dependent on the device dimensions and specifically to diameter of CNT. Hence design of multi-threshold CNFETS can be accomplished by having CNT with different diameters. A resistive load CNFET based ternary logic design has been proposed in [4]. The disadvantage of this

methodology is the need of large off-chip resistances. A more efficient design which avoids the use of resistances is presented in [9]. This methodology relies on the method proposed in [10] & eliminates large resistances by employing active load with p-type CNTFETs in the ternary logic gates. The design of CNFET based ternary arithmetic circuits like 1-bit half adder and 1-bit multiplier is also presented in [9].

## II. CNFET

CNFET is a field effect transistor which uses single-wall CNT as the cannel. Owing to a much simpler manufacturing process of CNT, it makes a very promising alternative for the current days MOSFET [7]. The angle of atom arrangement along the tube in a single wall CNT (SWCNT) makes it either conducting or semiconducting. This unique property of the SWCNT is referred to as chirality vector and is represented by the integer pair (n,m), called the indexes. The nanotube is metallic if n=m or n-m=3i, where *i*, is integer. If this condition is not met then the nanotube is semiconducting. The diameter of CNT can be calculated by the following equations.

(1)  $D_{CNT} = \left(\frac{\sqrt{3}}{2}\right)a0\sqrt{n2+m2+nm}$

Where, 0.142 nm is the interatomic distance between two carbon atoms. The CNFET also has four terminals as its silicon counterpart. I-V characteristics of MOSFET and those of CNTFET are similar. The voltage required to turn the transistor ON is defined as the threshold voltage. A first order approximation of the threshold voltage of the CNT channel is given by half the bandgap which is an inverse function of the diameter.

$$V_{th} \sim (E_g/2e) = \frac{\sqrt{3}}{3} (aVth/eD_{CNT})$$

(2)

Where a = 2.49  $A^0$  is the carbon to carbon atomic distance, V = 3.033 eV is the carbon - bond energy in tight bonding model, e is the electron charge and D<sub>CNT</sub> is the CNT diameter. From the equation in (2), the threshold voltage of a CNTFET using CNTs with chirality (19, 0), as channels is 0.293V. The DCNT of such a CNT is 1.487 nm, which is obtained from (2). A change in chirality vector changes the threshold voltage of the CNTFET. When the m in the chirality vector is assumed to be always zero, the threshold voltages ratio of two CNTFETs with different chirality vectors is given by [9].

$V_{\text{th}1}/V_{\text{th}2} = D_{\text{CNT2}}/D_{\text{CNT1}} = n_2/n_1$  (3) Equation (3) demonstrates that the threshold voltage of a CNTFET is inversely proportional to the chirality vector of the CNT. Hence the threshold voltage of CNFET can be controlled by changing the chirality vector or the diameter of the CNT [4]. Many advances have been reported in the manufacturing process [14] and synthesis process [15] for fabricating SWCNTs with the desired (n,m) chirality structure. This paper multi-diameter CNFET-based design for ternary logic implementation has been used. The details of the design of CNFET based NTI, STI, PTI, NAND, NOR and ternary decoder are presented in [9].

### **III. Ternary Logic**

Ternary logic is a three valued logic and the functions realized with the three values are called as Ternary logic functions. The values 0, 1 and 2 form the nomenclature to denote the ternary values in this paper. A function f(X) is defined as a ternary logic function mapping  $\{0,1,2\}^n$  to  $\{0,1,2\}$ where X is given by  $\{X_1,...,X_n\}$ . When  $X_i$ ,  $X_j =$  $\{0,1,2\}$  [9], the basic operations of ternary logic can be defined as follows.

$$X_{i}+X_{j} = \max \{X_{i}, X_{j}\}$$

(4)

$$X_{i}\cdot X_{j} = \min \{X_{i}, X_{j}\}$$

(5)

Where equations (4) and (5) indicate OR and AND operations respectively for ternary logic. The logic symbols for different levels assumed are if voltage level 0, 1/2 Vdd, Vdd then the subsequent Logic value 0, 1, 2. Another important logic gate is an inverter. A general ternary inverter is an operator with one input and three outputs. The Table I shows the ternary inverter truth table where *x* is the input *y*0, *y*1, *y*2are outputs. To generate the outputs y0, *y*1 and *y*2 three inverters are needed namely negative ternary inverter (NTI), standard ternary inverter (STI) and a positive ternary inverter (PTI) respectively.

In ternary logic, the ternary NAND and NOR are multiple entry operators. The truth tables and the definitions of ternary NOR and NAND gates is presented in [9].

| Input <i>x</i> | NTI ( $y\theta$ ) | <b>STI</b> ( <i>y1</i> ) | PTI (y2) |

|----------------|-------------------|--------------------------|----------|

| 0              | 2                 | 2                        | 2        |

| 1              | 0                 | 1                        | 2        |

| 2              | 0                 | 0                        | 0        |

Table I: Ternary InverterIV.Novel GizmoComparator

The proposed design is to generate the  $g_j$  and  $e_i$  signals for each operand bit pairs  $A_i$  and  $B_i$ , where,  $g_j$ (greater) indicates  $A_i > B_i$  and  $e_i$ (equal) indicates  $A_i = B_i$ . The greater and equal signals

generated out of each bit positions can be grouped together by grouping logic as presented in [16]. Let  $g_i$  and  $e_i$  indicate the greater and equal signals for  $i^{th}$  bit also let  $g_i$  and  $e_j$  indicate the greater and equal signals for  $j^{th}$  for bit such that j > i. Then the grouped greater and equal signals are given by

$$\begin{array}{l} \mathbf{G}_{[j:i]} = g_i + e_j, \ g_i \\ \mathbf{E}_{[j:i]} = e_j \cdot e_i \end{array} \tag{6}$$

Where +indicates OR operation and  $\cdot$  indicates AND operation. This grouping is done successively until final greater and equal signals indicated by *G* [*N*: 0] and *E*[*N*: 0] are obtained. The final greater and equal signals are further used to generatefinal lesser signal *L* using the NOR operation as shown below

$$L_{[N:0]} = G_{[N:0]} + \overline{E_{[N:0]}}$$

(8)

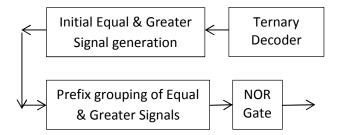

*New approach of Ternary comparator*: In the CNFET based ternary comparator consists of four stages as shown

#### Fig. 1 Ternary Comparator

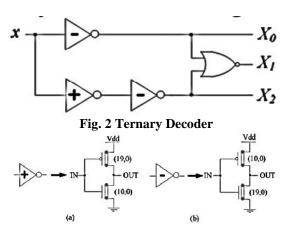

1) This stage consists of a ternary decoder, which is a one input 3-output combinational circuit and generates unary functions for an input x. The response of ternary decoder to the input x is given by

$$X_{k} = 2, \text{ if } f = k$$

0, if x k (9)

Where k, x can take logic values of 0, 1, 2. The schematic of the ternary decoder is shown in figure 2. The decoder consists of a PTI gate represented by inverter with '+' sign, two NTIgates, represented by inverters with '-' sign and a NOR gate.

Fig. 3 (a) PTI Gate (b) NTI Gate

The design methodology of CNFET PTI and NTI inverter is presented in [9]. The CNFET based PTI schematic diagram is shown in figure 3 (a). The threshold voltage of T1 is 0.557 V and the threshold voltage of T2 is -0.289 V. Therefore, only when the input voltage is higher than 0.6 V, the output voltage is zero. The outputs of NTI and PTI correspond to y0 and y2 of Table I. The CNFET based NTI schematic diagram is shown in figure 3(b). The threshold voltage of T1 is 0.289V, while the threshold voltage of T2 is -0.557V. When the input Voltage is below 0.3V (i.e., logic 0), the output voltage is 0.9 T2 is OFF, and the output voltage will be zero. The NOR gate that is used in the design of decoder is a simple binary logic gate (with logic levels 0 and 2) and can be designed by replacing the MOSFETs in CMOS design with CNFETs.

| Ai/B<br>i | E<br>q | G<br>r | E<br>q | G<br>r | E<br>q | G<br>r |

|-----------|--------|--------|--------|--------|--------|--------|

|           | 0      | 0      | 1      | 1      | 2      | 2      |

| 0         | 2      |        |        |        |        |        |

| 1         |        | 2      | 2      |        |        |        |

| 2         |        | 2      |        | 2      | 2      |        |

Table II KarnaughMap for Equal& Greater signal signal

2)This stage consists of a combinational circuit to generate  $g_i$  and  $e_i$  signals for a 1-bit comparator. The truth table of 1-bit ternary comparator is given in Table III. The karnaugh map of the comparator outputs equal and greater is given in Table II respectively.

| Ai                  | B <sub>i</sub><br>0 | ei                  | gi              |

|---------------------|---------------------|---------------------|-----------------|

| A <sub>i</sub><br>0 | 0                   | e <sub>i</sub><br>2 | $\frac{g_i}{0}$ |

| 0                   | 1                   | 0                   | 0               |

| 0                   | 2                   | 0                   | 0<br>2          |

| 1                   | 0                   | 0                   | 2               |

| 1                   | 1                   | 0<br>2<br>0         | 0               |

| 1                   | 2                   |                     | 0               |

| 2                   | 0                   | 0                   | 2               |

| 1<br>2<br>2<br>2    | 1                   | 02                  | 2<br>2          |

| 2                   | 2                   | 2                   | 0               |

Table III 1-Bit Comparator truth table

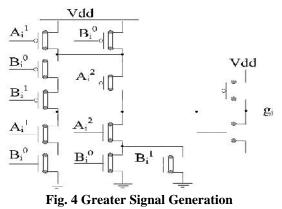

The output equations of a 1-bit comparator can be derived from the karnaugh map and are

$$g_{i} = A_{i}^{1} \cdot B_{i}^{0} + A_{i}^{2} \cdot B_{i}^{0} + A_{i}^{2} \cdot B_{i}^{1}$$

(10)

$$e_{i}^{0} = A_{i}^{0} \cdot B_{i}^{0} + A_{i}^{1} \cdot B_{i}^{1} + A_{i}^{2} \cdot B_{i}^{2}$$

(11)

Where  $A_i^k$  and  $B_i^k$  denotes the output of the decoder for the inputs  $A_i$  and  $B_i$ . This stage uses binary logic gates to implement (10) and (11). The transistor level implementation of for generation of  $g_i$  using CNFETs is shown in the figure 4.

All the CNFETs used here will have chirality vector equal to (19, 0). Similarly  $e_i$  signal is also generated. The equal andgreater signals generated at this stage correspond to the 1-bit comparison and they act as inputs to the grouping stage.

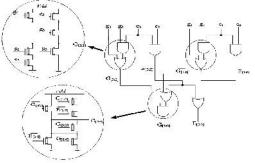

3) This stage consists of a binary prefix network. At this stage  $g_i$  and  $e_i$  are grouped according to the equations (6) and (7). As with the previous stage, this stage also uses binary logic gates. For optimized implementation the groupinglogic is designed in such a way that only AOI (AND-OR-INVERT) OrOAI (OR-AND-INVERT) gates are used in the prefix network as shown in the figure 5 for 4-bit comparator.

Fig. 5 Prefix grouping stage for 4- Bit Comparator

All the CNFETs used here will have chirality vector equal to (19, 0). This implementation eliminates the need of inverter at the output of each gate. The implementation of OAI and AOI gates is done using CNFETs.

4)The final Stage consists of a simple binary NOR gate to generate the lesser signal L from the greater and equal signals.

#### V.Simulation Results

Simulation on all implementations has been performed by HSPICE using the CNTFET model of [11] at 0.9V powersupply and room temperature.

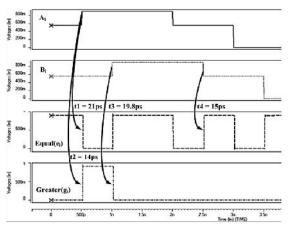

### Fig. 6 1-Bit Comparator input & output waveforms

All the CNFETs have used havebeen configured to have three tubes and default pitch valuewhich is equal to 20nm. Figure 5 shows the delay simulations for 1-bit comparator Simulation has been performed for 1-bit comparator stage with greater and equal signals.

The average power consumed by the 1-bit comparator is found out to be  $0.65\mu W$  and the power delay product is  $13.65 \times 10^{-18} J$ .

The table V shows the delay and power results for comparators with different operand lengths.

| Operand<br>Length | Delay<br>(ps) | Power<br>(µW) | Power- Delay<br>Product<br>(x10 <sup>-18</sup> J) |

|-------------------|---------------|---------------|---------------------------------------------------|

| 2                 | 24.33         | 1.336         | 32.5                                              |

| 4                 | 26.76         | 2.71          | 72.5                                              |

| 8                 | 29.2          | 5.45          | 159.14                                            |

| 16                | 31.6          | 10.9          | 344.44                                            |

Table V Comparator result analysis

## Conclusion

In this a Novel Gizmo on carbon nanotube FET having a ternary comparator designs. The comparator implementation uses both ternary and binary logic gates. The proposed design is based on prefix structure and is can easily be scaled for any operand length. The proposed ternary comparator design is designed and simulated using SPICE. Simulations results indicate that the proposed 1-bit comparator consumes  $0.65\mu$ W power and has a delay of 21ps. The result analysis of comparators with different operand lengths is also presented.

## References

[1]M. Mukaidono, "Regular ternary logic functions—Ternary logicfunctions suitable for treating ambiguity," IEEE Trans. Comput., vol. C35,no.2,pp.179–183,Feb.1986.

[2]P. C. Balla and A. Antoniou, "Low power

dissipation MOS ternary logic family," IEEE J.

Solid-State Circuits, vol. 19, no. 5, pp. 739–749, Oct. 1984.

[3]A. Heung and H. T.Mouftah, "Depletion/enhancement CMOS for alower power family of three-valued logic circuits," IEEE J. Solid-State Circuits, vol. 20, no. 2, pp. 609–616, Apr. 1985.

[4]A. Raychowdhury and K. Roy, "Carbonnanotube-based voltage-mode multiple-valued logic design," IEEE Trans. Nanotechnology., vol. 4, no. 2, pp. 168–179, Mar. 2005.

[5]D. A. Rich, "A survey of multivalued memories," IEEE Trans. Computer.,vol. 35, no. 2, pp. 99–106, Feb. 1986.

[6]Y. Yasuda, Y. Tokuda, S. Taima, K. Pak, T. Nakamura, and A. Yoshida, "Realization of quaternary logic circuits by n-channel MOS devices," IEEE J. Solid-State Circuits, vol. 21, no. 1, pp. 162–168, Feb. 1986.

[7]J. Appenzeller, "Carbon nanotubes for highperformance electronics—Progress and prospect," Proc. IEEE, vol. 96, no. 2, pp. 201–211, Feb. 2008.

[8]H. Hashempour and F. Lombardi, "Device model for ballistic CNFETs using the first conducting band," IEEE Des. Test. Comput., vol. 25, no. 2, pp. 178–186, Mar./Apr. 2008.

[9]Sheng Lin; Yong-Bin Kim; Lombardi, F.; , "CNTFET-Based Design of Ternary Logic Gates and Arithmetic Circuits," IEEE Transactions on Nanotechnology, vol.10, no.2, pp.217-225, March 2011.

[10]S. Lin, Y.-B. Kim, and F. Lombardi, "A novel CNTFET-based ternarylogic gate design," in Proc. IEEE Int. Midwest Symp. Circuits Syst., Aug. 2009, pp. 435–438.

[11](2008). Stanford University CNFET model Website. StanfordUniversity, Stanford, CA [Online]. Available:

http://nano.stanford.edu/model.php?id=23

[12]J. Deng and H.-S.P.Wong, "A compact SPICE model for carbon nanotube field-effect transistors including nonidealities and its application — PartI:Model of the intrinsic channel region,"IEEETrans.ElectronDevice,vol.54,no.12,pp .3186–3194,Dec. 2007.

[13]J. Deng and H.-S.P.Wong, "A compact SPICE model for carbonnanotubefield-effect transistors including non idealities and its application— PartII:Full device model and circuit performance bench marking, "IEEETrans. Electron Device, vol.54, no.12, pp.3195–3205, Dec.2007.

[14]Y. Ohno, S. Kishimoto, T. Mizutani, T. Okazaki, and H. Shinohara, "Chirality assignment of individual single-walled carbon nanotubes in carbon nanotube field-effect transistors by microphoto current spectroscopy," Appl. Phys. Lett., vol. 84, no. 8, pp. 1368–1370, Feb.2004.

[15]B.Wang, P. Poa, L.Wei, L. Li, Y. Yang, and Y. Chen, "(n,m) Selectivity of single-walled carbon nanotubes by different carbon precursors on Co–

Mo catalysts," J. Amer. Chem. Soc., vol. 129, no. 9, pp. 9014–9019,2007.

[16]Perri, S.; Corsonello, P.; , "Fast Low-Cost Implementation of Single Clock-Cycle Binary Comparator," *Circuits and Systems II:Express Briefs, IEEE Transactions on*, vol.55 no.12, pp.1239-1243, Dec.2008.

[17]A. P. Dhande and V. T. Ingole, "Design&Implementation of 2-BitTernary ALU slice," in Proc. Int. Conf. IEEE-Sci. Electron., Technol.Inf. Telecommun., Mar. 2005, pp. 17–21.

[18] ChetanVudadha, SaiPhaneendra P, GouthamMakkena, Sreehari V, N Moorthy Muthukrishnan, M B Srinivas Department of EEE,BITS-Pilani, "Digital System Design" IEEE conference, 2012.