International Journal of Science Engineering and Advance Technology, IJSEAT, Vol.3, Issue 7 J

ISSN 2321-6905 July 2015

# International Journal of Science Engineering and Advance Technology

# Configuration as well as Performance of an On-Chip IncarnationArrangement for Multiprocessor System-On-Chip

Badita Kali Vara Prasad, Jeswanth Theza Nadella Dept of ECE K L University, Green Fields, Vaddeswaram, Guntur (DT)

#### Abstract:

The novel on-chip coordinate in silicon indicated course of action to fortify ensured development change in multiprocessor SOC applications. A pipelined circuit-exchanging Employed in the proposed structure with FIFO strategy converged with a multistage system topology in segment way setup game plan. The runtime course strategy connected with by part way setup plan for subjective development changes adjacent the Error Correction Block (ECB). The circuit-exchanging technique offers the permuted information and its humbler overhead draws in the upside of stacking various structures in framework on chip. A CMOS test-chip with 0.13m insists the sound judgment and gainfulness of the proposed outline. The indicated exploratory result in the proposed on-chip system accomplishes 1.9x to 8.2x diminishment of silicon overhead emerged from other setup approaches.

*Index Terms*—Guaranteed throughput, multistage interconnection network, network-on-chip, permutation network, pipelined circuit-switching, traffic permutation.

#### **I.INTRODUCTION:**

The design of a chip is taking into record four particular points of view: figuring, memory, correspondence and I/O. The enlargement of the dealing with force and

the change of information bona fide applications has pulled in certified thought on the test of the correspondence point in single-chip frameworks (SoC). The Potential aftereffects of giving throughput ensures in a system on-chip by true blue development managing. A source facilitating is utilized to courses with indicated throughput for the information streams in a multiprocessor structure on-chip. The thought about the check of controlling, system topology and correspondence locale on the facilitating execution are considered. The outcomes demonstrate that our system for giving throughput confirmations to gushing development is doubled. The correspondence region has the solid in the impact of arranging execution while the directing figuring has feeble in the impact. Accordingly, the mapping figuring is more basic vitality for the structure execution than the organizing calculation and it is beneficial to utilize a more identity boggling mapping check that stick the correspondence locale together with a basic controlling estimation This paper demonstrates a novel outline of an on-chip stage system to sponsorship ensured throughput of permutated traffics under subjective change. Not in the scarcest degree like routine group exchanging techniques, our on-chip structure utilizes a circuitswitching instrument with a dynamic way setup plot under a multistage system topology. The dynamic way setup handles the test of runtime way approach for clash free permuted information. The pre-arranged information ways draw in a throughput ensure. By clear the pointless overhead of covering buffers, the satisfying execution is refined and stacking particular structures to bolster synchronous stages in runtime is doable. Looking over on-chip stage systems (supporting either full or divided change) as to their execution shows that most the structures utilize a bundle changing section to manage the conflict of permuted information. Their utilization either utilize firstenter first-yield (FIFO) lines for the clashing information, or time-opening movement in the general framework with the expense of all the all the all the more organizing stages, or a desires directing with a redirection approach that avoids buffering of the clashing information. The decisions of system configuration variables, i.e., topology, exchanging method and the arranging reckoning, have specific results for the on-chip execution.

#### **II. RELATED WORK:**

As to exchanging strategy, bundle exchanging requires an unnecessary measure of on chip force and region for the lining cradles (FIFOs) with prefigured lining profundity at the exchanging hubs and/or system interfaces. With respect to directing calculation, the diversion steering is not

energyefficient because of the additional jumps required for avoided information exchange, contrasted with a negligible steering. Also, the parcel avoidance makes dormancy less unsurprising; henceforth, it is difficult to ensure the inactivity and the all-together conveyance of information. This paper displays a novel silicondemonstrated outline of an on-chip stage system to backing ensured throughput of permutated traffics under subjective change. Not at all like ordinary bundle exchanging methodologies, our on- chip system utilizes a circuitswitching instrument with a dynamic way setup plot under a multistage system topology. The dynamic way setup handles the test of runtime way game plan for clash free permuted information. The preconfigured information ways empower a throughput ensure. By evacuating the exorbitant overhead of lining cushions, a minimal execution is accomplished and stacking various systems to bolster simultaneous stages in runtime is possible. In our blend approach, we utilize precise defer and force models for the system segments (switches and joins) that are acquired from formats of the segments utilizing industry standard instruments. The combination methodology uses the floor arrangement learning of the NoC (Network on Chip) to identify timing infringement on the NoC interfaces right on time in the configuration cycle. This prompts a speedier outline cycle and faster plan joining over the abnormal state combination approach and the physical usage of the configuration. We approve the outline stream consistency of our proposed approach by performing a design of the NoC for a 25-center CMP. orchestrated Our methodology keeps up the consistent and unsurprising structure of the NoC and is appropriate practically speaking to existing NoC architectures

#### A. The Switch and Network Taxonomy

The switch is the other important component in IIP and has a central function in NoC. Responsible for routing data packets, it implements the network (sending resource-to-receiving resource routing) and link layer (switch-to-switch routing) when receiving a data packet, the switch extracts the header information, makes routing decision based on the header information and current traffic load (to avoid congestion) and performs appropriate action (put the packet onto a link, delay the packet, drop the packet, etc.). So far, the NoC has been described as a communication network based on data packets and the high-level logic function of the switch is routing the packets. For different network cores, different approaches may be used for data packet routing. In the following text, the traditional telecommunications network taxonomy (also apply

on NoC), which determines the low-level architecture and Implementation of the switch will be studied. A traditional telecommunications network either employs circuit or packet switching. A link in a circuit switched network can use either frequency-division multiplexing (FDM) or time division multiplexing (TDM) while packet switched networks are either virtual circuit (VC) networks or datagram networks. This classification can be generalized and apply on any network core, including NoC.

## B. Packet Switching

Depending on the routing method, packet switched networks are divided into virtual circuit networks and datagram networks. The virtual circuit approach is connection-oriented and resembles the circuit switching. Both packet switched VC network and circuit switched network are suitable for uniform data traffic with long lifetime. For other bursty traffic, the connection management will tend to be computationally demanding and occupy a large portion of the bandwidth. They also require that the switches maintain the state information, resulting in more complex switch architecture and signalling scheme between switches. To reduce the switch complexity and therefore also the area overhead, datagram switching can be used. The datagram based switch is state and memory less, each packet is treated independently, with no reference to preceding packets. This approach more easily adapts to changes in the network such as congestion and dead links. However, it does not guarantee that packets with same source and destination will follow the same route. Consequently, the delay of packets with same source and destination may vary and packets may also arrive out of order, requiring buffering element at the receiving end. A datagram based switch implementation is described in.

#### C. Circuit Switching

A circuit switched network requires a dedicated end-to-end circuit (with a guaranteed constant bandwidth) between the transmitting and the receiving end. As the "circuit" is an abstract concept, most of the time, it is not a physical end to end wire, but can span over many links. In a telecommunications network, the circuit is typically implemented with either frequency division multiplexing or time-division multiplexing in each link. With FDM, the frequency spectrum of a link is shared among the connections across the link. For obvious reasons, the FDM is not suitable for NoC. For TDM on the other hand, time is divided into frames of fixed duration, and each frame is divided into a fixed number of time slots. When the network establishes a connection (or circuit) across a TDM link, the network dedicates a certain number of time slots in every frame to the connection. These slots are dedicated for the sole use of that connection, with some time slots available for use (in every frame) to transmit the connections data. The Ethereal Network on Chip developed at Philips Research is based on the timedivision multiplexed circuit switching approach described above.

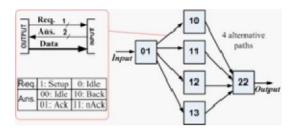

#### III. ON-CHIP NETWORK TOPOLOGY

Clos network, a family of multistage networks, is applied to build scalable commercial multi core processors with thousands of nodes in macro systems. A typical three-stage Clos network is defined as C (n, m, p), where n represents the number of inputs in each of p first stage switches and m is the number of second stage switches. In order to support a parallelism degree of 16 as in most practical MP SoCs, we proposed to use C (4, 4, 4) as a topology for the designed network. This network has a rearrange able property that can realize all possible permutations between its input and outputs. The choice of the three stage Clos network with a modest number of middle stage switches is to minimize implementation cost, whereas it still enables a rearrange able property for the networks. A pipelined circuit switching scheme is designed for use with the proposed network. This scheme has three phases: the setup, the transfer, and the release. A dynamic path setup scheme supporting the runtime path arrangement occurs in the setup phase. In order to support this circuit scheme, switch switch switching а by interconnection with its handshake signals is proposed. The bit format of the handshake includes a 1 bit Request (Req) and a 2 bit Answer (Ans). Req = 1 is used when a switch requests an idle link leading to the corresponding down-stream switch in the setup phase. The Req = 1 is also kept during data transfer along the set up path. A Req = 0denotes that the switch releases the occupied link. This code is used in both the setup and the release phases. An Ans = 01(Ack) means that the destination is ready to receive data from the source. When the Ans = 01 propagates back to the source, it denotes that the path is set up, then a data transfer can be started immediately. An Ans = 11(nAck) is reserved for end to end flow control when the receiving circuit is not ready to receive data due to being busy with other tasks, or overflow at the receiving buffer, etc. An Ans = 10 (Back) means that the link is blocked. This Back code is used for a back pressure flow control of the dynamic path setup scheme.

#### IV. DYNAMIC PATH SETUP TO SUPPORT PATH ARRANGEMENT

A dynamic path setup scheme of the proposed design to support a runtime path arrangement when the permutation is changed. In each path setup, which starts from an input to find a path leading to its corresponding output, is based on a dynamic probing mechanism. The concept of probing is introduced, in which a probe (or setup flit) is dynamically sent under a routing algorithm in order to establish a path towards the destination. The exhausted profitable backtracking (EPB) is proposed to use to route the probe in the network work. A path arrangement with full permutation consists of 16 path setups, whereas a path arrangement with partial permutation may consist of a subset of 16 path setups. A question is that can the proposed EPB based path setups used with the Clos C (4, 4, 4) realize all possible full permutations between its inputs and outputs? As proofed in works, the three stage Clos network C(n, n)m, p) is rearrange able if m>n In the proposed network of C(4, 4, 4) m = n = 4 so it is rearrange able. There will always exist an available path from an idle input leading to an idle output. By the Exhaustive Property of EPB as proofed in work, the EPB based path setup completely searches all the possible paths within the set of path diversity between an idle input and idle output. Directly applying the Exhaustive Property of the search into rearrange able C (4, 4, 4) shows that the EPB based path setup can always find an available path within the set of four possible paths between the input and the idle output. Based on this EPB based path-setup scheme, it is obvious that the path arrangement for full permutation can always be realized in the proposed network with C(4, 4, 4) topology.

Fig.1: Switch by switch interconnection and path diversity capacity

### V.PROPOSED ON-CHIP NETWORK DESIGN

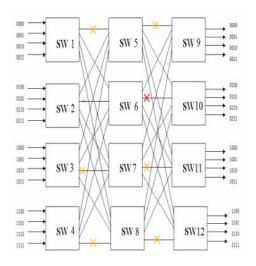

In our system both fault mitigation and data priority can be achieved to develop fault tolerant on chip network Priority network which empowers the router to choose the most suitable packet forwarding path, based on the priority of the router and the current energy status of the forwarding router. Fault detecting Our mitigation technique identify the faults in a router while detect any fault in the path the alternate router will be selected for data transmission to ensure the guaranteed data Fault-tolerance or graceful degradation is the property enables that а system (often computerbased) to continue operating properly in the event of the failure of (or one or more faults within) some of its component. If its operating quality reduce at all, the reduce is proportional to the severity of the act of failing a breakdown, as compared to a naïvelydesigned system in which even a small failure can cause total breakdown. Fault-tolerance is particularly sought-after in highavailability or life-critical systems. Recovery from errors in fault-tolerant systems can be characterized as either rollforward or roll-back. When the system detects that it has made an error, roll-forward recovery takes the system state at that time and corrects it, to be able to move forward. Within the scope of an individual system, fault-tolerance can be achieved by anticipating exceptional conditions and building the system to cope with them, and, in general, aiming for selfstabilization so that the system converges towards an error-free state. However, if the consequences of a system failure are catastrophic, or the cost of making it sufficiently reliable is very high, a better solution may be to use some form of duplication. In any case, if the consequence of a system failure is so catastrophic, the system must be able to use reversion to fall back to a safe mode. This is similar to rollback recovery but can be a human action if humans are present in the loop. In addition, fault tolerant systems are characterized in terms of both planned service outages and unplanned service outages. These are usually measured at the application level and not just at a hardware level.

Fig.2: PROPOSED SOC

In above NOC, switch 6 is affected by fault. It change the routing path automatically to switch 7

when try to access switch 7 by fault detecting mechanism.

#### VI. NETWORK ON CHIP (NoC)

Network-on-chip or network-on-a-chip (NoC or NOC) is an approach to designing the communication subsystem between IP cores ina system-on-a-chip (SoC). NoCs can span synchronous and asynchronous clock domains or use un clocked asynchronous logic. NoC applies networking theory and methods to on-chip communication and brings notable improvements over conventional bus and crossbar interconnections.NoC improves the scalability of SoCs, and the power efficiency of complex SoCs comprising an optical network-on-chip (NoC). Groinetal.call "the layered-stack approach to the design of the on-chip inters core communications the network-on-chip (NOC) methodology". In a Noc system, modules such as processor cores, memories and specialized IP blocks exchange data using a network as a "public transportation" subsystem for information traffic. A NoC is constructed from multiple point-to-point data links interconnected by switch (a,k.a. routers), such that messages can relayed from any source module to any destination module over several links, by making routing decisions at the switches. A NoC is similar to a modern telecommunications network. using digital bit-packet switching over multiplexed links. Although packet-switching is sometimes claimed as necessity for a NoC, there are several NoC proposals utilizing circuitswitchingtechniques. This definition based on routers is usually interpreted so that a single shared bus, a single crossbar switch or a point-to-point network are not NoCs but practically all other topologies are. This is somewhat confusing since all above mentioned are networks (they enable communication between two or more devices) but they are not considered as network-on-chips. Note that some articles erroneously use NoC as a synonym for mesh topology although NoC paradigm does not dictate the topology. Likewise, the regularity of topology is sometimes considered as a requirement which is, obviously, not the case in research concentrating on "application-specific NoC topology synthesis".

#### VII.Multiplexer

In electronics, a multiplexer (or MUX) is a device that selects one of several analog or digital input signals and forward the selected input into a single line. A multiplexer of 2ninputs has n select lines, which are used to select which input line to send to the output. Multiplexers are mainly used to increase the amount of data that can be sent over the network within a certain amount of time and bandwidth. A multiplexer is also called a selector. An electronic multiplexer makes it possible for several signals to share one device or resource, for example one A/D converter or one communication line, instead of having one device per input signal. A data selector, more commonly called a Multiplexer, shortened to "Mux" or "MPX", are combinational logic switching devices that operate like a very fast acting multiple position rotary switches. They connect or control, multiple input lines called "channels" consisting of either 2, 4, 8 or 16 individual inputs, one at a time to an output. Then the job of a multiplexer is to allow multiple signals to share a single common output. For example, a single 8-channel multiplexer would connect one of its eight inputs to the single data output. Multiplexers are used as one method of reducing the number oflogic gates required in a circuit or when a single data line is required to carry two or more different digital signals.

#### VIII. RESULTS AND DISCUSSION:

Fig.3: Simulated Environment

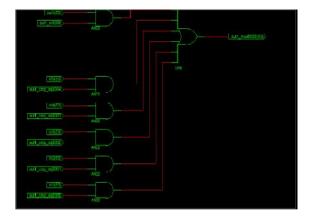

Fig.4: Simulation Results of Arbiter

The simulation waveform of the arbiter is as shown above in fig of R(4:0) shows the input for arbiter

which consists of controls signals from input circuit. Were credit and G(4:0) indicates the credit signals and grant signals respectively along with these control signals there are some deciding input signals for the arbiter which are reset and clock with the next-p signal for the next registers.

#### **IX. CONCLUSION:**

This paper has presented an on-chip network design supporting traffic permutations in MPSoC applications. By using a circuit-switching approach combined with dynamic path-setup scheme under a Clos network topology, the proposed design offers arbitrary traffic permutation in runtime with compact implementation overhead. A siliconproven test-chip validates the proposed design and suggests availability for use as an on-chip infrastructure-IP supporting traffic permutation in future MPSoC researches. On chip network design supporting traffic permutations in MPSoC applications. By using a circuit switching approach combined with dynamic path setup scheme under a Clos network topology, the proposed design offers arbitrary traffic permutation in runtime with compact implementation overhead. A silicon proven test chip validates the proposed design and suggests availability for use as an on-chip infrastructure-IP supporting traffic permutation in future MPSoC researches.

#### **REFERENCES:**

[1] S. Borkar, "Thousand core chips—A technology perspective," in Proc. ACM/IEEE Design Autom. Conf. (DAC), 2007, pp. 746–749.

[2] P.-H. Pham, P. Mau, and C. Kim, "A 64-PE folded-torus intra-chip communication fabric for guaranteed throughput in network-on-chip based applications," in Proc. IEEE Custom Integr. Circuits Conf.(CICC), 2009, pp. 645–648.

[3] C. Neeb, M. J. Thul, and N.Wehn, "Networkon-chipcentric approach to interleaving in high throughput channel decoders," in Proc. IEEE Int.Symp. Circuits Syst. (ISCAS), 2005, pp. 1766– 1769.

[4] H. Moussa, A. Baghdadi, and M. Jezequel, "Binary de Bruijn on-chip network for a flexible multiprocessor LDPC decoder," in Proc. ACM/IEEE Design Autom. Conf. (DAC), 2008, pp. 429–434.

[5] H. Moussa, O. Muller, A. Baghdadi, and M. Jezequel, "Butterfly and Benes-based on-chip communication networks for multiprocessor turbo decoding," in Proc. Design, Autom. Test in Euro. (DATE), 2007, pp. 654–659.

[6] S. R. Vangal, J. Howard, G. Ruhl, S. Dighe, H. Wilson, J. Tschanz, D. Finan, A. Singh, T. Jacob, S. Jain, V. Erraguntla, C. Roberts, Y. Hoskote, N. Borkar, and S. Borkar, "An 80-tile sub-100-w TeraFLOPS processor in 65- nm CMOS," IEEE J. Solid-State Circuits, vol. 43, no. 1, pp. 29–41, Jan. 2008.

[7] W. J. Dally and B. Towles, Principles and Practices of Interconnection Networks: San Francisco, CA: Morgan Kaufmann, 2004.

[8] N. Michael, M. Nikolov, A. Tang, G. E. Suh, and C. Batten, "Analysis of application-aware onchip routing under traffic uncertainty," in Proc.IEEE/ACM Int. Symp. Netw. Chip (NoCS), 2011, pp. 9–16.

[9] P.-H. Pham, J. Park, P. Mau, and C. Kim, "Design and implementation of backtrackingwavepipeline switch to support guaranteed throughput in network-on-chip," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 10.1109/TVLSI.2010.2096520.

[10] D. Ludovici, F. Gilabert, S. Medardoni, C. Gomez, M. E. Gomez, P. Lopez, G. N. Gaydadjiev, and D. Bertozzi, "Assessing fat-tree topologies for regular network-on-chip design under nanoscale technology constraints," in Proc. Design, Autom. Test Euro. Conf. Exhib. (DATE), 2009, pp. 562–565.

[11] Y. Yang and J.Wang, "A fault-tolerant rearrangeable permutation network," IEEE Trans. Comput., vol. 53, no. 4, pp. 414–426, Apr. 2004.

[12] P. T. Gaughan and S. Yalamanchili, "A family of faulttolerant routing protocols for direct multiprocessor networks," IEEE Trans. ParallelDistrib. Syst., vol. 6, no. 5, pp. 482–497, May 1995. [13] V. E. Bene's, Mathematical Theory of Connecting Networks and Telephone Traffic. New York: Academic Press, 1965.

[14] S. Talapatra, H. Rahaman, and J. Mathew, "Low complexity digit serial systolic montgomery multipliers for special class of," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 18, no. 5, pp. 847–852, May 2010.

[15] T. Itoh and S. Tsujii, "Structure of parallel multipliers for a class of fields ," Inform. Computation, vol. 83, no. 1, pp. 21–40, 1989.

[16] C. Negre, "Quadrinomial modular arithmetic using modified polynomial basis," in Proc. ITCC, 2005, pp. 550–555.

[17] Z. Chen, M. Jing, J. Chen, and Y. Chang, "New viewpoint of bit-serial/ parallel normal basis multipliers using irreducible all-one polynomial," in Proc. ISCAS, 2006, pp. 1499–1502.

[18] C.-Y. Lee, C. W. Chiou, J. M. Lin, and C. C. Chang, "Scalable and systolic montgomery multiplier over generated by trinomials," IET Circuits Dev. Syst., vol. 1, no. 6, pp. 477–484, 2007.

#### Authors:

1.**Mr. Badita KaliVara Prasad**wasborn in Andhra Pradesh, India. Hereceived the M.Tech degreein Digital Systems and Computer Electronics from Rajeev Gandhi Memorial College of Engineering and technology, Nandyal, Kurnool, He is pursuing

Ph. D from JNT University, Hyderabad. He is working as an Assistant Professor in KL University, Green fields, Vaddeswaram, Guntur (DT), Andhra Pradesh

Mr. Jeswanth Theza Nadella was born in Andhra Pradesh, India. He received B. Tech Degree in Electronics and Communications from Audisankara College of Engineering and Technology, Gudur, Nellore (DT). He is

pursuing M. Tech Degree in VLSI from KL UniversityGreen fields, Vaddeswaram, Guntur (DT), Andhra Pradesh.