# POLITECNICO DI TORINO Repository ISTITUZIONALE

A mixed-signal ASIC for time and charge measurements with GEM detectors

| Original A mixed-signal ASIC for time and charge measurements with GEM detectors / Cossio, Fabio (2019 Jul 19), pp. 1-199.              |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Availability: This version is available at: 11583/2743335 since: 2019-07-25T09:17:54Z                                                   |

| Publisher: Politecnico di Torino                                                                                                        |

| Published DOI:                                                                                                                          |

| Terms of use: openAccess                                                                                                                |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository |

|                                                                                                                                         |

| Publisher copyright                                                                                                                     |

|                                                                                                                                         |

|                                                                                                                                         |

| (Article begins on next page)                                                                                                           |

04 August 2020

### **Doctoral Dissertation**

Doctoral Program in Electrical, Electronics and Communications Engineering, with curriculum in "Electronic Devices" in convention with the National Institute for Nuclear Physics (31<sup>st</sup> cycle)

# A mixed-signal ASIC for time and charge measurements with GEM detectors

Fabio Cossio

**Supervisors**

Prof. Angelo Rivetti, Supervisor, Turin INFN

Dr. Manuel Dionisio Da Rocha Rolo, Co-supervisor, Turin INFN

Prof. Michele Goano, Co-supervisor, Turin Polytechnic

#### **Doctoral Examination Committee:**

Prof. Stefania Beolè, Referee, Turin University of Physics Prof. Alessandro Gabrielli, Referee, Bologna University of Physics

> Politecnico di Torino 2019

| This thesis is licensed under a Creative Commons License, Attribution - Noncommercial-NoDerivative Works 4.0 International: see www.creativecommons.org. The text may be reproduced for non-commercial purposes, provided that credit is given to the original |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I hereby declare that, the contents and organisation of this dissertation constitute my own original work and does not compromise in any way the rights of third parties, including those relating to the security of personal data.                           |

| Fabio Cossio<br>Turin, June 19, 2019                                                                                                                                                                                                                           |

# Summary

A novel lightweight detector based on CGEM (Cylindrical Gas Electron Multiplier) technology has been developed to replace the aging inner tracker of the BESIII Spectrometer, an experiment carried out at the Beijing Electron Positron Collider in China. The CGEM-IT (CGEM Inner Tracker) consists of three independent layers of cylindrical GEM and, thanks to its fast response, low material budget, high rate capability and excellent radiation tolerance, will provide an improved spatial resolution along the beam axis and the required performance for the entire experiment lifetime. In order to face the unprecedented challenge of achieving high level tracking performance in a strong magnetic field (1 T) with a cylindrical GEM detector, an analogue readout, implementing charge centroid and  $\mu$ TPC (micro Time Projection Chamber) reconstruction algorithms, has been adopted. Compared to a binary readout, this approach allows to reduce the total number of channels to about 10000 which are readout by a dedicated Application Specific Integrated Circuit (ASIC) providing simultaneous measurement of the input signals time-of-arrival and deposited charge.

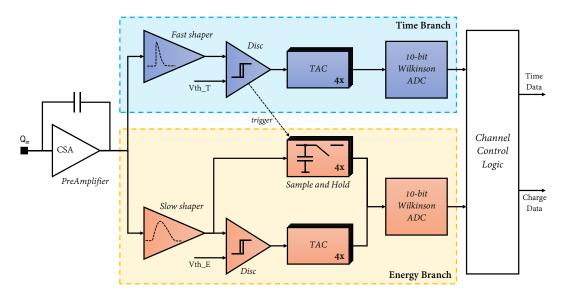

The chip comprises 64 independent channels, each of which featuring an analogue front-end for signal amplification and conditioning followed by a versatile back-end for the digitization of the event timestamp and input charge. The design of the analogue front-end has been driven by the requirements set by the detector. The ASIC is thus optimized for the readout of signals up to 50 fC, with a maximum event rate of 60kHz per channel and a noise below 2000 electrons r.m.s. for an input capacitance up to 100 pF. A dual-branch architecture, with different peaking time shapers, is employed in order to provide time and charge measurement with the required resolution. The event timestamp is digitized by low-power, quad-buffered TDCs, based on analogue interpolation, delivering a sub-50 ps time binning. In default operation mode, the charge information is extracted by a Sample-and-Hold (S&H) circuit, working as a digitally-controlled peak detector, that allows to capture the voltage peak at the output of the slower shaper. This value is then digitized by a 10-bit Wilkinson ADC which is shared with the TDCs.

In order to extend the input dynamic range and overcome the potential saturation of the measurement provided by the S&H circuit, the charge information can also be inferred from the Time-over-Threshold measurement. The ASIC has been fabricated in a cost-effective and well-established 110 nm CMOS technology node, which is largely adopted for radiation detection in particle physics. A first silicon iteration allowed to fully characterize the chip and correct some design weaknesses before the ASIC was submitted for the mass production. In view of the 2020 installation, integration tests with the CGEM-IT detector coupled with the full-chain readout electronics are now ongoing.

This thesis describes and discusses the design and characterization of a mixed-signal ASIC for the readout of the CGEM-IT and is organized as follows.

Chapter 1 reports a brief description about the BESIII experiment, discussing some details of the detector system and providing some motivations for the CGEM-IT upgrade. The main features and innovations of the CGEM-IT project are described. Moreover, an overview of the full-chain readout electronics is given.

The basic features of a typical front-end ASIC for a particle detector are described in Chapter 2. The main building blocks of the system are discussed, following the signal path: after its formation in the sensor, the signal is amplified and shaped by the analogue front-end and then, before being transmitted off-chip, discriminated and, eventually, digitized. In the last part of this chapter several readout architectures are illustrated, providing for some of them an example of practical implementation.

In Chapter 3 the design and functionality of each block of the ASIC described in this thesis, from the analogue front-end amplifier to the digital controller, are discussed in detail and supported by computer simulations results. Chapter 4 presents the results from the ASIC electrical characterization, showing its full functionality, and from two beam tests which have been carried out to confirm the suitability of this chip for the readout of GEM detectors.

**KEYWORDS**: ASIC; Readout electronics; Mixed-signal design; Charge and time measurement; BESIII; GEM.

# Acknowledgements

This thesis would not have been possible without the support of many people. Looking back at these three eventful years, I can say that I am extremely proud and enthusiastic about the path that I have taken and here I want to express my sincere gratitude towards all who contributed.

First and foremost, I would like to thank my supervisor, Angelo Rivetti, for his precious teachings and guidance throughout my doctoral studies. A special thanks goes to my co-supervisor, Manuel Rolo, for his mentorship. His positive attitude and encouragements helped me to improve myself, showing me the importance of hard work.

I am grateful also to the whole Turin BESIII group, in particular Marco Mignone and Richard Wheadon for their contribution in the development of the DAQ system; their incredible ability and expertise made possible the results presented in this thesis. Thanks to Michela Greco for coordinating the CGEM-IT electronics group and Alberto for his impressive help during the test and integration phase. Last but not least, thanks to Marco Maggiora for making this international collaboration possible, which allowed me to travel during these years across four continents.

Thanks to all the *Ufficio\_VLSI* members: Federico, Jonhatan and Serena for welcoming me when I joined this group and the useful advices they gave from the very first day; Ramshan, Simona, Weishuai, Alejandro, Lorenzo and Raffaele for enlarging the group and helping to build a friendly work environment in which each of us could enhance their professional skills.

I would like to extend my gratitude to all other people that I have not mentioned here with whom I have had the pleasure to work during these years. I sincerely hope that I have never missed to say thank you in the respective situations. Finally, thanks to my parents and my grandmother for always believing and supporting me during these years.

The research leading to these results has been performed within the BESIIICGEM Project (645664), funded by the European Commission in the call H2020-MSCA-RISE-2014.

# **Contents**

| Li | st of | Tables  |                                             | XIII |

|----|-------|---------|---------------------------------------------|------|

| Li | st of | Figures | S                                           | xiv  |

| 1  | Intr  | oductio | on                                          | 1    |

|    | 1.1   | The Bl  | ESIII Experiment                            | . 1  |

|    |       | 1.1.1   | BESIII detector                             | . 2  |

|    |       | 1.1.2   | BESIII trigger and DAQ systems              | . 3  |

|    | 1.2   | The C   | GEM-IT project                              | . 5  |

|    |       | 1.2.1   | Gas Electron Multiplier detectors           | . 6  |

|    |       | 1.2.2   | The CGEM-IT detector                        | . 8  |

|    |       | 1.2.3   | Overview of the CGEM-IT readout electronics | . 13 |

| 2  | Rea   | dout A  | SICs for radiation sensors                  | 23   |

|    | 2.1   | Signal  | l amplification and conditioning            | . 24 |

|    |       | 2.1.1   | Signal formation                            | . 24 |

|    |       | 2.1.2   | Input stage                                 | . 27 |

|    |       | 2.1.3   | Pulse shaping                               | . 31 |

|    |       | 2.1.4   | Baseline stabilization                      | . 35 |

|    |       | 2.1.5   | Noise                                       | . 36 |

|    | 2.2   | Reado   | out Architectures                           | . 42 |

|    |       | 2.2.1   | Binary readout                              | . 42 |

|    |       | 2.2.2   | Counting architectures                      | . 45 |

|    |       | 2.2.3   | Timing measurements                         | . 45 |

|    |       | 2.2.4   | Sample-and-Hold and peak detectors          | . 48 |

|    |       | 2.2.5   | Analogue memories                           | . 49 |

| 3 | TIG  | ER ASI         | (C                                        | 53  |

|---|------|----------------|-------------------------------------------|-----|

|   | 3.1  | Motiva         | ation and requirements                    | 53  |

|   | 3.2  | Chann          | nel architecture                          | 55  |

|   |      | 3.2.1          | Measurement concept                       | 57  |

|   |      | 3.2.2          | Input stage                               | 59  |

|   |      | 3.2.3          | Shaper stage                              | 67  |

|   |      | 3.2.4          | Discriminators                            | 79  |

|   |      | 3.2.5          | Analogue TDCs                             | 83  |

|   |      | 3.2.6          | Sample-and-Hold circuit                   | 86  |

|   |      | 3.2.7          | Channel controller                        | 89  |

|   |      | 3.2.8          | Full-channel simulations                  | 89  |

|   | 3.3  | Other          | structures                                | 93  |

|   |      | 3.3.1          | Global controller                         | 94  |

|   |      | 3.3.2          | Test pulse calibration circuitry          | 97  |

|   |      | 3.3.3          | ASIC Biasing                              | 99  |

|   |      | 3.3.4          | Debug outputs                             | 102 |

|   |      | 3.3.5          | Power distribution                        | 103 |

|   | 3.4  | ASIC l         | layout                                    | 104 |

|   | 3.5  | Perfor         | mance summary                             | 106 |

|   |      | 3.5.1          | Noise                                     | 106 |

|   |      | 3.5.2          | Jitter                                    | 107 |

|   |      | 3.5.3          | Time Walk                                 | 108 |

| 4 | Tool | results        |                                           | 111 |

| 4 | 4.1  |                |                                           |     |

|   | 4.1  | 4.1.1          | etup                                      |     |

|   |      |                | DAQ system                                |     |

|   |      | 4.1.2<br>4.1.3 | - •                                       |     |

|   | 4.2  |                | Data analysis software                    |     |

|   | 4.2  | 4.2.1          | Front-End response                        |     |

|   |      | 4.2.1          |                                           |     |

|   |      | 4.2.3          | Timing performance                        |     |

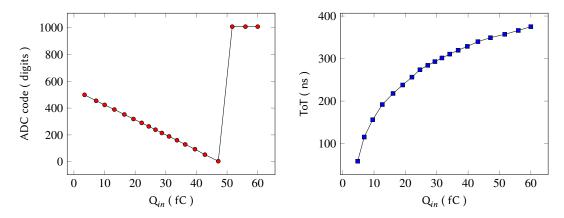

|   |      | 4.2.4          | Charge measurement                        |     |

|   | 4.3  |                | tector electronics assembly               |     |

|   | 4.3  | 4.3.1          | Charge and Time measurement calibration   |     |

|   |      | T.J.I          | Charge and this incasultinent callulation | 134 |

|    | 4.4                           | Testin     | g of GEM detectors with TIGER          | 136         |  |  |

|----|-------------------------------|------------|----------------------------------------|-------------|--|--|

|    |                               | 4.4.1      | Test beam with planar GEMs             | 136         |  |  |

|    |                               | 4.4.2      | Readout of the CGEM-IT                 | 142         |  |  |

| 5  | Sum                           | ımary a    | and Outlook                            | 149         |  |  |

| A  | Opti                          | imizati    | on of the Shaper-Baseline Holder stage | <b>15</b> 3 |  |  |

| В  | TIGER configuration registers |            |                                        |             |  |  |

| C  | Fron                          | nt-End     | Board pinout                           | 167         |  |  |

| Gl | ossar                         | · <b>y</b> |                                        | 171         |  |  |

# **List of Tables**

| 1.1  | Design specifications for the CGEM-11                        | 9   |

|------|--------------------------------------------------------------|-----|

| 3.1  | Design specifications of the TIGER ASIC                      | 55  |

| 3.2  | Relevant operating point and parameters of the pre-amplifier | 65  |

| 3.3  | Shaper stage design values                                   | 71  |

| 3.4  | Trigger logic configuration registers                        | 81  |

| 3.5  | Trigger_T register                                           | 82  |

| 3.6  | Trigger_E register                                           | 82  |

| 3.7  | Trigger_Q register                                           | 82  |

| 3.8  | Trigger_B register                                           | 82  |

| 3.9  | TDC design values                                            | 84  |

| 3.10 | Trigger mode register                                        | 89  |

| 3.11 | Event word content                                           | 95  |

| 3.12 | Counter modes                                                | 96  |

| 3.13 | TIGER output words                                           | 97  |

| 3.14 | Digital outputs for debug purposes                           | 102 |

| 3.15 | TIGER ASIC specifications                                    | 110 |

| A.1  | BLH PVT corners simulation results                           | 159 |

| B.1  | Global configuration register content                        | 162 |

| B.2  | Channel configuration register content                       | 163 |

# **List of Figures**

| 1.1  | Aerial view of BEPCII and BESIII                    | 1  |

|------|-----------------------------------------------------|----|

| 1.2  | The BESIII detector                                 | 3  |

| 1.3  | Data flow diagram of the L1 and L3 trigger          | 4  |

| 1.4  | Block diagram of the L1 trigger system              | 4  |

| 1.5  | MDC gain loss in the 10-year BESIII operation       | 6  |

| 1.6  | Details of a GEM foil                               | 6  |

| 1.7  | Signal formation inside a triple-GEM detector       | 7  |

| 1.8  | 3D view of the CGEM detector mechanical drawings    | 8  |

| 1.9  | Schematic view of the BESIII Cylindrical triple-GEM | 8  |

| 1.10 | XV strips layout                                    | 9  |

| 1.11 | Representation of the charge centroid algorithm     | 11 |

| 1.12 | Representation of the $\mu TPC$ algorithm           | 11 |

| 1.13 | $\mu TPC$ algorithm principle of operation          | 12 |

| 1.14 | Triple-GEM spatial resolution                       | 13 |

| 1.15 | General scheme of CGEM-IT electronics               | 13 |

| 1.16 | Front-End Board design for the CGEM-IT Layer 1      | 14 |

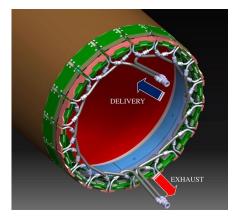

| 1.17 | 3D view representation of the cooling system        | 15 |

| 1.18 | Space allocation for the Front-End Boards           | 15 |

| 1.19 | FEBs size comparison for the different layers       | 15 |

| 1.20 | GEMROC module                                       | 16 |

| 1.21 | GEMROC module hardware and firmware block diagrams  | 17 |

| 1.22 | GEMROC Trigger-Matched data flow architecture       | 18 |

| 1.23 | Advanced Trigger Logic Board                        | 20 |

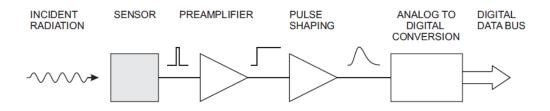

| 2.1  | Main blocks of a radiation detection system         | 23 |

| 2.2  | General scheme of an ionization chamber             | 25 |

| 2.3  | Signal collection with negative HV                  | 26 |

| 2.4  | Charge Sensitive Amplifier (CSA) schematics         | 27 |

| 2.5  | CSA pulses pile-up                                                      | 31 |

|------|-------------------------------------------------------------------------|----|

| 2.6  | Simpler CR-RC shaper implementation                                     | 32 |

| 2.7  | Implementation of a CR-RC shaper                                        | 33 |

| 2.8  | Baseline drift induced by a train of pulses                             | 35 |

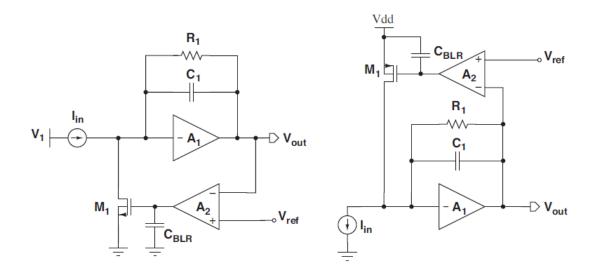

| 2.9  | Baseline holder principle of operation                                  | 36 |

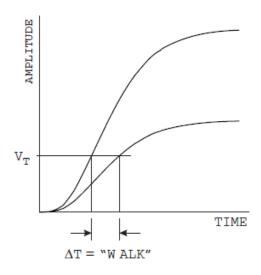

| 2.10 | Time walk effect for signals of different amplitude                     | 41 |

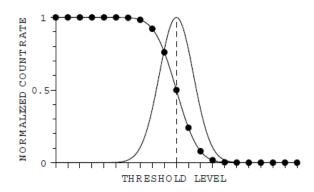

| 2.11 | Typical S-curve produced by a threshold scan                            | 43 |

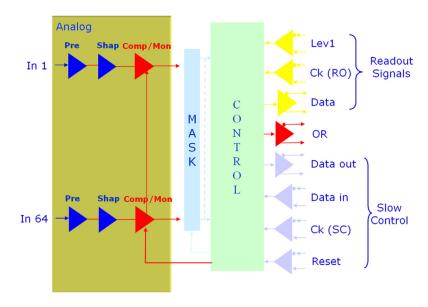

| 2.12 | GASTONE architecture block diagram                                      | 44 |

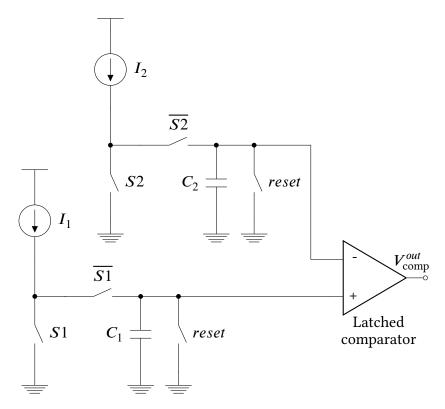

| 2.13 | TDC based on analogue interpolation                                     | 46 |

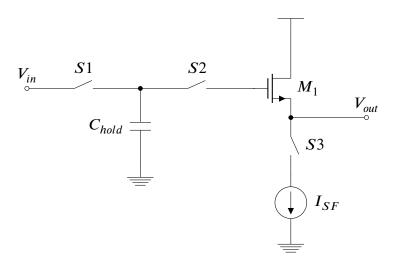

| 2.14 | Principle of operation of a Sample-and-Hold circuit                     | 49 |

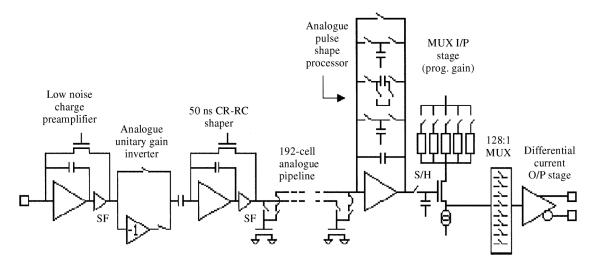

| 2.15 | APV25 architecture block diagram.                                       | 51 |

| 3.1  | TIGER channel architecture scheme                                       | 56 |

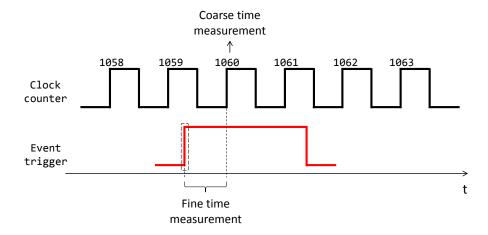

| 3.2  | Time measurement concept                                                | 57 |

| 3.3  | Charge measurement concept in ToT mode                                  | 58 |

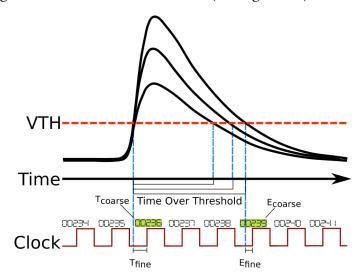

| 3.4  | Charge measurement concept in S&H mode                                  | 59 |

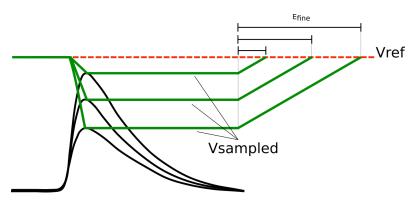

| 3.5  | S&H and ToT charge measurement comparison                               | 59 |

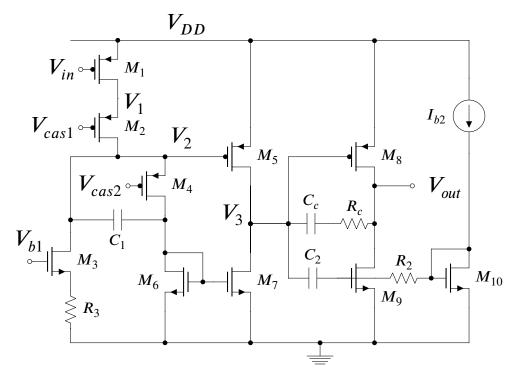

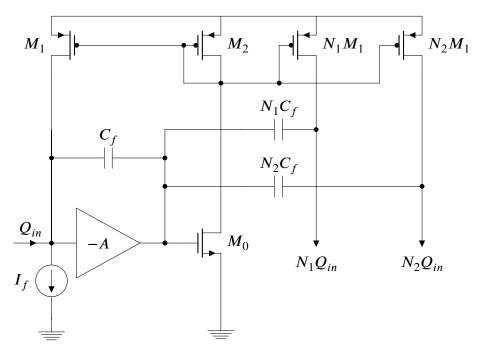

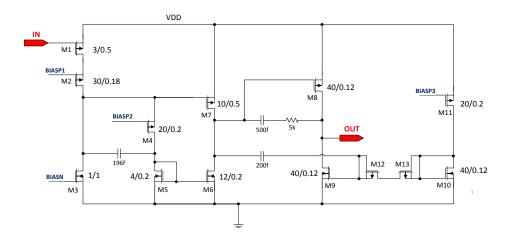

| 3.6  | Schematic of the CSA core amplifier                                     | 6( |

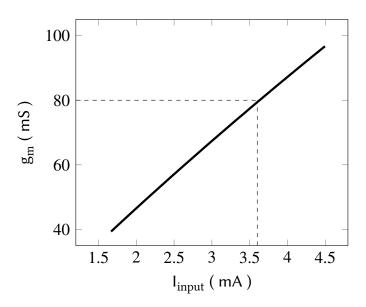

| 3.7  | Computer simulation of the input transistor transconductance as a func- |    |

|      | tion of the bias current                                                | 61 |

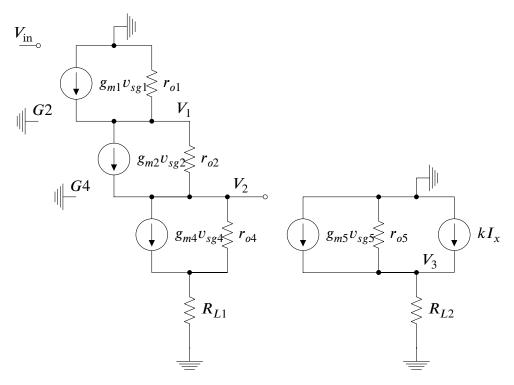

| 3.8  | Small signal model of the first two stages of the core amplifier        | 63 |

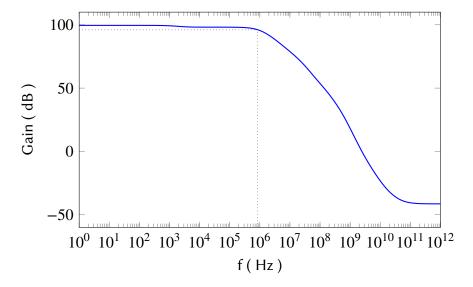

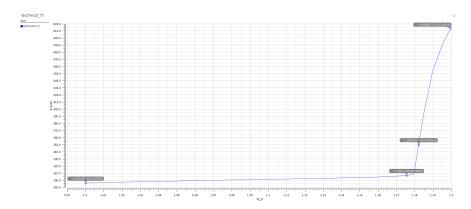

| 3.9  | Frequency response of the open-loop amplifier                           | 65 |

| 3.10 | Pre-amplifier stage with transconductance feedback implemented with     |    |

|      | current mirrors                                                         | 66 |

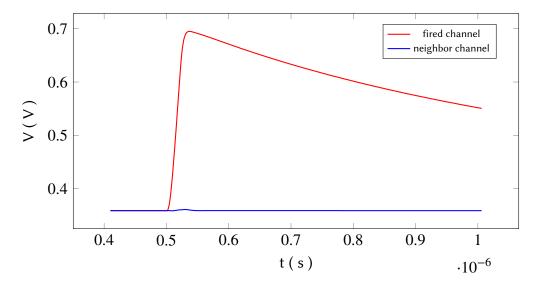

| 3.11 | Computer simulation of the cross-talk effect                            | 67 |

| 3.12 | Shaper with four complex conjugate poles used in the energy branch • 6  | 69 |

| 3.13 | CR-RC shaper in the timing branch                                       | 7( |

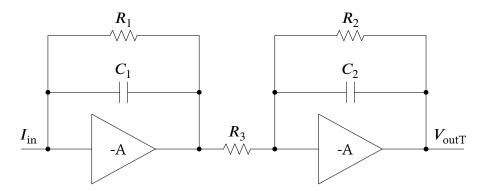

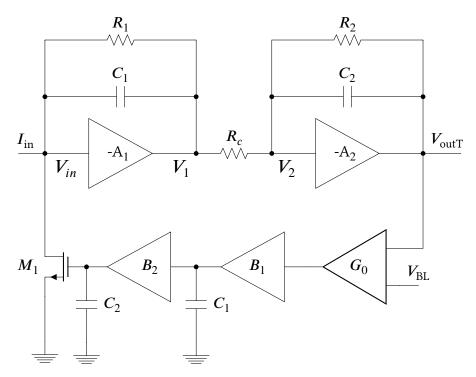

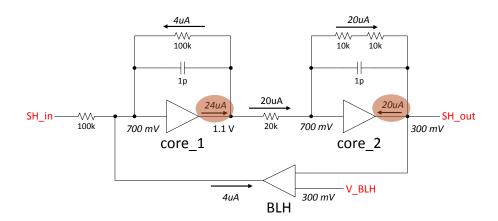

| 3.14 | Block diagram of the baseline holder                                    | 7( |

| 3.15 | Time branch shaper with BLH                                             | 71 |

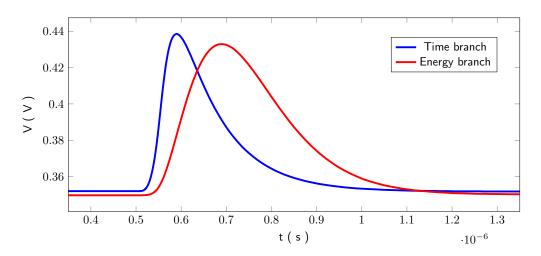

| 3.16 | Simulation of the time and energy branch response                       | 73 |

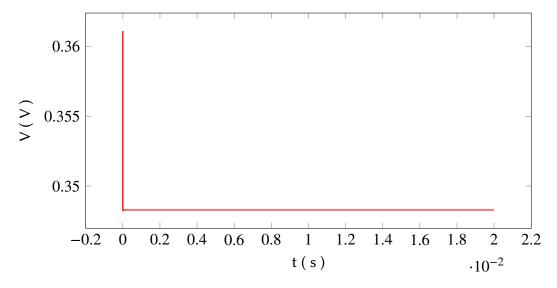

| 3.17 | 20 ms simulation of the energy branch shaper output to assess the cor-  |    |

|      | rect return to baseline.                                                | 73 |

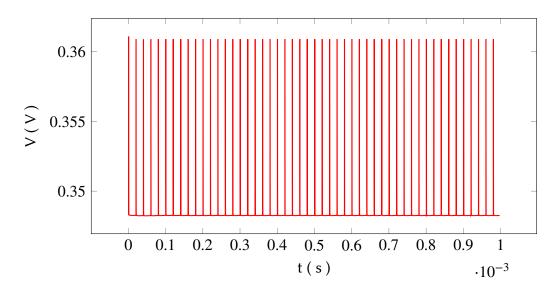

| 3.18 | Energy branch shaper baseline drift simulation at 50 kHz event rate     | 74 |

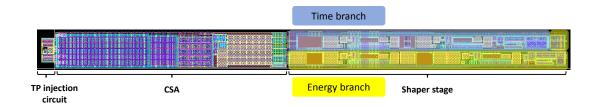

| 3.19 | Layout of the analogue front-end                                        | 74 |

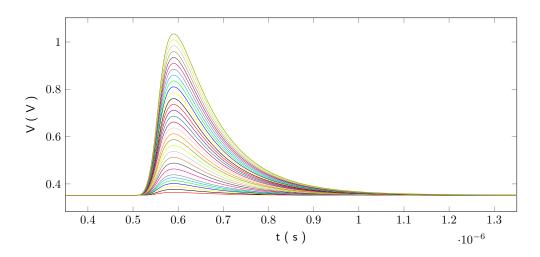

| 3.20 | Time branch output for input signals from 1 fC to 55 fC                 | 75 |

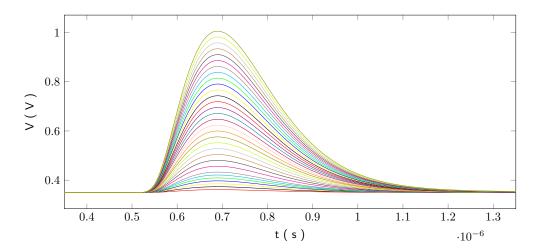

| 3.21 | Energy branch output for input signals from 1 fC to 55 fC               | 75 |

| 3.22 | Time branch gain and linearity.                                             | 76  |

|------|-----------------------------------------------------------------------------|-----|

| 3.23 | Energy branch gain and linearity.                                           | 77  |

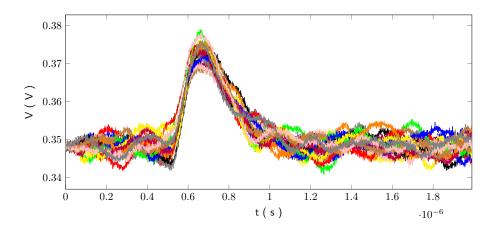

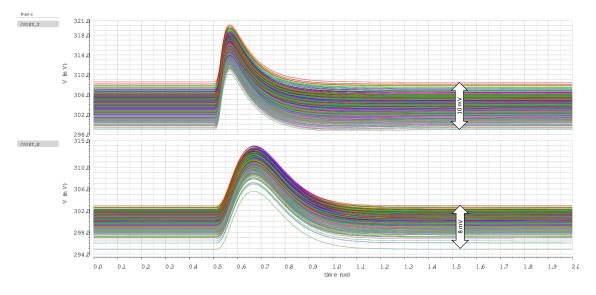

| 3.24 | Time branch output for a 2.5 fC input signal (20 iterations)                | 78  |

| 3.25 | Energy branch output for a 2.5 fC input signal (20 iterations)              | 78  |

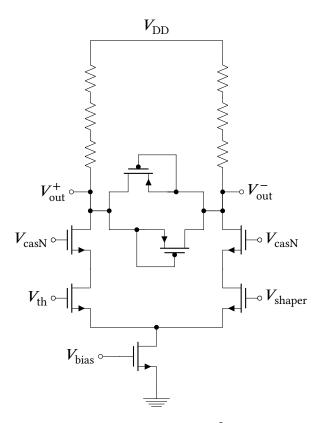

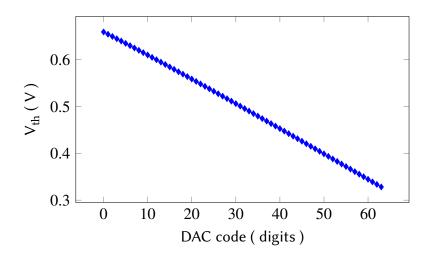

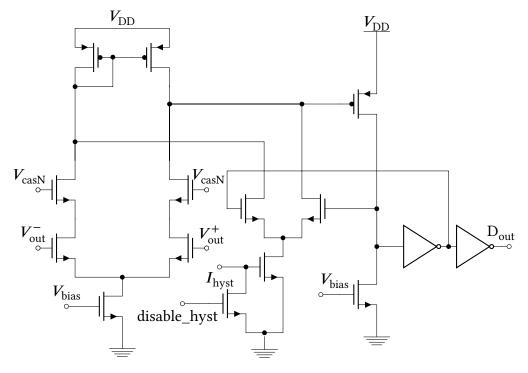

| 3.26 | Discriminator first stage                                                   | 79  |

| 3.27 | Linearity of the DAC used to generate the discriminator threshold           | 80  |

| 3.28 | Discriminator second stage                                                  | 80  |

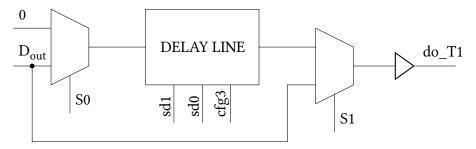

| 3.29 | Delay line                                                                  | 81  |

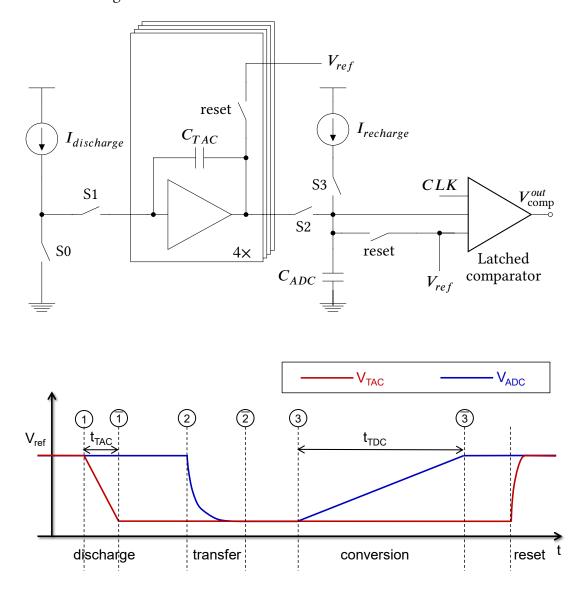

| 3.30 | TDC block diagram and principle of operation                                | 83  |

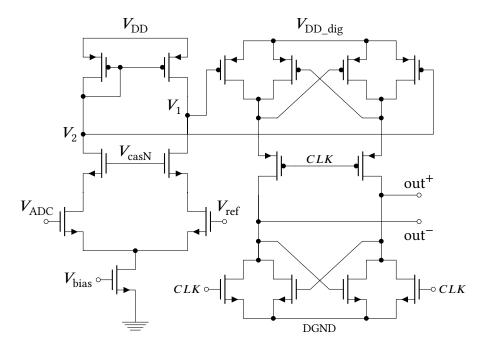

| 3.31 | Latched comparator (simplified version)                                     | 85  |

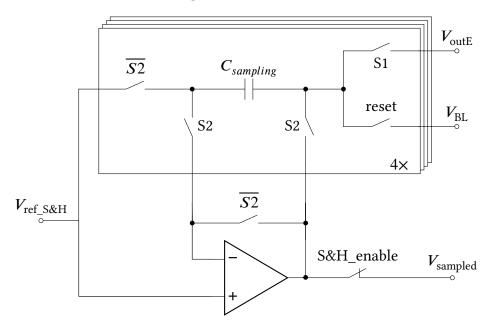

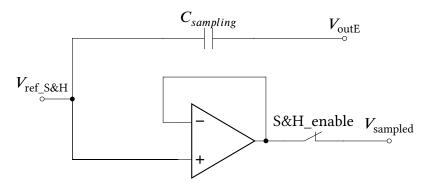

| 3.32 | Block diagram of the S&H circuit                                            | 86  |

| 3.33 | S&H circuit: sample phase                                                   | 87  |

| 3.34 | S&H circuit: hold phase.                                                    | 87  |

| 3.35 | Simulation of the S&H time walk error                                       | 88  |

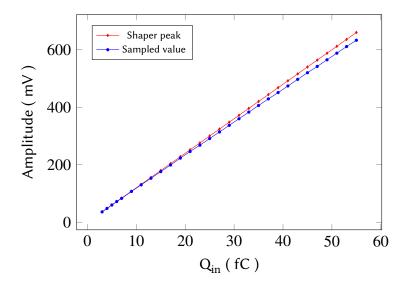

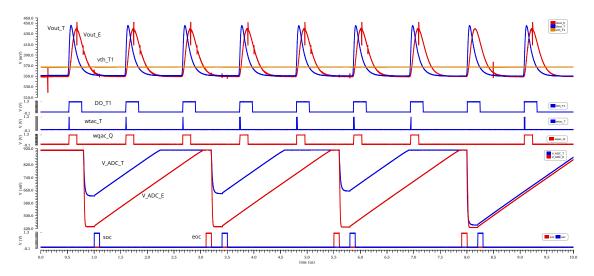

| 3.36 | Simulation of one event in S&H mode                                         | 90  |

| 3.37 | Simulation of the channel response to an event rate $\sim$ 1 MHz            | 91  |

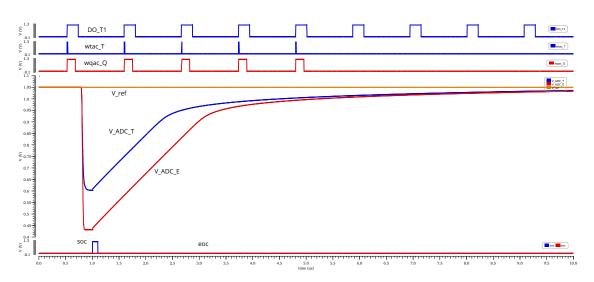

| 3.38 | Channel simulation with $V_{ref}$ = 1.05 V                                  | 92  |

| 3.39 | Layout of the mixed-signal backend of one TIGER channel                     | 93  |

| 3.40 | Block diagram representation of TIGER architecture                          | 93  |

| 3.41 | Global controller interface                                                 | 94  |

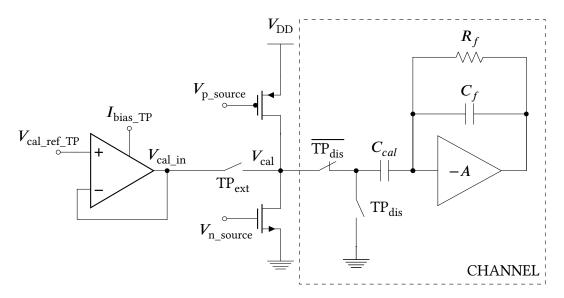

| 3.42 | Test pulse calibration and injection circuit                                | 98  |

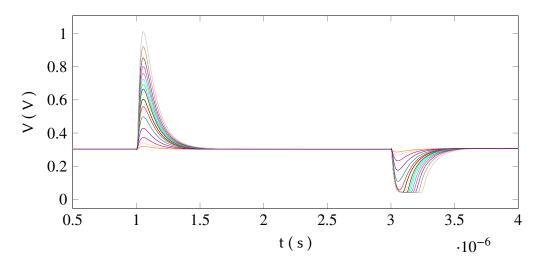

| 3.43 | Simulation of the front-end response to test-pulses of different amplitude. | 98  |

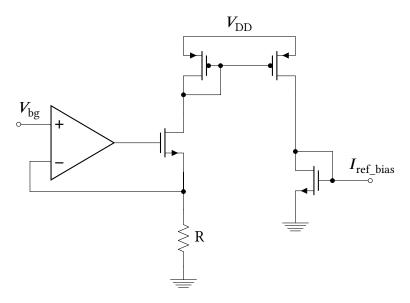

| 3.44 | Bias reference generator                                                    | 99  |

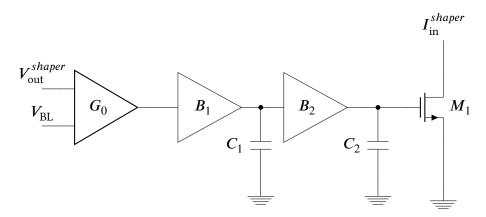

| 3.45 | TIGER ASIC bias cells                                                       | 100 |

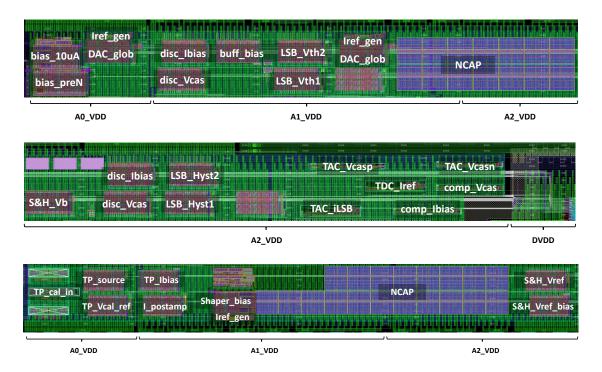

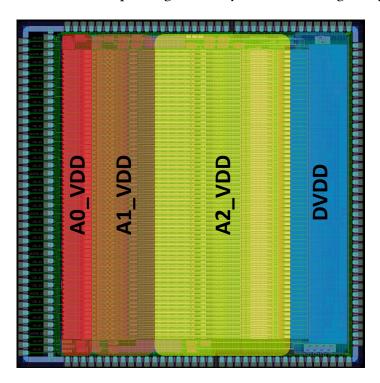

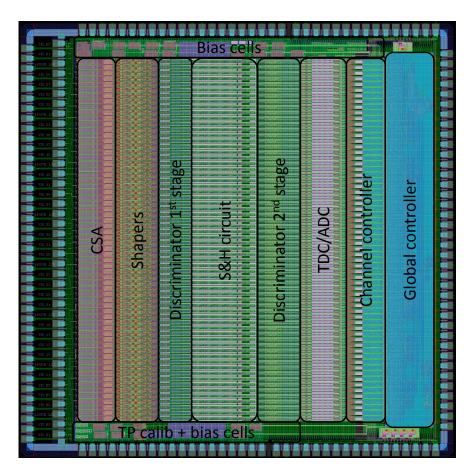

| 3.46 | TIGER power domains partitioning                                            | 103 |

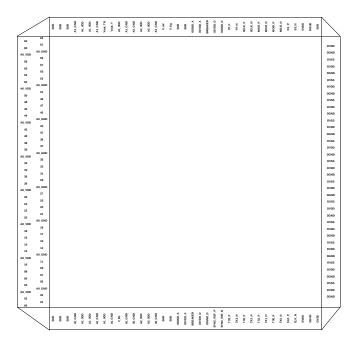

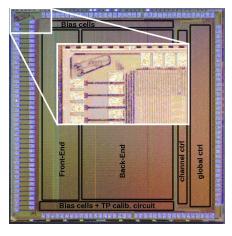

| 3.47 | TIGER full ASIC layout                                                      | 104 |

| 3.48 | TIGER padring                                                               | 105 |

| 3.49 | Time branch output noise                                                    | 106 |

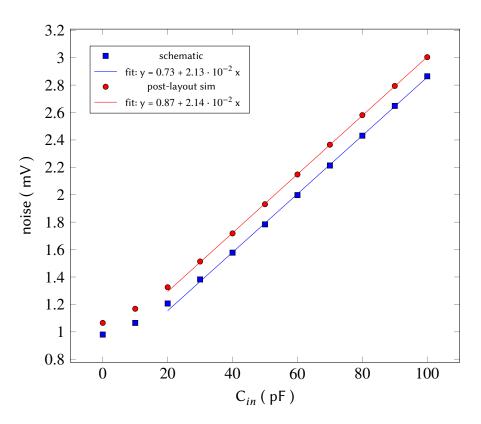

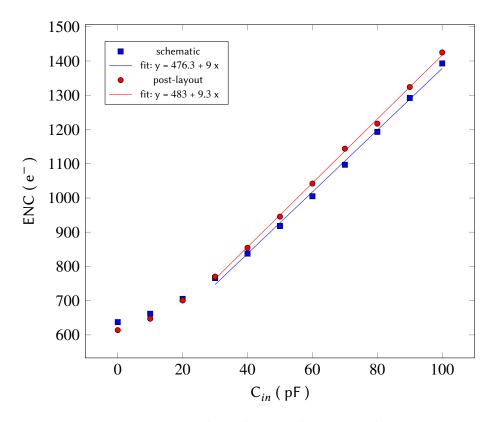

| 3.50 | Energy branch equivalent noise charge                                       | 107 |

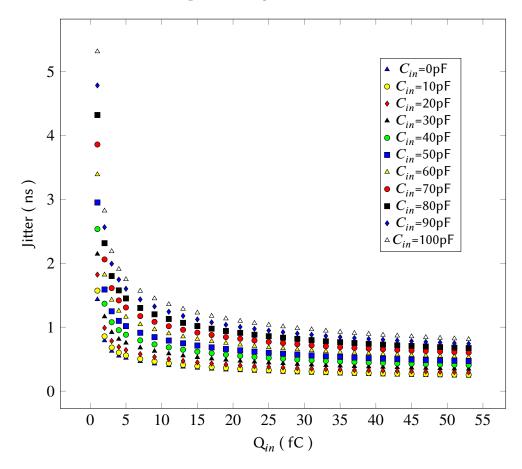

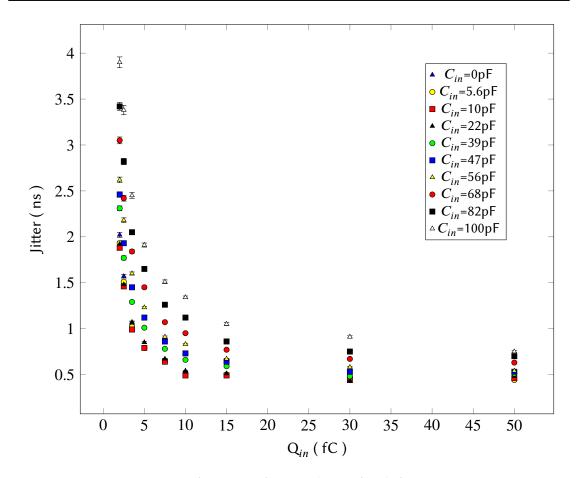

| 3.51 | Time jitter as a function of input charge for different input capacitances. | 108 |

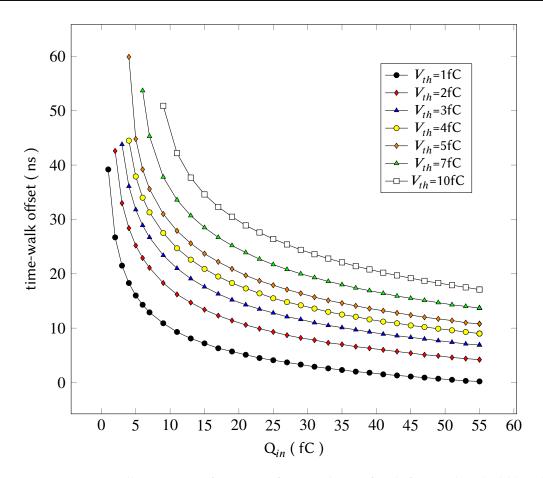

| 3.52 | Time walk curve as a function of input charge for different threshold       |     |

|      | levels                                                                      | 109 |

| 4.1  | TIGER ASIC                                                                  | 111 |

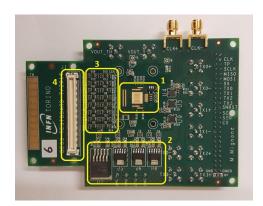

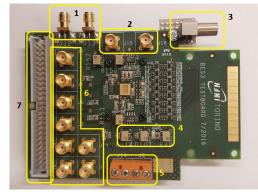

| 4.2  | TIGER testboard                                                             | 113 |

| 4.3  | Main building blocks of the DAO system                                      | 114 |

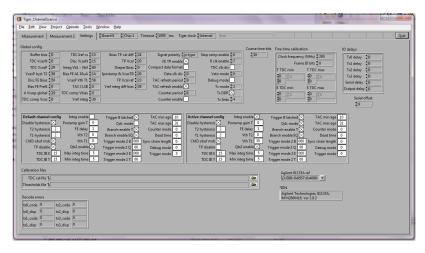

| 4.4  | LabVIEW GUI                                                                  | 115 |

|------|------------------------------------------------------------------------------|-----|

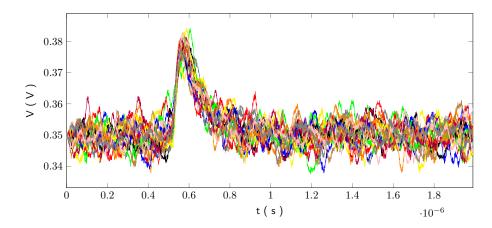

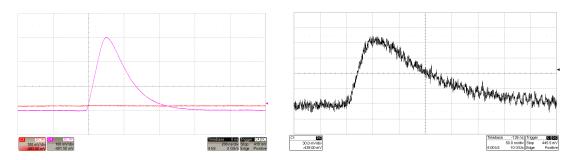

| 4.5  | TIGER analogue debug output probed at the oscilloscope                       | 117 |

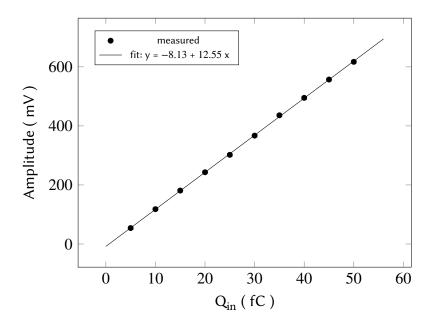

| 4.6  | Gain measured on channel 63 probing the debug output                         | 118 |

| 4.7  | Double S-curve used to evaluate the signal amplitude                         | 119 |

| 4.8  | Signal amplitude measured with the double S-curve method for different       |     |

|      | input charge values                                                          | 119 |

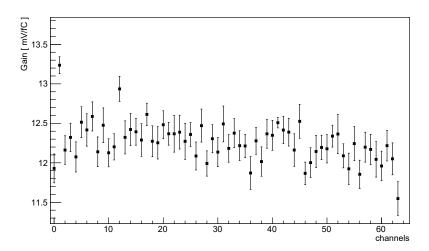

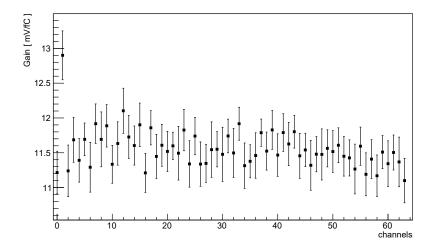

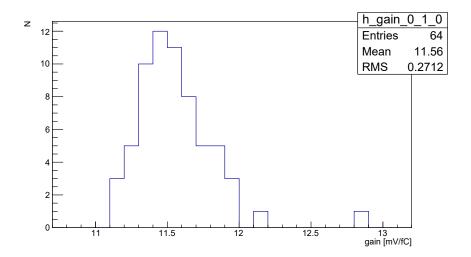

| 4.9  | Time branch 64-channel gain distribution                                     | 120 |

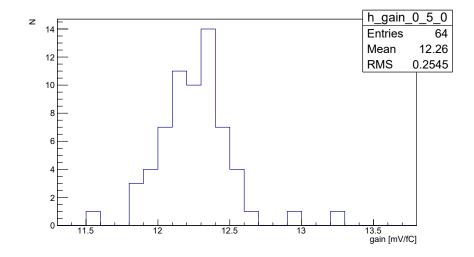

| 4.10 | Time branch gain dispersion of the 64 channels of one ASIC                   | 120 |

| 4.11 | Energy branch linearity and gain measurement for one channel using           |     |

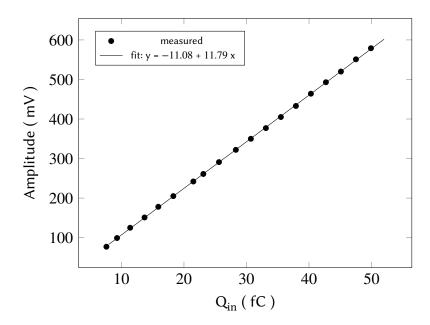

|      | the S-curve method                                                           | 121 |

| 4.12 | Energy branch 64-channel gain distribution                                   | 121 |

| 4.13 | Energy branch gain dispersion of the 64 channels of one ASIC                 | 122 |

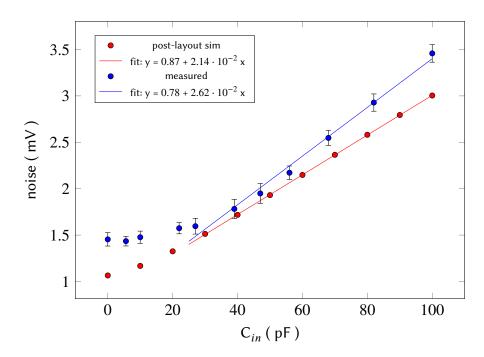

| 4.14 | Time branch r.m.s. output noise as a function of the input capacitance.      | 123 |

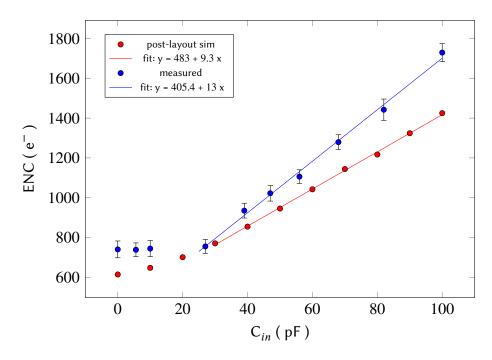

| 4.15 | Energy branch ENC as a function of the input capacitance                     | 124 |

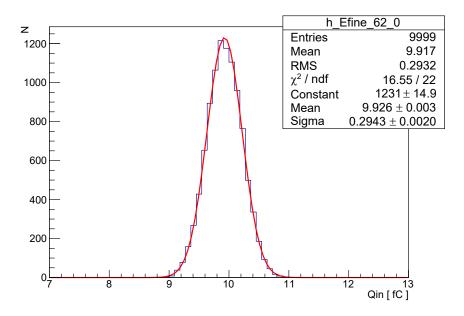

| 4.16 | Noise measured with the S&H circuit using a repetition of test pulse of      |     |

|      | fixed charge (10 fC)                                                         | 124 |

| 4.17 | Baseline level of the 64 channels before (left) and after (right) thresholds |     |

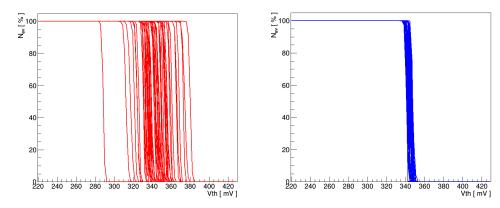

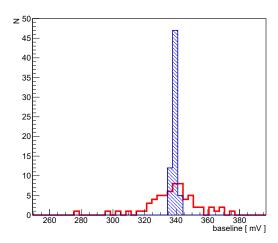

|      | equalization                                                                 | 125 |

| 4.18 | Threshold non-uniformity of the 64 channels in one chip before (red)         |     |

|      | and after (blue) the equalization                                            | 125 |

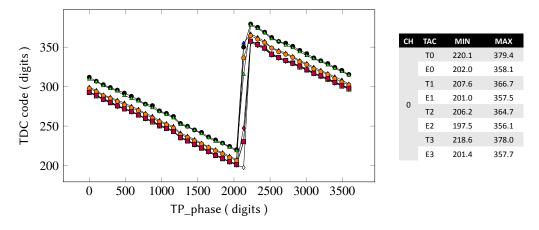

| 4.19 | TDC calibration curves                                                       | 126 |

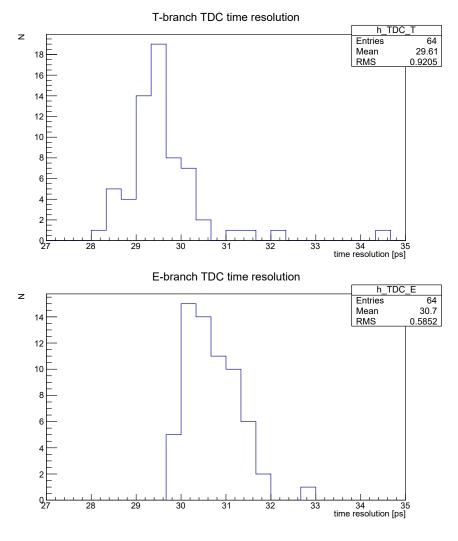

| 4.20 | TDC time resolution                                                          | 127 |

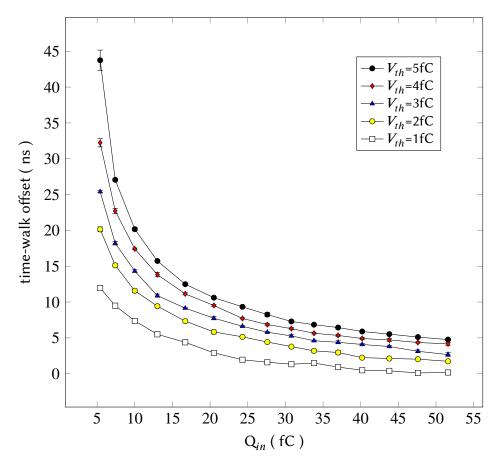

| 4.21 | Time walk curve as a function of input charge for different threshold        |     |

|      | settings                                                                     | 128 |

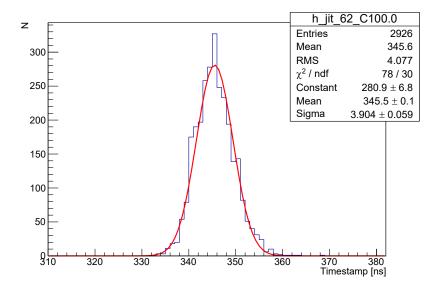

| 4.22 | Time branch jitter for $C_{in}$ = 100 pF and $Q_{in}$ = 2 fC                 | 129 |

| 4.23 | Time jitter as a function of input charge for different input capacitances.  | 130 |

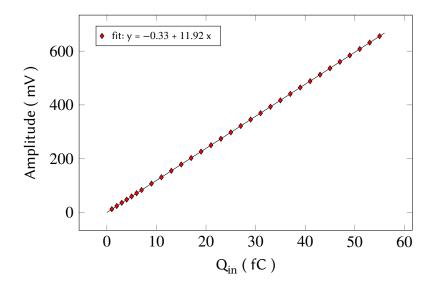

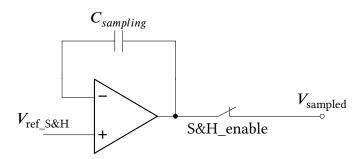

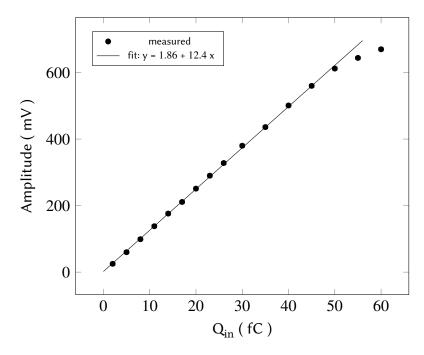

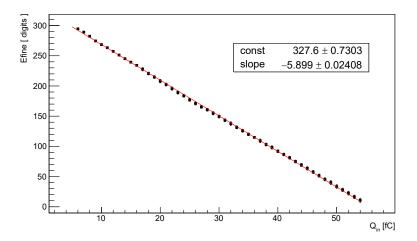

| 4.24 | S&H charge measurement using the external pulse generator                    | 131 |

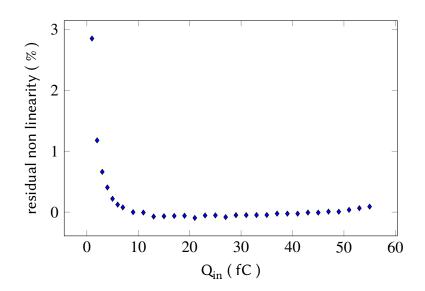

| 4.25 | Residual non-linearity of the S&H charge measurement                         | 131 |

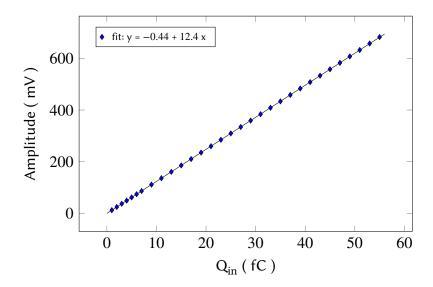

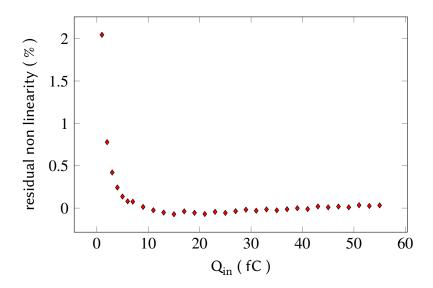

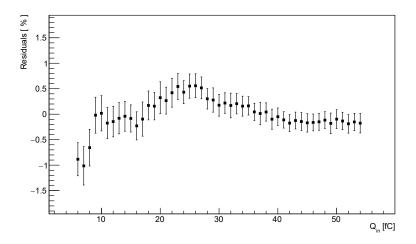

| 4.26 | S&H charge measurement using the internal calibration circuit                | 132 |

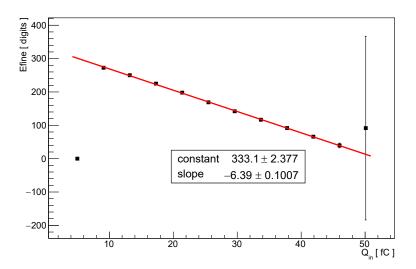

| 4.27 | Time-over-Threshold as a function of the input charge                        | 133 |

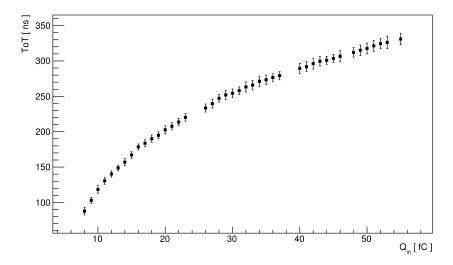

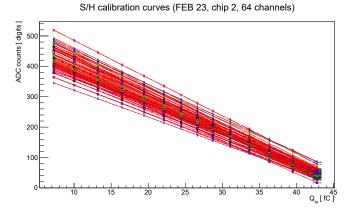

| 4.28 | S&H charge measurement calibration curves                                    | 135 |

| 4.29 | CERN H4 beam line                                                            | 137 |

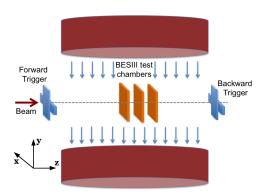

| 4.30 | CERN test beam setup                                                         | 137 |

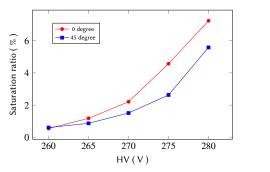

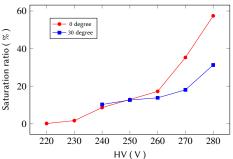

| 4.31 | Charge measurement saturation ratio                                          | 140 |

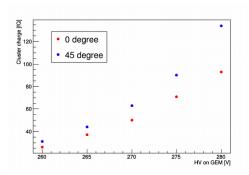

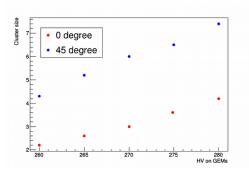

| 4.32 | Cluster charge and size for different HV and incident angles settings.       | 14( |

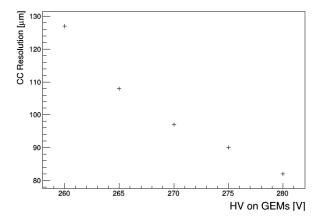

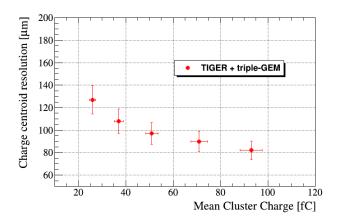

| 4.33 | Charge centroid spatial resolution for different detector gain settings        | 141 |

|------|--------------------------------------------------------------------------------|-----|

| 4.34 | Spatial resolution as a function of the mean cluster charge                    | 141 |

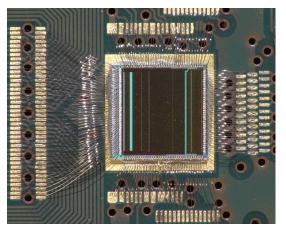

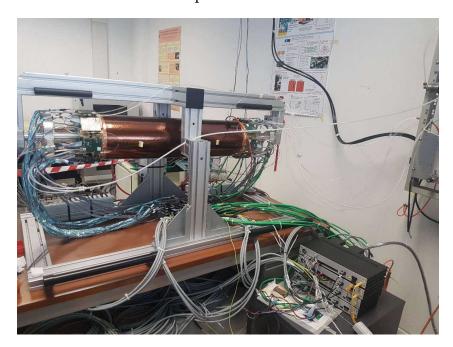

| 4.35 | CGEM-IT Layer 1 fully instrumented                                             | 142 |

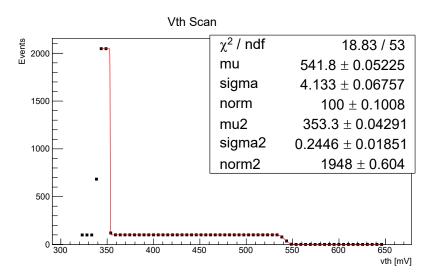

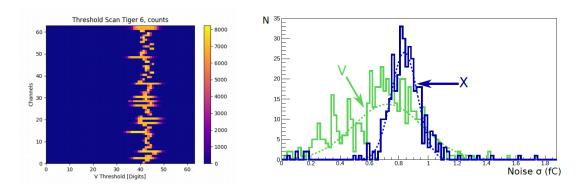

| 4.36 | 64-channel threshold scan and noise distribution measured on the CGEM-         |     |

|      | IT Layer 1                                                                     | 143 |

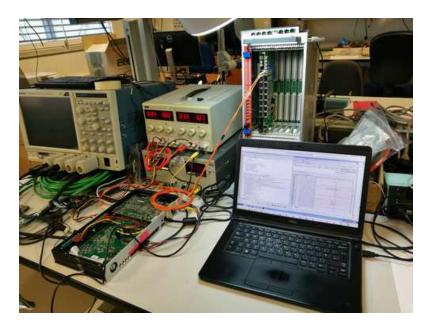

| 4.37 | GEMROC-GEM DC interconnection test setup                                       | 144 |

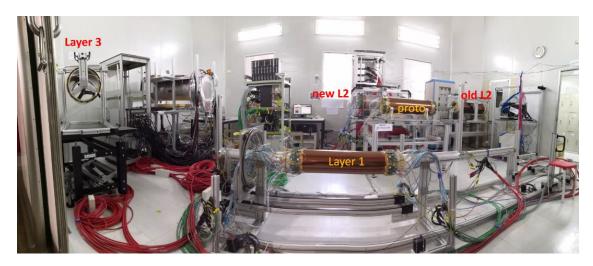

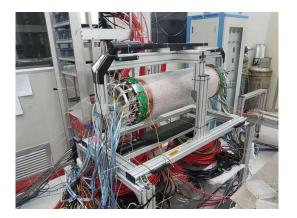

| 4.38 | IHEP laboratory where the CGEM-IT is assembled                                 | 145 |

| 4.39 | The assembly of Layer 1 and 2                                                  | 145 |

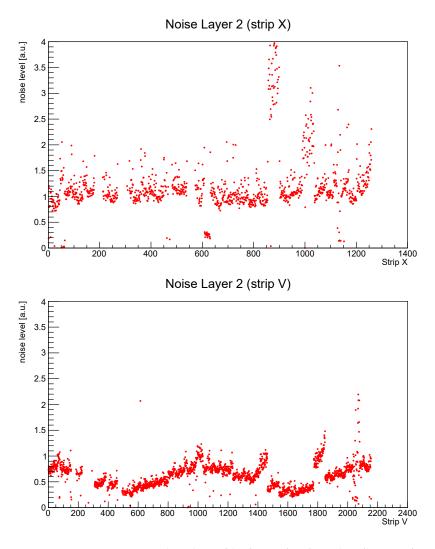

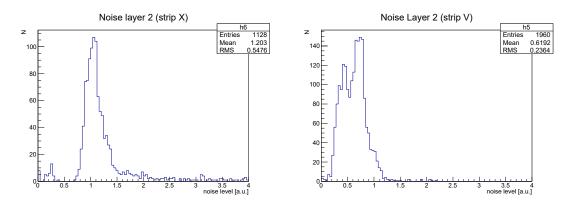

| 4.40 | Layer 2 strips noise profile                                                   | 146 |

| 4.41 | Layer 2 strips noise distribution                                              | 147 |

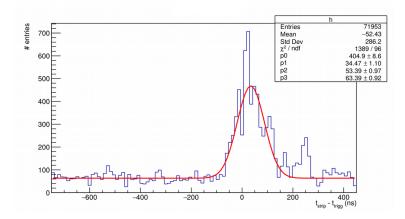

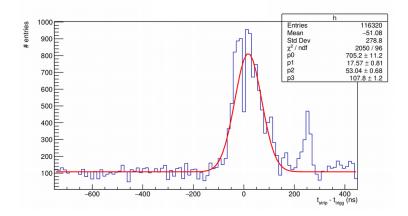

| 4.42 | Strips time distribution around the trigger time for a gain of 9000            | 147 |

| 4.43 | Strips time distribution around the trigger time for a gain of 12000           | 148 |

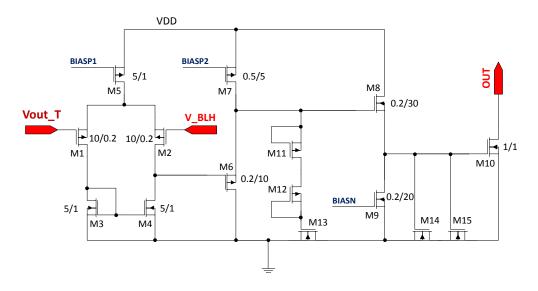

| A.1  | Baseline Holder circuit schematics                                             | 154 |

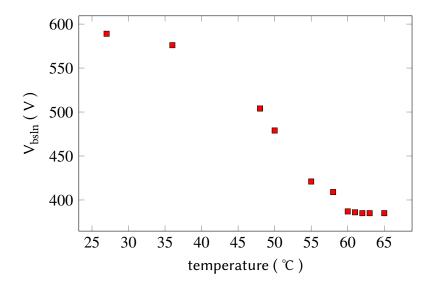

| A.2  | Measured baseline level as a function of the operating temperature             | 155 |

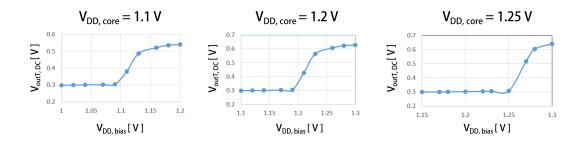

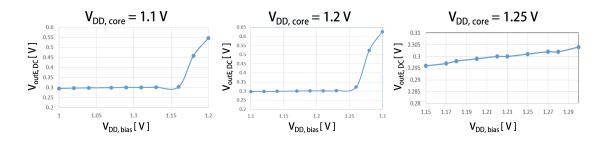

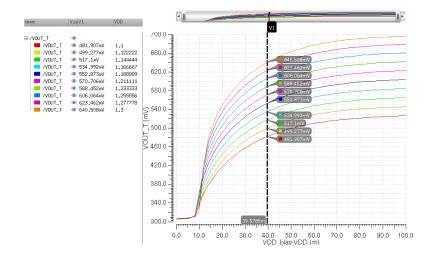

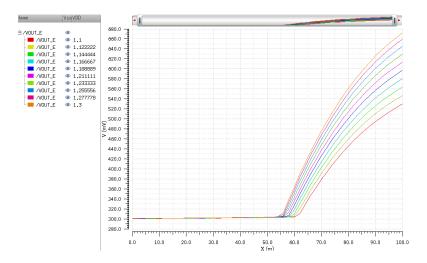

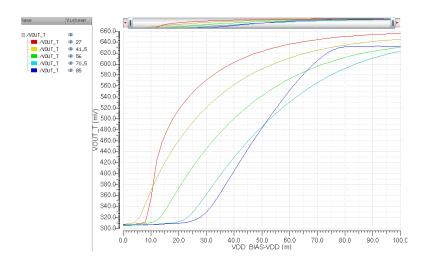

| A.3  | Time branch shaper DC output voltage as a function of the bias cells           |     |

|      | power supply for different core cells power supply values                      | 156 |

| A.4  | Energy branch shaper DC output voltage as a function of the bias cells         |     |

|      | power supply for different core cells power supply values                      | 156 |

| A.5  | Time branch shaper DC output voltage as a function of $\Delta V_{DD}$ for dif- |     |

|      | ferent $V_{DD,core}$ values                                                    | 156 |

| A.6  | Energy branch margin                                                           | 157 |

| A.7  | $\Delta V_{DD}$ margin for different temperature values                        | 157 |

| A.8  | Time branch shaper DC output as a function of the PMOS transistor bias.        | 158 |

| A.9  | Block diagram of the time branch shaper + BLH stage                            | 159 |

| A.10 | Shaper core amplifier schematics: old design                                   | 160 |

| A.11 | PVT corners post-layout simulations                                            | 160 |

| C.1  | Layer 1 FEB pinout                                                             | 168 |

| C.2  | Layer 2 FEB pinout                                                             | 169 |

| C 3  | Laver 3 FEB pinout                                                             | 170 |

# Chapter 1

# Introduction

## 1.1 The BESIII Experiment

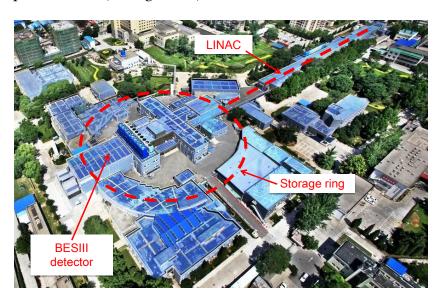

The Beijing Spectrometer III (BESIII) is a multi-purpose detector running at the  $e^+e^-$  collider BEPCII (Beijing Electron and Positron Collider) of the Institute for High Energy Physics (IHEP) in the People's Republic of China (PRC). The collider operates in the  $\tau$ -charm threshold energy region between 2 GeV and 4.6 GeV with a designed peak luminosity of  $10^{33} \text{cm}^{-2} \text{s}^{-1}$  [1]. Electrons and positrons are injected in two storage rings (237.5 m in circumference) using a 202 m long LINAC, which accelerates electrons and positrons up to 1.89 GeV (see Figure 1.1).

Figure 1.1: Aerial view of BEPCII and BESIII.

BESIII has been successfully running since 2008 and features a rich physics program studying strong, electromagnetic and weak interactions. The  $J/\psi$  high production rate in electron-positron collisions makes it suitable for studies on exotic hadrons composed of light quarks and gluons, which are the keys to understand the nature of the strong interaction [2].

## 1.1.1 BESIII detector

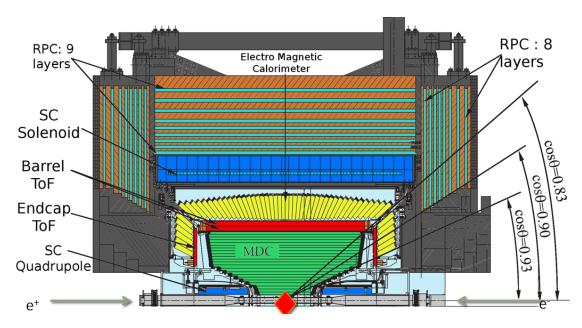

The BESIII detector, depicted in Figure 1.2, is located at the interaction point of the two pipe rings. It has a geometrical acceptance of 93% of the solid angle and can be divided in the following sub-detectors [3]:

- The **Multi-layer Drift Chamber** (MDC) is the tracking system of the detector and provides a spatial resolution of  $\sigma_{r\phi} \approx 120 \, \mu \text{m}$  and  $\sigma_z \approx 2 \, \text{mm}$  and a momentum resolution of  $\sigma_p/p \approx 0.5\%$  at 1 GeV/c. The MDC is made of 43 sense wire layers, with the first 8 defining the inner MDC.

- The **Time-Of-Flight** (TOF) detector is composed by two layers of 88 scintillating bars in the barrel region. A recent upgrade of the TOF endcaps has been carried out featuring the installation of 36 overlapping trapezoidal-shaped Multi-gap Resistive Plate Chambers (MRPC) for each endcap [4]. The TOF detector allows to extract the time information of the crossing particles with a time resolution of about 80-90 ps.

- The **Electromagnetic Calorimeter** (EMC) consists of 6240 CsI(Tl) crystals arranged in a cylindrical shape and two endcaps. It provides the energy information with a resolution of 2.5% in the barrel and 5% in the endcaps at 1.0 GeV. This measurement, combined with the TOF system time information, allows for the particle identification (PID).

- A **solenoidal superconducting magnet** provides a uniform 1 Tesla magnetic field, thus allowing to measure the basic particles momentum. Its steel flux return yoke acts as a hadron absorber allowing for hadron-muon separation and provides as well the support for the spectrometer components.

- Outside the superconducting solenoid, several arrays of Resistive Plate Chambers (RPC) allow to identify muons and separate them from charged pions, other

hadrons and backgrounds. There are nine layers of RPCs in the barrel and eight in the endcaps.

Figure 1.2: The BESIII detector [1].

## 1.1.2 BESIII trigger and DAQ systems

The trigger, data acquisition and online computing systems can accommodate multibeam bunches separated by 8 ns. Fully-pipelined electronics allows to achieve an almost zero dead-time operation.

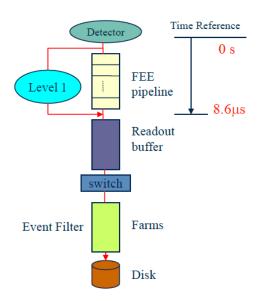

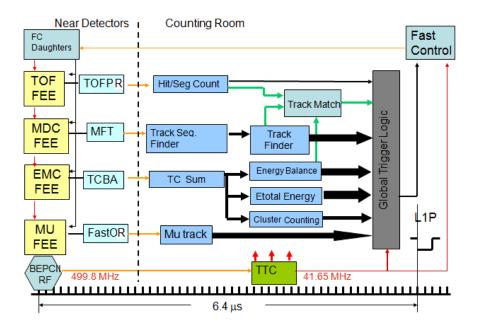

The trigger system diagram is shown in Figure 1.3. It comprises a hardware trigger level (L1) and a software trigger level (L3). The sub-detector signals used for the L1 trigger generation are first processed in the four sub-system modules and then transmitted, via optical links, to the L1 trigger crates where they are analyzed providing hit patterns, track segment finding, clusters and total energy. These sub-triggers are sent to the Global Trigger Logic for the generation of the final L1 trigger signal (see Figure 1.4). L1 signals, together with the system clock and other control commands, are transmitted to the Fast Control system in order to be distributed to the readout electronics crates of the sub-detectors via optical links.

Figure 1.3: Data flow diagram of the L1 and L3 trigger.

Figure 1.4: Block diagram of the L1 trigger system.

The trigger system and the sub-detectors readout electronics crates employ an 8-bit counter to count the L1 signals for event numbering and synchronization purposes. After the  $256^{\rm th}$  L1 signal, the trigger system generates one CHK signal which is transmitted to the readout modules to check if the number of generated and received L1 signals is

the same. If the internal counter of each readout module is zero the data acquisition can continue, otherwise it needs to be stopped.

The L1 trigger allows to select good physics events with high efficiency while reducing the cosmic ray (2 kHz) and beam (20 MHz) related backgrounds to a level smaller than the 2 kHz physics event rate. This results in a designed L1 trigger maximum rate of 4 kHz.

The BESIII DAQ system is based on VME and online computer farm designed to read large amounts of data from the front-end electronics system and record valid data on permanent storage devices. At the reception of an L1 trigger, which is generated 8.6 µs after the collision, the DAQ system transfers the event data stored in the VME crates buffers to the online computer farm where the data are merged, forming complete events, and then filtered for background suppression (L3 trigger).

In addition, a detector control system (DCS) allows to monitor the environmental parameters of the system, such as temperature, humidity and radiation, as well as the performance of the spectrometer and accelerator itself, such as the status of the detector high voltage and gas systems, providing safety interlocking among sub-detectors and between the detector and the accelerator.

# 1.2 The CGEM-IT project

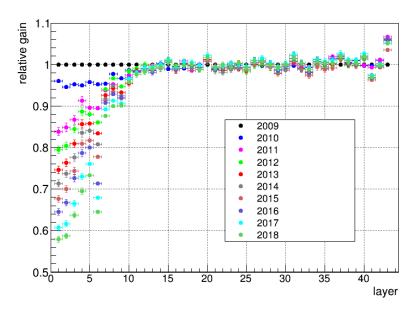

BESIII will run at least until the year 2024, and more likely until 2027. In order to guarantee optimal physics performance for the full experiment lifetime, the inner MDC needs to be replaced because of its aging induced by radiation damage [5]. Figure 1.5 shows the relative gain at which the MDC layers have been operated in the past years. In order to compensate the increment of sparks rate caused by the aging, the innermost layers are operated at lower relative gains and every year these effects become more relevant.

In 2014, an innovative solution featuring a lightweight tracker based on Cylindrical Gas Electron Multiplier (CGEM) technology was proposed by the Italian collaboration in BESIII and boosted by a INFN (Italian National Institute for Nuclear Physics) - IHEP (Chinese Institute of High Energy Physics) network. The project was funded by the European Commission within the H2020-RISE-MSCA-2014 framework and involved, apart from INFN and IHEP, also institutes from Mainz and Uppsala Universities.

Figure 1.5: MDC gain loss in the 10-year BESIII operation.

## 1.2.1 Gas Electron Multiplier detectors

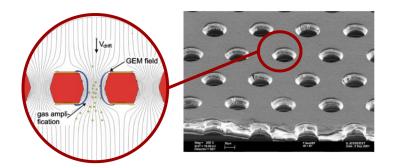

The Gas Electron Multiplier (GEM) is a gaseous detector invented in 1997 by F. Sauli [6]. A GEM foil is a metal coated polymer (typically 50  $\mu$ m kapton + 3  $\mu$ m copper), pierced with holes of ~50  $\mu$ m diameter (see Figure 1.6). A voltage of some hundreds of Volts is applied between the two copper layers to create an intense electric field (some tens of kV/cm) inside the holes. Electrons released by the primary ionization particle are attracted into the holes, where the charge multiplication occurs. The gas mixture typically is composed of Ar-CO<sub>2</sub> or Ar-iC<sub>4</sub>H<sub>10</sub> (Isobutane). Argon is the main gas (70-90%) enabling the ionization, while CO<sub>2</sub> and Isobutane serve as the quenching gases to lower the discharge risk.

Figure 1.6: Details of a GEM foil.

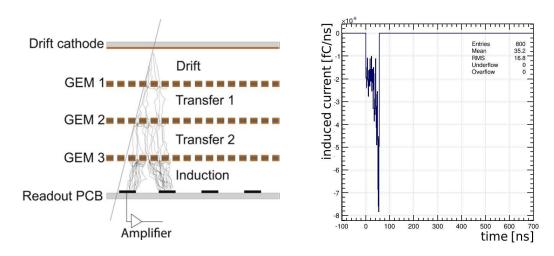

Several GEM foils can be placed at short distances (typically 1–2 mm) distributing the gas amplification among several stages in order to increase the total gain while reducing the discharge probability. The triple-GEM configuration shown in Figure 1.7 (left) allows to reach gains up to some 10<sup>4</sup> and has been extensively adopted in High Energy Physics experiments. Its typical response is displayed in Figure 1.7 (right) where the current induced by an electron on one strip has been evaluated using Garfield++ [7] simulations. This toolkit allows for a detailed computational simulation of gaseous sensors, taking into account many phenomena that occur inside the detector, such as gas ionization, electrons diffusion (in the gas medium) and amplification (in the GEM holes) and signal induction.

Figure 1.7: Schematic representation of the signal formation inside a triple-GEM (left) and Garfield++ simulation of the current induced by an electron on a strip as a function of the time (right) [8].

Compared to other drift devices, such as the currently operating MDC, this kind of detector offers better resistance to discharge and radiation damage. In addition, since the signal is produced only by electrons, and not from ion motion, higher operation rates can be achieved, without trading in terms of resolution. Therefore, thanks to their good spatial resolution, high particle flux, large area coverage, low material budget, favorable cost-effectiveness and high radiation tolerance GEM detectors are suitable for precise tracking in areas close to beam collisions.

## 1.2.2 The CGEM-IT detector

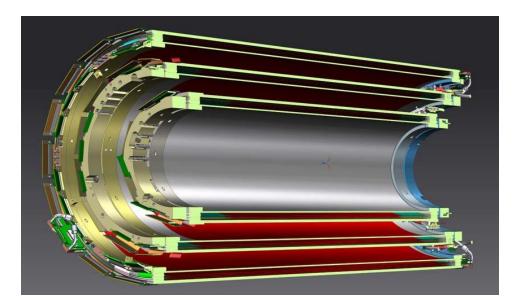

The CGEM-IT (Cylindrical Gas Electron Multiplier Inner Tracker) detector is the proposed upgrade of the BESIII inner tracker and is shown in Figure 1.8. The installation of the new detector is scheduled to take place in 2020. A detailed description of its design is given in [9].

Figure 1.8: 3D view of the CGEM detector mechanical drawings.

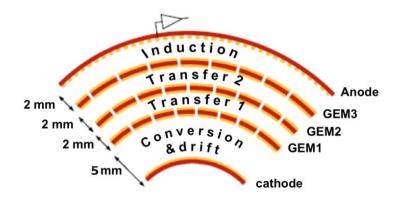

Figure 1.9: Schematic view of the BESIII Cylindrical triple-GEM.

The CGEM-IT comprises three independent concentric layers, covering 93% of the solid angle. Each layer is a Cylindrical triple-GEM detector and its configuration, shown in Figure 1.9, consists of a cathode, three GEM foils and a readout anode, where the

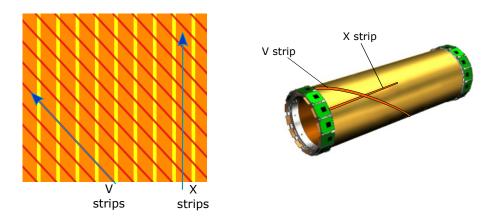

signal induced by the electron motion in the last gap is collected by bi-dimensional strips with a novel XV anode readout plane (see Figure 1.10). The X strips, parallel to the CGEM-IT axis and the beam pipe, provide the information of the  $r\phi$  coordinates, while the V strips have a stereo angle between 33° and 43° with respect to the X strips and provide, together with the other view, the z coordinate.

Figure 1.10: XV strips layout: the strips parallel to the cylinder axis (X-strips) are 570  $\mu$ m wide, while the width of the V-strips is only 130  $\mu$ m.

The design of the CGEM-IT took advantage from previous experience with cylindrical GEM employed as tracking system in KLOE-2 experiment [10], introducing several innovations in order to meet the requirements, from both mechanical and physics performance points of view, set by the BESIII Experiment, which are reported in Table 1.1.

| Parameter              | Value                  |

|------------------------|------------------------|

| Rate capability        | 10 kHz/cm <sup>2</sup> |

| Efficiency             | 98%                    |

| $\sigma_{r\phi}$       | 130 μm                 |

| $\sigma_z$             | 1 mm                   |

| $\sigma_{p_t}/p_t$     | 0.5% at 1 GeV/c        |

| Geometrical acceptance | $93\%~4\pi$            |

| Material budget        | $< 1.5 X_0$            |

| Inner radius           | 78 mm                  |

| Outer radius           | 178 mm                 |

Table 1.1: Design specifications for the CGEM-IT.

Compared to the KLOE-2 design, the CGEM-IT features the following innovations:

- In the KLOE-2 experiment the mechanical structure was realized with Honeycomb foils on the anode and cathode electrodes and a permaglass ring at the edges of the detector. For BESIII, the use of a very light mechanical structure based on Rohacell reduces the material budget of the detector [11]. In addition, the thickness of the GEM foils copper faces has been decreased from 5 to 3  $\mu$ m, thus allowing to further reduce the detector radiation length to about 1% of  $X_0$

- An analogue readout enabling charge centroid and  $\mu TPC$  reconstruction algorithms (refer to 1.2.2) has been chosen since it allows to achieve a better spatial resolution compared to the one provided by a digital readout, which is limited by the strips pitch dimensions. This choice relaxes the requirements concerning the number of channels to be readout: with a strip pitch of 650  $\mu$ m the number of channels is reduced to ~10000 [12].

- The drift gap has been increased from 3 mm to 5 mm in order to enhance the number of electrons from primary ionization, thus improving the performance of the position reconstruction algorithms: a larger gap provides more points for the  $\mu$ TPC technique and thus a better spatial resolution [8].

Thanks to the aforementioned innovations, the new detector will match the requirements for the momentum  $(\sigma_{p_t}/p_t)$  and radial  $(\sigma_{r\phi})$  resolution and will improve by at least a factor of 2 the resolution along the beam axis  $(\sigma_z)$ . This will enhance the performance of BESIII in reconstructing primary and secondary vertices, thus leading to a better background rejection and an improved efficiency for rare decays [13].

### Reconstruction algorithms

The measurement of both the time and the charge information of the CGEM signal collected on the anode strips enables the use of two algorithms to reconstruct the position of the impinging particle: the Charge Centroid (CC) and the micro-Time Projection Chamber ( $\mu$ TPC) readout. The performance of the two methods depends strongly on the shape of the charge distribution on the readout plane.

The charge centroid method determines the position x of a charged track on the anode by means of the weighted average of the fired strip positions  $x_i$ :

$$x = \frac{\sum_{i} x_i q_i}{\sum_{i} q_i} \tag{1.1}$$

where the weights  $q_i$  correspond to the charge collected by each fired strip (see Figure 1.11).

Figure 1.11: Representation of the charge centroid algorithm.

Figure 1.12: Representation of the  $\mu TPC$  algorithm for angled tracks without (left) and with (right) the presence of magnetic field.

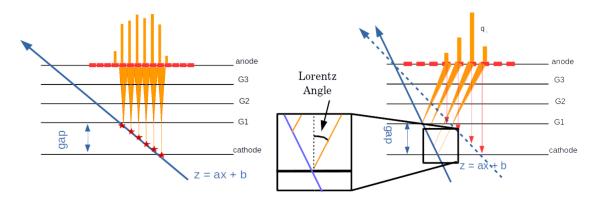

The CC algorithm provides a good spatial resolution with orthogonal tracks producing a Gaussian-shaped charge distribution, while its performance degrades in presence of high magnetic fields or non-perpendicular tracks. To overcome this issue a new reconstruction algorithm, named  $\mu TPC$ , has been developed [14], [15]. Shown in Figure 1.12, this technique allows to reconstruct the 3-dimensional particle position as in a Time Projection Chamber but within the few millimeters of the drift gap. By measuring the time of arrival of the signal on each strip and by knowing the electron drift velocity in the gas mixture it is possible to calculate the direction of the incident particle and then extract the position of the primary ionization point.

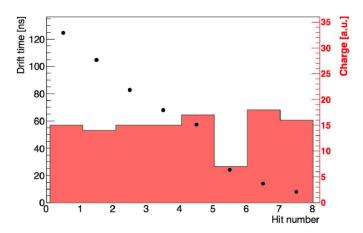

In Figure 1.13 the drift time distribution is reported for an event in which eight strips are hit and for which the charge distribution on the anode is no more Gaussian, making the CC method totally unusable. Knowing the coordinate  $x_i$  of each strip, the position of each primary ionization  $z_i$  perpendicular to the strip plane is obtained from the time measurement using the electron drift velocity. The  $(x_i, z_i)$  points are then fitted with a linear function z = ax + b and the position is extracted in the middle of the gap in order to minimize the errors [8] as:

$$x = \frac{\frac{gap}{2} - b}{a} \tag{1.2}$$

Figure 1.13: Drift time distribution as a function of hit strips (points). The histogram represents the charge distribution, which is no more Gaussian for this particular event [13].

The whole procedure is possible if the time resolution of the detector is good enough (<10 ns) to resolve the arrival times of the avalanches from different primary electrons, and with a highly segmented readout plane.

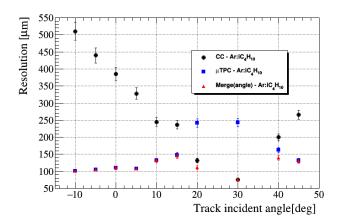

A merging algorithm to weight the contribution of these two anti-correlated methods has been developed in order to grant the required spatial resolution of 130  $\mu$ m for the different angular regions (see Figure 1.14) and thus provide a unique measurement to track the particles with the triple-GEM detector inside the BESIII spectrometer [8].

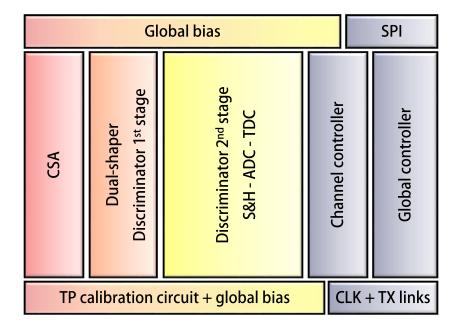

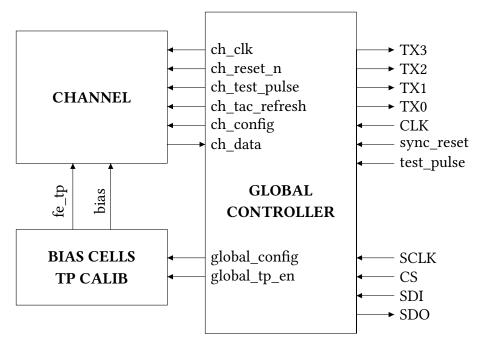

For the CGEM analogue readout a dedicated multi-channel Application-Specific Integrated Circuit (ASIC) has been developed. The chip, named TIGER (Turin Integrated Gem Electronics for Readout), features 64 parallel channels that extract and digitize the amplitude and time-of-arrival of the input signals coming from the CGEM detector. The ASIC design and characterization will be described in detail in Chapter 3 and

Figure 1.14: Spatial resolution for different incident angle in presence of magnetic field using the two reconstruction algorithms [8].

4, respectively. In the next section, an overview of the CGEM-IT readout electronics is given, discussing the main feature of each block composing the full-chain, from the on-detector front-end ASIC to the off-detector VME-based data collectors.

## 1.2.3 Overview of the CGEM-IT readout electronics

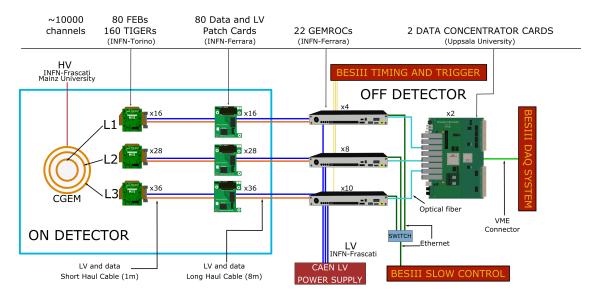

The general scheme of the CGEM-IT electronics is shown in Figure 1.15. The readout chain can be divided in 2 main blocks: the on-detector and the off-detector electronics.

Figure 1.15: General scheme of CGEM-IT electronics.

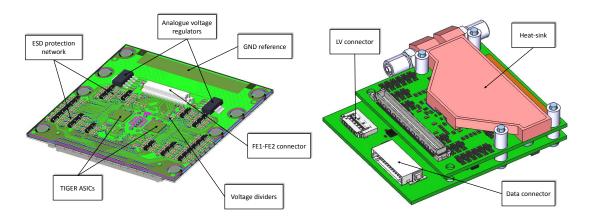

#### **On-detector electronics**

The on-detector electronics includes the Front-End boards (FEBs) that host the TIGER custom ASICs. The limited space available in the inner part of the BESIII spectrometer called for a compact design of the boards [16]. Each FEB, shown in Figure 1.16, can accommodate two 64-channel chips and consists of a stack of two printed circuit boards (FE1 and FE2). The two ASICs are bonded on the analogue-most layer (FE1), where power regulators and SMD voltage divider circuits are used to properly bias the chips. Each channel input features an ESD protection network to prevent potential damage caused by the detector discharges. The interface towards the anode is provided by a Hirose FX10A-144S-SV connector. The digital-domain FE2 hosts the LVDS buffers and provides interface to the off-detector electronics for data (ERNI SMC-B26 connector) and power (MOLEX 504050-0691 connector). The two layers of the FEB are connected together through a HIROSE DF12-60DS-0.5V connector [17].

Figure 1.16: Front-End Board design for the CGEM-IT Layer 1: top-side routing on FE1 (left) and FE1/FE2 assembly with liquid cooling heat exchanger plate (right).

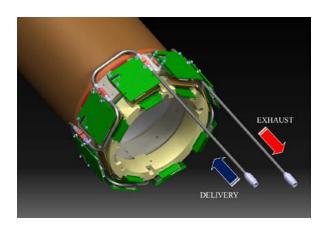

A copper heat-sink is mounted on the external side of FE1 to cool-down the electronics and keep the temperature stable by means of a closed circuit water-cooled system based on a SMC-HRS012 Thermo-chiller [18] and represented in Figure 1.17.

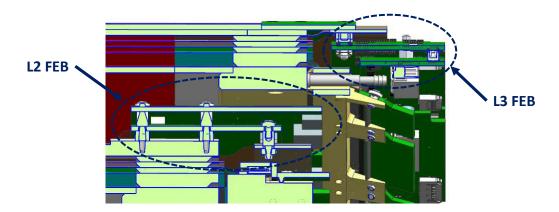

The different space available for the FEBs in the three layers of the CGEM-IT (see Figure 1.18) required a different and even more compact design for the L3 FEBs. The layout and routing have been completely revised in order to fit the same components in a smaller area. A size comparison of the FEBs for different layers is shown in Figure 1.19. This can be seen also in Figure 1.17 by observing the different geometry of the cooling system tubes.

Figure 1.17: 3D view representation of the cooling system for the CGEM-IT Layer 1 (left) and 3 (right).

Figure 1.18: Detail of the CGEM mechanical drawing. The very limited space made available for the Layer 3 FEB can be observed in the top-right angle of the figure and compared to the space reserved to the Layer 2 FEB.

Figure 1.19: Size comparison of the Front-End-Boards for Layer 1 and 2 (left) and Layer 3 (right).

As shown in Figure 1.17, the FEBs are installed at both ends of the detector, with each side reading one half of it. To fully instrument the three layers of the CGEM-IT a total of 80 FEBs (160 TIGER chips) are needed and they are distributed as follows:

- Layer 1: 8 FEBs (16 TIGER) per side

- Layer 2: 14 FEBs (28 TIGER) per side

- Layer 3: 18 FEBs (36 TIGER) per side

The validation and calibration of the chips required to fully equip the detector will be discussed in Chapter 4. The self-triggered readout operation of TIGER implies that every signal above the selected threshold is digitized and sent off-chip to the off-detector electronics where the ASIC raw data are filtered using a time-tag approach based on the BESIII Experiment L1 trigger signal.

#### **Off-detector electronics**

The off-detector electronics is mainly composed by two data processing units: the GEM Read-Out Card (GEMROC) module and the GEM Data Collector (GEM-DC).

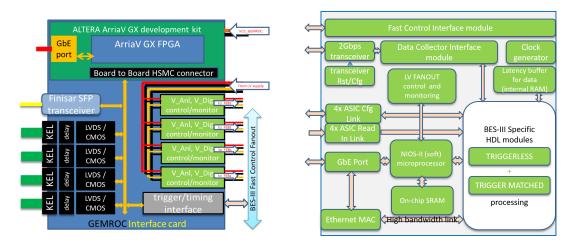

The GEMROC modules (see Figure 1.20) handle the interface with the on-detector electronics, providing data, configuration and monitoring through LVDS links. They also distribute the power supply coming from the Low-Voltage distribution system to the FEBs.

Each GEMROC module can handle up to four FEBs (8 chips, 512 channels) and is based on an ALTERA Arria V GX FPGA development board [19] coupled to a custom Interface Card (GEMROC\_IFC) through an High-Speed Mezzanine Card (HSMC) high

Figure 1.20: A GEMROC module assembled in its aluminum frame. The FPGA is the board mounted on the right.

Figure 1.21: Block diagram of the GEMROC hardware (left) and schematic view of the FPGA firmware (right).

performance connector. The Interface Card manages the electrical and physical interfaces to the FEBs, to the GEM-DC and the BES-III Fast Control system (L1 trigger).

A schematic view of the GEMROC hardware is shown in Figure 1.21 (left). Each GEMROC employs four KEL-8822 connectors interfaced with LVDS/CMOS buffers for the communication with the FEBs, while a Finisar SFP transceiver mounted on the interface card handles the communication between the GEMROC and the GEM-DC via optical fiber. The interface card also implements a connector which is used to deliver and share clock and trigger signals between several GEMROCs. A block diagram of the FPGA firmware is displayed in Figure 1.21 (right). It features:

- Clock generation, synchronization (between different GEMROC modules) and distribution to the front-end electronics

- Read and write operations of the TIGER configuration registers

- LV fanout control and monitoring of the TIGER bias voltages and drained currents

- Readout of TIGER raw data

- TRIGGER-LESS and TRIGGER-MATCHED data processing

- Data collector interface to build packets to be sent through Ethernet (UDP communication) or optical connection

- Communication with the PC or BESIII slow control through a GbE port.

Two different readout modes, TRIGGER-LESS and TRIGGER-MATCHED, are implemented in the GEMROC firmware [20]:

- The **TRIGGER-LESS** mode is a standalone mode used for debug and configuration purposes, allowing to perform some scans to determine the optimal parameters for TIGER operation (e.g. threshold scan). The GEMROCs directly communicate with the PC running the acquisition. In this operation mode the device does not perform any data selection, all incoming data are collected from the input buffer and put into packets to be sent to the acquisition PC. A packet is sent after eight TIGER frame-words ( $8 \times 204.8 \ \mu s = 1638.4 \ \mu s$ , refer to 3.3.1) or when the maximum packet size set for the GEMROCs communication (1440 bits) is reached. Data is sent without additional headers or trailers.

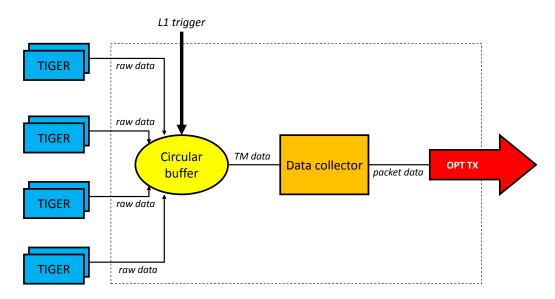

- The **TRIGGER-MATCHED** mode is used during physics acquisition runs. Hit data from ASICs are stored on a circular buffer waiting for the BESIII L1 trigger. The operation is shown in Figure 1.22. When a trigger signal is received, data is trigger-matched by reading a fixed number of words from the buffer which include the window of interest (8.6 µs latency, 1.5 µs window-centered), a formatted packet is created for each event with header and trailer words (8 bytes each) for event identification. The first received L1 trigger is used to sync-reset all the chips.

Figure 1.22: GEMROC Trigger-Matched data flow architecture.

Dedicated High-Voltage (HV) and Low-Voltage (LV) power distribution systems, mounted on CAEN SY4527LC and SY5527LC mainframes, are employed to supply the detector and electronics, respectively. The SY4527LC mainframe is equipped with two CAEN A1515CG boards and provides the HV bias to the CGEM detector. The SY5527LC mainframe hosts three CAEN A2519 cards (8 channels, 15V, 5A max) to supply the GEMROC modules and five CAEN A2517 cards (8 channels, 5V, 15A max) to supply the TIGER ASICs through the GEMROC LV power distribution section. The two systems can be controlled remotely via Ethernet and allow for single channel/board current/voltage monitoring and on/off capability.

80 "Data and LV Patch Cards" (DLVPC) are used to interconnect the "short haul" cables (about 1.5 m long) from the 80 TIGER FEBs to the "long haul" cables going to the GEMROC modules. Those boards are used to decouple the arrangement of long and short cables and can also serve as a common ground reference for the system.

To keep each detector layer and its electronics electrically floating with respect to the others a total of 22 GEMROC modules are needed:

- Layer 1: 2 GEMROC per side

- Layer 2: 4 GEMROC per side

- Layer 3: 5 GEMROC per side

The 22 GEMROCs send trigger-matched data to two GEM Data Collector (GEM-DC) modules through optical links running at 2 Gbit/s. These links are bidirectional communication channels and can also be used for ASIC configuration and monitoring. The GEM-DC are based on the VME Advanced Trigger Logic Board (ATLB, [21]), shown in Figure 1.23, and provide the interface between the CGEM-IT electronics and the BESIII Data Acquisition system.

Data coming from the GEMROCs are stored in buffers, events are time sorted and framed by an event builder module and then sent to an output buffer to be finally transmitted through the VME interface to the BESIII main DAQ.

One can estimate the raw data rate coming from one TIGER and, after that, the Trigger-Matched data rate sent by the GEMROCs to the GEM-DC modules. The maximum rate per channel is estimated to be 60 kHz. Each TIGER has 64 channels and

Figure 1.23: Advanced Trigger Logic Board.

generates event words of 64 bits each (80 bits after 8b/10b encoding) which are transmitted, in this application<sup>1</sup>, via two Tx links working at 160 MHz in SDR (single data rate) mode. This implies that the maximum data throughput from one chip is expected at around 307.2 Mbit/s, hence two Tx links are barely enough. Nevertheless, the expected hit rate per channel should be lower than the maximum rate. A realistic value (physics + noise) can be set to 25 kHz/ch.

For a rate of 25 kHz/ch (1.6 MHz per chip) we obtain a data throughput of 102.4 Mbit/s from one chip. Considering a trigger-matching time window of 1.5  $\mu$ s we can expect  $\sim$ 2.4 hit/packet, where each packet contains also two 64-bit header and trailer words. Each GEMROC reads data coming from 8 TIGER and the maximum L1 trigger rate is designed to be 4 kHz. From these assumptions, the expected trigger-matched data rate at the GEMROC output is about 6 Mbit/s, which is much lower than the limit set by the 2 GHz optical links.

In Trigger-Less acquisition, 8 TIGER produce a data rate of 102.4 MB/s which need to be transmitted via a GbE interface (UDP protocol) for standalone readout. The maximum raw bandwidth of a GbE link is 125 MB/s which is barely compatible with the Trigger-Less acquisition mode requirements. However, it must be pointed out that this mode is a debug/standalone operating mode, in which usually only a subset of the ASICs are

<sup>&</sup>lt;sup>1</sup>The ASIC has 4 Tx links which can work up to 200 MHz DDR.

selected to be monitored, thus relaxing the bandwidth requirements. Nevertheless, if all chips need to be readout at the same time, a multiplexed readout scheme could be implemented.

Finally, we can calculate the expected Trigger-Matched data bandwidth for the entire GEM detector. The full system comprises 160 TIGER, thus, with the same assumptions we made before, we obtain an event size of about 2-3 kB and thus a data rate of  $\sim$ 8-12 MB/s.

# Chapter 2

# Readout ASICs for radiation sensors

The past two decades have witnessed rapid progress in the area of radiation detectors and their readout electronics. Nowadays, Application Specific Integrated Circuits (ASIC) are very common in high-energy physics applications and play a key role in every modern detector system. Different applications may require different readout electronics, nevertheless the IC design features some aspects common to all. Typically, the ASICs comprise an array of identical channels, allowing to readout highly segmented detectors. For each channel the radiation is converted by the detector into an electrical signal whose charge is proportional to the energy deposited inside the detector by the incident particle. After that, it is processed by the front-end electronics performing signal amplification and filtering, analogue-to-digital conversion and high-speed data transmission (see Figure 2.1). Modern front-ends are mixed-signal ASICs able to integrate complex analogue and digital circuits on the same silicon substrate.

Figure 2.1: Main blocks of a radiation detection system [22].

In this chapter, a review of the components used in the signal processing chain will be provided. The main aspects in designing the front-end blocks performing signal amplification and conditioning are discussed, addressing the key design parameters related to them. In the second part of the chapter, the most recurrent readout architectures are described, reporting the functionalities of the main building blocks and discussing some practical implementation that played a role in the development of the TIGER ASIC.

The information and topics discussed in this chapter, unless otherwise specified, are taken from [22]–[24].

## 2.1 Signal amplification and conditioning

The first amplification stage is usually referred as "pre-amplifier" and plays a crucial role in the design of front-ends electronics for radiation sensors. Its response has a great impact on the measurement quality provided by the full system, hence the factors that may limit its performance must be properly studied.

First, the application requirements and the sensor properties need to be carefully investigated and understood. Several parameters play an important role in the design of a front-end:

- the amount of charge released in the detector defines the impact of the signal deterioration due to the presence of front-end noise and external interference;

- the shape and the duration of the detector signal determine the time necessary to collect a suitable amount of charge in the signal integration;

- the rate of interactions defines the number of signals the system has to cope with and thus limits the time available to process the detector signal.

These parameters are used to generate an electrical circuit model which allows to simulate the sensor response with adequate detail. After that, based on the analysis of the circuit specifications and their trade-offs, a suitable front-end architecture is chosen and the design of the building blocks can start.

Some applications may require multi-stage architectures, where the signal processing is split into several stages: after the pre-amplifier input stage, one or more shaper stages are cascaded to improve the flexibility and performance of the front-end electronics.

## 2.1.1 Signal formation

An optimized readout requires an adequate knowledge of the sensor and of the physical measurement the system is intended for.

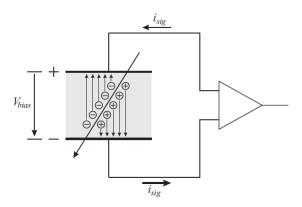

The working principle of a ionization chamber is depicted in Figure 2.2. Two conductive plates (electrodes) are kept at different potentials, thus creating an electric field inside the detecting volume. The sensing medium can be a gas, or a gas mixture, but also a semiconductor. For this discussion we will refer to a gas chamber but many aspects apply also for semiconductors.

Figure 2.2: General scheme of an ionization chamber [22].

When a charged particle crosses the sensor, it ionizes the gas generating ion-electron pairs. The electric field applied to the sensor drifts the charge carriers towards the electrodes. For gas detectors, the charge generated in the primary ionization is typically too small to be efficiently detected, so it is first transferred to a region where a higher electric field starts the avalanche multiplication process. For instance, in a Gas Electron Multiplier (GEM) detector the avalanche multiplication occurs inside the holes. According to the Ramo Theorem [25], the electrical signal observed by the front-end electronics originates from the induction of the charge carriers that move towards the electrodes. By integrating the signal current it is possible to retrieve the signal charge, which is proportional to the energy released by the impinging particle.

It must be pointed out that in order to measure the total charge all carriers have to be collected. A front-end electronics with an integration time smaller than the detector charge collection time will hence incur in the so called ballistic deficit, where only a part of the charge is measured. The fraction of charge that is lost fluctuates, thus introducing a dispersion in the amplitude of the signal measured at the front-end output.

For instance, in gas detectors the ions low mobility, which can be three order of magnitude smaller than the one of electrons, produces very slow signal components. Some systems, like GEM detectors, address this issue by connecting the front-end electronics only to the electrode where the electrons are collected, so that the ions signals

are not readout.

Since it has an impact on the analogue front-end implementation, it is crucial to model the electrical behavior of the sensor. To draw the detector equivalent circuit one must consider that in real applications one electrode of the detector is connected to a high voltage supply, which is usually filtered to reduce noise, while the other is connected to the front-end amplifier input.

In the configuration shown in Figure 2.3, the negative HV power supply moves the electrons towards the upper electrode. As a consequence the negative charges on this electrode are forced to move towards the amplifier input, generating a negative signal at its input node. Electric circuits models represent a current as a flow of positive charges, hence the electrons flowing towards the amplifier input can be seen as positive charges moving in the opposite direction and they can be represented as a time-dependent current source, whose shape depends on several factors such as the position of charge deposition, the sensor material properties, the applied bias voltage and the detector geometry. The sensor can be thus modeled as a capacitor, with the sensing medium as the dielectric, and with a current source in parallel.

Figure 2.3: Signal collection with negative HV.

## 2.1.2 Input stage

The "pre-amplifier" provides the electronics interface to the sensor. It must convert the small current signal coming from the detector into a signal suitable for the next stage of the readout chain. It is typically located as close as possible to the detector to minimize the electronic noise introduced by the connection lines from the sensor to the amplifier input.

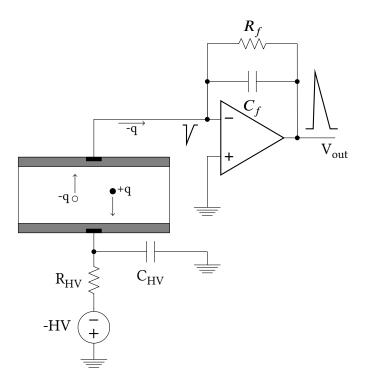

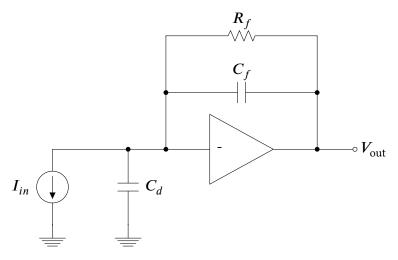

One of the most used configuration for sensor readout is the charge-sensitive amplifier (CSA), shown in Figure 2.4. It consists of an inverting high-gain voltage amplifier and a feedback capacitor,  $C_f$ , connected between the input and the output of the amplifier.

In order to write the transfer function of the pre-amplifier in Figure 2.4 some approximations can be done:

- The detector signal is modeled with a Dirac delta, as  $I_{in}(t) = Q_{in}\delta(t)$ . By doing this only the information about the total charge contained in the signal is kept.

- The core amplifier is assumed to be ideal, with infinite gain and bandwidth.

- The feedback resistance is chosen large enough so that it does not affect the signal processing. It only serves for establishing the correct DC bias point of the input transistor.

Figure 2.4: Charge Sensitive Amplifier (CSA) schematics.

Under these assumptions the pre-amplifier can be treated as an ideal integrator and

one can write:

$$V_{out}(t) = \frac{1}{C_f} \int I_{in}(t)dt = \frac{1}{C_f} \int Q_{in}\delta(t)dt = \frac{Q_{in}}{C_f}u(t)$$

(2.1)

where u(t) is the Heaviside step function. The response of an ideal CSA is therefore a voltage step, whose amplitude is inversely proportional to the feedback capacitance.

An important aspect of the CSA can be observed from this relationship. The charge gain of a CSA depends only on the value of its feedback capacitor which can be thus designed according to the specifications for the intended application. Thanks to the "virtual ground" action of the high-gain core amplifier, the gain of the CSA does not depend on the value of the detector capacitance,  $C_d$ .

Applying the Laplace transform, Equation (2.1) in the frequency domain becomes:

$$V_{out}(s) = \frac{I_{in}(s)}{C_f} \frac{1}{s}$$

(2.2)

The CSA can be seen as a transimpedance amplifier since it converts the sensor current into a voltage signal. Therefore its gain is commonly expressed in mV/fC units.

However, realistic amplifiers have finite gain and bandwidth. If the amplifier has a finite gain,  $A_0 = V_{out}/V_{in}$ , the input node is not anymore a "virtual ground" and Equation (2.1) becomes:

$$V_{out}(s) = I_{in}(s) \frac{A_0}{s \left[ C_d + C_f(1 + A_0) \right]}$$

(2.3)

If  $A_0 \gg 1$  and  $(1+A_0)C_f \gg C_d$  we find again the ideal result of Equation (2.2).

The charge coming from the detector,  $Q_{in}$ , is shared between the sensor capacitance  $C_d$  and the dynamic input capacitance  $C_{in} = (1 + A_0)C_f$ . The two terms can be written as:

$$\begin{cases}

Q_f = V_{in}(1+A_0)C_f \\

Q_d = V_{in}C_d

\end{cases}$$

(2.4)

where only  $Q_f$  is stored on  $C_f$ , thus contributing to the output signal, while  $Q_d$  is lost.

As a consequence, in order to readout a large fraction of the detector signal, the effective input capacitance of the CSA must be large compared to the sensor capacitance. In multi-channel systems, this issue can lead to cross-talk due to the fact that a fraction of the sensor capacitance comes from the coupling between one channel and its neighbors.

The finite bandwidth of a CSA affects the shape of the measured pulse, since it has not anymore a negligible rise time. This can be studied considering a simple amplifier made of an NMOS transistor with a load resistance  $R_L$  and an output capacitance  $C_L$ . The voltage gain of this inverting amplifier can be written as:

$$A_v = -g_m \frac{R_L}{1 + sR_L C_L} \tag{2.5}$$

where  $g_m$  is the transconductance of the input transistor and

$$Z_L = \left(\frac{1}{R_L} + sC_L\right)^{-1} = \frac{R_L}{1 + sR_LC_L} \tag{2.6}$$

is the load impedance given by the parallel combination of  $R_L$  and  $C_L$ . At low frequencies the second term is negligible and the gain is constant  $(A_v = -g_m R_L)$ , while at high frequencies the second term dominates and the gain decreases linearly with the frequency.

The cutoff frequency is where the asymptotic low and high frequency responses intersect and is determined by the output time constant  $\tau_L = R_L C_L$ :

$$f_u = \frac{1}{2\pi\tau_L} \tag{2.7}$$

In the time domain, this implies that when a voltage step is applied to the input of the amplifier, the output does not respond instantaneously, as the output capacitance must first charge up. The amplifier response to a signal step of amplitude  $V_0$  has therefore a finite rise time and can be expressed as:

$$v_{out}(t) = V_0 \left( 1 - e^{-\frac{t}{\tau}} \right)$$

(2.8)

In a continuous time system, the charge coming from multiple signals is integrated on the feedback capacitor,  $C_f$ . In order to avoid the saturation of the CSA output voltage, the capacitor must be discharged through  $R_f$ . Therefore, although very high,  $R_f$  can not be infinite and its effect on the signal must be considered. The feedback impedance of the CSA is now given by the parallel between  $R_f$  and  $1/(sC_f)$ :

$$Z_f = \frac{R_f}{1 + sR_f C_f} \tag{2.9}$$

The transfer function of the circuit becomes:

$$\frac{V_{out}}{I_{in}} = \frac{R_f}{1 + sR_fC_f + s^2 \frac{\zeta R_f}{g_{m1}}}$$

(2.10)

where  $g_{m1}$  is the transconductance of the input transistor of the amplifier,  $R_L$  and  $C_L$  are, respectively, the equivalent load resistance and capacitance and  $\zeta$  is given by:

$$\zeta = C_T C_L + C_T C_f + C_L C_f \tag{2.11}$$

$C_T$  is the total capacitance seen between the amplifier input and ground, in which the dominant contribution is usually given by the sensor.

Equation (2.10) can be approximated as:

$$\frac{V_{out}}{I_{in}} = \frac{R_f}{(1 + s\tau_f)(1 + s\tau_r)}$$

(2.12)

where:

$$\tau_r = \frac{\zeta}{g_{m1}C_f} \ll \tau_f = R_f C_f \tag{2.13}$$

The behavior of  $\tau_r$  can be analyzed in two limiting cases:

1. When

$$C_f \gg C_L$$

(and  $C_T \gg C_L$ )

$$\tau_r \approx \frac{C_T}{g_{m,1}} \eqno(2.14)$$

Here the speed of the circuit is weakly sensitive to the value of the feedback capacitor and mainly depends on the ratio between the total input capacitance and the transconductance of the input transistor.

2. When  $C_L \gg C_f$  (and  $C_T \gg C_f$ )

$$\tau_r \approx \frac{C_L C_T}{g_{m1} C_f} \tag{2.15}$$

On the contrary, the speed of the circuit is also limited by the ratio between the sensor and the feedback capacitance.

In both cases, if the sensor capacitance is increased, also the transconductance of the input transistor must be augmented to preserve the CSA speed. Sensors with large capacitances thus require more power to maintain adequate speed and noise performance

in the front-end.

Finally, Equation (2.12) in the time domain becomes:

$$v_{out}(t) = \frac{Q_{in}}{C_f} \frac{\tau_f}{\tau_r - \tau_f} \left( e^{-\frac{t}{\tau_r}} - e^{-\frac{t}{\tau_f}} \right)$$

(2.16)

From Equation (2.16) it can be observed that small  $\tau_f/\tau_r$  ratios lead to a significant attenuation of the output voltage, thus reducing the overall circuit gain.

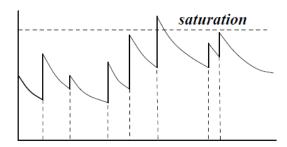

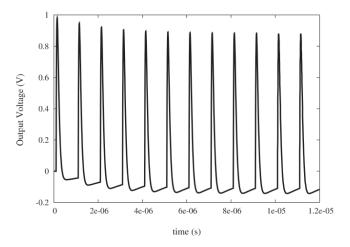

Figure 2.5 shows that high rates operation may cause the rising step of the next event to overlap with the exponential decay of the previous one, hence the CSA output does not return to the baseline and with a too high event rate the CSA may even reach its saturation point.

Figure 2.5: CSA pulses pile-up.

It must be taken into account that the pulses amplitudes carry the significant information, i.e. the charge deposited in the detector. Therefore, this issue can be addressed by shaping the pulses in such a way that their duration is reduced while their amplitude is not affected. Such signal filtering is typically carried out with a variety of RC shaper circuits.

## 2.1.3 Pulse shaping

Many applications require further signal conditioning which is implemented with a shaper stage connected at the pre-amplifier output. Its main task is to define the exact shape of the output signal in order to optimize the system performances in terms of signal-to-noise ratio and rate capability. The output signal shape should also be made insensitive to fluctuations in the input signal rise-time. In addition, it can provide a further signal amplification stage to optimize the front-end gain and match the input dynamic range requirements.

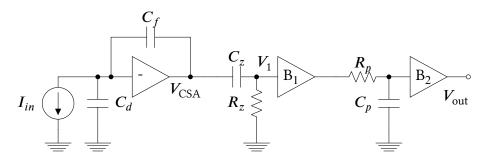

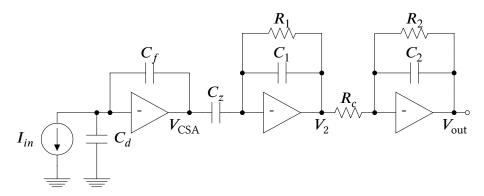

A simple pulse shaper connected at the output of the CSA is shown in Figure 2.6. Here a high-pass filter sets the duration of the pulse by introducing a decay time constant  $\tau_d$ , while a low-pass filter increases the rise time to limit the noise bandwidth. The filters are isolated by a voltage buffer to decouple the two time constants.

Figure 2.6: A simple CR-RC shaper using a CR "differentiator" as a high-pass filter and an RC "integrator" as a low-pass filter.

In the Laplace domain, the signal at the output of the high pass filter can be written as [23]:

$$V_1(s) = \frac{V_{CSA}}{s} \frac{sC_z R_z}{1 + sC_z R_z} = \frac{Q_{in}}{C_f} \frac{\tau_z}{1 + s\tau_z}$$

(2.17)

where  $V_{CSA} = Q_{in}/C_f$  and  $\tau_z = C_z R_z$ . The pole in the origin introduced by the CSA is canceled by the zero due to the high pass filter. In the time domain the expression becomes:

$$V_1(t) = \frac{Q_{in}}{C_f} e^{-t/\tau_z}$$

(2.18)