## POLITECNICO DI TORINO Repository ISTITUZIONALE

Design and test of readout electronics for medical and astrophysics applications

| Original Design and test of readout electronics for medical and astrophysics applications / Fausti, Federico (2018 Sep 14).             |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Availability: This version is available at: 11583/2713467 since: 2018-09-20T11:22:48Z                                                   |

| Publisher: Politecnico di Torino                                                                                                        |

| Published DOI:10.6092/polito/porto/2713467                                                                                              |

| Terms of use: openAccess                                                                                                                |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository |

|                                                                                                                                         |

| Publisher copyright thesis                                                                                                              |

| Da definire                                                                                                                             |

|                                                                                                                                         |

(Article begins on next page)

Doctoral Dissertation

Doctoral Program in Electrical, Electronics and Communications Engineering

with curriculum in "Electronic Devices" in convention with the National Institute for

Nuclear Physics (INFN) (30<sup>th</sup>cycle)

# Design and test of readout electronics for medical and astrophysics applications

By

#### Federico Fausti

\*\*\*\*\*

#### **Supervisor(s):**

Giovanni Mazza,

Italian National Institute for Nuclear Physics, Turin section

#### **Doctoral Examination Committee:**

Doctor U. Weber, Referee, GSI Helmholtz Centre for Heavy Ion Research, Darmstad Doctor S. Beolè, Referee, Turin University of Physics

Prof. M. Greco, Turin University of Physics

Prof. M. Martina, Polytechnic University of Turin

Prof. F. Bonani, Polytechnic University of Turin

Politecnico di Torino 2018

## **Declaration**

Federico Fausti 2018

<sup>\*</sup> This dissertation is presented in partial fulfillment of the requirements for **Ph.D. degree** in the Graduate School of Politecnico di Torino (ScuDo).

I would like to dedicate this thesis to some reference points, in my life:

to Giulia, my antiparticle, together we are brighting light

to my parents who always believed in me

and a special hug to anyone who gave me inspiration, a spark.

## Acknowledgements

I would like to acknowledge the Turin TERA group, especially my two Roberto whose suggestion convinced me in this great Ph.D. way. Thanks to the group members: Flavio, Vincenzo, Simona, Anna, Omar, Leslie, Mohammad, Felix, Lorenzo and Andrea. Feeling like home is not mandatory for a workplace but it is necessary, for a successful collaboration. I'm glad and thankful to Giuseppe Pittà, Marco Lavagno, and the DE.TEC.TOR. Devices and technologies Torino, for boosting my career with the TERA09 project; working for a young team, for its R&D core, has been a terrific experience for the fresh-Master-graduated me, who really needed a concrete goal while looking for a high-tech profile target. Thanks to all the Ufficio\_VLSI members, this place has been a solid but even sparkling spot, where I grew up shaping my technical knowledge, with the right motivation. Thanks to Jonhatan, Serena, Alessandra, Agostino and Fabio, the "senior colleagues"; thanks to Simona, Ramshan, Alejandro, Weishuai, Junying, Raffaele and Lorenzo, the new design force. Thanks to Gianni, my Ph.D. tutor, for the patient he had in the last four years and for being "the engineering point of view". Thanks for the kindness and the example given by Alexander and Pavel, my Russian Mini-EUSO colleagues, to Francesca for her strength and Mario for his generous professional sharing and for making this international collaboration possible. Another special thank goes to my martial art group and expecially to Master G. and Roberto with whom I spent so much time and shared much more than the sport passion.

Surfing this grateful wave, I'm glad and proud of being born in Brozzo, a very small village in Brescia province. Although the small boundary might appear too tight, I still need a reference frame that like me, helped other people to think broader. With Brozzo comes all the broad family including my parents, brother, sister, cousins aunts, uncles, grandparents and Giulia's family, that became part of my life.

I believe I took something good from each of you. I hope I left something in return.

#### **Abstract**

The applied particle physics has a strong R&D tradition aimed at rising the instrumentation performances to achieve relevant results for the scientific community. The know-how achieved in developing particle detectors can be applied to apparently divergent fields like hadrontherapy and cosmic ray detection. A proof of this fact is presented in this doctoral thesis, where the results coming from three different projects are discussed in likewise macro-chapters.

A brief introduction (Chapter 1) reports the basic features characterizing a typical particle detector system. This section is developed following the data transmission path: from the sensor, the data moves through the front-end electronics for being readout and collected, ready for the data manipulation. After this general section, the thesis describes the results achieved in two projects developed by the collaboration between the medical physics group of the University of Turin and the Turin section of the Italian Nuclear Institute for Nuclear Physics.

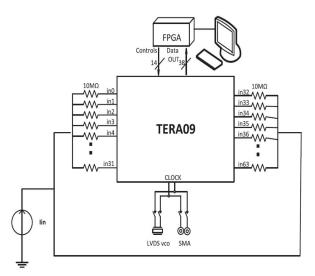

Chapter 2 focuses on the TERA09 project. TERA09 is a 64 channels customized chip that has been realized to equip the front-end readout electronics for the new generation of beam monitor chambers for particle therapy applications. In this field, the trend in the accelerators development is moving toward compact solutions providing high-intensity pulsed-beams. However, such a high intensity will saturate the present readout electronics. In order to overcome this critical issue, the TERA09 chip is able to cope with the expected maximum intensity while keeping high resolution by working on a wide conversion-linearity zone which extends from hundreds of pA to hundreds of  $\mu$ A. The chip gain spread is in the order of 1-3% (r.m.s.), with a 200 fC charge resolution. The thesis author took part in the chip design and fully characterized the device.

The same group is currently working on behalf of the MoVeIT collaboration for the development of a new silicon strip detector prototype for particle therapy applications. Chapter 3 presents the technical aspects of this project, focusing on the author's contribution: the front-end electronics design. The sensor adopted for the MoVeIT project is based on 50  $\mu$ m thin sensors with internal gain, aiming to detect the single beam particle thus counting their number up to  $10^9$  cm²/s fluxes, with a pileup probability < 1%. A similar approach would lead to a drastic step forward if compared to the classical and widely used monitoring system based on gas ionization chambers. For what concerns the front-end electronics, the group strategy has been to design two prototypes of custom front-end: one based on a transimpedance preamplifier with a resistive feedback and the other one based on a charge sensitive amplifier. The challenging tasks for the electronics are represented by the charge and dynamic range which are respectively the 3 - 150 fC and the hundreds of MHz instantaneous rate (100 MHz as the milestone, up to 250 MHz ideally).

Chapter 4 is a report on the trigger logic development for the Mini-EUSO detector. Mini-EUSO is a telescope designed by the JEM-EUSO Collaboration to map the Earth in the UV range from the vantage point of the International Space Station (ISS), in low Earth orbit. This approach will lay the groundwork for the detection of Extreme Energy Cosmic Rays (EECRs) from space. Due to its  $2.5 \,\mu s$  time resolution, Mini-EUSO is capable of detecting a wide range of UV phenomena in the Earth's atmosphere. In order to maximize the scientific return of the mission, it is necessary to implement a multi-level trigger logic for data selection over different timescales. This logic is key to the success of the mission and thus must be thoroughly tested and carefully integrated into the data processing system prior to the launch. The author took part in the trigger integration in hardware, laboratory trigger tests and also developed the firmware of the trigger ancillary blocks.

Chapter 5 closes this doctoral thesis, with a dedicated summary part for each of the three macro-chapters.

**Keywords**: Front-end; Readout electronics; ASIC; Trigger logic; Data management; Particle therapy; Cosmic ray detections.

# **Contents**

| Li                                               | st of I        | igures  |                                              | xiii |  |

|--------------------------------------------------|----------------|---------|----------------------------------------------|------|--|

| Li                                               | List of Tables |         |                                              |      |  |

| 1                                                | Introduction   |         |                                              |      |  |

| 2 Design and characterization of the TERA09 ASIC |                |         |                                              | 5    |  |

|                                                  | 2.1            | Introdu | uction                                       | . 5  |  |

|                                                  |                | 2.1.1   | The author's contribution                    | . 7  |  |

|                                                  | 2.2            | Interac | etion of photons and ions with matter        | . 7  |  |

|                                                  |                | 2.2.1   | The Bragg peak profile                       | . 11 |  |

|                                                  | 2.3            | Particl | e therapy: basic concepts                    | . 12 |  |

|                                                  |                | 2.3.1   | Technique overview                           | . 12 |  |

|                                                  |                | 2.3.2   | Ion accelerators in particle therapy         | . 14 |  |

|                                                  | 2.4            | Gas fil | led detectors                                | . 15 |  |

|                                                  |                | 2.4.1   | Gas filled detector operation modes          | . 16 |  |

|                                                  | 2.5            | Paralle | el plate ionization chambers                 | . 17 |  |

|                                                  |                | 2.5.1   | Advantages and drawbacks of ion chambers     | . 20 |  |

|                                                  |                | 2.5.2   | Collection efficiency in ionization chambers | . 21 |  |

|                                                  |                | 2.5.3   | Slow rate issues in ionization chambers      | . 22 |  |

|                                                  |                | 2.5.4   | Recombination rate                           | . 23 |  |

| Cantanta | <u>.</u> _  |

|----------|-------------|

| Contents | 12          |

| contents | <b>2</b> 23 |

|    |        | 2.5.5   | Collection efficiency in pulsed radiation beams | 24 |

|----|--------|---------|-------------------------------------------------|----|

|    |        | 2.5.6   | The multiple gap ionization chamber             | 26 |

|    | 2.6    | The TE  | ERA09 ASIC                                      | 31 |

|    |        | 2.6.1   | Motivations                                     | 31 |

|    |        | 2.6.2   | TERA09 circuit architecture                     | 32 |

|    |        | 2.6.3   | TERA09 OTA: design informations                 | 37 |

|    | 2.7    | The AS  | SIC characterization                            | 43 |

|    |        | 2.7.1   | Experimental setup                              | 43 |

|    |        | 2.7.2   | The TERA09 test board                           | 45 |

|    |        | 2.7.3   | Characterization results                        | 50 |

|    | 2.8    | Radiati | ion damage test                                 | 57 |

|    |        | 2.8.1   | Introduction                                    | 57 |

|    |        | 2.8.2   | Basis on Single Event Effects in CMOS           | 58 |

|    |        | 2.8.3   | SEU test setup                                  | 60 |

|    |        | 2.8.4   | Results and data analysis                       | 65 |

|    |        | 2.8.5   | Expected SEU rate in a clinical room            | 67 |

|    | 2.9    | TERA    | 09 Front-End board                              | 69 |

|    | 2.10   | Summa   | ary                                             | 72 |

| Re | eferen | ces     |                                                 | 73 |

| 3  | Desig  | gn of a | single ion discriminator for hadrontherapy      | 76 |

|    | 3.1    | Introdu | action                                          | 76 |

|    |        | 3.1.1   | The author's contribution                       | 78 |

|    | 3.2    | The M   | oVeIT single ion counter: general aspects       | 78 |

|    | 3.3    | Silicon | detector basis                                  | 79 |

|    | 3.4    | UFSD    | as LGAD evolution                               | 80 |

**x** Contents

|      | 3.4.1 UFSD issues and mitigation solutions 82 |

|------|-----------------------------------------------|

| 3.5  | UFSD design and simulation                    |

| 3.6  | Radiation damage and hardening                |

| 3.7  | UFSD productions                              |

| 3.8  | UFSD coupled amplifiers                       |

| 3.9  | Electronic noise: general considerations      |

| 3.10 | Beam test with UFSD pads                      |

| 3.11 | UFSD for MoVeIT                               |

| 3.12 | The ABACUS design                             |

|      | 3.12.1 Introduction                           |

|      | 3.12.2 ASIC overview                          |

|      | 3.12.3 Preamplifier                           |

|      | 3.12.4 Buffer                                 |

|      | 3.12.5 Discriminator                          |

|      | 3.12.6 Local threshold DAC control            |

|      | 3.12.7 Pulse generator                        |

|      | 3.12.8 Recovery system                        |

|      | 3.12.9 The CML driver                         |

| 3.13 | ABACUS layout                                 |

|      | 3.13.1 Introduction and general aspects       |

|      | 3.13.2 Layout view                            |

|      | 3.13.3 Power domain splitting                 |

|      | 3.13.4 Substrate noise coupling mitigation    |

|      | 3.13.5 Discrimination capability              |

| 3.14 | Summary                                       |

|      |                                               |

References

160

Contents

| 4  | The    | Mini-E  | EUSO multi-level trigger integration and testing     | 163   |

|----|--------|---------|------------------------------------------------------|-------|

|    | 4.1    | Introd  | uction                                               | . 163 |

|    |        | 4.1.1   | The author's contribution                            | . 164 |

|    | 4.2    | Mini-I  | EUSO in the behalf of the JEM-USO collaboration      | . 165 |

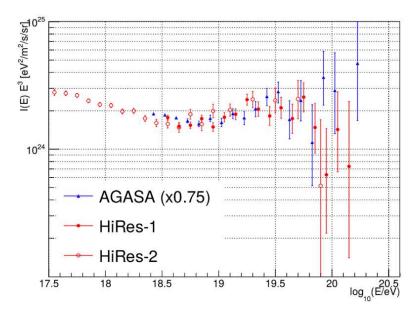

|    | 4.3    | The sc  | cientific scenario and motivations                   | . 166 |

|    |        | 4.3.1   | UHECRs: basic concepts                               | . 167 |

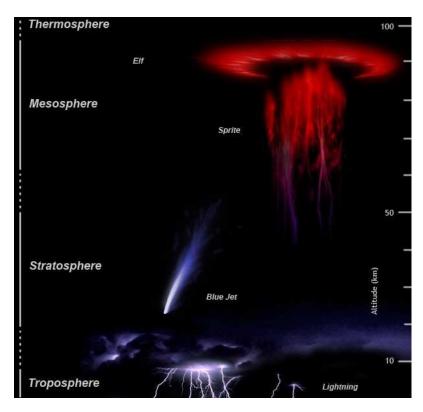

|    |        | 4.3.2   | TLEs: basic concepts                                 | . 170 |

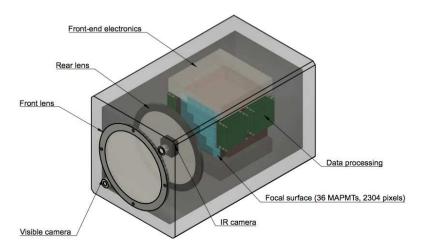

|    | 4.4    | The M   | Iini-EUSO telescope: Instrument overview             | . 173 |

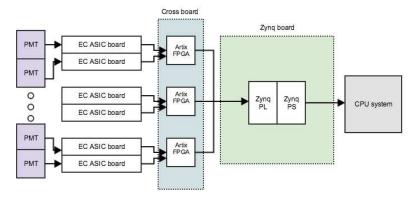

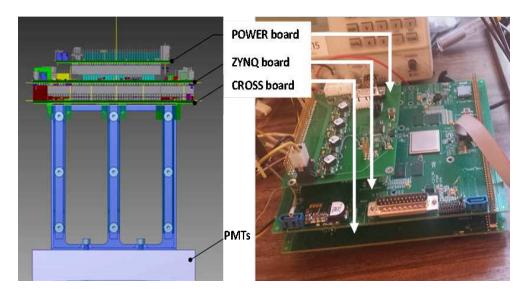

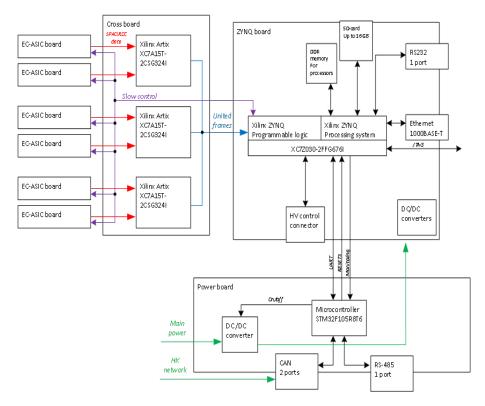

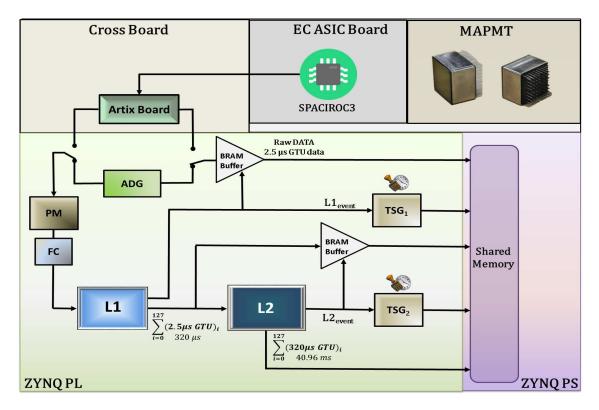

|    |        | 4.4.1   | The digitization data path                           | . 174 |

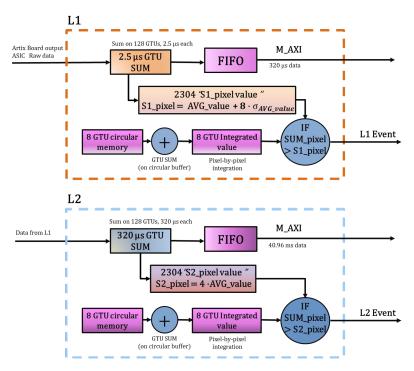

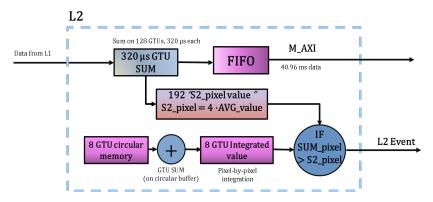

|    |        | 4.4.2   | The multi-level trigger                              | . 178 |

|    | 4.5    | Verific | cation of the trigger algorithm                      | . 181 |

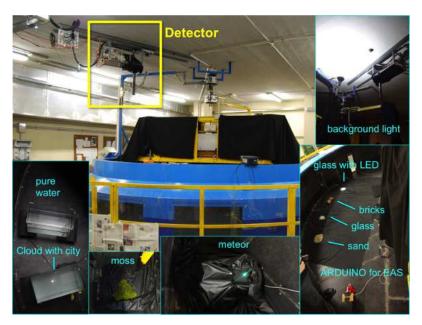

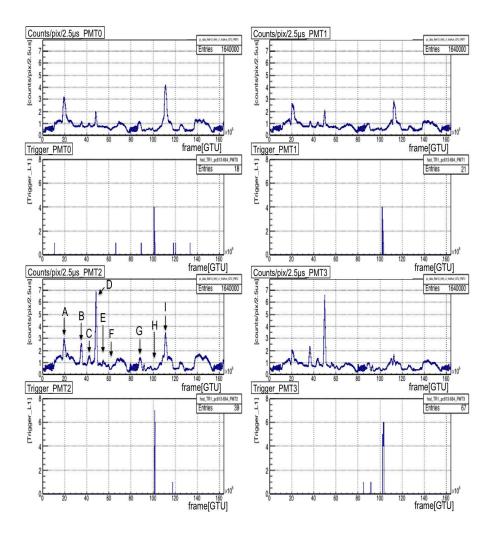

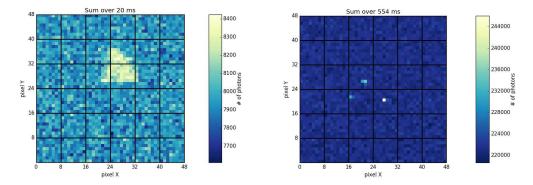

|    |        | 4.5.1   | L1 trigger tests at TurLab                           | . 182 |

|    |        | 4.5.2   | L1 trigger tests with ESAF                           | . 185 |

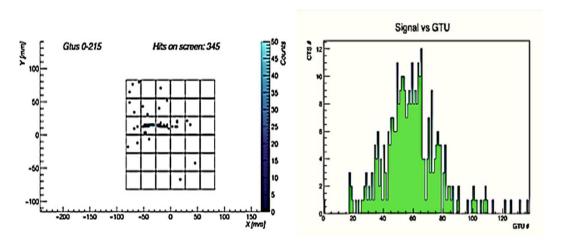

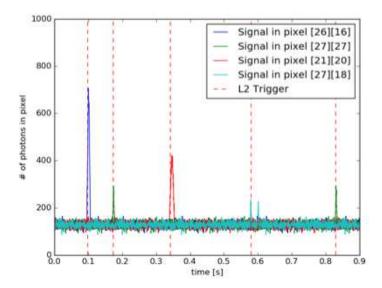

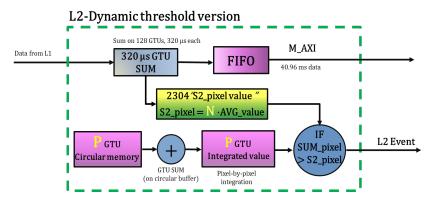

|    |        | 4.5.3   | L2 trigger tests                                     | . 186 |

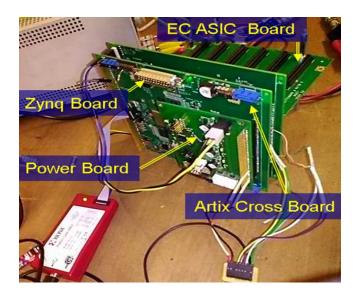

|    | 4.6    | Trigge  | er implementation in the Engineering Model hardware  | . 189 |

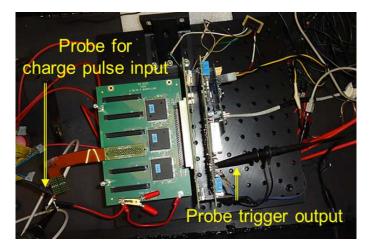

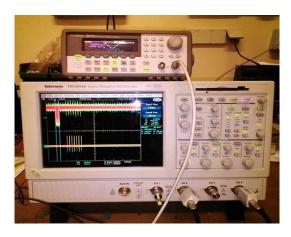

|    |        | 4.6.1   | First tests                                          | . 189 |

|    |        | 4.6.2   | Pulse generator as signal source: setup and outcomes | . 189 |

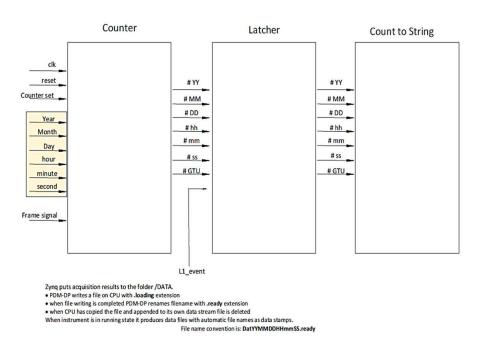

|    |        | 4.6.3   | Trigger ancillary IP blocks                          | . 192 |

|    | 4.7    | Trigge  | er logic improvements                                | . 196 |

|    |        | 4.7.1   | Dynamic threshold setting                            | . 196 |

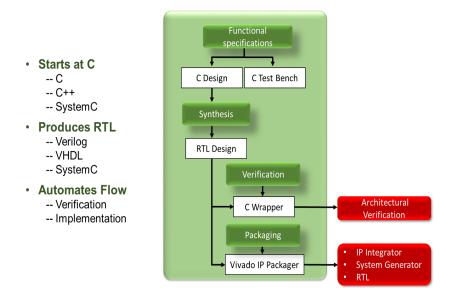

|    |        | 4.7.2   | High Level Synthesis trigger implementation          | . 197 |

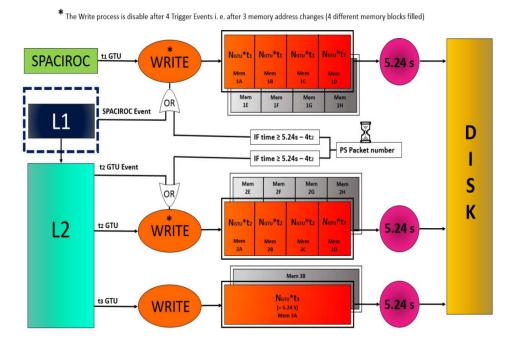

|    |        | 4.7.3   | Further upgrading idea: multiple events recording    | . 198 |

|    | 4.8    | Projec  | et status summary                                    | . 202 |

|    | 4.9    |         | nary                                                 |       |

|    |        |         |                                                      |       |

| Re | eferen | ces     |                                                      | 204   |

| 5 Conclusions |      |                                             |     |  |

|---------------|------|---------------------------------------------|-----|--|

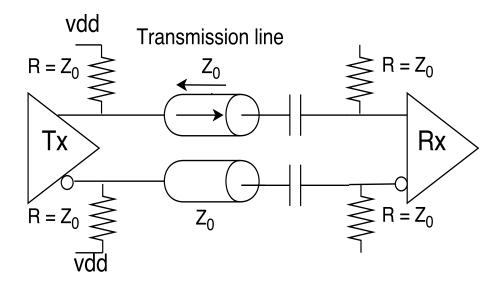

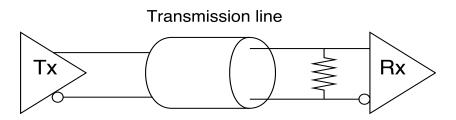

| Aŗ            | pend | ix A High speed signal transmission formats | 212 |  |

|               | A.1  | Current Mode Logic (CML)                    | 212 |  |

|               | A.2  | Low Voltage Differential Signaling (LVDS)   | 214 |  |

|               | A.3  | Scalable Low Voltage Signaling (sLVS)       | 215 |  |

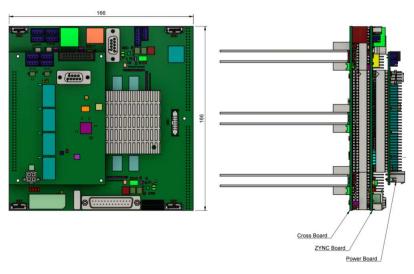

# **List of Figures**

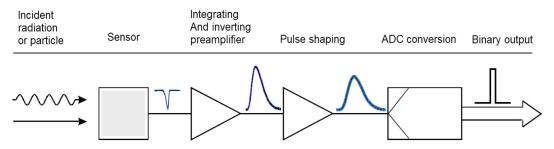

| 1.1 | Basic detector functions: radiation is absorbed in the sensor and converted into an electrical signal. This low-level signal is integrated in a preamplifier, fed to a pulse shaper, and then digitized for subsequent storage and analysis                                                                        | 2  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

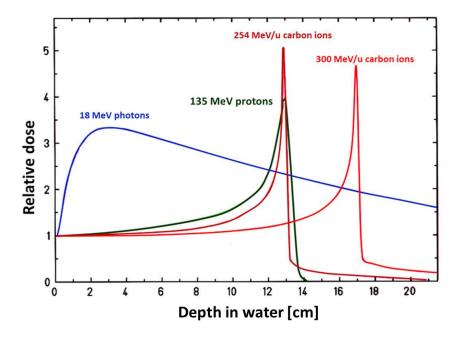

| 2.1 | Depth-dose distributions of protons, carbon ions and photons in water.                                                                                                                                                                                                                                             | 8  |

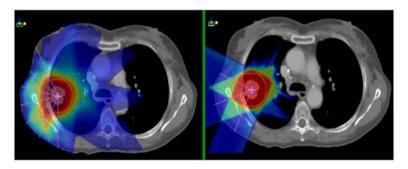

| 2.2 | Explicative computed tomography picture showing the selectivity differences between photons (left) and protons (right)                                                                                                                                                                                             | 9  |

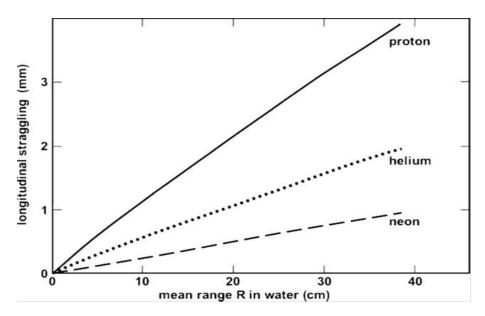

| 2.3 | Straggling effect highlighted comparing proton helium an neon beams in water                                                                                                                                                                                                                                       | 10 |

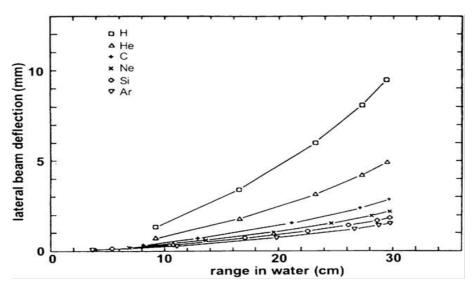

| 2.4 | The deflection of a beam with the increasing path length                                                                                                                                                                                                                                                           | 11 |

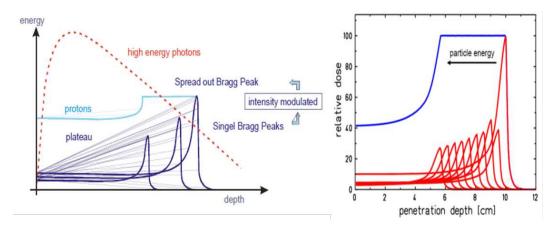

| 2.5 | Comparison between the photon dose distribution and a SOBP (left).  SOBP principle: the distal peak has the highest amplitude (right).  Picture taken from [10]                                                                                                                                                    | 13 |

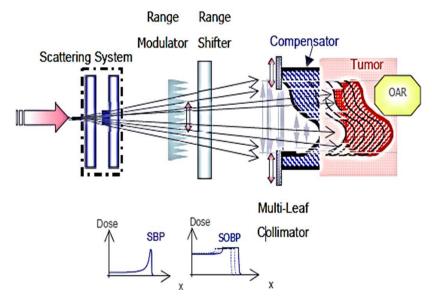

| 2.6 | Drawing of a passive modulating system. The transverse distribution is modeled with spreading scatterers. A Ridge filter followed by a range shifter provides the correct energy and depth for the SOBP components. The distal profile is then shaped with a properly modeled compensator. Picture taken from [10] | 14 |

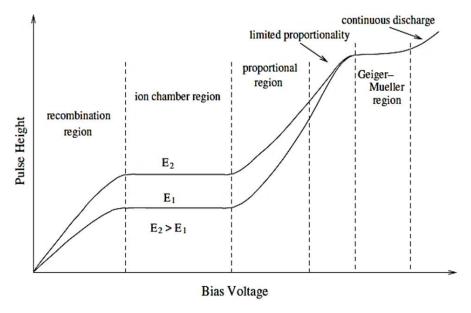

| 2.7 | Operation regions for a gas filled detectors. The pulse height depends on the bias voltage which define the detector mode of operation. $E_1$ and $E_2$ represents radiation with different energies. Picture taken                                                                                                |    |

|     | from [11]                                                                                                                                                                                                                                                                                                          | 16 |

**xiv** List of Figures

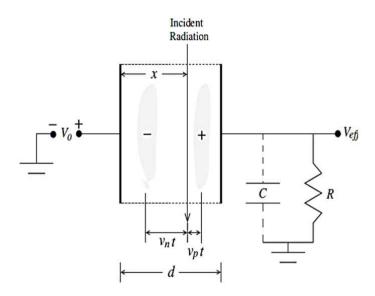

| 2.8  | Schematic representation of a parallel plate gas-filled ionization chamber. Considering a higher electron mobility they spread in a larger volume than positive ions; this is the reason why a larger negative zone is depicted                                                                                                                                                                                              | 17 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

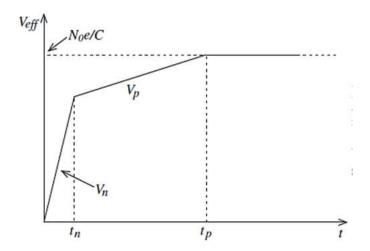

| 2.9  | Ideal representation of a pulse profile in a parallel plate ionization chamber. Electrons and ions shapes with different gradient, due to the mass difference and thus the different collection speeds. $V_n$ and $V_p$ are the signal amplitudes related to negative and positive charges respectively. Picture taken from [11]                                                                                             | 19 |

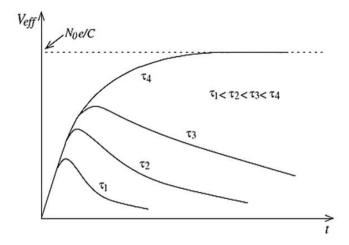

| 2.10 | Pulse profile representation. The smoother shapes (respect to Figure 2.9) are due to the difference between the detector time constant and the charge collection period. Picture taken from [11]                                                                                                                                                                                                                             | 20 |

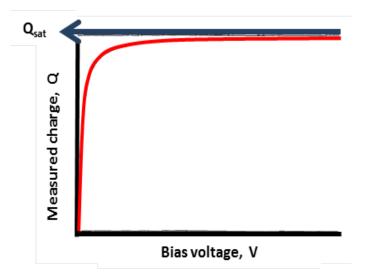

| 2.11 | Typical plot of measured charge $Q$ as a function of the chamber polarizing potential $V$ . The measured charge increases almost linearly for low voltages and approaches asymptotically the saturation charge $Q_{sat}$ at higher voltages                                                                                                                                                                                  | 21 |

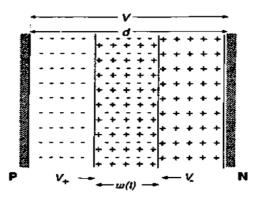

| 2.12 | Schematic diagram of a parallel-plate chamber in which a pulsed radiation beam has produced a uniform distribution of positive and negative charges. Positive charges drift toward the negative electrode N with velocity $V^+$ , while negative charges drift toward the positive electrode P with velocity $V^-$ . Charge recombination is possible only in the overlap region having a width $w$ chat decreases with time | 24 |

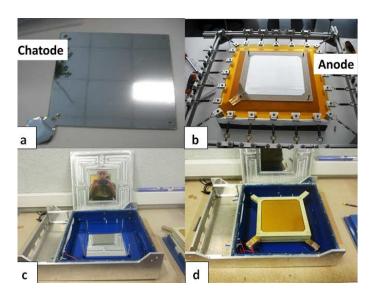

| 2.13 | Double gap chamber realized by INFN and University of Turin. a) cathode, made of aluminum deposited over a thin layer of mylar; b) anode, made in aluminum deposited over a layer of kapton; c) empty chamber box; d) the assembled double gap ionization chamber                                                                                                                                                            | 27 |

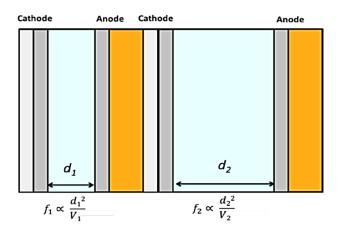

| 2.14 | Double gap chamber: conceptual representation                                                                                                                                                                                                                                                                                                                                                                                | 29 |

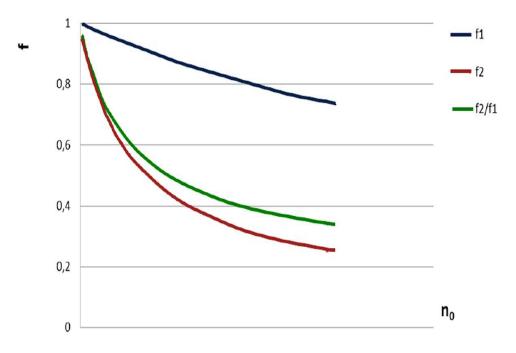

| 2.15 | Example of the graph used for the collection efficiency estimation                                                                                                                                                                                                                                                                                                                                                           | 31 |

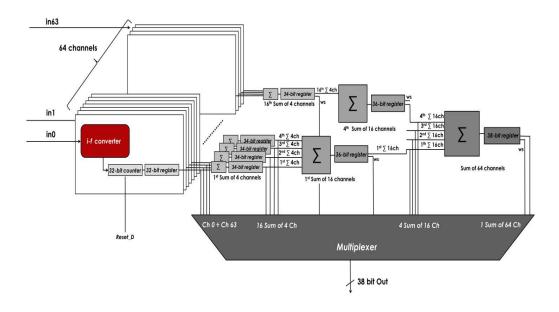

| 2.16 | TERA09: functional blocks representation                                                                                                                                                                                                                                                                                                                                                                                     | 33 |

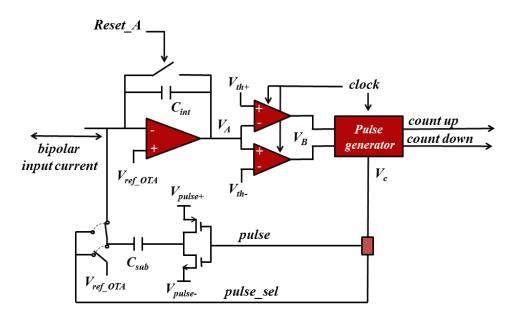

| 2.17 | Block diagram of the TERA09 electrical current-to-pulse converter.                                                                                                                                                                                                                                                                                                                                                           | 34 |

List of Figures xv

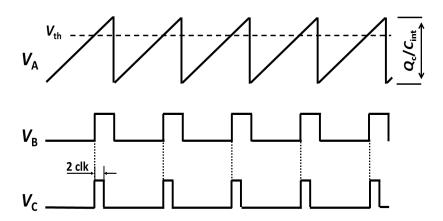

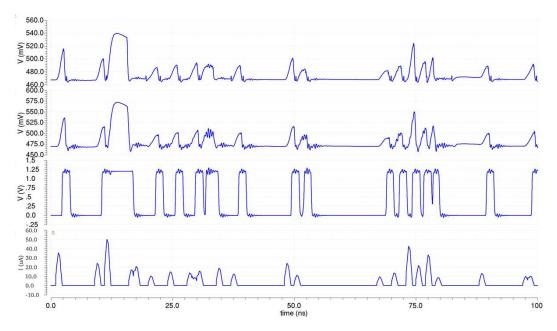

| 2.18 | Voltage waveforms at the output of the charge integrator $(V_A)$ , the comparator $(V_B)$ and the pulse generator $(V_C)$ for a constant negative input current                                                                                                                                                                                                                                           | 35 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.19 | Diagram of the circuit for the discharge of the integrating capacitor.                                                                                                                                                                                                                                                                                                                                    | 35 |

| 2.20 | Example of voltage waveforms of the two pulses used by the circuit for the discharge of the integrating capacitor                                                                                                                                                                                                                                                                                         | 36 |

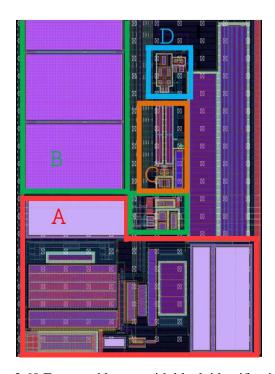

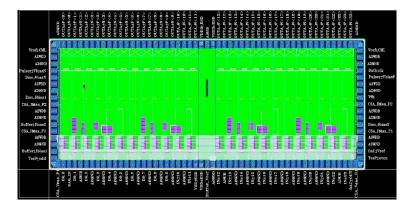

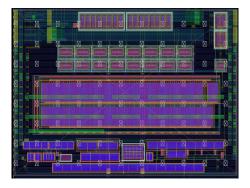

| 2.21 | Layout top view of the TERA09 ASIC                                                                                                                                                                                                                                                                                                                                                                        | 37 |

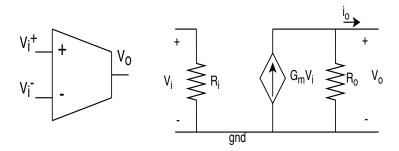

| 2.22 | OTA conventional symbol (left) and equivalent circuit representatin (right)                                                                                                                                                                                                                                                                                                                               | 38 |

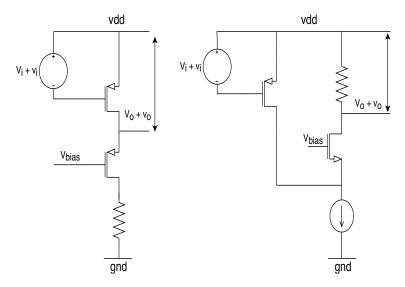

| 2.23 | Schematic representation of the conventional cascode scheme (left) and the folded cascode one (right). In both the cases the current in the MOSFET drain of the transistor closer to vdd is directly transferred to the second transistor.                                                                                                                                                                | 39 |

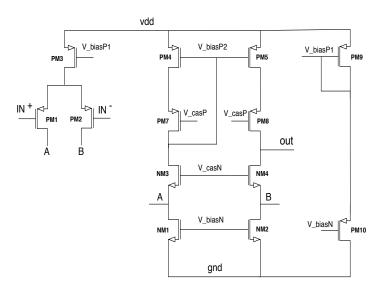

| 2.24 | Schematic representation of the TERA09 Folded Cascode amplifier.                                                                                                                                                                                                                                                                                                                                          | 39 |

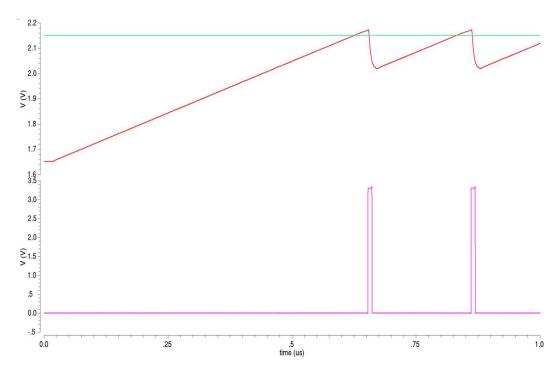

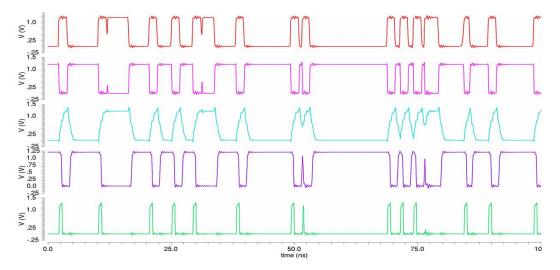

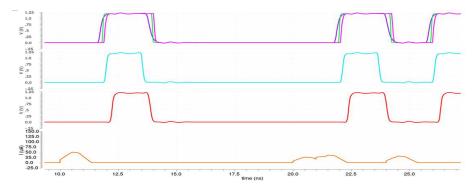

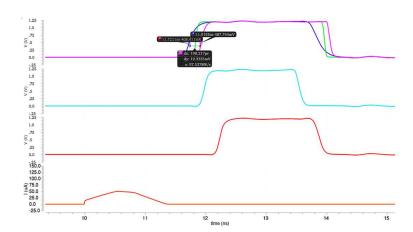

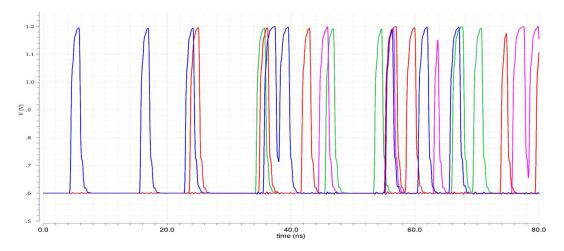

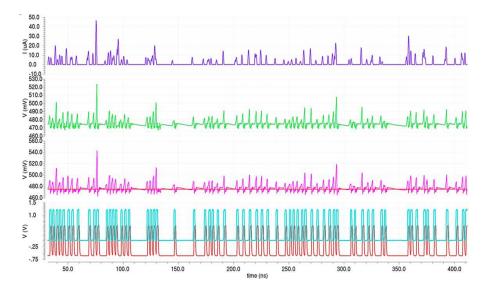

| 2.25 | Schematic simulation result showing the recycling integrator architecture in action. The TERA09 channel is here fed with a $1\mu A$ input current and the system clock is set at 250 MHz. The red curve is the OTA output voltage ramp which is brought under threshold (in green), subtracting a 200 fC charge quantum. The digitized output is reported in the lower part of the picture, in violet     | 42 |

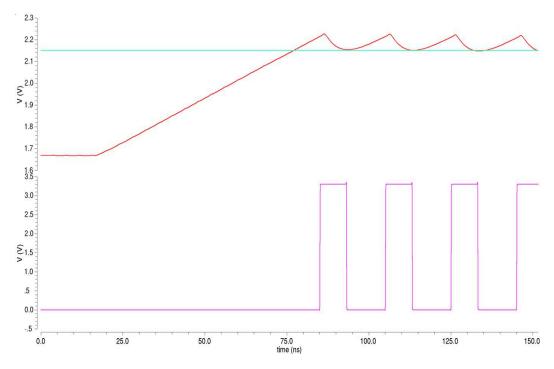

| 2.26 | Schematic simulation result showing the recycling integrator architecture in action. The TERA09 channel is here feeded with a $10\mu A$ input current and the system clock is set at 250 MHz. The red curve is the OTA output voltage ramp which is brought under threshold (in green), subtracting a 200 fC quantum charge. The digitized output is reported in the lower part of the picture, in violet | 43 |

| 2.27 | Schematic representation of the acquisition setup where 64 channels are connected in parallel to the current source.                                                                                                                                                                                                                                                                                      | 44 |

xvi List of Figures

| 2.28 | Fan-in boards with the surface mounted resistors for the TERA09 channel parallel connection. The connector adapted to the PCB inputs is visible in green, on the left side of the photo; on the right, it is possible to appreciate the SMD resistors and the jumpers with black hats which are used to physically close (or not) the electric paths.                                                                                  | 44 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.29 | The 160 pins MQFP socket open (left) and close (right). A mechanical pressure of the top cover, guarantee the electrical contact between the ASIC pins and the socket ones.                                                                                                                                                                                                                                                            | 45 |

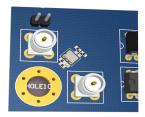

| 2.30 | 3D model detail for the VCO-SMA clock source splitting. The SMAs are represented with the withe round components and the oscillator with LVDS output is placed between them                                                                                                                                                                                                                                                            | 46 |

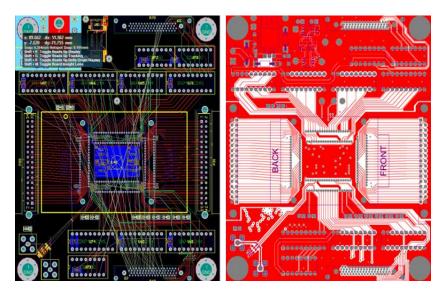

| 2.31 | Test board design views. Floor plan view (left). Gerber file of the top layer (right)                                                                                                                                                                                                                                                                                                                                                  | 46 |

| 2.32 | 3D model or rendering of the TERA09 test board. The chip inputs are routed through flat cables on the lateral edges (represented in white). The upper part has the voltage references and the voltage regulator for the 5 V to 3.3 V levels; in the left-high corner, the connector for the external voltage supply is represented in green. In the left-lower corner of the picture, there is the VCO-SMA clock source splitting path | 47 |

| 2.33 | TERA09 register addressing bits                                                                                                                                                                                                                                                                                                                                                                                                        | 48 |

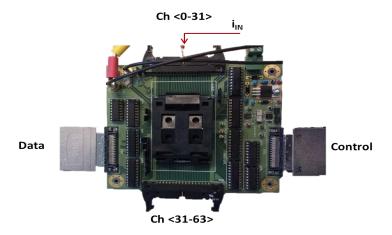

| 2.34 | TERA09 test board with the connector detail: two flat connectors for the 64 channel inputs (top and bottom), two VHDCI connectors for data and control management.                                                                                                                                                                                                                                                                     | 49 |

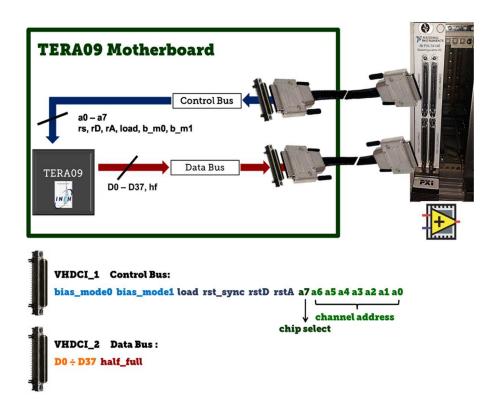

| 2.35 | Schematic representation of the ASIC-FPGA data exchange. The connection between the TERA09 test board (named Motherboard, in the picture) and the NI chassis are realized using VHDCI connectors.                                                                                                                                                                                                                                      | 50 |

| 2.36 | High density, 68 poles VHDCI connector                                                                                                                                                                                                                                                                                                                                                                                                 | 50 |

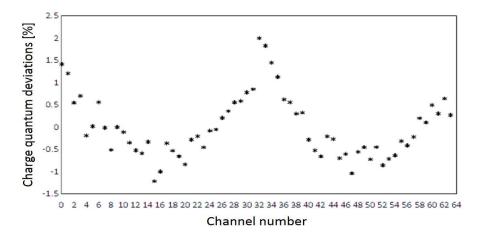

| 2.37 | Charge quantum relative deviations as a function of the input channel, obtained from $1\mu$ A input current measurements. Channels are numbered from 0 to 63                                                                                                                                                                                                                                                                           | 52 |

|      | numbered from 0 to 63                                                                                                                                                                                                                                                                                                                                                                                                                  | 32 |

List of Figures xvii

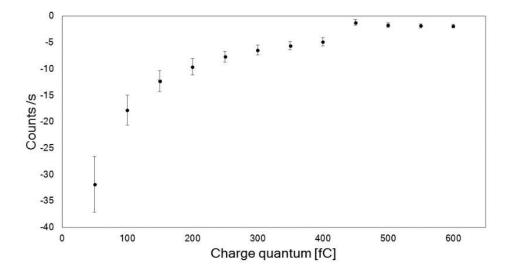

| 2.38 | Average background frequency as a function of the charge quantum Qc. The vertical bar indicates the standard deviation of the 64 channels of the chip.                                                                                                                                                                                                                   | 53 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

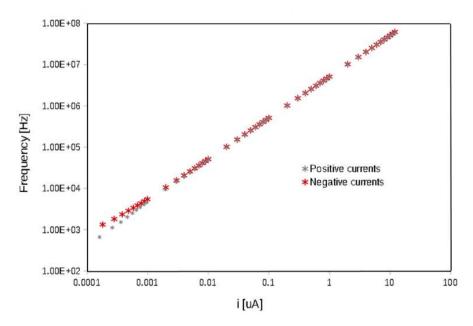

| 2.39 | Count frequency as a function of the absolute value of the input current for a single channel for a 200 fC charge quantum. Positive and negative currents are shown separately                                                                                                                                                                                           | 53 |

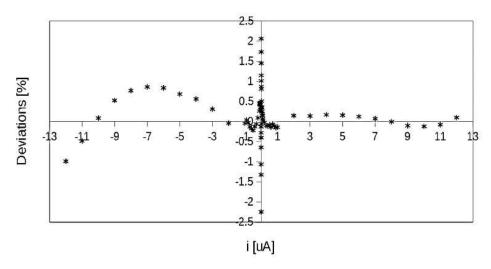

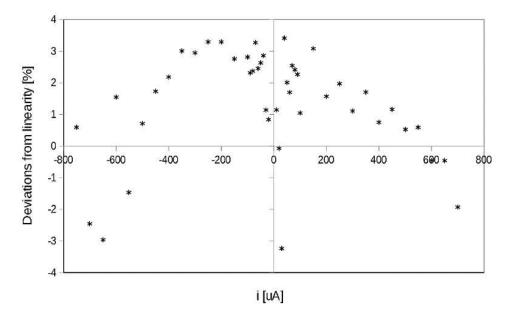

| 2.40 | Relative deviation from linearity as a function of the input current for the measurements reported in Figure 9                                                                                                                                                                                                                                                           | 54 |

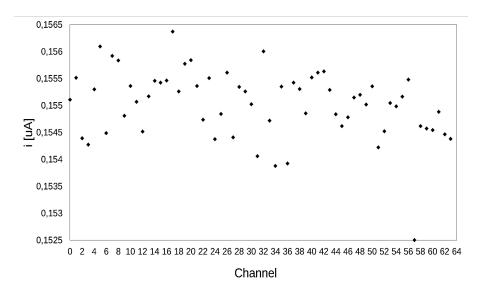

| 2.41 | Distribution of a 10 $\mu$ A input current among the 64 channels of the chip. Channels are numbered from 0 to 63                                                                                                                                                                                                                                                         | 55 |

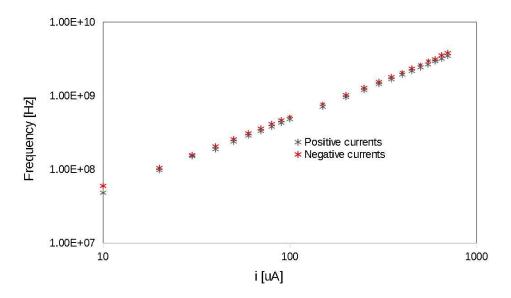

| 2.42 | Absolute value of the count frequency as a function of the absolute value of the input current for the sum of 64 channels, as described in the text. Positive and negative currents are shown separately                                                                                                                                                                 | 56 |

| 2.43 | Relative deviation from linearity as a function of the input current for the sum of 64 channels reported in Fig. 12                                                                                                                                                                                                                                                      | 56 |

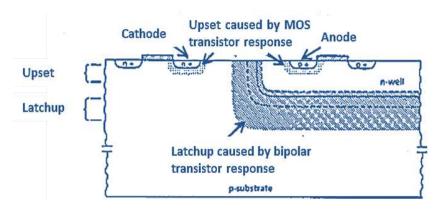

| 2.44 | Spatial distribution of different SEE: SEU are confined in the first micrometers thickness, under the device surface whereas the SEL are deeper in the silicon bulk                                                                                                                                                                                                      | 58 |

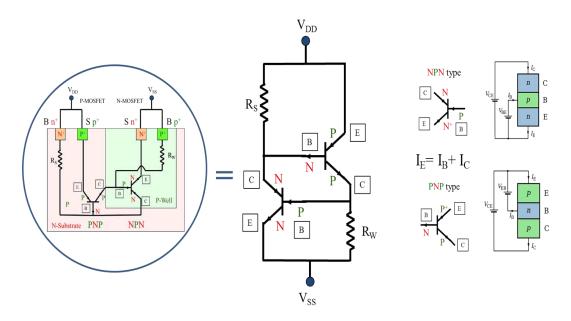

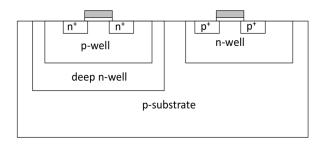

| 2.46 | Schematic representation of the thyristor-like path, responsible of SEL. From left to right: the CMOS n-p-n-p structure, the electric circuit and the BJT connections.                                                                                                                                                                                                   | 59 |

| 2.45 | The Single Event Lachup occurs in the deep volume of the silicon bulk. In a CMOS process, the combination of n-well, p-well and, substrate forms a parasitic n-p-n-p structure named thyristor. During a latch-up, both the MOSFETs are conducting resulting in a vdd-gnd short circuit. The permanent and destructive event can be avoided turning off the power supply | 59 |

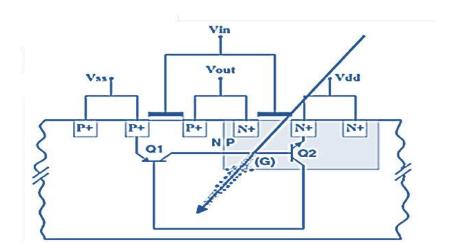

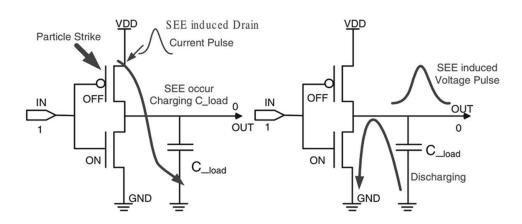

| 2.47 | Schematic representation of an inverter bit-flip due to a SEE                                                                                                                                                                                                                                                                                                            | 60 |

xviii List of Figures

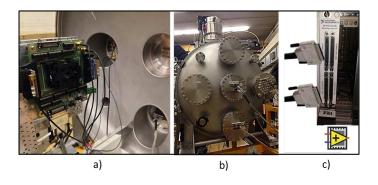

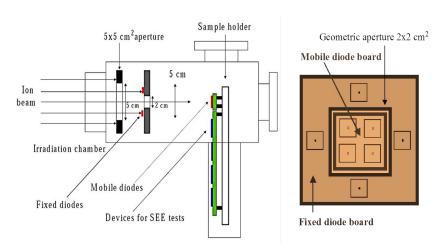

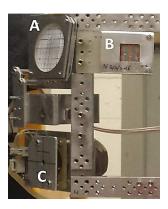

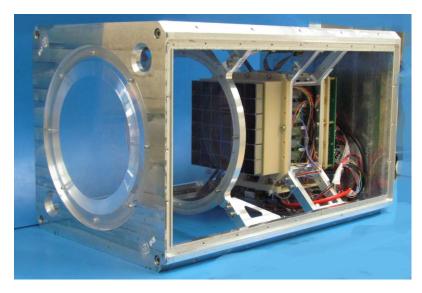

| 2.48 | <ul><li>a): The DUT thus the TERA09 ASIC carried by the PCB socket, fixed inside the vacuum chamber on the metal plate holder.</li><li>b): Vacuum chamber external flange connections.</li><li>c): VHDCI connectors carrying the ASIC data and controls to the National Instrument FPGA</li></ul>                                                                                                                                    | 61 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.49 | SEU DAQ graphical user interface. The left panel reports the number of counts for the 64 channels: after a first starting phase of current injection, the load signal (counters to registers latch) is turned off and the SEU test starts.                                                                                                                                                                                           | 62 |

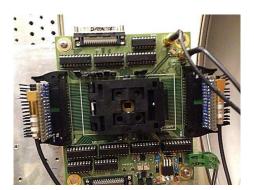

| 2.50 | SEU test setup: TERA09 test board with the current injection. The input current is equally split among all the 64 channels, thanks to custom upper boards with SMD resistors. An input current is needed to set the register values at random values before freezing them and then starting with the SEU test                                                                                                                        | 62 |

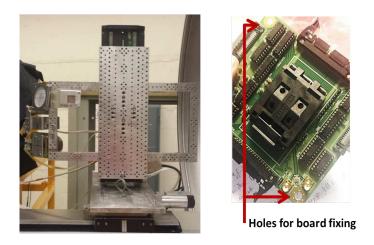

| 2.51 | Steel plate with 3-4 mm of diameter holes for the DUT holding (left). TERA09 test board with the holes in the corners for the mechanical fixing over the metal holder (right)                                                                                                                                                                                                                                                        | 63 |

| 2.52 | Schematic draw of the irradiation chamber with the dosimetry system and the device under test holder (left). Diodes geometry and placement scheme (right)                                                                                                                                                                                                                                                                            | 63 |

| 2.53 | Vacuum chamber inner photo: A) quartz; B) fixed diodes; C) mobile diodes                                                                                                                                                                                                                                                                                                                                                             | 64 |

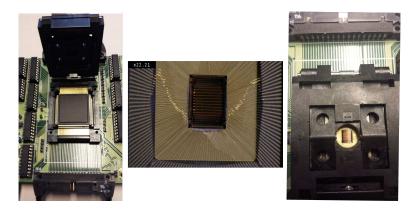

| 2.54 | The TERA09 test board with the socket hosting the ASIC open (left). Microscope picture of TERA09, after the ceramic lid removal (center). Hole in the cover lid of the ASIC carrier (right)                                                                                                                                                                                                                                          | 64 |

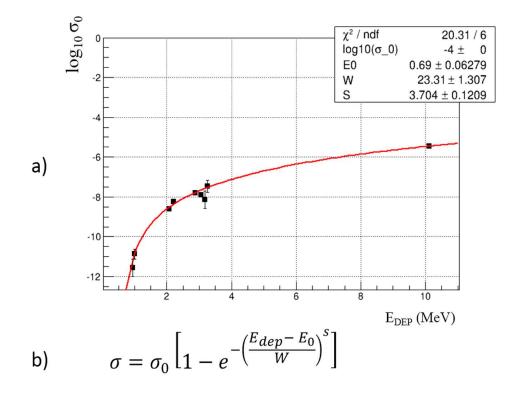

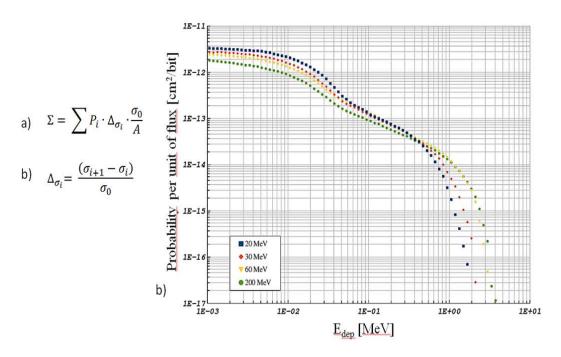

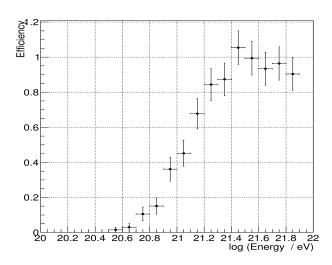

| 2.55 | a) SEU cross-section (y-axis) as a function of the deposited energy (x-axis). The fit has been performed using the Least Square Method.<br>b) Weibull function: $E_{DEP}$ is the energy deposited in the CMOS silicon; $E_0$ is the threshold energy to trigger a SEU event; $\sigma_0$ is the cross-section saturation that represent the situation when all the sensitive volumes are under SELL s and W are fit shape perpentage. | 66 |

|      | sensitive volumes are under SEU; s and W are fit shape-parameters.                                                                                                                                                                                                                                                                                                                                                                   | 00 |

List of Figures xix

| 2.56 | a): SEU cross section $\Sigma$ in the proton environment, where A is the cross-sectional area of the SV adopted.                                                                                                                                                                                                                                                                                                           |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | b): The increased cross section in the energy interval between two energy bin values i.                                                                                                                                                                                                                                                                                                                                    |    |

|      | c): Energy deposition probabilities for protons of different energies. The curve shows the probability to have within the SV an ionizing deposition greater or equal to the indicated $E_{DEP}$ . The curve selected for the data analysis is the one for 20 MeV protons (due to the average value in Figure 2.57), selecting the plot area from the threshold energy $E_0$ obtained with experimental data fit (0.69 MeV) | 68 |

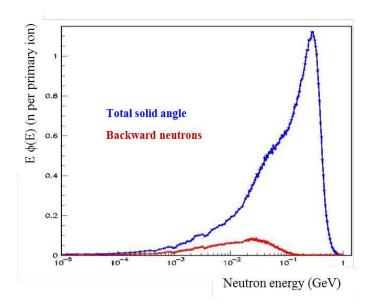

| 2.57 | Spectrum of secondary neutrons produced in the backward direction by 400 MeV/u carbon ions, hitting a phantom made of ICRU tissue; a comparison with the total energy spectrum of secondary neutrons is made                                                                                                                                                                                                               | 69 |

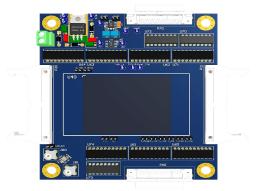

| 2.58 | The TERA09 front-end board hosting two ASICs is going to be the new monitor chamber readout electronics, adopted by DETECTOR Devices and Technology Torino                                                                                                                                                                                                                                                                 | 70 |

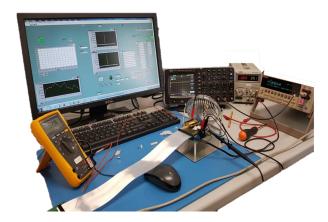

| 2.59 | TERA09 Front-End board characterization setup at DETECTOR laboratories                                                                                                                                                                                                                                                                                                                                                     | 71 |

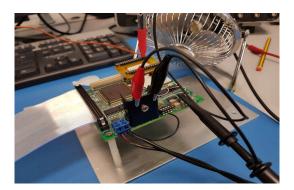

| 2.60 | TERA09 Front-End board characterization: power dissipation check.  The crocodiles probes detect the heat sink temperature                                                                                                                                                                                                                                                                                                  | 71 |

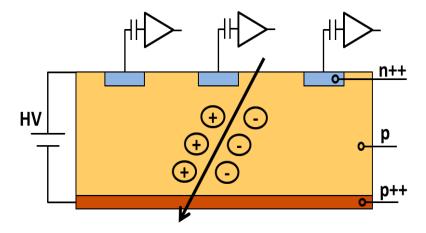

| 3.1  | Basic operational principles of a silicon detector: an external bias voltage polarizes inversely the p-n junction, creating a large depleted volume. When an incident charged particle crosses the sensor, it creates electron-hole pairs whose drift generates an induced current in the electronics                                                                                                                      | 80 |

| 3.2  | Qualitative drawing representing the comparison between a classical 300 $\mu m$ thick silicon sensor an a $50\mu m$ thick UFSD                                                                                                                                                                                                                                                                                             | 81 |

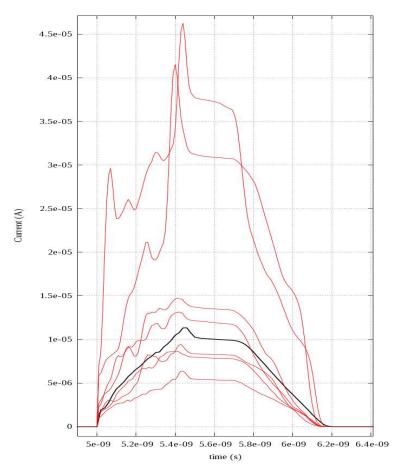

| 3.3  | Sensor signal for different charge values extracted from Landau distribution. The reference sensor is 50/mum thick and has a nominal gain factor of 15. The black line represents a MIP signal resulting in                                                                                                                                                                                                                |    |

|      | a peak current of $\sim$ 10 $\mu A$ for a 8 fC charge $\ .\ .\ .\ .\ .$                                                                                                                                                                                                                                                                                                                                                    | 83 |

xx List of Figures

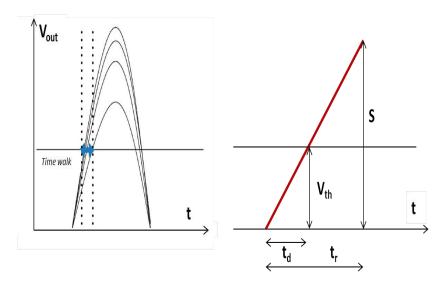

| 3.4  | Time Walk effect: geometrical explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 84 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

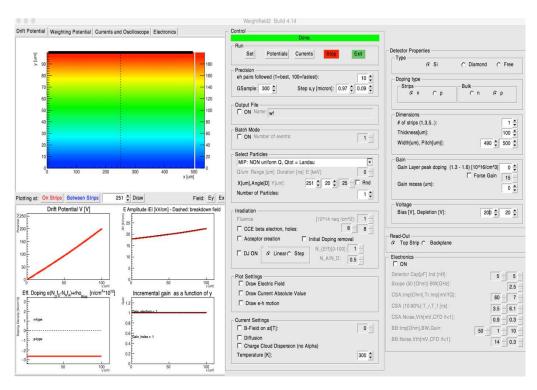

| 3.5  | Snapshot from the Weightfield2 graphical user interface. Figure taken with permission from [7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 86 |

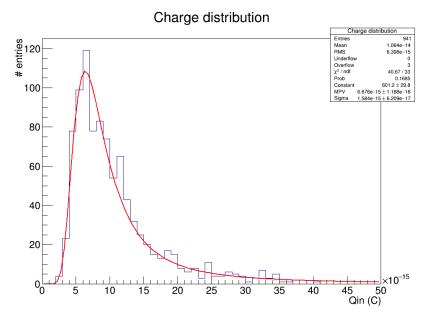

| 3.6  | Simulated input charge fitted with Landau distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 87 |

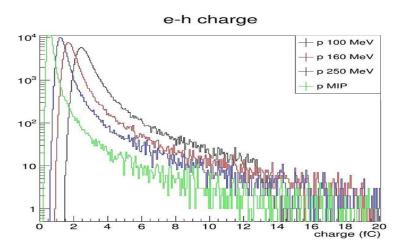

| 3.7  | Charge signal distributions, in a 50 $\mu$ m UFSD with gain 10. The different profiles represent 4 different proton projectiles energies: MIP equivalent, 100 MeV, 160 MeV and 250 MeV                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 88 |

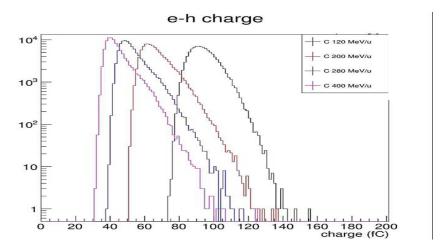

| 3.8  | Charge signal distributions, in a 50 $\mu$ m UFSD with no gain. The different profiles represent 4 different Carbon ion energies: 120 MeV/u, 200 MeV/u, 280 MeV/u and 400 MeV/u                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 88 |

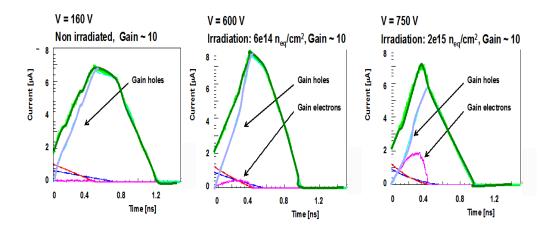

| 3.9  | 50 $\mu$ m UFSD current signals. Left: un-irradiated sensor with gain $\sim$ 10; center: UFSD current signal after a fluence $\phi$ = 6e14 neq / cm <sup>2</sup> ; right: UFSD current signal after a fluence $\phi$ = $2 \cdot 10^{15}$ n eq /cm <sup>2</sup> . Is it possible to notice than the decreasing of the current induced by trapping is higher for longer drift time, while the changes of the location where multiplication happens, from the gain layer to the bulk, affects the shape of the induced current signal since the contribution from gain electrons starts to be relevant. Figure taken with permission from [7] | 91 |

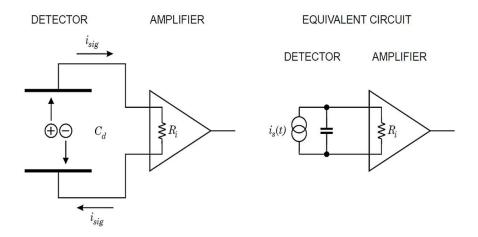

| 3.10 | The detector and amplifier (left) and the equivalent detector circuit (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 92 |

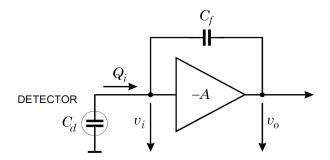

| 3.11 | Schematic representation of the charge sensitive amplifier topology.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 96 |

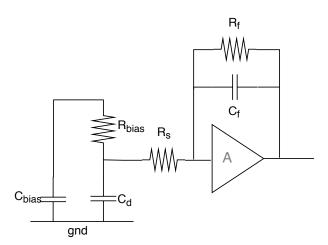

| 3.12 | Resistive and capacitive components in a generic sensor-amplifier connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 96 |

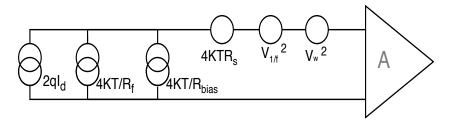

| 3.13 | Sensor-amplifier noise model: the spectral power density model representation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 97 |

| 3.14 | Test setup at CNAO: the squared black box fixed over the treatment bed contains two PCB mounting a 50 $\mu$ m thin UFSD pad each. the white device with a central metalized window is the beam monitor                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|      | chamber, placed at the end of the beam extraction line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 98 |

List of Figures xxi

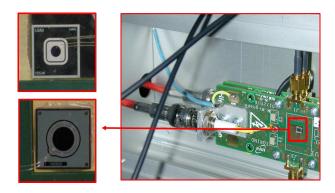

| 3.15 | Picture of the sensors mounted in a metallic box and aligned to the beam. Left-down corner: Hamamatsu sensor (1 mm Ø x 50 $\mu$ m thickness). Left-up corner: CNM sensor (1,2 x 1,2 x 50 $\mu$ m thickness). 99                                                                                                                                                                                                                                                    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

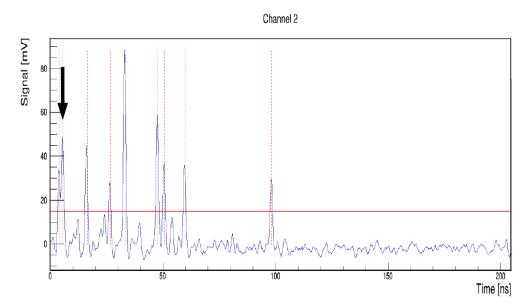

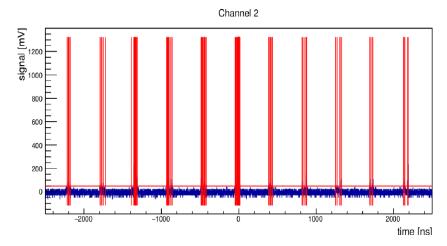

| 3.16 | A 200 ns snapshot acquired with the channel 2 of the digitizer. It is possible to estimate the nanosecond structure of the CNAO proton beam, looking at the tens of millivolts peaks, where each peak corresponds to a single ion signal. The black arrow highlights a pile-up event                                                                                                                                                                               |

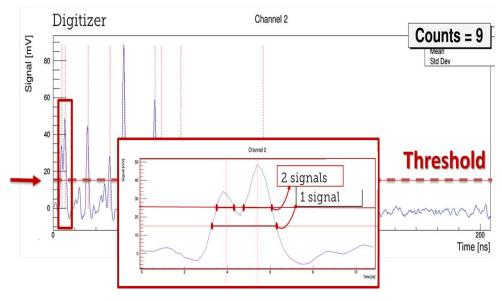

| 3.17 | Example of a 200 ns time window collected with the digitizer. The arrow points to a peak with pileup effect and the rectangular box zooms-in the area to underline the importance of the threshold selection in pileup situations                                                                                                                                                                                                                                  |

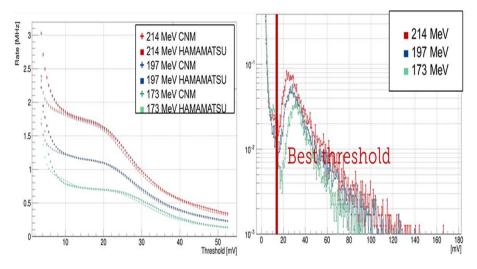

| 3.18 | On the left: rate versus threshold for three different energies, for both sensors (C = CNM at 250 V, H = Hamamatsu at 190 V). For low values of the threshold, a high contribution of the noise is clearly evident, while for high values of the threshold there is a significant loss of the signal. On the right: amplitude distribution of the signals for three different energies for the CNM sensor, in which the vertical scale is given in arbitrary units |

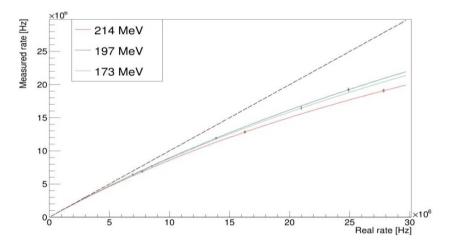

| 3.19 | Measured ion rate vs the expected one. The lack of efficiency is related to the fact that the particle beam distribution has been considered as Poissonian while, for the CNAO synchrotron, it is RF bunched with an istantaneous peak intensity higher than expected 102                                                                                                                                                                                          |

| 3.20 | The CNAO particle beam structure. The protons are collected in bunches distributed with a radio frequency given by the synchrotron. The instantaneous intensity reaches $10^{10} p \ cm^{-2} \ s^{-1}$ 102                                                                                                                                                                                                                                                         |

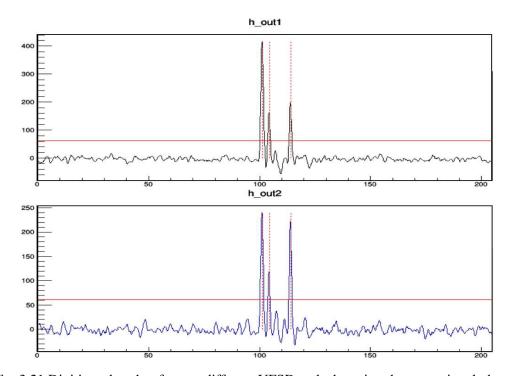

| 3.21 | Digitizer shapshot for two different UFSD pads detecting the same signal, thanks to a telescope setup. The simultaneous acquisition by two digitizer channels allows to appreciate the signal coincidences 103                                                                                                                                                                                                                                                     |

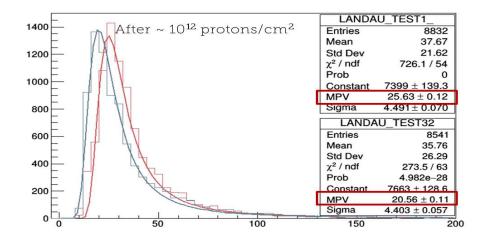

| 3.22 | The MPV value of the amplitude distribution passed from $25 \ 10^{-12}$ Vs before irradiation to $20 \ 10^{-12}$ Vs after 32 runs of proton irradiation $104$                                                                                                                                                                                                                                                                                                      |

**xxii** List of Figures

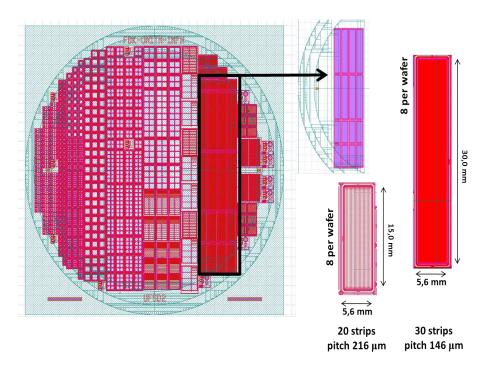

| 3.23 | UFSD strips for MoVeIT. On the left, the gerber file of the UFSD2 production wafer. On the right, the zoom-in on the MoVeIT sensors:                                                               |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | set of 20 short strips and set of 30 long strips                                                                                                                                                   |

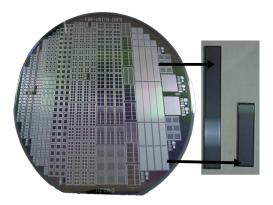

| 3.24 | Picture of the MoVeIT strips. On the left, the wafer from the UFSD2 production. On the right, the short and long type strips 107                                                                   |

| 3.25 | Test setup photo. From left to right: the microscope station, the probe card with the connector for the needles control, the needles zoom-in                                                       |

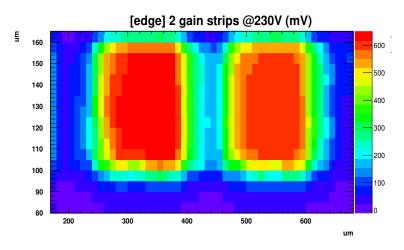

| 3.26 | Chromatic representation of the 2-D spatial distribution of the gain for a couple of strips biased at 230 V. The strips collected the charge as result of a laser shooting through the sensor edge |

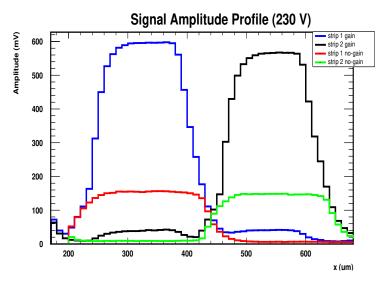

| 3.27 | Signal amplitude vs depth for a couple of strips biased at 230 V. The strips collected the charge as result of a laser shooting through the sensor edge                                            |

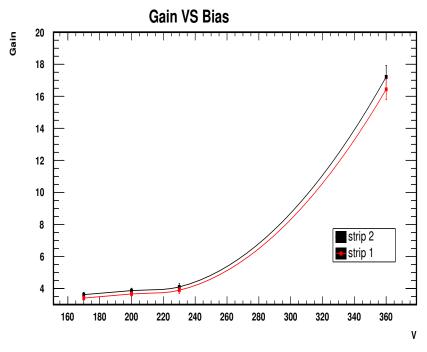

| 3.28 | Strip gain in function of the voltage, for a couple strips belonging to the same sensor                                                                                                            |

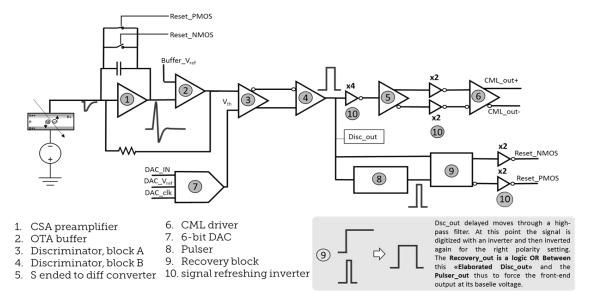

| 3.29 | Functional block representation of the ABACUS channel                                                                                                                                              |

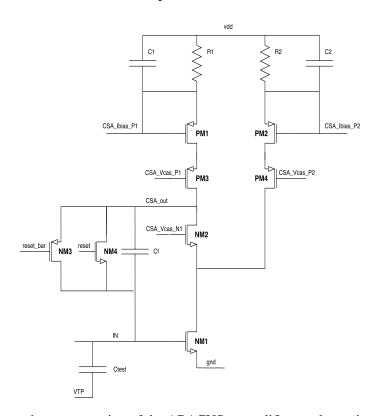

| 3.30 | Schematic representation of the ABACUS pramplifier, a telescopic cascode amplifier with split bias current and NMOS input transistor, working as CSA                                               |

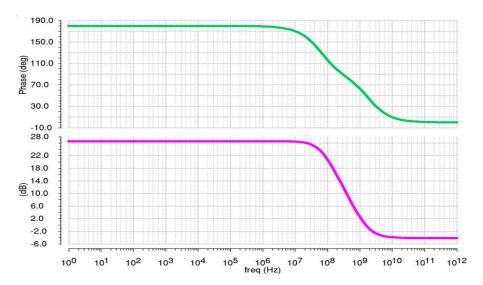

| 3.31 | Bode diagrams for the CSA representing the phase vs frequency (up) and the gain module in dB vs frequency (down)                                                                                   |

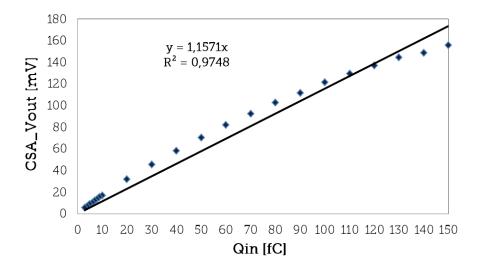

| 3.32 | Gain linearity performance of the CSA, in a 3 fC - 150 fC input charge range (schematic simulation)                                                                                                |

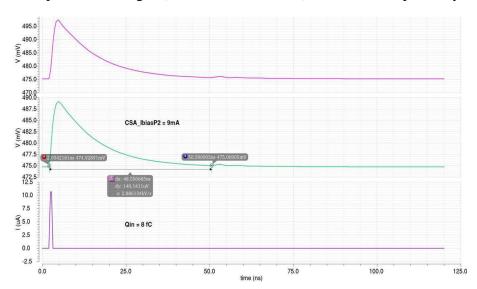

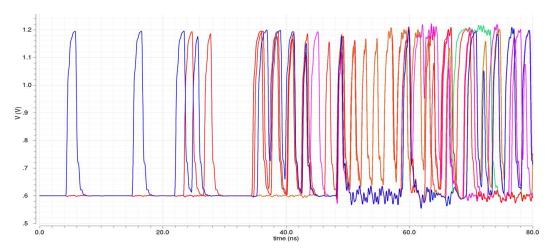

| 3.33 | RC shaping of the CSA for a MIP equivalent signal (8 fC in a 50 $\mu$ m UFSD). From the top to the bottom: OTA Buffer output voltage, CSA output voltage, input signal (layout simulation)         |

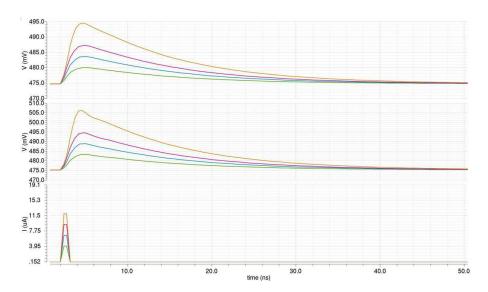

| 3.34 | RC shaping of the CSA for 4 different signals: 3 fC, 5 fC, 7 fC, 9 fC. From the top to the bottom: OTA Buffer output voltage, CSA output voltage, input signal (layout simulation)                 |

List of Figures xxiii

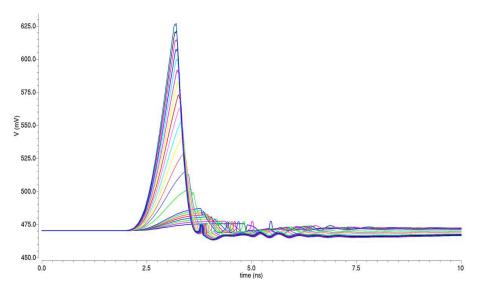

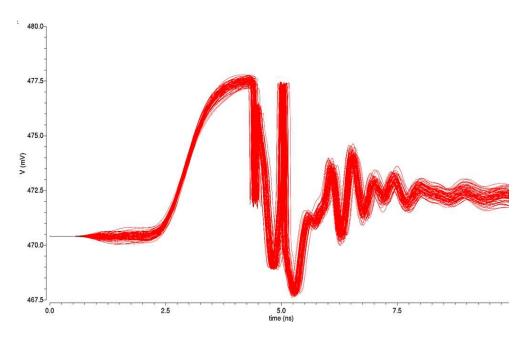

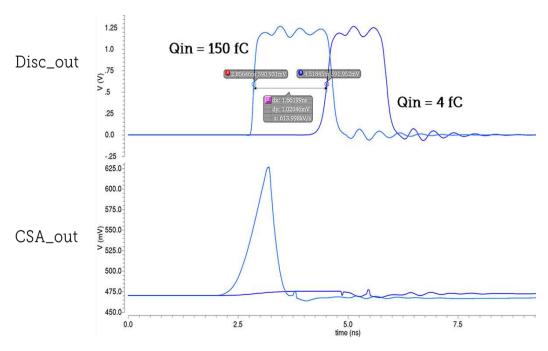

| 3.35 | Front-end shaping for a 3 fC - 150 fC input charge range. The sharp falling edge is the result of the discrimination triggered reset (schematic simulation)                                                                 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

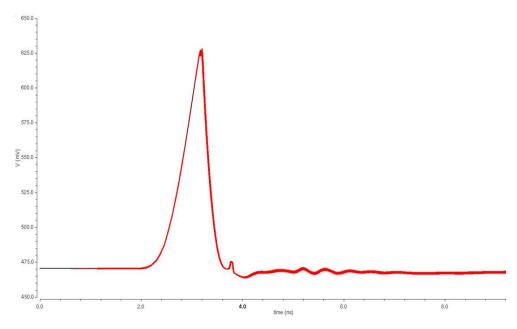

| 3.36 | Result from a 100 Hz - 100 GHz transient noise analysis. The noise effect has been observed on the CSA output, with a 3 fC input signal. 120                                                                                |

| 3.37 | Result from a 100 Hz - 100 GHz transient noise analysis. The noise effect has been observed on the CSA output, with a 150 fC input signal                                                                                   |

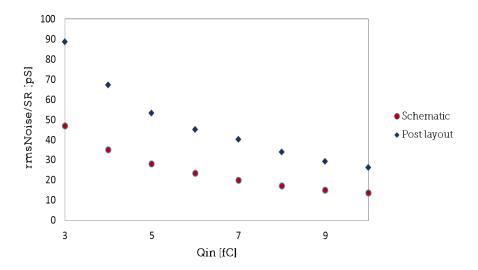

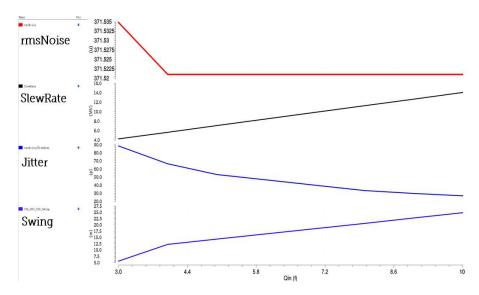

| 3.38 | CSA jitter vs input charge: comparison between schematic and post-layout simulation behavior                                                                                                                                |

| 3.39 | CSA details for the low-charge range (layout simulation) 121                                                                                                                                                                |

| 3.40 | CSA jitter vs the detector capacitance (layout simulation) 122                                                                                                                                                              |

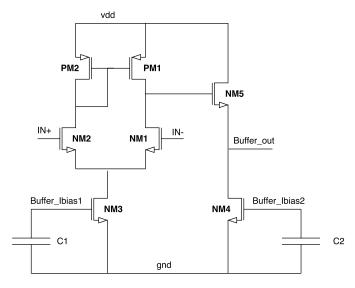

| 3.41 | Buffer pdf                                                                                                                                                                                                                  |

| 3.42 | To maximize the speed, a discriminator must be implemented cascading low-gain cells                                                                                                                                         |

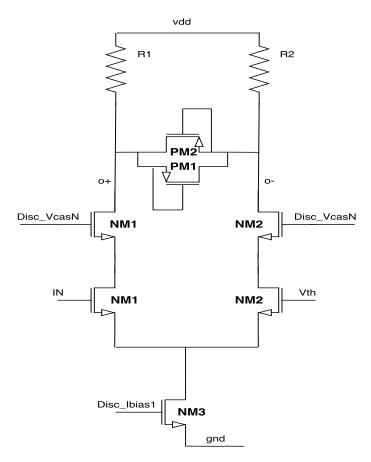

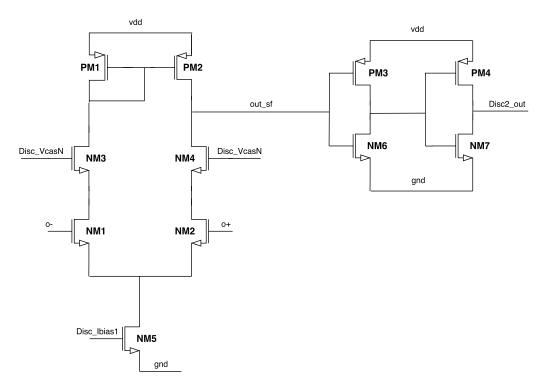

| 3.43 | Schematic representation of the comparator first block                                                                                                                                                                      |

| 3.44 | Schematic representation of the comparator second block 125                                                                                                                                                                 |

| 3.45 | timewalk                                                                                                                                                                                                                    |

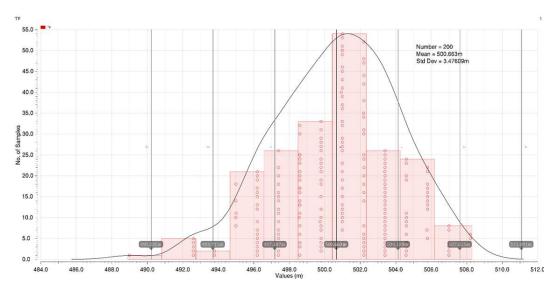

| 3.46 | Monte Carlo analysis for the discriminator threshold dispersion 127                                                                                                                                                         |

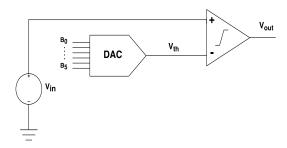

| 3.47 | Discriminator offset compensation with a fine tuning performed with an Digital to Analog Converter (DAC)                                                                                                                    |

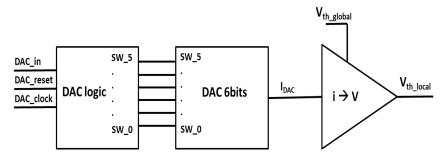

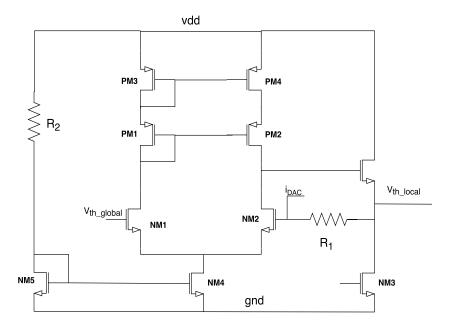

| 3.48 | ABACUS functional blocks dedicated to the digital-to-analog conversion. The $V_{th\_global}$ is fine tuned adding or subtracting a certain value selected by the user through a binary configuration 128                    |

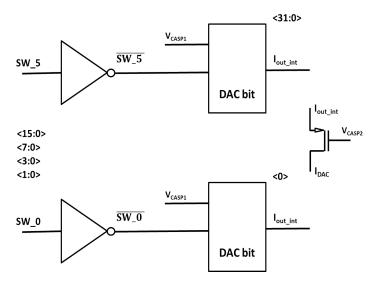

| 3.49 | Block representation of the DAC bit control. The inverters are used to keep an intuitive behavior with the stream of configuration bits: increasing the binary number means adding a positive value to the global threshold |

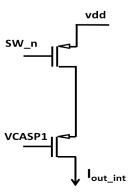

| 3.50 | Transistor detail of the unity current cell logic. The cascoded PMOS is controlled with the switch signal $SW_n$                                                                                                            |

**xxiv** List of Figures

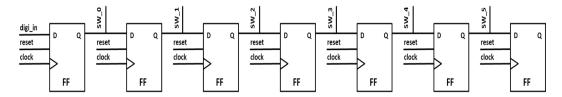

| 3.51 | DAC logic: block representation of the standard cell flip-flop chain and the extraction of the switch activation signals to control the bits. 130                                                                                                                                                                 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

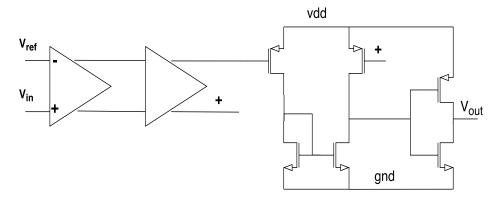

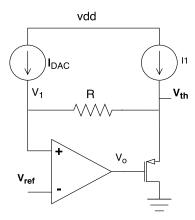

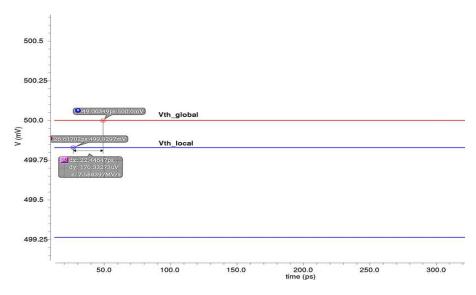

| 3.52 | Working principle of the adopted architecture for linear current to voltage conversion. The triangular block is the high gain transconductance amplifier                                                                                                                                                          |

| 3.53 | Schematic representation of the trans-impedance amplifier employed for $i_{DAC} \rightarrow V_{th}$ conversion                                                                                                                                                                                                    |

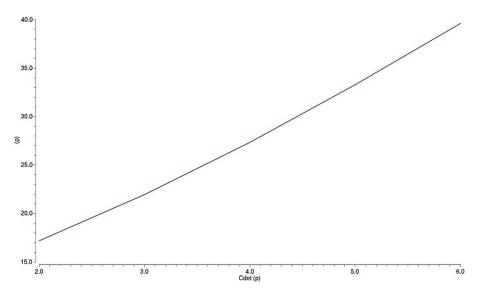

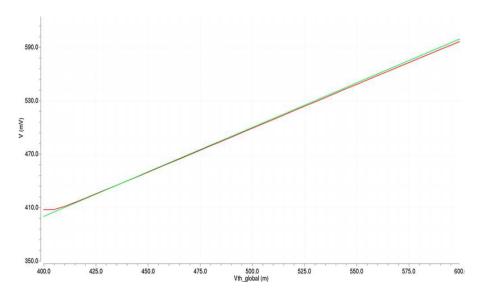

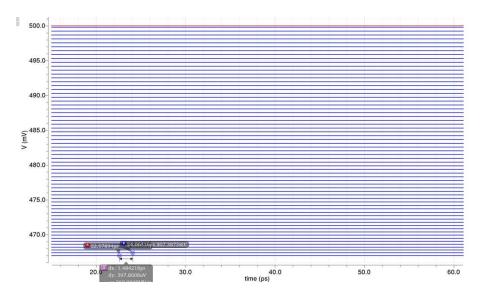

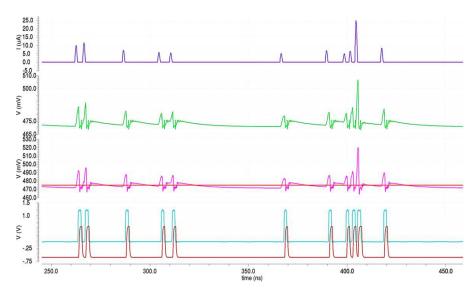

| 3.54 | DAC linearity: the conversion linearity is maintained over a $\sim$ 40 mV range. The plot shows the DAC output voltage in function of the global threshold voltage $V_{th\_global}$ . The latter is the top level threshold shared among all the chip channels and is then fine tuned with DACs, at channel level |

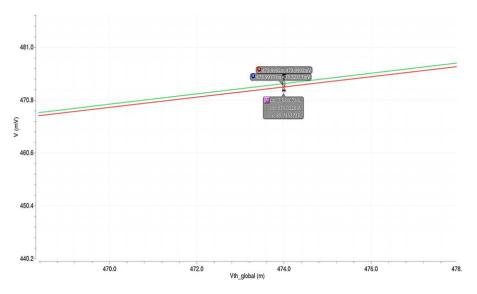

| 3.55 | DAC linearity: offset at 475 mV, a typical global threshold voltage 132                                                                                                                                                                                                                                           |

| 3.56 | The DAC voltage steps obtained with the 64 combinations of the 6 bits 133                                                                                                                                                                                                                                         |

| 3.57 | DACsteps3                                                                                                                                                                                                                                                                                                         |

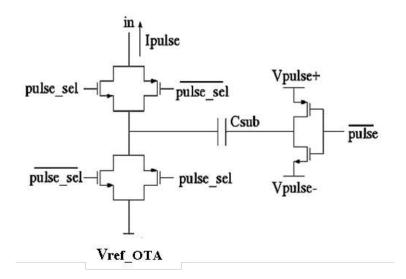

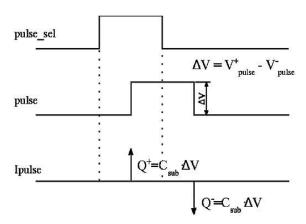

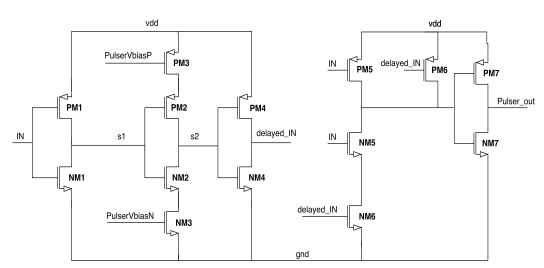

| 3.58 | Pulser: transistor level schematic. The output signal results form a bolean AND between the input and a delayed and inverter copy of the input. The two signals overlapping duration can be regulated with the PulserVbiasP and PulserVbiasN voltages                                                             |

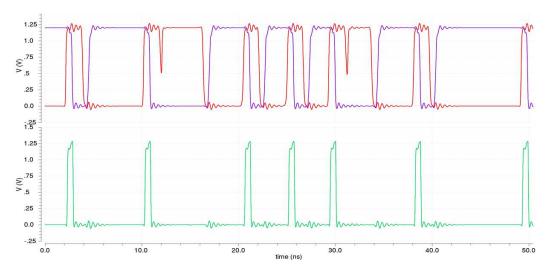

| 3.59 | Pulser working principle: the logic AND between the input and a delayed and inverter copy of the input (up) results in the pulse signal (bottom)                                                                                                                                                                  |

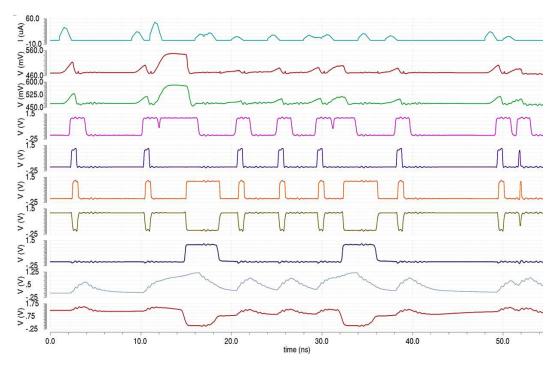

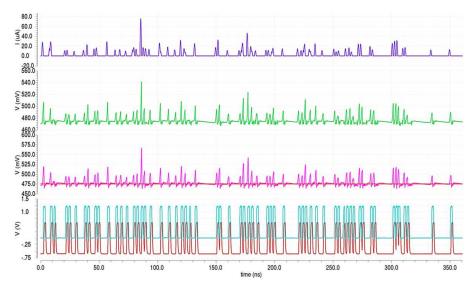

| 3.60 | Pulser, signal elaboration. Form the top to the bottom: the discriminator output (IN), the inverted discriminator output (S1), S1 inverted and delayed through a controlled RC shaping (S2), S2 inverted and digitized and in the picture bottom, the resulting pulse                                             |

| 3.61 | Pulser feature: pulse widht control. Light blue: PulserVbiasP = 700 mV, PulserVbiasN = 500 mV; blue: PulserVbiasP = 785 mV, PulserVbiasN = 700 mV                                                                                                                                                                 |

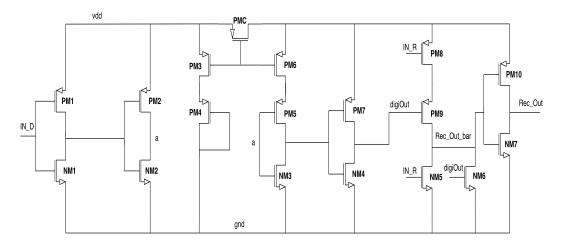

| 3.62 | Recovery: transistor level schematic                                                                                                                                                                                                                                                                              |

List of Figures xxv

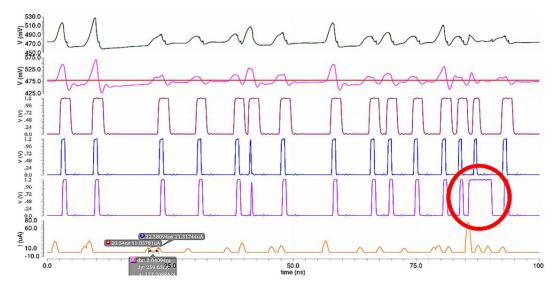

| 3.63 | The Recovery block working principle: the Recovery is different from the Pulser output only when the discriminator remains over threshold for more than a R-C fixed at 3.5 ns; whenever this happens, the boolean OR between the delayed discriminator output and the pulser signal, creates an extended reset signal                                                                                                       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

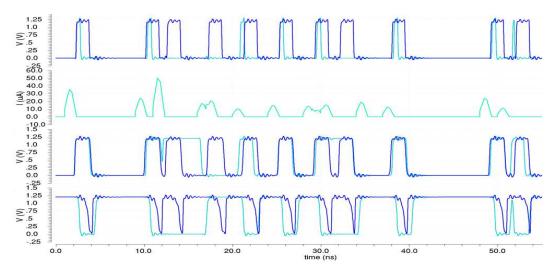

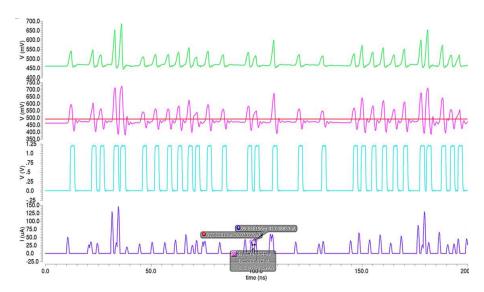

| 3.64 | Recovery, signal elaboration. From top to the bottom: the front-end input signal followed by the CSA output and the OTA Buffer output, the digitized discriminator output and the Pulser output. In the picture center, in orange, the Recovery output and its complement, followed by the signal added as active action from the Recovery (blue) and the RC with its digitized and inverted version, in the picture bottom |

| 3.65 | Single-ended to differential converter: transistor level schematic 139                                                                                                                                                                                                                                                                                                                                                      |

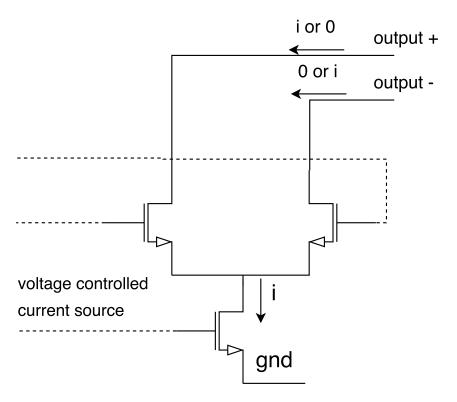

| 3.66 | CML driver: transistor level schematic                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.67 | CML embedded buffer: transistor level schematic                                                                                                                                                                                                                                                                                                                                                                             |

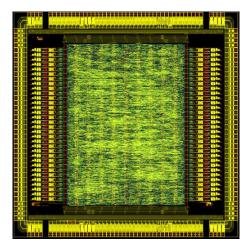

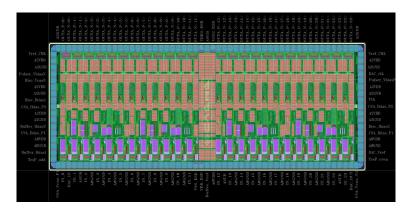

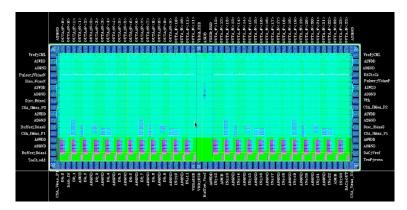

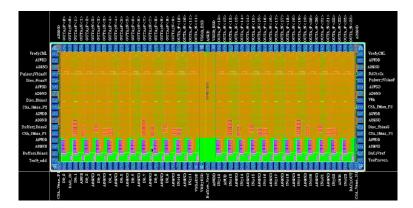

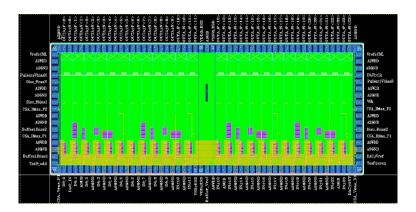

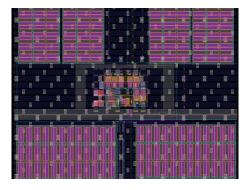

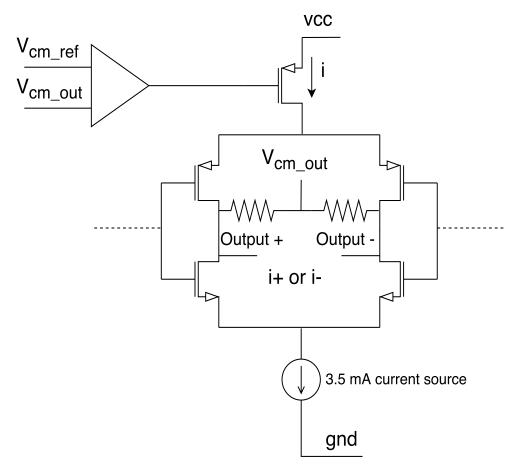

| 3.68 | ABACUS channel in its layout view                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.69 | Front-end layout with block identification                                                                                                                                                                                                                                                                                                                                                                                  |

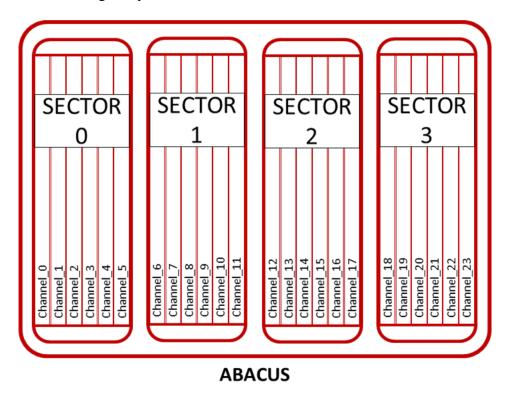

| 3.70 | ABACUS: sector division                                                                                                                                                                                                                                                                                                                                                                                                     |

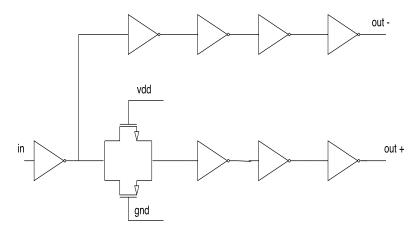

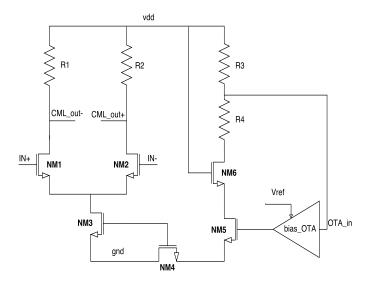

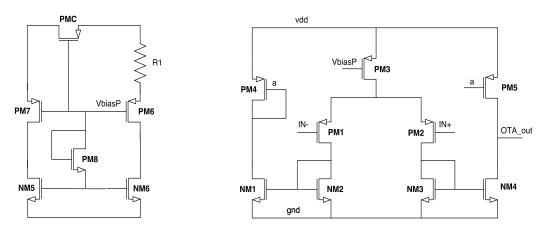

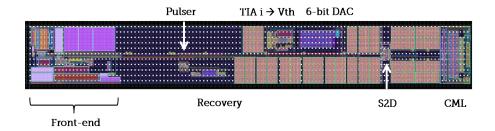

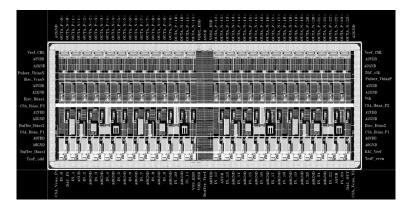

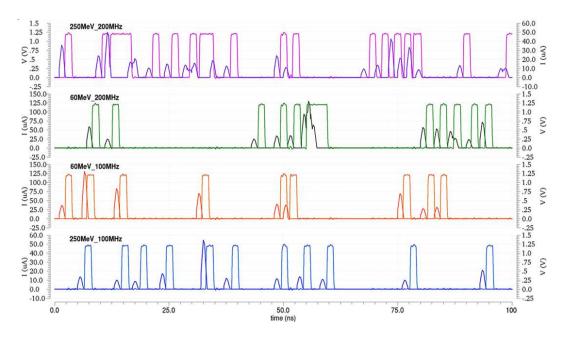

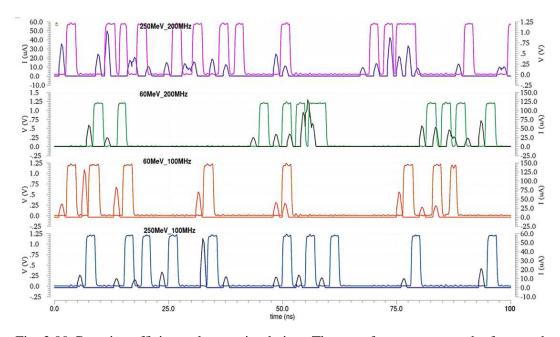

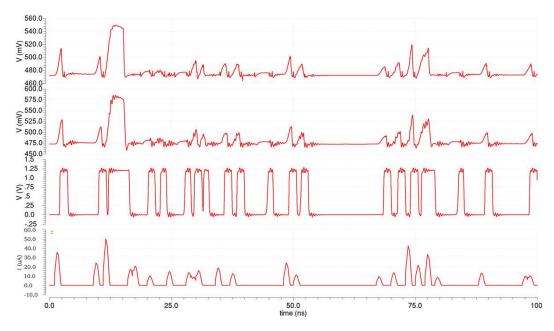

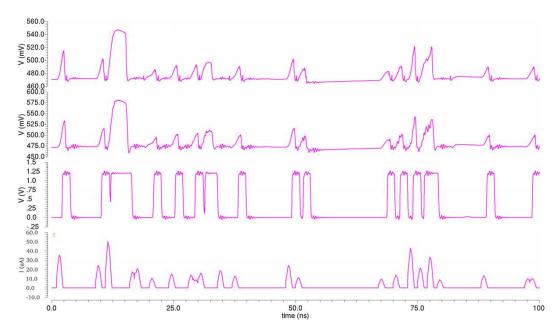

| 3.71 | Black and white layout view of the ABACUS top                                                                                                                                                                                                                                                                                                                                                                               |