## POLITECNICO DI TORINO Repository ISTITUZIONALE

### Digital VLSI Architectures for Advanced Channel Decoders

| Original Digital VLSI Architectures for Advanced Channel Decoders / Biroli, ANDREA DARIO GIANCARLO (2016).                              |

|-----------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                         |

|                                                                                                                                         |

| Availability: This version is available at: 11583/2653143 since: 2016-10-16T17:32:44Z                                                   |

| Publisher: Politecnico di Torino                                                                                                        |

| Published DOI:10.6092/polito/porto/2653143                                                                                              |

| Terms of use: Altro tipo di accesso                                                                                                     |

| This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository |

|                                                                                                                                         |

| Publisher copyright                                                                                                                     |

|                                                                                                                                         |

|                                                                                                                                         |

|                                                                                                                                         |

(Article begins on next page)

04 August 2020

# POLITECNICO DI TORINO

#### SCUOLA DI DOTTORATO

Dottorato in Ingegneria Elettronica – XXVIII ciclo

Tesi di Dottorato

# Digital VLSI Architectures for Advanced Channel Decoders

Ing. Andrea Dario Giancarlo Biroli

**Tutore** Prof. Guido Masera To my beloved parents

# Contents

| List of Figures |      |                                                           | IV |

|-----------------|------|-----------------------------------------------------------|----|

| 1               | Sun  | nmary                                                     | 1  |

| 2               | Intr | roduction                                                 | 3  |

|                 | 2.1  | Brief history of information and coding theory            | 3  |

|                 | 2.2  | Near-Capacity Channel Codes                               | 5  |

|                 |      | 2.2.1 Linear block codes                                  | 5  |

|                 |      | 2.2.2 Coding                                              | 7  |

|                 | 2.3  | Iterative Decoding                                        | 7  |

|                 |      | 2.3.1 Optimum decoding                                    | 9  |

|                 | 2.4  | Log-Likelihood ratio for AWGN channel and BPSK modulation | 10 |

|                 | 2.5  | QAM modulation                                            | 12 |

|                 |      | 2.5.1 Square QAM                                          | 14 |

| 3               | Pol  | ar code theory                                            | 19 |

|                 | 3.1  | Preliminary definitions                                   | 19 |

|                 |      | 3.1.1 Channel models and channel coding                   | 19 |

|                 | 3.2  | Channel polarization effect                               | 25 |

|                 |      | 3.2.1 Channel combining                                   | 25 |

|                 |      | 3.2.2 Channel splitting                                   | 28 |

|                 |      | 3.2.3 Operations on recursive synthetic channels          | 28 |

|                 |      | 3.2.4 Channel polarization                                | 30 |

|                 | 3.3  | Encoding and decoding of Polar Codes                      | 35 |

|                 | 3.4  | Belief propagation in polar codes                         | 36 |

|                 | 3.5  | Belief propagation scheduling                             | 42 |

|                 | 3.6  | Uniform Belief Propagation Decoder Structure              | 49 |

|                 | 3.7  | Graph Representation: Redundant Trellises                 | 50 |

|                 | 3.8  | Min-Sum Approximation                                     | 51 |

|                 | 3.9  | Performance evaluation                                    | 57 |

| 4                | $\mathbf{Bel}$ | ief Propagation Polar Decoder software model             | 60 |

|------------------|----------------|----------------------------------------------------------|----|

|                  | 4.1            | Introduction to C model                                  | 60 |

|                  |                | 4.1.1 Setting file                                       | 61 |

|                  |                | 4.1.2 Encoding                                           | 62 |

|                  |                | 4.1.3 Channel simulation and soft information evaluation | 62 |

|                  |                | 4.1.4 Graph description and Decoding                     | 64 |

|                  | 4.2            | Simulation Results                                       |    |

| 5                | Sta            | te of art for polar codes decoder implementations        | 70 |

| 6                | Bel            | ief Propagation Decoder hardware implementation          | 76 |

|                  | 6.1            | Effects of scheduling algorithms on architectures        | 76 |

|                  | 6.2            | Hardware Implementation                                  | 78 |

|                  |                | 6.2.1 Main Entity                                        | 78 |

|                  |                | 6.2.2 Processing Element                                 | 82 |

|                  | 6.3            | Synthesis results                                        | 85 |

| 7                | Cor            | nclusions                                                | 87 |

|                  | 7.1            | Achieved results                                         | 87 |

|                  | 7.2            | Future work                                              | 87 |

| $\mathbf{B}^{i}$ | ibliog         | graphy                                                   | 90 |

# List of Figures

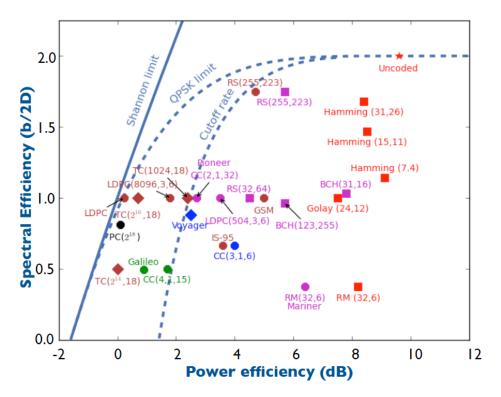

| 2.1  | Performance of codes example for Hamming, Golay, Reed-Muller (RM), concatenated (CC), BHC, Reed-Solomon (RS), LDPC, turbo (TC) |    |

|------|--------------------------------------------------------------------------------------------------------------------------------|----|

|      | and polar (PC) codes. It is also reported practical implementations of                                                         |    |

|      | codes for deep-space probes: Mariner (RM) 1969, Pioneer (CC) 1968,                                                             |    |

|      | Voyager(RS) 1977, Galileo (Viterbi) 1989. And for cellular applica-                                                            |    |

|      | tions: GSM (Viterbi) 1987, IS-95 standard (RM)1995. Figure from                                                                |    |

|      | [1].                                                                                                                           | 4  |

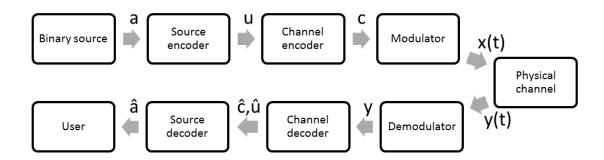

| 2.2  | Scheme representing transmitter, transmission channel and receiver.                                                            | 5  |

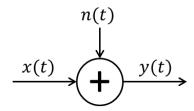

| 2.3  | Scheme of AWGN channel                                                                                                         | 10 |

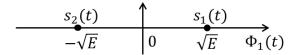

| 2.4  | BPSK signal constellation                                                                                                      | 11 |

| 2.5  | Used Mapping                                                                                                                   | 11 |

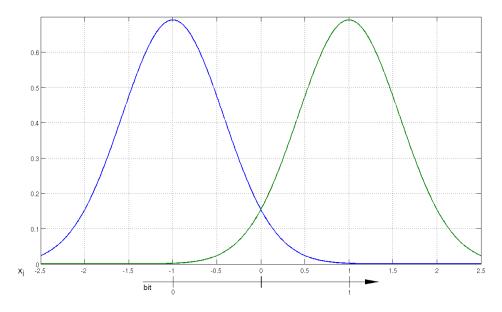

| 2.6  | Probability density for the AWGN channel                                                                                       | 11 |

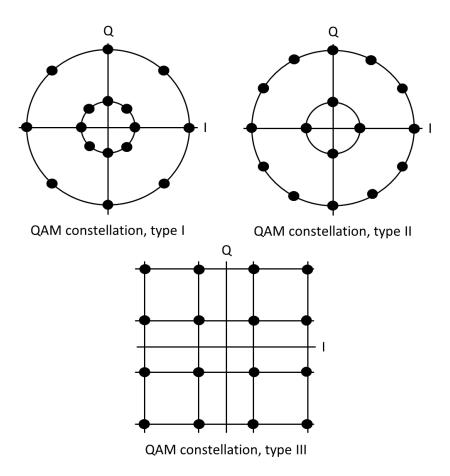

| 2.7  | Examples of type I, II, and III QAM constellations                                                                             | 13 |

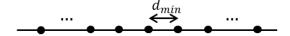

| 2.8  | The MASK constellation                                                                                                         | 16 |

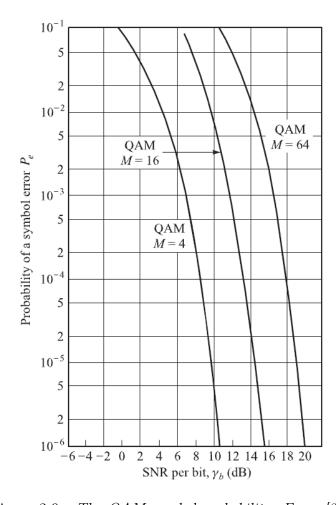

| 2.9  | The QAM symbol probability. From [2]                                                                                           | 17 |

| 2.10 | The 16-QAM constellation with Gray coding                                                                                      | 18 |

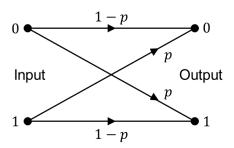

| 3.1  | Binary symmetric channel (BSC)                                                                                                 | 20 |

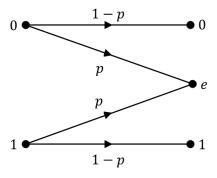

| 3.2  | Binary Erasure Channel (BEC)                                                                                                   | 24 |

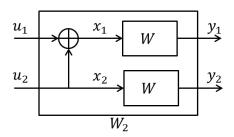

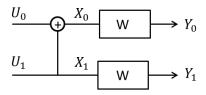

| 3.3  | $W_2$ channel                                                                                                                  | 25 |

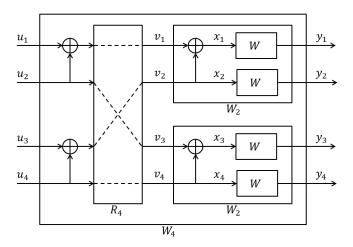

| 3.4  | $W_4$ channel obtained by recursions of $W_2$ and $W$                                                                          | 26 |

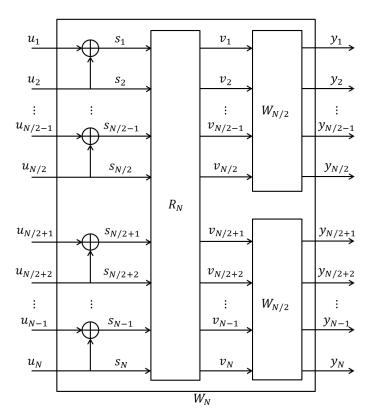

| 3.5  | Generalized $W_N$ channel obtained by recursion of two $W_{\frac{N}{2}}$                                                       | 27 |

| 3.6  | Channel variables relationship                                                                                                 | 30 |

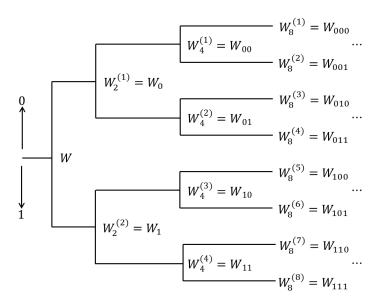

| 3.7  | Binary tree for the recursive construction of synthetic channels                                                               | 32 |

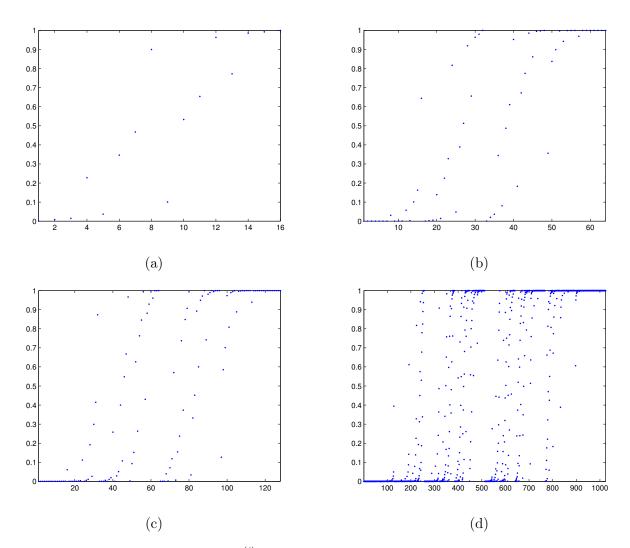

| 3.8  | Symmetric capacity $I(W_N^{(i)})$ for N BEC identical channels with era-                                                       |    |

|      | sure probability $\epsilon = 0.5$ . a) $N = 16$ b) $N = 64$ c) $N = 128$ d) $N = 1024$ .                                       | 34 |

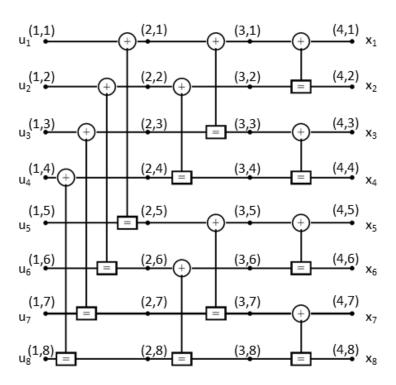

| 3.9  | Forney-style graph representation of a polar code of length eight                                                              | 37 |

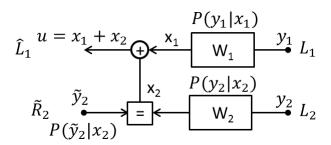

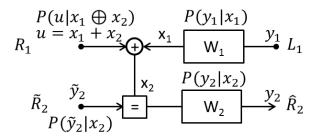

| 3.10 | Basic computational block for BP polar code decoding. Pointed out                                                              |    |

|      | messages for the evaluation of $\widehat{L_1}$ information                                                                     | 37 |

| 3.11 | Basic computational block for $\widehat{BP}$ polar code decoding. Pointed out                                                  |    |

|      | messages for the evaluation of $L_2$ information                                                                               | 39 |

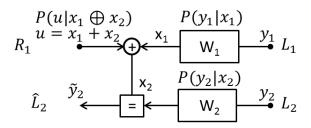

| 3.12       | Basic computational block for BP polar code decoding. Pointed out messages for the evaluation of $\widehat{R_2}$ information                                                                                                                                                                | 40 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.13       | Basic computational block for BP polar code decoding. Pointed out                                                                                                                                                                                                                           | 40 |

| 9 1 1      | messages for the evaluation of $R_1$ information                                                                                                                                                                                                                                            |    |

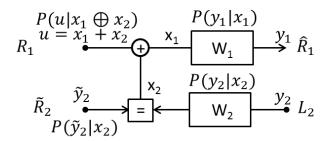

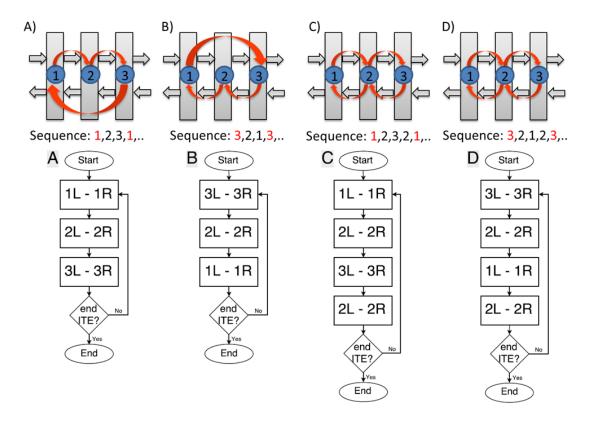

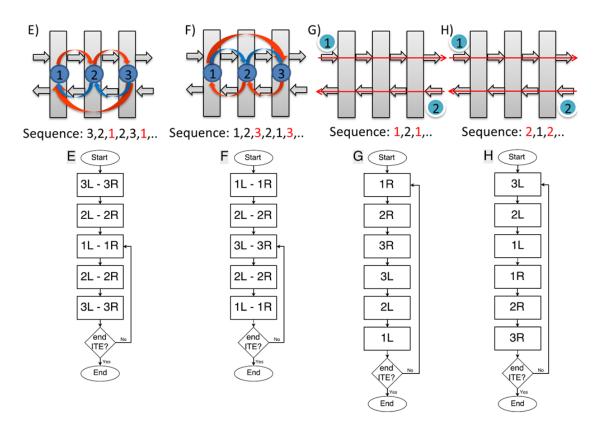

| 5.14       | Bidirectional scheduling algorithms: A)Linear LR. B)Linear RL. C)Circ<br>LR. D)Circular RL                                                                                                                                                                                                  | 43 |

| 3.15       | Bidirectional scheduling algorithms: A)Linear LR, start R. B)Linear RL, start L. Unidirectional scheduling algorithms: G)Circular LR.                                                                                                                                                       | 40 |

|            | H) Circular RL                                                                                                                                                                                                                                                                              | 44 |

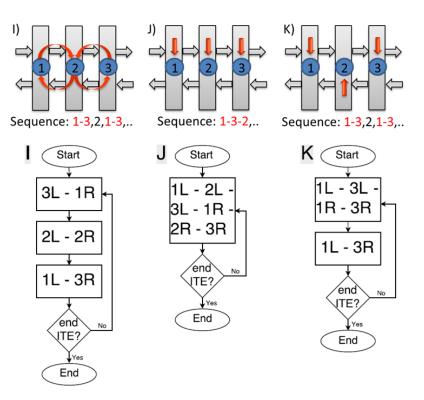

| 3.16       | Scheduling algorithms: I) Circular double-wave. J) All-on. K) Odd-<br>Even                                                                                                                                                                                                                  | 45 |

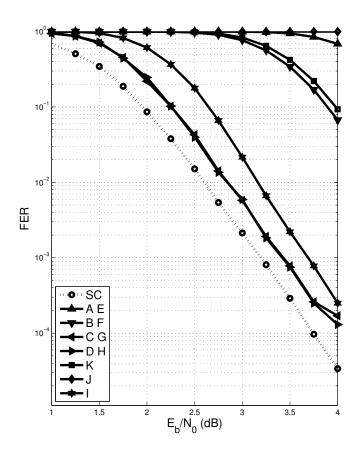

| 3.17       | Scheduling algorithms comparison for $N = 1024$ , rate $\frac{1}{2}$                                                                                                                                                                                                                        | 48 |

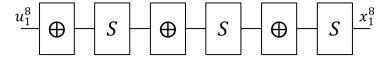

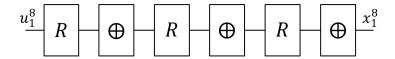

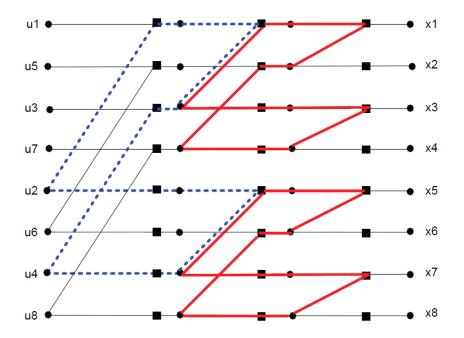

| 3.18       | Uniform graph representation with shuffle operators for $F^{\otimes 3}$                                                                                                                                                                                                                     | 49 |

| 3.19       | Uniform graph representation with reverse – shuffle operators for                                                                                                                                                                                                                           |    |

|            | $F^{\otimes 3}$                                                                                                                                                                                                                                                                             | 49 |

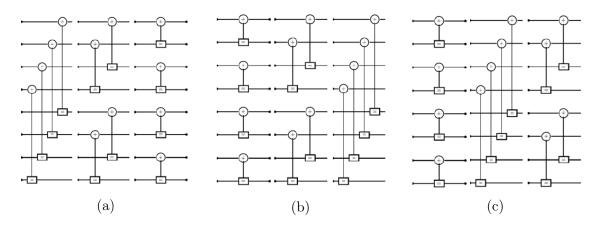

| 3.20       | Example of three redundant trellises                                                                                                                                                                                                                                                        | 50 |

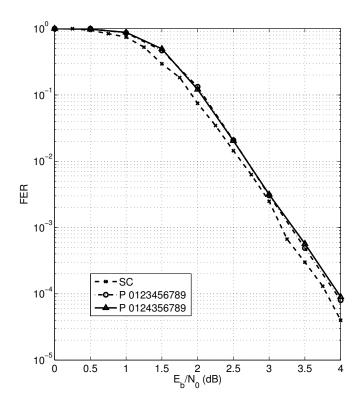

|            | Comparison result of FER performance of two redundant graph rep-                                                                                                                                                                                                                            |    |

|            | resentations for 15 iterations                                                                                                                                                                                                                                                              | 51 |

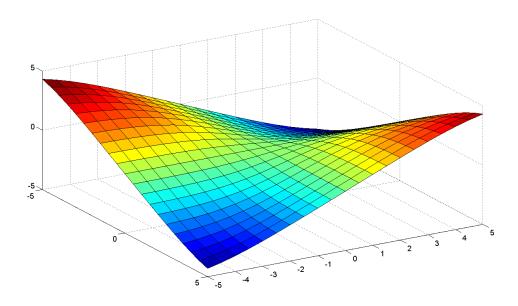

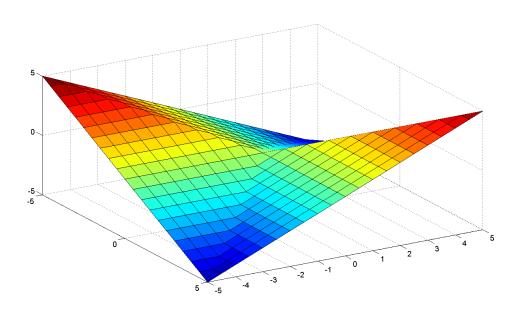

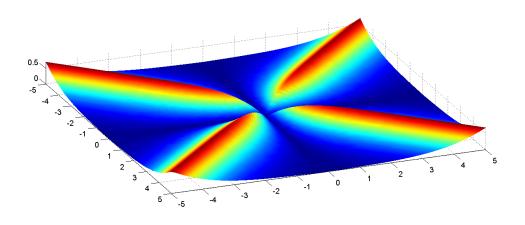

| 3.22       | Function $\Omega(x,y)$                                                                                                                                                                                                                                                                      | 54 |

| 3.23       | Min-Sum approximation of function $\Omega(x,y)$                                                                                                                                                                                                                                             | 55 |

| 3.24       | Approximation error of using Min-sum compared to function $\Omega(x,y)$ .                                                                                                                                                                                                                   | 55 |

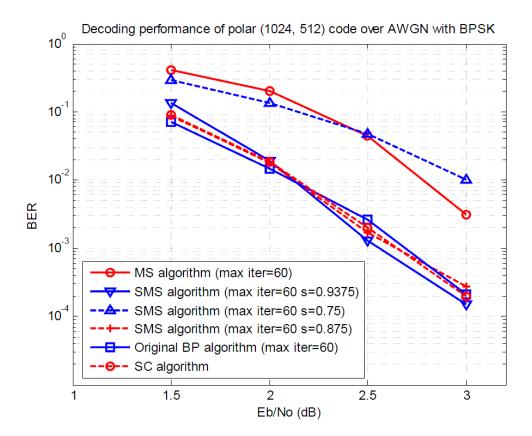

| 3.25       | Performance comparison of approximations for polar decoding. From                                                                                                                                                                                                                           |    |

|            | [3].                                                                                                                                                                                                                                                                                        | 56 |

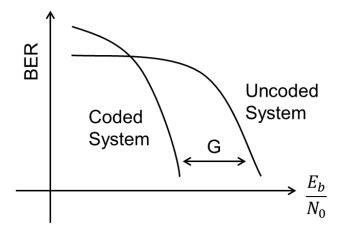

| 3.26       | Typical digital coded and uncoded communication system performance.  57                                                                                                                                                                                                                     |    |

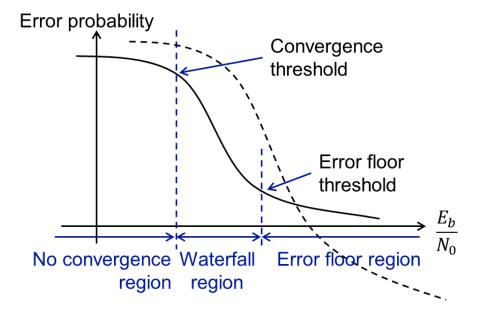

| 3.27       | Typical regions in an error probability curve for iterative decoding algorithms: the solid line identify the waterfall region and the error floor region. The trade-off between the two regions is illustrated by the second curve (dashed line) which has lower error floor at the expense |    |

| 3.28       | of higher convergence threshold                                                                                                                                                                                                                                                             | 58 |

|            | $g_{min} = 12$ . From [4]                                                                                                                                                                                                                                                                   | 59 |

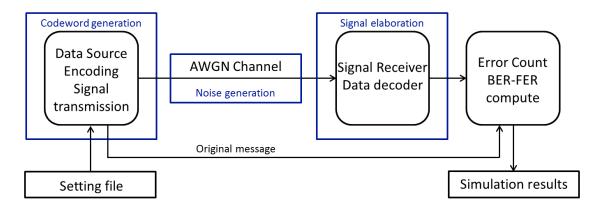

| 4.1        | Block description of $C$ model                                                                                                                                                                                                                                                              | 60 |

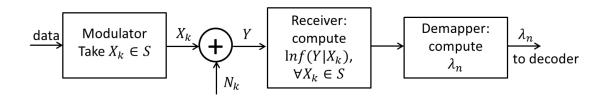

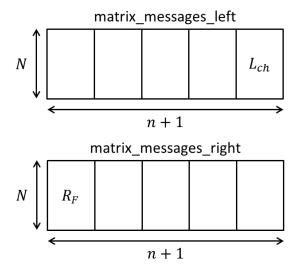

| 4.2        | Structure of LLRs message allocation for C model                                                                                                                                                                                                                                            | 63 |

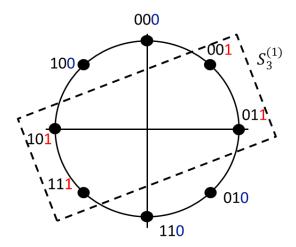

| 4.3        | Example of $S_3^{(1)}$                                                                                                                                                                                                                                                                      | 64 |

| 4.4<br>4.5 | Structure of LLRs message allocation for $C$ model                                                                                                                                                                                                                                          | 64 |

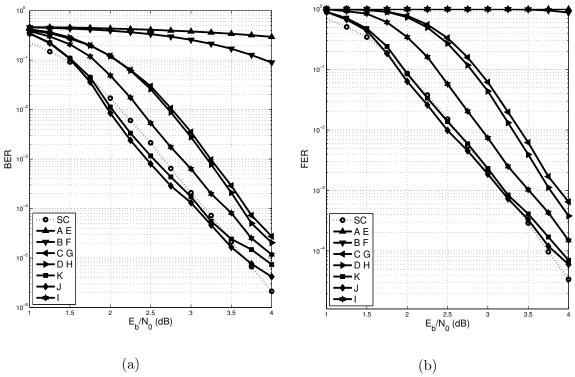

|            | 150 states a)BER. b)FER                                                                                                                                                                                                                                                                     | 66 |

|            |                                                                                                                                                                                                                                                                                             |    |

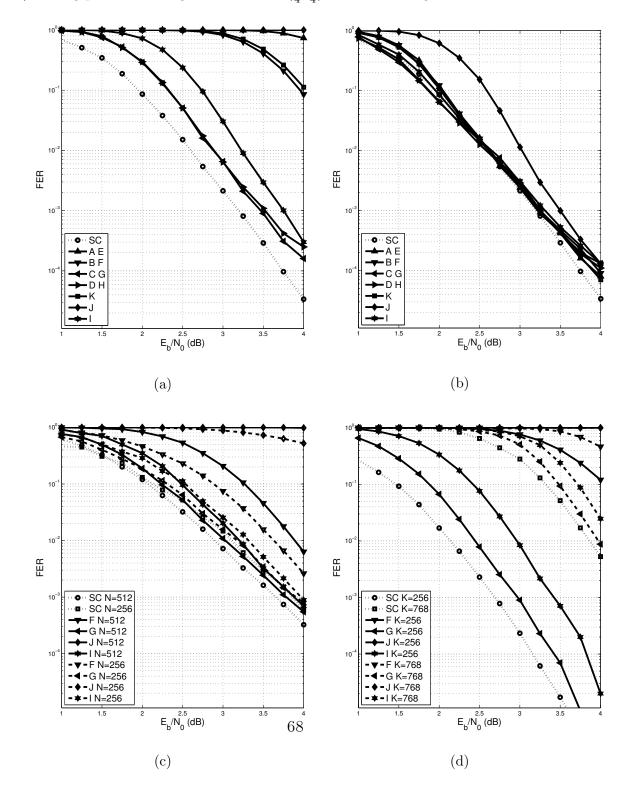

| 4.6 | FER performance for BP decoding with different schedules, BPSK                             |    |

|-----|--------------------------------------------------------------------------------------------|----|

|     | modulation, 200 operations. a)finite precision decoding (9 bit), rate                      |    |

|     | $\frac{1}{2}$ , codeword length $N=1024$ . b)floating point decoding, rate $\frac{1}{2}$ , |    |

|     | codeword length $N = 1024,650$ operations. c)floating point decoding,                      |    |

|     | rate $\frac{1}{2}$ , variable codeword length $(N = 512, 256)$ . d)floating point          |    |

|     | decoding, variable rate $(\frac{1}{4}, \frac{3}{4})$ , codeword length $N = 1024$          | 68 |

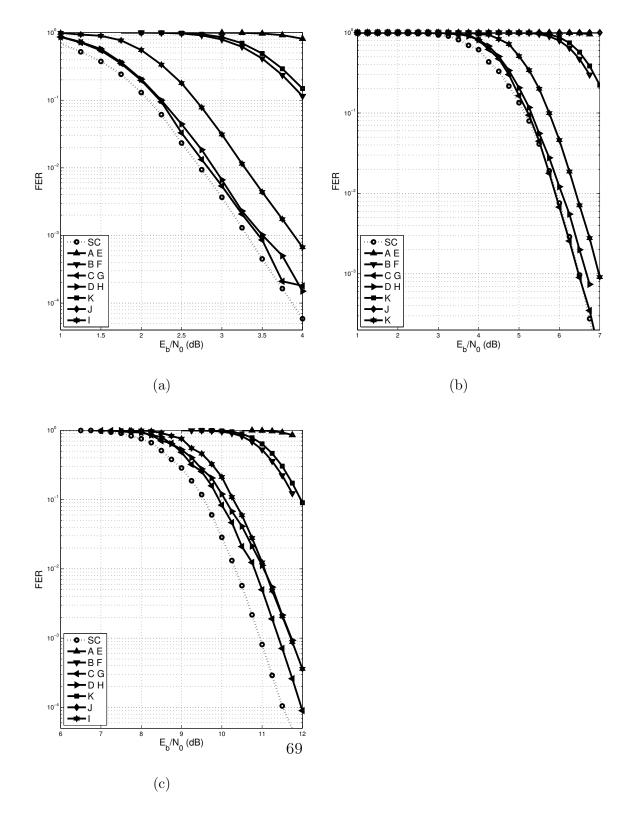

| 4.7 | FER performance for BP decoding with different schedules, floating                         |    |

|     | point decoding, rate $\frac{1}{2}$ , codeword length $N = 1024$ . a) 200 operations,       |    |

|     | 16-QAM modulation. c) 200 operations, 64-QAM modulation. d) 200                            |    |

|     | operations, 256-QAM modulation                                                             | 69 |

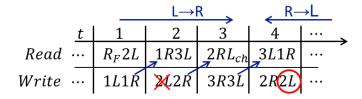

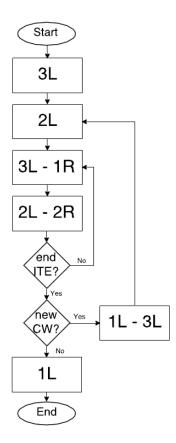

| 6.1 | Scheduling C message update example                                                        | 77 |

| 6.2 | Fully parallel architecture for a code of length $N = 4$                                   | 78 |

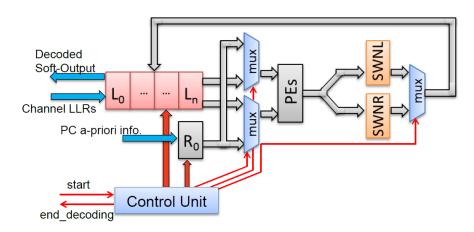

| 6.3 | Reduced complexity architecture                                                            | 79 |

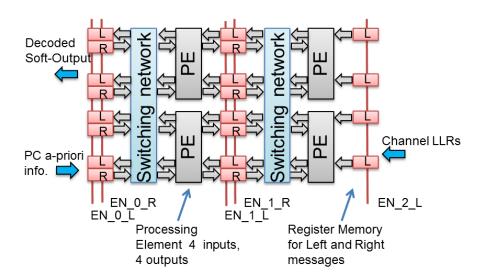

| 6.4 | Bidirectional wave architecture                                                            | 80 |

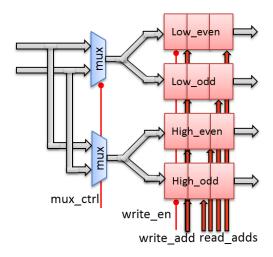

| 6.5 | Bidirectional wave register memory block detail                                            | 80 |

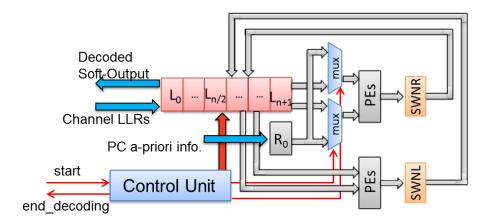

| 6.6 | Bidirectional wave architecture refined $I$ scheduling                                     | 81 |

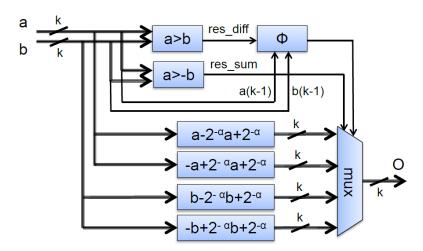

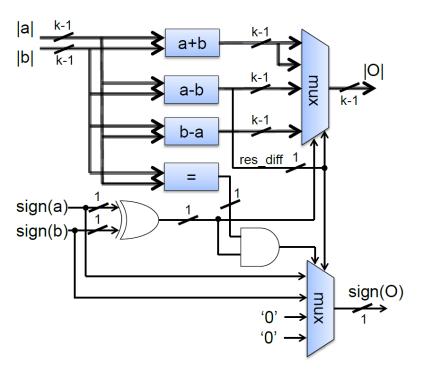

| 6.7 | Normalized min-sum block for two's complement data representation.                         | 82 |

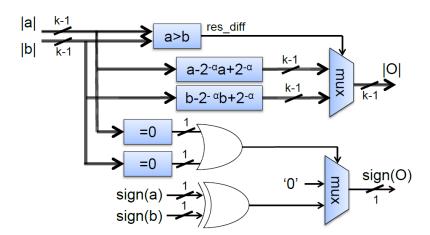

| 6.8 | Normalized min-sum block for modulus and sign data representation.                         | 83 |

| 6.9 | Sum block for modulus and sign data representation                                         | 84 |

# Chapter 1

# Summary

Every modern digital communication and storage system makes strong use of error-correcting codes. Typical applications are wireless communications, sensor networks, optical communications, computer hard drives, flash memories and space probes. The demand of codes with better error-correcting capability for new and emerging applications as well as the design and implementation of those high-gain error-correcting codes are open challenges. The direct mapping of these algorithms to hardware implementation often leads to very high complexity architecture because they usually involve complex mathematical computations so lots of research is performed to reduce complexity while enhancing decoding performance.

This work aims to focus on Polar codes, which are a recent class of channel codes with the proven ability to reduce decoding error probability arbitrarily small as the block-length is increased, provided that the code rate is less than the capacity of the channel. This property and the recursive code-construction of this algorithms attracted wide interest from the communications community.

Hardware architectures with reduced complexity can efficiently implement a polar codes decoder using either successive cancellation approximation or belief propagation algorithms. The latter offers higher throughput at high signal-to-noise ratio thanks to the inherently parallel decision-making capability of such decoder type. In Chapter 2 is proposed an overview on technological improvements from dawn of channel coding techniques and related forefront applications to actual solutions. In the same chapter general characteristics of error correcting block codes and iterative decoding properties are presented. Effects of Additive White Gaussian Noise are explored in relation to different channel modulations.

At Chapter 3 the polar codes theory is deeply analyzed. Channel polarization, effects of channel combining and splitting are described. Coding and decoding methods, approximations and performance evaluation are presented. A novel inspection on scheduling algorithms for Belief Propagation is given. Drawn observation enable to focus the research from simple maximum achievable throughput to throughput over

area efficiency ratio. Property of polar codes graph representation like uniformity or trellis redundancy are evaluated.

The model used to simulate different algorithms and hardware architectures is introduced in the fourth chapter. Simulation results are commented and general observation are drawn.

In Chapter 5 the state-of-art background for belief polar code decoders is presented. Chapter 6 describes implemented architectures in relation with proposed best scheduling algorithms discovered. Synthesis results of processing elements and overall structures are presented. Researched objectives in terms of absolute throughput and area efficiency are met.

Last chapter reports conclusion and compare achieved results with best architectures from literature. It also reports suggested future works in the direction of further improve obtained results.

# Chapter 2

## Introduction

### 2.1 Brief history of information and coding theory

The most fundamental parameter regarding a communication channel is its capacity C, a concept introduced by Claude E. Shannon in 1948 [5] that showed how to calculate the highest rate at which information can be transmitted reliably over the channel. This cut-off rate is considered the be the "practical coding limit" and is also known as "Shannon limit".

For the next half century, channel coding central objective was to find practical coding schemes that could approach channel capacity on well-understood channels such as the additive white Gaussian noise (AWGN) channel. This goal proved to be challenging, but not impossible. [6]

For the first couple of decades, algebraic coding dominated the field of channel coding. The principal objective of algebraic coding theory is to maximize the minimum Hamming distance for a given code to maximize error correction power. To improve error detection and correction, binary linear block codes were invented: Hamming code [7], Golay [8] codes and Reed-Muller codes [9] [10].

Even though algebraic codes were clearly limited to a few, channel models, their development appeared in the early sixties to be an area of considerable potential payoff, in applied as well as theoretical directions, beginning with the algebraic representation [11] of all linear error-correcting codes, and culminating at the end of the decade with the important class of Bose-Chaudhuri-Hocquenghem (BCH) codes [12], [13] and following Reed-Solomon [14] which are a class of non-binary BCH codes.

On the road to modern capacity-approaching codes, an essential step has been to replace hard-decision with soft-decision decoding (decoding that takes into account the reliability of received channel outputs). The earliest soft-decision decoding algorithm in literature is Wagner decoding, described in [15].

An alternative line of development that was more directly inspired by Shannon's

Figure 2.1: Performance of codes example for Hamming, Golay, Reed-Muller (RM), concatenated (CC), BHC, Reed-Solomon (RS), LDPC, turbo (TC) and polar (PC) codes. It is also reported practical implementations of codes for deep-space probes: Mariner (RM) 1969, Pioneer (CC) 1968, Voyager(RS) 1977, Galileo (Viterbi) 1989. And for cellular applications: GSM (Viterbi) 1987, IS-95 standard (RM)1995. Figure from [1].

probabilistic approach to coding is named "Probabilistic coding". It is more concerned with finding classes of codes that optimize average performance as a function of coding and decoding complexity. Following coding schemes fall into this class. Convolutional codes and product codes were invented by Peter Elias in 1954-1955 [16] [17]. In 1962 Gallager developed Low-density parity-check code (LDPC code) [18] but his work was not taken into account until nineties by David MacKay. Concatenated codes were introduced by Dave Forney in 1966 [19]. It is based on an inner and an outer code that can be relatively short and easy to encode and decode, while the resulting concatenated code is powerful and much longer.

To decode convolutional codes, Andy Viterbi in 1967 proposed an "asymptotically

optimal" algorithm (known as Viterbi Algorithm) which performs a maximum-likelihood decoding through the search of the closest sequence on a trellis with finite number of states. In nineties, we can date the main developments in codes approaching the Shannon's bound: Turbo codes (1993) [20], the rediscovery of LDPC (1996) [21],[22] and Polar codes (2008) [23].

In Figure 2.1 a performance comparison among cited codes and forefront applications of these codes can be observed. Notice that from the start in 1948, coding research has been oriented in closing the gap between practical achievable performance (with proper code structure influenced by technological constrains) and the Shannon bound  $(\frac{E_b}{N_0} > \frac{2^r-1}{r} > \ln 2 \simeq -1.6dB)$ .

### 2.2 Near-Capacity Channel Codes

#### 2.2.1 Linear block codes

In Figure 2.2 a generic numerical transmission classical point to point scheme is presented, even if nowadays a part of research, especially in multimedia applications, study the possibility of combining source and channel coding, in order to optimize transmissive resources. Block codes are channel codes which allow to reveal and correct errors induced by transmission channel. It is briefly reported fundamental

Figure 2.2: Scheme representing transmitter, transmission channel and receiver.

concept on linear block codes.

Let  $\mathbb{F} = GF(2)$  be a Galois Field of order 2 and  $\mathbb{F}^N$  a vector space of dimension N on GF(2). A block code  $\mathcal{C} \subseteq \mathbb{F}^N$  is an application  $\mathcal{C} : \mathbb{F}^K \mapsto \mathbb{F}^N$ . It is linear if:

- $\forall \lambda \in \mathbb{F}, \ u \in \mathcal{C}, \text{ also } \lambda u \in \mathcal{C};$

- $\forall u, v \in \mathcal{C}$ , also  $u \oplus v \in \mathcal{C}$ .

$\mathcal{C}$  is characterized by (N, K, d) where d is the *minimal distance* of the code, defined as in 2.1.

$$d \triangleq \min_{u \neq v} \ d_H(u, v) \tag{2.1}$$

where  $d_H$  is the *Hamming distance*. Hence information bitstream is divided in vectors u, of dimension 1xK and mapped on codeword x of dimension 1xN, through linear transformation 2.2.

$$x = uG (2.2)$$

The ratio R = K/N is called code rate. A code is called systematic if x can be rewritten as x = [u|c]. Matrix  $G^T$  of dimension KxN is called generating matrix and it is in systematical form if it respect following three properties:

- Leftmost not-zero value of every row is a 1;

- Every column containing the leftmost 1 has all other input equal to 0;

- If the leftmost not-zero value of the row i is in column  $t_i$ , then  $t_1 < t_2 ... < t_r$

So a particular case occurs when the matrix is built as follows.

$$G = [I_K | P_{N-K}] \tag{2.3}$$

where  $I_K$  is an identity matrix KxK and  $P_{N-K}$  of dimension Kx(N-K).

So the coding for a code C has the desirable characteristic that information symbols appear clearly in the  $codeword\ x$ ; more in general, the symbol  $x_i$  will appear in position  $t_i$  in the codeword x = uG, if the leftmost value of row i-th of G happens at column  $t_i$ .

Every code (linear or not), that verify the property that exist a rule of coding so that information symbols appear clearly is called *systematic*. It can be proven that every linear code can be made systematic.

In a digital transmission channel, sent codeword x can be corrupted by noisy channel and the received word y can be expressed as in 2.4.

$$y = x + e \tag{2.4}$$

where e is the error vector that represent channel effects. Knowing the received signal y, the decoder tries to evaluate an estimate of  $\hat{x}$  of the transmitted information word u. Estimated codeword  $\hat{x}$  must be calculated to be the closest word (inside the codeword set  $\mathcal{C}$ ) to the transmitted one. To do so, it is chosen a method based on codeword distance (either Hamming or Euclidean distance). To perform di evaluation, the decoder should compute (N-K) parity bits and compare them with original parity bits of x, if equal, the received word is correct. So an error occur if at least one parity check fails.

#### 2.2.2 Coding

For simplicity of exposition, it will be considered in the following paragraph that message bits u are placed at the end of the codeword. The codeword can be divided in M check bits followed by K message bits, so the codeword is divisible in M control bits followed by K message bits u.

$$x = [c|u] \tag{2.5}$$

Thanks to the previous assumption, H parity matrix can be divided in a A matrix  $M \times M$  which occupy first M column of H and a B matrix  $M \times K$  which occupy remaining columns of H.

$$H = [A|B] \tag{2.6}$$

So the requirement that a codeword comply with all parity checks (Hx = 0) can be written as:

$$Ac + Bu = 0 (2.7)$$

Assuming A is not singular, follows:

$$c = A^{-1}Bu (2.8)$$

A can be singular for some choices so codeword bits are message bits, however it always exist a choice of A not singular if H rows are linearly independent. Anyway it is possible that H rows are not linearly independent (i.e. some rows are redundant). This particular case is not very interesting.

Equation 2.8 defines which should be control bits, however the way those bits are evaluated can be fulfilled in different ways.

The developed software does not involve the use of a matrix representation in sparse form since the high number of ones in the generator polar code matrix, equal to  $3^{\log_2(N)}$  where N is the codeword length. The explicit representation of the generator matrix G can be expressed for the systematic form as in 2.9.

$$G = [A^{-1}B|I_K] (2.9)$$

This form, expressed for a generic generator matrix, does not take into account specific recursive structure of polar codes that will be discussed in detail in chapter 3.3.

### 2.3 Iterative Decoding

Actual high performance decoders work with data represented as information called "soft-information".

Block codes can be decoded through two different strategies which depend on input data format at the decoder. When decoder inputs are made by bits (0 or 1), it is called "Hard" decoding; while if inputs are real values (i.e. 0.784) it is considered "Soft" decoding.

Recalling Figure 2.2, channel decoder inputs are digital demodulator outputs, so if this component which receives channel signal, represent it as real values, then following decoder will be "soft". Instead if the digital demodulator takes its decision also on transmitted data choosing if the sent bit was a 0 or 1, it will be called "hard" decoder. Moreover, since in soft decoding, real values are involved, the metric for the chosen distance is the Euclidean, while for hard decoding Hamming distance is used.

On decoding performance point of view, it is well known in information theory that Soft Decoding overcame Hard Decoding because it is able to correct a larger number of errors. Decoding process becomes quite difficult when a word is searched in the space of all possible messages, which minimize the probability of having an error. Hard Decoding limits this process in the search into the subspace of binary words which are a limited set. Instead Soft Decoding "extends" the search by considering all real values, this means that the research space is considerably augmented. However the probability of finding transmitted codeword is also increased; and also adopting same error correction code, soft decoding can achieve better gains compared to hard decoding. From these remarks appear that high performance channel decoders use Soft decoding strategy even if decoder architectures are more complex.

For the specific case of Polar code decoders, they do not work on raw soft data received from the channel, but on a "reliability" measure obtained from the data. These metrics represent how received signal is close to bit 0 or 1 of the transmitted signal; they are called *likelihood-ratio* ( $\lambda_d$ ) and defined as in 2.10

$$\lambda_d = \frac{P(y_d|x_d = 0)}{P(y_d|x_d = 1)} = \frac{1 - P_d}{P_d}$$

(2.10)

Where  $y_d$  is the d-th received bit,  $x_d$  is d-th transmitted bit and  $P_d$  indicate the probability of receiving a bit 1 in position d given that bit 1 has been transmitted in position d. Let us remark that the conditional probability evaluated on input signal needs the knowledge on the transmitted information, that is if it has been sent a 1 or a 0 from transmitter.

It is also defined the Log-likelihood-ratio (LLR) as in 2.11.

$$\Lambda_d \triangleq \ln(\lambda_d) = \ln \frac{P(y_d | x_d = 0)}{P(y_d | x_d = 1)} = \ln \frac{1 - P_d}{P_d}$$

(2.11)

The decoder purpose is to determine the transmitted correct value, starting from the knowledge of the received information, iteratively updating *likelihood-ratio* metrics,

that means to determine the a posteriori probability on received data. Since these metrics are probabilities, the iterative update will be multiplication among them and resulting probability will be interpreted as an information on how close the received message is to a codeword. The choice of using logarithms is therefore motivated by the easiness to implement an algorithm which presents sums instead of multiplications, in fact the use of multiplicative blocks is more expensive in terms of hardware and less stable form numerical representation point of view compared to sum blocks. Moreover the introduction of the logarithmic domain does not modify the overall behaviour of the decoder.

For the AWGN channel and BPSK modulation some simplification occur to the evaluation formula of LLRs as presented in the following chapter 2.4, while for QAM modulation a detailed overview is given in 2.5.

#### 2.3.1 Optimum decoding

The purpose of decoders is to find the codeword  $\hat{c}$  with the highest probability of having been sent over the channel, given the channel output y and the knowledge of the used code:

$$\widehat{c} = \underset{c' \in \mathcal{C}}{arg \max} P(c = c'|y) \tag{2.12}$$

Such kind of decoding is called word maximum a posteriori (W-MAP). The code knowledge appears in the conditioned probability. Using Bayes theorem the a posteriori probability P(c = c'|y) can be expressed as:

$$P(c|y) = \frac{P(y|c)P(c)}{P(y)} = \frac{P(y|c)P(c)}{\sum_{c \in C} P(y|c)P(c)}$$

(2.13)

If the a priori probability P(c) is equal for every c (equiprobable source), since P(y) does not depend from c then 2.12 can be expressed as:

$$\widehat{c} = \underset{c' \in \mathcal{C}}{arg \max} P(y|c = c') \tag{2.14}$$

This criterion is known as word maximum likelihood (W-ML). P(y|c) is the likelihood function when expressed for a particular y and for a given c it represents the density probability function.

If the channel is memoryless, it is also valid:

$$P(y|c = c') = \prod_{j=0}^{N-1} P(y_j|c_j = c'_j)$$

(2.15)

So the W-ML criterion becomes:

$$\widehat{c_j} = \underset{c' \in \{0,1\}}{arg} \max P(y_j | c_j = c')$$

(2.16)

The only way to obtain an optimal W-MAP is to test every memory word, which means  $2^K$  combinations if a binary source is considered. W-MAP and W-ML decoders are optimum equivalent decoders if the source is equiprobable.

# 2.4 Log-Likelihood ratio for AWGN channel and BPSK modulation

Figure 2.3: Scheme of AWGN channel.

Supposing to represent the transmission medium as an AWGN (Additive White Gaussian Noise) channel with  $\mathcal{N}(0, \sigma^2 = \frac{N_0}{2})$ , the received signal y(t) can be written as y(t) = x(t) + n(t), where x(t) is the transmitted signal, so it is considered a constellation of only two symbols as for binary phase shift keying (BPSK) modulation, and n(t) represent the noise component (Figure 2.3).

Phase shift keying (PSK) is widely used in the communication industry and BPSK is the simplest implementation with just two signals with different phases.

Typically these two phases are 0 and  $\pi$ , the signals are:

$$s_1(t) = A\cos(2\pi f_c t), \quad 0 \le t \le T, \quad \text{for } 1$$

$s_2(t) = -A\cos(2\pi f_c t), \quad 0 \le t \le T, \quad \text{for } 0$  (2.17)

These signals are called *antipodal* and they can also be graphically represented by a *signal constellation* (Figure 2.4) in the coordinate system with

$$\Phi_1(t) = \sqrt{\frac{2}{T}}\cos(2\pi f_c t) \text{ for } 0 \le t \le T$$

(2.18)

The energy of a transmitted signal is therefore:

$$E = A^2 \frac{T}{2} \tag{2.19}$$

Figure 2.4: BPSK signal constellation.

Let us remind that for AWGN channel the density probability function is defined

Figure 2.5: Used Mapping.

Figure 2.6: Probability density for the AWGN channel.

by

$$2.20$$

$$f(r_i|b_i) = \frac{1}{\sqrt{2\pi}\sigma} e^{-\frac{(r_i - (1 - 2b_i))^2}{2\sigma^2}}$$

(2.20)

where  $b_i$  is the bit that is transmitted and is mapped as  $b_i = 0$  for symbol  $x = s_2$  and  $b_i = 1$  for symbol  $x = s_1$  with unit energy that is normalized (as in Figure 2.5).  $r_i$  is the received symbol. So for the Gaussian channel with variance  $\sigma$  is given by  $\frac{E_S}{N_0} = \frac{1}{2\sigma^2}$ . As LLR was previously defined (2.11) it can be written the following.

$$\Lambda_{d} = \ln \frac{P(y_{d}|x_{d} = s_{2})}{P(y_{d}|x_{d} = s_{1})} = \ln \frac{f(r_{d}|b_{d} = 0)}{f(r_{d}|b_{d} = 1)} = \frac{e^{-\frac{(r_{d} - 1)^{2}}{2\sigma^{2}}}}{e^{-\frac{(r_{d} + 1)^{2}}{2\sigma^{2}}}} = \frac{1}{2\sigma^{2}} = \frac{e^{-\frac{(-2r_{d} - 2r_{d})}{2\sigma^{2}}}}{e^{-\frac{(-2r_{d} - 2r_{d})}{2\sigma^{2}}}} = \frac{1}{2\sigma^{2}} = \frac{1}$$

The final result of 2.21 will be used to compute simulations probability of the AWGN transmission channel with BPSK signal mapping of sent data for the software implementation.

### 2.5 QAM modulation

Quadrature amplitude modulation (QAM) is a class of nonconstant envelope schemes that can achieve higher bandwidth efficiency than M-ary Phase Shift Keying (MPSK) with the same average signal power. The first QAM scheme was proposed by C. R. Cahn in 1960 [24]. He extended phase modulation to a multi-amplitude phase modulation. This means that more than one amplitude is associated to every allowed phase. Many different types of constellation have been presented in literature over the years. Adopting the description of QAM constellation in [25] let us introduce three most significative types .

Type I constellation is a fixed number of signal points (or phasors) equally spaced on N circles, where N is the number of amplitude levels (Figure 2.7(a)). This type of constellation suffers of the problem that the points on the inner ring are closest together in distance so are most vulnerable to errors. To mitigate this problem, type II constellation was proposed by Hancock and Lucky a few months later [26] (Figure

Figure 2.7: Examples of type I, II, and III QAM constellations.

2.7(b)). Signal points of type II constellation are still on circles, but the number of points on the inner circle is lower than the number of points on the outer circle. This makes the distance between two adjacent points on the inner circle approximately equal to that on the outer circle.

In 1962 Campopiano and Glazer [27] proposed the square QAM constellation shown in Figure 2.7(c). This III type of constellation does not offer a big improvement in performance over the type II system, but its implementation is considerably simpler than that of type I and II. It can be easily generated by two M-ary Amplitude Shift Keying (MASK) signals sent on two phase-quadrature carriers and demodulated to yield the two quadrature components. Few of the other constellations offer slightly better error performance for AWGN channels, but with more complicated system implementation. Due to this, the type III constellation has been the most widely used system. QAM is used for instance in modems designed for telephone channels.

QAM schemes starting from uncoded 16QAM to trellis coded 128QAM are used in CCITT telephone circuit modem standards V.29 to V.33. A very active research on QAM applications are also satellite systems, point-to-point wireless systems, and mobile cellular telephone systems. [25]

#### 2.5.1 Square QAM

Considering both amplitude and phase modulation in a scheme, a general QAM signal can be written as:

$$s_i(t) = A_i cos(2\pi f_c t + \theta_i), \text{ for } i = 1, 2, ...M$$

(2.22)

where  $A_i$  is the amplitude and  $\theta_i$  is the phase of the *i*-th signal in the M-ary signal set. The pulse shaping parameter p(t) which multiply  $s_i(t)$  has been neglected because there is no particular interest to discuss the improvement of the spectrum and the intersymbol interference (ISI) for QAM current description for simulation, but it is good to know for a practical implementation. In fact even if pulse shaping is not desired, it inevitably occurs due to the limit of bandwidth for the considered system. Pulse shaping is usually achieved through filtering so  $P(f) = H_T(f)H_C(f)H_R(f)$  (or equivalently  $p(t) = h_T(t) * h_C(t) * h_R(t)$ ) where  $H_T(f), H_C(f)$  and  $H_R(f)$  are the spectral responses of the transmitter filter, channel, and receiver filter. A common choice of P(f) is the raised-cosine (or its approximated delayed version due to causality issues), whose time domain function p(t) has zero values at sampling instants except at t = 0, thus p(t) incurs no ISI.

Equation 2.22 can be written as

$$s_{i}(t) = I_{i}\sqrt{\frac{E_{0}}{T}}cos(2\pi f_{c}t) + Q_{i}\sqrt{\frac{E_{0}}{T}}sin(2\pi f_{c}t) =$$

$$= I_{i}\sqrt{\frac{E_{0}}{2}}\Phi_{1}(t) + Q_{i}\sqrt{\frac{E_{0}}{2}}\Phi_{2}(t)$$

(2.23)

where  $(I_i, Q_i)$  are a pair of independent integers which determine the location of the signal point in the constellation.  $E_0$  is the energy of the signal with the lowest amplitude, or equivalently the average energy of the signal when  $(I_i, Q_i)$  are normalized. The two orthonormal function in 2.23 are:

$$\Phi_{1}(t) = \sqrt{\frac{2}{T}}cos(2\pi f_{c}t) , for 0 \leq t \leq T$$

$$\Phi_{2}(t) = \sqrt{\frac{2}{T}}sin(2\pi f_{c}t) , for 0 \leq t \leq T$$

(2.24)

The pair  $(I_i, Q_i)$  is an element of an LxL matrix with all possible combinations. For instance a 16QAM matrix has L = 4 and is represented by:

$$[I_i, Q_i] = \begin{bmatrix} (-3, 3) & (-1, 3) & (1, 3) & (3, 3) \\ (-3, 1) & (-1, 1) & (1, 1) & (3, 1) \\ (-3, -1) & (-1, -1) & (1, -1) & (3, -1) \\ (-3, -3) & (-1, -3) & (1, -3) & (3, -3) \end{bmatrix}$$

(2.25)

The generalized M-QAM matrix, where  $M=4^n, n=1,2,3,...$ , and  $L=\sqrt{M}$ , can be written as:

$$[I_{i}, Q_{i}] = \begin{bmatrix} (-(L-1), (L-1)) & (-(L-3), (L-1)) & \cdots & ((L-1), (L-1)) \\ (-(L-1), (L-3)) & (-(L-3), (L-3)) & \cdots & ((L-1), (L-3)) \\ \vdots & \vdots & & \vdots \\ (-(L-1), -(L-1)) & (-(L-3), -(L-1)) & \cdots & ((L-1), -(L-1)) \end{bmatrix}$$

$$(2.26)$$

The constellation can be conveniently expressed in terms of  $(I_i, Q_i)$ , but the phasor for the square QAM is

$$s_i = \left(I_i \sqrt{\frac{E_0}{2}}, Q_i \sqrt{\frac{E_0}{2}}\right) \tag{2.27}$$

And consequently the average energy is given by:

$$E_{avg} = E\left\{\frac{E_0}{2}\left(I_i^2 + Q_i^2\right)\right\} = \frac{E_0}{2}\left[E\left\{I_i^2\right\} + E\left\{Q_i^2\right\}\right] = E_0E\left\{I_i^2\right\}$$

(2.28)

where

$$E\{I_i^2\} = \frac{1}{L} \left[ (-(L-1))^2 + (-(L-3))^2 + \dots + (L-3)^2 + (L-1)^2 \right] =$$

$$= \frac{2}{L} \left[ 1^2 + 3^2 + \dots + (L-1)^2 \right] = \frac{2}{L} \left[ \sum_{i=1}^{L/2} (2i-1)^2 \right] =$$

$$= \frac{1}{3} (L^2 - 1) = \frac{1}{3} (M - 1)$$

(2.29)

Thus the average power is

$$P_{avg} = \frac{E_0}{3T}(M-1) = \frac{P_0}{3}(M-1)$$

(2.30)

Where  $P_0$  is the power associated to the smallest signal. The average transmitted power required to achieve a given minimum distance is only slightly greater than the average power required for the best M-ary QAM signal constellation. For these reasons, rectangular M-ary QAM signals are most frequently used in practice.

#### Error probability

Square QAM signal constellations have the distinct advantage of being easily generated as two MASK signals impressed on the in-phase and quadrature carriers, each having  $L = \sqrt{M}$  signal points. An error occurs if the additive Gaussian noise either  $n_1$  or  $n_2$  on the orthonormal bases  $\Phi_1$ ,  $\Phi_2$  is large enough to cause an error in one of the two MASK signals. A QAM symbol is detected correctly only when two MASK symbols are detected correctly. Thus the probability of correct detection of a

Figure 2.8: The MASK constellation.

QAM symbol is the product of correct decision probabilities for constituent MASK systems.

$$P_{c,M-QAM} = P_{c,\sqrt{M}-ASK}^2 = (1 - P_{e,\sqrt{M}-ASK})^2$$

(2.31)

And consequently the error probability is

$$\begin{split} P_{e,M-QAM} &= 1 - (1 - P_{e,\sqrt{M}-ASK})^2 = \\ &= 2 P_{e,\sqrt{M}-ASK} - P_{e,\sqrt{M}-ASK}^2 \end{split} \tag{2.32}$$

where  $P_{e,\sqrt{M}-MASK}$  is symbol error probability of a single MASK with one-half the average power of the QAM signal.

Recalling that the symbol error probability of a MASK signal is given by

$$P_{e,M-ASK} = \frac{1}{M} \sum_{m=1}^{M} P(err|m)$$

$$= \frac{1}{M} \left[ 2(M-2)Q\left(\frac{d_{min}}{\sqrt{2N_0}}\right) + 2Q\left(\frac{d_{min}}{\sqrt{2N_0}}\right) \right] =$$

$$= \frac{2(M-1)}{M} Q\left(\frac{d_{min}}{\sqrt{2N_0}}\right) =$$

$$= 2\left(1 - \frac{1}{M}\right) Q\left(\sqrt{\frac{6log_2M}{M^2 - 1}} \frac{E_{b,avg}}{N_0}\right)$$

(2.33)

where  $d_{min}$  is the distance between two signal of the constellation (as in Figure 2.9) and  $Q(x) = \frac{1}{2} erfc\left(\frac{x}{\sqrt{2}}\right)$ .[2] It comes that the 2.32 becomes:

$$\begin{split} P_{e,\sqrt{M}-ASK} &= 2\left(1-\frac{1}{\sqrt{M}}\right)Q\left(\sqrt{\frac{3log_2M}{M-1}\frac{E_{b,avg}}{N_0}}\right) \\ P_{c,M-QAM} &= 4\left(1-\frac{1}{\sqrt{M}}\right)Q\left(\sqrt{\frac{3log_2M}{M-1}\frac{E_{b,avg}}{N_0}}\right) - \left(2\left(1-\frac{1}{\sqrt{M}}\right)Q\left(\sqrt{\frac{3log_2M}{M-1}\frac{E_{b,avg}}{N_0}}\right)\right)^2 \end{split}$$

That is an exact expression for the symbol error probability of a M-ary QAM signal.

Figure 2.9: The QAM symbol probability. From [2].

#### Gray coding

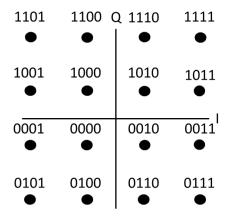

To minimize the bit error of n-tuples of QAM points, Gray coding is typically used for mapping these data. In fact the Grey code is constructed imposing that adjacent symbols differ only for one bit. In Figure 2.10 an example of Gray coding is given

Figure 2.10: The 16-QAM constellation with Gray coding.

for 16-QAM constellation. Observing that square QAM can implement perfectly Gray code, the bit error probability can be obtained from symbol error probability as

$$P_b \cong \frac{P_S}{\log_2 M} \tag{2.35}$$

supposing that there is only one bit of difference between close symbols.

# Chapter 3

# Polar code theory

Polar coding discover came out by studying a technique to improve the cutoff rate of sequential decoding of a concatenated decoding scheme. Starting from a vector channel and splitting it into multiple correlated subchannels, it was possible to use a different sequential decoder on each subchannel. Polar coding was originally designed as a simple recursive operation to be used as low complexity inner code that implemented this behaviour. But it was noticed that polar coding performance was so good that no outer convolutional code was needed to increment the cutoff rate to channel capacity. [28]

### 3.1 Preliminary definitions

#### 3.1.1 Channel models and channel coding

In order to specify a mathematical model for a channel, we shall specify:

- 1. the set of possible inputs to the channel,

- 2. the set of possible outputs,

- 3. for each input, a probability measure on the set of outputs.

Discrete memoryless channels (DMC) are a simple class of channel models and can be defined as follows: the input is a sequence of letters from a finite alphabet  $\mathcal{X} = \{a_1, \ldots, a_K\}$ , and the output is a sequence of letters from the same or a different alphabet  $\mathcal{Y} = \{b_1, \ldots, b_J\}$ . Each letter in the output sequence is statistically dependent only on the letter in the corresponding position of the input sequence and is determined by a fixed conditional probability assignment  $P(b_j|a_k)$  defined for each letter  $a_k$  in the input alphabet and each letter  $b_j$  in the output alphabet. For

Figure 3.1: Binary symmetric channel (BSC).

example, the binary symmetric channel (BSC) (see Figure 3.1) is a discrete memoryless channel (DMC) with binary input and output sequence where each digit in the input sequence is reproduced correctly at the channel output with some fixed probability 1-p and is altered by noise into the opposite digit with probability p. In general, for discrete memoryless channels, the transition probability assignment tells us everything that we have to know about how the noise combines with the channel input to produce the channel output. Another class of channel models which bears a more immediate resemblance to physical channels is the class where the set of inputs and set of outputs are each a set of time functions (waveforms), and for each input waveform the output is a random process. A particular model in this class which is of great theoretical and practical importance (particularly in space communication) is the additive Gaussian noise channel. The set of inputs for this model is the set of time functions with a given upper limit on power and the output is the sum of the input plus withe Gaussian noise. [29]

The binary-input discrete memoryless channel (B-DMC) can be defined with W:  $\mathcal{X} \to \mathcal{Y}$ , where  $\mathcal{X} = \{0,1\}$  is the input alphabet,  $\mathcal{Y}$  is the output alphabet, and W(y|x) are the transition probabilities for every  $x \in \mathcal{X}; y \in \mathcal{Y}$ . The output alphabet and the transition probabilities may be arbitrary.

Given a B-DMC , there are two channel parameters of primary interest for polar codes: the symmetric capacity and the Bhattacharyya parameter. The symmetric capacity is also known as maximum of the average mutual information, that is the mean of the mutual information, which is a random variable defined as in 3.1.

$$I_{X;Y}(a_k, b_j) = log \frac{P_{X|Y}(a_k|b_j)}{P_X(a_k)} = log \frac{P_{Y|X}(b_j|a_k)}{P_Y(b_j)} = I_{Y;X}(b_j, a_k)$$

(3.1)

where  $\{a_1, \ldots, a_K\}$  is the X sample space,  $\{b_1, \ldots, b_J\}$  is the Y sample space and XY is the joint ensemble with the probability assignment  $P_{XY}(a_k, b_j)$ . An event  $x = a_k$  might be interpreted as the input letter into a noisy discrete channel and  $y = b_j$  its output so 3.1 gives the information provided about the event x by the

occurrence of the event y.

The base of the logarithm defines the numerical scale used to measure information. For base 2 logarithms, the numerical value is called the number of bits (binary digits) of information, while for base e (natural logarithms) is the number of nats (natural units).

The average mutual information between input and output is given by 3.2.

$$I(W) = I(X;Y) \triangleq \sum_{k=1}^{K} \sum_{j=1}^{J} P_{XY}(a_k, b_j) log \frac{P_{X|Y}(a_k|b_j)}{P_X(a_k)}$$

(3.2)

For a DMC where Q(k) is the probability to measure to the input integer k and P(j|k) is the transition probability of receiving integer j given k at the channel input, 3.2 can be written as

$$I(W) = I(X;Y) = \sum_{k=1}^{K} \sum_{j=1}^{J} Q(k)P(j|k)log \frac{P(j|k)}{\sum_{i=1}^{K} Q(i)P(j|i)}$$

(3.3)

The capacity C of a discrete memoryless channel (DMC) can be written as

$$C \triangleq \max_{Q(0),\cdots,Q(K-1)} \sum_{k,j} Q(k)P(j|k)log \frac{P(j|k)}{\sum_{i} Q(i)P(j|i)}$$

(3.4)

Notice that I(X;Y) is a function of both the channel and the input assignment, while C is a function only of the channel.

The evaluation of C involves a maximization over K variables with following constraints:  $Q(k) \geq 0$  and  $\sum Q(k) = 1$ . Since the function is continuous and the maximization is over a closed bounded region of vector space, the maximum value must exist.

The average mutual information for a DMC with independent identical distributed (i.i.d.) inputs has been proved to be the symmetric capacity as in [29, Sec. 4.5] and for a B-DMC can be written as in 3.5

$$I(W) = \sum_{y \in \mathcal{Y}} \sum_{x \in \mathcal{X}} \frac{1}{2} W(y|x) \log \frac{W(y|x)}{\frac{1}{2} W(y|0) + \frac{1}{2} W(y|1)}$$

(3.5)

Another important information is given by the Bhattacharyya parameter of W,

$$Z(W) \triangleq \sum_{y \in \mathcal{Y}} \sqrt{W(y|0) + W(y|1)}$$

(3.6)

that is the upper bound on the probability of maximum-likelihood decision error when W is used only once to transmit 0 or 1. The Bhattacharyya measure has a

simple geometric interpretation as the cosine of the angle between the K-dimensional vectors  $(\sqrt{W(y_1|0)}, \ldots, \sqrt{W(y_k|0)})$  and  $(\sqrt{W(y_1|1)}, \ldots, \sqrt{W(y_k|1)})$ .[30] The parameter in 3.6 will be used instead of 3.5, to select the information set of good channels  $W_N^{(i)}$ . Intuitively the relation between I(W) and Z(W) are:

$$I(W) \approx 1 \Leftrightarrow Z(W) \approx 0$$

$I(W) \approx 0 \Leftrightarrow Z(W) \approx 1$  (3.7)

Considering the cutoff symmetric channel it can be written as:

$$E_0(\rho, Q) = -\log \sum_{j=0}^{J-1} \left[ \sum_{k=0}^{K-1} Q(k) P(j|k)^{1/(1+\rho)} \right]^{1+\rho}$$

(3.8)

It is proven in [29, Sec. 5.6] that  $I(W) \geq E_0(1, Q)$  so it can be rewritten as

$$E_{0}(1,Q) = -\log \sum_{j=0}^{J-1} \left[ \sum_{k=0}^{K-1} Q(k) P(j|k)^{1/2} \right]^{2} =$$

$$= -\log \sum_{j=0}^{J-1} \left[ Q(0) P(j|0)^{\frac{1}{2}} + Q(1) P(j|1)^{\frac{1}{2}} \right]^{2}$$

$$= -\log \sum_{j=0}^{J-1} \left[ \frac{1}{2} \sqrt{P(j|0)} + \frac{1}{2} \sqrt{P(j|1)} \right]^{2}$$

$$= \log \frac{1}{\sum_{j=0}^{J-1} \left[ \frac{1}{4} P(j|0) + \frac{1}{4} P(j|1) + \frac{1}{2} \sqrt{P(j|0)} \sqrt{P(j|1)} \right]}$$

$$= \log \frac{2}{\sum_{j=0}^{J-1} \left[ \frac{1}{2} P(j|0) + \frac{1}{2} P(j|1) \right] + \sum_{j=0}^{J-1} \left[ \sqrt{P(j|0) P(j|1)} \right]}$$

$$= \log \frac{2}{1 + Z(W)}$$

$$(3.9)$$

The information of 3.7 is then partially given by the following inequality.

$$I(W) \ge \log \frac{2}{1 + Z(W)} \tag{3.10}$$

To impose an upper limit to I(W) for a B-DMC, firstly define variation distance d(W) as

$$d(W) \triangleq \frac{1}{2} \sum_{y \in \mathcal{Y}} |W(y|0) - W(y|1)| \tag{3.11}$$

Let us consider 3.5; it can be explicitly written for both inputs as

$$I(W) = \sum_{y \in \mathcal{Y}} \frac{1}{2} \left[ W(y|0)log \frac{W(y|0)}{\frac{1}{2}W(y|0) + \frac{1}{2}W(y|1)} + W(y|1)log \frac{W(y|1)}{\frac{1}{2}W(y|0) + \frac{1}{2}W(y|1)} \right]$$

(3.12)

The *i*th term in brackets is given by

$$f(x) = x \log \frac{x}{x+\delta} + (x+2\delta)\log \frac{x+2\delta}{x+\delta}$$

(3.13)

where  $x = min\{W(y|0), W(y|1)\}$  and  $\delta = \frac{1}{2}|W(y|0) - W(y|1)|$ . To maximize f(x) over  $0 \le x \le 1 - 2\delta$  it is computed:

$$\frac{df(x)}{dx} = \log\left(\frac{x(x+2\delta)}{(x+\delta)^2}\right) = \frac{1}{2}\log\left(\frac{\sqrt{x(x+2\delta)}}{(x+\delta)}\right)$$

(3.14)

It appears  $\sqrt{x(x+2\delta)}$  the geometric mean and  $(x+\delta)$  the arithmetic mean of x and  $(x+2\delta)$ , consequently  $\frac{df}{dx} \leq 0$  and f(x) is maximum when x=0. In conclusion  $f(x)|_{x=0}=2\delta$  so  $f(x)\leq 2\delta$  and substituting in 3.12 it follows:

$$I(W) \le \sum_{y \in \mathcal{V}} \frac{1}{2} |W(y|0) - W(y|1)| = d(W)$$

(3.15)

Let  $R_i \triangleq (W(y_i|0) + W(y_i|1))/2$  and  $\delta_i \triangleq \frac{1}{2}|W(y_i|0) - W(y_i|1)|$ , then Z(W) can be rewritten as:

$$Z(W) = \sum_{y_i \in \mathcal{Y}} \sqrt{(R_i + \delta_i)(R_i - \delta_i)} = \sum_{i=1}^{J} \sqrt{(R_i^2 - \delta_i^2)}$$

(3.16)

To carry out the maximization of 3.16 over  $\delta_i$  subject to  $0 \le \delta_i \le R_i$  and i = 1, ..., J, partial derivatives are computed:

$$\frac{dZ(W)}{d\delta_{i}} = -\frac{\delta_{i}}{\sqrt{R_{i}^{2} - \delta_{i}^{2}}}$$

$$\frac{d^{2}Z(W)}{d\delta_{i}^{2}} = -\frac{R_{i}^{2}}{(R_{i}^{2} - \delta_{i}^{2})^{\frac{3}{2}}}$$

(3.17)

Z(W) is therefore is decreasing over all its domain and it is a concave function of  $\delta_i$  for each i. The maximum occurs at the solution of the set of i equations  $\frac{dZ(W)}{d\delta_i} = k$ ,

where k is a constant, in other words for  $\delta_i = R_i \sqrt{\frac{k^2}{(1+k^2)}}$ .

Impose that  $d(W) = \sum_{i=1}^{J} \delta_i = \delta$  and notice the fact that  $\sum_{i=1}^{J} R_i = 1$ , we find  $\sqrt{\frac{k^2}{(1+k^2)}} = \delta$ .

So the maximum occurs at  $\delta_i = \delta R_i$  and 3.16 has the value  $\sum_{i=1}^J \sqrt{R_i^2 - \delta^2 R_i^2} = \sqrt{1 - \delta^2}$ . We have thus shown that  $Z(W) \leq \sqrt{1 - d(W)^2}$ , which is equivalent to  $d(W) \leq \sqrt{1 - Z(W)^2}$ .

In conclusion following inequality which relates I(W) and Z(W) can be written.

$$I(W) \le d(W) \le \sqrt{1 - Z(W)^2}$$

(3.18)

An important channel considered to obtain specific results (later discussed) for polar codes theory is the B-DMC called binary erasure channel (BEC). As represented in

Figure 3.2: Binary Erasure Channel (BEC).

Figure 3.2 this channel has binary input  $\mathcal{X} = \{0,1\}$  and ternary outputs  $\mathcal{Y} = \{0,1,e\}$ , where the inputs are received unaltered with fixed probability 1-p otherwise inputs are completely lost (erased) with probability p, so the symbol e is received with probability p, called  $erasure\ probability$ .

Another important definition is the Kronecker product of a matrix  $A = [A_{i,j}]$  of

dimension  $m \times n$  and matrix  $B = [B_{i,j}]$  of dimension  $r \times s$  as:

$$A \otimes B = \begin{bmatrix} A_{1,1}B & \cdots & A_{1,n}B \\ \vdots & \ddots & \vdots \\ A_{m,1}B & \cdots & A_{m,n}B \end{bmatrix}$$

$$(3.19)$$

which is an mrxns matrix. Starting from this definition it can be given the Kronecker power  $A^{\otimes n}$  which is defined with a recursion for all  $n \geq 1$  as:

$$A^{\otimes n} = A \otimes A^{\otimes (n-1)} \tag{3.20}$$

It is also given by convention that  $A^{\otimes 0} \triangleq [1]$ .

### 3.2 Channel polarization effect

The channel polarization effect described in [23] is given by the creation of a vector of N synthetic channels  $\{W_N^{(i)}: 1 \leq i \leq N\}$  from N independent copies of a given B-DMC channel that causes as N becomes large, the symmetric capacity terms  $\{I(W_N^{(i)})\}$  tend towards 0 or 1 for all channels, with exception of a vanishing fraction of indices i. This effect can be achieved through channel splitting and channel combining operations based on [31].

#### 3.2.1 Channel combining

Starting from identical copies of a given B-DMC channel W, with a recursive method is produced the synthetic channel vector  $W_N: \mathcal{X}^N \to \mathcal{Y}^N$ , where  $N = 2^n$ ,  $n \geq 0$ . For n = 0 the synthetic channel vector equals the given channel  $W_1 \triangleq W$ , so no

Figure 3.3:  $W_2$  channel.

modification are introduced. For the second step of recursion (n = 1) two copies of  $W_1$  are used to obtain channel  $W_2: \mathcal{X}^2 \to \mathcal{Y}^2$  with the transition probability

$$W_2(y_1, y_2|u_1, u_2) = W(y_1|u_1 \oplus u_2)W(y_2|u_2)$$

(3.21)

In Figure 3.3 is given a graphical representation of how two channels are combined to obtain the synthetic channel vector for n = 1. The recursion then follows by using the new synthetic channels and combine again in the same way of the previous step, so since  $W_2$  has two channels, two copy of it will be used to generate  $W_4: \mathcal{X}^4 \to \mathcal{Y}^4$  with transition probability

$$W(y_1^4|u_1^4) = W_2(y_1^2|u_1 \oplus u_2, u_3 \oplus u_4)W_2(y_3^4|u_2, u_4)$$

(3.22)

where it is used the general notation for row vectors  $a_i^j$  as  $(a_1, \ldots, a_N)$  with  $1 \leq i$ ,  $j \leq N$ . If j < i,  $a_i^j$  is considered void. In Figure 3.4 graphical representation

Figure 3.4:  $W_4$  channel obtained by recursions of  $W_2$  and W.

of interconnection for channel  $W_4$  is shown, it is also pointed out the permutation operation  $R_4$  that maps an input  $s_1^4 = (s_1, s_2, s_3, s_4)$  to  $v_1^4 = (s_1, s_3, s_2, s_4)$ . The generating matrix that maps  $u_1^4 \mapsto x_1^4$  form the inputs of  $W_4$  to the inputs of every W (this set will be called  $W^4$ ) can be written as

$$x_1^4 = u_1^4 G_4 = u_1^4 \begin{bmatrix} 1 & 0 & 0 & 0 \\ 1 & 0 & 1 & 0 \\ 1 & 1 & 0 & 0 \\ 1 & 1 & 1 & 1 \end{bmatrix}$$

(3.23)

So it is generated the relation between the transition probabilities of  $W_4$  and those of  $W^4$ .

$$W_4(y_1^4|u_1^4) = W^4(y_1^4|u_1^4G_4) (3.24)$$

The recursion for creating the channel vector is generalized in Figure 3.5 where two

Figure 3.5: Generalized  $W_N$  channel obtained by recursion of two  $W_{\frac{N}{2}}$ .

independent copies of  $W_{\frac{N}{2}}$  are combined to produce the channel  $W_N$ . The input vector  $u_1^N$  is transformed according to:

$$\begin{cases} s_{2i-1} = u_{2i-1} \oplus u_{2i} \\ s_{2i} = u_{2i} \end{cases}$$

(3.25)

for  $1 \leq i \leq \frac{N}{2}$ . The operator  $R_N$  in figure is a reverse shuffle permutation operation over input  $s_1^N$  to produce  $v_1^N = (s_1, s_3, \ldots, s_N - 1, s_2, s_4, \ldots, s_N)$ .  $v_1^N$  is the input of the two copies of  $W_{\frac{N}{2}}$ .

The overall mapping  $u_1^N \mapsto x_1^N$  from inputs to the inputs of raw channels  $W^N$ , is linear thanks the fact that every mapping  $u_1^N \mapsto v_1^N$  in the recursion is linear over GF(2). So the final mapping can be represented by the generator matrix  $G_N$  of size  $N \times N$ , where

$$x_1^N = u_1^N G_N (3.26)$$

The transition probabilities of the two channels  $W_N$  and  $W^N$  are related by

$$W_N(y_1^N|u_1^N) = W^N(y_1^N|u_1^NG_N)$$

(3.27)

for every  $y_1^N \in \mathcal{Y}^N$ ,  $u_1^N \in \mathcal{X}^N$ .

In Section 3.3 is shown that  $G_N = B_N F^{\otimes n}$  where  $N = 2^n$ ,  $n \geq 0$ ,  $B_N$  is the bit-reversal permutation matrix and  $F \triangleq \begin{bmatrix} 1 & 0 \\ 1 & 1 \end{bmatrix}$ .

As presented, the channel combining operation is fully specified by F, and  $G_N$  and  $F^{\otimes n}$  differ only by the (bit-reversed) order of rows.

#### 3.2.2 Channel splitting

The process of splitting the vector channel  $W_N$  into N binary-input independent copies of channel W is called *channel splitting*. Formally  $W_N^{(i)}: \mathcal{X} \to \mathcal{Y}^N \mathbf{x} \mathcal{X}^{i-1}$ , for  $1 \leq i \leq N$ , defined by the transition probabilities

$$W_N^{(i)}(y_1^N, u_1^{i-1}|u_i) \triangleq \sum_{u_{i+1}^N \in \mathcal{X}^{N-i}} \frac{1}{2^{N-1}} W_N(y_1^N|u_1^N)$$

(3.28)

where  $u_i$  is the given input and  $(y_1^N, u_1^{i-1})$  is the output of  $W_N^{(i)}$ . To have an intuitive understanding of the channels  $\{W_N^{(i)}\}$ , consider to use a genie-aided decoder in which the *i*-th decision of  $u_i$  is taken after observing  $y_i^N$  and previous channel inputs  $u_1^{i-1}$  supplied correctly by the genie regardless of any decision errors at early stages. If  $u_1^N$  is a-priori uniform on  $\mathcal{X}^N$ , then  $W_N^{(i)}$  is the effective channel seen by the *i*th decision element.

For example in the case of synthetic channel vector  $W_2$ , it can be split in  $W_2^{(1)}$  and  $W_2^{(2)}$ , the transition probabilities of  $W_2^{(1)}: \mathcal{X} \to \mathcal{Y}^2$  and  $W_2^{(2)}: \mathcal{X} \to \mathcal{Y}^2 \times \mathcal{X}$  can be written as:

$$W_2^{(1)}(y_1^2|u_1) = \frac{1}{2} \sum_{u_2} W_2(y_1^2|u_1^2) = \frac{1}{2} \sum_{u_2} W(y_1|u_1 \oplus u_2)W(y_2|u_2)$$

$$W_2^{(2)}(y_1^2, u_1|u_2) = \frac{1}{2} W_2(y_1^2|u_1^2) = \frac{1}{2} W(y_1|u_1 \oplus u_2)W(y_2|u_2)$$

(3.29)

where 3.25 channel combining information has been used. For the  $\{W_N^{(i)}\}$  channels the Bhattacharyya parameter 3.6 becomes

$$Z(W_N^{(i)}) = \sum_{y_1^N \in \mathcal{Y}^N} \sum_{u_1^{i-1} \in \mathcal{X}^{i-1}} \sqrt{W_N^{(i)}(y_1^N, u_1^{i-1}|0) W_N^{(i)}(y_1^N, u_1^{i-1}|1)}$$

(3.30)

### 3.2.3 Operations on recursive synthetic channels

The goal of this section is to show that the operations 3.27 and 3.28 obtained for entire synthetic channel  $W_N^{(i)}$  originates from recursive single-step transformation of same operation on channels which created it.

Considering a pair of binary-input channels  $W': \mathcal{X} \to \tilde{\mathcal{Y}}$  and  $W'': \mathcal{X} \to \tilde{\mathcal{Y}} \times \mathcal{X}$  are obtained by a single step-step transform of two independent copies of a binary-input channel  $W: \mathcal{X} \to \mathcal{Y}$  if exist a one-to-one mapping  $f: \mathcal{Y}^2 \to \mathcal{Y}$  such that

$$W'(f(y_1, y_2)|u_1) = \sum_{u_2'} \frac{1}{2} W(y_1|u_1 \oplus u_2') W(y_2|u_2')$$

$$W''(f(y_1, y_2), u_1|u_2) = \frac{1}{2} W(y_1|u_1 \oplus u_2) W(y_2|u_2)$$

(3.31)

for every  $u_1, u_2 \in \mathcal{X}, y_1, y_2 \in \mathcal{Y}$ . If it is true we can write:

$$(W, W) \mapsto (W', W'') \tag{3.32}$$

Let us recall 3.28 for 2N channels and  $1 \le i \le N$ , we write

$$W_{2N}^{(2i-1)}(y_1^{2N}, u_1^{2i-2}|u_{2i-1}) = \sum_{u_{2i}^{2N}} \frac{1}{2^{2N-1}} W_{2N}(y_1^{2N}|u_1^{2N})$$

$$W_{2N}^{(2i)}(y_1^{2N}, u_1^{2i-1}|u_{2i}) = \sum_{u_{2i+1}^{2N}} \frac{1}{2^{2N-1}} W_{2N}(y_1^{2N}|u_1^{2N})$$

(3.33)

so considering the first equation and introducing subscript o and e on a vector that respectively represent a subvector of the initial one composed by elements with only odd or even indices, follows:

$$W_{2N}^{(2i-1)}(y_{1}^{2N}, u_{1}^{2i-2}|u_{2i-1}) = \sum_{u_{2i,o}^{2N}, u_{2i,e}^{2N}} \frac{1}{2^{2N-1}} W_{2N}(y_{1}^{2N}|u_{1}^{2N}) =$$

$$= \sum_{u_{2i,o}^{2N}, u_{2i,e}^{2N}} \frac{1}{2^{2N-1}} W_{N}(y_{1}^{N}|u_{1,o}^{2N} \oplus u_{1,e}^{2N}) W_{N}(y_{N+1}^{2N}|u_{1,e}^{2N}) =$$

$$= \sum_{u_{2i}} \frac{1}{2} \sum_{u_{2i+1,e}^{2N}} \frac{1}{2^{N-1}} W_{N}(y_{N+1}^{2N}|u_{1,e}^{2N}) \sum_{u_{2i+1,o}^{2N}} \frac{1}{2^{N-1}} W_{N}(y_{1}^{N}|u_{1,o}^{2N} \oplus u_{1,e}^{2N}) =$$

$$= \sum_{u_{2i}} \frac{1}{2} \sum_{u_{2i+1,e}^{2N}} \frac{1}{2^{N-1}} W_{N}(y_{N+1}^{2N}|u_{1,e}^{2N}) W_{N}^{(i)}(y_{1}^{N}, u_{1,o}^{2N} \oplus u_{1,e}^{2N}|u_{2i-1} \oplus u_{2i}) =$$

$$= \frac{1}{2} \sum_{u_{2i}} W_{N}^{(i)}(y_{N+1}^{2N}, u_{1,e}^{2i-2}|u_{2i,e}) W_{N}^{(i)}(y_{1}^{N}, u_{1,o}^{2i-2} \oplus u_{1,e}^{2i-2}|u_{2i-1} \oplus u_{2i})$$

$$= \frac{1}{2} \sum_{u_{2i}} W_{N}^{(i)}(y_{N+1}^{2N}, u_{1,e}^{2i-2}|u_{2i,e}) W_{N}^{(i)}(y_{1}^{N}, u_{1,o}^{2i-2} \oplus u_{1,e}^{2i-2}|u_{2i-1} \oplus u_{2i})$$

because, as  $u_{2i+1,o}^{2N}$  rages over  $\mathcal{X}^{N-i}$ ,  $u_{2i+1,o}^{2N} \oplus u_{2i+1,e}^{2N}$  ranges also over  $\mathcal{X}^{N-i}$ . Similarly for second equation of 3.31 we can write

$$W_{2N}^{(2i)}(y_1^{2N}, u_1^{2i-1}|u_{2i}) = \sum_{u_{2i+1}^{2N}} \frac{1}{2^{2N-1}} W_{2N}(y_1^{2N}|u_1^{2N}) =$$

$$= \frac{1}{2} \sum_{u_{2i+1,e}^{2N}} \frac{1}{2^{N-1}} W_N(y_{N+1}^{2N}|u_{1,e}^{2N}) \sum_{u_{2i+1}^{2N}} \frac{1}{2^{N-1}} W_N(y_1^N|u_{1,o}^{2N} \oplus u_{1,e}^{2N}) =$$

$$= \frac{1}{2} W_N^{(i)}(y_1^N, u_{1,o}^{2i-2} \oplus u_{1,e}^{2i-2}|u_{2i-1} \oplus u_{2i}) W_N^{(i)}(y_{N+1}^{2N}, u_{1,e}^{2i-2}|u_{2i})$$

$$(3.35)$$

Considering following substitutions in 3.34 and 3.35 is possible to prove that these equations are equal to 3.31.

$$W_{N}^{(i)} \to W,$$

$$W_{2N}^{(2i-1)} \to W',$$

$$W_{2N}^{(2i)} \to W'',$$

$$u_{2i-1} \to u_{1},$$

$$u_{2i} \to u_{2},$$

$$(y_{1}^{N}, u_{1,o}^{2i-2} \oplus u_{1,e}^{2i-2}) \to y_{1},$$

$$(y_{N}^{N}, u_{1,e}^{2i-2}) \to y_{2},$$

$$(y_{1}^{2N}, u_{1}^{2i-2}) \to f(y_{1}, y_{2}).$$

$$(3.36)$$

So the recursive mapping used can be written in general form as

$$(W_N^{(i)}, W_N^{(i)}) \mapsto (W_{2N}^{(2i-1)}, W_{2N}^{(2i)})$$

(3.37)

This shows that channel transformation from  $W_N$  to  $(W_N^{(1)}, \ldots, W_N^{(N)})$  can be broken into single-step channel transformation.

#### 3.2.4 Channel polarization

In the previous sections, using the channel combining and splitting operation, we have created N new channels  $W_N^{(i)}$ . Let us consider the core recursion for two identical channels and to use a simplified case of example this can be thought to be equal to the case n = 1 recursion which generates 3.29. In section 3.2.3 the validity of this approach has been proven.

This result can be exploited to evaluate how rate  $I(W_N^{(i)})$  and reliability  $Z(W_N^{(i)})$  parameters in function of the single-step transformation.

Suppose  $(W, W) \mapsto (W^-, W^+)$ , where  $W : \mathcal{X} \to \mathcal{Y}$ ,  $W^- : \mathcal{X} \to \tilde{\mathcal{Y}}$ ,  $W^+ : \mathcal{X} \to \tilde{\mathcal{Y}} \times \mathcal{X}$  and there is a one-to-one function  $f : \mathcal{Y} \to \tilde{\mathcal{Y}}$  such that 3.31 are verified. Let us

Figure 3.6: Channel variables relationship.

consider the pairs of random variables  $(U_0, U_1)$  uniformly distributed over  $\mathcal{X}^2$ , they

generate  $(X_0, X_1) = (U_0 \oplus U_1, U_1)$  (Figure 3.6). The transition probability becomes  $P_{Y_0, Y_1|X_0, X_1} = W(y_0|x_0)W(y_1|x_1)$ , and define  $\tilde{Y} = f(Y_0, Y_1)$ . It is possible to write

$$W^{-}(\tilde{y}|u_{0}) = P_{\tilde{Y}|U_{0}}(\tilde{y}|u_{0})$$

$$W^{+}(\tilde{y}, u_{0}|u_{1}) = P_{\tilde{Y}U_{0}|U_{1}}(\tilde{y}, u_{0}|u_{1})$$

(3.38)

Considering also the fact that  $(Y_0, Y_1) \mapsto \tilde{Y}$  is invertible, we get

$$I(W^{-}) = I(U_0; \tilde{Y}) = I(U_0; Y_0 Y_1)$$

$$I(W^{+}) = I(U_1; \tilde{Y} U_0) = I(U_1; Y_0 Y_1 U_0)$$

(3.39)

Since  $U_0$  and  $U_1$  are independent,  $I(U_1; Y_0Y_1U_0) = I(U_1; Y_0Y_1|U_0)$ , using the chain rule of mutual information is possible to write

$$I(W^{-}) + I(W^{+}) = I(U_{0}; Y_{0}Y_{1}) + I(U_{1}; Y_{0}Y_{1}U_{0}) =$$

$$= I(U_{0}; Y_{0}Y_{1}) + I(U_{1}; Y_{0}Y_{1}|U_{0}) =$$

$$= I(U_{0}U_{1}; Y_{0}Y_{1}) =$$

$$= I(X_{0}X_{1}; Y_{0}Y_{1})$$

(3.40)

where the one-to-one relation between  $(X_0, X_1)$  and  $(U_0, U_1)$  has been used. From Figure 3.6 can be observed that

$$I(X_0X_1; Y_0Y_1) = I(X_0; Y_0) + I(X_1; Y_1) = 2I(W)$$

(3.41)

Starting from this result is possible to prove  $I(W^+) \geq I(W)$  by noticing

$$I(W^{+}) = I(U_{1}; Y_{0}Y_{1}U_{0}) =$$

$$= I(U_{1}; Y_{1}) + I(U_{1}; Y_{0}U_{0}|Y_{1}) =$$

$$= I(W) + I(U_{1}; Y_{0}U_{0}|Y_{1})$$

(3.42)

In conclusion is possible to write

$$I(W^{-}) + I(W^{+}) = 2I(W)$$

$I(W^{-}) \le I(W) \le I(W^{+})$  (3.43)

The first equality in 3.43 means that the single-step channel transform preserves the symmetric capacity. The second inequality becomes  $I(W^-) = I(W) = I(W^+)$  if and only if W is a perfect noiseless channel ((W) = 1) or a completely noisy channel (I(W) = 0), otherwise the single-step transform moves symmetric capacity as  $I(W^-) < I(W) < I(W^+)$ , thus generating polarization. The last sentence is proven by studying when  $I(U_1; Y_0U_0|Y_1) = 0$ , this can be rewritten equivalently as

$$P_{U_0,U_1,Y_0|Y_1}(u_0,u_1,y_0|y_1) = P_{U_0,Y_0|Y_1}(u_0,y_0|y_1)P_{U_1|Y_1}(u_1|y_1)$$

(3.44)

for all  $(u_0, u_1, y_0, y_1)$  such that  $P_{Y_1}(y_1) > 0$ , or equivalently

$$P_{Y_0,Y_1|U_0,U_1}(y_0,y_1|u_0,u_1)P_{Y_1}(y_1) = P_{Y_0,Y_1|U_0}(y_0,y_1|u_0)P_{Y_1|U_1}(y_1|u_1)$$

(3.45)

for all  $(u_0, u_1, y_0, y_1)$ . Since  $P_{Y_0, Y_1|U_0, U_1}(y_0, y_1|u_0, u_1) = W(y_0|u_0 \oplus u_1)W(y_1|u_1)$ , it is possible to write 3.45 as

$$W(y_1|u_1)[W(y_0|u_0 \oplus u_1)P_{Y_1}(y_1) - P_{Y_0,Y_1|U_0}(y_0,y_1|u_0)] = 0$$

(3.46)

By construction  $P_{Y_1}(y_1) = \frac{1}{2}W(y_1|u_1) + \frac{1}{2}W(y_1|u_1 \oplus 1)$  and  $P_{Y_0,Y_1|U_0}(y_0,y_1|u_0) = \frac{1}{2}W(y_0|u_0 \oplus u_1)W(y_1|u_1) + \frac{1}{2}W(y_0|u_0 \oplus u_1 \oplus 1)W(y_1|u_1 \oplus 1)$ , simplifying is possible to obtain:

$$W(y_1|u_1)W(y_1|u_1\oplus 1)[W(y_0|u_0\oplus u_1) - W(y_0|u_0\oplus u_1\oplus 1)] = 0$$

(3.47)

choosing  $(u_0, u_1) = (0,0)$ , (but is equal for all four realizations) 3.48 becomes:

$$W(y_1|0)W(y_1|1)[W(y_0|0) - W(y_0|1)] = 0 (3.48)$$

so if  $W(y_0|0) = W(y_0|1)$  implies I(W) = 0 or exist no  $y_1$  such that  $W(y_1|0)W(y_1|1) > 0$  which means I(W) = 1.

Figure 3.7: Binary tree for the recursive construction of synthetic channels.

In Figure 3.7 is shown the process of recursive construction of channels by a binary tree graph. Starting from the root node which is associated to channel W, two children channels  $W_2^{(1)}$  and  $W_2^{(2)}$  are generated. According to previous result