### POLITECNICO DI TORINO Repository ISTITUZIONALE

#### ISPET: Interface Sintering Process Enhanced Technology

*Original* ISPET: Interface Sintering Process Enhanced Technology / Cosiansi, Fernando. - (2016).

Availability: This version is available at: 11583/2643767 since: 2016-06-13T12:39:58Z

*Publisher:* Politecnico di Torino

Published DOI:10.6092/polito/porto/2643767

*Terms of use:* Altro tipo di accesso

This article is made available under terms and conditions as specified in the corresponding bibliographic description in the repository

Publisher copyright

(Article begins on next page)

Politecnico di Torino

DOCTORAL THESIS

# ISPET: Interface Sintering Process Enhanced Technology

Author: Fernando Cosiansi Supervisor: Prof. Fabrizio Pirri *Co-Supervisor:* Marcello Turnaturi Emilio Mattiuzzo

A thesis submitted for the degree of Doctor of Philosophy in Electronics and Telecommunication Engineering

XXVIII CYCLE: 2013-2016

"Hay hombres que de su ciencia Tienen la cabeza llena; Hay sabios de todas menas, Mas digo sin ser muy ducho: Es mejor que aprender mucho El aprender cosas buenas"

José Hernández - "Martín Fierro"

#### POLITECNICO DI TORINO

## Abstract

Department of Electronics and Telecommunication

Doctor of Philosophy in Electronics and Telecommunication Engineering ISPET: Interface Sintering Process Enhanced Technology

by Fernando COSIANSI

The research presented in this thesis was carried out in VISHAY Semiconductor Italiana S.P.A.<sup>1</sup> at Borgaro Torinese - Italy.

The framework of this thesis is the study of new materials for power electronics application, analysing their thermal, mechanical and electrical properties. Emerging application of high power systems requires new methods for power electronics integration and packaging. Stringent requirements in size and weight, reliability, durability, ambient and operation temperatures are pushing to go beyond the limits in industrial applications. As a consequence, our studies are focused on power modules, incorporating new materials and technology processes (sintering) for dies or chips (silicon), substrates and interconnection materials (wire bonding).

This thesis work starts introducing the power semiconductor devices used in power electronics and their integration on Power Integrated Circuits (low and medium power density) and Power Modules (medium, high and very high power density). This chapter will explain technology evolution, power semiconductor device utilization mode and some applications.

Chapter 2 will be focused on power modules packages. They have an important role for providing cooling, electrical connection and correct insulation, between the internal semiconductor devices and the external circuit. Isolated and non isolated packages are analysed and compared.

Chapter 3 will make a point on the methods of thermal characterization and reliability tests, that were implemented to evaluate the impact of the introduction of new materials and processes into the device.

In chapter 4, first experimental results, related to the sintering process will be discussed. In this chapter the attention will be focused on the Chip to substrate Joint of the device, analysing methods to mechanically fix die to substrate. The sintering process will be

<sup>&</sup>lt;sup>1</sup>For more information http://www.vishay.com/

treated, analysing the process and the results will be thermally and mechanically characterized.

The chapter 5 will present the experimental part oriented to the combinations of materials to produce a better heavy wire bonding, supported by a Design of Experiments (DOE). The behaviour of different wires will be compared through thermal characterization methods and reliability test.

## Acknowledgements

Firstly, I would like to thank my supervisor Fabrizio Pirri from Politecnico of Torino, for the interest and trust in carrying out this project.

I would like to thank my Co-supervisors Emilio Mattiuzzo and Marcello Turnaturi for pointing me to the right path of work, for his constant availability and patience, and for giving me the opportunity to complete this experience in VISHAY Semiconductor Italiana S.P.A. at Borgaro Torinese - Italy.

Because this thesis work is the result of three years in VISHAY Semiconductor Italiana S.P.A., I would like to thank who had a key role in developing this work: Marisa Carlevaro, Adriana Aimone, Oscar Belletti, Sebastiano Ferrero, Alessio Verna, Zina Randazzo, Francesca Mastrouomo, Barbara Bernardini, Sara Martorana, Massimo Dosio, Isabelle Suberbielle, Giancarlo Di Leo, Vito Tambone, Nabil El Baradai, Carmelo Sanfilippo, Enzo Trentin, Marco Nebiolo, Domenico Cavaiuolo, Paolo Mercaldi and a special thanks in memory of Anna Maria Bonardo.

Moreover I thank all of the members of VISHAY Semiconductor Italiana S.P.A, for their hospitality and friendliness.

In addition, in collaboration with Heraeus Materials Technology GmbH & Co. and MRS Electronic GmbH from Germany, I would like to thank for their technical and scientific support to: Sven Thomas, Steffen Kötter, Susanne Duck, Thomas Krebs and Uwe Ptacek.

Finally I want really to thank my family and friends for their encouraging words and to Chiara for your faithful support.

# Contents

| A  | bstra | act     |                                                               | iv  |

|----|-------|---------|---------------------------------------------------------------|-----|

| A  | ckno  | wledge  | ements                                                        | vi  |

| C  | ontei | nts     |                                                               | vii |

| Li | st of | Figure  | es                                                            | x   |

| A  | bbre  | viation | ۱S                                                            | xiv |

| 1  | Inti  | roducti | ion                                                           | 1   |

|    | 1.1   | Power   | Semiconductor Device                                          | 1   |

|    |       | 1.1.1   | History                                                       | 1   |

|    |       | 1.1.2   | Rectifier Mode                                                | 3   |

|    |       | 1.1.3   | Switch Mode                                                   | 4   |

|    | 1.2   | Power   | Integrated Circuits (PIC)                                     | 6   |

|    | 1.3   | Power   | Modules                                                       | 7   |

|    |       | 1.3.1   | Applications                                                  | 9   |

| 2  | Pov   | ver Mo  | odules                                                        | 12  |

|    | 2.1   | Packag  | ges                                                           | 12  |

|    |       | 2.1.1   | Non isolated and isolated - Internal electronic configuration |     |

|    |       | 2.1.2   | Non Isolated Package                                          | 13  |

|    |       | 213     | Isolated Packages                                             | 14  |

|   |     | 2.1.3  | Isolated I acr  | ages                   | • • • •               | • • •                 | • • | • • | • • | • • | • • | • | • • | • • | · | • • | 14 |

|---|-----|--------|-----------------|------------------------|-----------------------|-----------------------|-----|-----|-----|-----|-----|---|-----|-----|---|-----|----|

|   |     | 2.1.4  | Critical and    | improvabl              | e points              |                       |     |     |     |     |     |   | ••• |     | • |     | 16 |

| 2 | The | nmol ( | Characteriza    | tion and               | Doliah                | :1:+                  |     |     |     |     |     |   |     |     |   |     | 18 |

| J | THE |        |                 | tion and               | nenau                 | muy                   |     |     |     |     |     |   |     |     |   |     | 10 |

|   | 3.1 | Therm  | al Characteriz  | zation - Te            | est Meth              | od.                   |     |     |     |     |     | • | ••  |     |   |     | 18 |

|   |     | 3.1.1  | Thermal Res     | istance $\mathbf{R}_t$ | $h \cdot \cdot \cdot$ |                       |     |     |     |     |     |   |     |     |   |     | 21 |

|   | 3.2 | Reliab | ility - Test Me | ethods                 |                       |                       |     |     |     |     |     |   |     |     |   |     | 24 |

|   |     | 3.2.1  | Power Cyclin    | ig Test                |                       |                       |     |     |     |     |     |   |     |     |   |     | 24 |

|   |     |        | 3.2.1.1 Lon     | g Power (              | Cycling '             | $\operatorname{Test}$ |     |     |     |     |     |   |     |     |   |     | 25 |

|   |     |        | 3.2.1.2 Sho     | rt Power               | Cycling               | Test                  |     |     |     |     |     |   |     |     |   |     | 26 |

|   |     | 3.2.2  | Temperature     | Cycling 7              | Fest                  |                       |     |     |     |     |     |   | •   |     |   |     | 28 |

|   | 3.3 | Conch  | sion            |                        |                       |                       |     |     |     |     |     |   |     |     |   |     | 30 |

| 4 | Chi  | p to substrate Joint 32                                                                                                                                             | 1 |

|---|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|   | 4.1  | Materials                                                                                                                                                           |   |

|   |      | 4.1.1 $SnAg(3.5)$                                                                                                                                                   | , |

|   |      | 4.1.2 mAgic Paste                                                                                                                                                   |   |

|   | 4.2  | Processes                                                                                                                                                           |   |

|   |      | 4.2.1 Soldering                                                                                                                                                     | 1 |

|   |      | 4.2.2 Sintering                                                                                                                                                     |   |

|   |      | 4.2.2.1 Overview                                                                                                                                                    |   |

|   |      | $4.2.2.2  \text{Solid phase sintering} \dots 38$                                                              |   |

|   |      | $4.2.2.3  \text{Sintering parameters} \dots \dots$            | i |

|   |      | 4.2.2.4 Sintering Process of Silver Powder                                                                                                                          | , |

|   | 4.3  | Experimental Procedure                                                                                                                                              |   |

|   |      | 4.3.1 Silver sintering adapting                                                                                                                                     |   |

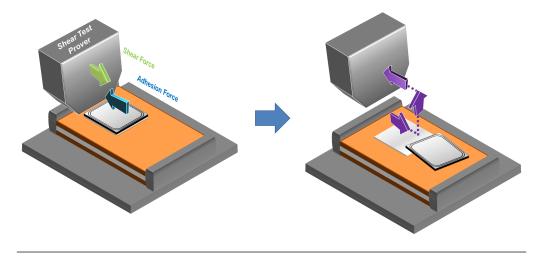

|   |      | 4.3.2 Evaluation of mechanical adhesion                                                                                                                             |   |

|   |      | 4.3.3 Power Cycling capability                                                                                                                                      | , |

|   |      | $4.3.3.1  Rth_{j-c} \text{ measures } \dots $                 | I |

|   |      | 4.3.4 Failure Analysis (F.A.)                                                                                                                                       |   |

|   |      | 4.3.4.1 MTP (Isolated) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 55$                                                                                 |   |

|   |      | 4.3.4.2 TO-244 (Non isolated) and ADD-A-PAK (Isolated) $\ldots$ 58                                                                                                  |   |

|   | 4.4  | Evaluation of Electrochemical Migration (ECM) 59                                                                                                                    |   |

|   |      | 4.4.1 Electrochemical migration phenomenon                                                                                                                          |   |

|   |      | 4.4.2 Test without environmental isolation                                                                                                                          |   |

|   |      | 4.4.3 Test on performed power module                                                                                                                                | , |

|   | 4.5  | Conclusion                                                                                                                                                          |   |

| 5 | Bor  | nd Connection 66                                                                                                                                                    |   |

| J | 5.1  | Heavy wire bonds materials                                                                                                                                          |   |

|   | 0.1  | 5.1.1 Ultrasonic $(U/S)$ bonding process                                                                                                                            |   |

|   | 5.2  | Experimental Part                                                                                                                                                   |   |

|   | 0.2  | 5.2.1 Temperature Cycling capability                                                                                                                                |   |

|   |      | 5.2.2 Design of Experiments (DOE) applied to obtain the CucoreAl                                                                                                    |   |

|   |      | $60/40 (12 \text{ mils}) \text{ bond parameters} \dots \dots$ |   |

|   |      | 5.2.3 Power Cycling capability 80                                                                                                                                   |   |

|   |      | 5.2.3.1 Failure Analysis (F.A.)                                                                                                                                     |   |

|   | 5.3  | Conclusion                                                                                                                                                          | į |

|   |      |                                                                                                                                                                     |   |

| 6 | Cor  | nclusive Remarks 97                                                                                                                                                 |   |

|   |      |                                                                                                                                                                     |   |

|   | ~    |                                                                                                                                                                     |   |

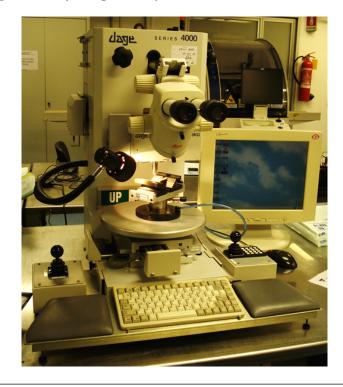

| Α |      | ear Test 100                                                                                                                                                        |   |

|   | A.1  | 4000 Multipurpose Bondtester                                                                                                                                        |   |

| В | Fail | ure Analysis Instrumentation 102                                                                                                                                    |   |

|   | B.1  | Curve Tracer                                                                                                                                                        |   |

|   | B.2  | Microscopes                                                                                                                                                         |   |

|   |      | B.2.1 Nikon Eclipse LV150                                                                                                                                           |   |

|   |      | B.2.2 Tagarno                                                                                                                                                       |   |

|            | B.2.3  | Leica Wild MZ8                              | . 104 |

|------------|--------|---------------------------------------------|-------|

|            | B.2.4  | C-Mode Scanning Acoustic Microscopy (C-SAM) | . 105 |

|            | B.2.5  | Thermal Emission                            | . 107 |

| B.3        | Polish | ing System                                  | . 108 |

| <b>B.4</b> | Chemi  | ical Fume Hood                              | . 109 |

### Bibliography

# List of Figures

| 1.1               | Diode - (a)Electronic symbol, (b) Die representation and (c) Operating<br>wave form.                                                                                                                      | 4        |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2               | Switch Mode - (a) Schematic electric and (b) Wave forms of Inverter                                                                                                                                       |          |

| 1.3               | configuration                                                                                                                                                                                             | 5        |

| 1.4               | (b) Wave forms                                                                                                                                                                                            | 5        |

| 1.5               | tracted from [1])                                                                                                                                                                                         | 6        |

| 1.6               | drive                                                                                                                                                                                                     | 8<br>11  |

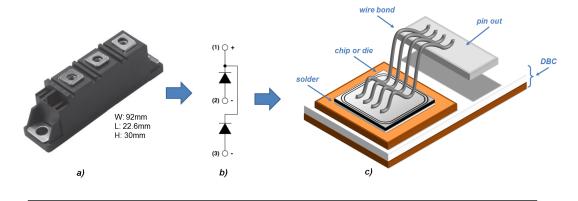

| 2.1               | Non isolated power module - (a) Real device, (b) Internal electronic con-<br>figuration and (c) Internal composition.                                                                                     | 14       |

| 2.2               | Isolated power module - (a) Real device, (b) Internal electric scheme and (c) Internal composition.                                                                                                       | 15       |

| 2.3               | Isolated power module without base plate - (a) Real device, (b) Internal electric scheme and (c) Internal composition.                                                                                    | 16       |

| 2.4               | Improvable points on an isolated power module                                                                                                                                                             | 17       |

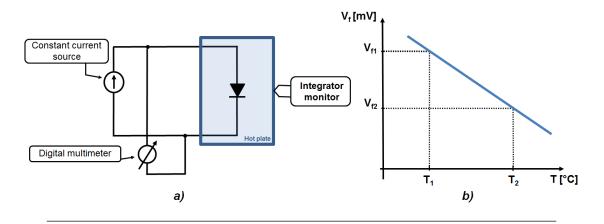

| $3.1 \\ 3.2$      | Thermal circuit of a power module                                                                                                                                                                         | 19       |

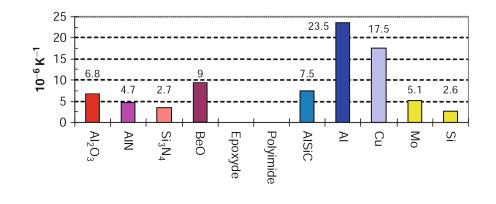

| 3.3               | connection and (b) Measured $V_f$ in function of temperature Coefficient of Thermal Expansion (CTE) of materials frequently used in                                                                       | 20       |

| 3.4               | package technologies                                                                                                                                                                                      | 21<br>22 |

| 3.5               | Thermocouple locations                                                                                                                                                                                    | 22       |

| $\frac{3.6}{3.7}$ | Typical temperature excursion of Power Cycling Test set-up Large Power Cycling Test (PCT) - (a) Schematic draw of tools connection and (b) Example of power modules connection and thermocouple location. | 26<br>26 |

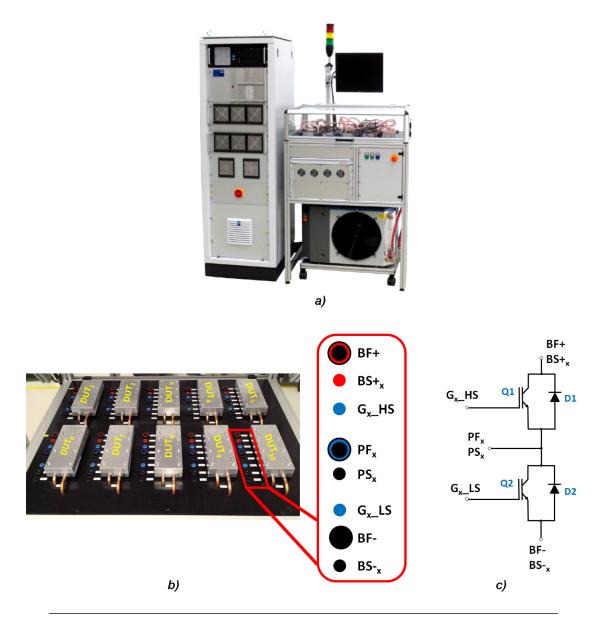

| 3.8               | Short Power Cycling Test (PCT) - (a) MRS Tester, (b) Internal connec-<br>tion possibilities and (c) Electric scheme reference.                                                                            | 28       |

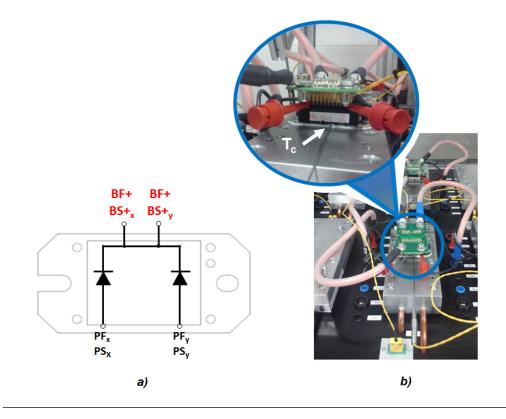

| 3.9               | Example connection - (a) Scheme electric of isolated power module on                                                                                                                                      |          |

| 3.10              | test (b) Thermocouple location                                                                                                                                                                            | 29<br>30 |

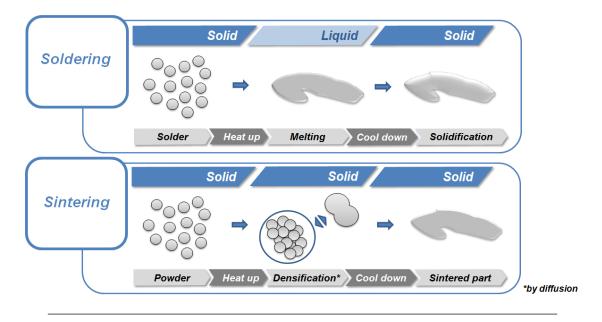

| 4.1 $4.2$         | Solder Vs. Silver Sintering - Scheme of Physical Phases during the processes.<br>Solder Process Scheme - a) Printing/dispensing, b) Die placement, c)                                                     | 36       |

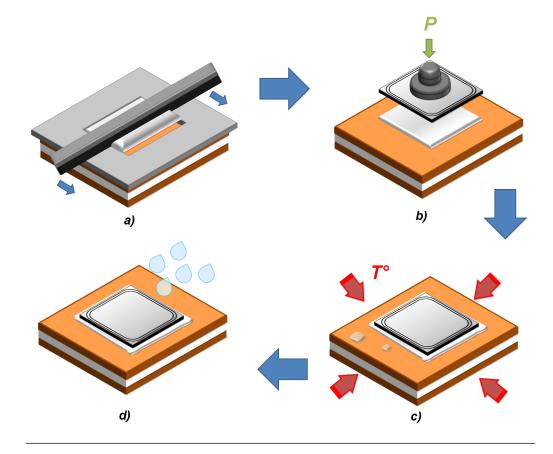

|                   | Vacuum reflow and c) Cleaning                                                                                                                                                                             | 37       |

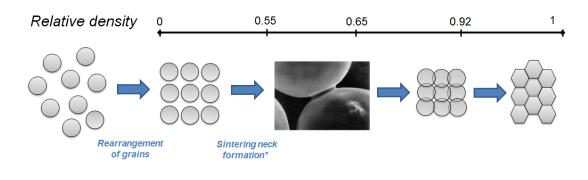

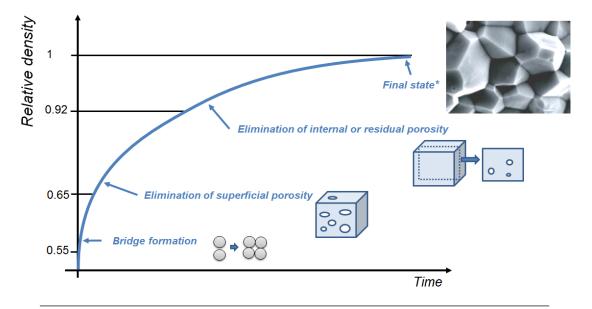

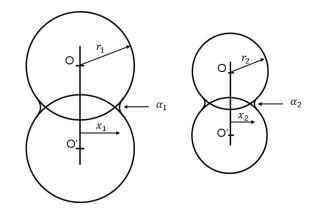

| 4.3  | Scheme of initial stage of sintering process in solid phase                                                                             | 39 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.4  | Density evolution during sintering process in solid phase [2]                                                                           | 39 |

| 4.5  | Scheme of Herring law illustrating the influence of the particles diameter                                                              |    |

|      | of the powder to be sintered [2]                                                                                                        | 41 |

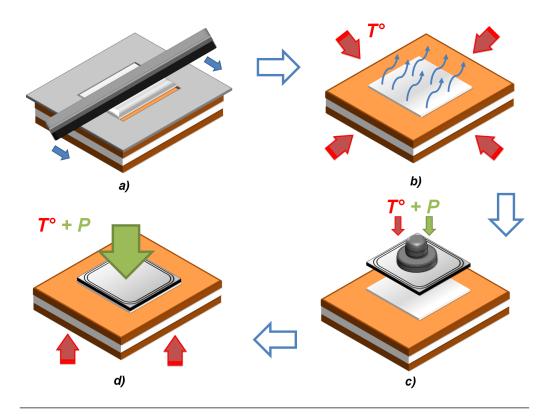

| 4.6  | Sinter Process Scheme - a) Paste application, b) Drying, c) Die placement                                                               |    |

|      | and d) Pressure Assisted sintering                                                                                                      | 43 |

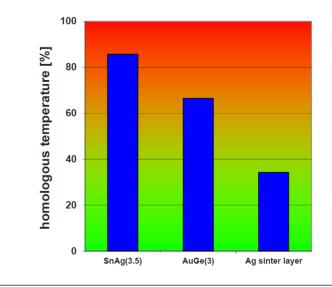

| 4.7  | Homologous temperature comparison between solders and sinter materi-                                                                    |    |

|      | als, for an operation temperature of $150^{\circ}C$ (extracted from [3])                                                                | 44 |

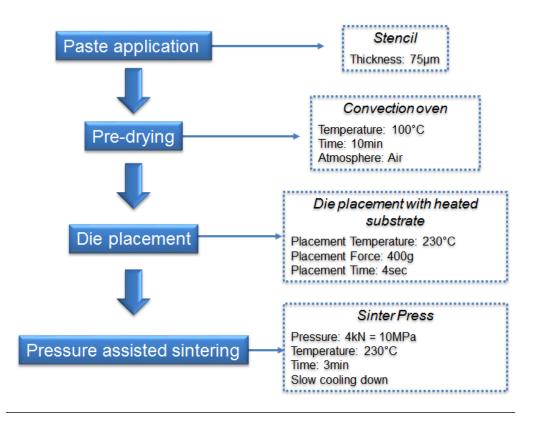

| 4.8  | Description of silver sintering process flow used in collaboration with                                                                 |    |

|      | HERAEUS Materials Technology.                                                                                                           | 46 |

| 4.9  | AES image of Element Analysis of die BSM                                                                                                | 46 |

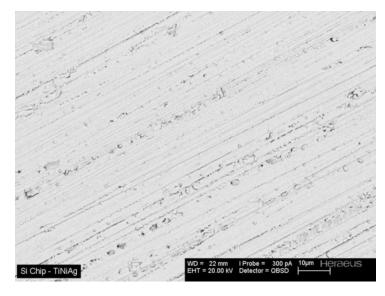

| 4.10 | SEM images of die BSM (Ag thickness $0.3\mu m$ )                                                                                        | 47 |

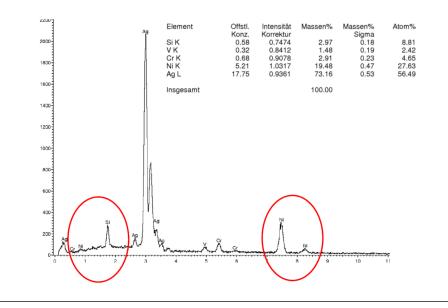

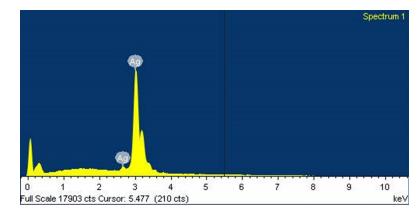

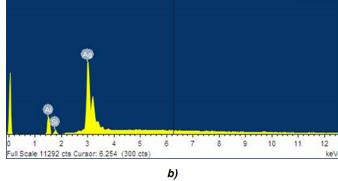

| 4.11 | EDX analysis of die BSM Ag thickness $0.6\mu m@10 KeV$                                                                                  | 47 |

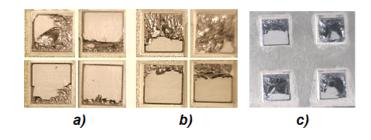

| 4.12 | Some examples of broken dies after shear test at TCT $@-40/+150^{\circ}C$ ,                                                             |    |

|      | (a) MTP DBC "A" and (b) MTP DBC "B" and (c) TO-244 Base Plate                                                                           |    |

|      | "Ag"                                                                                                                                    | 49 |

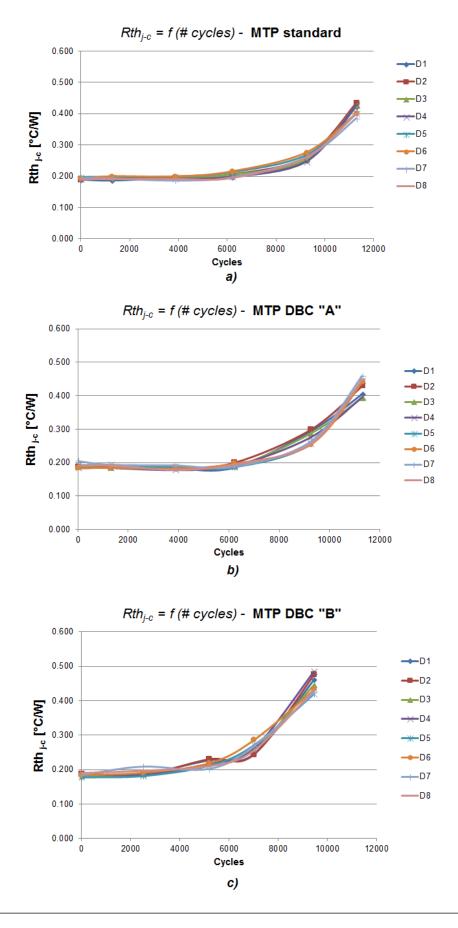

| 4.13 | $Rth_{j-c}$ measures of MTP (a) Standard, (b) DBC "A" and (c) DBC "B",                                                                  |    |

|      | during Long Power Cycling Test ( $@\Delta T_c \cong 100^\circ C$ )                                                                      | 51 |

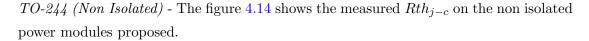

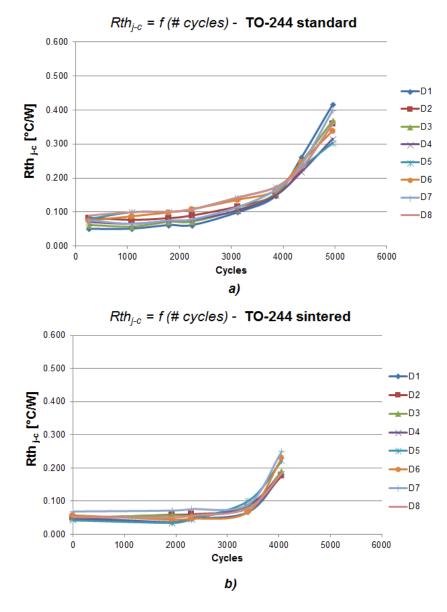

| 4.14 | $Rth_{j-c}$ measures of TO-244 (a) Standard and (b) Sintered during Long                                                                |    |

|      | Power Cycling Test (@ $\Delta T_j \cong 100^{\circ}C$ ).                                                                                | 52 |

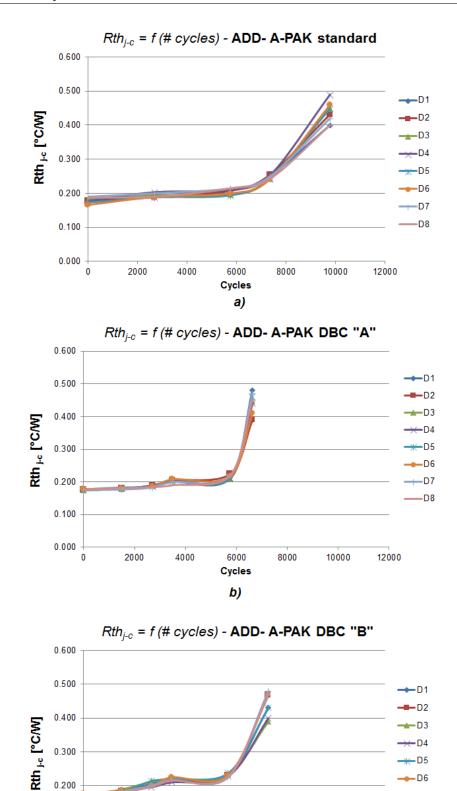

| 4.15 | $Rth_{j-c}$ measures of ADD-A-PAK (a) Standard, (b) DBC "A" and (c)                                                                     |    |

|      | DBC "B", during Long Power Cycling Test ( $@\Delta T_c \cong 100^{\circ}C$ )                                                            | 54 |

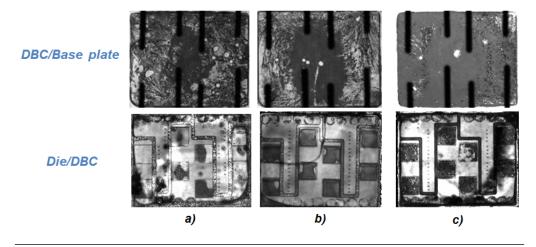

| 4.16 | C-SAM images of DBC/Base plate and Die/DBC joints of (a) DBC type                                                                       |    |

|      | "A", (b) DBC type "B" and (c) Standard.                                                                                                 | 55 |

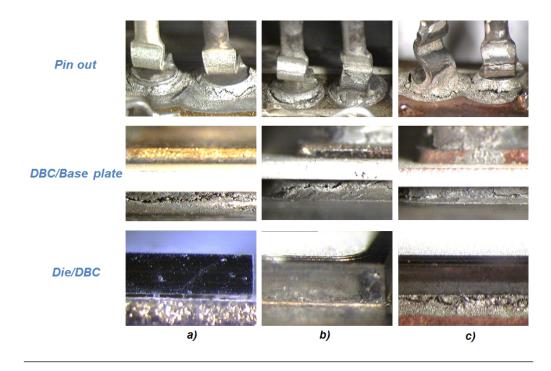

| 4.17 | Tilt microscope analysis of (a) DBC type "A", (b) DBC type "B" and                                                                      | •  |

|      | (c) Standard. $\ldots$                                                                                                                  | 56 |

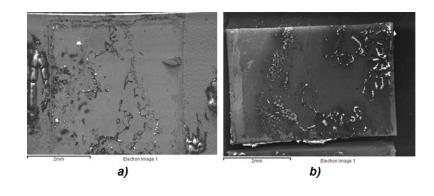

| 4.18 | DBC type "A" - SEM images of (a) Sinter layer on substrate after diode                                                                  |    |

| 1 10 | removing and (b) Die backside.                                                                                                          | 57 |

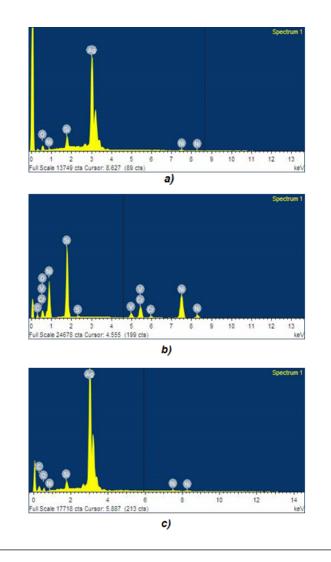

| 4.19 | DBC type "A" - EDX analysis of (a) Sinter layer on substrate after diode                                                                |    |

|      | removing, where only silver was found and back side die: (b) V, Cr and Ni were found on the centre area and (c) Ag and Ni on the border | 57 |

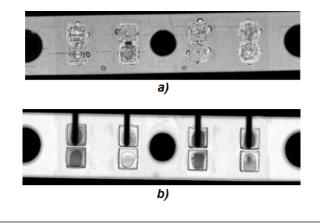

| 4.90 | C-SAM images of die/Base plate joint of (a) TO-244 soldered and (b)                                                                     | 51 |

| 4.20 | TO-244 sintered.                                                                                                                        | 59 |

| 1 91 | C-SAM images of die/DBC joint of (a) Standard, (b) DBC type "A" and                                                                     | 05 |

| 7.21 | (c) DBC type "B"                                                                                                                        | 59 |

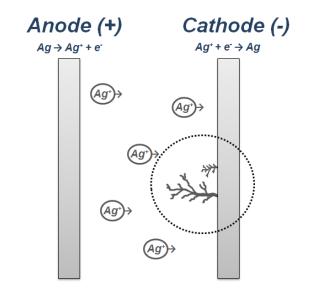

| 4 22 | Silver migration schematic diagram.                                                                                                     |    |

|      | Scheme of used method to study the dependency of TTF and reverse bias                                                                   | 00 |

| 1.20 | applied on three different structures without gel potting                                                                               | 61 |

| 4.24 | Standard structure - Copper DBC and solder die attach: (a) SEM images                                                                   |    |

|      | of silver dendrites around the die top, (b) EDX analysis shows dendrites                                                                |    |

|      | with Cu/C/Ca/Cr/O/Al/Si/Ag/Sn composition.                                                                                              | 62 |

| 4.25 | Sintered structure - DBC Ag finishing and Ag sinter die attach (a) SEM                                                                  |    |

|      | images of silver dendrites around the die top, (b) EDX analysis shows                                                                   |    |

|      | dendrites with Ag/C/O/Al/Si material composition.                                                                                       | 63 |

| 4.26 | Sintered structure - DBC Au finishing and Ag sinter die attach (a) SEM                                                                  |    |

|      | images of silver dendrites around the die top, (b) EDX analysis shows                                                                   |    |

|      | dendrites with Ag/Al/Si composition.                                                                                                    |    |

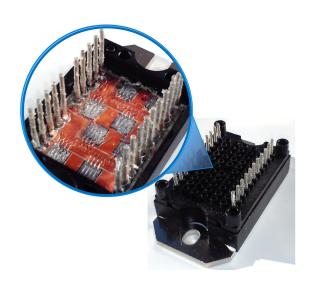

| 4.27 | Completed power module                                                                                                                  | 64 |

| 5.1          | Perpendicular and parallel cross section, and mechanical behaviour - (a) 5N-H11 wire and (b) 5N-H11-CR wire.                                                                                                                                                                | 68       |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

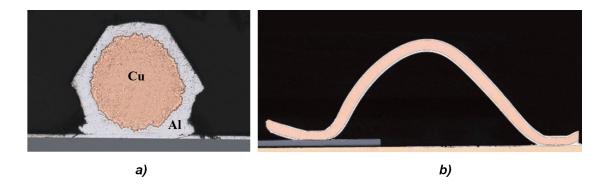

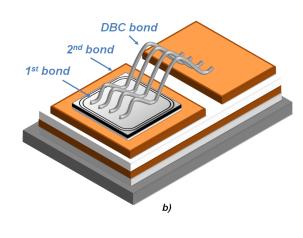

| 5.2          | CucorAl wire bonding: perpendicular (a) and parallel (b) cross section to<br>the bonding direction.                                                                                                                                                                         | 69       |

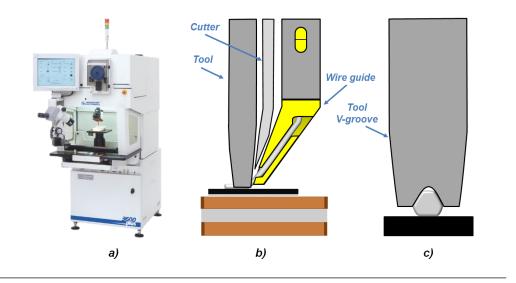

| 5.3          | U/S bonding equipment - (a) Wire bonder machine utilized and description of (b) bonder head "lateral view" and (c) tool "front view".                                                                                                                                       | 70       |

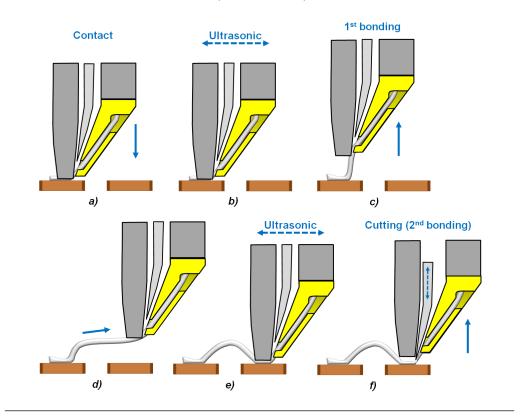

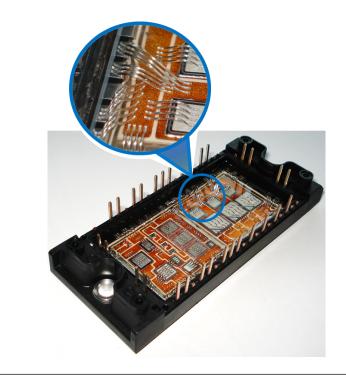

| 5.4          | U/S bonding process description.                                                                                                                                                                                                                                            | 70       |

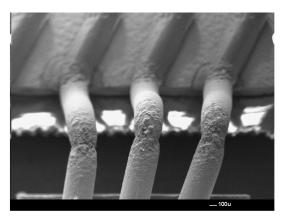

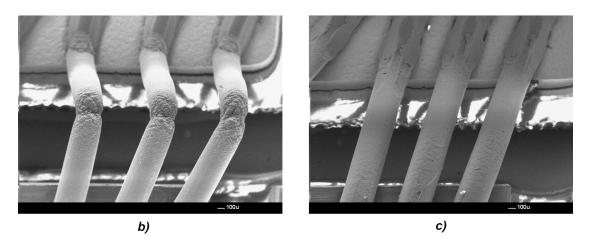

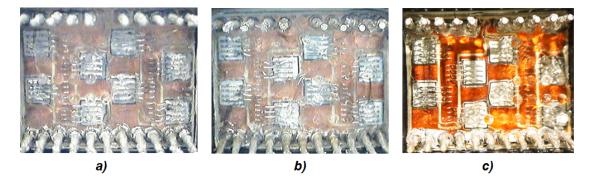

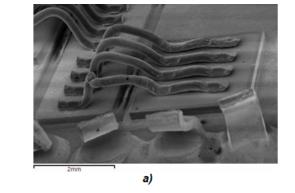

| $5.5 \\ 5.6$ | Wire bonding location into the power module dedicated to TCT analysis.<br>Stressed loops for three different types of wire bonding Al based materials<br>after 1400 cycles of TCT $@-55^{\circ}C$ to $+150^{\circ}C$ - (a) 5N-H11, (b) 5N H11-<br>CR and (c) CucorAl 60/40. | 72<br>73 |

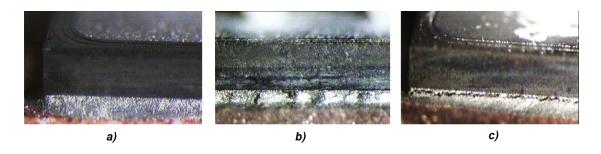

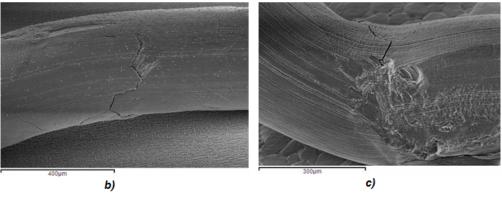

| 5.7          | Bonding point stressed of an 5N-H11-CR wire, as resulting after TCT                                                                                                                                                                                                         | 73       |

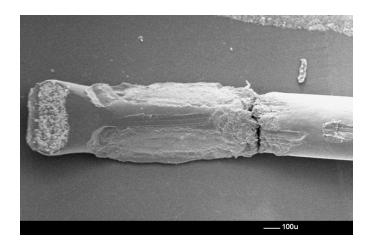

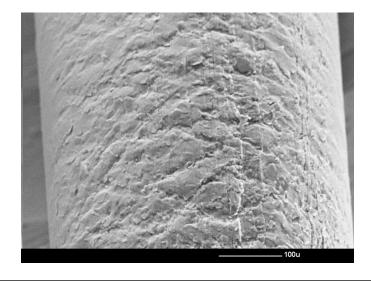

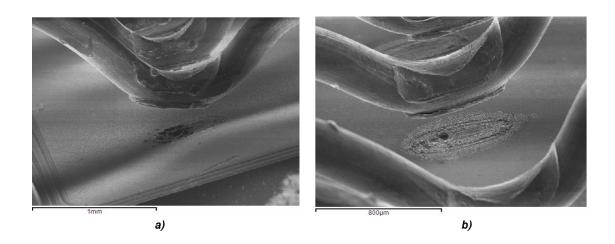

| 5.8          | Crack initiations at the surface of an 5N-H11-CR wire under thermo-<br>mechanical stress.                                                                                                                                                                                   | 74       |

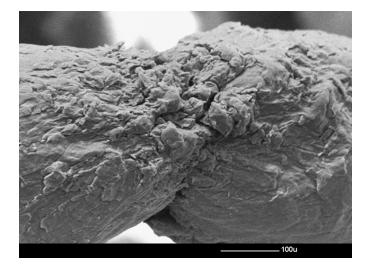

| 5.9          | Crack initiations and corrugation formation at the surface of a CucorAl wire under thermo-mechanical stress.                                                                                                                                                                | 75       |

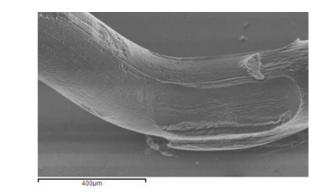

| 5.10         | CucorAl wire bonding cross section under thermomechanical stress.                                                                                                                                                                                                           | 75       |

|              | DOE wire bonding - (a) Utilized matrix and (b) involved bondings representation.                                                                                                                                                                                            | 77       |

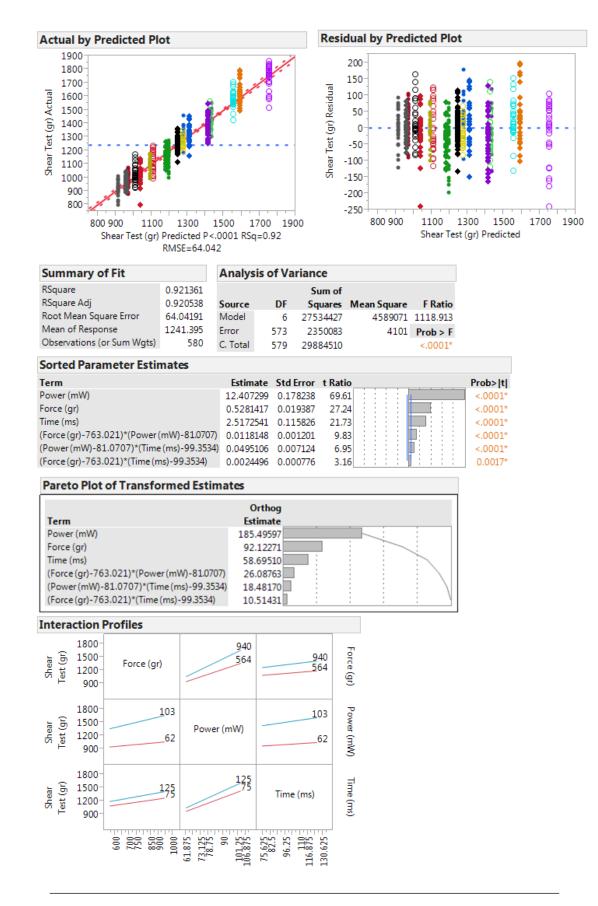

| 5 12         | DOE results of $1^{st}$ response: Shear Test.                                                                                                                                                                                                                               | 79       |

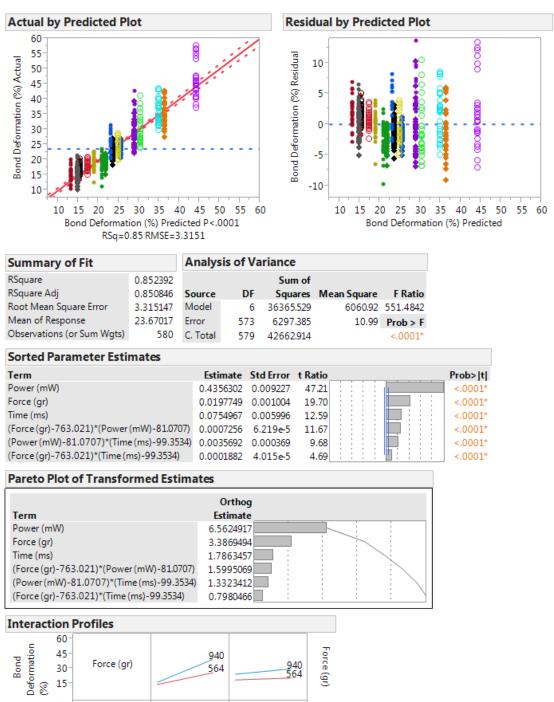

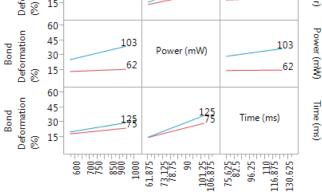

|              | DOE results of $2^{nd}$ response: Bond Deformation %                                                                                                                                                                                                                        | 81       |

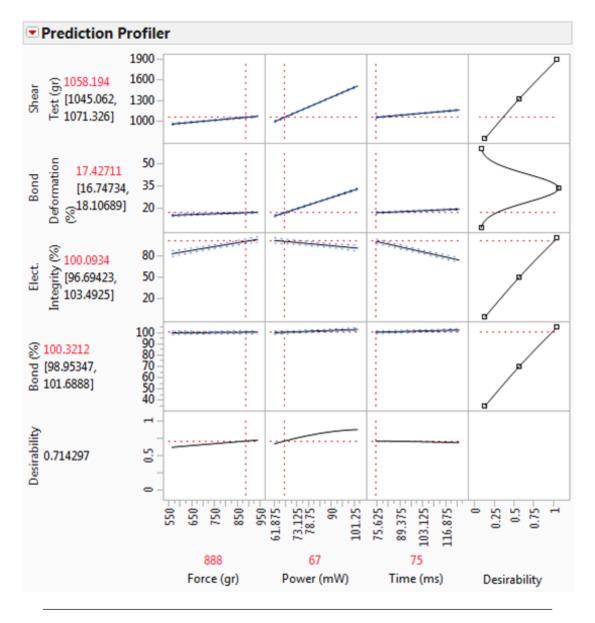

|              | Final optimised parameters obtained with Prediction Profiler.                                                                                                                                                                                                               | 82       |

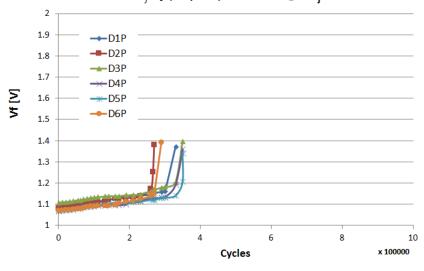

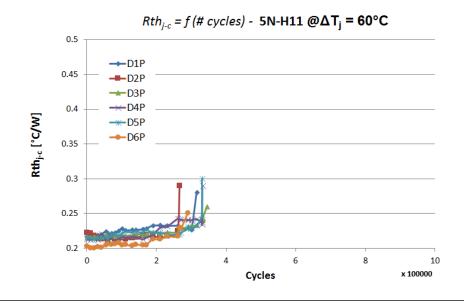

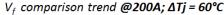

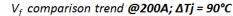

|              | $V_f$ measures during Short Power Cycling Test ( $@\Delta T_j \cong 60^\circ C$ ) with 5N-H11 wire.                                                                                                                                                                         | 83       |

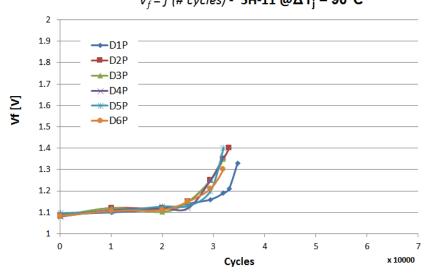

| 5.16         | $Rth_{j-c}$ measures during Short Power Cycling Test ( $@\Delta T_j \cong 60^\circ C$ ) with 5N-H11 wire.                                                                                                                                                                   | 84       |

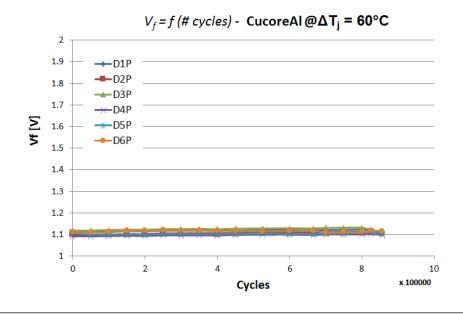

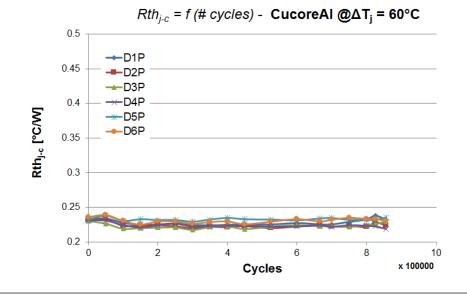

| 5.17         | $V_f$ measures during Short Power Cycling Test (@ $\Delta T_j \cong 60^{\circ}C$ ) with CucoreAl wire.                                                                                                                                                                      | 84       |

| 5.18         | $Rth_{j-c}$ measures during Short Power Cycling Test ( $@\Delta T_j \cong 60^\circ C$ ) with CucoreAl wire.                                                                                                                                                                 | 85       |

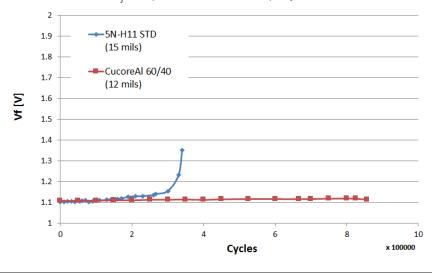

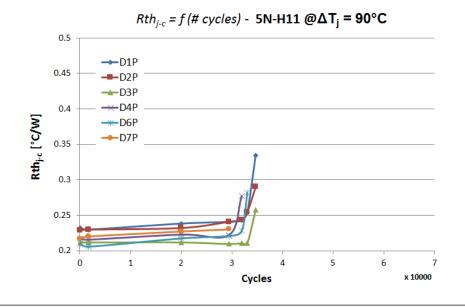

| 5.19         | $V_f$ average trend comparison between 5N-H11 and CucoreAl wire mate-<br>rials (@ $\Delta T_j \cong 60^{\circ}C$ )                                                                                                                                                          | 85       |

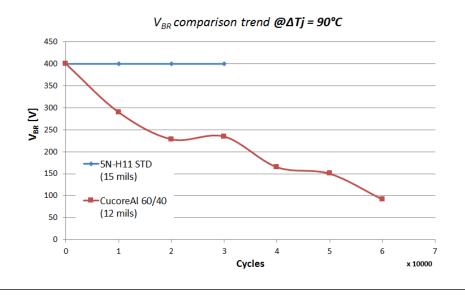

| 5.20         | 5N-H11 vs. CucoreAl wire under Short PCT ( $@\Delta T_i \cong 60^\circ C$ ) - $V_{BR}$ trend.                                                                                                                                                                               |          |

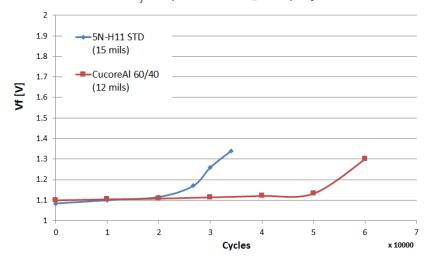

|              | $V_f$ measures during Short Power Cycling Test (@ $\Delta T_j \cong 90^{\circ}C$ ) with 5N-H11 wire.                                                                                                                                                                        | 86       |

| 5.22         | $Rth_{j-c}$ measures during Short Power Cycling Test ( $@\Delta T_j \cong 90^\circ C$ ) with 5N-H11 wire.                                                                                                                                                                   | 87       |

| 5.23         | $V_f$ average trend comparison between 5N-H11 and CucoreAl wire mate-<br>rials ( $@\Delta T_i \cong 90^\circ C$ ).                                                                                                                                                          | 87       |

| 5.24         | 5N-H11 vs. CucoreAl wire under Short PCT ( $@\Delta T_i \cong 90^\circ C$ ) - $V_{BR}$ trend.                                                                                                                                                                               | 88       |

|              | $\# cycles = f(\Delta T_i)$ under Short Power Cycling Test                                                                                                                                                                                                                  | 89       |

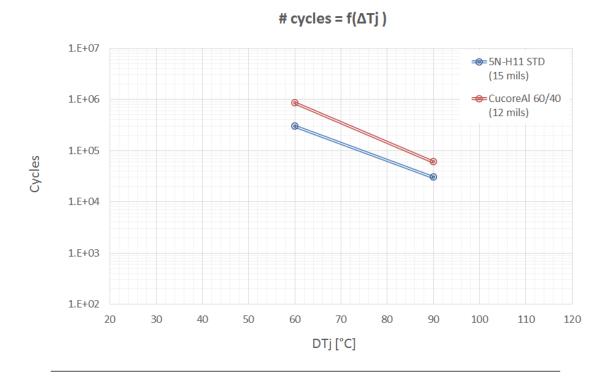

|              | $T_{j} = 60^{\circ}C$ , (b) 5N-H11 $@\Delta T_{j} = 90^{\circ}C$ and (c) CucoreAl $@\Delta T_{j} = 90^{\circ}C$ .                                                                                                                                                           | 90       |

| 5.27         | Silicon gel after Short PCT - (a) 5N-H11 @ $\Delta T_j \cong 60^{\circ}C$ , (b) 5N-H11<br>@ $\Delta T_j \cong 90^{\circ}C$ and (c) CucoreAl @ $\Delta T_j \cong 90^{\circ}C$                                                                                                | 90       |

| 5.28         | Tilt magnification view of solder below diode - (a) 5N-H11 $@\Delta T_j \cong 60^{\circ}C$ ,<br>(b) 5N-H11 $@\Delta T_j \cong 90^{\circ}C$ and (c) CucoreAl $@\Delta T_j \cong 90^{\circ}C$ .                                                                               | 91       |

|              |                                                                                                                                                                                                                                                                             |          |

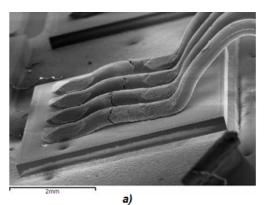

| 5.29 | SEM images of 5N-H11 wires $@\Delta T_j \cong 60^{\circ}C$ - (a) Analysed wires, (b)   |    |

|------|----------------------------------------------------------------------------------------|----|

|      | Break between the $1^{st}$ and the $2^{nd}$ bond and (c) Modifications of the          |    |

|      | grain structure at the surface in the $2^{nd}$ loop.                                   | 91 |

| 5.30 | SEM images of 5N-H11 wires $@\Delta T_i \cong 90^\circ C$ - (a) Analysed wires, (b)    |    |

|      | Breaks between the $1^{st}$ and the $2^{nd}$ bond and (c) Cracks close to the $2^{nd}$ |    |

|      | bond                                                                                   | 92 |

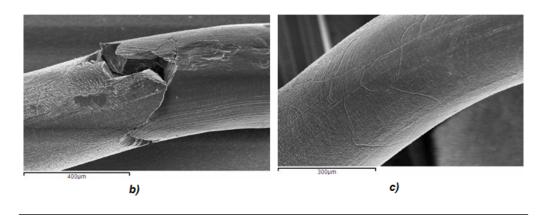

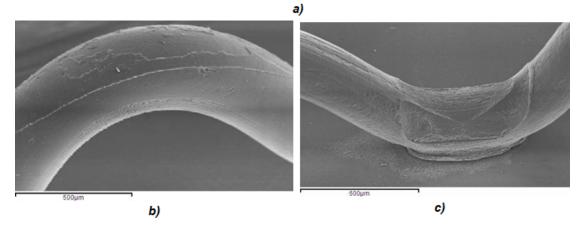

| 5.31 | SEM images of CucorAl wires $@\Delta T_i \cong 90^\circ C$ - No damages presented on   |    |

|      | (a) $1^{st}$ bond, (b) $1^{st}$ loop and (c) $2^{nd}$ bond                             | 93 |

| 5.32 | SEM images of CucorAl wires $@\Delta T_j \cong 90^\circ C$ - (a) Crater produced and   |    |

|      | (b) Wire lit-off.                                                                      | 93 |

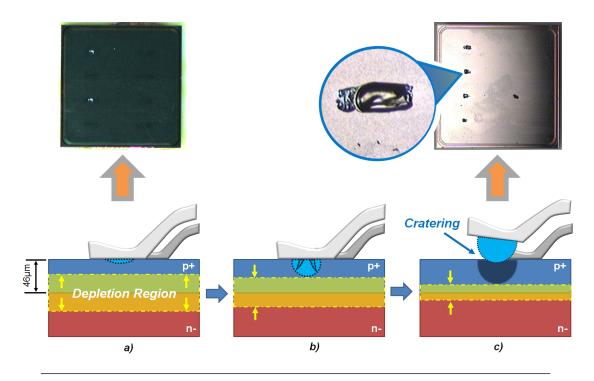

| 5.33 | $V_{BR}$ degradation by cratering formation under CuroreAl bond during                 |    |

|      | Short PCT - (a) Smaller induced stress during bonding process, (b) Stress              |    |

|      | induced during PCT and (c) Finally cratering formation.                                | 94 |

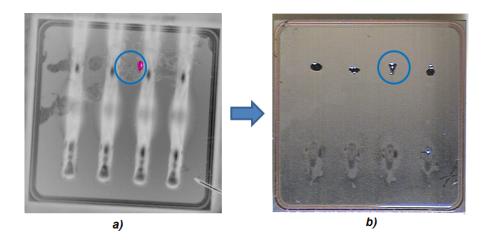

| 5.34 | Thermal emission analysis - (a) Hot spot under CucoreAl wire and (b)                   |    |

|      | Silicon cratering in correspondence of hot point after chemical etching                | 95 |

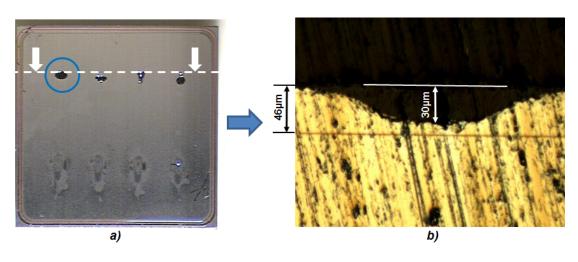

| 5.35 | Cross-section analysis - (a) Indication of sectioned area and (b) Crater               |    |

| 0.00 | magnification with measurements.                                                       | 95 |

|      |                                                                                        | 00 |

# Abbreviations

| AC            | Alterning Current                                                                                                                                                                                |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AES           | $\mathbf{A} uger \; \mathbf{E} lectron \; \mathbf{S} pectroscopy$                                                                                                                                |

| ASP           | $\mathbf{Ag}$ Sinter Paste                                                                                                                                                                       |

| BJT           | ${\bf B} {\rm ipolar} \ {\bf J} {\rm unction} \ {\bf T} {\rm ransistor}$                                                                                                                         |

| BLDC          | $\mathbf{B} \text{rushless} \ \mathbf{D} \mathbf{C}$                                                                                                                                             |

| BSM           | $\mathbf{B}$ ackside $\mathbf{M}$ etallization                                                                                                                                                   |

| C-SAM         | $\mathbf{C}\text{-}\mathrm{Mode}\ \mathbf{S}\mathrm{canning}\ \mathbf{A}\mathrm{coustic}\ \mathbf{M}\mathrm{icroscopy}$                                                                          |

| CTE           | Coeficient of Thermal Expansion                                                                                                                                                                  |

| DBC           | Direct Bond Copper                                                                                                                                                                               |

| DC            | Direct Current                                                                                                                                                                                   |

| DOE           | Design Of Experiments                                                                                                                                                                            |

| ECM           | $\mathbf{E}$ lectrochemical $\mathbf{M}$ igration                                                                                                                                                |

| EDX           | $\mathbf{E}$ nergy- $\mathbf{D}$ ispersive $\mathbf{X}$ -ray                                                                                                                                     |

| EMI           | $\mathbf{E}$ lectro $\mathbf{m}$ agnetic Interference                                                                                                                                            |

| $\mathbf{EV}$ | Electric Vehicles                                                                                                                                                                                |

| FA            | $\mathbf{F}$ ailure $\mathbf{A}$ nalysis                                                                                                                                                         |

| FRED          | Fast Recovery Epitaxial Diodes                                                                                                                                                                   |

| GTO           | Gate Turn-Off Thyristors                                                                                                                                                                         |

| HEV           | $\mathbf{H}$ ybrid <b>E</b> lectric <b>V</b> ehicles                                                                                                                                             |

| HF            | High Frequency                                                                                                                                                                                   |

| HR            | $\mathbf{H} \text{unidity } \mathbf{R} \text{elative}$                                                                                                                                           |

| IGBT          | Insulated Gate Bipolar Transistor                                                                                                                                                                |

| IOL           | Intermittent $\mathbf{O}$ peration $\mathbf{L}$ ife                                                                                                                                              |

| LTJT          | $\mathbf{Low} \ \mathbf{T} \mathbf{e} \mathbf{m} \mathbf{p} \mathbf{e} \mathbf{t} \mathbf{r} \mathbf{e} \mathbf{h} \mathbf{n} \mathbf{c} \mathbf{a} \mathbf{J} \mathbf{o} \mathbf{n} \mathbf{t}$ |

| mAgic         | Microbond Ag Interconnect                                                                                                                                                                        |

| MOSFET         | $\mathbf{M} \mathrm{etal}~\mathbf{O} \mathrm{xide}~\mathbf{S} \mathrm{emiconductor}~\mathbf{F} \mathrm{ield}~\mathbf{E} \mathrm{ffect}~\mathbf{T} \mathrm{ransistor}$ |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCB            | Print Circuit Board                                                                                                                                                   |

| PCT            | Power Cycling Test                                                                                                                                                    |

| PIC            | Power Integrated Circuit                                                                                                                                              |

| RFI            | $\mathbf{R}$ adio- <b>f</b> requency Interference                                                                                                                     |

| SCR            | Silicon Controlled Rectifier                                                                                                                                          |

| SEM            | $\mathbf{S} \text{canning } \mathbf{E} \text{lectron } \mathbf{M} \text{icroscopy}$                                                                                   |

| TCT            | $\mathbf{T} emperature \ \mathbf{C} ycling \ \mathbf{T} est$                                                                                                          |

| TRIAC          | Triode of Alternating Current                                                                                                                                         |

| $\mathbf{TSM}$ | $\mathbf{Tops}$ ide $\mathbf{M}$ etallization                                                                                                                         |

| TTF            | Time To Failure                                                                                                                                                       |

Dedicated to Chiara and my Dear family

### Chapter 1

# Introduction

This chapter will firstly introduce the power semiconductor devices used in power electronics, considering their evolution along the history and their classification regarding the utilization mode.

Secondly, Power Integrated Circuits (PICs) will be presented in order to describe the semiconductor device integration on a single chip (low and medium power density) and finally, the attention will be focused on Power Modules technology (medium, high and very high power density) representing the subject of this thesis.

#### 1.1 Power Semiconductor Device

A **power semiconductor device** is a solid state semiconductor able to control output parameters, such as high current, voltage or frequency [4]. As a matter of fact, power electronics technology converts electric power from one form to another, employing electronic power devices. It constitutes the heart of modern power electronics apparatus [5].

#### 1.1.1 History

- **1948** Is introduced by William Shockley the first bipolar transistor device with substantial power handling capabilities.

- **1952** Appears the first power semiconductor device. The power diode was introduced by R.N. Hall: it was made of Germanium and it had a voltage capability of 200V and a current rating of 35A.

- 1957 The thyristor appears. It could withstanding very high reverse breakdown voltage and it could carry high current. One of the disadvantage of the thyristor, for switching circuits, is that once it is "latched-on" in the conducting state it cannot be turned off by external control. The thyristor turn-off is passive, i.e., the power must be disconnected from the device.

- **1960** Appears the called Gate Turn-Off Thyristors (GTO), which could be turned off. Unfortunately, these components overcame some limitations of the thyristors because they can be turned on or off with an applied signal [6].

- **1970** With the improvements of the Metal Oxide Semiconductor technology (initially developed to produce integrated circuits), appear the power MOSFETs.

- **1975** The power module is introduced [7]. As a result of the isolated construction this new architecture penetrated the market.

- **1978** International Rectifier introduces a 25A, 400V power MOSFET. This device allows operation at higher frequencies than a bipolar transistor, but it is limited to low voltage applications [8].

- 1980s The Insulated Gate Bipolar Transistor (IGBT) is developed.

- **1990s** IGBT became widely available. This component has the power handling capability of the bipolar transistor, with the advantages of the isolated gate drive of the power MOSFET [1].

- **2000s** New types of large band-gap materials, such as silicon carbide "SiC" and gallium nitride "GaN" [9], became promising for the future generation of devices. SiC material has faster minority carrier lifetime, high carrier mobility and high thermal and electrical conductivities. These properties allow high-voltage and high-power capabilities, low conduction drop, fast switching (for example, high switching frequency), high junction temperature (i.e., up to  $350^{\circ}C$ ) and good radiation hardness.

This material started to be applied on devices, such as diodes, power MOSFETs, thyristors, GTOs, IGBTs, etc. [5].

It is interesting to note that, the evolution on power electronics technology has generally followed the evolution of power semiconductor devices. The improvement of industrial microelectronics has strongly contributed to the knowledge of power device materials, processing, fabrication, packaging, modelling, and simulation [5].

Power devices are almost exclusively based on silicon material and according to their controllability degree can be classified into three groups:

**Uncontrolled** - This group includes diodes. The driving of the diode state, closing (ON) and opening (OFF), depends on the external power circuit to which it is connected. Therefore, these devices do not have any external control terminal.

**Semi-controlled** - Thyristor, Silicon Controlled Rectifier (SCR) and Triode of Alternating Current (TRIAC) belong to this group. In this case start-conduction (OFF to ON) is due not only to its external power circuit, but also to an external control signal applied to one of the terminals of the device, commonly called 'gate'. However, the set blocking (from ON to OFF) is determined by the power circuit itself that only allows an external control start driving.

**Full controlled -** This group includes bipolar transistors Bipolar Junction Transistor (BJT), MOSFET, IGBT and GTO, among others. In this case the set blocking can be controlled also by their driving terminal.

Another possible classification could be made considering the utilization mode, because a power semiconductor device is used as a switch or rectifier in power electronics.

#### 1.1.2 Rectifier Mode

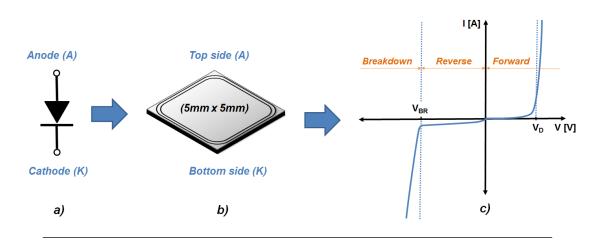

This group is composed by power diodes and it is a two-terminal device (Anode "A" and Cathode "K").

On forward-biased (conduction state), diodes must be able to support an high current intensity with a low drop voltage  $(V_D)$ . On the contrary, on reverse-biased (rectifier state) condition, they must be able to support an high negative voltage drop, with a little leakage current. Furthermore, if the reverse voltage applied is higher than the Break Voltage drop  $(V_{BR})$ , the leakage current increases quickly up to break the device. Summarizing, the blocking voltage capability of a power diode depends on the polarity of the applied voltage [4].

In the figure 1.1, the electric symbol shows the anode and cathode connection, that corresponds to the top and the bottom side of the die. In addition, the graphic of the diode behaviour shows a static characteristic that could be described by three zones:

- Forward condition. High current increases when  $V > V_D$ .

- Reverse condition. Low leakage current while  $-V < V_{BR}$ .

- Breakdown condition High leakage current with high negative voltage drop  $-V > V_{BR}$ .

The characteristic to provide an uncontrolled power rectification, makes them suitable for applications as electroplating, battery charging, welding, power supplies (DC and AC), variable frequency drives, etc [5].

FIGURE 1.1: Diode - (a) Electronic symbol, (b) Die representation and (c) Operating wave form.

#### 1.1.3 Switch Mode

This group is composed by semi-controlled and full controlled semiconductor devices, used as a switch. Power devices behave like a statically operating switch, without moving contacts [4].

The various combination of on-off switches in a matrix form, allows to create a vast amount of power electronic converters. For example, to convert power from AC-to-DC(rectifier), DC - to - DC (chopper), DC - to - AC (inverter), and AC - to - AC at the same (AC controller) or different frequencies (cycloconverter) [5].

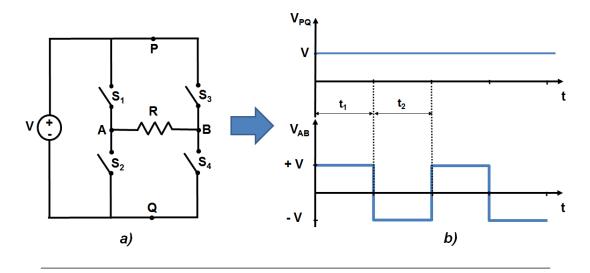

In many converter types, the individual switches are operated in a particular sequence, on one time period, and this sequence is repeated at the switching frequency of the converter. For example: The figure 1.2 shows an electric scheme DC/AC converter, also called "inverter" because an "inverted power conversion" is obtained.

The electric scheme shows four switches  $S_1 - S_4$ , powered by a *DC* voltage source (V) connected to the input terminals P (positive) and Q (negative). The timing of the switches shows that, during  $t = t_1$ ,  $S_1$  and  $S_4$  are kept ON, then the input *DC* voltage appears at the output terminals with terminal A positive  $(V_{AB} = +V = V_{PQ})$ . On the next time interval  $t = t_2$ ,  $S_1$  and  $S_4$  are kept OFF and  $S_2$  and  $S_3$  are kept ON. Therefore, the input *DC* voltage appears at the output terminal A positive terminals with terminal A negative  $(V_{AB} = -V \text{ but } V_{PQ} = +V)$ .

If this sequence of switching is repeated during the time, the DC voltage present on the input and also on the terminals PQ, describes on the output (terminals AB) an ACsquare wave voltage [4].

FIGURE 1.2: Switch Mode - (a) Schematic electric and (b) Wave forms of Inverter configuration.

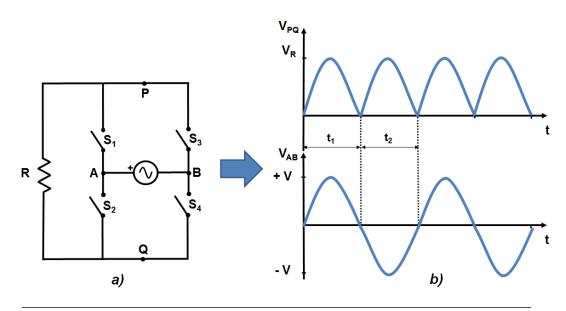

However a rectifier circuit could be obtained (see the figure 1.3) changing the DC voltage with an AC generator, and exchanging it with the load "R" position.

FIGURE 1.3: Rectifier circuit obtained with Switch Mode - (a) Schematic electric and (b) Wave forms.

This circuit is called rectifier because the alternate wave form  $(V_{AB} = AC \text{ current})$  is transformed on only positive cycles  $(V_{PQ})$ .

The switches  $S_1 - S_4$  operate following the same timing explained before. Therefore, the input AC voltage presented in the input terminal "AB" is now as a unidirectional voltage at the output terminals "PQ".

In this case, it should be noted that the current direction through the switches is opposite [4].

The switching mode power conversion is characterized for allowing high efficiency, but switches are not ideal. The non linearity of switches, causes at both sides, harmonics generation (the supply and load sides). In addition, switching losses happen during the turn-on and turn-off state [4].

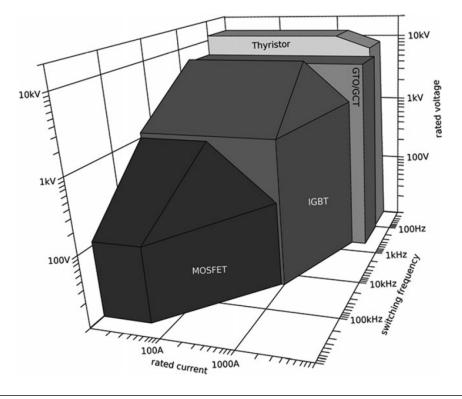

Characteristic of "Semi-controlled" and "Full-controlled" devices, as switching frequency, voltage range or current range, leads to classify the devices on a practical application range. The figure 1.4 illustrates this practical application range of each type of power silicon device in power converters [1].

FIGURE 1.4: Operating rate of "Semi-controlled" and "Full-controlled" devices (Extracted from [1]).

Converters can be used in applications such as AC and DC power supplies or motor drives, heating and lighting controls, static VAR generation, electrochemical processes, active harmonic filtering, etc [5].

#### **1.2** Power Integrated Circuits (PIC)

Due to the interest of the industrialized countries to reducing their greenhouse gas emission and for using energy more efficiently and intelligently [10][11], power integrated circuits (PICs) appeared on the market, offering a combination of control and power electronics monolithically integrated on the same chip [12]. Called also as "smart" power circuits or power ICs, these integrated circuits consist of a level-shifting and drive circuit that translates logic-level input signals from a microprocessor to a voltage and current level, enough to control a power load [5][13][14].

The motivations behind a PIC are reduction in size, cost and improvement in reliability.

On the other hand, the PIC manufacture presents two main problems:

- isolation between high-voltage and low-voltage devices,

- thermal management.

The key feature that differentiates it from other semiconductor technologies is its ability to handle power conversion and to control high voltages and high currents in automobiles, audio equipment and television, heat transfer, home appliances, aircraft, robotics, motors, traction, flat-panel, electroluminescent displays, switching devices, electrostatic printing, and power systems (transmission, distribution, and conditioning of energy) etc. An example of this is an automotive multiplexed bus system with distributed power integrated circuits for control of lights, motors, air conditioning, etc. [14][13].

The power delivered by the PIC into a load can be tens, hundreds, or even thousands of watts; PICs can deliver either high-output current at low supply voltage, low-output current at high supply voltage, or medium-output current at medium supply voltage.

Recently, a large family of PICs that includes power MOSFETs or IGBT smart switches, two-phase step or three-phase brushless DC motor drivers, half-bridge inverter drivers, one-quadrant choppers for DC motor drives, etc. has become available.

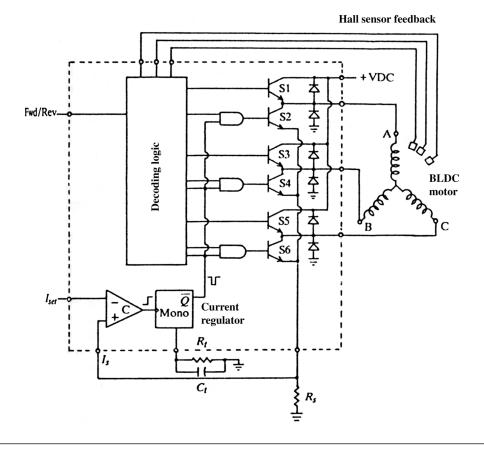

Figure 1.5 shows a monolithic PIC (into the dotted rectangle) for driving a brushless dc motor: the simplified block diagram describes a 40V, 2A PIC that consists of a six-switch power stage, current-regulated Pulse With Modulated (PWM) control of the lower switches, Hall sensor decoding logic and thermal/undervoltage protection features [5].

#### **1.3** Power Modules

Introduced by Semikron<sup>1</sup> in 1975, this new architecture got into the power devices market [7][1].

A **power module** or **power electronic module** is a set of power electronic devices (socalled dies or chips), able to drive high voltage and current, doing a particular function. As a consequence a high power density is manipulated.

The main function of the "module" is to provide a physical containment, id est their

<sup>&</sup>lt;sup>1</sup>For more information http://www.semikron.com/

FIGURE 1.5: PIC application example - Monolithic PIC for brushless dc (BLDC) motor drive [5].

structure, commonly called package, must be able to provide and guarantee cooling, electrical connection and insulation between the internal device and the external circuit.

Comparing this kind of structure with the discrete components, while them are suitable for: lower current applications, low volume applications (no tooling) and looser Electromagnetic interference (EMI) requirements, power modules are suitable for:

- high current application,

- high volume applications,

- high power density requirements,

- unconventional shape requirement.

Furthermore, power modules present multiples advantages as for example:

Form Factor - Modules could be designed to optimize layout,

Power Density - Offer a more compact and easy mounting solution,

Additional Functionality - Shunt, thermistor, capacitor, gate resistor can be integrated,

Lower Risk - Sub-assembly/Assembly have inner cost to be counted.

#### **1.3.1** Applications

The overall power electronics market grew, during the last years, thank to the continuous growth of the technology, allowed power electronic to embrace every day more and more applications.

However, time-to-market differs from application to application as a function of value proposals for cost, specifications, availability, etc. [15].

Multiple circuit configurations or devices can be contained into a single module, from a single power electronic switch (as MOSFET, IGBT, BJT, Thyristor, GTO or JFET) or diode, to multiple semiconductor dies that are connected to form a specific electrical circuit.

Hence, numerous examples that include a single or multiple power modules can be described. The table 1.1, for example, shows an idea about applications and requirements connected to a kind of power module that can be involved.

Thereby, the market requirements of power modules could be summarized as:

- Long lifetime,

- Low thermal impedance,

- High power density,

- Optimized cost,

- Optimized packaging for low internal and external stray inductance,

- Optimized chip technology, high current density,

- Optimized coefficient of thermal expansion (CTE) [16].

Though, the mentioned applications on the table 1.1 covers a wide range of market, there is one sector that concentrates an elevate number of power modules. This is the Automotive application [15].

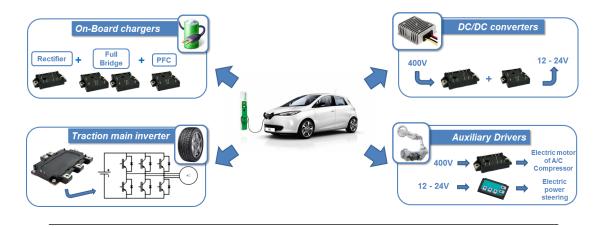

The incursion of power electronics in Electric Vehicles and Hybrid Electric Vehicles (EV/HEV) gave the possibility to control efficiently different parts of the car, reducing the consumes and including also the possibility to consider all electrically controlled (since electric power train to electric "fuel").

The figure 1.6 shows a short description about where power modules are applied in EV/HEV application:

| Application                            | Requirements                                                                                     | Power Module Solution                       |

|----------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------|

| Solar panels and inverters             | Long life<br>High power density<br>Small size<br>Safety approvals                                | Inverter modules                            |

| Energy exploration                     | Long life<br>High temperature<br>operation<br>Safety approvals                                   | Inverter modules                            |

| Power Transmission and<br>Distribution | Long life<br>High voltage capability<br>Custom design                                            | Phase-leg thyristors;<br>SCR/IGBT modules   |

| Intralogistics<br>Lift trucks          | Very robust<br>Long life<br>Transient resistant<br>High power and current<br>density             | IGBT/MOSFET/diode<br>modules                |

| Windmills<br>and large inverters       | Safety approvals<br>High reliability<br>Custom design<br>High power density                      | Phase-leg thyristors;<br>SCR/IGBT modules   |

| Efficient Motor drives                 | High voltage capability<br>High power and current<br>density<br>Transient resistant<br>Long life | Bipolar<br>SCR/IGBT/MOSFET<br>diode modules |

TABLE 1.1: Power modules applications.

FIGURE 1.6: Example of HEV automotive application.

**Auxiliary Inverters** - Former belt-driven devices, as alternator, water pump, aircon, etc. have been electrified and integrated in the power system.

Aircon Compressor Driver - High voltage main batteries are connected to the power module (IGBT + diodes) in order to drive an electric motor (3 - 7kW).

Electric Power Steering - In this case the power module (power MOSFET) is connected to a low voltage auxiliary battery and drives the electric motor of the electric power steering.

**DC/DC converters** - Different voltage levels are required for various electronic components in an EV. The power module (IGBT + diodes) supplies the 12V power system from the high voltage battery (400V).

**On-Board chargers** - With On-board battery charger unit (power MOSFETs/-Diodes), the battery can be charged from a standard power outlet (Plug-in Hybrid). Charging via the main grid calls for design flexibility given the different voltage and current levels.

**Traction main inverter** - Featuring an electric power train, the inverter controls the electric motor. It also captures energy released through regenerative breaking and feeds this back to the battery.

### Chapter 2

# Power Modules

This chapter presents the different power modules packages used and studied in this thesis work (isolated and non isolated), paying a particular attention to describe their critical and improvable points.

#### 2.1 Packages

As explained in Chapter 1, the power module package has an essential role: it is responsible for provides cooling, electrical connection and a correct insulation, between the internal semiconductor devices and the external circuit.

There are many typologies of packages and, the selection of an appropriate one depends on the contained semiconductor device range performance [1].

This work is focused on analysing and comparing three different packages, divided in two big categories: Isolated and Non Isolated. Note that the isolation corresponds to the possibility to electrically isolate the package with external circuit.

However, before starting with the packages description, it is interesting to spend some words about their internal circuit.

#### 2.1.1 Non isolated and isolated - Internal electronic configuration

Both in the isolated and non isolated category, the internal electronic configuration is composed by two diodes connected in common cathode. Internal diodes are classified as "Ultrafast Soft Recovery Diode, 60A FRED<sup>1</sup>" and they are optimized to reduce losses and Radio-frequency/Electromagnetic Interferences (RMI/EMI) in high frequency power conditioning systems. Furthermore, the softness of the recovery eliminates the need for a snubber in most applications. These devices are ideally suited for High Frequency (HF) welding, power converters and other applications, where switching losses are not a significant portion of total losses.

#### Features and benefits:

- 200x200mils die size and 14mils of thickness

- Bondable front side metal and sonderable back side metal

- Ultrafast recovery time

- Low forward voltage drop

- $175^{\circ}C$  operating junction temperature

- Designed and qualified according to  $\text{JEDEC}^{\mathbb{R}}$  JESD 47.

- Reduced RFI and EMI

- Higher frequency operation

- Reduced snubbing

- Reduced parts count.

In the following table 2.1 absolute maximum ratings of diodes are showed:

| Parameter                | $\mathbf{Symbol}$                        | Test condition        | Values  | Units       |

|--------------------------|------------------------------------------|-----------------------|---------|-------------|

| Cathode to anode voltage | $V_R$                                    |                       | 400     | V           |

| Continuous forward       | Incar                                    | $T_C = 127^{\circ}C$  | 60      | A           |

| current                  | $I_{F(AV)}$                              | $I_C = 121^{\circ}$ C | 00      | 71          |

| Single pulse forward     | Ingw                                     | $T_C = 25^{\circ}C$   | 600     | A           |

| current                  | $I_{FSM}$                                | 10 - 20 C             | 000     |             |

| Maximum repetitive       | $I_{FRM}$                                | Square wave,          | 120     | А           |

| forward current          | IF KM                                    | 20kHz                 | 120     |             |

| Operating junction and   | $T_J, T_{JStq}$                          |                       | -55to + | $^{\circ}C$ |

| storage temperatures     | <b>1</b> <i>J</i> , <b>1</b> <i>JStg</i> |                       | 175     | 0           |

TABLE 2.1: Absolute Maximum Raitings of a Ultrafast Soft Recovery Diode, 60A FRED.

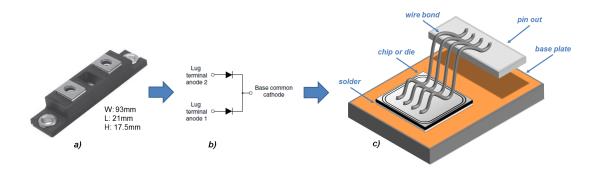

#### 2.1.2 Non Isolated Package

This kind of package is called non isolated, because the metal base plate (that fixes the dies internally) is not electrically isolated and it represents the cathode of diodes.

The figure 2.1 shows the called TO-244 package.

Internally there are 8 diodes (4 for each leg) connected in a parallel common cathode

<sup>&</sup>lt;sup>1</sup>For more information: http://www.vishay.com/

FIGURE 2.1: Non isolated power module - (a) Real device, (b) Internal electronic configuration and (c) Internal composition.

and, as it is possible to observe, this typology of power module is composed by different parts:

Wire bonding - It connects the top of dies among other dies and with the external pin (pin out),

Dies or chips - Electronic components making a particular function.

**Pin out or terminals -** Mechanically stronger than the wire bond, the pin out connects the power module with the external circuit. It is inserted on the box (not soldered on the structure) and it provides a mechanical connection with the external circuit, not soldered.

Solder or die attach - A commonly conductive metal leg (AgSn(3.5)) makes an electrical connection between the bottom of the die and the base plate.

**Base plate** - Composed by Cu metal with external nickel finish, it guarantees the thermal dissipation and the mechanical fixing of the package with the heat sink.

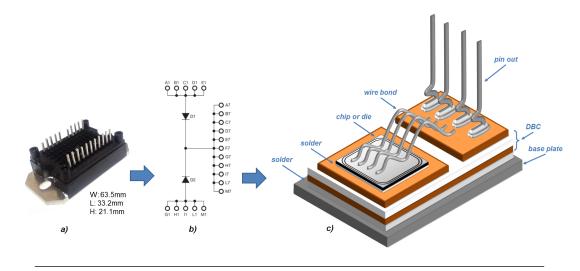

#### 2.1.3 Isolated Packages

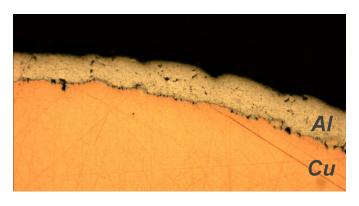

This kind of package is called isolated, because a Direct Bond Copper (DBC) is included inside.

The DBC, produced by Curamik<sup>2</sup>, is composed by two external metal layers and an insulated one between of them. The standard structure includes a copper "Cu" bonded (thickness 0.3mm) to a ceramic substrate such as alumina Al<sub>2</sub>O<sub>3</sub> (thickness 0.38mm).

This material is adapted for high power and temperature applications. In addition, it offers the following advantages:

- great heat conductivity and temperature resistance,

- high heat spreading,

- adjusted Coefficient of Thermal Expansion (CTE) between chip and substrate. The

<sup>&</sup>lt;sup>2</sup>For more information: http://www.curamik.com

mechanical stress on silicon chips mounted directly on the substrate (chip on board) is very low, since the CTE of the ceramic substrate is better matched to the CTE of silicon, compared to substrates using metal or plastic basis.

- High flexibility to obtain various circuits layout. Different electrical configurations can be obtained by chemical etching.

FIGURE 2.2: Isolated power module - (a) Real device, (b) Internal electric scheme and (c) Internal composition.

The figure 2.2 shows the called MTP package.

This kind of package presents the same internal circuit showed on the TO-244 package, but it provides some advantages:

- Ceramic fully insulated package  $(V_{ISOL} = 3500V_{AC})$

- Print Circuit Board (PCB) solderable terminals

- Direct mounting of heatsink

Therefore, looking at the representation of the internal composition in the figure 2.2, and comparing again with the TO-244 package (explained in 2.1), it is possible to observe that MTP package differs by having:

Wire bonding - Bonded between dies and dies-substrate,

**Pin out -** This electrical connection with the external circuit is soldered to the DBC and can be soldered on the external circuit.

**Solder layers -** The metal contact (AgSn(3.5)) is located between die/DBC and DBC/base plate.

**DBC** - Situated between the solder layers, it guarantees the electrical isolation. **Base plate** - Soldered with the DBC.

The last package included in this thesis work is the called ADD-A-PAK (see figure 2.3). This kind of package, isolated package, is a sort of combination of TO-244 and MTP. It combines the external pin out of TO-244 and the electrical isolation of MTP packages.

Furthermore, its principal advantage is the excellent thermal performance obtained by the usage of exposed DBC substrate directly mounting with the heatsink.

FIGURE 2.3: Isolated power module without base plate - (a) Real device, (b) Internal electric scheme and (c) Internal composition.

Finally, in order to conclude about the internal composition of this packages, all of the boxed structures (2.1 and 2.2) are fill in with silicone dielectric gel SYLGARD 527. This kind of gel, produced by Dow Corning<sup>3</sup>, is a bi-component material, with excellent dielectric properties, low viscosity and adapted to industrial production.

It is used to provide long term sealing against moisture and atmospheric contaminants.

#### 2.1.4 Critical and improvable points

Hard conditions on which power modules applications are subjected (modules placed in inaccessible locations and subjected to harsh environments), combined with the increasing power density (from the combination of increased device power levels and reduced packaging), lead to higher junction temperatures and reduced reliability [17][18]. Furthermore, power losses, generated during on-state and blocking state of a device and the additional losses, caused by the transition between these states, are deposited as thermal energy in the chip and must be extracted along the package [3][19].

The study of new materials for packages design in "isolated and non isolated" (chip, interconnections substrates, wire bonding, etc) must take into account the above described hard conditions.

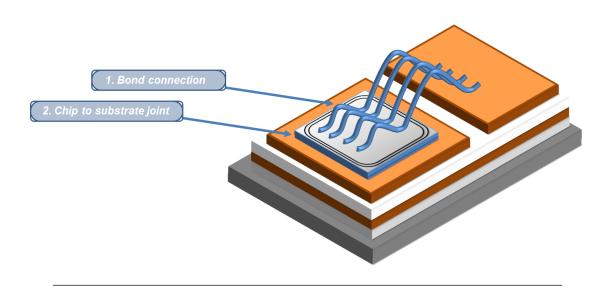

This thesis work will be focused on study the application of new materials, with the aim to improve the interconnections related to the die (see figure 2.4):

#### 1 - Chip to substrate layer

#### 2 - Bond Connection

<sup>&</sup>lt;sup>3</sup>For more information: http://www.dowcorning.com

FIGURE 2.4: Improvable points on an isolated power module.

### Chapter 3

# Thermal Characterization and Reliability

The increasing power density, on which the power module is submitted, put its internal constituent material under stress condition.

As a consequence, if an higher lifetime device is required, a particular attention has to be focused on the thermal, electrical and mechanical properties of the new materials involved.

This chapter will introduce the methods of characterization and the reliability tests that were employed to evaluate the power module lifetime and the impact of the change on bond connection and chip to substrate layer on the power module characteristics.

#### 3.1 Thermal Characterization - Test Method

The purpose of this test is to thermally characterize the power module[19].

Thermal resistance (Rth) is defined as the ratio of temperature rising along a thermal path (die/DBC/base plate, die/DBC or die/base plate) to the heat flowing in that same path, namely, it is a measurement of a temperature difference  $(\Delta T)$  for which an object or material resists to a heat flow.

Therefore, this test can be associated to the heat dissipation capability of one or more materials (as for example a power module).

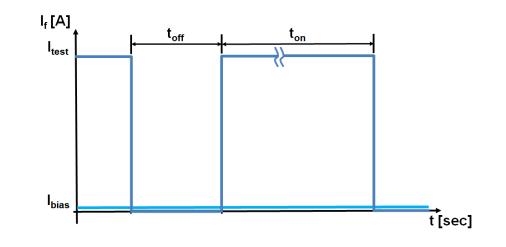

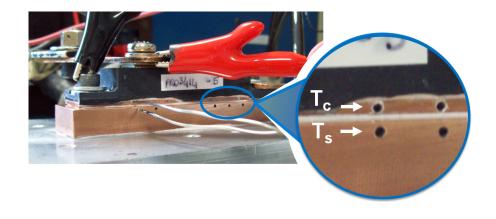

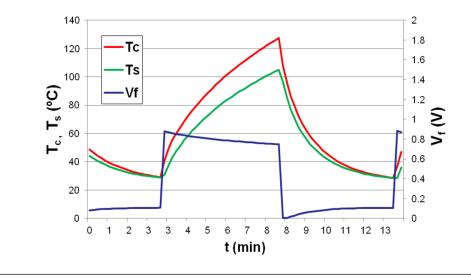

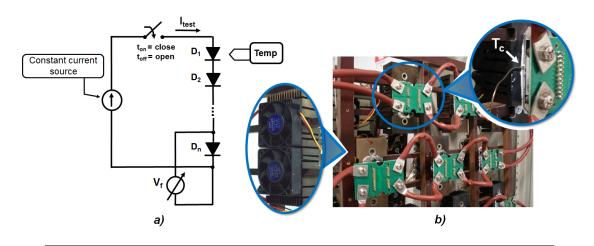

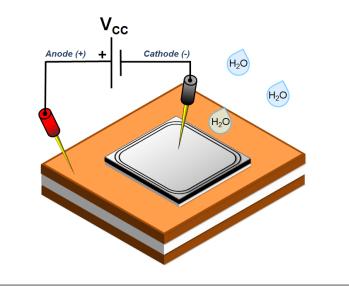

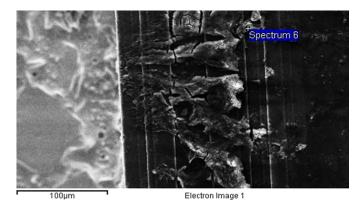

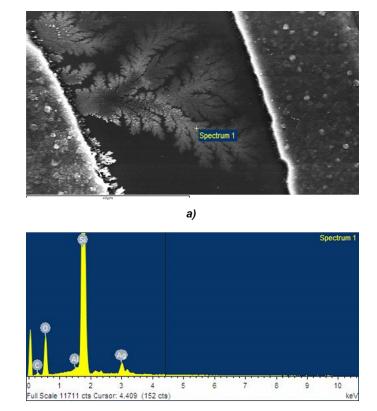

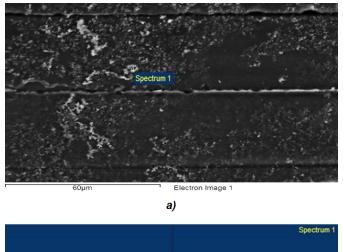

#### Equivalent thermal circuits