Control Theory and Informatics ISSN 2224-5774 (Paper) ISSN 2225-0492 (Online) Vol.4, No.4, 2014

# Switched-Capacitor 2:1 Step-Down Voltage Converter Modulated on 90nm and 45nm

Swati Singh<sup>1\*</sup> Uma Nirmal<sup>2</sup>

- 1. Faculty of Engineering ,Mody University of Science & Technology, Laxmangarh(Sikar), India

- 2. Faculty of Engineering ,Mody University of Science & Technology, Laxmangarh(Sikar), India

- \* E-mail of the corresponding author:singhswati.3334@gmail.com

#### Abstract

DC-DC converters are one of the main component of a power management unit. Their main role is to provide a constant, smooth output voltage to power the electronic devices. Switching mode DC-DC converters are critical building blocks in portable devices such as mobile phones, laptop, etc and hence their efficiency and power are a important issue. This paper describes design techniques to maximize the efficiency of switched-capacitor (SC) DC-DC converters. The measured performance of switched capacitor converter implemented on tanner EDA tool at 45 nm and 90nm CMOS technology with 2V input voltage to support efficiency 94-95% **Keywords:** DC-DC conversion, switched-capacitor, switching converter

#### 1. Introduction

Due to coming of the mobile-commerce generation, various portable electronic equipments have been produced and easily available, including PDA, notebook, cellular phone, digital camera, pager, e-book, etc. Such products emphasize to keep the excellent characteristics as in the following, for examples mobile convenience, integrated communication function, small volume, light weight, and long time high efficiency power supply. In recent years, especially for the last one of these characteristics, the portable communication systems always ask for a new DC-DC power module with more functions, including small volume, light weight, high power density and great efficiency, and good regulation capability, because that is one of the most important key to determine the continuous available time, reliable capability, and life time limit of the portable products. This power module is the type of converter which converts an unregulated dc voltage input and outputs a constant or regulated voltage. The regulators can be mainly classified into linear and switching regulators. All regulators have a power transfer stage and a control circuitry to sense the output voltage and adjust the power transfer stage to maintain the constant output voltage. A DC-DC converter is a device that accepts a DC input voltage and produces a DC output voltage Therefore the use of switched capacitor(SC) DC-DC converter is suggested, because these converter require capacitor-switching technique for developing low-power converters. Since such SC converters do not require any magnetic elements, for examples inductor and transformer, possibility of integrated circuit fabrication is not only pretty promising but also overcoming classical converter limitations on the physical sizes of the magnetic devices. The function of DC-DC converter is to Convert a DC input voltage Vs into a DC output voltage Vo, Regulate the DC output voltage against load and line variations, Reduce the AC voltage ripple on the DC output voltage below the required level, Provide isolation between the input source and the load, Protect the supplied system and the input source from electromagnetic interference.

### 2. 2:1 SWITCHED CAPACITOR CONVERTER

In this section we will analysis the operation of 2:1 switched capacitor DC-DC converter and the loss mechanism.

#### 2.1 Operation of switched capacitor converter

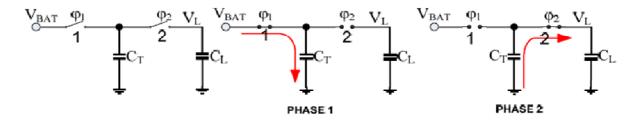

In order to clarify the key loss mechanisms that will set the trade-off between converter efficiency and power density we will begin by examining the basic operation of the SC step-down converter shown in Fig1. Switched-capacitor(SC) DC-DC converters typically operate in two phases  $\phi_1$  and  $\phi_2$ . During phase  $\phi_1$ , the capacitor  $C_T$  is connected between the input node Vi and the output node Vo. The charge which is drawn from Vi though charges this capacitor up and flows towards the load. Now during phase  $\phi_2$ , is connected between Vo and GND, and thus the charge previously stored on the capacitor  $C_T$  is transferred to the output. In practice, SC converters always have some load attached with them. Moreover, switch on-resistance  $R_{on}$  is not negligible. Due to these load and switch on-resistance, output voltage  $V_L$  of the SC converter drops below the no-load output voltage  $V_{NL}$ . The difference between the  $V_{NL}$  and  $V_L$  is known as dropout voltage and is given by  $\Delta V = V_{NL}$ . It has been observed that  $V_L$  is mainly dependent on output current, switching frequency, and the charge transfer capacitor's value. The value of  $V_L$  is important in determining the efficiency related with the SC converter given by

$$\eta = V_L / V_{NL} \tag{1}$$

Figure 1. Basic operation of SC DC-DC Converter

# 2.2 Loss mechanism

Various loss mechanism exist in SC converters due to which power efficiency of SC is greatly suffered. This section analysis the important losses of SC converter.

#### 2.2.1 Conduction loss

The charging and discharging of the flying capacitor  $C_1$  through Req is a lossy operation that results in conduction losses, which are included in the output current analysis. Due to current balance of the flying capacitor, the output current is Iout = 2Iin, and the resulting converter efficiency becomes

$$2V_{out}/V_{in}$$

(2)

n=

equation 2, shows that the efficiency when including conduction losses. In the no-loaded case, i.e.  $I_{out} = 0A$ , the output voltage is half the input voltage[1], however, the output voltage is less than half the input voltage when loaded due to conduction losses. Hence the output voltage specification directly determines the conduction losses.

#### 2.2.2 Switching loss

In SC converters, parasitic capacitances exist from the bottom plate of the charge transfer capacitors to ground. The bottom plate capacitance can be up to 5-20% of the total charge-transfer capacitance and constitute a major role in SC circuits transfer functions. In gate-oxide implementation of capacitors with N-well as a bottom plate , the parasitic arise due to reverse-biased diode capacitance of N-well ,p-substrate junction.

#### 2.2.3 Gate drive Loss

When a transistor is switched on in SC converters, parasitic capacitance associated with the transistor switches get abruptly discharged to zero[2]. Power consumed in this process is given by

$P_{sw} = f_{sw} \Sigma C_{MOS,i} \cdot V_i^2$ (3)

where  $C_{MOS}$  represents any of the MOS transistor capacitance, while  $V_i$  represents the maximum voltage swing across these capacitors. Increasing the width of the transistor is associated with bigger transistor parasitic capacitances and will eventually increases the gate drive loss. On the other hand, bigger transistor width results in smaller  $R_{ON}$ , which will decrease the conduction loss. Hence, there is an optimum width of the transistor at which efficiency is maximum.

# **3. SC CONVERTER CIRCUIT DESIGN**

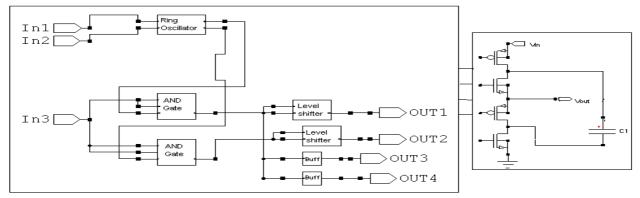

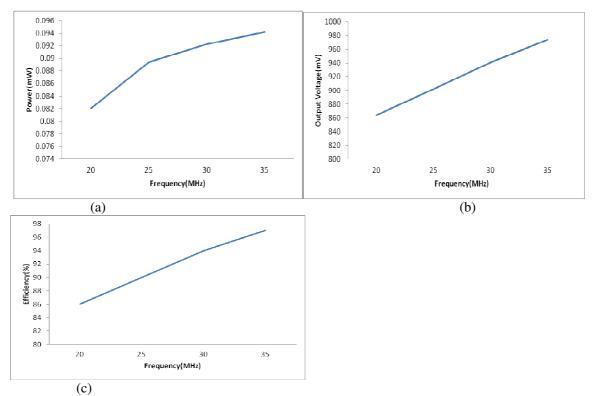

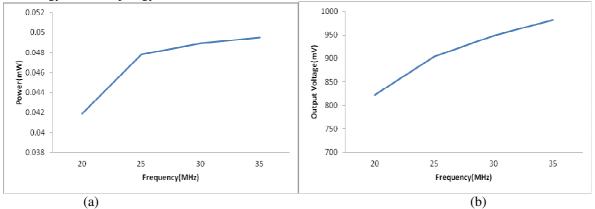

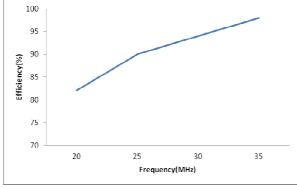

This section discusses the implementation of the 2:1 SC converter integrated in a 45nm and 90nm technology. In this work the demonstration of high efficiency voltage conversion is done by using the circuit shown in fig-2. In 2:1 conversion the output voltage is lower than the input voltage. . In a step-down converter which are intended to generate output voltages near the nominal process voltage, then the breakdown voltage of these switches will most likely to be smaller than the input voltage  $V_{BAT}$ , and therefore appropriate switch driving strategies are needed. Therefore a differential ring oscillator is used to meet the requirement of clock generation. The output of ring oscillator is used to drive two different phases of SC converter topologies. The output of ring oscillator is applied to AND gate with enable. here AND gate is designed because it provides buffering to the clock generator and clock produce with sharper edges, it also provides additional control from outside for enabling/disabling the clock generator .Some transistor in SC stage require different clock voltage to operate . This poses the requirement of level shifter[3] which can shift the voltage level of  $V_{drive}$  to GND. here  $V_{drive}$  is the optimum value of gate to source voltages at which the efficiency is higher. This circuit for both topologies is simulated for current and power dissipation for different values of frequency on different technologies such as 45nm and 90nm. Simulated figures are depicted from fig2 to fig3. Here it is shown that 2:1 topology gives better efficient result on 90nm technology i.e. 95% at 2v supply on 90nm technology and 94% on 45nm technology. Summary of work is shown in table-1.

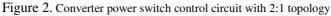

Figure 3. (a)Power v/s frequency (b) Output Voltage V/s Frequency (c)Efficiency v/s Frequency on 45nm technology for 2:1 topology

(c)

Figure 4. (a)Power v/s frequency (b) Output Voltage V/s Frequency (c)Efficiency v/s Frequency on 90nm technology for 2:1 topolog.

| Topology       | 2                | 2:1              |  |  |  |

|----------------|------------------|------------------|--|--|--|

| Process        | 45nm Tanner Tool | 90nm Tanner Tool |  |  |  |

| Input Voltage  | 2v               | 2v               |  |  |  |

| Output Voltage | 0.974v           | 0.982v           |  |  |  |

| Power          | 94.2uW           | 49.5uW           |  |  |  |

| Frequency      | 35MHz            | 35MHz            |  |  |  |

| Efficiency     | 94%              | 95%              |  |  |  |

| Table | 1  | Summary | of | the | 2.1 | Converter |

|-------|----|---------|----|-----|-----|-----------|

| raute | 1. | Summary | 01 | unc | 2.1 | Conventer |

# 4. Comparison and Result

In Table.2, the results presented in this paper are compared to previously published results on SC converters focusing on efficiency. This work is implemented on 90nm and 45nm Technology on Tanner EDA Tool and it gives 95% efficiency at low power for 2:1 topology on 90nm .Therefore 2:1 converter gives better efficient results on 90nm technology at low power.

# 5.Conclusion

In this paper 2:1topology is simulated on 90nm and 45nm technology on Tanner EDA Tool. This work shows the better efficient result on 90nm technology for 2:1 topology when input voltage is 2V at 35MHz frequency which results in 0.98V output voltage, 49.5uW power and 95% efficiency.

| Reference      | [4]      | [5]       | [This work]                | [This work]                |

|----------------|----------|-----------|----------------------------|----------------------------|

| Technology     | 45nm SOI | 90nm BULK | 45nm Tanner EDA<br>Generic | 90nm Tanner EDA<br>Generic |

| Topology       | 2:1      | 2:1       | 2:1                        | 2:1                        |

| Input Voltage  | 2V       | 2.4V      | 2V                         | 2V                         |

| Output Voltage | 0.95V    | 1V        | 0.974V                     | 0.982v                     |

| Power          | 2.6mV    | 1650mW    | 94.2uW                     | 49.5uW                     |

| Frequency      | 100MHz   | N/A       | 35MHz                      | 35MHz                      |

| Efficiency     | 90%      | 69%       | 94%                        | 95%                        |

Table 2. Comparison of the work presented in this paper to previously published work

### References

Y. K. Ramadass and A. P. Chandrakasan, "Voltage scalable switched capacitor DC-DC converter for ultralow-power on-chip applications," in *Proc. of the IEEE Power Electronics Specialists Conference (PESC)*, Orlando, Florida, Jun. 2007, pp. 2353–2359.

Arntzen.B, Maksimovic.D, "Switched Capacitor DC-DC Converters with Resonant Gate Drive,"In IEEE trans,Power Electron,pp.892-902,1998

R.Yokesh K, C.Anantha P, "Voltage Scalable Switched DC-DC Converter For Ultra Low Power on ChipApplication," *IEEE Conf, Power Electronics Specialist*, pp2353-2359, 2009.

Deen, S.M. (1993), "Cooperation Issues in Holonic Manufacturing Systems", *Proceedings of DIISM'93 Conference*, 410-412.

Hanh-Phuc, Seth R, Sanders, Elad Alon, "Design Technique for fully Integrated Switched Capacitor DC-DC Converter," IEEE J.Solid state Circuits, Vol 46,no9,pp.2120-2131,2011

L.Chang,, R.K.Montoye, B.L.Ji, A.J.Weger, K.G.Stawiasz and R.H.Dennard,"A Fully Integrated Switched Capacitor 2:1 Voltage Converter with Regulation capability and 90% Efficiency at 2.3A/mm<sup>2</sup>,"IEEE symp on VLSI Circuits/ Technical Digest of Technical Papers, pp55-56,2010

The IISTE is a pioneer in the Open-Access hosting service and academic event management. The aim of the firm is Accelerating Global Knowledge Sharing.

More information about the firm can be found on the homepage: <u>http://www.iiste.org</u>

# CALL FOR JOURNAL PAPERS

There are more than 30 peer-reviewed academic journals hosted under the hosting platform.

**Prospective authors of journals can find the submission instruction on the following page:** <u>http://www.iiste.org/journals/</u> All the journals articles are available online to the readers all over the world without financial, legal, or technical barriers other than those inseparable from gaining access to the internet itself. Paper version of the journals is also available upon request of readers and authors.

# **MORE RESOURCES**

Book publication information: <u>http://www.iiste.org/book/</u>

Recent conferences: http://www.iiste.org/conference/

# **IISTE Knowledge Sharing Partners**

EBSCO, Index Copernicus, Ulrich's Periodicals Directory, JournalTOCS, PKP Open Archives Harvester, Bielefeld Academic Search Engine, Elektronische Zeitschriftenbibliothek EZB, Open J-Gate, OCLC WorldCat, Universe Digtial Library, NewJour, Google Scholar