## PROCEEDINGS OF THE 11<sup>TH</sup> OVERTURE WORKSHOP

**Electrical and Computer Engineering** Technical Report ECE-TR-17

## DATA SHEET

Title: Proceedings of the 11th Overture Workshop Subtitle: Electrical and Computer Engineering Series title and no.: Technical report ECE-TR-17

Editors: Ken Pierce and Stefan Hallerstede Department of Engineering – Electrical and Computer Engineering, Aarhus University

**Internet version**: The report is available in electronic format (pdf) at the Department of Engineering website http://www.eng.au.dk.

Publisher: Aarhus University© URL: http://www.eng.au.dk

Year of publication: 2013 Pages: 68 Editing completed: November 2013

Abstract: The 11th Overture Workshop was held in Aarhus, Denmark on Wed/Thu 28-29th Au- gust 2013. It was the 11th workshop in the current series focusing on the Vienna De- velopment Method (VDM) and particularly its community-based tools development project, Overture (http://www.overturetool.org/), and related projects such as COMPASS (http://www.compass-research.eu/) and DESTECS (http: //www.destecs.org). Invited talks were given by Yves Ledru and Joe Kiniry. The workshop attracted 25 participants representing 10 nationalities.

The goal of the workshop was to provide a forum to present new ideas, to identify and encourage new collaborative research, and to foster current strands of work towards publication in the mainstream conferences and journals. The Overture initiative held its first workshop at FM'05. Workshops were held subsequently at FM'06, FM'08 and FM'09, FM'11, FM'12 and in between.

Keywords: software engineering and systems

**Please cite as**: Ken Pierce and Stefan Hallerstede (Editors), 2013. Proceedings of the 11th Overture Workshop. Department of Engineering, Aarhus University. Denmark. 68 pp. - Technical report ECE-TR-17

Cover image: Logo, Overture Open Source Community

ISSN: 2245-2087

Reproduction permitted provided the source is explicitly acknowledged

# PROCEEDINGS OF THE 11<sup>TH</sup> OVERTURE WORKSHOP

Ken Pierce and Stefan Hallerstede Aarhus University, Department of Engineering

## Abstract

The 11th Overture Workshop was held in Aarhus, Denmark on Wed/Thu 28–29th August 2013. It was the 11th workshop in the current series focusing on the Vienna Development Method (VDM) and particularly its community-based tools development project, Overture (www.overturetool.org/), and related projects such as COMPASS (www.compass-research.eu/) and DESTECS (www.destecs.org). Invited talks were given by Yves Ledru and Joe Kiniry. The workshop attracted 25 participants representing 10 nationalities.

The goal of the workshop was to provide a forum to present new ideas, to identify and encourage new collaborative research, and to foster current strands of work towards publication in the mainstream conferences and journals. The Overture initiative held its first workshop at FM'05. Workshops were held subsequently at FM'06, FM'08 and FM'09, FM'11, FM'12 and in between.

## Introduction

The 11th Overture Workshop was held in Aarhus, Denmark on Wed/Thu 28–29th August 2013. It was the 11th workshop in the current series focusing on the Vienna Development Method (VDM) and particularly its community-based tools development project, Overture (http://www.overturetool.org/), and related projects such as COMPASS (http://www.compass-research.eu/) and DESTECS (http: //www.destecs.org). Invited talks were given by Yves Ledru and Joe Kiniry. The workshop attracted 25 participants representing 10 nationalities.

The goal of the workshop was to provide a forum to present new ideas, to identify and encourage new collaborative research, and to foster current strands of work towards publication in the mainstream conferences and journals. The Overture initiative held its first workshop at FM'05. Workshops were held subsequently at FM'06, FM'08 and FM'09, FM'11, FM'12 and in between.

The workshop organisers and editors of these proceedings were:

- Ken Pierce (Newcastle University, UK)

- Stefan Hallerstede (Aarhus University, Denmark)

## List of Participants

Ken Pierce Newcastle University, UK.

Martin Mansfield Newcastle University, UK.

John Fitzgerald Newcastle University, UK.

Peter Gorm Larsen Aarhus University, Denmark.

Stefan Hallerstede Aarhus University, Denmark.

Peter Würtz Vinther Jørgensen Aarhus University, Denmark.

Sune Wolff Aarhus University, Denmark.

Kenneth Lausdahl Aarhus University, Denmark.

José Antonio Esparza Isasa Aarhus University, Denmark.

Luis Diogo Couto Aarhus University, Denmark.

Joey Coleman Aarhus University, Denmark.

Martin Peter Christiansen Aarhus University, Denmark.

Jesper Gaarsdahl Aarhus University, Denmark.

Sergi Rotger Griful Aarhus University, Denmark.

Sren Mikkelsen Aarhus University, Denmark.

George Kanakis Aarhus University, Denmark.

Morten Larsen Conpleks Innovation, Denmark.

Nico Plat West Consulting BV, The Netherlands.

Hiroshi Ishikawa Niigata University of International and Information Studies (NUIS), Japan.

Mads von Qualen Terma A/S, Denmark.

Klaus Kristensen Bang & Olufsen, Denmark.

Uwe Schulze University of Bremen, Germany.

Lasse Lorenzen CLC bio, Aarhus, Denmark.

Yves Ledru Laboratoire d'Informatique de Grenoble (LIG), France.

Joe Kiniry Technical University of Denmark (DTU), Denmark.

## **Table of Contents**

| Introduction                                                                            | 3  |

|-----------------------------------------------------------------------------------------|----|

| List of Participants                                                                    | 5  |

| Table of Contents                                                                       | 7  |

| <b>The Overture Approach to VDM Language Evolution</b>                                  | 8  |

| An Architectural Evolution of the Overture Tool                                         | 16 |

| Towards an Overture Code Generator          Peter W. V. Jørgensen and Peter Gorm Larsen | 22 |

| The COMPASS Proof Obligation Generator                                                  | 28 |

| Model Based Testing of VDM Models                                                       | 34 |

| <b>Co-modelling of a Robot Swarm with DESTECS</b>                                       | 42 |

| Modelling Systems of Cyber-Physical Systems                                             | 48 |

| Modelling Different CPU Power States in VDM-RT                                          | 56 |

| Modelling a Smart Grid System-of-Systems using VDM                                      | 63 |

### The Overture Approach to VDM Language Evolution

Nick Battle, Anne Haxthausen, Sako Hiroshi, Peter Jørgensen, Nico Plat, Shin Sahara, and Marcel Verhoef

The Overture Language Board

**Abstract.** The Overture Language Board (LB) has a strategic role in the development of the VDM-10 Languages, VDM-SL, VDM++ and VDM-RT, and deals in particular with Requests for Modifications (RMs) to the language. Such requests come usually from participants in the Overture project. This paper describes how the LB uses a well-defined process with several phases to deal with the RMs, from when they are requested until they are either rejected or accepted and implemented. The paper also gives an overview of language changes that have been accepted and implemented in the period April 2009 – June 2013.

**Keywords:** VDM, formal specification languages, language design, language modification process, The Overture Language Board

#### 1 Introduction

Languages evolve, whether these be natural languages, programming languages or formal specification languages (or any other languages for that matter). Obviously the same holds for what is now known as the VDM-10 family of formal specification languages. New needs arise as a result of new insights, and application of the language in new areas also requires the definition of new language constructs or the revision of previous ones.

VDM "as a language" dates back to 1970, and was called VDL (Vienna Definition Language) at that time. VDL later evolved into languages or dialects such as "Meta-IV" [1] and the "VDM notation" [7] in the late eighties.

The next milestone in the development of VDM was the production of the ISO VDM-SL standard [6,10]. An official ISO standard was put forward, after a rather lengthy effort, coordinated by the BSI (British Standardization Institute), including all aspects of language definition, such as lexis, syntax, and semantics. This was done for the so-called "flat language": there was no concept of modularization (although this was considered at the time), let alone real-time aspects and so forth. Nevertheless the definition of the language was set in stone at that point.

Much of the language evolution was the result of joint European research projects. For example, the Afrodite ESPRIT project, which was undertaken in the early nineties, proposed extensions for object-orientation [8]. The VICE project (VDM In Constrained Environments) introduced a real-time extension [9] and this strand of work continued in the context of the BODERC project [5]. Asynchronous operations and explicit computation and communication architectures were introduced which enable reasoning about

deployment and performance in a distributed setting. This dialect is now commonly referred to as VDM-RT and this work has matured in the DESTECS project [2], where focus was on developing tool support based on a unified structured operational semantics for co-simulation of VDM-RT (discrete event) models with continuous time models specified using bond graphs [4,3].

In 2004, the language was "adopted" by the Overture project, and in the years following this meant that the language was more or less defined by the tools that supported it. In 2009 the Language Board (LB) was introduced consisting of a selection of members from the Overture Community, with the specific task of coordinating changes to the language, and/or clarifying any issues with the language. In 2010, it was adapted to use the term "VDM-10" for the family of languages based on the original VDM-SL.

In its five years of existence the LB has taken a fairly reactive approach in dealing with language changes, meaning that it has not initiated any language changes by itself, but has awaited proposals to be put forward by the community at large. This is due to the fact that the Overture project is an open source project run by volunteers. More fundamental tasks, such as a solid (re)definition of the semantics of the object oriented nature of the language require a major research effort, something which cannot reasonably be expected from the LB considering the current resources.

#### 2 Language Board process

At its start, the LB proposed a community process to deal with "Request for Modifications" (RM) for the language. In principle, an RM may be put forward by anyone (this person is referred to as the "originator"), even individuals outside the Overture Community. The RM has to describe aspects such as motivation for the request (rationale), a precise description, if possible including semantics, and so on. As a first step an "owner" is assigned to an RM. This is an LB member and therefore not necessarily the same person as the one who put the RM forward. The owner is responsible for moving the RM forward through the process of any possible language changes to support the RM. A special issue tracker in the SourceForge environment <sup>1</sup> is used to coordinate and manage all RMs and this environment also provides an audit trail for each RM. Then the following phases and milestones are acknowledged:

- **1. Initial consideration:** The RM is evaluated by the LB. The LB may then request expert opinions from named members, subject to the agreement of the originator. After this the RM may be (1) "rejected" (2) "approved unmodified", or (3) "approved subject to revision". Next steps for (1) and (3) are obvious, in case (2) the next phase is entered, the Discussion phase.

- **2. Discussion:** During the discussion phase, the wider Overture Community is given the opportunity to participate in discussing the RM. The discussion takes places via e-mail, but also at the monthly Overture meetings on Skype. The results of the discussion are taken back to the LB and is input for the next phase: Deliberation.

- **3. Deliberation:** The LB considers the outcome of the discussion by the overall Overture Community in the Deliberation phase. As a result, the RM may be rejected, and

http://sourceforge.net/projects/overture

in that case the process terminates. It can also be the case that the RM is accepted without modification. In that case the next phase, the Execution phase, is entered. Finally it may be the case that the RM is accepted but modifications are required. In that case the RM is returned to the originator asking him to revise it.

4. Execution: Once a language change has been accepted, it must be reflected in the VDM-10 Language Reference Manual (LRM). This is the responsibility of the owner of the RM. The release manager of the Overture toolset is responsible for planning and organizing an update of the toolset reflecting the language change that has been proposed. This activity is coordinated with the LRM update. Once the LRM has been updated and the RM has been implemented in the tools, the Execution phase (and the process) ends. It may be the case that the RM cannot be implemented in the tools. In that case the RM is returned to the LB to make a decision on how to proceed (so far this has never happened).

#### **3** Examples of language change

Over the years several RMs have been dealt with by the LB. In the following subsections we discuss the highlights for only a few of those that are considered of most importance to the language.

#### 3.1 RM #23, Map Patterns

This RM was received in November 2011. VDM includes patterns for matching various aggregate types, like sets, sequences and tuples, but the language did not include support for map patterns. This RM was a proposal to add support for map patterns, following some initial work in VDMTools.<sup>2</sup>. The example below demonstrates the use of the map pattern and returns the value 3:

**let** {1 |-> a, a |-> b} = {1 |-> 2, 2 |-> 3} **in** b

The changes to the grammar are as follows:

pattern = ... map enumeration pattern

| map munion pattern

| ... ;

map enumeration pattern = `{', maplet pattern list, '}'

| `{', `|->', `}' ;

maplet pattern list = maplet pattern, { `, `, maplet pattern } ;

maplet pattern = pattern, `|->', pattern ;

map munion pattern = pattern, `munion', pattern ;

<sup>2</sup> http://www.vdmtools.jp/en/

There was some initial discussion regarding the detail of how a match would work, and under what circumstances a match would fail. The proposal for the map union pattern was changed from using the ++ operator to the munion operator, as this was closer to the intuitive semantics, and the map enumeration pattern was modified to include the empty map as a legal value. The result is a natural extension to the language that significantly simplifies the process of working with map data.

#### 3.2 RM #12, Non-deterministic statements in traces

In June 2010, an RM was submitted to the LB requesting that the language be extended to include a non-deterministic trace statement. The purpose of this is to allow traces to explore the effect of the unpredictable ordering of operation calls in a concurrent environment. The new trace statement is similar to the normal non-deterministic statement, which calls the list of statements defined in a non-deterministic order <sup>3</sup>. Within a trace definition, the new trace concurrent expression now expands to *every possible order* of the trace statements contained within it.

It was agreed that the syntax should be like the normal non-deterministic statement. As an example, the two trace statements below are equivalent:

(Op1(); Op2(); Op3())

(Op1(); Op2(); Op3()) |

(Op1(); Op3(); Op2()) |

(Op2(); Op1(); Op3()) |

(Op2(); Op3(); Op1()) |

(Op3(); Op2(); Op1()) |

(Op3(); Op1(); Op2())

#### 3.3 RM #2, The introduction of the "reverse" sequence operator

In May 2009, an RM was received which requested a change to the sequence reverse processing defined in the language. Before the change, the reverse keyword was available only as part of for loops that iterate over sequences, causing them to iterate in reverse. The RM proposed to introduce a new unary reverse operator, taking a sequence argument and returning the sequence in reverse order. At the same time, the change also proposed removing the reverse keyword from the for loop, since this would be redundant. The affected syntax is as follows:

<sup>&</sup>lt;sup>3</sup> The interpreter actually executes statements in a consistent under-determined order, rather than a non-deterministic order.

The new unary reverse operator is the same precedence and grouping as other unary sequence operators -i.e. precedence 6 in the Evaluator family, with left grouping.

The change is a generalization of the existing semantics, with the advantage that legal specifications under the old grammar are still legal in the new grammar. There is one subtle change in the semantics which could occur, if a specification uses a combination of sequence operators in a for reverse loop, for example for elem in reverse S1^S2. This used to mean the reverse of the entire concatenated list, but under the new grammar this means the concatenation of (reverse S1) and S2. It was considered sufficient that this case should cause a warning to be generated in the tools, "Warning 5013: New reverse syntax affects this statement".

#### 3.4 RM #3, Generalising let-be expressions

This RM was received in May 2009. Before the change, the let be st expression and statement used a simple pattern bind, as did the equivalent trace let be st binding. The change proposed to extend this to include a multiple bind, allowing multiple separate patterns to bind to the same set or type. This avoids having to write nested let expressions, and it is particularly useful in traces, where it is common to want to bind over multiple variables. The new syntax is as follows:

let be expression = 'let', multiple bind, [ 'be', 'st', expression ], 'in', expression ;

The proposal was accepted with little discussion as it is a natural extension, and avoids the need to write nested expressions to achieve the same effect. The change is also backward compatible with existing specifications. The proof obligations generated for the binding are extended in a natural way.

#### 3.5 RM #4, Functions should be implicitly static in VDM++

This RM was received in May 2009. Before the change, the existing implementations of VDM++ would allow functions to be declared as static or non-static, and it was also possible for functions to call operations. A function cannot access instance variables, and therefore does not need a self reference – in effect functions are always static. Similarly, a function should produce no side effects in the state, and so it should not be possible to call an operation from a function. This proposal created considerable debate, much of which overlapped with the issues raised in RMs #13, #14 and #15 regarding the object oriented semantics of VDM++.

At the LB meeting on the 20th September 2009, the following points were agreed: (1) every function is implicitly static; (2) reference to self is not allowed in a function; (3) obj.fn() binding is determined by actual type of obj (polymorphism); (4) fn() binding is determined by the enclosing class and super classes statically; (5) C fn() is still possible, as is obj.Bfn(), to select a function in a hierarchy; (6) we disallow all operation calls in a function definition.

Points 1, 2 and 6 were new at the time, while rest were current functionality. For existing specifications, occurrences of 1, 2 and 6 should generate deprecated warnings. Going forward, violations of these will become type checking errors. Issues remain regarding the object-oriented semantics of VDM++, but enforcing the purity of functions is a step in the right direction.

#### 4 Synchronization with tool development

Although it is the business of the LB to consider language changes, these would be of little value if the tools did not implement them. On the other hand, it is not the business of the LB to control the development and release schedule of the tools – this is a matter for the Overture Core group. Therefore there needs to be clear communication between the LB and the development group, partly to implement the changes when approved, but also to coordinate updates to the LRM (which is owned by the LB) with releases of the tools. In this way the language features described are actually supported at the time of release. Currently, this is coordinated through the Overture core group, who convene for an on-line meeting ten times per year. A release manager is appointed and currently a tool group is established to coordinate tool development at a higher level.

The LB follows the *Overture Community Process*<sup>4</sup>. At any given time, several RMs may be progressing through the process. Towards the end of the process, the Execution phase allows the LB to track the implementation of the change in the tools. This is done informally, between the RM owner and the development group. The RM owner is then responsible for updating the LRM to describe the changes implemented. When the LRM changes have been made, and the tool implementation is complete (or complete enough for beta testing in a release), the LB informs the Release Manager of the availability of the change and the corresponding updates to the LRM. If all goes well with beta testing, the new feature will then be made available in the next release of the tool.

#### 5 Future and conclusions

In this paper we presented the approach that the Overture community has taken in dealing with requests for changes to the VDM-10 family of specification languages. This approach has been a structured one and very much aimed towards making decisions as a community. Central in the approach has been the installation of the "Overture Language Board" (LB), which is responsible for moving language change requests (Requests for modification: RM) forward and providing expert knowledge on the details of the language and advising on the RMs. The LB actively consults the Overture community as

<sup>&</sup>lt;sup>4</sup> http://wiki.overturetool.org/index.php/Community\_Process

part of its decision making. Since the beginning of the existence of the LB it has received a total of 23 RMs, 8 of which are in progress. The paper has described some of them in more detail.

The attitude the LB has taken so far been rather reactive, i.e. waiting for RMs to come in and then deal with them according to the established process. Recently, the language board proposed to extend their scope also to the standard libraries that the Overture tool currently supports. Main motivation for this widened scope is that in the context of language evolution the consistency of (legacy) models do not only rely on the definition of the language itself, but also on the definition and behavior of any support libraries. More fundamental changes, or at least enhanced language definitions need to be made as well. For example, the formal semantics of the object-oriented version of the language needs to be defined, and this at the very least requires further research. This is a certainly an area that the LB wishes to coordinate, however significant further resources are needed to do this which are not currently available to the LB or the Overture community.

**Acknowledgments.** The authors would like to thank all people who have contributed to the evolution of the VDM languages, e.g. by making requests for language modifications (RMs), by discussing RMs, and by implementing RMs.

#### References

- Bjørner, D., Jones, C. (eds.): The Vienna Development Method: The Meta-Language, Lecture Notes in Computer Science, vol. 61. Springer-Verlag (1978)

- Broenink, J.F., Larsen, P.G., Verhoef, M., Kleijn, C., Jovanovic, D., Pierce, K., F., W.: Design Support and Tooling for Dependable Embedded Control Software. In: Proceedings of Serene 2010 International Workshop on Software Engineering for Resilient Systems. pp. 77–82. ACM (April 2010)

- Coleman, J.W., Lausdahl, K., Larsen, P.G.: Semantics for generic co-simulation of heterogenous models (April 2013), Submitted for publication to the Formal Aspects of Computing journal

- Coleman, J.W., Lausdahl, K.G., Larsen, P.G.: D3.4b Co-simulation Semantics. Tech. rep., The DESTECS Project (CNECT-ICT-248134) (December 2012)

- Heemels, M., Muller, G.: Boderc: Model-Based Design of High-tech Systems. Embedded Systems Institute, Den Dolech 2, Eindhoven, The Netherlands, second edn. (March 2007)

- ISO: Information technology Programming languages, their environments and system software interfaces – Vienna Development Method – Specification Language – Part 1: Base language (December 1996)

- Jones, C.B.: Systematic Software Development Using VDM. Prentice-Hall International, Englewood Cliffs, New Jersey, second edn. (1990), iSBN 0-13-880733-7

- Lano, K., Haughton, H. (eds.): Object-oriented Specification Case Studies, chap. 6: Objectoriented Specification in VDM++. Object-oriented Series, Prentice-Hall International (1993)

- Mukherjee, P., Bousquet, F., Delabre, J., Paynter, S., Larsen, P.G.: Exploring Timing Properties Using VDM++ on an Industrial Application. In: Bicarregui, J., Fitzgerald, J. (eds.) Proceedings of the Second VDM Workshop (September 2000), Available at www.vdmportal.org

- Plat, N., Larsen, P.G.: An Overview of the ISO/VDM-SL Standard. Sigplan Notices 27(8), 76–82 (August 1992)

| ID Summary                                                                    | Milestone            | Status    | Milestone Status Tool support         |

|-------------------------------------------------------------------------------|----------------------|-----------|---------------------------------------|

| 1 International character support for Overture identifiers.                   | Completed Closed     | Closed    | yes                                   |

| 2 The introduction of the "reverse" sequence operator.                        | Completed Closed yes | Closed    | yes                                   |

| 3 Generalising let-be expressions.                                            | Completed            | Closed    | yes                                   |

| 4 Functions should be implicitly static.                                      | Completed Closed     | Closed    | yes                                   |

| 5 Scope rules for assignments.                                                | Completed Closed     | Closed    | yes                                   |

| 6 Inheritance of constructors.                                                | Withdrawn Closed     | Closed    | no                                    |

| 7 Adding explicit object reference expressions to VDM++.                      | Withdrawn Closed     | Closed    | ou                                    |

| 8 Need definition of VDM++ operation pre/post functions                       | Withdrawn            | Closed    | no                                    |

| 9 VDM++ object oriented issues.                                               | Rejected             | Closed    | ou                                    |

| 10 Invariant functions for record types                                       | Rejected             | Closed no | no                                    |

| 11 Exception handling in interpreter.                                         | Rejected             | Closed no | no                                    |

| 12 Include the non-deterministic statement inside traces.                     | Completed            | Closed    | Closed yes (Overture only).           |

| 13 Static Initialization.                                                     | Withdrawn Closed     | Closed    | no                                    |

| 14 Object Construction.                                                       | Withdrawn Closed     | Closed    | no                                    |

| 15 Inheritance, Overloading, Overriding and Binding.                          | Withdrawn Closed no  | Closed    | no                                    |

| 16 Expressions in periodic thread definitions.                                | Completed            | Closed    | Completed Closed yes (Overture only). |

| 17 Values in duration / cycles statements.                                    | Completed Closed     | Closed    | yes (Overture only).                  |

| 18 Sporadic thread definitions.                                               | Execution            | Open      | n.a.                                  |

| [19] Extend duration and cycles (allow intervals + probabilities). Discussion |                      | Open      | no                                    |

| 20 Antagonist STOP operation for periodic threads is missing. Execution       |                      | Open      | n.a.                                  |

| 21 More descriptive time expressions.                                         | Rejected             | Closed    | n.a.                                  |

| 22 Append narrow expression.                                                  | Completed            | Closed    | yes                                   |

| 23 Append map pattern.                                                        | Completed Closed     |           | yes                                   |

| 24 Additional print statements in IO library in VDM-RT.                       | Rejected             | Closed no | no                                    |

|                                                                               |                      |           |                                       |

## Appendix: Request for Modifications – Overview and Status

Table 1. Overview and status of all community Requests for Modifications

## An Architectural Evolution of the Overture Tool

Peter W. V. Jørgensen, Kenneth Lausdahl, Peter Gorm Larsen

Department of Engineering, Aarhus University, Finlandsgade 22, 8200 Aarhus N, Denmark

Abstract. The Overture project governs an open source platform providing tools for formal modeling, and thus the success of the project depends on contributions made by members of the community. Source code contributions are often provided as plugins that rely on core elements of the platform such as the VDM Abstract Syntax Tree (AST), the type checker and the interpreter. To support the efficient development of plugins, the most recent changes made to the platform modify the structure of the AST to promote the extendability of the platform. The intent is to make core functionality more easily accessible for outside developers and create an attractive platform to build on. This paper covers some of the important changes recently made to the AST. Using real examples, demonstrations will be given for how these changes can be exploited in order to benefit from and extend the existing platform.

**Keywords:** Overture tool, VDM, abstract syntax tree, tool development, software architecture, plugin development, Eclipse IDE

#### 1 Introduction

The development of the Overture tool started back in 2003 and was primarily carried out by Master's students [13]. At that time the tool was Eclipse [4] based with support for partial checking of the syntax and its static semantics. The syntax tree was stored in XML and did not preserve all the information of the parse tree. This design choice was made to avoid the inefficiency of storing the potentially large tree and traversing the entire structure. Later it was changed to an AST isomorphic to the concrete syntax, composed of hand written nodes [11]. This design was, however, prone to errors due to the manual work of maintaining and extending the tree. As a response to this, Verhoef developed a tool enabling the generation of AST nodes in both Java and VDM. The generated Java nodes were used in Eclipse for developing the tool, while the VDM nodes supported the development of tool extensions using the VDM related validation techniques such as invariant checks. These VDM models would then be transformed into Java code as enabled by VDMTools [3, 6] and then adopted by the Overture platform or a new code generator can be added to Overture directly [8].

While these efforts were ongoing the command-line based VDM interpreter, VDMJ, was being developed [1] and later integrated with the Overture tool in order to establish a common front-end [10]. This resulted in two different internal representations of the AST inside Overture, which is costly to maintain and would have complicated reuse across platform components. Although it was possible to convert the generated AST

into a structure compatible with VDMJ, this architecture has several drawbacks, which opposes the goal of having an extendable platform. For that reason, and to solve these design conflicts, a redesign of the AST architecture was needed.

This paper is structured such that the introduction is followed by Section 2, which provides an overview of the VDMJ based AST architecture used in version one releases of the Overture tool. Then Section 3 covers the new AST architecture used in version two releases, motivated by the above mentioned design conflicts. Afterwards Section 4 demonstrates the new architecture by example using recent development projects. Finally, Section 5 provides suggestions for future platform extensions with the aim of making it a more attractive and sound foundation for developers to build on.

#### 2 The VDMJ based AST architecture

Initially VDMJ was developed independently of the Overture tool. Therefore it has not been a primary goal to extend or integrate VDMJ with the Overture tool in the first place. This is reflected in the implementation, which is characterized by 1) performance being a key quality architectural design driver and 2) a close coupling between core components (e.g. the type checker and the interpreter). Design choices motivated by performance often require architectural decisions to be made, which impact extendability in a negative manner. Thus it is appropriate to say that the performance of VDMJ comes at the cost of extendability.

The AST nodes of VDMJ are hand written and functionality like type checking and interpretation is integrated directly into the tree structure. For example, nodes that can be type checked and evaluated must implement the typeCheck and eval methods, and the same applies to other functionality such as generation of proof obligations. Following this design, tool extensions are likely to require direct modifications to the AST nodes, which may affect other components using the tree. Therefore this design opposes the goal of the Overture tool being a platform for developers to build on.

The feedback from Overture development has motivated a new design that aims for an extendable AST with the possibility of adding custom nodes, and where functionality can be added without affecting other components using the tree. In addition, modifications or extensions to the AST should require minimum effort to avoid tedious and erroneous work. This is desirable for large grammars like that of VDM, as it results in many AST nodes being produced.

#### **3** The new AST architecture

In order to deal with the design conflicts of the VDMJ based AST architecture, the new design introduces three major changes. First, it moves all non-trivial functionality (e.g. type checking and evaluation) out of the nodes. Secondly, nodes are being generated using a tool that takes as input an AST description and produces Java based AST nodes. This tool is inspired by the SableCC [12] parser generator and produces fixed nodes in the sense that they should only be changed via the AST description and regenerated based on that. Finally, the AST structure uses bidirectional node relations so information requiring navigating up or down the tree can be obtained. This is intended

to support the implementation of commonly used Eclipse features such as refactoring, auto-completion and going to a definition. For example, it is possible to find the type definition of a given type in the following manner:

```

type.getAncestor (ATypeDefinition.class)

```

Functionality such as type checking and evaluation resides in visitor classes, which specify the appropriate actions to be taken when nodes of different type are being visited. Thus the type check of each node is specified in a method of appropriate name in the type checker visitor class. As an example, the type check of a "greater than" expression (>) requires that the left and right hand sides are of numeric type. The interpreter is developed using the exact same approach as that of the type checker, and visitors can be implemented by all platform extensions that need access to the AST.

#### 3.1 How to extend the AST

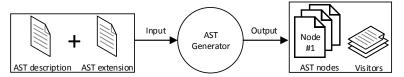

The output of the AST generator reduces the effort needed to experiment with the language. For example, in order to add a new expression to the AST one would first have to update the AST description and process it using the generator as shown in Figure 1. Next the parser, type checker and interpreter must be extended to handle the new expression. For type checking and evaluation this means implementing the appropriate methods in the visitor subclasses.

Fig. 1. The AST generator takes an AST description and outputs the AST and visitor base classes

The AST description supports inheritance, and thus a newly declared (say) numeric expression becomes a child of that node (in the object-oriented sense). To demonstrate this, the AST description snippet below shows the declaration of the two numeric binary expressions "greater than" and "less than". From this the AST generator will produce Java nodes for each of the two expression declarations.

```

#Numeric {-> package='org.overture.ast.expressions'}

= {greater} //e.g. '3 > 2'

... // Other numeric expressions omitted

| {less} //e.g. '2 < 3'</pre>

```

#### 3.2 AST analysis using visitor classes

Like for AST nodes, visitor base classes are generated from the AST description. The most general visitor is designed according to a question-answer principle and serves as a template for various kinds of analyses. It is implemented as a parametrized class

(or generic in Java terms) and takes as input two types representing a question and an answer. The question is passed along to the nodes as they are visited and holds information that is needed in order to answer the question. The answer, on the other hand, specifies the information to be contained in a reply each time nodes are being visited.

The type checker is a visitor structured according to this principle with the parametrized visitor QuestionAnswerAdaptor as base class. For this example, the question holds the information needed to do the type checking, whereas the answer requires each node visited to return the resolved type. This leads to the type checker implementation shown in the code snippet below. Note that it includes the type check of the "greater than" expression mentioned in Section 3.1.

```

public class TypeCheckerExpVisitor

extends QuestionAnswerAdaptor<TypeCheckInfo, PType> {

... // Fields and visitor cases omitted

@Override

public PType caseAGreaterNumericBinaryExp(

AGreaterNumericBinaryExp node,

TypeCheckInfo question)

throws AnalysisException {

... // Type check omitted

}

}

```

The visitor design supports termination of an analysis even if some nodes are left to be visited. This may be appropriate if the visitor has found what it was looking for, e.g. an operation of a certain signature used as entry point in a VDM model. In that case the most convenient way of terminating the visitor is simply to throw an AnalysisException to avoid further tree traversal. In addition, the new AST architecture introduces the notion of an assistant which provides a placeholder for node functionality that does not belong to the visitor itself. As an example, the visibility of a node representing an access specifier can be found using the associated type checker assistant.

#### 4 Applications of the visitor based architecture

The new AST architecture introduced above is already adopted by the Overture platform and used in multiple projects. This means that practical experience has given feedback and influenced the design. However, some projects and plugins developed for the platform make heavy use of the new architectural constructs and deserve to be mentioned.

*The COMPASS project:* In the ongoing EU-FP-7-Frame Programme Project COM-PASS research is made that extends the VDM language [5, 2]. COMPASS builds tools for formal modeling based on the Overture/Eclipse platform to support the COMPASS modeling language (CML), which includes subsets of VDM-SL and VDM++. The COMPASS tool developers at Aarhus University are active contributors to the Overture platform, and thus the project provides continuous feedback for the architecture of the Overture platform. This experience has given rise to a number of suggestions for architectural changes to promote the extendability of the Overture platform, some of which will be addressed in Section 5.

*VDM-UML mapping:* Available in the Overture tool is a plugin [9] that translates between VDM-RT and the Unified Modeling Language (UML) [7]. Aside from accessing the parse tree through the model representation, the plugin performs different kinds of AST analyses in order to enable translation from VDM to UML. This plugin is interesting with respect to the new AST architecture as it makes heavy use of the functionality in the assistant classes to analyse the AST nodes. For example, in UML classes representing threads and processes are "active" and drawn differently from those that are passive. Therefore, the translation checks whether the class contains a thread definition.

#### 5 Future plans

The new AST architecture brings the Overture platform closer to its goal of being an attractive platform to use for developing tools for formal modeling. The changes from the VDMJ based design to the new visitor based architecture have made it easier to benefit from the existing functionality of the platform. This is enabled by the automatic generation of the AST from a description and the visitor based design that moves all non-trivial functionality out of the nodes and places it into visitors and assistants. However, this change in architectural design is only the first step towards the goal and more things remain to be done. In this section some suggestions for future improvements to the design are discussed.

*Integrated Development Environment (IDE) modeling support:* Modern development environments offer auto-completion of e.g. identifiers and operations as these are being typed, and refactoring for making behavior-preserving model transformations that reduce manual intervention. The new AST design is the first step towards implementing such features, which require the possibility to search and manipulate the tree structure. By providing a convenient way of accessing the AST, the intent is to alleviate the effort needed for developing new tool features.

*Generation of Overture components:* Generally speaking, writing parsers is a time consuming task, prone to errors, and it only gets more difficult the larger a language is. In the visitor based design currently adopted, the parser almost remains the same with respect to the VDMJ based architecture, i.e. it is written manually. VDM is a large language, and reducing the effort needed for maintaining and extending on the parser functionality would be a good place to improve on the platform architecture in upcoming releases of the Overture tool. This would potentially lead to a shorter development cycle with respect to extensions and maintenance of core functionality.

*Constructing a core interpreter:* The current interpreter (including the parser and type checker) is structured in a way so it handles all three dialects of the VDM language: Prior to invoking the interpreter the VDM dialect is set and then taken into account

during evaluation. Perhaps a better design would be to identify a core set of language elements that are evaluated in the same way for both the VDM-SL and VDM++ interpreters. This core could then have its own abstract interpreter base class extended by the VDM-SL and VDM++ interpreters, the latter being a superclass of the VDM-RT interpreter. This would allow the VDM-SL and VDM++ interpreters to share the core VDM language subset without depending on each other. This design is illustrated in Figure 2. The challenge is to design this structure so that subtle differences across dialects do not cause similar code to be maintained in the interpreters. For example, the code for instantiating a class during evaluation is almost the same for VDM++ and VDM-RT, except in the latter dialect an object can be deployed to a CPU.

| VDM-SL Int. | VDM Core Int. | VDM-PP Int. | VDM-RT Int. |

|-------------|---------------|-------------|-------------|

|-------------|---------------|-------------|-------------|

Fig. 2. Illustration of the architectural interpreter design based on a common language core

Acknowledgments. The authors would like to thank the reviewers for their valuable feedback on the work presented in this paper. Special thanks to Nick Battle, Augusto Ribeiro, Joey Coleman and Marcel Verhoef for their vital contributions to the development of the Overture platform.

#### References

- 1. Battle, N.: VDMJ User Guide. Tech. rep., Fujitsu Services Ltd., UK (2009)

- Coleman, J.W., Malmos, A.K., Nielsen, C.B., Larsen, P.G.: Evolution of the Overture Tool Platform. In: Proceedings of the 10th Overture Workshop 2012. School of Computing Science, Newcastle University (2012)

- 3. CSK: VDMTools homepage. http://www.vdmtools.jp/en/ (2007)

- 4. Eclipse website (2013), http://www.eclipse.org/

- 5. The COMPASS project website (2013), http://www.compass-research.com/

- Fitzgerald, J., Larsen, P.G., Sahara, S.: VDMTools: Advances in Support for Formal Modeling in VDM. ACM Sigplan Notices 43(2), 3–11 (February 2008)

- Fowler, M., Scott, K.: UML Distilled: A Brief Guide to the Standard Object Modeling Language. Addison-Wesley (2003)

- 8. Jørgensen, P.W., Larsen, P.G.: Towards an Overture Code Generator. In: Submitted to the Overture 2013 workshop (August 2013)

- Lausdahl, K., Lintrup, H.K.A., Larsen, P.G.: Connecting UML and VDM++ with Open Tool Support. In: Cavalcanti, A., Dams, D.R. (eds.) Proceedings of the 2nd World Congress on Formal Methods. Lecture Notes in Computer Science, vol. 5850, pp. 563–578. Springer-Verlag, Berlin, Heidelberg (November 2009), http://dx.doi.org/10.1007/978-3-642-05089-3\_36, ISBN 978-3-642-05088-6

- Møller, D.H., Thillermann, C.R.P.: Using Eclipse for Exploring an Integration Architecture for VDM. Master's thesis, Aarhus University/Engineering College of Aarhus (June 2009)

- Nielsen, J.P., Hansen, J.K.: Development of an Overture/VDM++ Tool Set for Eclipse. Master's thesis, Technical University of Denmark, Informatics and Mathematical Modelling (August 2005), iMM-THESIS-2005-58

- 12. SableCC website (2013), http://www.sablecc.org/

- van der Spek, P.: The Overture Project: Designing an Open Source Tool Set. Master's thesis, Delf University of Technology (August 2004)

## **Towards an Overture Code Generator**

Peter W. V. Jørgensen and Peter Gorm Larsen

Department of Engineering, Aarhus University, Finlandsgade 22, 8200 Aarhus N, Denmark

**Abstract.** When one spends time on producing a formal model using a notation such as VDM, the insight one gains should make it worth the time spent on producing this model. One possible way to improve the value of the model is to use it for automatic generation of the implementation in a programming language. In this paper we describe work in progress targeting such a code generation feature for the Overture platform.

Keywords: VDM, Java, code generation

#### 1 Introduction

The intent of spending a significant amount of time on producing, validating and verifying a high quality formal model is to gain an improved understanding of the system under construction and its solution. Having invested that time it is desirable to automatically generate the implementation from this model in order to reduce the effort needed for transitioning to the implementation phase. Automation tools such as code generators may be helpful for this task.

In this paper we demonstrate our initial attempt to produce a VDM to Java code generator for the Overture platform inspired by the earlier work of VDMTools [4]. The intent of this paper is to enable the reader to get a first impression of the general principles used in this new attempt to produce code generation support for VDM models.

When considering the use of code generators for production code one also needs to be aware of what this means with respect to the possible abstraction levels that are appropriate to apply to a formal model. For example, a type checker for a computer language could be written as a model that simply yields true or false depending upon the static correctness of the input it takes. However, from a practical perspective the model will be of low value since the user of the computer language would like error messages indicating where problems occur so they can be fixed. Thus, code generation can be a cost-effective approach but one needs to be aware of the consequences of applying the different abstraction mechanisms.

This paper starts with an overview of related contributions that have inspired our work in Section 2. Afterwards Section 3 describes the architecture of the code generator. This is followed by a small case study we use for generating code in Section 4. Finally, Section 5 ends the paper with an indication of the future work planned so far.

#### 2 Related work

For VDMTools a code generation feature was produced already in the nineties for both C++ and Java [2]. Towards the end of the nineties support was also produced for the

concurrency parts of VDM++ [6]. However, the target for most of this work has been prototype code generation, rather than targeting final production code.

Much later a first attempt to produce a code generator inside the Overture project was made [5]. However, with this solution it was not possible to extract type information from the Abstract Syntax Tree (AST). As a consequence the code generator produced at that time never got to a stage where it was working for anything but trivial examples.

#### **3** Code generator architecture

All version one releases of the Overture tool rely on the performance efficient architecture of the VDMJ interpreter [1]. However, from version two releases onwards this has changed into a *visitor* based architecture, which intends to provide a more convenient way of extending the Overture platform through simple access to the information in the (decorated) AST [3]. This change has been imposed to make it easier for community users to contribute with additional platform extensions.

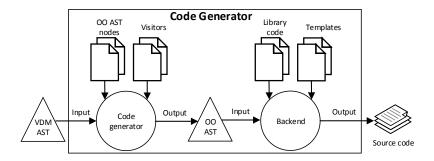

The code generator for the Overture platform presented in this paper uses visitors for traversing the AST describing the VDM model the code generator takes as input. Several visitors deal with *VDM nodes* of certain types (expressions, definitions etc.). Together these visitors construct a new intermediate AST based on nodes reflecting concepts present in most Object-Oriented (OO) programming languages (construction of objects, class definitions etc.). Subsequently these trees are referred to as *OO ASTs* consisting of *OO nodes*.

The OO AST serves two primary purposes: First, it provides a way to gradually deal with the complexity of generating code from a VDM model as the OO AST does not include details specific to a programming language. Secondly, it intends to make code generation for multiple OO languages easier through configuration of the *backend* that generates the code based on the OO AST. The backend can be configured with *templates* and *library code* all specific to a programming language and which completely determine the code generated from the VDM model. The templates<sup>1</sup> consist of scripts describing how OO nodes are mapped into a programming language based on the information stored in the OO AST. In addition, the backend makes use of library code that implement equivalent VDM functionality that is not easily expressed in a programming language (e.g. Java code handling concatenation of sequences). A complete overview of the code generator architecture is shown in Fig. 1.

#### 4 Case study

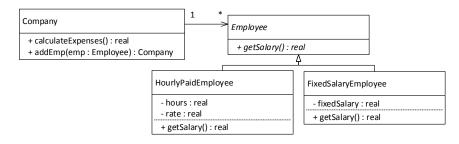

To illustrate the current state of the code generator this section generates code from a small VDM model representing a system for handling company salary expenses. We use this particular model as it includes many of the VDM constructs currently supported by the code generator. The VDM model is shown in the UML class diagram in Fig. 2 which only shows public operations to keep the diagram simple.

<sup>&</sup>lt;sup>1</sup> The templates are targeting the Apache Velocity template engine: http://velocity.apache.org/

Fig. 1. An architectural overview of the code generator

Fig. 2. The Company Salary Expenses System illustrated using a class diagram

In Fig. 2 the abstract Employee class is parent of FixedSalaryEmployee and HourlyPaidEmployee, which both provide the appropriate implementations of the getSalary operation declared in Employee. The code generator generates the inheritance hierarchy from the VDM model one would expect, since inheritance exists both in VDM and Java. However, one should be aware that the current version of the code generator does not allow code to be generated from a VDM model that uses multiple inheritance. Instead the modeller must refine the model to avoid use of such VDM constructs before applying the code generator to it.

A Company is associated with a number of employees that together constitute the company salary expenses. The calculateExpenses operation in the Company class performs this calculation by iterating through the collection of company employees while summing the salaries. In the VDM model a sequence is used for associating employees with a company. The calculation of the company expenses is done in VDM by traversing this sequence recursively in the start\_calc function as shown in Listing 1.1.

Listing 1.1. The VDM specification of the Company class

```

class Company

instance variables

private employees : seq of Employee;

operations

```

```

-- Constructor omitted...

public calculateExpenses: () ==> real

calculateExpenses() ==

return start_calc(employees);

public addEmp : Employee ==> Company

addEmp (emp) ==

(

employees := employees ^ [emp];

return self;

);

functions

private start_calc: seq of Employee -> real

start_calc(emps) ==

if emps = [] then 0

else (hd emps).getSalary() + start_calc(tl emps);

end Company

```

Due to space limitation we focus on the code generated from the Company class. For mapping of sequences we use library code based on standard functionality of subclasses realizing the java.util.List interface and Java generics, the last being similar to C++ templates. The code generated from the Company class is shown in listing 1.2 from which we see that the hd emps and tl emps expressions map into the Java calls emps.get(0) and emps.subList(1, emps.size()), respectively. In addition, we see that concatenation of sequences in Java is handled in the Util class using the seqConc method.

```

import java.util.List;

public class Company {

private List<Employee> employees;

// Constructor omitted...

public double calculateExpenses() {

return start_calc(employees);

1

public Company addEmp(Employee emp) {

employees = Utils.seqConc(employees, Utils.seq(emp));

return this;

}

private double start_calc(List<Employee> emps) {

if (emps.isEmpty()) {return 0;}

else {

return emps.get(0).getSalary()

+ start_calc(emps.subList(1, emps.size()));

}

}

```

#### 5 Future plans

Although the code generator present in this paper is early work, it has raised several questions that would be interesting to address as part of the future work. We discuss some of these in the sub-sections below.

#### 5.1 Code generation for a distributed hardware architecture

The initial intent of the code generator was to address the research challenge of generating code for a distributed hardware architecture. Modelling of a distributed system executing on CPUs communicating through buses is already supported by the VDM-RT extension. However, extensions to the Overture tool will be needed in order to allow the model to be annotated with additional information before generating code for a distributed hardware architecture. Such an annotation could be the specification of the communication protocol used between different CPUs (TCP/IP, UDP etc.).

#### 5.2 Mapping of union types

Mapping of union types into a programming language that does not support this construct is considered one of the difficult challenges of generating code from a VDM model. One possibility is to include no support for union types, but this is impractical as they easily appear in a VDM model without the modeller being aware of this. Expressions similar to the two examples shown in Listing 1.3 will be likely to appear in a VDM model. Here the if expression and the sequence expression have types **seq1 of char** | **nat1** and **seq1 of** (FixedSalaryEmployee | HourlyPaidEmployee), respectively.

Listing 1.3. Two examples of VDM expressions that involve union types

| I    | Has type seql of (char) / natl                                |

|------|---------------------------------------------------------------|

| if t | true then "one" else 2                                        |

| I    | Has type seq1 of (FixedSalaryEmployee   HourlyPaidEmployee)   |

| [nev | <pre>w FixedSalaryEmployee(), new HourlyPaidEmployee()]</pre> |

If the sequence expression in Listing 1.3 is generated to Java and assigned to a variable what should the type of that variable be? This mapping is not trivial because no construct similar to union types is supported by the language. One approach is to find a common denominator such as the Object class which acts as a parent of every class in Java. The advantage of this approach is its simplicity, but it is likely to lead to a lot of cast operations in the produced code since the type of an expression must be narrowed down before members can be accessed. This makes the code harder to read and maintain. Therefore, this future work item suggests investigating and comparing different approaches to mapping of union types into a OO language that does not support this construct.

#### 5.3 Investigating the extensibility of the code generator

The architecture of the code generator intends to keep a clear separation between OO concepts and the actual programming language that the code generator generates code for. The initial work has been focusing on Java, but it would be interesting to use the OO AST with templates based on other programming languages. Since different OO programming languages have subtle differences in (for example) constructor semantics challenges are envisaged here. Ideally, extending the code generator with another programming language should be done by changing the templates that specify how the different constructs of the OO AST are mapped to the concrete programming language. However, it may be difficult to perform a mapping if the information needed for a particular programming language is not easily accessible from the OO AST, i.e. it requires extensive analysis of the tree. The OO AST could provide additional information that would make it easier for languages that require (say) declaration before use to easily get hold of the forward declarations needed for the generated code to compile.

**Acknowledgments** The authors would like to thank the reviewers for their valuable feedback on the work presented in this paper. Special thanks to Nick Battle and Kenneth Lausdahl for vital input and interesting discussions on the code generator architecture.

#### References

- 1. Battle, N.: VDMJ User Guide. Tech. rep., Fujitsu Services Ltd., UK (2009)

- 2. Group, T.V.T.: The VDM++ to Java Code Generator. Tech. rep., CSK Systems (January 2008), http://www.vdmtools.jp/en/

- Jørgensen, P.W., Lausdahl, K., Larsen, P.G.: An Architectural Evolution of the Overture Tool. In: Submitted to the Overture 2013 workshop (August 2013)

- Larsen, P.G., Battle, N., Ferreira, M., Fitzgerald, J., Lausdahl, K., Verhoef, M.: The Overture Initiative – Integrating Tools for VDM. SIGSOFT Softw. Eng. Notes 35(1), 1–6 (January 2010), http://doi.acm.org/10.1145/1668862.1668864

- 5. Maimaiti, M.: Towards Development of Overture/VDM++ to Java Code Generator. Master's thesis, Aarhus University, Department of Computer Science (May 2011)

- Oppitz, O.: Concurrency Extensions for the VDM++ to Java Code Generator of the IFAD VDM++ Toolbox. Master's thesis, TU Graz, Austria (April 1999)

## The COMPASS Proof Obligation Generator: A test case of Overture Extensibility

Luis Diogo Couto<sup>1</sup> and Richard Payne<sup>2</sup>

<sup>1</sup> Aarhus University lcouto@iha.dk <sup>2</sup> Newcastle University richard.payne@ncl.ac.uk

**Abstract.** Proof obligation generation is used as a compliment to type checking for the verification of consistency of VDM specifications. The Overture toolset includes a Proof Obligation Generator (POG). Overture is designed to be a highly extensible platform. CML, a new language designed for modelling systems of systems is based in part on VDM. The CML tools are themselves built on Overture. We evaluate the extensibility and potential for reuse of Overture by reporting our experiences in developing a POG for CML as an extension of the Overture POG. During this process, we alter the existing Overture POG visitors in order to make them more extensible and reusable.

#### **1** Introduction

Type checking is statically undecidable in VDM [1]. VDM specifications can be generally divided into 3 sets: on the one end we have correct or "good" specifications; on the other end we have incorrect or "bad" specifications; and between these two ends, we have undecidable specifications.

The VDM type checker can handle the first 2 sets on its own (it accepts correct specifications and rejects incorrect ones). Specifications from these 2 sets will not have any associated proof obligations. But for the third set, the undecidable specifications, we need the assistance of a Proof Obligation Generator (POG).

The POG therefore picks up where the type checker leaves off and generates a series of proof obligations related to the elements that make the specification undecidable. Discharging these obligations helps prove the internal consistency and correctness of the specification.

The Overture platform, an open source tool for VDM, has a POG for VDM as part of its toolset, although there is no support yet for discharging proof obligations [9].

The COMPASS project seeks to develop tools and practices for modelling Systems of Systems (SoS) [4], including the COMPASS Modelling Language (CML) and a supporting toolset built on top of Overture [3]. Part of the COMPASS toolset will include a POG for CML, developed as an extension of the Overture one.

In this paper, we consider the extensibility of the Overture POG and discuss the issues in the reuse of the Overture toolset. In Section 2, we provide a brief introduction to CML, Section 3 describes the CML POG, we discuss the extensibility of the Overture POG and issues for future development effort in Section 4. Counclusions are drawn in Section 5.

#### 2 The COMPASS Modelling Language

The CML is the first language to be designed specifically for the modelling and analysis of SoS [10]. It is based on the languages VDM [6], CSP [7] and Circus [11]. A CML model comprises a collection of types, functions, channels and processes. Each process encapsulates a state and operations written in VDM and interacts with the environment via synchronous communications in CSP. A semantic model for CML using UTP [8] is in development as part of the COMPASS project [2].

As CML and the COMPASS tool platform are based upon VDM and Overture, the Abstract Syntax Tree (AST) generated by the COMPASS parser is extended from the Overture AST. The ASTCreator tool, a part of the Overture platform, is used to automatically generate ASTs for VDM dialects, which is extended to support CML. This reuse allows us to directly reuse elements of the Overture platform, including the type checker, interpreter and POG.

Being partly based upon VDM, the CML POG will generate those VDM Proof Obligation (PO)s generated by the Overture platform. As such, we aim to reuse and extend the Overture POG.

#### 3 The COMPASS Proof Obligation Generator

#### 3.1 Structure

The COMPASS POG is built on two sets of classes: visitors [5] and proof obligations. This structure was inherited from the existing Overture POG.

The ProofObligation class and its various subclasses are responsible for holding proof obligation data. Each different type of proof obligation has its own subclass (for example NonZeroObligation is a class for representing proof obligations that an expression must evaluate to something other than zero). There are also a related set of classes for storing data related to the proof obligation context. For example, the PO-FunctionContextDefinition stores the various syntactic elements of a function required for function-related proof obligations.

The other set of classes are the visitors. They are responsible for traversing the CML AST and generating the various proof obligations. Whereas the proof obligation classes can be thought of as holding the data, the visitor classes implement the behavior of the POG. Unlike the proof obligation classes, whose type hierarchy is dictated by the proof obligations we want to generate, the visitor hierarchy reflects the CML ast. We have 4 kinds of visitors, each responsible for a subset of AST nodes (POGProcessVisitor is responsible for traversing processes, etc.). At runtime we need an instance of each visitor type and we also need to move between them and so every visitor has a pointer to its parent visitor.

#### 3.2 Behavior

The COMPASS POG is built as a series of visitors. The overall behaviour is relatively simple. The main visitor (ProofObligationGenerator) initializes the various sub-visitors and applies them to the AST. Whenever one of the sub-visitors encounters a node it cannot handle (e.g. the process visitor encounters an expression) it will pass the node up to the main Visitor who will then re-apply the correct sub-visitor.

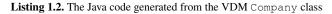

This behavior is shown in the SysML sequence diagram in Figure 1.

Fig. 1: Sequence diagram representing COMPASS POG visit

#### 3.3 Reuse

Our main goal for reuse was to be able to directly utilise the Overture POG to generate all the Proof Obligations from VDM constructs directly. Because of this, the overall structure and behavior of the COMPASS POG are heavily influenced by the Overture POG. The entire visitor style of passing AST nodes between the various is lifted from Overture.

However, rather then simply passing a node up to their root, CML visitors must pass the node up to the Overture visitors. For example, the CML expression visitor must handle new CML expressions and then call the Overture expression visitor to handle the VDM expressions. There are two main issues with this approach.

The first issue is that there is no way to immediately identify a node as being from Overture or CML without using instanceof checks in a manually implemented decision method. One must use the default cases of visitors to work around this limitation. We can set up a for default case for CML nodes and another default case for all nodes (including the extended ones). This of course limits our ability to handle default cases. It would be good if we had 3 default cases available: extended, non-extended and all nodes. This limitation seems to be in the AST itself and not the Overture POG

The second issue we encountered was with the Overture POG visitors. When we pass a node to the Overture visitors, we are no longer able to control what happens. The AST goes under control of the Overture visitors and that is never relinquished. Their default cases are to call the root Overture visitor and its default case is to simply return null. The issue of course comes when you have both VDM and non-VDM nodes in a branch of the AST, which happens quite often. When the AST is passed to Overture, its visitors will not know how to handle the VDM nodes. Of course, this means that at best our POG will be unable to produce the proof obligations for these hybrid trees and at worst, it will die (this will be the most frequent outcome).

To handle this second issue, we had to alter the existing Overture POG to enable its visitors to release the AST back to COMPASS. We introduce the notion of a main visitor. The main visitor is the one that is called on most (any non-parent) calls of the apply() method. Previously these calls were of form node.apply(this). Now they become node.apply(mainVisitor). This main visitor becomes a parameter in the Overture visitors. To preserve compatibility with existing Overture plugins, we rename the altered visitors to ParamVisitor and create new subclasses of these parametrized visitors with the old visitor names. In these cases, the visitor receives a reference to itself as the main visitor parameter.

When the Overture visitors are used by COMPASS the COMPASS visitor is set as the main visitor parameter. This means that every apply() method will return the AST to COMPASS. Now, all decisions belong to COMPASS. The Overture visitor will simply unpack the node, generate any relevant proof obligations and apply the COMPASS visitor to any sub-nodes. In effect, the Overture visitor is called for the use of only one method at a time.

#### 4 Discussion

The current version of the COMPASS POG generates the majority of VDM POs as generated in Overture. This is due to the reuse of the Overture Expression visitor, the ability to reuse the majority of the Overture declaration and definition visitors (apart from the Operation syntactic elements which differ in CML), and the reuse of ProofObligation and POContext classes. As mentioned above, this to reuse these elements required some effort. Whilst this reuse has been useful and reduced the amount of effort to generate VDM-related POs, there are two main dimensions in which the reuse is insufficient for a CML POG.

- We shall need to address the CSP syntactic elements of CML and the resultant POs not covered in VDM. The CML visitors currently have placeholders for most of the process and action CML language elements, influenced by the Overture visitors. Further language development effort is required to define the POs resulting from CML, not present in VDM.

- The current format of storing POs is adequate when their use is limited to printing to the screen. However, as the POs will be used by other analysis tools, storing POs

as strings is not appropriate. This is due to the fact that storing POs in this way allows only one form of PO representation, limiting the use the toolset can make from the generated POs. To address this issue, the PO representation format will be reimplemented in the form of its own AST, which will be an extended subset of the existing CML expression nodes. This new PO format will be composed of one PO expression (the assertion to be proved) and a set of PO expressions holding the context information. Work on this new format is underway, beginning with its implementation in Overture.

When tackling these issues, we should consider how much effort should be made in making changes in the Overture POG (which can be reused in the COMPASS tool platform) and how much is COMPASS-specific. Effort placed in the former case may slow down development of the COMPASS POG, however this will aid in future Overture reuse. However, we must be careful not to add complexity to Overture where it is not necessary for VDM. Our initial thought would be to make COMPASS-specific POG changes for the first issue above, and make changes in the Overture for the second issue.

The COMPASS toolset proposes the incorporation of several analysis tools as plugins to reason over properties of a CML model. The POG, therefore, is a clear source of such properties and thus the proof obligations generated must be made available to the analysis plugins and the analysis results must be related to the PO in the COMPASS toolset. Different plugins will need the proof obligation in different syntaxes and the new AST format will help with that. We can simply develop new visitors that traverse the PO AST and generate the relevant syntax. A clear example of this need for extensibility is the use of the proof assistant Isabelle<sup>3</sup>. To be of use, the proof obligations must be made available in Isabelle compatible syntax, refer to the relevant part of the CML model, and be associated with the result of any proof generated in Isabelle. The connection between proof obligations and their respective Isabelle proofs, particularly across multiple versions of a model is a problem currently under study.

#### 5 Conclusion

We have presented a POG for CML, developed as an extension of the Overture POG. In developing, we have gained insight into the current extensibility and potential for reuse of Overture.

Overall, reuse is definitely possible and is quite powerful. However, it is not a particularly easy task. There were several issues with extending the Overture POG and were it not for existing familiarity with Overture, the task would have been extremely complicated.

We also benefited greatly from being able to alter existing Overture code. The visitor context swaps (particularly, return going from Overture back to COMPASS) were very challenging and without changes to the existing code, it would have been impossible to implement the COMPASS POG with proper reuse. It is clear to us that more work must be done to improve the extensibility of Overture.

<sup>&</sup>lt;sup>3</sup> http://isabelle.in.tum.de

It is also worth mentioning that the development of these extended versions of Overture plugins can be quite challenging. It will be interesting to see how the combination of all Overture and COMPASS plugins turns out.

#### Acknowledgements

The authors wish to thank Peter Gorm Larsen and Joey Coleman for reviews on the manuscript. Nick Battle implemented the original Overture POG and is currently working on the AST version. His work is greatly appreciated. Simon Foster is developing the Isabelle plugin for COMPASS and his ideas on the format for proof obligations have been a great help.

The work presented here is supported by the EU Framework 7 Integrated Project "Comprehensive Modelling for Advanced Systems of Systems" (COMPASS, Grant Agreement 287829). For more information see http://www.compass-research.eu.

#### References

- Hans Bruun, Flemming Damm, and Bo Stig Hansen. An Approach to the Static Semantics of VDM-SL. In VDM '91: Formal Software Development Methods, pages 220–253. VDM Europe, Springer-Verlag, October 1991.

- Jeremy Bryans, Andy Galloway, and Jim Woodcock. CML definition 1. Technical report, COMPASS Deliverable, D23.2, September 2012.

- 3. Joey W. Coleman, Anders Kaels Malmos, Peter Gorm Larsen, Jan Peleska, Ralph Hains, Zoe Andrews, Richard Payne, Simon Foster, Alvaro Miyazawa, Cristiano Bertolini, and André Didier. COMPASS Tool Vision for a System of Systems Collaborative Development Environment. In *Proceedings of the 7th International Conference on System of System Engineering, IEEE SoSE 2012*, volume 6 of *IEEE Systems Journal*, pages 451–456, July 2012.

- Comprehensive Modelling for Advanced Systems of Systems, 2011. http://www.compassresearch.eu/.

- R.Johnson E.Gamma, R.Helm and J.Vlissides. *Design Patterns. Elements of Reusable Object-Oriented Software*. Addison-Wesley Professional Computing Series. Addison-Wesley Publishing Company, 1995.

- John Fitzgerald, Peter Gorm Larsen, Paul Mukherjee, Nico Plat, and Marcel Verhoef. Validated Designs for Object-oriented Systems. Springer, New York, 2005.

- Tony Hoare. Communication Sequential Processes. Prentice-Hall International, Englewood Cliffs, New Jersey 07632, 1985.

- 8. Tony Hoare and Hi Jifeng. Unifying Theories of Programming. Prentice Hall, April 1998.

- Peter Gorm Larsen, Nick Battle, Miguel Ferreira, John Fitzgerald, Kenneth Lausdahl, and Marcel Verhoef. The Overture Initiative – Integrating Tools for VDM. ACM Software Engineering Notes, 35(1), January 2010.

- J. Woodcock, A. Cavalcanti, J. Fitzgerald, P. Larsen, A. Miyazawa, and S. Perry. Features of CML: a Formal Modelling Language for Systems of Systems. In *Proceedings of the 7th International Conference on System of System Engineering*, volume 6 of *IEEE Systems Journal*. IEEE, July 2012.

- Jim Woodcock and Ana Cavalcanti. The semantics of Circus. In Proceedings of the 2nd International Conference of B and Z Users on Formal Specification and Development in Z and B, ZB '02, pages 184–203, London, UK, UK, 2002. Springer-Verlag.

## Model Based Testing of VDM Models

Uwe Schulze\*