# Simulation Techniques

Anders Gammelgaard

December 1991

## Summary

In the papers surveyed in this thesis a number of simulation techniques are presented together with their applications to several examples. The papers improve upon existing techniques and introduce new techniques.

The improvement of existing techniques is motivated in programming methodology: It is demonstrated that existing techniques often introduce a double proof burden whereas the improved techniques alleviate such a burden. One application is to ensure delay insensitivity in a class of self-timed circuits.

A major part of the thesis is concerned with the deduction and use of two simulation techniques to prove the correctness of translations from subsets of occam-2 to transputer code.

The first technique is based on weak bisimulation. It is argued that Milner's notion of observation equivalence must be modified to cope with nondeterminism and silent divergence as found in occam-2. In the resulting technique a stronger, but asymmetric, simulation condition must be proved and an additional index to the simulation relation must be shown to decrease at certain computation steps. An application of the technique to a sequential subset of occam-2 is successful but results in a large proof.

The second technique drastically reduces the size of the proof in the first technique. It marks a major departure from traditional simulation ideas; instead of simulating single transitions, only conveniently long sequences of transitions are simulated. This idea turns out to remove the previous need for indexing the simulation relation and gives more natural proofs.

Parallelism presents a slight problem to the second technique. Three different proofs for the parallel construct are consequently carried out. The first two build on generalizations of the technique to parallel processes; of these generalizations the second employs a new notion of truly concurrent executions. The third uses a more abstract "external" semantics and the fact that this semantics is compositional in the parallel construct.

## Dansk resumé

Nærværende licentiatafhandling er en sammenfatning af nedenstående publikationer, der alle omhandler udvikling og brug af simuleringsteknikker.

- I A. Gammelgaard. Reuse of invariants in proofs of implementation. DAIMI PB-360, Aarhus Universitet, 1991.

- II A. Gammelgaard. Implementation Conditions for Delay Insensitive Circuits. Proc. PARLE 1989, LNCS 365, Vol. 1, pp. 341–355.

- III A. Gammelgaard og F. Nielson. Verification of a compiling specification. DAIMI IR-105, Aarhus Universitet, 1991.

- IV A. Gammelgaard. Constructing simulations chunk by chunk. DAIMI IR-106, Aarhus Universitet, 1991.

- V Kapitel tre og kapitel fire af en kommende monografi dokumenteret i [19]:

A. Gammelgaard, H. H. Løvengreen (ed.), C. Ø. Rump og J. F. Søgaard-Andersen. Volume 4: Base System Verification, ProCoS teknisk rapport, ID/DTH HHL 4/1, Danmarks Tekniske Højskole, 1991.

Simuleringsteknikker har været kendt længe inden for teoretisk datalogi. Teknikkerne kan bruges til at bevise, at et program opfylder en specifikation. Teknikkerne bygger på en operationel forståelse af både programmer og specifikationer: Den grundlæggende idé er, at hvert skridt i et program modsvares af nul, et, eller flere skridt i specifikationen. Såfremt dette krav, samt eventuelle ekstra krav, er opfyldt, vil programmet opfylde specifikationen.

I *I* benyttes en simuleringsteknik til at vise sikkerhedsegenskaber for implementerende programmer. Først vises en sikkerhedsegenskab for en specifikation af det konkrete program, og derefter vises kravene i simuleringsteknikken at være overholdt; de ønskede egenskaber fås derpå ved nedarvning fra specifikation til implementation. Det påvises at eksisterende bevisteknikker, i den konkrete anvendelse, ofte fører til dobbelte bevisbyrder; den nedarvede egenskab må genbevises som en del af simuleringsbeviset. Derefter vises det, hvordan en eksisterende teknik kan modificeres, så den dobbelte bevisbyrde fjernes.

I *II* anvendes den modificerede teknik til at vise hastighedsuafhængighed i en speciel type elektroniske kredse. I stedet for at vise hastighedsuafhængighed direkte, i en model med ledninger, vises det, ved hjælp af den modificerede teknik, at en række implementations-betingelser, i en model uden ledninger, er tilstrækkelige. Disse betingelser udtrykker at kredsen er opbygget af firefase logik.

Publikationerne III, IV og V behandler alle anvendelsen af simuleringsteknikker på et specielt problem: Korrekthed af oversættelser. De betragtede oversættelser går fra forskellige delmængder af programmeringssproget occam-2 til abstrakte versioner af assemblerkode for transputere.

I *III* tages der udgangspunkt i Milners svage bisimulation. Der argumenteres for, at en serie af modifikationer er nødvendige for at opnå en teknik, der kan bruges på den valgte delmængde af **occam**-2. Vigtigst er svækkelsen af kravet om en symmetrisk relation begrundet i behandlingen af non-determinisme og tilføjelsen af et indeks til simuleringsrelationen, der gør det muligt at sikre, at intern divergens simuleres af intern divergens.

Korrekthedsbeviset i afhandling *III* viser sig at være uforholdsmæssigt stort. I *IV* føres størrelsen delvis tilbage til det faktum, at opbygningen af en simulerende occam-beregning sker ved at sammenstykke delberegninger i occam, der svarer til enkeltskridt på transputeren. Derfor foreslås en ny teknik, hvor kun længere bidder af transputerberegninger simuleres i occam. Den resulterende teknik giver væsentlig kortere korrekthedsbeviser for sekventielle programmer i occam.

Parallelisme kan ikke behandles direkte med den nye teknik; problemet er, at det er vanskeligt naturligt at opsplitte en flettet udførsel af et parallelt program i bidder, således at hver enkelt bid kun indeholder skridt fra en enkelt af de parallelle processer. I afhandling IV foreslås der to generaliseringer af teknikken.

I den første generalisering udnævnes et enkelt skridt i hver bid til at være et "principal" skridt . En **occam**-simulering opbygges atter ved at sammen-

stykke occam-delberegninger svarende til enkeltskridt på transputeren, men nu vil kun principale skridt blive simuleret af ikke-tomme sekvenser af skridt. I stedet for at relatere globale konfigurationer relateres projektioner af konfigurationer på enkeltprocesser i systemet. For at sikre at hvert skridt resulterer i en konfiguration for hvilken alle projektioner kan relateres, er det nødvendigt at indicere hver relation med en tæller, der måler afstanden til næste principale skridt.

Den anden generalisering af teknikken er mere radikal. I stedet for at ændre grundideen i teknikken ændres den underliggende model for beregning. Den sædvanlige semantik for parallelle processer baseret på fletningen af udførsler af enkeltprocesser erstattes således af begrebet en ikke-flettet udførsel. En sådan udførsel er basalt set en graf og ikke en linær sekvens. Med ikkeflettede udføersler kan bidder af udførsler af enkeltprocesser direkte bruges til at finde bidder (delgrafer) af udførsler af parallelle programmer, og den nye teknik er derfor relativt let at generalisere.

I *IV* tages en anden tilgangsvinkel til behandlingen af parallelisme. I stedet for at prøve at generalisere simuleringsteknikken vises det, at korrekthed af oversættelsen på sekventielle processer er tilstrækkelig: Hvis hver process i et program af parallelle processer implementeres korrekt, så vil den parallelle sammensætning af implementerende processer være en korrekt implementation af programmet. Rækkevidden af dette resultat illustreres også af de øvrige bidrag til [19], hvor det benyttes til at vise korrektheden af kerner, der samarbejder om at afvikle transputerkode.

# Acknowledgements

My first thanks must go to Flemming Nielson without whose patient advice, encouragement, and administrative work this thesis would have been much poorer if it had been finished at all; his constructive criticism to drafts of my papers has helped me a lot. Also many thanks to Erik Meineche Schmidt for the many improvements he suggested and for the inspiring talks which I had with him in the early stages of the project.

I have participated in several incentive ProCoS meetings. Especially the cooperation with Hans Henrik Løvengreen, Camilla Rump, and Jørgen Søgaard-Andersen has been stimulating.

Uffe Engberg is thanked for his personal support and for the many interesting discussions we have had through the years that we have been roommates.

Lastly my thanks go to Jørgen Staunstrup who introduced me to delay insensitive circuits and who had the gift of cheering me up—even via e-mail—when a felt down.

The work reported here was supported by a scholarship from Aarhus University and by the ESPRIT BRA project no. 3104: Provably Correct Systems.

# Contents

| 1        | Intr                                                        | oduction                                      | 1  |

|----------|-------------------------------------------------------------|-----------------------------------------------|----|

|          | 1.1                                                         | Transition systems                            | 3  |

|          | 1.2                                                         | Open and closed systems                       | 5  |

| <b>2</b> | A simulation technique for inheritance of safety properties |                                               |    |

|          | 2.1                                                         | Basic technique                               | 7  |

|          | 2.2                                                         | Extensions                                    | 9  |

|          | 2.3                                                         | An application to delay insensitive circuits  | 12 |

| 3        | A s                                                         | imulation technique for compiling correctness | 13 |

|          | 3.1                                                         | Definition of correctness                     | 14 |

|          | 3.2                                                         | Towards an internal correctness predicate     | 15 |

|          | 3.3                                                         | The correctness proof                         | 18 |

| 4        | Chu                                                         | ink by chunk simulation                       | 21 |

|          | 4.1                                                         | In search for a better technique              | 22 |

|          | 4.2                                                         | The correctness proof                         | 26 |

|          | 4.3                                                         | External semantics                            | 27 |

|          | 4.4                                                         | Treatment of parallelism                      | 29 |

| <b>5</b> | An                 | algebraic approach to parallelism                        | 34       |

|----------|--------------------|----------------------------------------------------------|----------|

|          | 5.1                | The idea                                                 | 35       |

|          | 5.2                | Treatment of alternations                                | 36       |

|          | 5.3                | Redundant information in the external semantics $\ldots$ | 38       |

|          | 5.4                | Limitations and difficulties                             | 39       |

|          |                    |                                                          |          |

|          |                    |                                                          |          |

| 6        | Disc               | cussion                                                  | 41       |

| 6        | <b>Disc</b><br>6.1 | cussion<br>Summary of results                            |          |

| 6        | 2.00               |                                                          | 41       |

| 6        | 6.1                | Summary of results                                       | 41<br>43 |

# Chapter 1

# Introduction

This thesis consists of the present survey and the five papers below.

- A. Gammelgaard. Reuse of invariants in proofs of implementation.

DAIMI PB-360, Aarhus University, 1991.

- A. Gammelgaard. Implementation Conditions for Delay Insensitive Circuits.

*Proc. PARLE 1989*, LNCS 365, Vol. 1, pp. 341–355.

- III A. Gammelgaard and F. Nielson. Verification of a compiling specification.

DAIMI IR-105, Aarhus University, 1991.

- IV A. Gammelgaard. Constructing simulations chunk by chunk. DAIMI IR-106, Aarhus University, 1991.

- V Chapters three and four of a forthcoming monograph documented in [19]:

A. Gammelgaard, H. H. Løvengreen (ed.), C. Ø. Rump, and

J. F. Søgaard-Andersen.

Volume 4: Base System Verification, ProCoS technical report ID/DTH HHL 411, 1991.

The thesis is about simulation techniques. Simulation techniques are used to establish that one program correctly implements another program or a specification. Such techniques are an important tool in the construction of correct computing systems. The papers introduce various simulation techniques and demonstrate how they can be applied at different stages in the development of correct computing systems.

Computing systems are often described at different levels of abstraction. A high-level description may abstract away many architecture dependent details and may thus be easier to reason about than the corresponding lowlevel description where these details are present. This observation is often exploited to split up a correctness proof into a series of smaller subproofs: First an abstract description of the program is given as a program in a high level programming language; this program is either proven to meet some specification in logic or is taken to be a specification in itself. Then the program is refined through a series of steps ending with a description right down at the hardware level. For each successive pair of descriptions one has to carry out a proof that the more concrete description correctly implements the more abstract description. If all these proofs can be successfully carried out, then it has been proven that the most concrete description of the computing system satisfies the original specification.

There are different views at the meaning of the phrase "description D' implements description D". Here we shall follow a linear time view [32, 50]. In this view D' implements D if it is possible, for each execution of D', to find a simulating execution of D [1, 22, 28, 31, 38, 59]". A simulation technique is a proof technique which reduces the obligation of finding simulations in D for executions of D' to simpler conditions relating individual transitions in D and D'.

A number of simulation techniques have been proposed already [1, 22, 28, 31, 38, 48, 59]. This thesis modifies some of the known techniques, presents new techniques, and gives a number of examples of their application. Furthermore results are presented which ensure that double work in some of the techniques can be avoided.

The concept of an implementation arises naturally at several places in the

<sup>&</sup>lt;sup>1</sup>Descriptions are constructed such that they define non-empty sets of executions. Consequently the trivial implementation having no executions is not feasible.

development of computing systems. Starting from a specification we can identify (at least) the following steps.

- 1. The initial design of the program is written in some high level programming language. Transformations to the program are then made within the language in order to cope with more and more implementation specific details.

- 2. The final program is subsequently translated into machine code by a compiler.

- 3. The machine code is interpreted by the hardware of the machine.

In all these steps it is necessary to prove that the lower level description implements the higher level description. In the latter two steps we are really interested in making *one* proof for a class of programs instead of making individual proofs for each program.

The paper I presents a technique along with a number of examples of its use for the first of the above steps. The paper II uses the same technique in the third step to deal with a specific problem in hardware built of self-timed four phase logic. Finally III, IV, and V present and apply two different techniques for dealing with the second of the above steps. The techniques used in IV and V are the same except for the treatment of parallelism.

Section 2 surveys the technique in I and describes its use on hardware verification in II. Section 3 describes the technique from III and its application to compiling verification. Section 4 describes how the technique of III can be modified into the technique of IV and furthermore demonstrates how the new technique can be applied to parallel languages. In Section 5 the algebraic approach to parallelism from V is described. Finally Section 6 surveys the relevant literature and points out directions for future research.

### **1.1** Transition systems

Simulation techniques to deal with concurrency is a main thread through the entire thesis. The first concern in all the papers consequently is to model concurrent programs. Numerous models have been suggested in the literature. In this thesis we will focus on models based on transition systems.

We consider two types of communication. In [I] and [II] communication is performed through shared variables; in [III], [IV], and [V] communication is through channels. To deal with the latter form of communication we will, as usual, introduce transition labels, either of form ch : v where ch is a channel and v is a communicated value, or of form  $\tau$  where  $\tau$  indicates an internal (silent) step in a system. No such labelling is needed in order to deal with communication through shared variables. Thus we end up with two different types of transition systems, labelled and unlabelled.

Besides a set of configurations (or states) and a transition relation, transition systems often include various other components [8, 49, 51]. Here we will only include a set of initial states. By requiring this set to be non-empty it is ensured that the behaviour of a transition system will be non-trivial.

An unlabelled transition system S is a triple  $(C, Init, \rightarrow)$  where

- C is a set of configurations (or states);

- $Init \subseteq C$  is a non-empty set of initial configurations (states);

- $\rightarrow \subseteq C \times C$  is the transition relation.

A labelled transition system S is a 4-tuple  $(C, Init, L, \rightarrow)$  where

- C is a set of configurations (or states);

- $Init \subseteq C$  is a non-empty set of initial configurations (states);

- L is a set of labels;

- $\rightarrow \subseteq C \times L \times C$  is the relation of labelled transitions.

An execution of an unlabelled transition system is a finite or infinite sequence of configurations such that the first configuration belongs to *Init* and such that adjacent configurations belong to  $\rightarrow$ . An execution of a labelled transition system is likewise defined except that the label of the mediating transition has to be inserted between each pair of adjecent configurations.

## **1.2** Open and closed systems

When modelling concurrent systems another distinction than the labelledunlabelled one can be made—the distinction between open and closed systems.

An open system is a system with an interface to some external environment. Values are communicated forth and back over this interface. In an unlabelled transition system such communications are usually modelled by picking out some part of the configuration (the shared interface variables) and letting this part be under the control of both the system and its environment (e.g. [1]). In a labelled transition system communications with the environment are usually modelled by selecting some of the labels as being input/output labels (e.g. [28, 31, 38]). The environment then communicates with the system by executing transitions with input/output labels in cooperation with the system.

A closed system is a system which does not communicate with any external agent. Such systems explicitly describe both the program in question and its environment (see e.g. [8] and [47]). In transition systems describing such systems there is no partitioning of neither the individual configurations nor the transition labels to reflect the distinction between the program and its environment. When specifying and constructing such a system the designer instead has to be fully aware of the actions which the program can control and those which it cannot control.

In open systems one can compare two systems at their respective interfaces to the environment. Executions of each system give rise to observations at the interface<sup>2</sup>. If the two systems have the same interface—i.e. the same interface variables or the same input/output labels—, then observations at the two systems' interfaces become simple to compare; as indicated earlier we say that a concrete system implements an abstract system if all observations at the concrete system's interface are also possible observations at the abstract system's interface. The notion of one system implementing another system can thus be expressed by an external criterion relating the two systems at their interface.

<sup>&</sup>lt;sup>2</sup>These observations need not merely be projected executions; in [IV] and [V] they also contain information about refused interactions.

In closed systems the situation is rather different because of the lack of interfaces at which two systems can be compared. Here it is up to the designer to decide what the important properties of a system are and how to reformulate them for the implementation. Since there is no interface to the environment, the designer has to suggest some interpretation or some relation which shows how to interpret properties of the high level as properties of the low level. On the other hand this enables the designer to refine interfaces of a program: Since there is no formal notion of an interface to the environment in closed systems, the designer is free to substitute certain interface variables or interface communications with others as long as he is able to reformulate and retain the import ant properties of thy system; he is not bound to show that all observations at a predefined interface at the higher level.

In both [I] and [II] we consider closed systems with communicatio between parallel processes via shared variables. In [III] [IV], and [V] we consider open systems with communication through channels. The lack of papers combining closed systems with channel communication or open systems with communication through shared variables is purely coincidental. We believe that there is nothing which prevents such combinations of concurrency models from being exploited.

# Chapter 2

# A simulation technique for inheritance of safety properties

The first simulation technique is developed in [I] and builds on ideas of Lamport [33, 34, 35]. In this overview we only describe a simple version of the technique.

The technique is used to reduce the effort needed to prove that each state in executions of some low level description of a program satisfy some property. Such properties belong to the category of safety properties [2]. The reduction is obtained by treating the low level description as an implementation of some high level description.

### 2.1 Basic technique

We need some notation. Given an unlabelled transition system  $S = (C, Init, \rightarrow)$ , let the set of reachable states *Reach* be the minimal set such that

- 1. *Init*  $\subseteq$  *Reach*;

- 2. if  $c \in Reach$  and  $(c, c') \in \rightarrow$ , then  $c' \in Reach$ .

The importance of this definition is that all states occurring in executions of S will belong to *Reach*. So to prove properties of these states we only need

to prove properties of states in *Reach*.

To demonstrate that a system has a property we must express this property as a set  $P \subseteq C$  and we must prove  $Reach \subseteq P$ . For instance the system could describe an algorithm for achieving mutual exclusion between some number of processes; the property P would then consist of all states in which at most one process is in its critical section. We say that P is *safe* in S whenever  $Reach \subseteq P$ .

Traditionally, to prove that a P is safe in S, one finds a property  $Inv \subseteq C$ and proves

- 1. Init  $\subseteq$  Inv;

- 2. if  $c \in Inv$  and  $(c, c') \in \rightarrow$ , then  $c' \in Inv$ ;

- 3.  $Inv \subseteq P$ .

The first two conditions obviously ensure  $Reach \subseteq Inv$  and the third condition then gives  $Reach \subseteq P$ . The property Inv is called an *invariant* whenever it satisfies 1 and 2.

For systems describing simple algorithms the invariant Inv can often be chosen to be equal to the property P. For systems describing more complicated algorithms the invariant has to be strengthened such that Inv becomes a proper subset of P and a proper superset of *Reach*.

In concrete systems containing a lot of architecture dependent details invariants can be difficult to find and to work with. In a realisation of the mutual exclusion algorithm, for example, it could be necessary to implement some shared data structure by a whole set of low level data-structures; the invariant then has to describe how manipulations change the lower level data-structures along with the high level properties which enforce mutual exclusion. This mixture of high and low level properties may make the invariant difficult to work with and consequently it may be difficult to establish that P is safe in S by these methods.

We want instead to prove P safe in S in two steps; first we prove it safe for an abstract description of the system; and next we prove that the concrete system can be treated as an implementation of the abstract system. This will enable us to inherit P from the abstract to the concrete level. So assume that we are given two transition systems  $S_1 = (C_1, Init_1, \rightarrow_1)$ and  $S_2 = (C_2, Init_2, \rightarrow_2)$  which describe closed systems and for which  $S_1$  is supposed to be an implementation of  $S_2$ . Since  $S_1$  and  $S_2$  describe closed systems we do not have a priori interfaces at which the systems can be compared. Instead we have to explicitly relate the states of the two systems. This must be done by defining a map  $\alpha : C_1 \rightarrow C_2$ . This map should be thought of as abstracting away the implementation specific details in  $S_1$ .

The next thing we must do is to prove that transitions in  $S_1$  are simulated by transitions in  $S_2$ . This is not always quite possible, however, because the more refined data structures of  $S_1$  may require more operations than the corresponding high level data structures of  $S_2$ . Consequently we also allow  $S_1$  transitions to be simulated by transitions which simply repeat the configuration (called *stuttering* transitions in [1, 33, 35].)

Given two transition systems  $S_1$  and  $S_2$  and a map  $\alpha : C_1 \to C_2$  the simulation conditions then become

1.  $\alpha(Init_1) \subseteq Init_2;$ 2. if  $(c, c') \in \rightarrow_1$ , then  $\alpha(c) = \alpha(c')$  or  $(\alpha(c), \alpha(c')) \in \rightarrow_2.$

If these conditions hold, then executions of  $S_1$  map into (possibly stuttered) executions of  $S_2$ . Thus for any property  $P_2$  which is safe in  $S_2$  we also have that the inverse image  $\alpha^{-1}(P_2)$  of  $P_2$  is safe in  $S_1$ . So properties can be inherited.

### 2.2 Extensions

Thus far the development has not been materially different from Lamport's original ideas. The subsequent extensions will be a deviation and are the main contribution of the paper [I]. As will be discussed, the first extension has a parallel in [38] whereas the second part is new.

After constructing the mapping  $\alpha$  it often turns out that some transitions in  $\rightarrow_1$  do not map as desired (examples are given in both [I] and [II]). This does not always detrude the technique since actually only the transitions

$(c, c') \in \to_1$  with  $c \in Reach_1$  need to map as described above. Consequently one may have to restrict somehow the set of  $S_1$ -transitions which are investigated. This means that one has to find a property  $P_1$  which can be proven safe in  $S_1$ ; and this may once again involve finding an invariant  $Inv_1$  of  $S_1$ such that  $Inv_1 \subseteq P_1$ .

The proof of safety of  $Inv_1$  often turns out to be double work: Apparently, to inherit a property we first have to prove the safety of another property which is nothing but a sharpened version of the property that we want to inherit. For instance, to prove that all low level transitions map as desired we may have to exploit mutual exclusion between the processes. And if mutual exclusion is the property that we want to inherit, then the technique does not buy us anything; we anyway have to give a traditional proof of mutual exclusion at the low level.

#### First extension

There is a quite easy remedy in many of the above situations. It turns out that one can simply inherit the properties an use them as restrictions to the set of investigated transitions; if the subsequent simulation proof goes through, then, as proved in [I] page 13, it turns out that reachable transitions are mapped as desired.

A similar result has been reported by Lynch and Tuttle in [38]. Their setup is slightly different, however; formulated in our framework their result is that if all transitions  $(c, c') \in \to_1$  such that  $c \in Reach_1$  and  $\alpha(c) \in Reach_2$ map as desired, then all properties of  $S_2$  can be inherited. The condition  $\alpha(c) \in Reach_2$  corresponds to our usage of  $\alpha^{-1}(Reach_2)$  as an  $S_1$ -property in the "Characterisation Lemma 1" on page 13 in [I],

#### Second extension

Still there are examples for which the thus strengthened technique—and hence also Lynch and Tuttle's—will fail (again see [I] and [II]). It may be necessary to further shrink down the set of considered transitions. In mutual exclusion algorithms it may thus be necessary—in order to make the simulation proof go through—to know more about the low level system than just the mutual exclusion property. The question then is whether inherited properties can be used in proofs of additional low level properties. It turns out that they can. The proof of such relative invariants can be incorporated into the simulation technique (pages 16-17 in [I]). The conditions for inheriting properties then become that there should exist some  $Inv_1 \subseteq C_1$  such that the following conditions hold

- 1.  $\alpha(Init_1) \subseteq Init_2$  and  $Init_1 \subseteq Inv_1$ ;

- 2. if  $(c, c') \in \rightarrow_1$  and  $c \in Inv_1 \cap \alpha^{-1}(Reach_2)$ , then  $c' \in Inv_1$ ;

- 3. if  $(c,c') \in \to_1$  and  $c \in Inv_1 \cap \alpha^{-1}(Reach_2)$ , then  $\alpha(c) = \alpha(c')$  or  $(\alpha(c), \alpha(c')) \in \to_2$ .

In [I] a number of examples are given on how to use this simulation technique (it is called an inheritance technique in [I] page 17 because the above checks allow one to inherit properties). It is also described how more general safety properties than those expressible by a safe property can be inherited. E.g. the paper considers properties of the form "process *i* cannot overtake process *j* in queue *q*".

Finally it is discussed in [I] what completeness of the simulation technique means when dealing with closed systems. As mentioned previously it is not possible to compare two closed systems independently of an interpretation or relation between the two systems.

So a traditional completeness result saying that if  $S_1$  implements  $S_2$ , then the simulation technique can be applied is not adequate here. Since part of the simulation technique in [I] is to construct the map  $\alpha$ , the designer has full control over this interpretation. We exploit this fact to state a different kind of result which says that under very mild restrictions on  $S_2$  it is possible to obtain any safety property of  $S_1$  as an inherited property. This is not a traditional completeness result but it has, unfortunately, been called a completeness result in [I].

## 2.3 An application to delay insensitive circuits

In [II] the technique from [I] is used to facilitate the construction of delay insensitive hardware.

A circuit is delay insensitive if it is robust to variations in delays of signals through the wires of the components of the circuit [58, 63]. To model such circuits one has to describe explicitly the possibility of delays in wires. In a shared variable model this is done by introducing two bit-valued variables w! and w? for each wire w. These two variables model the two endpoints of the wire, and the delay is modelled by an assignment

$$w? := w!$$

For wires the condition of delay insensitivity then says that w! may not change value as long as  $w? \neq w!$ , i. e. the circuitry may not attempt sending a new value via w when the old value is still in progress.

The explicit modelling of delays in wires tends to complicate the correctness arguments for delay insensitive circuits. The aim in [II] is to reduce this complexity by allowing the designer to reason about a more abstract model. In the more abstract model each wire w is simply represented by a single variable. Instead of treating the delays explicitly the designer is requested to verify a number of so-called implementation conditions. These implementation conditions are nothing but safe properties of the abstract model; they express that the circuit should follow the rules for so-called self-timed fourphase logic (see [58]). An application of the simulation technique from [I] then formally proves the claim that four-phase logic is insensitive to delays in wires.

# Chapter 3

# A simulation technique for compiling correctness

The second simulation technique is documented in [III].

The aim in [III] is to prove a compiling specification correct. The source language of the compilation is called PL<sub>0</sub> (see [15]) and is a subset of the occam-2 programming language [26]. A PL<sub>0</sub> program is a sequential process prefixed with declarations. Declarations introduce integer valued variables. The sequential process communicates with the environment via one input and one output channel. Sequential processes are constructed front primitive statements—input/output statements, the two processes SKIP and STOP and these processes are composed into compound sequential, conditional and iterative processes.

Finiteness is an important aspect of  $PL_0$ : integers are assumed to lie in the interval  $[-2^n, 2^n - 1]$  for some fixed n and the workspace needed by processes for allocation of both permanent and temporary variables is assumed to be bounded.

The target language of the compilation is called  $BAL_0$  (see [17]) and is a block structured assembly language for the transputer [27]. The block structure is used to avoid difficulties in generating unique jump labels. Input and output is performed through the same two predefined channels as in PL<sub>0</sub>.

In [16, 17] the languages  $PL_0$  and  $BAL_0$  are given Plotkin style structural op-

erational semantics [49]. Such a semantics defines for each of  $PL_0$  and  $BAL_0$  a single global transition system which resembles, but is slightly different from our labelled transition system. Instead of a set of initial configurations the Plotkin style semantics works with a set of terminal configurations. The set of terminal configurations is only used to define the transitions through an inference system and we will ignore it for the present. Our set of initial configurations is implicitly defined by any concrete program that we consider. In the subsequent discussion we will consequently assume that for each program in  $PL_0$  or  $BAL_0$  we have a labelled transition system as defined earlier.

The shape of PL<sub>0</sub>-configurations depend on the syntactic category under consideration. For processes, e.g., they have shape  $\langle p, \sigma \rangle$  where p is a process term and  $\sigma$  is a store. In BAL<sub>0</sub> the configurations have shape  $\langle [u, v], ms \rangle$  here u and v are BAL<sub>0</sub> code sequences, where the comma indicates the position of the program counter, and where ms is a machine state indicating the contents of certain registers and the workspace.

The compiling specification is given as an ordinary, recursively defined, function t from  $PL_0$  to  $BAL_0$  (see [18]).

### **3.1** Definition of correctness

Let  $S_p$ , be the labelled transition system defined be the PL<sub>0</sub> program p and let  $S_{t(p)}$  be the labelled transition system defined by the corresponding compiled program t(p). We will take t to be correct if  $S_{t(p)}$  correctly implements  $S_p$  for each p. Since p and t(p) describe open systems with the same interface, we require each observation of  $S_{t(p)}$  to be an observation of  $S_p$ .

This definition has not been formally stated in [III]. It has been used, however, to give an informal argument for the shape of what we will call the internal correctness predicate. Part of this argument will be repeated here.

The internal correctness predicate expresses correctness as a requirement on individual transitions and simulations of these. Thus it highly resembles a proof obligation in a simulation technique. It should be noted, however, that the only purpose of the internal correctness predicate is to ensure that  $S_{t(p)}$ implements  $S_p$ , for each p. It is another matter whether the internal correctness predicate can serve as induction hypothesis in a proof by induction. Quite in analogy with the need to consider an  $inv \subset P$  in the previous technique it turns out to be necessary to considerably strengthen the internal correctness predicate in order to get a working induction hypothesis.

### **3.2** Towards an internal correctness predicate

The internal correctness predicate in [III] page 25 arose through a series of modifications to a predicate taken from the literature. Our initial attempt at expressing correctness of the compiling specification was to use the wellknown notion of observation equivalence from [42] page 108. For the present we assume that both  $Init_p$  and  $Init_{t(p)}$  consist of just a single configuration. Then we say that  $S_p$  and  $S_{t(p)}$  are observation equivalent if there exists a relation **R** in  $C_p \times C_{t(p)}^3$  such that  $Init_p \mathbf{R}Init_{t(p)}$  and such that

- 1. if  $c_p \mathbf{R} c_{t(p)}$  and  $c_p \stackrel{l}{\longrightarrow} c'_p$ , then there is a  $c'_{t(p)}$  such that  $c_{t(p)} \stackrel{\hat{l}}{\Longrightarrow} c'_{t(p)}$ and  $c'_p \mathbf{R} c'_{t(p)}$ ;

- 2. if  $c_p \mathbf{R} c_{t(p)}$  and  $c_{t(p)} \xrightarrow{l} c'_{t(p)}$  then there is a  $c'_p$  such that  $c_p \stackrel{\hat{l}}{\Longrightarrow} c'_p$  and  $c'_p \mathbf{R} c'_{t(p)}$ .

Here the expression l yields the empty sequence  $\varepsilon$  if  $l = \tau$  (the label indicating an invisible step) and it yields the sequence consisting of just l otherwise. The expression  $c \stackrel{s}{\Longrightarrow} c'$  means that there is a sequence of transitions from cto c' such that the non- $\tau$  labelled transitions are labelled, in sequence, with the labels in s.

It was soon realized that observation equivalence is not an adequate internal correctness notion in the ProCoS project: In successive stages of the project  $PL_0$  is extended with non-deterministic constructs. Non-determinism is then treated as underspecification. This means that if p is non-deterministic, then t(p) may be made deterministic by cutting off some of the internal choices made by p.

<sup>&</sup>lt;sup>3</sup>The two sets of configurations are swapped in [III].

The treatment of non-determinism as underspecification makes it impossible to meet requirement 1 above: If there is a sequence of high level transitions

$$c_p \xrightarrow{l} c'_p \xrightarrow{l'} c''_p \dots$$

then there is no guarantee that we have a low level simulation

$$c_{t(p)} \stackrel{\hat{l}}{\Longrightarrow} c'_{t(p)} \stackrel{\hat{l'}}{\Longrightarrow} c''_p \dots$$

as would be the case if requirement 1 were met. We weaken requirement 1 by removing the last condition

$$c_p' \mathbf{R} c_{t(p)}'$$

So the simulation is not required to continue from the pair of configurations  $(c'_p, c'_{t(p)})$ .

On the other hand we do not want to completely remove requirement 1 for the remaining condition

$$c_{t(p)} \stackrel{\hat{l}}{\Longrightarrow} c'_{t(p)}$$

ensures that external communication capabilities at the high level are reflected at the low level. We will state this condition differently, however, since we want to use the mental picture of constructing high-level simulations for low level executions. So we formulate the requirement contrapositively: if the low level can refuse to participate in some external communication, then so can the high level.

To express the modified requirement we only have to analyse the circumstances under which a communication can be refused.

If the program reaches a configuration  $c_{t(p)}$  where execution has stopped, then certainly no communication is possible. We will write that the execution has stopped as

for all

$$l: c_{t(p)} \xrightarrow{l} d$$

.

In this case we require that if  $c_p \mathbf{R} c_{t(p)}$  holds, then it is possible from  $c_p$  via some number of  $\tau$ -steps to reach a configuration where also p has stopped execution.

At both levels we have that if a configuration is reached where the program is waiting for communication via channel ch (that is  $c \xrightarrow{ch:v} c'$  for some v and c'), then it simultaneously refuses to communicate via any other channel. But requirement 2 already ensures that low-level transitions are simulated by high-level transitions with the same label so if the low level refuses some communication by being ready to communicate via ch, then so does the high level. We consequently do not need any extra condition to express that the high level simulates this kind of low-level refusal.

Finally the low level can refuse to make any communication by diverging internally. For the translation from  $PL_0$  to  $BAL_0$  it turns out that this only happens when the high level also diverges internally. We want our correctness predicate to express also this simulation of internal divergence by internal divergence. It is not possible to use requirement 2 directly for this because this requirement only states that each internal low level transition  $c_{t(p)} \xrightarrow{\tau} c'_{t(p)}$  be simulated by some, maybe empty, sequence of high-level transitions  $c_p \stackrel{\hat{\tau}}{\Longrightarrow} c'_p$ . If all but finitely many of these sequences were empty, then an internal divergence could be simulated by a finite sequence of transitions in which the last configuration could be able to accept communication via some channel. Consequently some low level refusals would not be simulated at the high level.

To express that infinitely many of the simulations  $c_p \stackrel{\hat{\tau}}{\Longrightarrow} c'_p$  must be nonempty we index the simulation relation  $\mathbf{R}$  by elements w from a well-founded order (W, <). Requirement 2 is then hanged to say that if  $c_p \mathbf{R}_w c_{t(p)}$  holds and  $c_{t(p)} \stackrel{l}{\Longrightarrow} c_{t(p)'}$ , then there must be a configuration  $c'_p$  such that  $c_p \stackrel{\hat{l}}{\Longrightarrow} c'_p$ and such that  $c'_p \mathbf{R}_{w'} c'_{t(p)}$  holds with w' < w whenever  $c_p \stackrel{\hat{l}}{\longrightarrow} c'_p$  is an empty sequence; the index, then, is only allowed to increase when  $c_p \stackrel{\hat{l}}{\Longrightarrow} c'_p$  is nonempty. Since (W, <) is well-founded, this means that when constructing a simulation of a divergent computation we occasionally have to choose nonempty simulations of transitions and this forces the constructed simulating computation to be infinite.

Two additional comments are necessary before we can present the resulting correctness predicate.

First, the sets  $Init_p$  and  $Init_{t(p)}$  of initial configurations do not consist of just a single state each. E.g. the program p really defines a bunch of initial configurations, one for each choice of initial value for the variables. We consequently cannot require  $\mathbf{R}$  to relate all of  $Init_p$  with all of  $Init_{t(p)}$ . Since we want to construct high level simulations of low level executions we instead require that for each  $c_{t(p)} \in Init_{t(p)}$  there should exist a  $c_p \in Init_p$  such that  $c_p \mathbf{R}_w c_{t(p)}$  holds for some w.

Next, we have not yet taken into account the limited size of workspace and of transputer words. This is taken into account by recursively defining a set of functions which measure the words needed by each subpart of the program and the necessary word-size for jumps within the program. A program is then said to be compilable whenever the total workspace needed is less than the available workspace and whenever all jumps can be implemented with the available word-size.

The resulting correctness predicate can be summed up as follows. Let  $S_p$  be the labelled transition system defined by p and let  $S_{t(p)}$  be the labelled transition system defined by t(p). We say that t is correct if for each compilable program p there exists a family of relations  $\mathbf{R}_w$  such that

- 1. if  $c_p \mathbf{R}_w c_{t(p)}$  and  $c_{t(p)} \stackrel{l}{\longrightarrow} c'_{t(p)}$ , then there is a  $c'_p$  such that  $c_p \stackrel{\hat{l},m}{\Longrightarrow} c'_p$ and  $c'_p \mathbf{R}_{w'} c'_{t(p)}$  where m = 0 implies w' < w;

- 2. for each  $c_{t(p)} \in Init_{t(p)}$  there is a  $c_p \in Init_p$  and a  $w \in W$  such that  $c_p \mathbf{R}_w c_{t(p)}$ ;

- 3. If  $c_p \mathbf{R}_w c_{t(p)}$  and for all  $l : c_{t(p)} \xrightarrow{l}{/}$ , then there is a  $c'_p$  such that  $c_p \stackrel{\epsilon}{\Longrightarrow} c'_p$  and for all  $l : c'_p \xrightarrow{l}{/} \stackrel{l}{/} \stackrel{4}{\longrightarrow}$

### **3.3** The correctness proof

We next turn to how the proof of this correctness predicate is conducted. We are required, for each p, to define an appropriate family of relations  $\mathbf{R}_{w}^{p}$  and

$<sup>{}^{4}</sup>$ In [*III*] page 25 the predicate is slightly stronger since we distinguish between proper and improper termination. This is due to the view that it is possible to communicate with the system after its termination to see how it terminated.

to prove that it satisfies the three conditions. Basically we want to reuse the corresponding families of  $\mathbf{R}_w^q$ -relations defined for each subconstruct q of p along with the properties enjoyed by them. This could be done by defining the relations  $\mathbf{R}_w^p$  by recursion on the structure of p. It turns out, however, that for some p it is inconvenient to give a direct closed form definition of  $\mathbf{R}_w^p$ . For instance the process  $\mathtt{WHILE}(b,p)$  gets packed into a sequence  $\mathtt{SEQ}[\cdot]$  for each iteration so that the process becomes  $\mathtt{SEQ}^n[\mathtt{WHILE}(b,p)]$  after n iterations whereas the  $\mathtt{BAL}_0$  program counter just cycles n times through the code; for this process we rather want from

$$\langle p, \sigma \rangle \mathbf{R}_{w}^{\mathtt{WHILE}(b,p)} \langle [u, v], ms \rangle$$

to infer

$$\langle \operatorname{SEQ}[p], \sigma \rangle \mathbf{R}_w^{\operatorname{WHILE}(b,p)} \langle [u, v], ms \rangle$$

This suggests to use inference systems for the definition of  $\mathbf{R}_w^p$  for each p. Since definition by inference systems encompasses definition by recursion in p we have made the choice to give a simultaneous definition of all  $\mathbf{R}_w^p$  by means of an inference system. The proof that the three above requirements are met is consequently conducted by induction on the inference trees of relation instances  $c_p \mathbf{R}_u^p(c_{t(p)})$ .

As already mentioned the three requirements have to be strengthened in order to serve as an induction hypothesis in the induction proof. Consider for instance the process  $SEQ[p_1, p_2]$  where  $p_1$  translates into u and  $p_2$  translates into v. When the process  $p_1$  has been executed, then one needs to relate  $\langle p_2, \sigma \rangle$  to  $\langle [u, v], ms \rangle$ . This is only possible if ms is a proper representation of  $\sigma$ . And consequently it has to be explicitly expressed that if some BAL<sub>0</sub> transition is simulated by some sequence of high level transitions, then the final ms actually is a proper representation of  $\sigma$ .

Even though  $PL_0$  is just a small language, the proof in [III] is large; it runs over more than 40 pages. It seems that there are (at least) three different reasons for this.

First, the languages and the compiling specification have been defined independently of the proof effort. This means that all the "fine-tuning" of the definitions which usually precedes the publication of similar proofs has not been possible here. Second, the bounded size of transputer words and of the available memory makes it necessary to make a lot of extra checks. It has to be demonstrated that references to words do not fall outside the workspace in use; and for each arithmetic operation one has to distinguish between situations with normal and abnormal outcomes.

Third, and most importantly, the proof technique itself seems to introduce complications since it requires us to find simulations for every single transition at the low level. This means that we are often forced to relate quite awkwardly. For instance a process like ch!x is translated to a BAL<sub>0</sub> sequence of seven instructions. So execution of the construct requires seven steps at the low level but only a single step at the high level and the problem then is to find out with what high level configuration the six intermediate configurations of the low level should be related.

# Chapter 4

# Chunk by chunk simulation

The third simulation technique is documented in [IV]. The technique is an attempt to cut down on the size of the proof for sequential processes in [III]. Furthermore the paper gives two different ways to extend the third simulation technique to deal with parallelism. The sequential part of the technique and its use is also documented in [V] and the presentation there is a slight improvement over the presentation in [IV].

The programming language PL in [IV] page 7 is both an extension and a simplification of PL<sub>0</sub> from [15]. It contains parallelism at the outermost level, an arbitrary number of channels can be used for communication, and a CHOICEconstruct introducing internal non-determinism has been included. On the other hand the declarations have been removed (they were only present in PL<sub>0</sub> in order to make the statical semantics of PL<sub>0</sub> non-trivial) and integers may take on arbitrarily large values.

The assembly language AL is adjusted accordingly. Furthermore configurations of a running AL program are made more low level as they now contain an instruction pointer pointing into the code instead of the comma notation in BAL<sub>0</sub>.

### 4.1 In search for a better technique

The new simulation technique is an attempt to overcome two problems with the previous simulation technique. We want to get rid of the indices w on the simulation relation and we want to relax the strict demand of relating high and low level configurations after each transition at the low level. It will turn out that a single idea overcomes both problems.

The indices w were introduced to ensure that infinite sequences at the low level are simulated by infinite sequences at the high level. We now try to ensure this differently.

The first suggestion is to require that each transition be simulated by a non-empty sequence of high level transitions. This of course forces infinite executions to be simulated by infinite executions. But it also has the consequence that high level executions must contain more transitions than the low level executions which they simulate and this is clearly undesirable.

To avoid forcing the high level execution to contain more transitions we suggest to find simulations only for chunks of low level executions and not for individual transitions. So our requirement will be that if  $c_p \mathbf{R} c_{t(p)}$  holds and  $c_{t(p)} \rightarrow c'_{t(p)}$  is the first transition of a sufficiently long low level execution, then it is possible to find a prefix  $c_{t(p)} \rightarrow c'_{t(p)} \Rightarrow c''_{t(p)}$  of this execution and a non-empty high level simulation  $c_p \Rightarrow c''_p$  such that  $c''_p \mathbf{R} c''_{t(p)}$  holds. This again ensures that infinite low level executions are simulated by infinite high level executions are not forced to contain more transitions than the low level executions.

The sketched idea is also appropriate for relaxing the requirement of relating configurations after each low level step. Consider for instance the high level process x := e and its translation  $eval(e); stl(x)^5$ . They give rise to the following executions.

$$\begin{array}{ll} \text{high level} & \langle x := e, \sigma \rangle \xrightarrow{\tau} \langle \textbf{terminated}, \sigma \oplus \{ x \mapsto e(\sigma) \} \rangle \\ \text{low level} & \langle 0, reg, \sigma \rangle \xrightarrow{\tau} \langle 1, e(\sigma), \sigma \rangle \xrightarrow{\tau} \langle 2, e(\sigma), \sigma \oplus \{ x \mapsto e(\sigma) \} \rangle \end{array}$$

In PL the value  $e(\sigma)$  of the expression e evaluated in store  $\sigma$  is saved in

<sup>&</sup>lt;sup>5</sup>For simplicity we assume the existence of AL-instructions which evaluate expressions in one step.

variable x whereby the process becomes terminated. In AL the instruction pointer first moves from 0 to 1 while  $e(\sigma)$  is loaded into the general purpose register; next the instruction pointer moves from 1 to 2 while the value in the general purpose register is stored in variable x.

The problem in the previous simulation technique is that the intermediate configuration  $\langle 1, e(\sigma), \sigma \rangle$  is required to be related to some of the two high level configurations and neither choice seems to be natural. The best would be simply to avoid relating  $\langle 1, e(\sigma), \sigma \rangle$  to anything while relating only  $\langle 0, reg, 0 \rangle$  to  $\langle x := e, \sigma \rangle$  and  $\langle 2, e(\sigma), \sigma \oplus \{x \mapsto e(\sigma)\} \rangle$  to  $\langle \text{terminated}, \sigma \oplus \{x \mapsto e(\sigma)\} \rangle$ . The seketched idea allows us to do just so by grouping the two low level transitions into a chunk such that only the initial and the final configurations need to be related to high level configurations.

Unfortunately the sketched idea does not directly work. There are both pragmatic and theoretical reasons for this.

The sketched idea requires us to match non-empty low level sequences of transitions with non-empty high level sequences. This is not always as natural as we may hope for. Consider e.g. the process

#### $p_1$ SEQ SKIP SEQ $p_2$

The process SKIP just translates into the empty code sequence so the result of translating the above process is the code sequence

$$t(p_1); t(p_2)$$

At the high level we get the execution

$$\cdots \langle \text{SKIP SEQ } p_2, \sigma \rangle \xrightarrow{\tau} \langle p_2, \sigma \rangle \cdots$$

So it takes one transition to remove the process SKIP. At the low level there is no such transition

$$\cdots \langle i, reg, \sigma \rangle \cdots$$

The problem then is to what simulation the SKIP transition should belong; it could belong either to the simulation of a chunk ending in  $\langle i, reg, \sigma \rangle$  or to the simulation of a chunk beginning in  $\langle i, reg, \sigma \rangle$ . Neither choice seems attractive. Rather it seems desirable to have the ability of inserting an *empty*  chunk between the chunks ending and beginning in  $\langle i, reg, \sigma \rangle$  and to simulate this *empty* chunk by the transition

$$\langle \text{SKIP SEQ } p_2, \sigma \rangle \longrightarrow \langle p_2, \sigma \rangle$$

The reverse effect can also be observed—that some low level transitions most naturally are simulated by empty sequences of high level transitions. This effect occurs e.g. when executing a loop WHILE(b, p). At the low level, after executing the body of p, there is an explicit jump transition which leaves control at the beginning of the loop. At the high level there is no such transition, rather the last transition in the execution of p leads directly to a configuration of form  $\langle \text{WHILE}(b, p), \sigma \rangle$ . Now it would be desirable to simulate the non-empty chunk consisting of the jump transition by an *empty* high level execution.

As we did in the previous simulation technique, we also want the chunk by chunk technique to ensure that low level refusals are simulated by high level refusals. This is the origin of the theoretical problem with the sketched idea.

To explain the problems consider first a finite low level execution for which a simulating high level execution can be found. We can identify two necessary requirements in the technique. To start the construction of the high level execution we must require that the initial low level configuration and the initial high level configuration are related.

Furthermore, to ensure that the two executions define the same set of refusals, it must be the case that the two final configurations enable the same set of communications. Since the two final configurations will be related, this is ensured by requiring that related configurations enable the same set of communications.

But now consider the process ch!e and its translation eval(e); out(ch) which give rise to the following executions

high level

$$\langle ch!e, \sigma \rangle \xrightarrow{ch:e(\sigma)} \langle (\mathbf{terminated}, \sigma \rangle$$

low level  $\langle 0, reg, \sigma \rangle \xrightarrow{\tau} \langle 1, e(\sigma), \sigma \rangle \xrightarrow{ch:e(\sigma)} \langle 2, e(\sigma), \sigma \rangle$

It is easily seen that the two above requirements collide in this case: First we are required to relate  $\langle ch!e, \sigma \rangle$  with  $\langle 0, reg, \sigma \rangle$  and next we are required to

show that the thus related configurations enable the same set of communications which is clearly not the case since  $\langle ch!e, \sigma \rangle$  enables a communication along *ch* whereas  $\langle 0, reg, \sigma \rangle$  does not. Again in this case it seems desirable to simulate the first transition from  $\langle 0, reg, \sigma \rangle$  to  $\langle 1, e(\sigma), \sigma \rangle$  by an *empty* high level execution such that  $\langle ch!e, \sigma \rangle$  and  $\langle 1, e(\sigma), \sigma \rangle$  which enable the same communications can subsequently be related. Furthermore the relation between the two initial configurations should be of another sort not requiring the same set of communications to be enabled.

As hinted at both the pragmatic and the theoretical problems can be solved by introducing two relations  $\mathbf{S}$  and  $\mathbf{R}$  with different requirements. If two configurations are  $\mathbf{S}$ -related, then they enable the same set of communications and from any sufficiently long execution it is possible to cut out a non-empty chunk which has a non-empty high level simulation such that the respective final configurations are  $\mathbf{R}$ -related.  $\mathbf{R}$ -related configurations need not have the same communication capabilities as  $\mathbf{SS}$ -related. We only require that if two configurations are  $\mathbf{R}$ -related, then it is possible from any execution originating in the low level configuration to cut out a chunk which has a high level simulation such that the respective final configurations are  $\mathbf{S}$ -related.

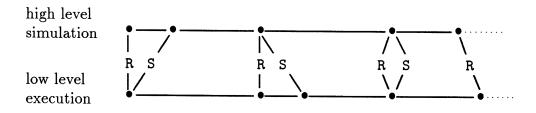

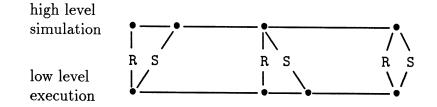

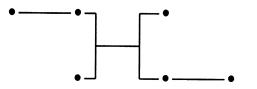

Figure 4.1: The chunk-by-chunk technique on infinite executions.

When using the  $\mathbf{R}$ - and  $\mathbf{S}$ -relations to construct simulations of low level executions we end up with a picture like in figure 1 for infinite executions. For finite executions a typical picture is given in figure 2. Notice that a finite execution and its simulation must end in a pair of configurations which are  $\mathbf{S}$ -related.

To express the requirements on  $\mathbf{R}$ - and  $\mathbf{S}$ -related configurations formally we have to express that an execution  $\gamma$  is sufficiently long. In [IV] the approach taken is to require  $\gamma$  to be complete which means that  $\gamma$  cannot be extended with internal transitions (page 15).

Figure 4.2: The chunk-by-chunk technique on finite executions.

In the following formalization we assume that  $\gamma$  is any complete execution. The notation  $\beta \sqsubseteq \gamma$  means that  $\beta$  is an initial chunk of  $\gamma$ , i.e.  $\beta$  is a prefix of  $\gamma$ . The initial configuration of  $\gamma$  is denoted  $\gamma$ . Finally the function *enable* yields the set of enabled channels when applied to a PL configuration pc and the (code-dependend) function  $enable_{t(p)}$  yields the set of enabled channels (in code t(p)) when applied to an AL configuration mc. We say that t is correct if, for each p, it is possible to find  $\mathbf{R}^p$  and  $\mathbf{S}^p$  satisfying the below requirements

1.

$$\downarrow \begin{array}{l} pc\mathbf{R}mc \wedge b = \mathbf{\hat{\gamma}} \\ \exists \alpha, \beta : (\alpha = pc \stackrel{\varepsilon}{\Rightarrow} pc') \wedge (\beta = mc \stackrel{\varepsilon}{\Rightarrow} mc') \wedge (\beta \sqsubseteq \gamma) \wedge pc'\mathbf{S}mc' \\ \end{aligned}$$

2.

$$\downarrow \begin{array}{l} pc\mathbf{S}mc \wedge \gamma = mc \stackrel{l}{\longrightarrow} \cdots \\ \exists \alpha, \beta : (\alpha = pc \stackrel{l}{\Rightarrow} pc') \wedge (\beta = mc \stackrel{l}{\Rightarrow} mc') \wedge (\beta \sqsubseteq \gamma) \wedge pc'\mathbf{R}mc' \\ \end{aligned}$$

3.

$$pc\mathbf{S}mc \Rightarrow (enable(pc) = enable_{t(p)}(mc))$$

### 4.2 The correctness proof

As in the previous simulation technique we define the two relations  $\mathbf{R}^p$  and  $\mathbf{S}^p$  by an inference system and the proof that the above requirements hold is consequently performed by induction on the structure of inference trees.

Again it is necessary to strengthen the above predicate in order to get a working induction hypothesis. The strengthening is only very slight; condition 3 has to be strengthened into

3'.

$$pc\mathbf{S}mc \Rightarrow (enable(pc) = enable_{t(p)}(mc)) \land (pc \in T_{PL} \Leftrightarrow mc \in T_{AL}^{t(p)})$$

The stronger version 3' is necessary to deal with the SEQ-construct, It ensures that an **S** to **R** chunk inside a  $t(p_1)$ ;  $t(p_2)$ -execution corresponds to an **S** to **R** chunk of a  $t(p_1)$ -execution whenever the instruction pointer of the  $\mathbf{S}^{\text{SEQ}[p_1,p_2]}$ -related configurations points to a location inside  $t(p_1)$ . And it enables us to treat a special problem which arises, namely the problem that both the final chunk of  $t(p_1)$  and the initial chunk of  $t(p_2)$  will be of the **R** to **S** type. If no countermeasures were taken, this would lead to a violation of the principle that the two types of chunks should strictly alternate. We will not go deeper into the technical motivation for using 3' but refer to [V] page 65.

### 4.3 External semantics

In the discussion leading up to the internal correctness predicates in both the previous and the present technique we used arguments which build on our expectations to the externally observable behaviour of transition systems. These expectations can be formalized. When this is done it becomes possible to give an external definition of the relationship that one transition system implements another. Furthermore it becomes possible to formally prove that the simulation techniques establish that the transition system given by t(p)implements the transition system given by p for each p.

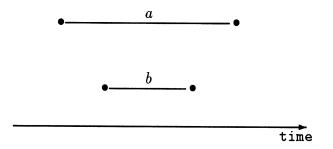

As mentioned previously the external semantics is only used as an informal guide in [III]. In [IV] the external semantics is treated fully formally. There are *two* definitions of external semantics, however, due to different treatments of parallelism. Since these two definitions coincide for programs consisting of just a single sequential process, we will take the opportunity to sketch the external semantics of sequential processes. Furthermore we describe how correctness of sequential processes can be expressed by this external semantics and how the internal correctness predicate is correct with repsect to the external notion of correctness.

In correspondence with our general linear time view (see the Introduction) we take the external semantics of a system to be a set of observations where each observation is derived from an execution of the system. There are two

things which can be observed in an execution. The first is the sequence of communications with the environment—the trace [6]. The second is the set of channels along which the system refuses to communicate—the refusal set [6].

Although we follow the failure semantics of [6] in the structure of observations we do not follow it in the interpretation of refusal sets and in the treatment of diverging processes. In [6] a channel is only refused if the execution ends in a stable configuration (a configuration not allowing internal transitions) in which a communication labelled with the channel is not possible. In our approach we take a channel to be refused if it is refused—under an assumption of weak fairness—in the long run. More precisely, in addition to the refusals in [6] we also regard a channel as being refused in an infinite execution if communication via the channel only occurs a finite number of times and if communication along the channel is infinitely often disabled. The latter requirement says that we can only force the system to participate in a communication if the system is continuously prepared to do so from some point in the execution.

Notice that a system which diverges internally will refuse every channel. This is in contrast with failure semantics where diverging processes are treated to be equivalent with the chaotic process from the point where the divergence starts. The chaotic process can exhibit any behaviour, also a behaviour where no channel is refused.

It is now easy to express that transition system S' implements transition system S. With the view that non-determinism in S is just a means of underspecification we get that every observation made of S' should also be a possible observation of S—in other words the observations of S' should be included in the observations of S. If we let [S] and [S'] denote the external semantics of S and S' respectively, then the formal statement of S'implements S becomes

$$\llbracket S' \rrbracket \subseteq \llbracket S \rrbracket^6$$

<sup>&</sup>lt;sup>6</sup>This inclusion property could be weakened slightly to correspond more closely with our informal explanation. If some refusal set is observed in an execution at the low level, then it is not necessary to require that the constructed high level simulation defines the *same* refusal set as the low level execution; it is sufficient to require that the simulation defines a larger refusal set since refusing a set also means refusing each of its subsets. This

With this definition we say that translation t is correct on sequential processes if, for each sequential p, transition system  $S_{t(p)}$  implements transition system  $S_p$ . We call this kind of correctness predicate an external correctness predicate since it relates the external semantics of the systems.

A simulation technique is said to be sound with respect to the external semantics if its internal correctness predicate entails the external correctness predicate. It is not directly proven in [IV] that the chunk by chunk technique is sound for sequential processes. Instead, as will be described below, a similar claim is proved with two different external semantics for parallel processes, and the claim for sequential processes follow as an easy specialization of both these results.

#### 4.4 Treatment of parallelism

The major part of [IV] is concerned with generalizations of the chunk by chunk technique to deal with parallelism also.

A PL program is a parallel composition  $PAR[p_1, \ldots, p_N]$  of sequential processes  $p_1, \ldots, p_N$ . To describe the distribution of code on different processors in AL we introduce the operator **par** where  $par(\pi_1, \ldots, \pi_N)$  is interpreted as the system consisting of N processors where code  $\pi_i$  is executed of processor i (in [IV] we use  $\parallel$  instead of **par**, but we want to reserve  $\parallel$  for an operation introduced in [V]). Then the translation of parallel programs in PL simply is

$$t(\text{PAR}[p_1, \ldots, p_N]) = || (t(p_1), \ldots, t(p_N))$$

If we try to follow the chunk by chunk technique for parallel constructs also, then we must break down each execution of  $par(t(p_1), \ldots, t(p_N))$  into smaller chunks, simulate each chunk at the PL-level, and glue all these subsimulations together to one simulating execution of  $PAR[p_1, \ldots, p_N]$ . In this approach we of course want to reuse the chunks and simulations found for each of the processes  $p_i$ . But as the following example shows, this may be very difficult to do directly.

leads to a weaker notion of implementation which is used in the next section.

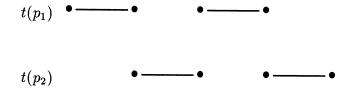

Assume that N = 2, that  $p_1$  is the process  $x_1 := e_1$  and  $p_2$  the process  $x_2 := e_2$ . The translation of each of these processes is  $eval(e_i)$ ;  $stl(x_i)$  for i = 1, 2. For each of i = 1, 2 this machine code executes in two transitions and these two transitions are chosen to constitute a chunk when when using the chunk by chunk technique. But when we execute the two pieces of machine code in parallel, then the chunks may interleave very inconveniently as demonstrated in figure 4.3. The chunks for the two processes get entangled in such a way that we cannot directly use a chunk for  $t(p_i)$  as a chunk for the entire program; the chunk is mixed with transitions from other processes.

Figure 4.3: Inconvenient interleaving of two chunks.

The first idea to get around this problem is the idea of simulating *principal* transitions instead of chunks [IV] page 42. A principal transition is a transition in a chunk which is chosen to represent the entire chunk. In contrast to the chunks which may be heavily interleaved and thus may be only partially ordered, the principal transitions will be linearly ordered and it is thus possible to glue together a linear simulating execution from the subsimulations found for each principal transition. So whereas it is quite possible that the chunks are very entangled in the low level execution, in the constructed high level execution the subsimulation will be nicely separated.

When refraining from breaking down the global low level executions into chunks, we once again have to relate after each low level transition. The only thing we want to express, however, is that if some process reaches a principal transition, then this transition can be simulated from the current high level configuration. This means that we do not relate the global low level configuration to a global high level configuration, instead we relate the projection of the low level configuration onto each of the processes to a likewise projected high level configuration. For the sequential processes we have only defined relations at the endpoints of chunks so we need to create new relations for all the intermediate configurations. This is done by taking the relation which holds at one endpoint and attaching a counter to it which simply counts the number of transitions in process  $t(p_i)$  till the endpoint of the chunk. Since it turns out to be convenient to place principal transitions first in chunks, the counter also indicates the number of transitions to the next principal transition.

The use of counters also proves helpful when it comes to the demonstration that the constructed high level simulation is fair when the considered low level execution is. When parallel processes are introduced an execution is called fair if no continuously enabled internal transitions are postponed indefinitely. In parallel systems internal transitions encompass both  $\tau$ -labelled transitions and transitions labelled with communications via internal channels in the system. All non-principal transitions at the low level are  $\tau$ -labelled so the fairness condition at the low level ensures that these transitions are eventually executed when enabled. This means that the counter for each process is eventually decreased and since counters are natural numbers, each counter eventually gets the value 0; so the principal transition is enabled eventually. The fairness requirement then forces the principal transition to be taken if it is an internal transition and this ensures that a subsimulation can be found which extends the high level execution under construction. Consequently the high level fairness constraint gets satisfied.

In [IV] the sketched simulation technique is proved sound relative to an external semantics (pages 55 to 58). This external semantics is a direct generalization of the already described semantics. The meaning of a parallel program is taken to be a set of observations where an observation consists of a trace and a refusal set defined as before. The executions which are considered must satisfy the above mentioned fairness constraint.

The basic structure in the proof of soundness is to construct a simulating execution as a limit of approximations. The next approximation is obtained by concatenating the current approximation with the subsimulation found for the next transition in the considered low level execution.

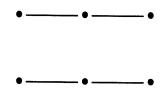

The paper [IV] also presents another way around the problem that chunks may overlap very inconveniently when executions of individual processes are interleaved. The crucial observation is that it is really the interleaving of the sequential executions that causes the problem. So instead of sticking with the traditional view that executions of parallel processes are just interleavings of sequential executions we introduce the notion of non-interleaved executions (page 66 in [IV]).

The basic observation which leads to non-interleaved executions is that an execution of a sequential program can be viewed as labelled graph consisting of a single path where vertices are labelled with configurations and edges are labelled with transitions. The generalization to N sequential processes then is a graph consisting of N paths. Because of communications it is not possible to directly use the traditional concept of a graph; a communication is conceptually just a single transition, but it has two initial and two final configurations. We consequently introduce the notion of a multi-graph where edges are allowed to have more than one origin and more than one destination.

Figure 4.4: Non-interleaved execution without communications.

With the concept of a non-interleaved execution the execution of

$$t(PAR[x_1 := e_1, x_2 := e_2])$$

will now be depicted as in figure 4.4. As is seen the two chunks found for the respective two processes are kept completely separated. If the translated program were instead, say, PAR[ch!e, ch?x], then the non-interleaved execution would give rise to a picture like in figure 4.5. Here the process t(ch!e)first evaluates e; then the two processes communicate; finally process t(ch?x)stores the communicated value in variable x.

Figure 4.5: Non-interleaved execution with a communication.

Non-interleaved executions allow a simpler expression of our fairness condition. Now we can simply say that a non-interleaved execution is fair if it is inextensible by internal transitions.

With non-interleaved executions it is possible to directly reuse the internal correctness predicate for sequential processes: The non-interleaved low level execution can be broken down into the chunks found for sequential processes, their respective simulations can subsequently be glued together into a simulating non-interleaved high level execution.

Non-interleaved executions could be used as a basis of extracting the already described external semantics. They do, however, also open up for the definition of a more general external semantics based on pomsets [52]. In this kind of external semantics we extract a pomset instead of a trace from the execution. A pomset is a partially ordered multiset where the elements in the multiset are labels of transitions and the partial order is the causal dependencies between the labels. A non-interleaved execution identifies two labels as being ordered if there is a path in the execution from the smaller label to the larger label.