# Washington University in St. Louis Washington University Open Scholarship

All Computer Science and Engineering Research

**Computer Science and Engineering**

Report Number: WUCS-93-35

1993-01-01

# A Unified Model for Shared-Memory and Message-Passing Systems

Kenneth Goldman and Katherine Yelick

A unified model of distributed systems that accomodates both shared-memory and messagepassing communication is proposed. An extension of the I/O automaton model of Lynch and Tuttle, the model provides a full range of types of atomic accesses to shared memory, from basic reads and writes to read-modify-write. In addition to supporting the specification and verification of shared memory algorithms, the unified model is particularly helpful for proving correspondences between atomic shared objects and invocation-response systems and for proving the correctness of systems that contain both message passing and shared memory (such as a network of shared-memory multiprocessors or a... **Read complete abstract on page** 2.

Follow this and additional works at: https://openscholarship.wustl.edu/cse\_research Part of the Computer Engineering Commons, and the Computer Sciences Commons

### **Recommended Citation**

Goldman, Kenneth and Yelick, Katherine, "A Unified Model for Shared-Memory and Message-Passing Systems" Report Number: WUCS-93-35 (1993). *All Computer Science and Engineering Research*. https://openscholarship.wustl.edu/cse\_research/324

Department of Computer Science & Engineering - Washington University in St. Louis Campus Box 1045 - St. Louis, MO - 63130 - ph: (314) 935-6160. This technical report is available at Washington University Open Scholarship: https://openscholarship.wustl.edu/ cse\_research/324

# A Unified Model for Shared-Memory and Message-Passing Systems

Kenneth Goldman and Katherine Yelick

#### Complete Abstract:

A unified model of distributed systems that accomodates both shared-memory and message-passing communication is proposed. An extension of the I/O automaton model of Lynch and Tuttle, the model provides a full range of types of atomic accesses to shared memory, from basic reads and writes to read-modify-write. In addition to supporting the specification and verification of shared memory algorithms, the unified model is particularly helpful for proving correspondences between atomic shared objects and invocation-response systems and for proving the correctness of systems that contain both message passing and shared memory (such as a network of shared-memory multiprocessors or a distributed memory multiprocessor with multi-threaded nodes). As an illustration of the model, we consider distributed systems in which the shared objects have the linearizability property proposed by Herlihy and Wing. We use the model to construct a careful proof that invocation-response systems constructed from linearizable objects simulate atomic shared memory systems. In addition, we extend the work of Herlihy and Wing by treating not only safety properties of invocation-response systems, but also liveness properties.

A Unified Model for Shared-Memory and Message-Passing Systems

Kenneth Goldman and Katherine Yelick

WUCS-93-35

June 1993

Department of Computer Science Washington University Campus Box 1045 One Brookings Drive Saint Louis, MO 63130-4899

·

.

:

# A Unified Model for Shared-Memory and Message-Passing Systems

Kenneth Goldman\* Department of Computer Science Washington University St. Louis, MO 63130 kjg@cs.wustl.edu Katherine Yelick<sup>†</sup> Computer Science Division University of California Berkeley, CA 94720 yelick@cs.berkeley.edu

June 29, 1993

#### Abstract

A unified model of distributed systems that accommodates both shared-memory and messagepassing communication is proposed. An extension of the I/O automaton model of Lynch and Tuttle, the model provides a full range of types of atomic accesses to shared memory, from basic reads and writes to read-modify-write. In addition to supporting the specification and verification of shared memory algorithms, the unified model is particularly helpful for proving correspondences between atomic shared objects and invocation-response systems and for proving the correctness of systems that contain both message passing and shared memory (such as a network of shared-memory multiprocessors or a distributed memory multiprocessor with multi-threaded nodes). As an illustration of the model, we consider distributed systems in which the shared objects have the *linearizability* property proposed by Herlihy and Wing. We use the model to construct a careful proof that invocation-response systems constructed from linearizable objects simulate atomic shared memory systems. In addition, we extend the work of Herlihy and Wing by treating not only safety properties of invocation-response systems, but also liveness properties.

Keywords: distributed systems, I/O automata, invocation-response, linearizability, message passing, models, shared memory

# 1 Introduction

Reasoning about algorithms for asynchronous concurrent systems is difficult, primarily because of the arbitrary interleaving of process steps that may occur in an execution. As a result, researchers have turned to formal models in order to define problems precisely, give unambiguous descriptions

<sup>\*</sup>This work was supported in part by the National Science Foundation as a Research Initiation Award (number CCR-91-10029). A portion of this work has appeared as: Kenneth Goldman and Nancy Lynch, Modelling Shared State in a Shared Action Model, *Proceedings of the 5th Annual IEEE Symposium on Logic in Computer Science*, June 1990, and was supported in part by the National Science Foundation under Grant CCR-86-11442, by the Office of Naval Research under Contract N00014-85-K-0168, and by the Defense Advanced Research Projects Agency (DARPA) under Contract N00014-83-K-0125.

<sup>&</sup>lt;sup>†</sup>This work was supported in part by the National Science Foundation as a Research Initiation Award (number CCR-9210260), and as an Infrastructure Grant (number CDA-8722788), by Lawrence Livermore National Laboratory (task number 33), by the Advanced Research Projects Agency of the Department of Defense monitored by the Office of Naval Research under contract DABT63-92-C-0026, by the Semiconductor Research Consortium under contract 92-DC-008 and 93-DC-008, and by AT&T. The information presented here does not necessarily reflect the position or the policy of the Government and no official endorsement should be inferred.

of algorithms, and construct careful proofs for safety and progress properties. These models allow one to be explicit about the possible interleavings that may occur in a distributed system and may specify which of those interleavings are to be considered "fair" to the individual system components. Examples include CSP [9], in which system components communicate by sending messages over synchronous channels, and UNITY [4], in which components communicate by reading and modifying shared variables.

The I/O automaton model [15, 16] is particularly well-suited for modelling distributed algorithms described using message passing. The I/O automaton model is a (not necessarily finite) state machine model that provides extra support for classifying actions as input or output and for describing fairness conditions. Precise problem statements are defined in terms of the input and output actions that occur at the boundary between the algorithm and its "environment." These problem statements may include nontrivial liveness constraints on the behavior of the algorithm. Careful algorithm descriptions are constructed by specifying the states and transition relations of I/O automata. A range of proof techniques, from simple assertional reasoning to hierarchical possibilities mappings, may be used to verify an algorithm satisfies a problem statement. In addition, the model can be used for carrying out complexity analysis and for proving impossibility results. The communication mechanism in a distributed system is modeled as an explicit I/O automaton that shares actions with the other system components. Therefore, the model can accommodate a variety of message-passing systems, from systems with strictly FIFO message delivery to those in which messages may be delivered out of order or not at all.

Although the I/O automaton model provides excellent support for modelling message-passing algorithms, many of the important asynchronous concurrent algorithms are described using shared memory. Also, one might wish to use both shared-memory and message-passing to describe different components of a heterogeneous system. Therefore, introducing a shared-memory mechanism into the I/O automaton model is a useful unification of these two approaches. The shared memory model of Lynch and Fischer [13] introduced the separation of input and output actions, and was a precursor of the current I/O automaton model. However, until now it has not been clear how to integrate the two basic approaches.

In this paper, we present an extension to the I/O automaton model to allow modelling of shared memory systems, as well as systems that have both shared memory and shared action communication. A full range of types of atomic accesses to shared memory is allowed, from basic reads and writes to atomic read-modify-write. We define a special class of actions, called "shared memory actions," to model atomic accesses to shared memory. Actions in the basic I/O Automaton model contain information about input and output values; we define shared memory actions to contain additional information that corresponds to the contents of the shared memory before and after the action occurs. A "shared memory automaton" is then defined to be an I/O automaton that satisfies certain natural conditions regarding its shared memory actions. For example, one condition captures the idea that an access to shared memory must be prepared to observe any value in the memory.

Since shared memory automata are simply special cases of I/O automata, all the I/O automaton model definitions and properties, notably composition and fairness, apply to shared memory automata as well. We show that composing of a collection of shared memory automata (for a given set of shared variables) yields another shared memory automaton (for the same set of variables). To combine shared memory automata having different (not necessarily disjoint) sets of shared variables, we define an "augmentation" operator that is used to expand the set of shared variables for each component before composing. We show that the natural compositionality results hold when we combine shared memory automata in this way. For example, projecting the execution of a composition on the individual components yields executions of those components. Since we expose the observed state of shared memory in the behavior of an automaton, we also achieve compositionality of the *behaviors* of shared memory automata. That is, in the standard sense of I/O automaton composition, the behaviors of a composition of shared memory automata are the same as the composition of the behaviors of the individual automata.

Shared memory automata operate in a system in which the environment is free to change the contents of the shared memory at any time. We define a "closeout" operator, which takes a shared memory automaton and a set of variables and produces a new shared memory automaton in which the given set of variables is made private, absorbed into the local state. In this way, we restrict the set of components in a system that may access portions of the shared memory.<sup>1</sup> We provide an analogous closeout operator on sets of behaviors, and we show that the behaviors of a *closed out automaton* are the same as the *closed out behaviors* of the original automaton.

Just as does the original I/O automaton model, our extended model supports careful problem specification (including both safety and progress properties), unambiguous system description, verification and analysis. Both safety and progress properties of algorithms may be shown using standard proof techniques (e.g., invariant assertions and variant functions). For example, these techniques have been used within the extended model for proving the correctness of Dijkstra's classical shared memory mutual exclusion algorithm [7].

Although the shared memory extensions do expand the capabilities of the I/O automaton model to include support for shared memory algorithms, the major benefit of a unified model that supports both atomic shared memory and message passing is not merely the ability to reason about shared memory algorithms and message passing algorithms with the same set of tools. The major benefit is the ability to combine shared memory and message passing in a single formal setting. For example, the extended model has been used as the basis of a new methodology for reasoning about recursive distributed algorithms in which each recursive invocation of an algorithm is modeled as a separate automaton using dynamic process creation. The various recursive instantiations of the algorithm on a given processor communicate with their corresponding instantiations on other processors through message passing, and they communicate among themselves through shared memory [17].

In addition, a unified model provides the ability to describe systems that use both shared memory and message passing communication. For example, systems like the Alewife multiprocessor [1] or the Split-C language [5] implement a global shared memory abstraction using a combination of message passing between processors and shared memory accesses between threads (or handlers) on a single processor. Reasoning about the behavior of these systems requires a mixture of shared memory and message passing semantics. Another class of systems that mix message passing and shared memory are programs (typically scientific applications) implemented on a heterogeneous network of workstations and multiprocessors. Within a multiprocessor, communication may be done using shared memory, while communicating across the network involves message passing. Numerous examples of systems exist to support such heterogeneous network computing, with one of the most popular being PVM [6].

Perhaps one of the most important benefits of a unified model is that of providing a context in which to understand and prove correspondences between shared memory and message passing systems. We emphasize that both shared memory and message passing are modelled *directly*; in no sense is one "implemented" on top of the other. Therefore, one may describe both kinds of systems using the primitives of the model, and then formally relate the two.

To illustrate this benefit of our unified model, we consider the problem of simulating an atomic shared memory in a distributed system where message passing is the physical means of communica-

<sup>&</sup>lt;sup>1</sup>The ability to closeout with respect to a subset of the shared variables (as opposed to the entire set) may be likened to lexical scoping of variable declarations in a conventional programming language.

tion. The motivation for simulating an atomic shared memory system on a message passing system is that algorithms described using atomic accesses to shared memory are easy to reason about, since one is not concerned with the possible interleavings of invocations and responses for object access. However, the invocation-response approach, in which the invocation of an operation on an object and the corresponding response are modelled as separate atomic steps, fits more naturally with multiprocessor architectures and often supports greater concurrency. Thus, an important problem in multiprocessor algorithm design is to carefully construct the processes and objects in such a way that any the invocation-response system "simulates" an atomic access system. One approach to this problem has been advanced by Herlihy and Wing [8]. They propose a property of objects, called *linearizability*, that permits one to construct invocation-response systems, and then to reason about only those executions in which each response immediately follows the corresponding invocation.

We exercise the unified model resulting from our shared memory extensions by proving a useful relationship between the invocation-response approach and the atomic access approach in the context of linearizable objects. In addition, we extend the work of Herlihy and Wing by treating not only safety properties of invocation-response systems, but liveness properties as well. The proof rests on a simulation argument, namely that systems of linearizable objects "simulate" atomic shared memory systems. The unified model assists us in this proof possible because we are able to express both the invocation-response system and the atomic shared memory system within the same model, and thereby are able to relate the two.

The remainder of the paper is organized as follows. In Section 2, we review the I/O automaton model. We define our extensions for shared memory in Section 3 and show some important properties that follow from these definitions. Next, in Section 4, we use the extended model to establish a formal relationship between invocation-response systems and atomic access systems. The paper concludes with a summary and discussion.

# 2 The I/O Automaton Model

The I/O automaton model of Lynch and Tuttle [15, 16] is the starting point for this work. One of the I/O automaton model's distinguishing features is the clear separation of input and output actions. This will be particularly important for our shared memory extensions for two reasons. First, the fact that each action is under the control of exactly one component means that simply by using output actions to model updates to the shared memory, we capture the notion of a single module making an atomic update to shared memory (without any active participation by other modules). Second, the fact that input actions are always enabled means that we can write modules that passively observe the shared memory accesses by others without interfering. Other features of the model important to us are its treatment of fairness and its compositionality properties.

Before describing our extensions to the I/O automaton model, we present a brief introduction to the I/O automaton model. This brief introduction is adapted from [16], which explains the model in more detail, presents examples, and includes comparisons to other models.

#### 2.1 I/O Automata

I/O automata are best suited for modelling systems in which the components operate asynchronously. Each system component is modeled as an I/O automaton, which is essentially a nondeterministic (possibly infinite state) automaton with an action labeling each transition. An automaton's actions are classified as either 'input', 'output', or 'internal'. An automaton can establish restrictions on when it will perform an output or internal action, but it is unable to block the performance of an input action. An automaton is said to be *closed* if it has no input actions; it models a closed system that does not interact with its environment.

Formally, an action signature S is a partition of a set acts(S) of actions into three disjoint sets in(S), out(S), and int(S) of input actions, output actions, and internal actions, respectively. We denote by  $ext(S) = in(S) \cup out(S)$  the set of external actions. We denote by  $local(S) = out(S) \cup int(S)$  the set of locally-controlled actions. An I/O automaton consists of five components:

- an action signature sig(A),

- a set states(A) of states,

- a nonempty set  $start(A) \subseteq states(A)$  of start states,

- a transition relation  $steps(A) \subseteq states(A) \times acts(A) \times states(A)$  with the property that for every state s' and input action  $\pi$  there is a transition  $(s', \pi, s)$  in steps(A), and

- an equivalence relation part(A) partitioning the set local(A) into at most a countable number of equivalence classes.

The equivalence relation part(A) will be used in the definition of fair computation. Each class of the partition may be thought of as a separate process. We refer to an element  $(s', \pi, s)$  of steps(A) as a step of A. If  $(s', \pi, s)$  is a step of A, then  $\pi$  is said to be *enabled* in s'. Since every input action is enabled in every state, automata are said to be *input-enabled*. This means that the automaton is unable to block its input.

An execution of A is a finite sequence  $s_0, \pi_1, s_1, \ldots, \pi_n, s_n$  or an infinite sequence  $s_0, \pi_1, s_1, \pi_2, \ldots$ of alternating states and actions of A such that  $(s_i, \pi_{i+1}, s_{i+1})$  is a step of A for every i and  $s_0 \in start(A)$ . The schedule of an execution  $\alpha$  is the subsequence of  $\alpha$  consisting of the actions appearing in  $\alpha$ . The behavior of an execution or schedule  $\alpha$  of A is the subsequence of  $\alpha$  consisting of external actions. The sets of executions, finite executions, schedules, finite schedules, behaviors, and finite behaviors are denoted execs(A), finexecs(A), scheds(A), finscheds(A), behs(A), and finbehs(A), respectively. The same action may occur several times in an execution or a schedule; we refer to a particular occurrence of an action as an event.

The separation of input and output actions will be important in our shared memory extensions for two reasons. First, the fact that each action is under the control of exactly one component means that by simply using actions to model updates to the shared memory, we capture the notion of a single module making an atomic update to shared memory (without any active participation by other modules). Second, the fact that input actions are always enabled means that we can use shared memory input actions to construct modules that passively observe the shared memory accesses by others without interfering.

#### 2.2 Composition

We can construct an automaton modelling a complex system by composing automata modelling the simpler system components. When we compose a collection of automata, we identify an output action  $\pi$  of one automaton with the input action  $\pi$  of each automaton having  $\pi$  as an input action. Consequently, when one automaton having  $\pi$  as an output action performs  $\pi$ , all automata having  $\pi$  as an action perform  $\pi$  simultaneously (automata not having  $\pi$  as an action do nothing).

Since we require that at most one system component controls the performance of any given action, we must place some compatibility restrictions on the collections of automata that may be composed. A countable collection  $\{S_i\}_{i \in I}$  of action signatures is said to be *strongly compatible* if for all  $i, j \in I$  satisfying  $i \neq j$  we have

- 1.  $out(S_i) \cap out(S_j) = \emptyset$ ,

- 2.  $int(S_i) \cap acts(S_j) = \emptyset$ , and

- 3. no action is contained in infinitely many sets  $acts(S_i)$ .

We say that a collection of automata are *strongly compatible* if their action signatures are strongly compatible.

The composition  $S = \prod_{i \in I} S_i$  of a countable collection of strongly compatible action signatures  $\{S_i\}_{i \in I}$  is defined to be the action signature with

- $in(S) = \bigcup_{i \in I} in(S_i) \bigcup_{i \in I} out(S_i),$

- $out(S) = \bigcup_{i \in I} out(S_i)$ , and

- $int(S) = \bigcup_{i \in I} int(S_i)$ .

The composition  $A = \prod_{i \in I} A_i$  of a countable collection of strongly compatible automata  $\{A_i\}_{i \in I}$  is the automaton defined as follows:<sup>2</sup>

- $sig(A) = \prod_{i \in I} sig(A_i),$

- $states(A) = \prod_{i \in I} states(A_i),$

- $start(A) = \prod_{i \in I} start(A_i),$

- steps(A) is the set of triples  $(\vec{s_1}, \pi, \vec{s_2})$  such that, for all  $i \in I$ , if  $\pi \in acts(A_i)$  then  $(\vec{s_1}[i], \pi, \vec{s_2}[i]) \in steps(A_i)$ , and if  $\pi \notin acts(A_i)$  then  $\vec{s_1}[i] = \vec{s_2}[i]$ , and

- $part(A) = \bigcup_{i \in I} part(A_i).$

Given an execution  $\alpha = \vec{s_0}\pi_1\vec{s_1}\dots$  of A, let  $\alpha|A_i$  (read " $\alpha$  projected on  $A_i$ ") be the sequence obtained by deleting  $\pi_j\vec{s_j}$  when  $\pi_j \notin acts(A_i)$  and replacing the remaining  $\vec{s_j}$  by  $\vec{s_j}[i]$ .

#### 2.3 Fairness

Of all the executions of an I/O automaton, we are primarily interested in the 'fair' executions those that permit each of the automaton's primitive components (i.e., its classes or processes) to have infinitely many chances to perform output or internal actions. The definition of automaton composition says that an equivalence class of a component automaton becomes an equivalence class of a composition, and hence that composition retains the essential structure of the system's primitive components. In the model, therefore, being fair to each component means being fair to each equivalence class of locally-controlled actions. A *fair execution* of an automaton A is defined to be an execution  $\alpha$  of A such that the following conditions hold for each class C of *part*(A):

- 1. If  $\alpha$  is finite, then no action of C is enabled in the final state of  $\alpha$ .

- 2. If  $\alpha$  is infinite, then either  $\alpha$  contains infinitely many events from C, or  $\alpha$  contains infinitely many occurrences of states in which no action of C is enabled.

<sup>&</sup>lt;sup>2</sup>Here start(A) and states(A) are defined in terms of the ordinary Cartesian product, while sig(A) is defined in terms of the composition of actions signatures just defined. Also, we use the notation  $\vec{s}[i]$  to denote the *i*th component of the state vector  $\vec{s}$ .

We denote the set of fair executions of A by fairexecs(A). We say that  $\beta$  is a fair behavior of A if  $\beta$  is the behavior of a fair execution of A, and we denote the set of fair behaviors of A by fairbehs(A). Similarly,  $\beta$  is a fair schedule of A if  $\beta$  is the schedule of a fair execution of A, and we denote the set of fair schedules of A by fairscheds(A).

The definitions of composition and fairness imply certain natural relationships between the (fair) executions of a composition and the (fair) executions of the individual components. For example, the following lemma from [16] states that (fair) executions of component automata can often be pasted together to form a (fair) execution of the composition.

Lemma 1: Let  $\{A_i\}_{i\in\mathcal{I}}$  be a strongly compatible collection of automata and let  $A = \prod_{i\in\mathcal{I}}A_i$ . Suppose  $\alpha_i$  is a (fair) execution of  $A_i$  for every  $i \in I$ , and suppose  $\beta$  is a sequence of actions in acts(A) such that  $\beta|A_i = sched(\alpha_i)$  for every  $i \in \mathcal{I}$ . Then there is an (fair) execution  $\alpha$  of A such that  $\beta = sched(\alpha)$  and  $\alpha_i = \alpha|A_i$  for every  $i \in \mathcal{I}$ . Moreover, the same result holds when *acts* and *sched* are replaced by *ext* and *beh*, respectively.

#### 2.4 Problem Specification

A 'problem' to be solved by an I/O automaton is formalized as a set of (finite and infinite) sequences of external actions. An automaton is said to *solve* a problem P provided that its set of fair behaviors is a subset of P. Although the model does not allow an automaton to block its environment or eliminate undesirable inputs, we can formulate our problems (i.e., correctness conditions) to require that an automaton exhibits some behavior only when the environment observes certain restrictions on the production of inputs.

We want a problem specification to be an interface together with a set of behaviors. We therefore define a schedule module H to consist of two components, an action signature sig(H), and a set scheds(H) of schedules. Each schedule in scheds(H) is a finite or infinite sequence of actions of H. Subject to the same restrictions as automata, schedule modules may be composed to form other schedule modules. The resulting signature is defined as for automata, and the schedules scheds(H) is the set of sequences  $\beta$  of actions of H such that for every module H' in the composition,  $\beta|H'$  is a schedule of H'.

It is often the case that an automaton behaves correctly only in the context of certain restrictions on its input. A useful notion for discussing such restrictions is that of a module 'preserving' a property of behaviors. A set of sequences  $\mathcal{P}$  is said to be *prefix-closed* if  $\beta \in \mathcal{P}$  whenever both  $\beta$ is a prefix of  $\alpha$  and  $\alpha \in \mathcal{P}$ . A module M (either an automaton or schedule module) is said to be *prefix-closed* provided that *finbehs*(M) is prefix-closed. Let M be a prefix-closed module and let  $\mathcal{P}$ be a nonempty, prefix-closed set of sequences of actions from a set  $\Phi$  satisfying  $\Phi \cap int(M) = \emptyset$ . We say that M preserves  $\mathcal{P}$  if  $\beta \pi | \Phi \in \mathcal{P}$  whenever  $\beta | \Phi \in \mathcal{P}, \pi \in out(M), \text{ and } \beta \pi | M \in finbehs(M)$ . Informally, a module preserves a property  $\mathcal{P}$  iff the module is not the first to violate  $\mathcal{P}$ : as long as the environment only provides inputs such that the cumulative behavior satisfies  $\mathcal{P}$ . One can prove that a composition preserves a property by showing that each of the component automata preserves the property.

## 3 Shared Memory Definitions

In this section, we present a set of definitions that extends the I/O automaton model in order to allow modelling shared memory algorithms. We do not redefine any concepts, but simply add new concepts to the existing model. We model each system component that accesses shared memory as

a restricted I/O automaton called a "shared memory automaton". The fact that shared memory automata are simply special cases of I/O automata means that all the standard definitions and properties of I/O automata (e.g., composition and fairness) can be used directly in descriptions and proofs of shared memory algorithms.

#### 3.1 Variables

We will model shared memory in terms of a collection of variables, so the first step is to define what is meant by a variable. We define a variable x to have a domain dom(x) of values and an initial value  $init(x) \in dom(x)$ . Given a set X of variables, we model a state of X by an assignment mapping for X, denoted  $f_X$ , that maps each variable  $x \in X$  to a value in dom(x). We let  $F_X$  denote the set of all possible assignment mappings for X. We define init(X) to be the assignment mapping  $f_X \in F_X$  such that  $\forall x \in X, f_X(x) = init(x)$ . If X and Y are sets of variables such that  $Y \subseteq X$ , we define  $f_X|Y$  to be the assignment mapping  $f_Y \in F_Y$  such that for all  $y \in Y, f_Y(y) = f_X(y)$ . If X and Y are disjoint sets of variables, and  $S_X, S_Y$  are sets of assignment mappings for X and Y, respectively, then we define  $S_X \circ S_Y$  to be the set of assignment mappings S for  $X \cup Y$  such that for all  $s \in S, s|X \in S_X$  and  $s|Y \in S_Y$ . As shorthand, we may represent a singleton set of assignment mappings by its only element. For example, if  $f_X$  is an assignment mapping for X, we write  $f_X \circ S_Y$ instead of  $\{f_X\} \circ S_Y$ . Analogously, for  $f_X \in F_X$  and  $f_Y \in F_Y$ , we let  $f_X \circ f_Y$  represent its only element when it is clear from context that a mapping (rather than a set of mappings) is called for. If  $f \in F_X, x \in X$ , and  $v \in dom(x)$ , we define  $f_{[x=v]}$  to be the assignment mapping f' such that  $f'|(X - \{x\}) = f|(X - \{x\})$  and f'(x) = v.

#### 3.2 Shared Memory Actions

Since the only "sharing" that occurs in the I/O automaton model is the sharing of actions, we construct shared memory on top of the existing shared action mechanism. We begin by defining a special type of action called a "shared memory action" that will be used to model accesses to the shared variables. In some sense, this is the reverse of what is often done to incorporate message passing into a shared memory model. In UNITY [4], for example, shared queue variables are declared to model "channels" and atomic accesses to these shared queues model "sending" and "receiving" data across the channels. However, we emphasize that we do *not* implement shared memory on top of message passing. Rather, both are modelled directly in terms of the shared action mechanism.

We fix  $\mathcal{L}$ , a universal set of access labels. Let X be a set of variables. We define a shared memory action for X to be a triple of the form  $(f'_X, a, f_X)$ , where  $f'_X, f_X \in F_X$  and  $a \in \mathcal{L}^3$  We let sm-acts(X) denote the set of all possible shared memory actions for X. We say that  $\pi$  is a shared memory action iff it is a shared memory action for some X. We say  $\sigma$  is a shared memory step (for X) iff its contained action is a shared memory action (for X).

To construct signatures for shared memory automata, we need the following technical definition. Let II be a set of actions and X a set of variables. We say that II is *complete* for X iff  $\forall \pi \in \Pi$ , if  $\pi = (f'_X, a, f_X)$  is a shared memory action for X, then  $\forall \hat{f'_X}, \hat{f_X} \in F_X, (\hat{f'_X}, a, \hat{f_X}) \in \Pi$ .

Let X and Y be sets of variables such that  $Y \subseteq X$ . If  $\pi = (f'_X, a, f_X)$  is a shared memory action for X, we define its projection on Y, denoted  $\pi | Y$ , to be  $(f'_X | Y, a, f_X | Y)$ , a shared memory action for Y. If  $\beta$  is a sequence of actions, all of whose shared memory actions are shared memory actions for X, then we define  $\beta | Y$  to be the sequence that results from replacing each shared memory action of  $\beta$  by its projection on Y. Projections on sets of shared memory actions, signatures

<sup>&</sup>lt;sup>3</sup>These triples are action names, not to be confused with the steps of an automaton.

containing shared memory actions, and sets of sequences containing shared memory actions are defined analogously. If  $\sigma = (s', \pi, s)$  is a step with  $\pi$  a shared memory action for X, then  $\sigma|Y$  is defined to be  $(s', \pi|Y, s)$ .

#### 3.3 Shared Memory Automata

Let X be a set of variables, and let A be an I/O automaton all of whose shared memory actions are external shared memory actions for X. Let *shared-in*(A) denote the set of shared memory actions that are inputs to A, and let *shared-out*(A) denote the shared memory actions that are outputs of A. We say that A is a *shared memory automaton for* X iff it satisfies the following conditions:

- 1. The sets of actions shared-in(A) and shared-out(A) are each complete for X.

- 2. For all steps  $(s', (f'_X, a, f_X), s) \in steps(A)$ , if  $(f'_X, a, f_X) \in shared-out(A)$ , then for all  $\hat{f'_X} \in F_X$ , there exists a state  $\hat{s}$  and some  $\hat{f_X} \in F_X$ such that  $(s', (\hat{f'_X}, a, \hat{f_X}), \hat{s}) \in steps(A)$ .

- 3. In the equivalence relation part(A), any two output actions  $(f'_X, a, f_X)$  and  $(\hat{f'_X}, a, \hat{f_X})$  are elements of the same equivalence class.

The first condition says that if A has a shared memory action with a given label a, then it has all possible shared memory actions with label a. For input actions, this means that A must be prepared to handle any value it may observe in the shared variables (since inputs are always enabled). For output actions, this condition is simply a technical restriction that makes composition of shared memory automata work out properly, as we will see later. The condition also makes describing the signatures of shared memory automata more convenient, since we need not list all the allowable values of the shared variables for each shared memory action label used.

The second condition says that for each shared memory output step, there exists a step from the same state for each possible assignment of the shared variables. In essence, this says that the preconditions of an output action may not depend on the values of the shared variables. This corresponds with the notion that one cannot observe the values of shared variables except by accessing them, and that one must be prepared to handle any value that might be observed.

The third condition says that the equivalence class membership of an output action may not depend upon the values of the external variables. This is a technical condition that prevents a nonsensical situation in which executions must be "fair" to the different values of the shared variables.

Since a shared memory automaton is an I/O automaton, all the standard I/O automaton definitions for executions, schedules, behaviors, composition, and fairness carry over to shared memory automata.

**Theorem 2:** The composition of a strongly compatible collection of shared memory automata for X is a shared memory automaton for X.

**Proof:** We know that the composition of a strongly compatible collection of I/O automata is an I/O automaton. Furthermore, since external actions of the components are external actions of the composition, we know that all of the shared memory actions are external actions in the composition. All of these are shared memory actions for X. It remains to be shown that the composition satisfies the three conditions imposed on shared memory automata for X. Condition 1 holds, since the union of complete sets of actions is clearly a complete set. For condition 2, we note that composition does not introduce any new output actions, nor does it remove any existing output actions. Furthermore, input-enabling and the definition of composition imply that for each output step  $(s'_i, \pi, s_i)$  of a component  $\mathcal{A}_i$ , for all states s' of the composition  $\mathcal{A}$ , if  $s'|\mathcal{A}_i = s'_i$ , then there exists a state s of  $\mathcal{A}$  such that  $(s', \pi, s)$  is a step of  $\mathcal{A}$ . Thus, Condition 2 holds. Since the equivalence relation of the composition is the union of the individual equivalence relations of the components, any two actions in the same equivalence class in a component are in the same equivalence class in the composition. Since the set of shared memory output actions for each component is complete, strong compatibility assures us that no two shared memory output actions with the same label occur in different classes of the composition. This guarantees Condition 3.

So far, we have given a general set of definitions for modelling collections of modules that access shared memory. Our accesses allow a module to atomically read the entire contents of memory, perform some local computation (possibly resulting in a state transition), and update the entire contents of shared memory. This general type of shared memory access is, of course, an expensive operation to implement. Therefore, we would like to define systems in which the shared memory accesses are more restricted. For example, in the most restricted case, we might only allow read or write accesses to single shared variables.

Let A be a shared memory automaton for X, let a be an access label of A, and let  $x \in X$ . We say that a is a

- 1. read access to x iff  $\forall (s', (f', a, f), s) \in steps(A)$ ,

- (a) f = f' and

- (b)  $\forall \hat{f} \in F_X$  such that  $\hat{f}(x) = f'(x), (s', (\hat{f}, a, \hat{f}), s) \in steps(A)$ .

- 2. write access to x with value v iff  $\forall (s', (f', a, f), s) \in steps(A)$ ,

(a)

$$f = f'_{[x=v]}$$

and

(b)

$$\forall \hat{f} \in F_X, (s', (\hat{f}, a, \hat{f}_{[x=v]}), s) \in steps(A)$$

In a read access to x, the shared memory is unmodified and the new state of A depends only upon the value observed in variable x. In a write access to x, the "before" and "after" states of shared memory differ only in the value of variable x, and the new state of A and the new value of x are independent of the "before" state of shared memory.

We now define a restricted class of shared memory automata called "single-variable read-write automata." In such automata, each access label for a shared memory output is constrained to be a read access or a write access to a single variable. Let A be a shared memory automaton for X, and let  $\psi$  be a partition of the access labels for actions in *shared-out*(A) such that there exist exactly two classes in  $\psi$  for each variable in  $x \in X$ , denoted  $\psi_r(x)$  and  $\psi_w(x)$ . The partition  $\psi$  is called the *access partition* of A. We say that A is a *single-variable read-write automaton under*  $\psi$  iff  $\forall x \in X$ ,  $\psi_r(x)$  contains only read accesses to x and  $\psi_w(x)$  contains only write accesses to x. We say that such an automaton *can read* x iff  $\psi_r(x)$  is nonempty, and *can write* x iff  $\psi_w(x)$  is nonempty. If Q is a collection of single-variable read-write automata, then a component of Q is said to *own* a variable x if it is the only component that can write x; in this case, x is said to be a *single-writer* variable. *Multi-writer, single-reader*, and *multi-reader* variables are defined in the obvious way.

Other classes of shared memory automata could be constructed in a similar manner. For example, one might define test-and-set or memory-to-memory-swap accesses and define automata in which the access labels are appropriately partitioned into additional classes. In fact, this style of definition can be used to define shared memory accesses for operations on arbitrary data types, such as enqueue and dequeue. Of course, any shared memory algorithm could be expressed and studied using the general shared memory automaton definition only, but being specific about the types of shared memory accesses allowed makes the assumptions about the underlying shared memory more explicit, and also may help simplify reasoning about the algorithm.

Notice that by exposing the values of the shared variables as part of the shared memory accesses, we not only carry forward the compositionality properties of I/O automaton behaviors but also provide a useful notion of a shared memory action as an input. We expect normal communication through shared variables to be modeled using output actions only, but the input actions allow a module to passively observe the accesses to shared memory made by other processes. We see two potential uses for this feature. First, one might use shared memory actions as inputs to construct external processes that are not part of the algorithm but monitor the use of shared memory (possibly as a means to check algorithms in a simulation system). Second, in a modular algorithm design, it may be appropriate to divide a task into several I/O automaton components such that only one component accesses the shared memory while the others are kept "informed" of these accesses by receiving them as inputs (e.g., to model a collection of processes "snooping" on a memory bus to update local caches).

#### 3.4 Augmentation and Augmented-Composition

In building up I/O automaton systems, we may wish to compose collections of shared memory automata having different (either intersecting or disjoint) sets of shared variables. We would like the result of this composition to be a shared memory automaton for Z, where Z is the union of the sets of shared variables of the automata being composed. In order to accomplish this, we first "augment" each of the automata with additional shared variables so that its set of shared variables is Z. Then we compose as usual.<sup>4</sup>

We now define what is meant by augmenting an automaton. Let X and Z be sets of variables, with  $X \subseteq Z$ . Given a shared memory automaton A for X, we define augment(A, Z), read "the augmentation of A to Z," to be the automaton B as follows:

- $in(B) = \{\pi \in sm\text{-}acts(Z) : \pi | X \in shared\text{-}in(A)\} \cup (in(A) shared\text{-}in(A)).$

- $out(B) = \{\pi \in sm\text{-}acts(Z) : \pi | X \in shared\text{-}out(A)\} \cup (out(A) shared\text{-}out(A)).$

- int(B) = int(A).

- states(B) = states(A).

- start(B) = start(A).

- $steps(B) = all steps \sigma = (s', \pi, s)$  such that either

- 1.  $\sigma \in steps(A)$  and  $\pi$  is not a shared memory action, or

- 2.  $\sigma | X \in steps(A)$  and  $\pi \in shared-in(B)$ , or

- 3.  $\sigma | X \in steps(A), \pi = (f'_Z, a, f_Z) \in shared-out(B), \text{ and } f'_Z | (Z X) = f_Z | (Z X).$

- $part(B) = \{C \subseteq local(B) : C | X \in part(A)\}$  such that part(B) forms a partition of the locally-controlled actions of B.

<sup>&</sup>lt;sup>4</sup>When composing a shared memory automaton with an "ordinary" I/O automaton, no augmentation is necessary, since an ordinary I/O automaton is by definition an SMA for any set of variables X.

Essentially, we augment A by making the signature complete for Z, while leaving the set of states unchanged. For each step involving a shared memory action  $\pi$  for X, we substitute the set of all steps in which  $\pi$  is replaced by a shared memory action for Z (call it  $\pi'$ ) such that  $\pi'|X = \pi$ . For output actions steps, we make the further restriction that if  $\pi' = (f'_Z, a, f_Z)$ , then  $f'_Z$  and  $f_Z$  differ only in their assignments to the variables of X. This models the fact that outputs of B only change the values of shared variables in X. We do not make this restriction for input actions because they are always enabled. This also highlights the fact that the shared memory accesses of B are independent of all shared variables other than those in X. The partition of B is constructed from that of A to reflect the differences in their signatures.

**Theorem 3:** Let X and Z be sets of variables, with  $X \subseteq Z$ , and let A be a shared memory automaton for X. Then augment(A, Z) is a shared memory automaton for Z.

*Proof:* Immediate from the definitions of augmentation and shared memory automata.

Our next result, Theorem 6, says that augmentation does not (in any significant way) affect the behavior of an automaton. This is proved using the following lemmas.

Lemma 4: Let X and Z be sets of variables such that  $X \subseteq Z$ . If A is a shared memory automaton for X and  $\alpha_A$  is an execution of A, then there exists an execution  $\alpha_B$  of B = augment(A, Z) such that  $\alpha_B | X = \alpha_A$ .

Proof: Clearly, if  $\alpha_A$  contains no actions, the claim holds. For the inductive hypothesis, let  $\alpha_A = \alpha'_A \pi_A s$  be an execution of A, and let  $\alpha'_B$  be the execution of B such that  $\alpha'_B | X = \alpha'_A$ . Clearly the state of A after  $\alpha'_A$  is the same as the state of B after  $\alpha'_B$ . Let this state be s'. It remains to be shown that some  $\pi_B$  is enabled from s' in B, resulting in state s, where  $\pi_B | X = \pi_A$ . If  $\pi_A$  is not a shared memory action, then the result is trivial, since the steps of A and B differ only with respect to shared memory actions. If  $\pi_A$  is a shared memory action  $(f'_X, a, f_X)$ , then by the definition of augmentation, there must be a step  $(s', \pi_B = (f'_Z, a, f_Z), s) \in steps(B)$  such that  $\pi_B | X = \pi_A$ .

Lemma 5: Let X and Z be sets of variables such that  $X \subseteq Z$ . If A is a shared memory automaton for X and  $\alpha_B$  is an execution of B = augment(A, Z), then there exists an execution  $\alpha_A$  of A such that  $\alpha_A = \alpha_B | X$ .

**Proof:** If  $\alpha_B$  has no actions, the claim holds. For the inductive hypothesis, let  $\alpha_B = \alpha'_B \pi_B s$  be an execution of B, and let  $\alpha'_A$  be the execution of A such that  $\alpha'_A | X = \alpha'_A$ . Clearly the state of B after  $\alpha'_B$  is the same as the state of A after  $\alpha'_A$ . Let this state be s'. It remains to be shown that some  $\pi_A$  is enabled from s' in A, resulting in state s, where  $\pi_A = \pi_B | X$ . If  $\pi_B$  is not a shared memory action, then the result is trivial as before. If  $\pi_B$  is a shared memory action  $(f'_Z, a, f_Z)$ , then by the definition of augmentation, the step  $(s', (f'_Z | X, a, f_Z | X), s) \in steps(A)$ . Therefore, the second claim holds.

**Theorem 6:** Let X and Z be sets of variables such that  $X \subseteq Z$ . If A is a shared memory automaton for X, then

- 1. behs(augment(A, Z))|X = behs(A), and

- 2. fairbehs(augment(A, Z))|X = fairbehs(A).

Proof: Part 1 is immediate from Lemmas 4 and 5.

For Part 2, let  $\alpha_A$  be a fair execution of A, and let  $\beta_A = beh(\alpha_A)$ . From Lemma 4, we know that there exists an execution  $\alpha_B$  of B = augment(A, Z) such that  $\alpha_B|_X = \alpha_A$ . To show that

$\alpha_B$  is fair, we apply the definition of augmentation. From the construction of steps(B), a shared memory action  $\pi \in acts(B)$  is enabled in state s of B only if  $\pi | X$  is enabled in state s of A. The remaining actions  $\pi \in acts(B)$  are enabled in in state s of B only if  $\pi$  is enabled in state s of A. Furthermore, any two actions  $\pi$  and  $\pi'$  are in the same equivalence class of B iff  $\pi | X$  and  $\pi' | X$  are in the same equivalence class of A. So, since  $\alpha_A$  is fair,  $\alpha_B$  is fair.

Now, to show the other direction, let  $\alpha_B$  be a fair execution of B. By Lemma 5, there exists an execution  $\alpha_A$  of A such that  $\alpha_A = \alpha_B | X$ . To show that  $\alpha_A$  is fair, we argue similarly to above.

We can now define augmented-composition, making use of the augmentation definition and standard I/O automaton composition.

Augmented-Composition: Let  $\{X_i\}_{i\in I}$  be a collection of (not necessarily disjoint) sets of variables, let  $Z = \bigcup_{i\in I} X_i$ , let each  $A_i$  be a shared memory automaton for  $X_i$ , and let the collection  $\{augment(A_i)\}_{i\in I}$  be strongly compatible. We define the *augmented composition*  $\prod_{i\in I}^+ A_i$  to be the ordinary I/O automaton composition  $\prod_{i\in I}^+ augment(A_i, Z)$ .

**Theorem 7:** Let  $\{X_i\}_{i \in I}$  be a collection of (not necessarily disjoint) sets of variables, let  $Z = \bigcup_{i \in I} X_i$ , let each  $A_i$  be a shared memory automaton for  $X_i$ , and suppose that the collection of automata  $\{augment(A_i, Z)\}_{i \in I}$  is strongly compatible. Then the augmented composition  $\prod_{i \in I}^+ A_i$  is a shared memory automaton for Z.

*Proof:* By Theorem 3, for each  $A_i$ ,  $augment(A_i, Z)$  is a shared memory automaton for Z. Therefore, by Theorem 2, the result holds.

The following three compositionality results follow immediately from the corresponding results in [16], together with Theorems 6 and 7. The first result says that an execution of an augmented-composition induces executions of the component shared memory automata.

Corollary 8: Let  $\{X_i\}_{i\in I}$  be a collection of sets of variables, where  $Z = \bigcup_{i\in I} X_i$ . Let  $\{A_i\}_{i\in I}$  be a collection of automata such that each  $A_i$  is a shared memory automaton for  $X_i$ . Let the collection of automata  $\{augment(A_i, Z)\}_{i\in I}$  be strongly compatible, and let  $A = \prod_{i\in I}^+ A_i$ . If  $\alpha \in execs(A)$  then  $(\alpha|augment(A_i, Z))|X_i \in execs(A_i)$  for every  $i \in I$ . Moreover, the same result holds if execs() is replaced by fairexecs(), scheds(), fairscheds(), behs(), or fairbehs().

The next result says that executions of component shared memory automata can often be pasted together to form an execution of the augmented-composition.

Corollary 9: Let  $\{X_i\}_{i \in I}$  be a collection of sets of variables, where  $Z = \bigcup_{i \in I} X_i$ . Let  $\{A_i\}_{i \in I}$  be a collection of automata such that each  $A_i$  is a shared memory automaton for  $X_i$ . Let the collection of automata  $\{augment(A_i, Z)\}_{i \in I}$  be strongly compatible, and let  $A = \prod_{i \in I}^+ A_i$ . Suppose  $\alpha_i$  is a (fair) execution of  $A_i$  for every  $i \in I$ , and let  $\beta$  be a sequence of actions in acts(A) such that  $(\beta|augment(A_i, Z))|X_i = sched(\alpha_i)$  for every  $i \in I$ . Then there is a (fair) execution  $\alpha$  of A such that  $\beta = sched(\alpha)$  and  $\alpha_i = (\alpha|augment(A_i, Z))|X_i$  for every  $i \in I$ . Moreover, the same result holds when acts() and scheds() are replaced by ext() and beh().

Finally, schedules and behaviors of component shared memory automata can also be pasted together to form schedules and behaviors of the augmented-composition.

Corollary 10: Let  $\{X_i\}_{i \in I}$  be a collection of sets of variables, where  $Z = \bigcup_{i \in I} X_i$ . Let  $\{A_i\}_{i \in I}$  be a collection of automata such that each  $A_i$  is a shared memory automaton for  $X_i$ . Let the collection of automata  $\{augment(A_i, Z)\}_{i \in I}$  be strongly compatible, and let  $A = \prod_{i \in I}^+ A_i$ . Let  $\beta$

be a sequence of actions in acts(A). If  $(\beta|augment(A_i, Z))|X_i \in scheds(A_i)$  for every  $i \in I$ , then  $\beta \in scheds(A)$ . Moreover, the same result holds when acts() and scheds() are replaced by ext() and behs(), respectively, and similarly when replaced by acts() and fairscheds() or by ext() and fairbehs().

#### 3.5 The Closeout Operator

So far, we have introduced shared memory actions to model accesses to shared variables, and we have defined a special kind of I/O automaton containing shared memory actions in its signature. We have interpreted the first triple of each action as the "before state" of shared memory and the third component as the "after state." However, we have not yet placed any restrictions on the the relationship between the "after state" of one shared memory action and the "before state" of the next. A shared memory automaton is *not* guaranteed that the value it writes to a given shared variable will be the value observed by the next system component reading that variable. In other words, we permit the environment to freely modify the values in shared memory. We would like to construct systems in which the set of components that may modify a particular shared variable is fixed, closed to the environment. We therefore define a "closeout" operator, which takes a shared memory automaton A and produces a new automaton B such that some or all of the shared variables of A become part of the local state of B. In this way, the "absorbed" variables can be touched only the by the actions of B. Since A may be the result of restricting shared variable accesses to a particular collection of system modules.

We now define the closeout operator C. Since the state of an automaton may be thought of as a mapping from a set of variables to a set of values, we will feel free to operate on states as if they were assignment mappings. Let X and Y be disjoint sets of variables, let  $Z = X \cup Y$ , and let A be a shared memory automaton for Z. We define B = C(A, X) as follows:

- sig(B) = sig(A)|Y

- $states(B) = states(A) \circ F_X$ ,

- $start(B) = start(A) \circ init(X)$ ,

- steps(B) contains exactly the following set of steps: for each step  $(s', \pi, s)$  in steps(A),

- 1. if  $\pi = (f'_Z, a, f_Z)$  is a shared memory action, then  $(s' \circ (f'_Z|X), (f'_Z|Y, a, f_Z|Y), s \circ (f_Z|X)) \in steps(B),$

- 2. if  $\pi$  is not a shared memory action, then  $\{(s' \circ f_X, \pi, s \circ f_X) : f_X \in F_X\} \subseteq steps(B)$ , and

- part(B) = part(A), where each class is projected on Y.

Essentially, the variables in X are absorbed into the internal state of the "closed out" automaton. If  $x \in X$ , we use the familiar record notation s.x to refer to the value of x in a particular state s of B. That is, if  $s_B = s_A \circ f_X$ , where  $s_A$  is a state of A, then  $s_B.x = f_X(x)$ .

Given the definition of the closeout operator, we get the following natural result.

**Theorem 11:** Let A be a shared memory automaton for Z and let X and Y be disjoint sets of variables such that  $Z = X \cup Y$ . Then B = C(A, X) is a shared memory automaton for Y.

*Proof:* To show that B is an I/O automaton, we must demonstrate that for all states s' and input actions  $\pi$  of B, there exists a state s' of B such that  $(s', \pi, s) \in steps(B)$ . Since this property

is true of A, and since shared-in(A) is complete, this property is also true of B by the construction of steps(B). (When we construct the steps of B, completeness of shared-in(A) guarantees that we include all possible values for X in the "before states" of the steps for each input action.)

We now show that I/O automaton B is a shared memory automaton for Y. Clearly, all the shared memory actions of B are external shared memory actions for Y. We now show that each of the three conditions in the definition of a shared memory automaton hold for B. For the first condition, since shared-in(A) is complete for Z, shared-in(B) = shared-in(A)|Y must be complete for Y. Similarly, for shared-out(B). The second condition requires that for every step  $(s', (f'_Y, a, f_Y), s)$ in steps(B), if  $(f'_Y, a, f_Y) \in shared-out(B)$ , then for all  $\hat{f}'_Y \in F_Y$ , there exists a state  $\hat{s}$  and some  $\hat{f}_Y \in F_Y$  such that  $(s', (\hat{f}'_Y, a, \hat{f}_Y), \hat{s})$  is in steps(B). Since this condition is true for A, we know that for each shared memory output action label a, there exists a step  $(s', (f'_X \circ f'_Y, a, f_X \circ f_Y), s)$  for every possible assignment mapping  $f'_X \circ f'_Y$  for Z. Therefore, when we project on Y in constructing steps(B), we have a step  $(s', (f'_Y, a, f_Y), s)$  for each possible assignment mapping  $f'_Y$  for Y. The third condition, regarding membership of equivalence classes, is obviously true of B.

#### 3.6 Closeout for behaviors

We now give a closeout definition for behaviors that is analogous to the one for automata.

Let X and Z be sets of variables with  $X \subseteq Z$ . If  $\beta$  is a sequence of actions of a shared memory automaton A for Z, then we say that  $\beta$  is consistent for X iff the following conditions hold:

- 1. if  $(f'_Z, a, f_Z)$  is the first shared memory action in  $\beta$ , then  $f'_Z|_X = init(X)$ , and

- 2. if  $(f_Z'', a_1, f_Z'')$  and  $(f_Z', a_2, f_Z)$  are shared memory actions in  $\beta$  such that no shared memory action occurs between them, then  $f_Z''|X = f_Z'|X$ .

If  $\Sigma$  is a set of sequences of actions of a shared memory automaton for Z, then we define  $\mathcal{C}(\Sigma, X)$  to be the set  $\Sigma_X|(Z-X)$ , where  $\Sigma_X$  is the subset of  $\Sigma$  containing exactly those sequences that are consistent for X.

Lemma 12: Let X and Z be sets of variables such that  $X \subseteq Z$ . Let A be a shared memory automaton for Z, and let  $\alpha_B$  be an execution of  $B = \mathcal{C}(A, X)$  with behavior  $\beta_B$ . Then there exists an execution  $\alpha_A$  of A, with behavior  $\beta_A$  consistent for X, such that  $\beta_A|(Z - X) = \beta_B$ .

*Proof:* Let Y = Z - X. We construct the sequence  $\alpha_A$  from  $\alpha_B$  as follows. For each step  $(s' \circ f'_X, \pi, s \circ f_X)$  in  $\alpha_B$ , if  $\pi = (f'_Y, a, f_Y)$  is a shared memory action of B, then we let the corresponding step in  $\alpha_A$  be  $(s', (f'_Y \circ f'_X, a, f_Y \circ f_X), s)$ ; and if  $\pi$  is not a shared memory action, we let the corresponding step in  $\alpha_A$  be  $(s', (f'_Y \circ f'_X, a, f_Y \circ f_X), s)$ ; and if  $\pi$  is not a shared memory action,

Let  $\beta_B = beh(\alpha_A)$ . Clearly,  $\beta_B|Y = \beta_A$ . It remains to be shown that  $\alpha_A$  is an execution of A and that  $\beta_A$  is consistent for X. We show that  $\alpha_A$  is an execution of A by showing that each step of  $\alpha_A$  is in steps(A). Let  $\sigma = (s' \circ f'_X, \pi, s \circ f_X)$  be a step of B. If  $\pi = (f'_Y, a, f_Y)$  is a shared memory action of B, then by the construction of steps(B) in the definition of closeout,  $(s', (f'_Y \circ f'_X, a, f_Y \circ f_X), s)$  must be a step of A. Similarly, if  $\pi$  is not a shared memory action, then  $(s', \pi, s)$  must be a step of A. Therefore, the construction produces an execution of A.

Finally, we show that  $\beta_A$  is consistent for X. Since every initial state of  $\mathcal{C}(A, X)$  is in  $states(A) \circ init(X)$ , it must be that the first shared memory action  $(f'_Z, a, f_Z)$  of  $\beta_B$  has  $f'|_X = init(X)$ , so the first consistency condition is satisfied. We know that the second consistency condition must be satisfied, since any two successive steps  $(s'', \pi_1, s'')$  and  $(s', \pi_2, s)$  of any execution must have s'' = s', the assignments to the variables of X are part of the state of  $\mathcal{C}(A, X)$ , and the only actions that may change the values for X in the state of  $\mathcal{C}(A, X)$  correspond to shared memory actions for Z.

Lemma 13: Let X and Z be sets of variables such that  $X \subseteq Z$ . Let A be a shared memory automaton for Z and let  $\alpha_A$  be an execution of A with behavior  $\beta_A$ . If  $\beta_A$  is consistent for X, then there exists an execution  $\alpha_B$  of B = C(A, X) such that  $\beta_A | (Z - X)$  is the behavior of  $\alpha_B$ .

*Proof:* Let Y = Z - X. Let  $\alpha_B$  be the execution constructed from  $\alpha_A$  as follows. For each shared memory action  $\pi$  in  $\alpha_A$ , let the corresponding action in  $\alpha_B$  be  $\pi|Y$ . Leave the remaining actions as in  $\alpha_A$ . For each state s in  $\alpha_A$ , let the corresponding state in  $\alpha_B$  be  $s \circ (f_Z|X)$ , where  $f_Z$  is the third component of the preceding shared memory action in  $\alpha_A$  (or  $f_Z = init(Z)$  if there is no preceding shared memory action).

Clearly  $\beta_A|Y = beh(\alpha_B)$ . We claim that  $\alpha_B$  is an execution of B. To prove this claim, we proceed by induction on the length of  $\alpha_B$ , showing that each action is enabled from the state in which it occurs. Clearly, if  $\alpha_B$  contains no actions, then the claim holds. Let  $(s'_A, \pi, s_A)$  be a step of  $\alpha_A$ , and let  $\alpha'_B$  be the portion of  $\alpha_B$  up to (but not including) the action  $\pi|Y$  for the corresponding step in  $\alpha_B$ . We wish to show that if  $\alpha'_B$  ends in state  $s'_B$ , then the step  $(s'_B, \pi|Y, s_B) \in steps(B)$ , where  $s_B$  is the next state of  $\alpha_B$ . By the construction, we know that  $s'_B = s'_A \circ (f'_Z|X)$ , where  $f'_Z$ is the third component of the preceding shared memory action in  $\alpha_A$  (or  $f'_Z = init(Z)$  if there is no preceding shared memory action), and similarly for  $s_B$ . There are two cases for  $\pi$ :

- 1. If  $\pi$  is not a shared memory action, then clearly it is enabled from  $s'_B$ , since (by the construction)  $s'_A$  and  $s'_B$  are identical except that  $s'_A$  does not assign values to the variables in X. Furthermore, since  $\pi$  is not a shared memory action,  $s_B|X = s'_B|X$ , so the step exists by the definition of the closeout operator.

- 2. If  $\pi = (f'_Z, a, f_Z)$  is a shared memory action, then consistency of  $\beta_A$  requires that  $f'_Z$  be the third component of the preceding shared memory action in  $\alpha_A$  (or init(Z) if there is no such preceding action). By the definition of closeout, we know steps(B) contains the step  $(s'_A \circ (f'_Z|X), (f'_Z|Y, a, f_Z|Y), s_A \circ (f_Z|X))$ . And by the construction,  $s'_A \circ (f'_Z|X) = s'_B$  and  $s_A \circ (f_Z|X) = s_B$ . Therefore, the desired step exists.

In both cases,  $\pi | Y$  is enabled and leads to state  $s_B$ .

**Theorem 14:** Let X and Z be sets of variables such that  $X \subseteq Z$ . If A is a shared memory automaton for Z, then

- 1.  $behs(\mathcal{C}(A, X)) = \mathcal{C}(behs(A), X)$ , and

- 2.  $fairbehs(\mathcal{C}(A, X)) = \mathcal{C}(fairbehs(A), X).$

**Proof:** Part 1: Let Y = Z - X. By Lemma 12, we know that if  $\beta | Y$  is a behavior of  $\mathcal{C}(A, X)$ , then  $\beta$  is a behavior of A that is consistent for X. Therefore  $\beta | Y \in \mathcal{C}(behs(A), X)$ , by definition. If  $\beta | Y \in \mathcal{C}(behs(A), X)$ , then by definition of closeout on behaviors,  $\beta$  is consistent for X. Therefore, Lemma 13 tells us that  $\beta | Y \in behs(\mathcal{C}(A, X))$ .

Part 2: First, we show that  $fairbehs(\mathcal{C}(A, X))$  contains  $\mathcal{C}(fairbehs(A), X)$ . Let  $\beta_B$  be a fair behavior of  $B = \mathcal{C}(A, X)$ , and let  $\alpha_B$  be an execution of B with  $beh(\alpha_B) = \beta_B$ . Construct execution  $\alpha_A$  of A from  $\alpha_B$  as in the proof of Lemma 12 such that  $beh(\alpha_A)|(Z - X) = \beta_B$ . Since A is a shared memory automaton, we know that shared-out(A) is complete and that for any given access label  $a \in \mathcal{L}$ , all shared memory actions with label a belong to the same class. Furthermore, by the definition of closeout,  $\pi_A$  and  $\pi'_A$  belong to the same equivalence class in A iff  $\pi_A|X$  and  $\pi'_A|X$  belong to the same equivalence class in B. Therefore, given that  $\alpha_B$  is fair, we can show that  $\alpha_A$  is fair by arguing that an action  $\pi_A$  is enabled in state  $s_A$  of  $\alpha_A$  iff  $\pi_A|X$  is enabled in the corresponding state  $s_B$  of  $\alpha_B$ . This is easily seen from the construction of steps(B), since  $s_A = s_B|(Z - X)$ .

Now, we show that C(fairbehs(A), X) contains the set fairbehs(C(A, X)). Let  $\beta_A$  be a fair behavior of A that is consistent for X, and let  $\alpha_A$  be an execution of A with  $beh(\alpha_A) = \beta_A$ . Construct execution  $\alpha_B$  of C(A, X) from  $\alpha_A$  as in the proof of Lemma 13 such that  $\beta_A|(Z - X) = beh(\alpha_B)$ . The remainder of the proof is argued as above.

## 4 Proofs for Shared Object Systems

It is convenient to use shared atomic objects as system components when building large concurrent systems. Each operation on an atomic object appears to execute indivisibly, thereby allowing the programmer to consider only interleavings of the operations, rather than their true concurrency. For performance reasons, however, it is often useful to allow concurrency between operations on a single object, so the condition of atomicity is only on an object's behavior, not on its implementation.

There are two general approaches to modelling shared objects. Which is more natural depends upon whether the intent is to model a system that uses atomic objects, or one that *implements* them. In a system that uses atomic objects, it is convenient to represent each operation as a single shared action between the object and the invoking process; we call these *atomic access systems*. In a system that implements atomic objects, each operation can be modeled by an invocation event and response event, denoting, respectively, the beginning and end of operation execution; we call these *invocation-response systems*.

In an invocation-response system, it is possible to consider operation executions that overlap in time. Herlihy and Wing [8] use this model to define a correctness condition called *linearizability* that extends Lamport's notion of atomicity for reads and writes [11] to arbitrary data types. Linearizability requires that in any (concurrent) execution, each operation "appears" to take effect instantaneously, sometime between the invocation and response events of the operation. Linearizability is also similar to Lamport's *sequential consistency* [10], but requires that if two operations on a given object do not overlap in time, then the order in which they "appear" to occur is consistent with the order in which they actually occur <sup>5</sup>. Furthermore, unlike sequential consistency, linearizability has a locality property: if each object is linearizable, then the entire system is linearizable.

In this section, we take the linearizability notion one step further, and show that a linearizable invocation-response system is equivalent to an atomic access system. In particular, we show that if the objects in the invocation-response system are each *linearizable*, then every behavior of the entire invocation-response system is a behavior of the atomic access system. Thus, in reasoning about complex systems, it is possible to consider overlapping operation executions at one level of abstraction, and shared atomic actions for the same operations when reasoning at higher levels of abstraction. This is an important benefit of using a model that unifies invocation-response and atomic access in a single formal framework. In addition, we extend the work of Herlihy and Wing by treating not only safety properties of invocation-response systems, but liveness properties as well.

These results are intended to be used for reasoning about multiprocessor programs, in which the shared memory is assumed to be atomic and the program is modularized by layers of linearizable concurrent objects. They may also be useful in reasoning systems having a mixture of message passing and shared memory operations. For example, a network of shared memory multiprocessors or a message passing multiprocessor with multi-threaded nodes would involve message passing between nodes and shared memory operations within a node.

We begin, in Section 4.1 by describing the basic architecture of an invocation-response system, including the interfaces and specification mechanisms for the objects and processes. Then, in

<sup>&</sup>lt;sup>5</sup>A comparison of sequential consistency and linearizability is given by Attiya and Welch [2].

Section 4.2, we describe three systems: a concurrent system, a sequential system, and an atomic system. All three systems are described in the I/O automaton model. We show that if the objects of the concurrent system are linearizable and if the processes obey certain well-formedness restrictions, then each of these systems "simulates" the next. This gives us a unified theory for describing systems in terms of invocations and responses, but reasoning about them in terms of atomic accesses.

#### 4.1 Invocation-Response Systems

We are interested in studying systems in which processes invoke operations on objects and then wait for the objects to respond. In this section, we define a general architecture for *invocation-response* systems (or *IR* systems). Later, this architecture will be used to define two systems: System C, a concurrent system containing linearizable objects, and System B, a sequential system used as a stepping stone in our proof. A different structure will be used to define System A, an atomic shared object system that will form the basis of our correctness condition.

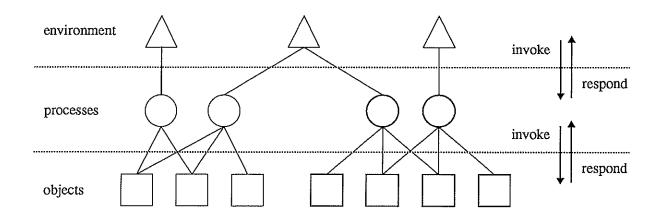

An IR system consists of a set of processes and a set of objects, where each process and each object is modelled as an I/O automaton. Processes may request operations on objects by issuing "invoke" actions. These actions are inputs to the objects, which issue "respond" output actions after performing the requested operation. The interface at the boundary between a process and its environment is analogous to the interface at the boundary between an object and a process. To request that the system perform a particular function, the environment may "invoke" operations on a process, which later replies to the environment with a "respond" action. Here, we consider systems of only three layers: the objects, the processes, and the environment. However, by modelling the interaction between a process and the environment in the same way as the interaction between an object and a process, we set the stage for constructing complicated objects hierarchically. That is, one might compose a collection of objects and processes, and treat the composition as a single object. To describe the set of operations that may be invoked on an object or process, we define an "interface type." An *interface type T* consists of:

- ops(T), a set of operation names, and

- for each operation  $\rho \in ops(T)$ ,

- $args(\rho)$ , the domain of arguments to the operation, and

- $rets(\rho)$ , the domain of return values of the operation.

The operation names identify the operations that may be invoked on the corresponding object or process. For each operation name, the domain of argument values specifies the allowable operation arguments that may be supplied by the user of the object. Similarly, the return value domain for an operation specifies the possible values that may be returned by the object as a result of that operation. We will see shortly how the interface type of an object or process is used to derive the signature of the corresponding automaton.

In IR systems, there are three kinds of components: the shared objects, the processes that invoke operations on those objects, and the environment that directs the activities of the processes. For the remainder of the paper, we fix three sets of indices,  $\mathcal{I}$ ,  $\mathcal{J}$ , and  $\mathcal{K}$ . We use the elements of  $\mathcal{I}$ to name the objects in a system, and we use the elements of  $\mathcal{J}$  to name the processes that invoke operations on the objects. An IR system is modelled as the composition of an object automaton  $o_i$ for each  $i \in \mathcal{I}$ , and a process automaton  $p_j$  for each  $j \in \mathcal{J}$ . The indices in  $\mathcal{K}$  identify the processes (or users) that constitute the environment of a system.

An example IR system is shown in Figure 1. Objects (in  $\mathcal{I}$ ) are shown as squares, processes (in  $\mathcal{J}$ ) are circles, and components of the environment (in  $\mathcal{K}$ ) are triangles. We do not model the

Figure 1: An IR System.

environment explicitly, but simply use the elements of  $\mathcal{K}$  to refer to its components. One may think of these components either as I/O automata or as users interacting with the system. We require that the environment, as a whole, obey certain well-formedness restrictions on its interactions with each process. Informally, we require that the environment wait for a process to respond to a request before making a new request of that process.<sup>6</sup> If several components in the environment may make requests of the same process, then those components must cooperate (possibly by participating in a mutual exclusion protocol) in order to ensure that well-formedness is preserved at that process. We now define the objects and processes of IR systems.

#### 4.1.1 Objects

Each object automaton  $o_i, i \in \mathcal{I}$ , has an associated interface type, denoted type(i), and the signature of  $o_i$  is determined from this interface type. For each  $i \in \mathcal{I}$ , we define  $sig(o_i)$  as follows:

The subscripts on each action identify the object automaton  $o_i$  at which the operation occurs and the process automaton  $p_j$  responsible for the request. The following definition is useful for describing executions of  $o_i$ . Let  $\alpha$  be an execution of  $o_i$ . We say that  $\alpha$  is *input well-formed* iff  $\forall j \in \mathcal{J}$ , no two invoke<sub>*i*,*j*</sub> actions occur in  $\alpha$  without a respond<sub>*i*,*j*</sub> action between them. Input wellformedness does not prohibit concurrency at an object, since multiple invocations from *different* elements of  $\mathcal{J}$  may occur without intervening responses.

#### 4.1.2 Processes

Each process in an IR system is modelled as an I/O automaton  $p_j$ ,  $j \in \mathcal{J}$ , that has an associated interface type, denoted type(j). The interface type describes the set of operations that may be invoked on a process. In addition, a process may itself invoke operations on objects. Therefore, its signature not only contains actions corresponding to operations in its interface type, but also invoke and respond actions corresponding to the interface types of the objects that it may access. For each  $j \in \mathcal{J}$ , we let  $obj(j) \subseteq \mathcal{I}$  denote that set of objects that  $p_j$  may access, and define the signature of  $p_j$  as follows:

<sup>&</sup>lt;sup>6</sup>A similar idea appears in [14] on page 79.

| Input Actions:         | $	ext{invoke}_{j,k}( ho,a), 	ext{ where } k \in \mathcal{K},  ho \in ops(type(j)) 	ext{ and } a \in args( ho)$         |

|------------------------|------------------------------------------------------------------------------------------------------------------------|

|                        | respond <sub><i>i</i>,<i>j</i></sub> ( $\rho, a, r$ ), where $i \in obj(j), \rho \in ops(type(i)), a \in args(\rho)$ , |

|                        | and $r \in rets( ho)$                                                                                                  |

| <b>Output Actions:</b> | $\operatorname{respond}_{j,k}( ho,a,r), 	ext{ where } k \in \mathcal{K},  ho \in ops(type(j)), a \in args( ho),$       |

|                        | and $r \in rets( ho)$                                                                                                  |

|                        | $\mathrm{invoke}_{i,j}( ho,a), 	ext{ where } i \in obj(j),  ho \in ops(type(i)) 	ext{ and } a \in args( ho)$           |

In reasoning about the schedules of a process in an IR system, it will be helpful to distinguish those actions that are shared with the objects from those shared with the environment. Let  $\beta$  be a sequence of actions of  $p_j$ . We define  $\beta | \mathcal{I}$  to be the subsequence of  $\beta$  containing exactly the invoke<sub>*i*,*j*</sub> and respond<sub>*i*,*j*</sub> actions, for all  $i \in \mathcal{I}$  (the objects). Similarly, we define  $\beta | \mathcal{K}$  to be the subsequence of  $\beta$  containing exactly the invoke<sub>*j*,*k*</sub> and respond<sub>*j*,*k*</sub> actions, for all  $k \in \mathcal{K}$  (the environment).