## Washington University in St. Louis Washington University Open Scholarship

All Computer Science and Engineering Research

**Computer Science and Engineering**

Report Number: WUCSE-2004-72

2004-12-01

## Techniques for Processing TCP/IP Flow Content in Network Switches at Gigabit Line Rates

David Vincent Schuehler

The growth of the Internet has enabled it to become a critical component used by businesses, governments and individuals. While most of the traffic on the Internet is legitimate, a proportion of the traffic includes worms, computer viruses, network intrusions, computer espionage, security breaches and illegal behavior. This rogue traffic causes computer and network outages, reduces network throughput, and costs governments and companies billions of dollars each year. This dissertation investigates the problems associated with TCP stream processing in high-speed networks. It describes an architecture that simplifies the processing of TCP data streams in these environments and presents a... **Read complete abstract on page 2**.

Follow this and additional works at: https://openscholarship.wustl.edu/cse\_research

#### **Recommended Citation**

Schuehler, David Vincent, "Techniques for Processing TCP/IP Flow Content in Network Switches at Gigabit Line Rates" Report Number: WUCSE-2004-72 (2004). *All Computer Science and Engineering Research.*

https://openscholarship.wustl.edu/cse\_research/1042

Department of Computer Science & Engineering - Washington University in St. Louis Campus Box 1045 - St. Louis, MO - 63130 - ph: (314) 935-6160.

This technical report is available at Washington University Open Scholarship: https://openscholarship.wustl.edu/ cse\_research/1042

# Techniques for Processing TCP/IP Flow Content in Network Switches at Gigabit Line Rates

David Vincent Schuehler

### **Complete Abstract:**

The growth of the Internet has enabled it to become a critical component used by businesses, governments and individuals. While most of the traffic on the Internet is legitimate, a proportion of the traffic includes worms, computer viruses, network intrusions, computer espionage, security breaches and illegal behavior. This rogue traffic causes computer and network outages, reduces network throughput, and costs governments and companies billions of dollars each year. This dissertation investigates the problems associated with TCP stream processing in high-speed networks. It describes an architecture that simplifies the processing of TCP data streams in these environments and presents a hardware circuit capable of TCP stream processing on multi-gigabit networks for millions of simultaneous network connections. Live Internet traffic is analyzed using this new TCP processing circuit.

Department of Computer Science & Engineering

2004-72

# Techniques for Processing TCP/IP Flow Content in Network Switches at Gigabit Line Rates, Doctoral Dissertation, December 2004

Authors: Schuehler, David V.

Abstract: The growth of the Internet has enabled it to become a critical component used by businesses, governments and individuals. While most of the traffic on the Internet is legitimate, a proportion of the traffic includes worms, computer viruses, network intrusions, computer espionage, security breaches and illegal behavior. This rogue traffic causes computer and network outages, reduces network throughput, and costs governments and companies billions of dollars each year.

This dissertation investigates the problems associated with TCP stream processing in high-speed networks. It describes an architecture that simplifies the processing of TCP data streams in these environments and presents a hardware circuit capable of TCP stream processing on multi-gigabit networks for millions of simultaneous network connections. Live Internet traffic is analyzed using this new TCP processing circuit.

Type of Report: Other

#### WASHINGTON UNIVERSITY

### SEVER INSTITUTE OF TECHNOLOGY

### DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

### TECHNIQUES FOR PROCESSING TCP/IP FLOW CONTENT

### IN NETWORK SWITCHES AT GIGABIT LINE RATES

by

David Vincent Schuehler

Prepared under the direction of Professor John W. Lockwood

A dissertation presented to the Sever Institute of Washington University in partial fulfillment of the requirements for the degree of

Doctor of Science

December, 2004

Saint Louis, Missouri

Washington University in St. Louis Technical Report WUCSE-2004-72 Nov 22, 2004 http://www.arl.wustl.edu/arl/projects/fpx/reconfig.htm

## WASHINGTON UNIVERSITY SEVER INSTITUTE OF TECHNOLOGY DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

### ABSTRACT

## TECHNIQUES FOR PROCESSING TCP/IP FLOW CONTENT IN NETWORK SWITCHES AT GIGABIT LINE RATES

by David Vincent Schuehler

ADVISOR: Professor John W. Lockwood

December, 2004

Saint Louis, Missouri

The growth of the Internet has enabled it to become a critical component used by businesses, governments and individuals. While most of the traffic on the Internet is legitimate, a proportion of the traffic includes worms, computer viruses, network intrusions, computer espionage, security breaches and illegal behavior. This rogue traffic causes computer and network outages, reduces network throughput, and costs governments and companies billions of dollars each year.

This dissertation investigates the problems associated with TCP stream processing in high-speed networks. It describes an architecture that simplifies the processing of TCP data streams in these environments and presents a hardware circuit capable of TCP stream processing on multi-gigabit networks for millions of simultaneous network connections. Live Internet traffic is analyzed using this new TCP processing circuit. copyright by

David Vincent Schuehler

2004

This dissertation is dedicated to

my family,

my friends,

and the pursuit of knowledge.

# Contents

| Li | st of T | ables   | Х                                        | ci |

|----|---------|---------|------------------------------------------|----|

| Li | st of F | igures  | X                                        | ii |

| Al | obrevi  | ations  |                                          | ii |

| Ac | cknow   | ledgme  | ents                                     | X  |

| Pr | eface   |         |                                          | ii |

| 1  | Intro   | oductio | <b>n</b>                                 | 1  |

|    | 1.1     | Proble  | m Framework                              | 4  |

|    | 1.2     |         |                                          | 5  |

|    | 1.3     | Contril | butions                                  | 7  |

|    | 1.4     | Organi  | ization of Dissertation                  | 8  |

| 2  | Back    | ground  | and Motivation                           | 1  |

|    | 2.1     | Hardw   | are Processing Technologies              | 4  |

|    |         | 2.1.1   | Microprocessors                          | 5  |

|    |         | 2.1.2   | Application Specific Integrated Circuits | 6  |

|    |         | 2.1.3   | Field Programmable Gate Arrays           | 6  |

|    | 2.2     | Challer | nges                                     | 8  |

|    |         | 2.2.1   | Performance                              | 9  |

|    |         | 2.2.2   | Packet Classification                    | 0  |

|    |         | 2.2.3   | Context Storage                          | 3  |

|    |         | 2.2.4   | Packet Resequencing                      | 4  |

|    |         | 2.2.5   | Overlapping Retransmissions              | 6  |

|    |         | 2.2.6   | Idle Flows                               | 6  |

|   |             | 2.2.7 Resource Exhaustion                | 27       |

|---|-------------|------------------------------------------|----------|

|   |             | 2.2.8 Selective Flow Monitoring          | 28       |

|   |             | 2.2.9 Multi-Node Monitor Coordination    | 29       |

|   |             | 2.2.10 Fragmentation                     | 29       |

|   |             | 2.2.11 Flow Modification                 | 31       |

|   |             | 2.2.12 Bi-Directional Traffic Monitoring | 32       |

| 3 | Rela        | ed Work                                  | 34       |

|   | 3.1         | Network Monitoring Systems               | 34       |

|   | 3.2         |                                          | 35       |

|   | 3.3         | Hardware-Based Network Monitors          | 37       |

|   | 3.4         | Packet Classification                    | 38       |

|   | 3.5         | Related Technologies                     | 41       |

|   |             | 3.5.1 Load Balancers                     | 41       |

|   |             | 3.5.2 SSL Accelerators                   | 43       |

|   |             | 3.5.3 Intrusion Detection Systems        | 44       |

|   |             | 3.5.4 TCP Offload Engines                | 46       |

|   | 3.6         | Hardware-Accelerated Content Scanners    | 48       |

|   | 3.7         | Summary                                  | 51       |

| 4 | Arc         | tecture                                  | 52       |

| - | 4.1         | Initial Investigations                   |          |

|   |             | -                                        | 53       |

|   |             |                                          | 55       |

|   | 4.2         | ΓCP-Processor                            |          |

|   | 4.3         | Application Interface                    |          |

|   | 4.4         |                                          | 63       |

|   | 4.5         |                                          | 64       |

| 5 | Fnv         | onment                                   | 67       |

| 5 | <b>5</b> .1 |                                          | 67       |

|   | 5.2         |                                          | 68       |

|   | 5.3         |                                          | 69       |

|   | 5.4         |                                          | 70       |

|   | 5.5         |                                          | 70<br>71 |

|   | 5.5         |                                          | 11       |

| 6 | ТСР   | -Processor Internals                              |

|---|-------|---------------------------------------------------|

|   | 6.1   | Endianness                                        |

|   | 6.2   | Packet Parameters                                 |

|   | 6.3   | Flow Control                                      |

|   | 6.4   | External Memories                                 |

|   | 6.5   | Configuration Parameters                          |

|   | 6.6   | TCP Processor                                     |

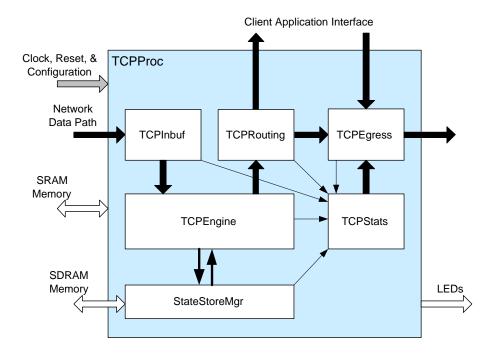

|   | 6.7   | TCP Proc                                          |

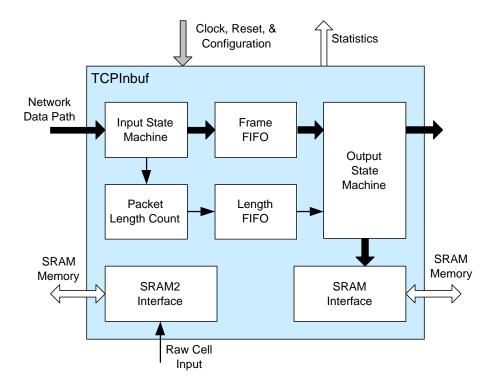

|   | 6.8   | TCP Input Buffer                                  |

|   | 6.9   | TCP Engine                                        |

|   | 6.10  | State Store Manager                               |

|   | 6.11  | TCP Routing                                       |

|   |       | 6.11.1 Client Interface                           |

|   | 6.12  | TCP Egress                                        |

|   | 6.13  | TCP Stats                                         |

| 7 | Strea | amExtract Circuit                                 |

|   | 7.1   | StreamExtract_Module                              |

|   | 7.2   | StreamExtract                                     |

|   | 7.3   | LEDs                                              |

|   | 7.4   | Serialization/Deserialization (Endoding/Decoding) |

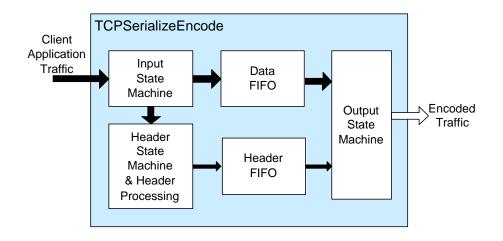

|   |       | 7.4.1 TCPSerializeEncode                          |

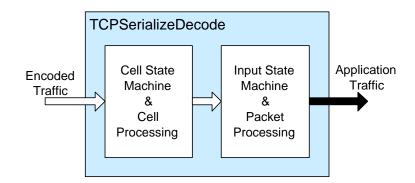

|   |       | 7.4.2 TCPSerializeDecode                          |

|   | 7.5   | Implementation                                    |

| 0 |       | •                                                 |

| 8 |       | -Lite Wrappers                                    |

|   | 8.1   | TCPDeserialize                                    |

|   | 8.2   | TCPReserialize                                    |

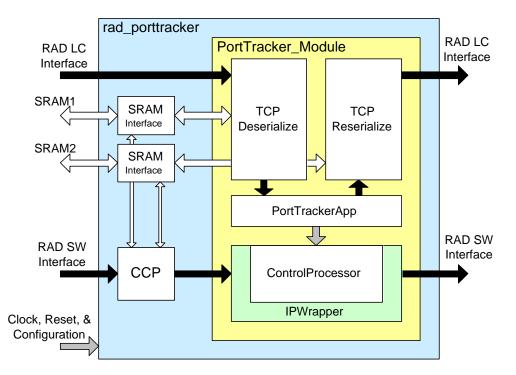

|   | 8.3   | PortTracker                                       |

|   |       | 8.3.1 PortTracker_Module                          |

|   |       | 8.3.2 PortTrackerApp                              |

|   |       | 8.3.3 ControlProcessor                            |

|   | 8.4   | Scan                                              |

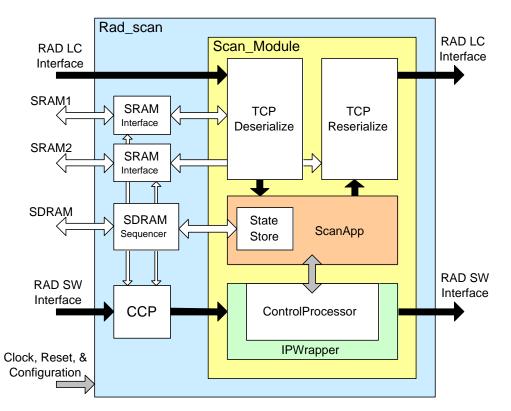

|   |       | 8.4.1 Scan_Module                                 |

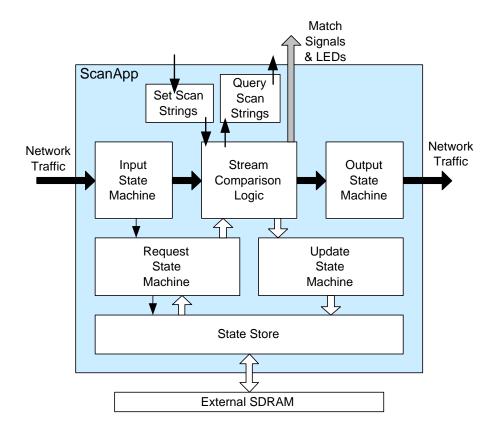

|   |       | 8.4.2 ScanApp                                     |

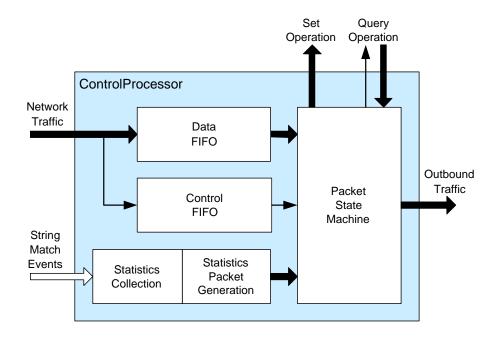

|   |       | 8.4.3 ControlProcessor                            |

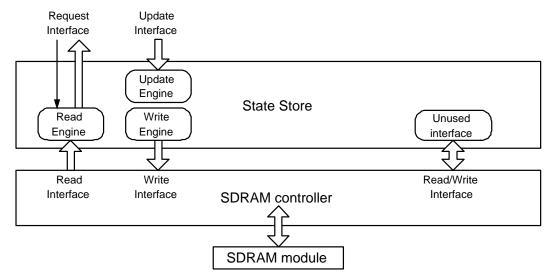

|    |       | 8.4.4   | StateStore                        | . 129 |

|----|-------|---------|-----------------------------------|-------|

| 9  | Ana   | lysis . |                                   | 131   |

|    | 9.1   | Test Se | etup                              | . 131 |

|    | 9.2   | Data C  | Collection                        | . 132 |

|    | 9.3   | Result  | ts                                | . 133 |

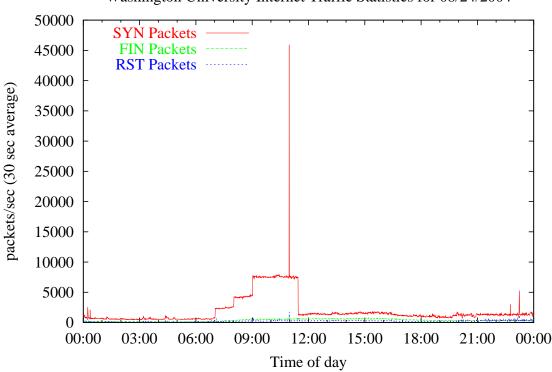

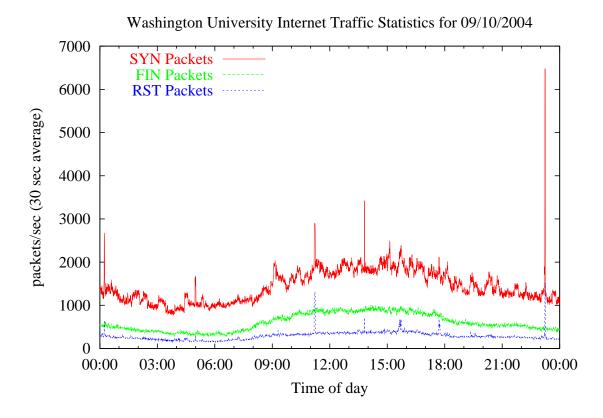

|    |       | 9.3.1   | Denial of Service Attack          | . 135 |

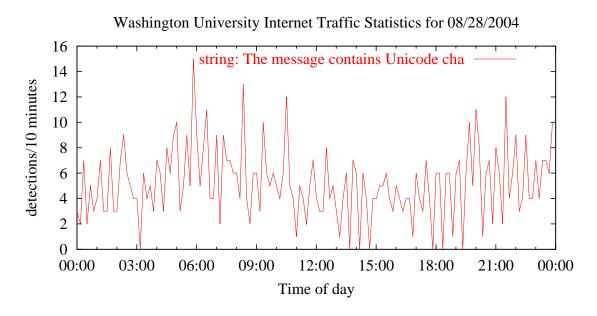

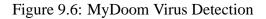

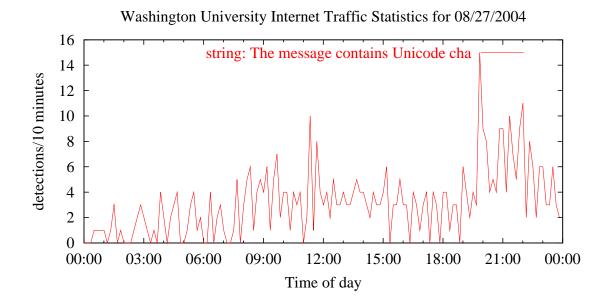

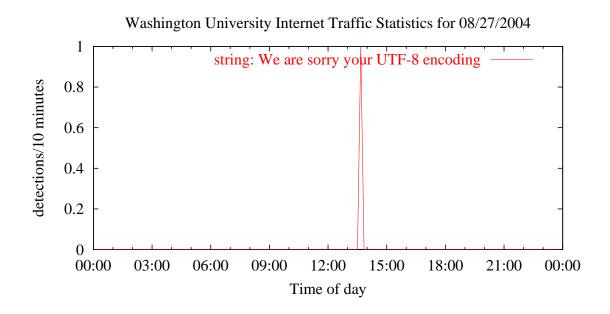

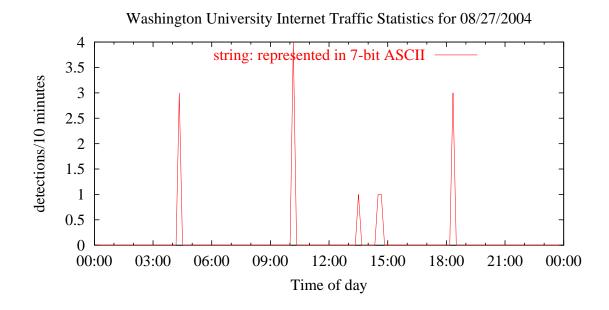

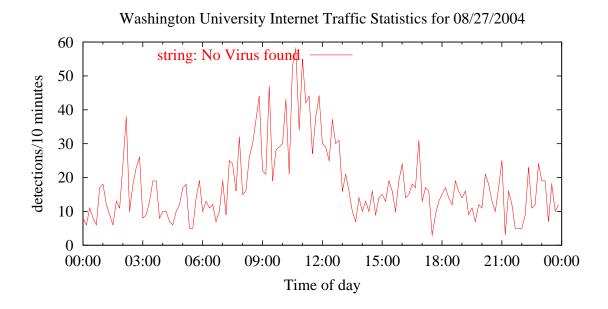

|    |       | 9.3.2   | Virus Detection                   | . 137 |

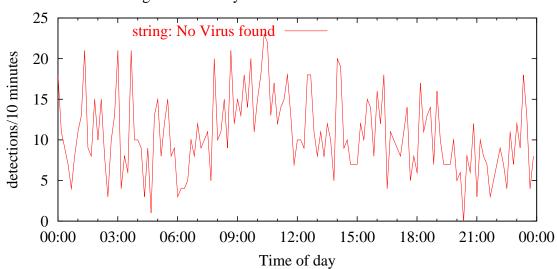

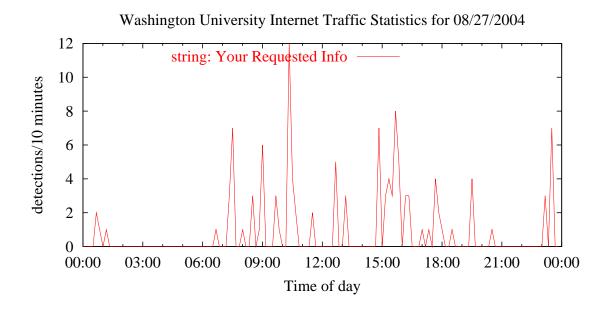

|    |       | 9.3.3   | Spam                              | . 138 |

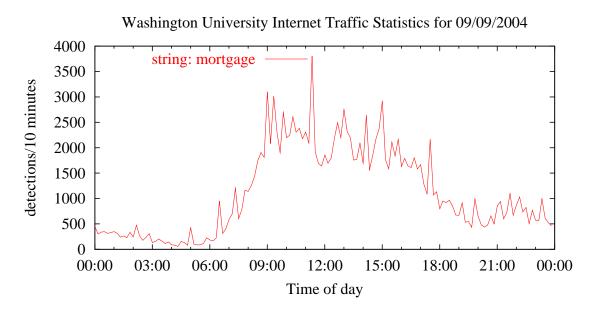

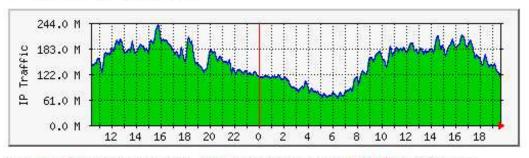

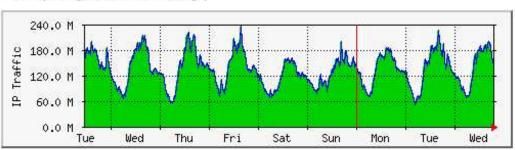

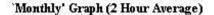

|    |       | 9.3.4   | Traffic Trends                    | . 139 |

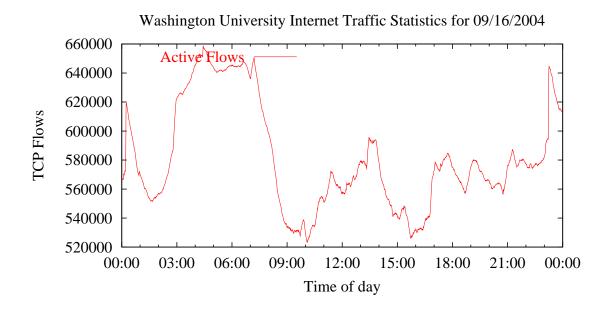

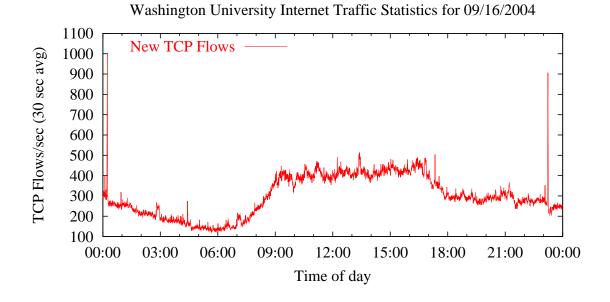

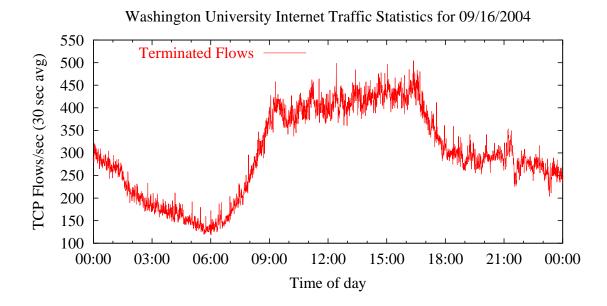

|    |       | 9.3.5   | TCP Flow Classification           | . 141 |

|    |       | 9.3.6   | Traffic Types                     | . 143 |

| 10 | Con   | clusion |                                   | 145   |

|    |       |         | ibutions                          |       |

|    |       |         | of Live Traffic Testing           |       |

|    |       |         | of the TCP-Processor              |       |

| 11 | Futu  | iro Wor | rk                                | 151   |

| 11 |       |         | t Defragmentation                 |       |

|    |       |         | Classification and Flow Aging     |       |

|    |       |         | t Storage Manager                 |       |

|    |       |         | os and 40Gbps Data Rates          |       |

|    |       | -       |                                   |       |

|    |       |         | c Sampling and Analysis           |       |

|    |       |         | cation Integration                |       |

|    |       |         |                                   |       |

| Aŗ | ppend | ix A Us | sage                              | 159   |

|    | A.1   | Stream  | nExtract                          |       |

|    |       | A.1.1   | Compile                           | . 160 |

|    |       | A.1.2   | Generating Simulation Input Files | . 160 |

|    |       | A.1.3   | Simulate                          | . 161 |

|    |       | A.1.4   | Synthesize                        | . 162 |

|    |       | A.1.5   | Place & Route                     | . 162 |

|    |       | A.1.6   | Setup                             | . 163 |

|    | A.2   | Scan &  | & PortTracker                     | . 163 |

|        | A.2.1          | Compile                                                                                                |

|--------|----------------|--------------------------------------------------------------------------------------------------------|

|        | A.2.2          | Generating Simulation Input Files                                                                      |

|        | A.2.3          | Simulate                                                                                               |

|        | A.2.4          | Synthesize                                                                                             |

|        | A.2.5          | Place & Route                                                                                          |

|        | A.2.6          | Setup                                                                                                  |

| A.3    | New A          | Applications $\ldots$ |

|        | A.3.1          | Client Interface                                                                                       |

| A.4    | Runtin         | ne Setup                                                                                               |

| A.5    | Known          | n Problems                                                                                             |

|        | A.5.1          | Xilinx ISE 6.2i                                                                                        |

|        | A.5.2          | Synplicity 7.5                                                                                         |

|        | A.5.3          | Outbound IPWrapper Lockup                                                                              |

|        | A.5.4          | Inbound Wrapper Problems                                                                               |

| Append | ix B Ge        | enerating Simulation Input Files                                                                       |

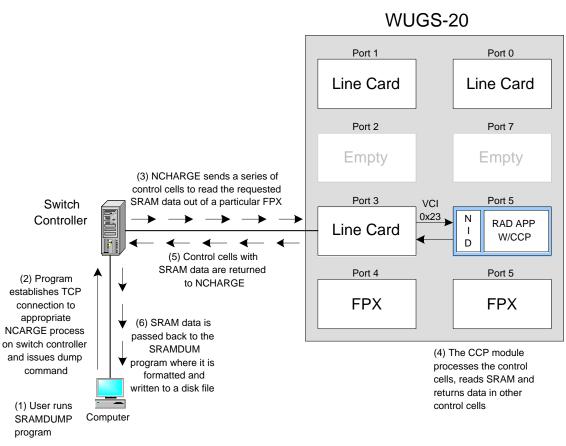

| B.1    |                | np $\ldots$ $\ldots$ $\ldots$ $\ldots$ $175$                                                           |

| B.2    |                | bp                                                                                                     |

| B.3    | -              | TBENCH                                                                                                 |

| B.4    |                | ump                                                                                                    |

| B.5    |                | apture                                                                                                 |

| B.6    | Interna        | al Data Captures                                                                                       |

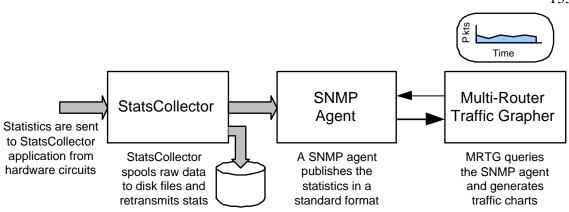

| Annend | ix C St        | atistics Collection and Charting                                                                       |

| C.1    |                | 'ollector                                                                                              |

| C.2    |                | pp                                                                                                     |

| C.3    |                | P Support                                                                                              |

| C.4    |                | G Charting                                                                                             |

| Annond | iv D Ad        | Iditional Traffic Charts                                                                               |

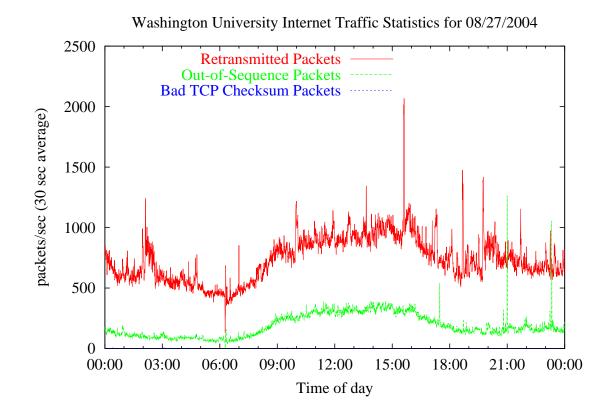

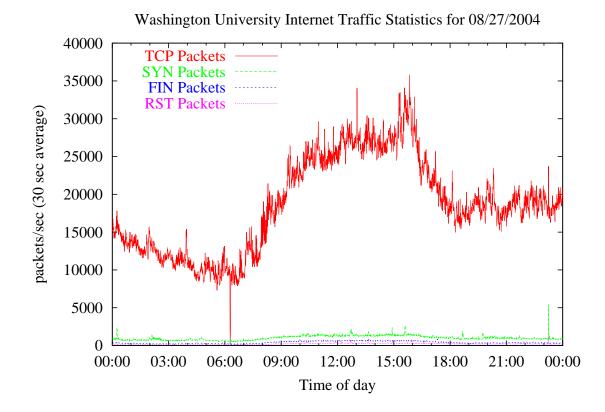

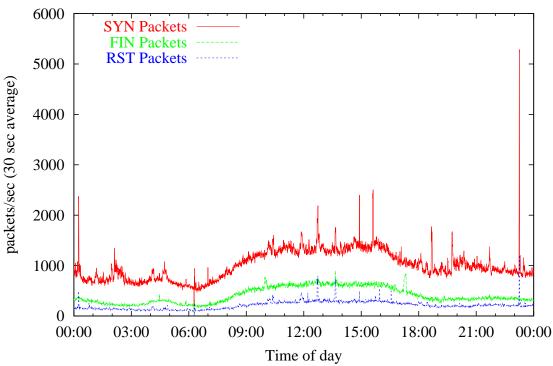

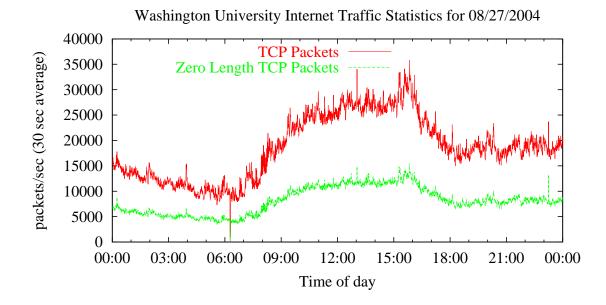

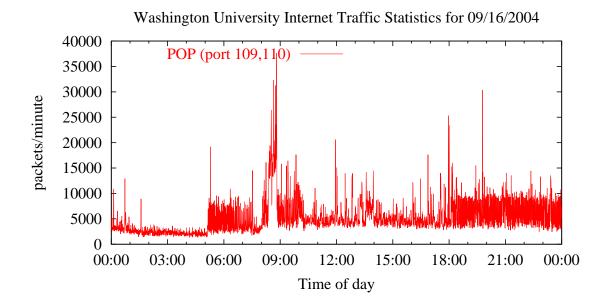

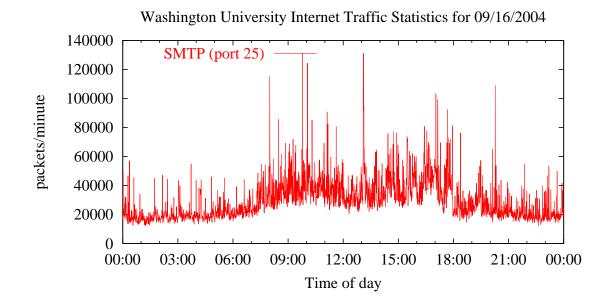

| D.1    |                |                                                                                                        |

| D.1    | D.1.1          | ics for Aug 27, 2004                                                                                   |

|        | D.1.1<br>D.1.2 |                                                                                                        |

|        | D.1.2<br>D.1.3 | Traffic Statistics                                                                                     |

|        | D.1.5<br>D.1.4 | Virus Statistics                                                                                       |

| ۲Л     |                |                                                                                                        |

| D.2    | Statist        | ics for Sep 16, 2004                                                                                   |

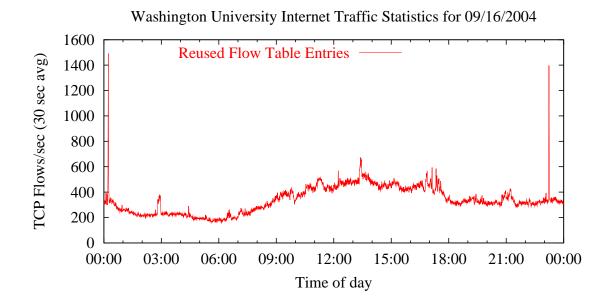

| D.2.1        | Flow Statistics    |

|--------------|--------------------|

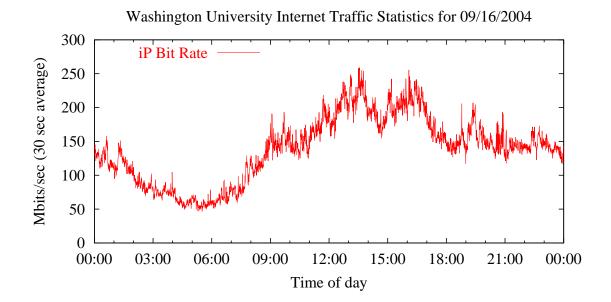

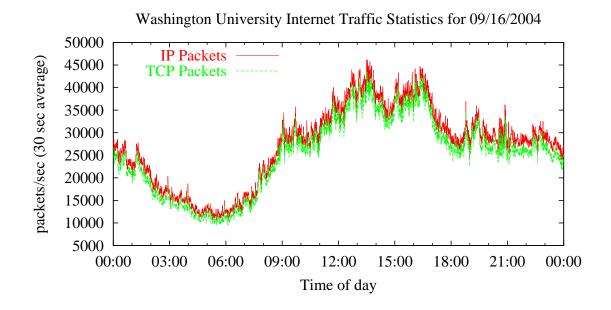

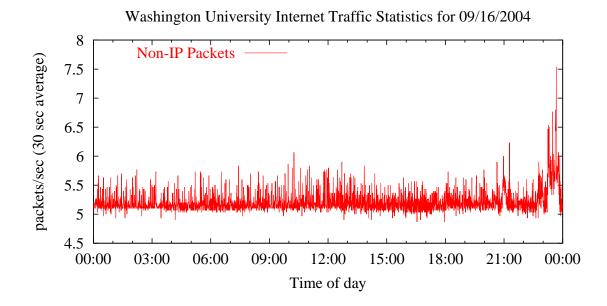

| D.2.2        | Traffic Statistics |

| D.2.3        | Port Statistics    |

| D.2.4        | Scan Statistics    |

| References . |                    |

| Vita         |                    |

# **List of Tables**

| 1.1  | Optical links and associated data rates           |

|------|---------------------------------------------------|

| 2.1  | Cost of Internet Attacks                          |

| 2.2  | Comparison of Hardware Processing Technologies    |

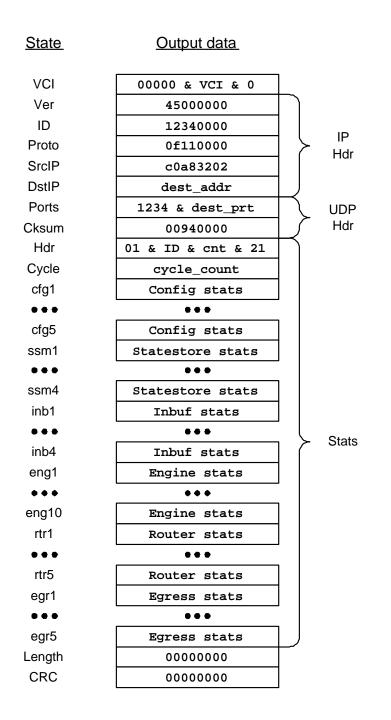

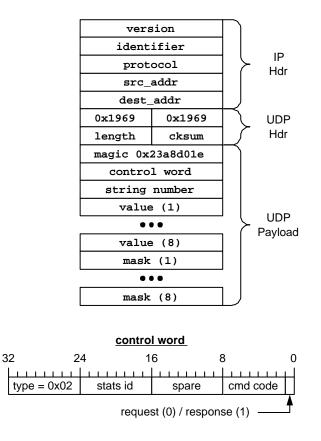

| 5.1  | IP packet contents                                |

| 6.1  | State Store Request Sequence                      |

| 6.2  | State Store Response Sequence                     |

| 11.1 | Performance improvements and estimated data rates |

| A.1  | Active Monitoring Routing Assignments             |

| A.2  | Passive Monitoring Routing Assignments            |

| C.1  | Statistics Format                                 |

# **List of Figures**

| 1.1 | Anatomy of a Network Packet                                     | 2  |

|-----|-----------------------------------------------------------------|----|

| 1.2 | IP(v4) and TCP Headers                                          | 2  |

| 1.3 | Types of Network Monitors                                       | 3  |

| 1.4 | Heterogenous Network                                            | 5  |

| 2.1 | Gilder's Law versus Moore's Law                                 | 14 |

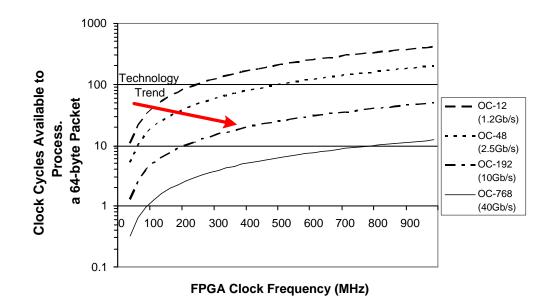

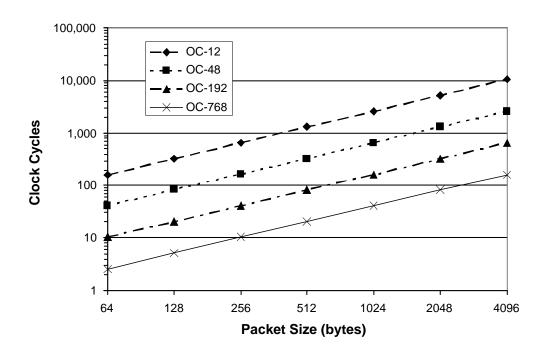

| 2.2 | Clock Cycles Available to Process 64 byte Packet                | 20 |

| 2.3 | Clock Cycles Available to Process Packets of Various Sizes      | 21 |

| 2.4 | Overlapping Retransmission                                      | 26 |

| 2.5 | Multi-Node Monitor                                              | 30 |

| 2.6 | Bi-directional Flow Monitoring                                  | 33 |

| 3.1 | Taxonomy of Network Monitors                                    | 35 |

| 3.2 | Web Farm with Load Balancer                                     | 41 |

| 3.3 | Delayed Binding Technique                                       | 42 |

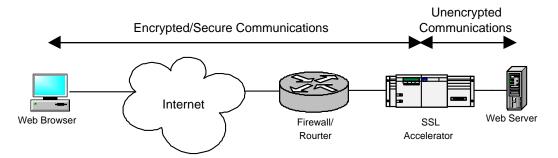

| 3.4 | SSL Accelerator Employed at Web Server                          | 43 |

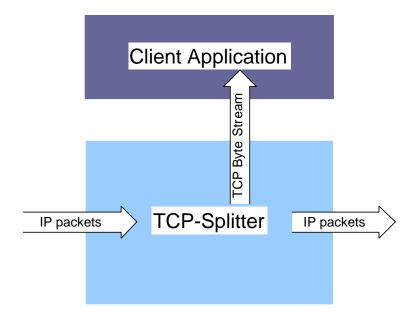

| 4.1 | TCP-Splitter Data Flow                                          | 53 |

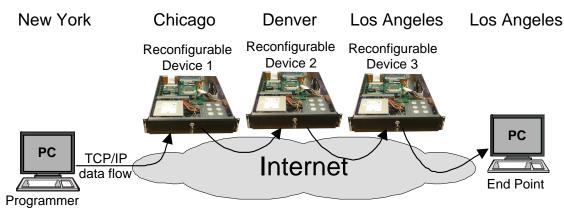

| 4.2 | Multi-Device Programmer Using TCP-Splitter Technology           | 54 |

| 4.3 | StreamCapture Circuit                                           | 57 |

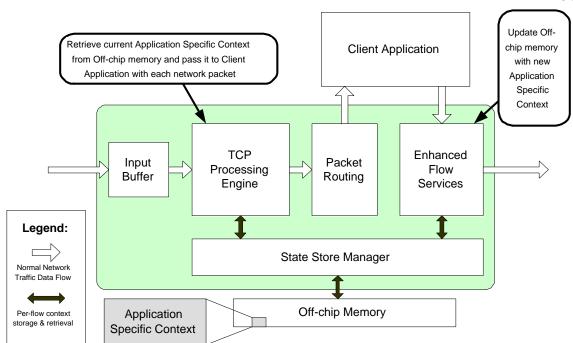

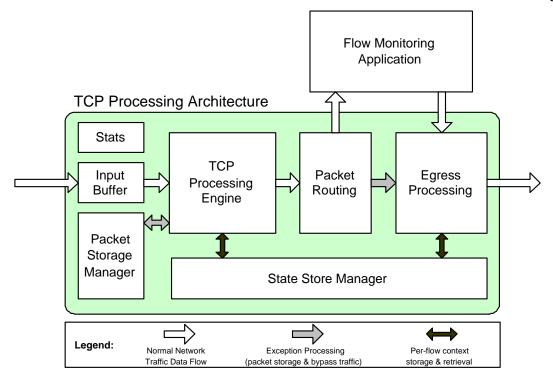

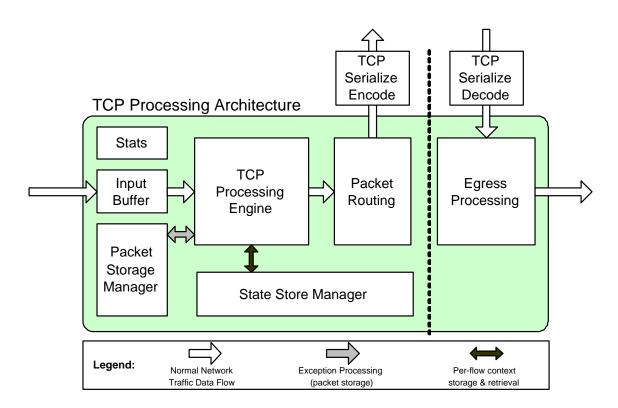

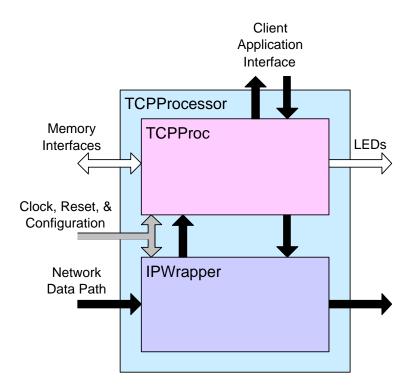

| 4.4 | TCP-Processor Architecture                                      | 58 |

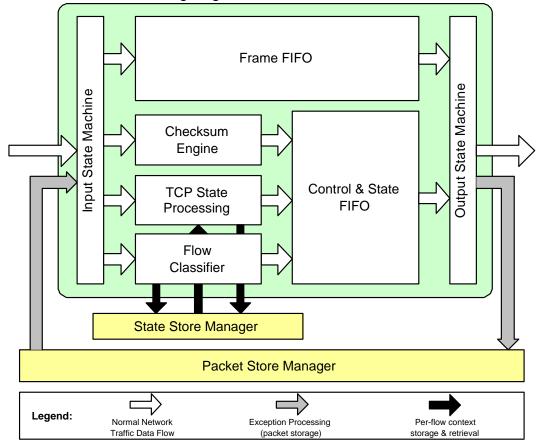

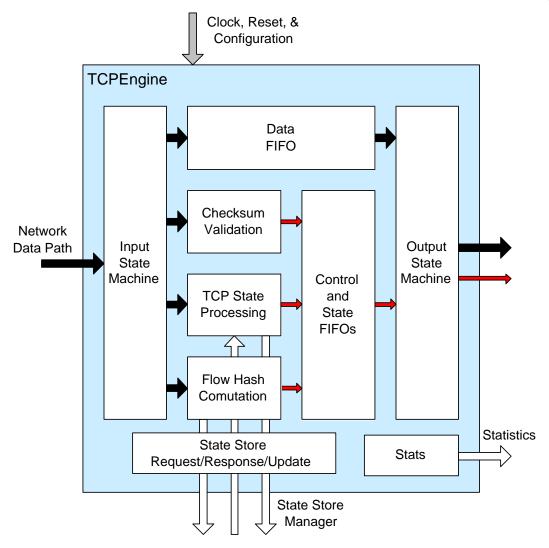

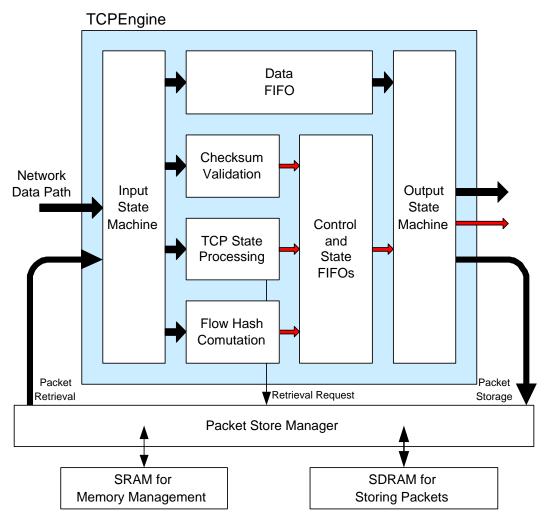

| 4.5 | TCP Processing Engine                                           | 60 |

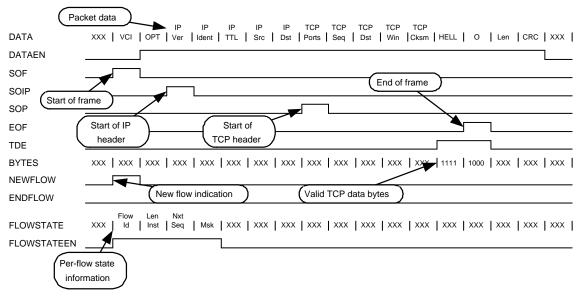

| 4.6 | Timing Diagram showing Client Interface                         | 63 |

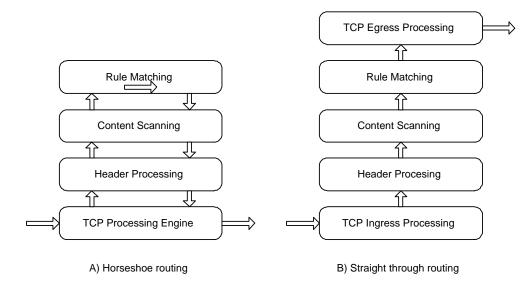

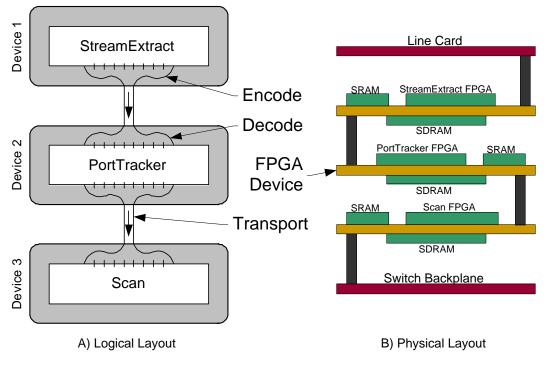

| 4.7 | Multi-Board Traffic Routing                                     | 65 |

| 4.8 | Circuit Configuration for Multi-Board Operation                 | 66 |

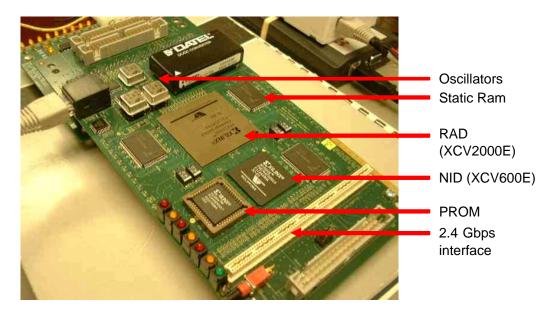

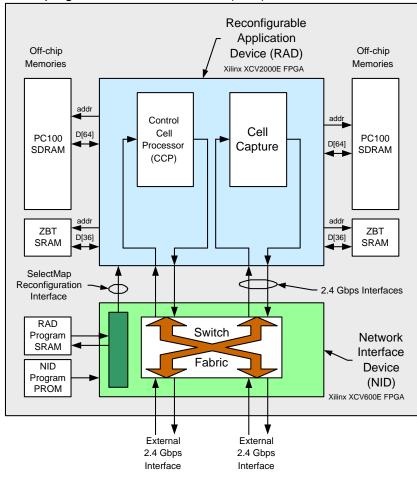

| 5.1 | Field Programmable Port Extender                                | 68 |

| 5.2 | Washington University Gigabit Switch Loaded with Four FPX Cards | 69 |

| 5.3  | FPX-in-a-Box System                                |

|------|----------------------------------------------------|

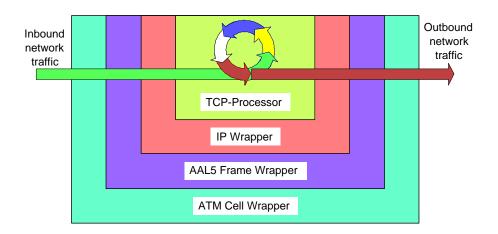

| 5.4  | Layered Protocol Wrappers                          |

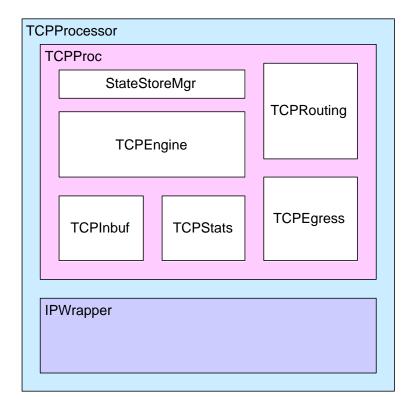

| 6.1  | Hierarchy of TCP-Processor Components              |

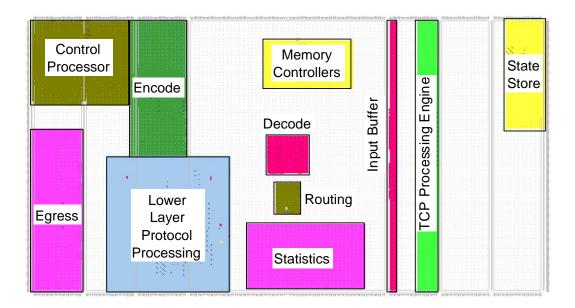

| 6.2  | TCPProcessor Layout                                |

| 6.3  | TCPProc Layout                                     |

| 6.4  | TCPInbuf Layout                                    |

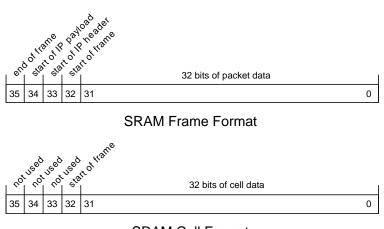

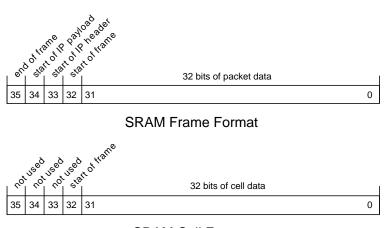

| 6.5  | SRAM data Formats                                  |

| 6.6  | TCPEngine Layout                                   |

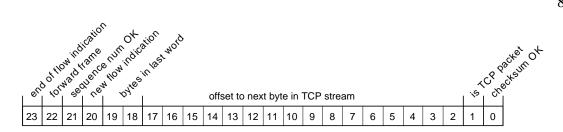

| 6.7  | Control FIFO data format                           |

| 6.8  | Data FIFO data format                              |

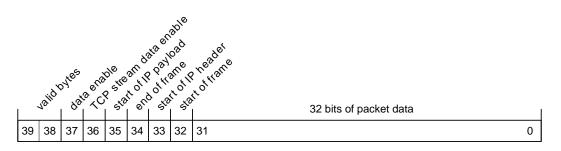

| 6.9  | Layout of StateStoreMgr                            |

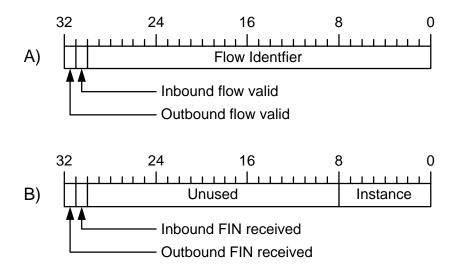

| 6.10 | Per-Flow Record Layout                             |

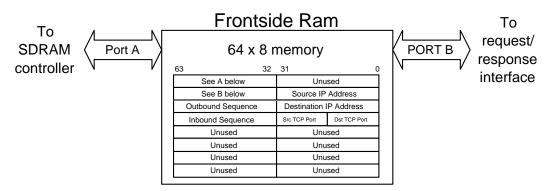

| 6.11 | Frontside RAM Interface Connections                |

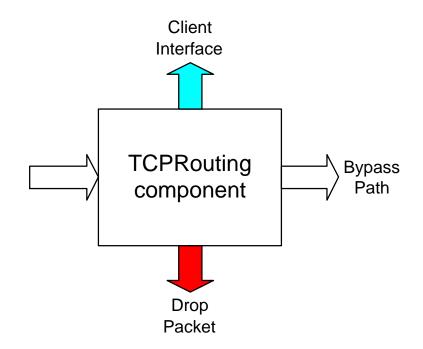

| 6.12 | TCPRouting Component                               |

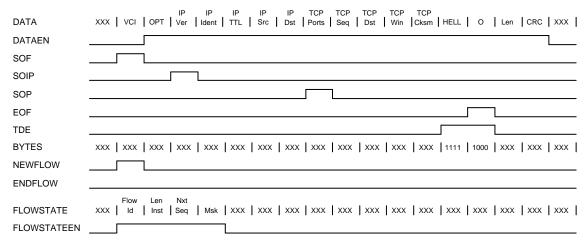

| 6.13 | TCP Outbound Client Interface                      |

| 6.14 | Flowstate Information                              |

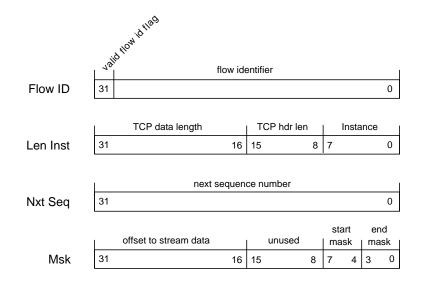

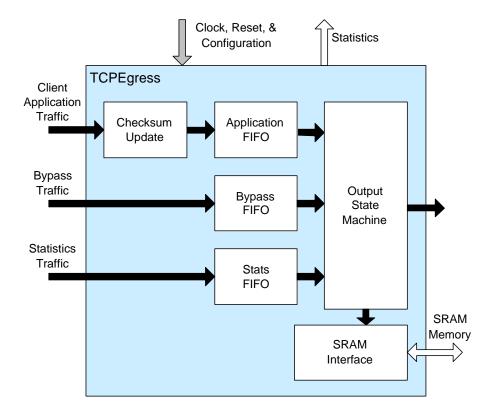

| 6.15 | TCPEgress Component                                |

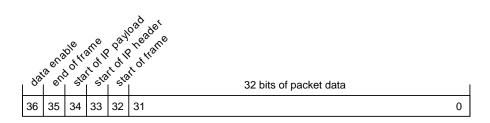

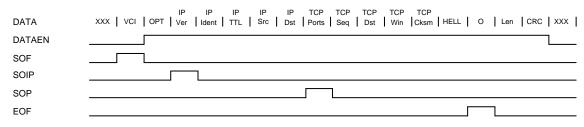

| 6.16 | TCPEgress FIFO Format                              |

|      | TCP Inbound Client Interface                       |

| 6.18 | Stats Packet Format                                |

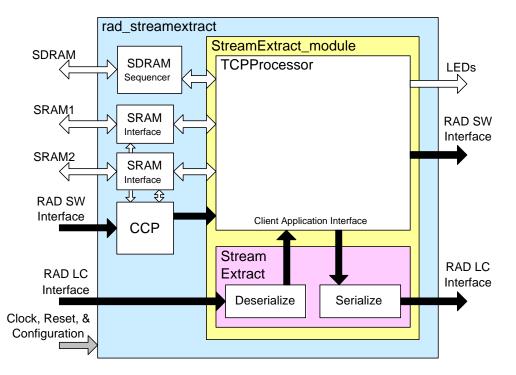

| 7.1  | StreamExtract Circuit Layout                       |

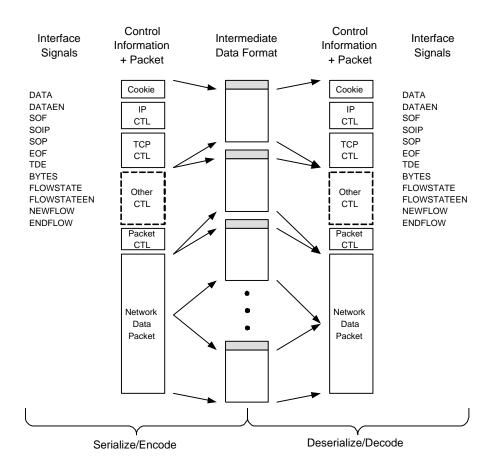

| 7.2  | Packet Serialization and Deserialization Technique |

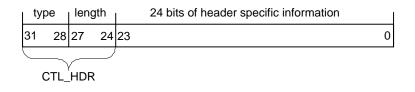

| 7.3  | Control Header Format                              |

| 7.4  | TCPSerializeEncode Circuit Layout                  |

| 7.5  | TCPSerializeDecode Circuit Layout                  |

| 7.6  | StreamExtract Circuit Layout on Xilinx XCV2000E    |

| 8.1  | PortTracker Circuit Layout                         |

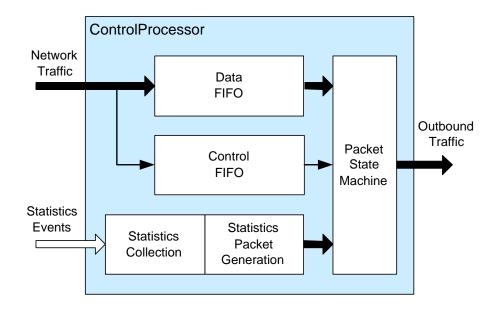

| 8.2  | PortTracker ControlProcessor Layout                |

| 8.3  | Scan Circuit Layout                                |

| 8.4  | ScanApp Circuit Layout                             |

| 8.5  | Scan ControlProcessor Layout                       |

| 8.6  | Scan Control Packet Format                         |

| 8.7  | Layout of StateStore                               |

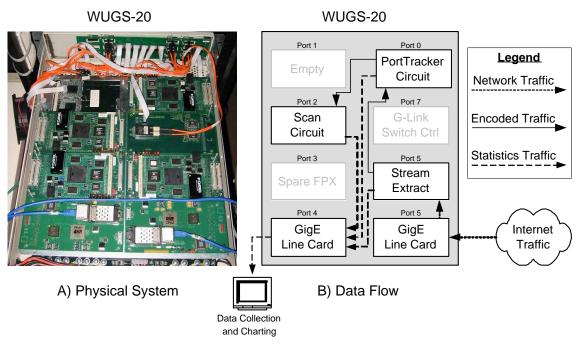

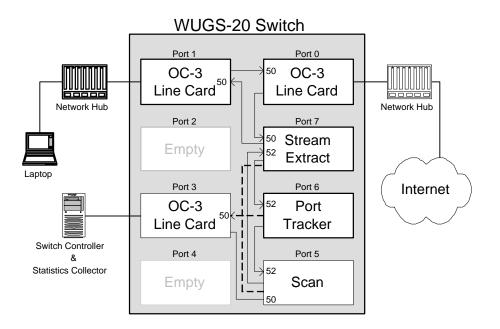

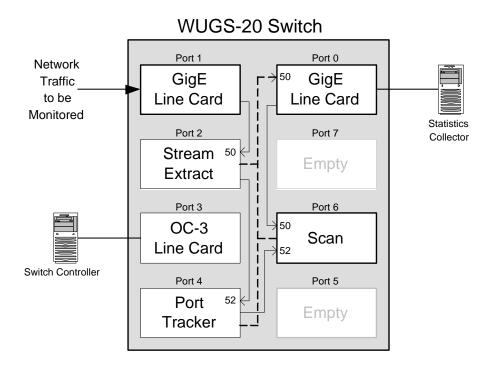

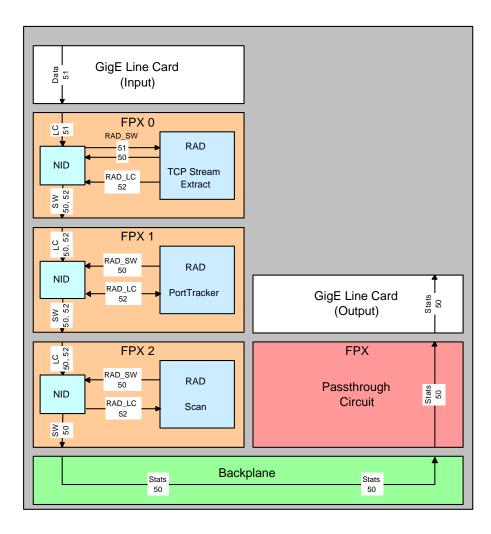

| 9.1         | Internet Traffic Monitor Configuration        |

|-------------|-----------------------------------------------|

| 9.2         | Statistics Collection and Presentation        |

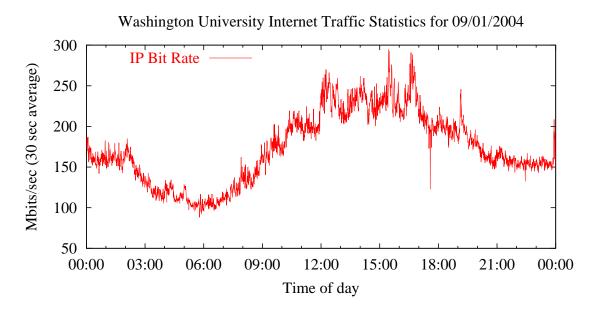

| 9.3         | IP Packet Data Rate                           |

| 9.4         | TCP SYN Flood DoS Attack                      |

| 9.5         | TCP SYN Burst                                 |

| 9.6         | MyDoom Virus Detection                        |

| 9.7         | Netsky Virus                                  |

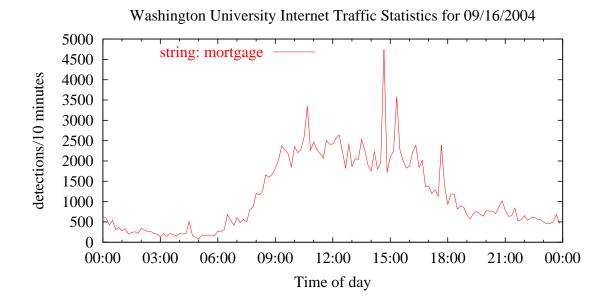

| 9.8         | Occurrences of the String "mortgage"          |

| 9.9         | IP and TCP Packets                            |

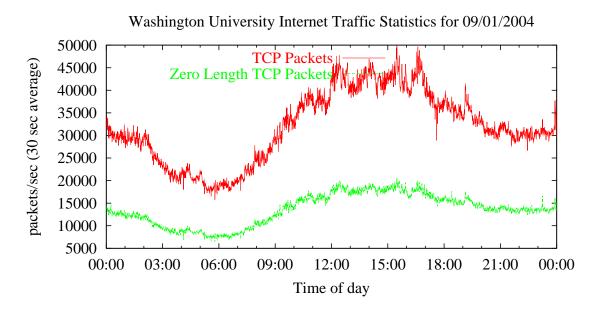

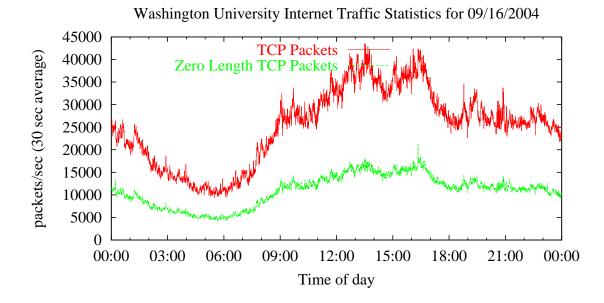

| 9.10        | Zero Length TCP Packets                       |

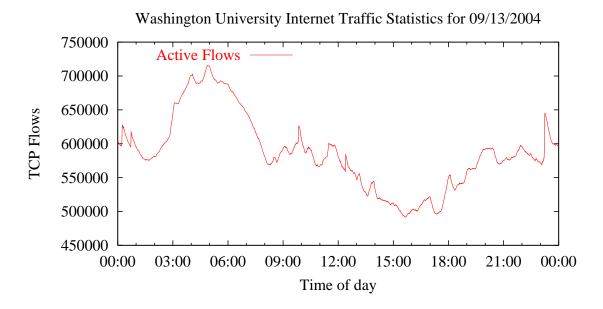

| 9.11        | Active Flows                                  |

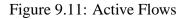

| 9.12        | Flow Transitions                              |

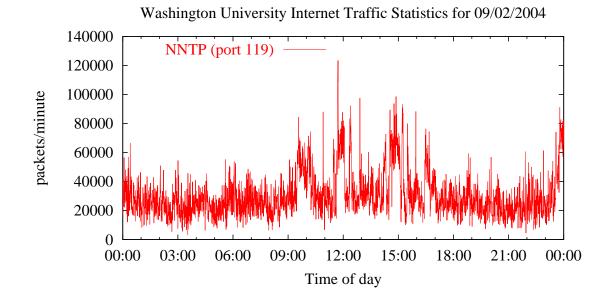

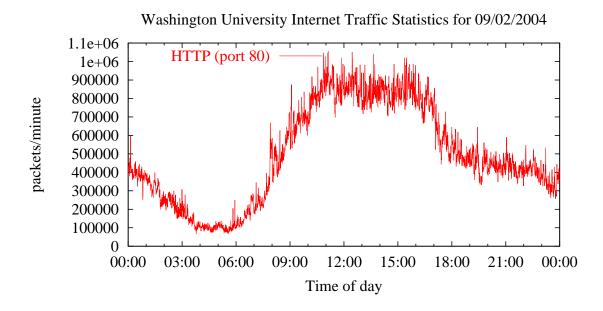

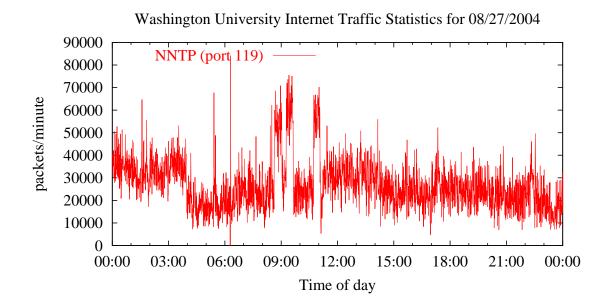

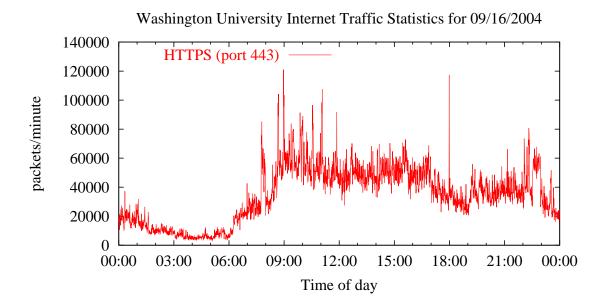

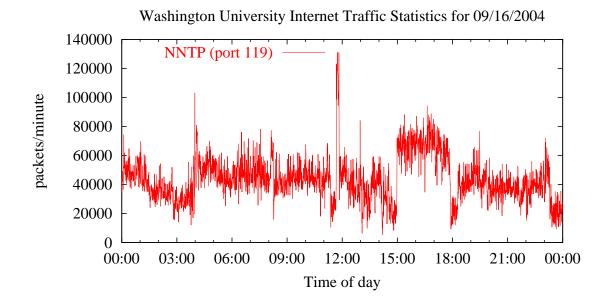

| 9.13        | NNTP Traffic                                  |

| 9.14        | HTTP Traffic                                  |

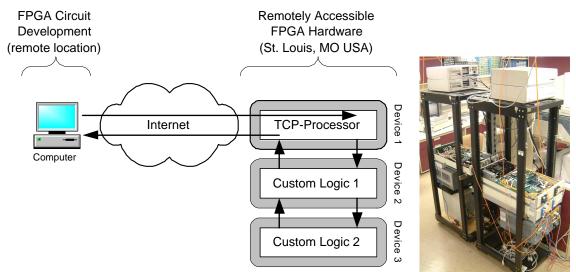

| 10.1        | Remote Research Access                        |

| 11.1        | Packet Store Manager Integration              |

| A.1         | Multidevice Circuit Layout                    |

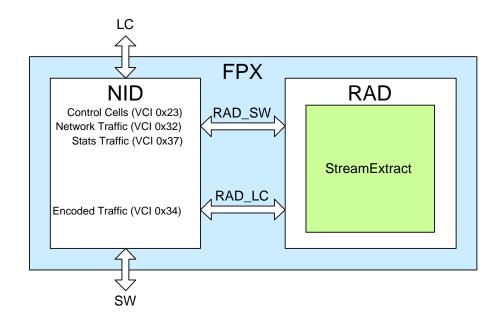

| A.2         | StreamExtract NID Routes                      |

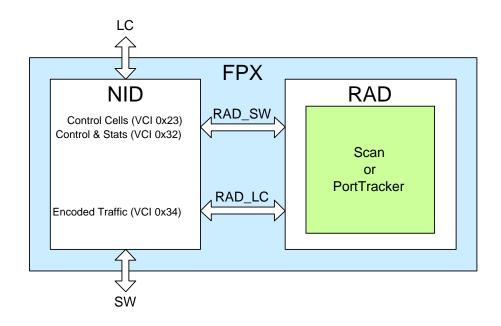

| A.3         | Scan/PortTracker NID Routes                   |

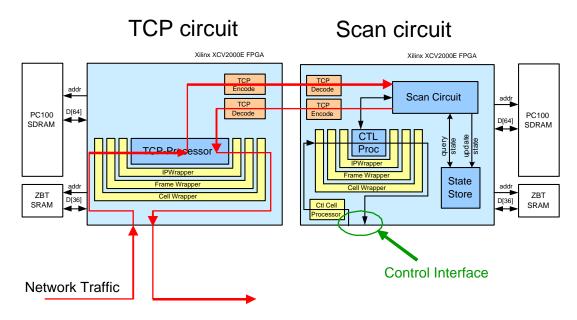

| A.4         | Multidevice Circuit Layout                    |

| A.5         | Active Monitoring Switch Configuration        |

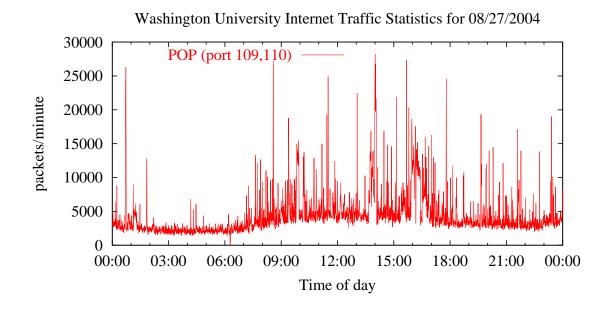

| A.6         | Passive Monitoring Switch Configuration       |

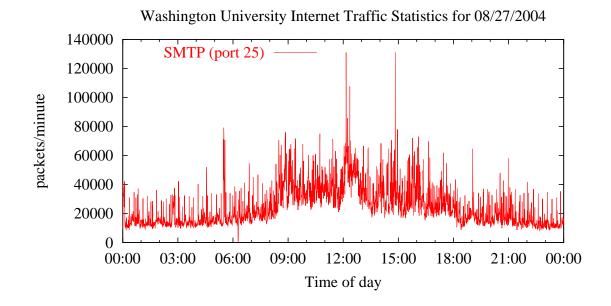

| A.7         | Passive Monitoring FPX-in-a-Box Configuration |

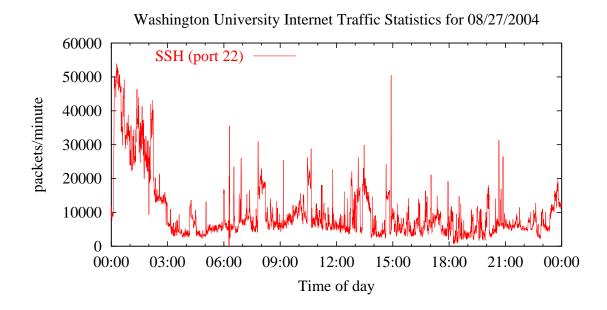

| <b>B</b> .1 | Operation of SRAMDUMP Utility                 |

| B.2         | SRAM data Formats                             |

| В.2<br>В.3  | CellCapture Circuit Layout                    |

| <b>D</b> .5 |                                               |

| C.1         | StatsCollector Operational Summary            |

| C.2         | Sample StatApp Chart                          |

| C.3         | Sample MRTG Generated Chart                   |

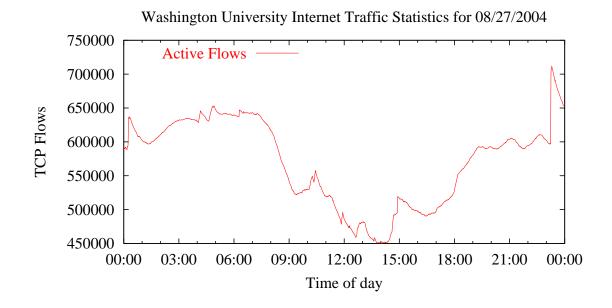

| D.1         | Active Flows                                  |

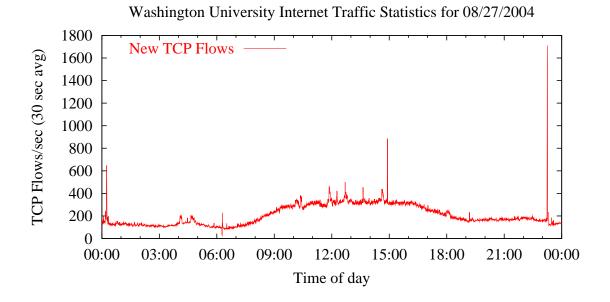

| D.1<br>D.2  | New Flows                                     |

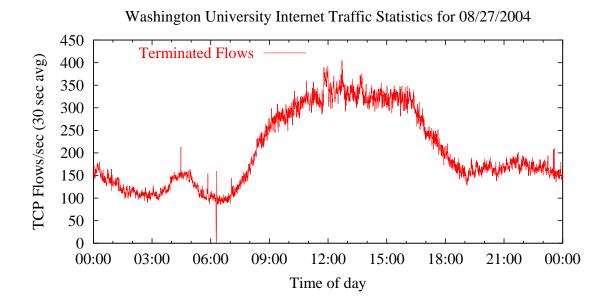

| D.3         | Terminated Flows                              |

| <b>-</b>    |                                               |

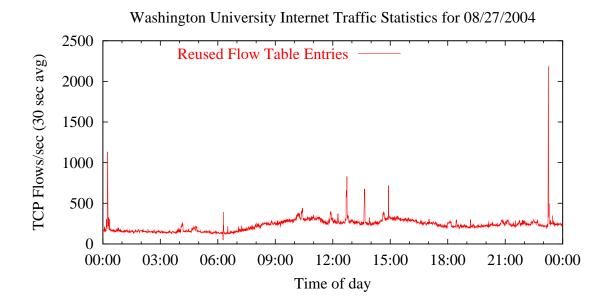

| D.4 Reused Flows           |

|----------------------------|

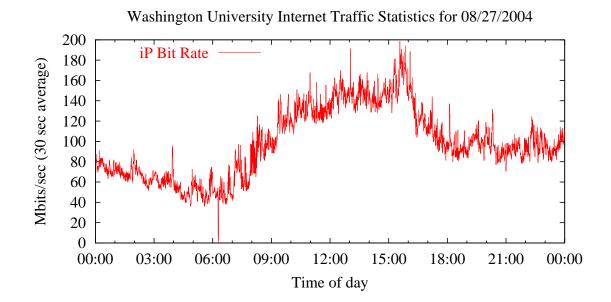

| D.5 IP bit rate            |

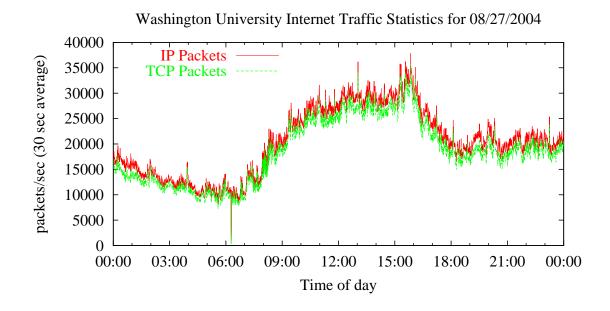

| D.6 IP Packets             |

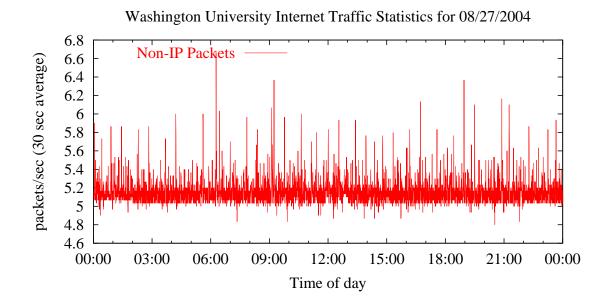

| D.7 Non-IP Packets         |

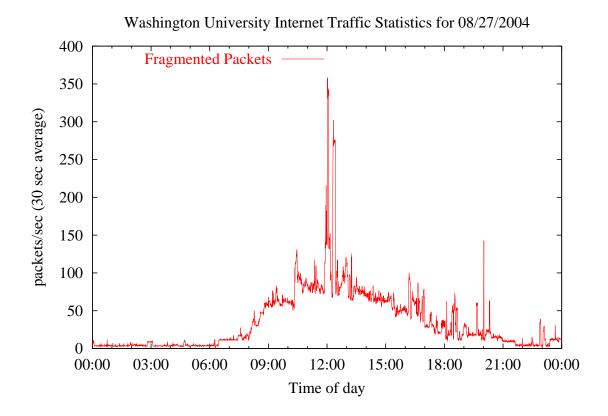

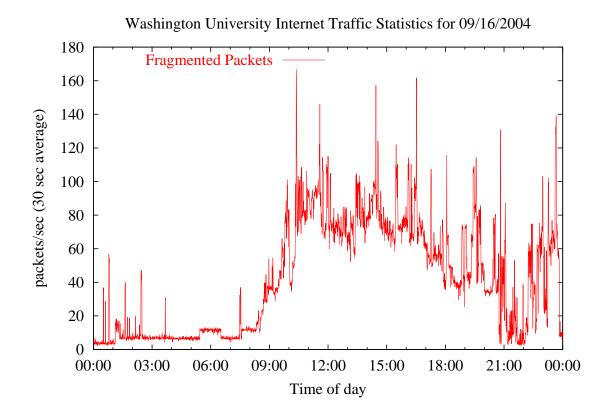

| D.8 Fragmented IP Packets  |

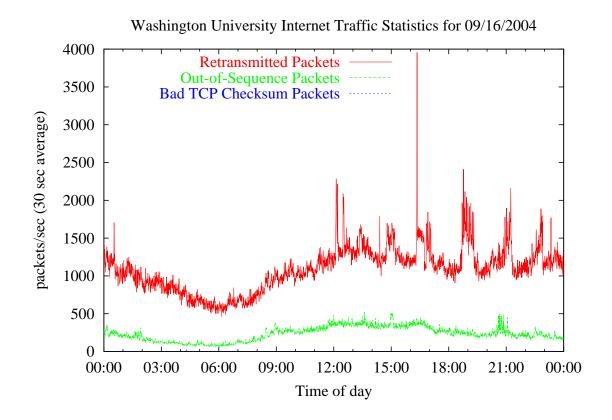

| D.9 Bad TCP Packets        |

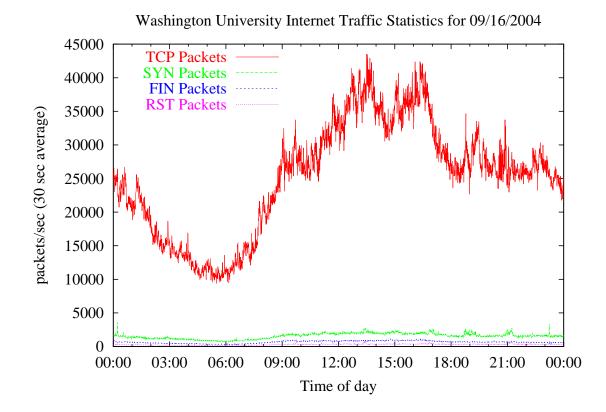

| D.10 TCP Packets           |

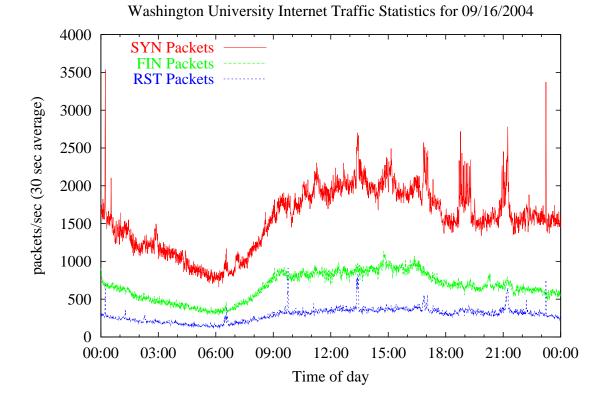

| D.11 TCP Packet Flags      |

| D.12 Zero Length Packets   |

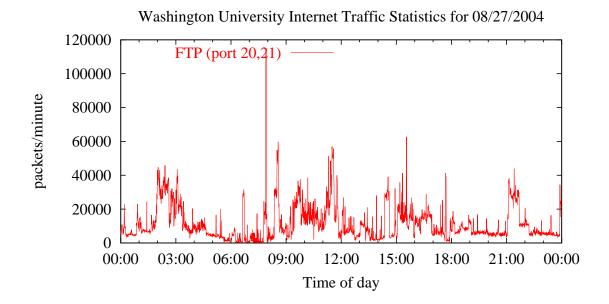

| D.13 FTP traffic           |

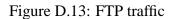

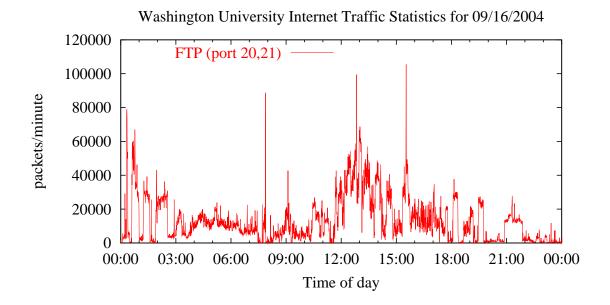

| D.14 HTTP traffic          |

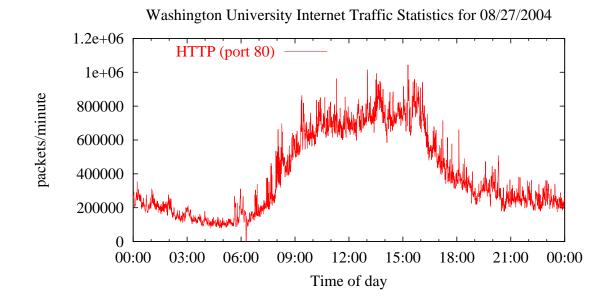

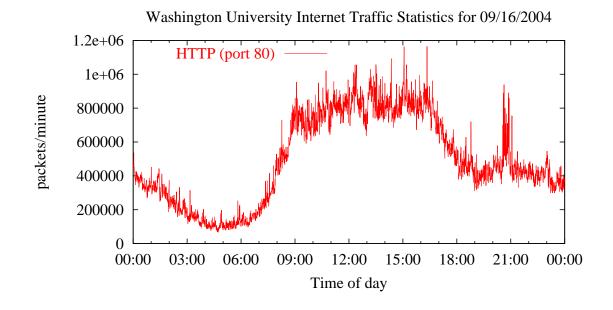

| D.15 HTTP traffic          |

| D.16 NNTP traffic          |

| D.17 POP traffic           |

| D.18 SMTP traffic          |

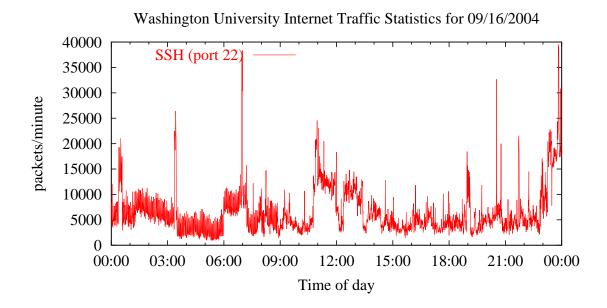

| D.19 SSH traffic           |

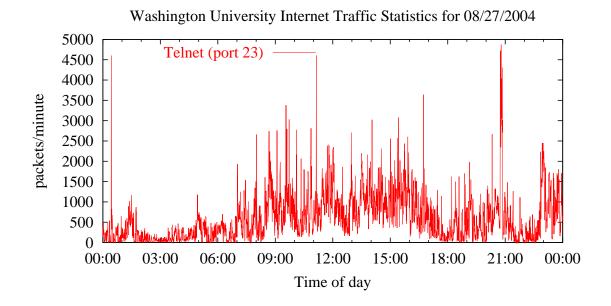

| D.20 Telnet traffic        |

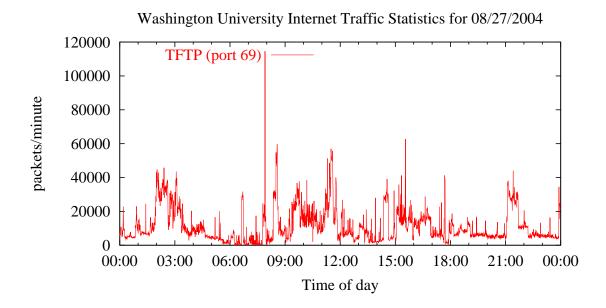

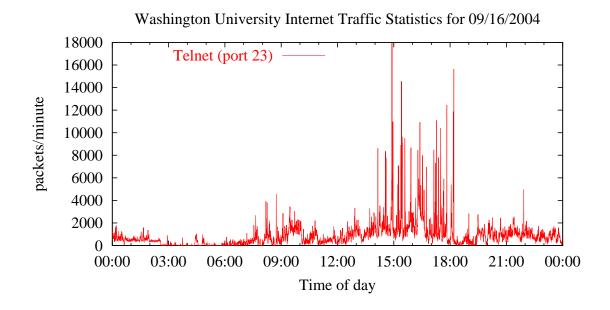

| D.21 TFTP traffic          |

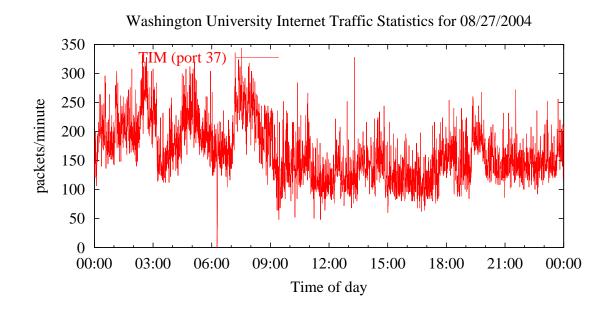

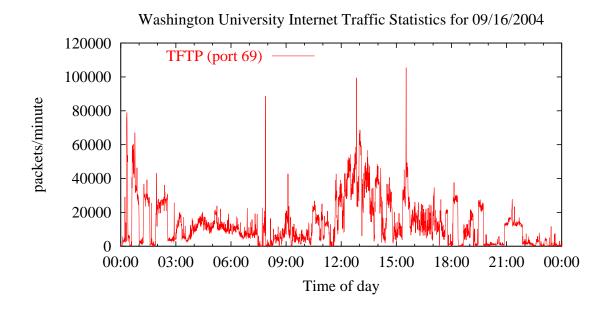

| D.22 TIM traffic           |

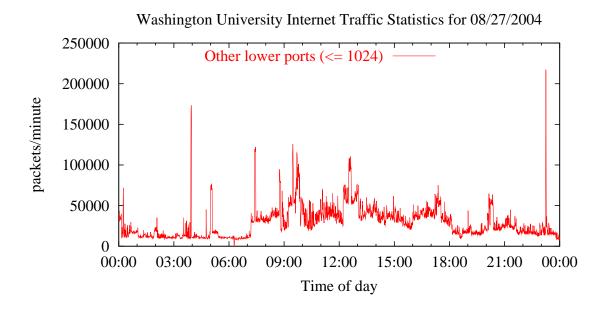

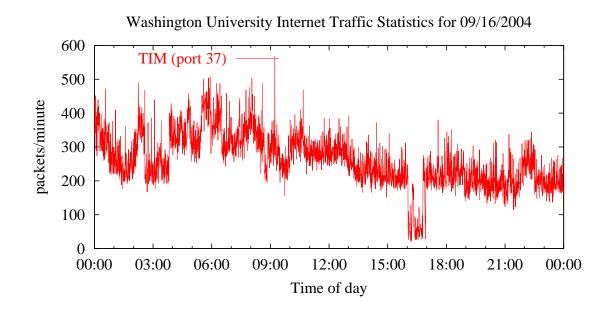

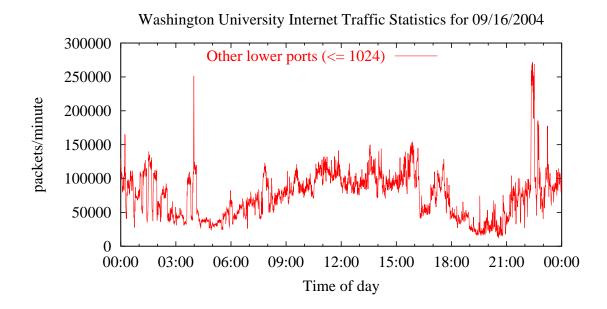

| D.23 Lower port traffic    |

| D.24 MyDoom Virus 1        |

| D.25 MyDoom Virus 2        |

| D.26 MyDoom Virus 3        |

| D.27 Spam                  |

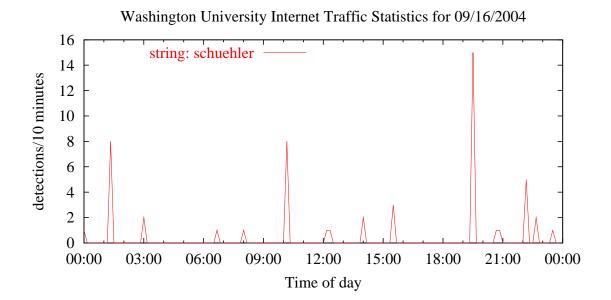

| D.28 Netsky Virus          |

| D.29 Active Flows          |

| D.30 New Flows             |

| D.31 Terminated Flows      |

| D.32 Reused Flows          |

| D.33 IP bit rate           |

| D.34 IP Packets            |

| D.35 Non-IP Packets        |

| D.36 Fragmented IP Packets |

| D.37 Bad TCP Packets       |

| D.38 TCP Packets           |

| D.39 TCP Packet Flags               |

|-------------------------------------|

| D.40 Zero Length Packets            |

| D.41 FTP traffic                    |

| D.42 HTTP traffic                   |

| D.43 HTTP traffic                   |

| D.44 NNTP traffic                   |

| D.45 POP traffic                    |

| D.46 SMTP traffic                   |

| D.47 SSH traffic                    |

| D.48 Telnet traffic                 |

| D.49 TFTP traffic                   |

| D.50 TIM traffic                    |

| D.51 Lower port traffic             |

| D.52 Scan for HTTP                  |

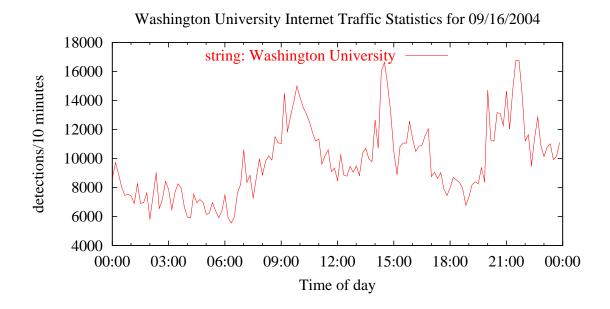

| D.53 Scan for Washington University |

| D.54 Scan for mortgage              |

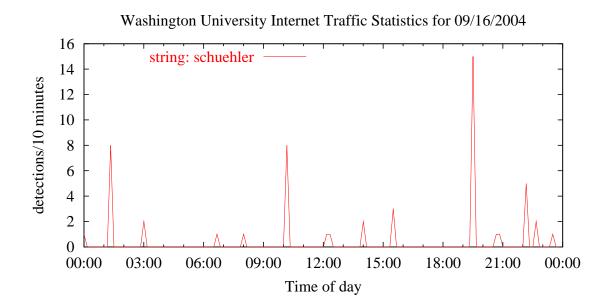

| D.55 Scan for schuehler             |

# Abbreviations

| AAL  | ATM Adaptation Layer                    |

|------|-----------------------------------------|

| ALU  | Arithmetic Logic Unit                   |

| ARL  | Applied Research Laboratory             |

| ARQ  | Automatic Repeat Request                |

| ASIC | Application Specific Integrated Circuit |

| ATM  | Asynchronous Transfer Mode              |

| BGP  | Border Gateway Protocol                 |

| CAM  | Content Addressable Memory              |

| CISC | Complex Instruction Set Computer        |

| CLB  | Configurable Logic Block                |

| CPU  | Central Processing Unit                 |

| DDR  | Double Data Rate (Memory)               |

| DMA  | Direct Memory Access                    |

| DoS  | Denial of Service                       |

| DRAM | Dynamic Random Access Memory            |

| DSP  | Digital Signal Processor                |

| FIFO | First-In First-Out queue                |

| FIPL | Fast Internet Protocol Lookup           |

- **FPGA** Field Programmable Gate Array

- **FPX** Filed-programmable Port Extender

- **FSM** Finite State Machine

- HEC Header Error Checksum

- HTTP Hyper Text Transfer Protocol

- IP Internet Protocol

- **IDS** Intrusion Detection System

- **IPS** Intrusion Prevention System

- **iSCSI** Internet SCSI

- **ISP** Internet Service Provider

- LC Logic Cell

- MAC Media Access Control

- MIB Management Information Base

- MTU Maximum Transmission Unit

- MRTG Multi Router Traffic Grapher

- NAS Network Attached Storage

- NIC Network Interface Card

- OC Optical Carrier

- PHY Physical Layer

- RAM Random Access Memory

- **RFC** Recursive Flow Classification

- **RISC** Reduced Instruction Set Computer

- SAN Storage Area Network

| SAR    | Segmentation and Reassembly                         |

|--------|-----------------------------------------------------|

| SCSI   | Small Computer Systems Interface                    |

| SDRAM  | Synchronous Dynamic Random Access Memory            |

| SNMP   | Simple Network Management Protocol                  |

| SRAM   | Static Random Access Memory                         |

| SSL    | Secure Sockets Layer                                |

| ТСАМ   | Ternary Content Addressable Memory                  |

| ТСР    | Transmission Control Protocol                       |

| TCP/IP | Transmission Control Protocol/Internet Protocol     |

| TOE    | TCP Offload Engine                                  |

| UTOPIA | Universal Test and Operations PHY Interface for ATM |

| VCI    | Virtual Channel Identifier                          |

| VHDL   | VHSIC Hardware Description Language                 |

| VHSIC  | Very High-Speed Integrated Circuit                  |

| VPI    | Virtual Path Identifier                             |

| WUGS   | Washington University Gigabit Switch                |

| ZBT    | Zero Bus Turnaround (memory devices)                |

# Acknowledgments

First and foremost, I would like to thank my parents, Jerry and Lois Schuehler. They have instilled in me a strong work ethic, a thirst for knowledge, and the confidence to achieve any goal. Without their love, support, and guidance, none of my accomplishments would have been possible.

I would like to thank my brother Chris for his friendship and companionship over the years. He has taught me many things and provided me the opportunity to participate in a variety of activities. We have had yearly excursions out west, rock climbing, back packing, mountain biking, snow skiing, hiking and camping.

I would also like to thank my sister Nancy and brother-in-law Jeff for helping me during my doctoral studies. Due to their proximity, they were called upon time and time again to take care of my dog, Fritz, while I was working late in the lab. They also provided me with a nephew, Nathan, who managed to brighten my days and offered a much needed distraction from school work.

Additional thanks goes out to Bertrand Brinley who wrote the *The Mad Scientists' Club* books [15, 16]. These books captivated me as a child and introduced me to the wonderful adventures awaiting those with an understanding of math, science and engineering.

I would also like to thank Scott Parsons, Don Bertier, Andy Cox, and Chris Gray for writing letters of recommendation. These recommendation letters were very flattering of my intellect and abilities, and continue to be a great source of pride for me. I do not believe that I would have been accepted into the doctoral program at Washington University without their compelling letters of recommendation.

Thanks also goes out to the Computer Science Department graduate committee at Washington University in St. Louis for accepting me into the doctoral program. They provided me with the opportunity to prove myself capable and accomplish this goal.

I would also like to thank all those at Reuters (formerly Bridge Information Systems) who supported my efforts to pursue a doctoral degree. My supervisor Scott Parsons, senior site officer Deborah Grossman, and coworker John Leighton deserve additional thanks for going out of their way to make this doctoral work possible.

James Hartley has been a friend and colleague since my freshman year of college in 1983. James and I share a passion for technical topics in the computer and networking fields. We spent many hours on the phone discussing various aspects of my graduate studies. His input as an impartial and independent party has been invaluable.

A special thanks goes out to Tanya Yatzeck who tirelessly reviewed much of my written work. In addition, Tanya nominated me for the St. Louis Business Journal 2004 Technology Award. The ensuing award and accompanying accolades would not have been possible if Tanya hadn't taken the initiative.

I would like to thank Jan Weller and Steve Wiese of Washington University Network Technology Services for providing live Internet traffic feeds which were used in the debugging and analysis phases of this research project. This network traffic was analyzed using the hardware circuits described in this dissertation.

No doctoral research project occurs in a vacuum, and this research is no exception. My interactions with the faculty, staff and students of the department of Computer Science and Engineering and the Applied Research Laboratory were invaluable in helping me complete this research work. I would especially like to thank Dr. Jon Turner, Dr. Ron Citron, Fred Kuhns, John DeHart, Dave Taylor, James Moscola, Dave Lim, Chris Zuver, Chris Neeley, Todd Sproull, Sarang Dharmapurikar, Mike Attig, Jeff Mitchell, and Haoyu Song.

This research work was supported in part by Global Velocity. I would like to thank Matthew Kulig and Global Velocity for supporting my research work.

I would like to thank the members of my thesis committee: Dr. John Lockwood, Dr. Chris Gill, Dr. Ron Loui, Dr. David Schimmel, and Dr. Ron Indeck.

I would like to give special thanks to my research advisor, Dr. John Lockwood, for his invaluable guidance and direction during my doctoral studies. He was a sounding board for thoughts and ideas and helped spur research in new directions.

Finally, I would like to thank my dog Fritz, who had to deal with a greatly reduced play schedule. He also had to endure long days and nights alone while I was working on the computer, doing research, writing papers, reading papers and doing homework.

Thank you all.

David Vincent Schuehler

Washington University in Saint Louis December 2004

# Preface

User application data moves through the Internet encapsulated in network data packets. These packets have a well-defined format containing several layered protocol headers and possibly trailers which encapsulate user data. The vast majority of Internet traffic uses the Transmission Control Protocol (TCP). The TCP implementation on the sending host divides user application data into smaller transmission segments and manages the delivery of these segments to remote systems. The protocol stack on the remote system is responsible for reassembling the segments back into the original data set, where it is presented to the user or the application.

Extensible networking services, like those that detect and eliminate Internet worms and computer viruses as they spread between machines, require access to this user application data. These services need to process the various protocols in order to reassemble application data, prior to performing any detection or removal operations. TCP processing operations similar to those which occur in protocol stacks of end systems are necessary.

Large, high-speed routers and switches are used to route data through the interior of the Internet because they are capable of handling traffic from millions of end systems at multi-gigabit per second data rates. To operate within this environment, extensible networking services need to process millions of packets per second. Existing services which block Internet worms and computer viruses do not have sufficient throughput to operate on a network backbone.

This dissertation investigates the problems associated with high performance TCP processing systems and describes an architecture that supports flow monitoring in extensible networking environments at multi-gigabit per second data rates. This architecture provides stateful flow tracking, TCP stream reassembly services, context storage, and flow manipulation services for applications which monitor and process TCP data streams. An FPGA-based implementation of this architecture was used to analyze live Internet traffic.

# Chapter 1

## Introduction

Studies show that over 85% of the network packets on the Internet utilize Transmission Control Protocol (TCP) [112]. Content-aware networking services, like data security and content scanning, need to look inside of TCP flows in order to implement higher levels of functionality. In order to accomplish this, the TCP processing must be capable of reconstructing data streams from individual network packets. TCP processing systems capable of achieving this in gigabit speed networking environments do not currently exist.

New protocol processing systems are necessary to satisfy the current and future needs of content-aware network services. These services will have a greater impact on network traffic when located with large routers processing traffic on high-speed network connections exceeding 2Gbps. These types of routers are also most likely to contain extensible networking technology.

The concept of extensible networking implies that reconfigurable and reprogrammable elements exist within the network which can be altered, or extended, during the normal operation of the network. Extensible networking switches may employ applicationspecific integrated circuits (ASICs), field-programmable gate arrays (FPGAs), network processors, or general purpose microprocessors which can be programmed or configured to operate on the network traffic which transits the switch. Extensible networking environments can enhance the end user's experience by incorporating value-added services into the network infrastructure. In order to be effective, services which operate in these environments require access to the application level data which traverses the network. This research involves the design and implementation of a TCP processing system which makes application data available to high-speed network services. A simple, hardware-based application interface provides the means by which data processing circuits can easily access the payload contents of TCP flows.

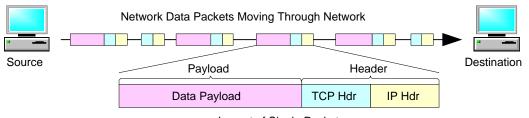

Layout of Single Packet

#### Figure 1.1: Anatomy of a Network Packet

| <sup>31</sup> <sup>30</sup> <sup>29</sup> <sup>28</sup> | 27   26   25                                    | <sup>5</sup>   <sup>24</sup> | 23 | <sup>22</sup> | <sup>21</sup> | 20 | 19  | <sup>18</sup> | 1 <sup>1</sup> | 7   10 | ٦ſ     | 15   1 | 4 1 | <sup>3</sup>   <sup>1</sup> | <sup>2</sup> | <sup>11</sup> | 10 | 9 | ۱٤ | · ۱ | 7  | 6 | Ľ | 5 | 4 | 3 | l i | <sup>2</sup> | 1 | 0 | I |        |

|---------------------------------------------------------|-------------------------------------------------|------------------------------|----|---------------|---------------|----|-----|---------------|----------------|--------|--------|--------|-----|-----------------------------|--------------|---------------|----|---|----|-----|----|---|---|---|---|---|-----|--------------|---|---|---|--------|

| Version                                                 | Version Hdr length Type of service Total length |                              |    |               |               |    |     |               |                |        | Ν      |        |     |                             |              |               |    |   |    |     |    |   |   |   |   |   |     |              |   |   |   |        |

| Identification Flags Fragment offset                    |                                                 |                              |    |               |               |    |     |               |                |        | ₽      |        |     |                             |              |               |    |   |    |     |    |   |   |   |   |   |     |              |   |   |   |        |

| TT                                                      | TTL Protocol Header checksum                    |                              |    |               |               |    |     |               |                |        | -      |        |     |                             |              |               |    |   |    |     |    |   |   |   |   |   |     |              |   |   |   |        |

|                                                         | Source IP address                               |                              |    |               |               |    |     |               |                |        | Header |        |     |                             |              |               |    |   |    |     |    |   |   |   |   |   |     |              |   |   |   |        |

| Destination IP address                                  |                                                 |                              |    |               |               |    |     |               | er             |        |        |        |     |                             |              |               |    |   |    |     |    |   |   |   |   |   |     |              |   |   |   |        |

| Options & padding (optional)                            |                                                 |                              |    |               |               |    |     |               |                |        |        |        |     |                             |              |               |    |   |    |     |    |   |   |   |   |   |     |              |   |   |   |        |

|                                                         | Source port Destination port                    |                              |    |               |               |    |     |               |                | Ν      | l l    |        |     |                             |              |               |    |   |    |     |    |   |   |   |   |   |     |              |   |   |   |        |

|                                                         | Sequence number                                 |                              |    |               |               |    |     |               |                | ТCР    |        |        |     |                             |              |               |    |   |    |     |    |   |   |   |   |   |     |              |   |   |   |        |

|                                                         |                                                 |                              |    |               |               |    | Ad  | ckno          | ow             | edg    | me     | enti   | num | ber                         | •            |               |    |   |    |     |    |   |   |   |   |   |     |              |   |   |   |        |

| Hdr length                                              | Res                                             | serve                        | d  |               |               |    | Fla | ags           |                |        |        |        |     |                             |              |               |    |   | Wi | ndo | ow |   |   |   |   |   |     |              |   |   |   | Header |

| Checksum Urgent pointer                                 |                                                 |                              |    |               |               |    |     |               | der            |        |        |        |     |                             |              |               |    |   |    |     |    |   |   |   |   |   |     |              |   |   |   |        |

|                                                         | Options & padding (optional)                    |                              |    |               |               |    |     |               |                |        |        |        |     |                             |              |               |    |   |    |     |    |   |   |   |   |   |     |              |   |   |   |        |

#### Figure 1.2: IP(v4) and TCP Headers

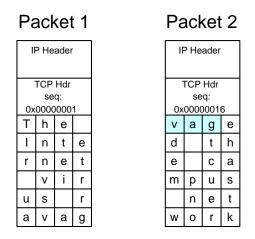

Data in TCP flows moves through the Internet encapsulated in network packets. Every packet contains a header section and possibly a payload section. The header section can be further subdivided to provide information about encapsulated protocols. Figure 1.1 shows the layout of TCP packets moving through the network. Each packet contains an Internet Protocol (IP) header, a TCP header, and possibly a data payload section.

To exchange information over a network, a TCP connection is established between two end systems. Information placed in the payload section of one or more packets is delivered to the remote system. As these packets traverse the Internet, they can be dropped, reordered, duplicated, or fragmented while they make their way to the destination host. It is the responsibility of the TCP implementation on the end systems to provide end-to-end reordering and retransmission services.

Figure 1.2 shows a diagram of the header fields for TCP and IP version 4. The IP header fields include packet routing information which is used by network equipment to deliver packets to the proper end destination. The information contained in the IP header is similar in function to the address on traditional courier-based mail. The TCP header fields

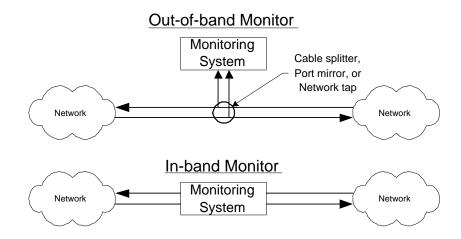

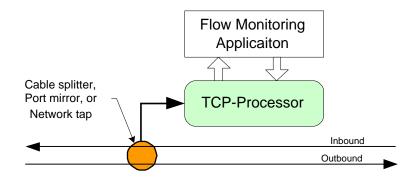

Figure 1.3: Types of Network Monitors

provide information needed to reconstruct data streams from individual network packets. In addition, these header fields contain data needed to perform connection setup and teardown, packet retransmissions, and localized packet delivery information.

Network monitors can be classified as either out-of-band or in-band, as illustrated in Figure 1.3. An out-of-band network monitor is a passive device and is typically implemented with a cable splitter, a network tap, port replication or other content duplicating technique which delivers a copy of the network traffic to the monitor. Passive monitors have no means by which to alter network content. In contrast, an in-band network monitor resides within the data path of the network and can alter network traffic by either inserting, dropping, or modifying packets. As an in-band network monitor, the TCP processing system presented in this dissertation provides a flexible platform upon which either passive or active extensible networking services can be developed.

Processing higher level protocols, such as TCP, is a complex task. This complexity is increased when operating on multi-gigabit links in high-speed networking environments, potentially dealing with millions of packets per second and processing millions of active TCP connections in the network at any one time. Data monitoring and processing applications are varied and have a broad range of resource requirements. Simple applications like those that count data bytes or represent traffic patterns may have relatively small implementations. In contrast, applications which detect and eliminate many different types of Internet worms and viruses may utilize substantially more resources. Specialized applications which implement custom network security features may also require complex processing operations for every packet on the network. Limitations in chip densities prevent these large, complex applications from being completely implemented in a single device. A system using multiple processing devices would support these complex applications. In order for this type of design to work, efficient mechanisms are required for coordinating tasks amongst the multiple devices.

This dissertation presents a hardware circuit called the TCP-Processor which is capable of reassembling TCP data flows into their respective byte streams at multi-gigabit line rates. The reference implementation contains a large per-flow state store which supports 8 million bidirectional TCP flows. Additional logic enables the payload contents of a TCP flow to be modified. To support complex flow processing applications, a flexible and extensible data encoding system has been developed which enables data passing and task coordination between multiple devices. This technology enables a new generation of content-aware network services to operate within the core of the Internet.

### **1.1 Problem Framework**

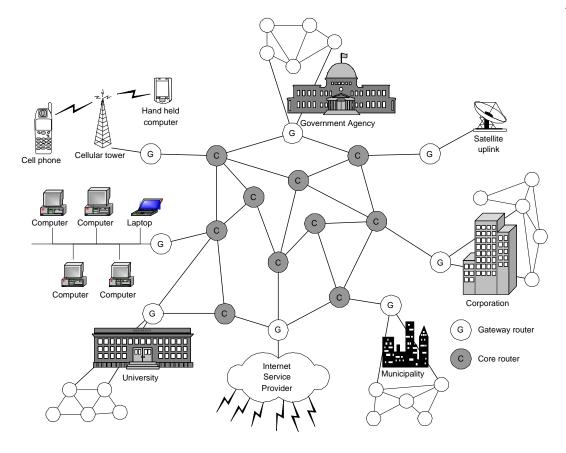

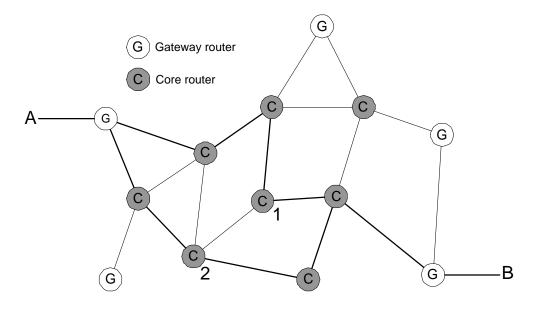

A large heterogenous network, such as the Internet, provides network connectivity between a vast number of end systems and autonomous environments. Figure 1.4 shows a representative network topology. The interior of the network is made up of core routers - responsible for routing data through the interior of the network - and gateway routers. Each gateway router provides a single point of entry into the network for an external organization. Many different types of organizations, including government agencies, corporations, municipalities, and universities connect to the network by interfacing with a gateway router. Cell phones and handheld computers connect to the network through cellular towers to carriers which provide access to the Internet. In addition, Internet Service Providers (ISPs) provide communication services to individual and organizational customers, and satellite and fiber-optic links interconnect wide-area networks.

Due to the vast number of end systems which communicate over the Internet and the relatively small number of routers which forward traffic in the interior of the network, communication between these routers occurs at a very high bandwidth. Currently, interconnects typically operate over communication links ranging in speed from OC-3 to OC-768. Network routers capable of communicating at 160 Gigabits/second are expected in the future. Table 1.1 compares the various types of communication links, their corresponding data rates, and the rate at which packets of different sizes can be transmitted over those links.

Figure 1.4: Heterogenous Network

## **1.2 Problem Statement**

There are distinct advantages associated with consolidating common network services. In addition to running data security, data compression, intrusion prevention, and virus elimination applications on end systems, applications can be moved into the network at gateway routers. Running these applications in the network reduces the administrative overhead of managing the number of installation points. Large organizations may have thousands of end systems to manage. Instantly updating virus filters on all end systems in the face of a new worm or virus outbreak can be a daunting task. In contrast, updating a few well-placed network appliances positioned within the network can provide protection from the virus outbreak in a fraction of the time required to update all end systems.

Universities and Internet Service Providers (ISPs) have networks where the network administrators do not have access to or control of the machines connected to the network. Student computers and client ISP systems are connected to these networks, but the network

|                |           | 40 byte  | 64 byte  | 500 byte | 1500 byte |

|----------------|-----------|----------|----------|----------|-----------|

| Link type      | Data rate | pkts/sec | pkts/sec | pkts/sec | pkts/sec  |

| OC-3           | 155 Mbps  | .48 M    | .3 M     | 38 K     | 12 K      |

| OC-12          | 622 Mbps  | 1.9 M    | 1.2 M    | .16 M    | 52 K      |

| GigE           | 1.0 Gbps  | 3.1 M    | 2.0 M    | .25 M    | 83 K      |

| OC-48          | 2.5 Gbps  | 7.8 M    | 4.8 M    | .63 M    | .21 M     |

| OC-192/10 GigE | 10 Gbps   | 31 M     | 20 M     | 2.5 M    | .83 M     |

| OC-768         | 40 Gbps   | 125 M    | 78 M     | 10 M     | 3.3 M     |

| OC-3072        | 160 Gbps  | 500 M    | 312 M    | 40 M     | 13 M      |

Table 1.1: Optical links and associated data rates

operations staff has no ability to patch or upgrade the end systems. In these types of environments, data security, intrusion detection, and worm and virus preventions systems have to occur within the fabric of the network. Furthermore, with the widespread acceptance of cellular and wireless technologies, computer systems can quickly appear and disappear from the network, only to reappear later in a different part of the network.

Data security applications which prevent the dissemination of proprietary or confidential documents to outside parties are ideally suited for placement at the interface to the external network. This type of security solution would allow confidential and proprietary documents to be passed freely amongst computers within an organization, but prevents their transmission to non-trusted systems outside the organization.

Most existing network monitoring systems which perform data security and intrusion prevention tasks are software-based. These systems have performance limitations which prevent them from operating within high-speed networked environments. The research associated with this dissertation addresses the performance limitations associated with existing network services.

This dissertation presents an architecture for a high-speed TCP processing system which provides access to TCP stream content at locations within the network. The architecture is capable of processing traffic at multi-gigabit per second data rates and supports the monitoring and processing of millions of active TCP flows in the network.

## **1.3** Contributions

The main focus of this research involves the design, development, and implementation of hardware circuits which are able to process TCP flows within the context of multi-gigabit per second communication links. The primary contributions of this research are:

- The definition of a high-performance TCP flow processing architecture, called TCP-Processor, capable of processing large numbers of active TCP connections traversing multi-gigabit network links. A hardware implementation of this architecture supports the processing of 8 million simultaneous TCP connections on a network link operating at 2.5Gbps.

- An architecture that coordinates high-performance packet processing circuits operating on separate devices by defining an inter-device transport protocol. This protocol is extensible, which allows for future enhancements and extensions without requiring modifications to the underlying protocol specification. The self-describing nature of the protocol allows previous versions of the processing circuits to work with newer extensions which do not pertain to that specific component.

- An analysis of live Internet traffic processed by hardware circuit implementations of the TCP processing architecture. Network traffic travelling between the Washington University campus network and the Internet was processed by the TCP flow monitoring circuits outlined in this dissertation. Statistics collected while processing this traffic are analyzed and presented.

Additional contributions presented in this dissertation include the development of two sample TCP flow monitoring applications, PortTracker and Scan, which illustrate how to interface with the TCP-Processor to perform TCP flow processing on large numbers of active flows at multi-gigabit data rates. Furthermore, it defines a common statistics packet format which is used by the TCP flow processing circuits and by other researchers at the Applied Research Laboratory. It also presents extensible data collection and charting utilities which have been developed to aid in the collection and presentation of the monitored statistics. Detailed documentation on the design, layout, and operation of the various TCP processing circuits is provided. The appendices include setup, configuration, and usage instructions so that other investigators have the information necessary to either reproduce or extend this research.

## **1.4 Organization of Dissertation**

Chapter 1 provides introductory material and an overview of the problem domain. The problem framework and a problem statement are discussed along with the contributions of the dissertation and the organization of the dissertation.

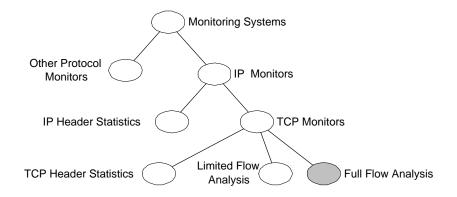

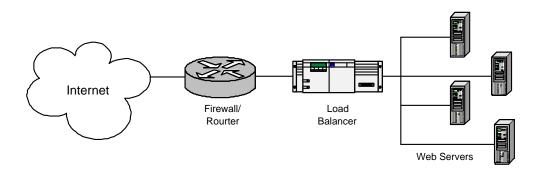

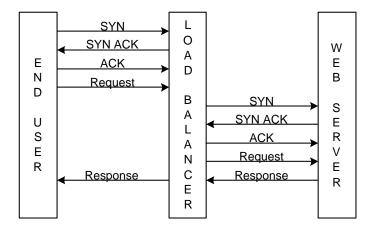

Chapter 2 provides background and motivation information for the dissertation. It discusses the currently available computing platforms along with their relative merits for use in high-performance network data processing systems. This chapter also covers a thorough review of the challenges associated with protocol processing in high-speed networks. Chapter 3 examines related work in network monitoring and processing systems. It presents a taxonomy of network monitors to show the problem domain of the research relating to this dissertation. It also discusses other software-based and hardware-based network monitors, along with their features and shortcomings. In addition, this chapter presents current research in packet classification techniques and covers information on other types of network devices. These devices include load balancers, Secure Sockets Layer (SSL) accelerators, intrusion detection systems and TCP offload engines; all of which require protocol processing operations similar to those presented in this dissertation. Finally, this chapter presents current research involving hardware-accelerated content scanners to showcase a class of applications which are ideal candidates for integration with the TCP-Processor.

Chapter 4 provides an overview of the TCP processing architectures developed as part of this research. Initial investigations into high-performance TCP processing in hardware circuits led to the development of the TCP-Splitter technology. The knowledge gained through this research contributed to the development of the TCP-Processor technology. This chapter describes both of these architectures.

Chapter 5 provides information regarding the testing environment where the TCP-Processor was developed, refined, and analyzed. This environment includes hardware platforms, circuit designs, and control software. This chapter discusses each of the components of this environment.

Chapter 6 provides detailed descriptions of the implementation and internal operation of the TCP-Processor circuit. Implementation details of each circuit component are discussed separately, providing insight into the operation and interaction among the various components. This chapter also describes the lightweight client interface which provides easy access to TCP stream content for large numbers of TCP connections in an efficient manner. Chapter 7 examines the StreamExtract circuit. This circuit forms the basis for all multi-device TCP processing designs. This chapter includes a description of the data encoding and decoding techniques which allow annotated network traffic to pass easily between devices. It describes the encoded data format, highlighting the extensible and expandable features of the protocol.

Chapter 8 discusses the TCP-Lite Wrappers which provide access to TCP stream content in multi-device TCP processing environments. These wrappers include lightweight hardware circuits which decode and re-encode TCP stream traffic. This includes exposure of a client interface which is identical to the interface of the TCP-Processor. In addition to the TCP-Lite Wrappers, this chapter presents PortTracker and Scan as example circuits which use this wrapper to perform TCP flow processing. The PortTracker circuit keeps track of the number of packets sent to or received from various well known TCP ports. The Scan circuit searches TCP stream content for up to four 32-byte signatures.

Chapter 9 analyzes live Internet traffic using the TCP flow processing technology presented in this dissertation. It consists of the examination of the Internet traffic for the Washington University campus network during a five week period.

Chapter 10 summarizes the work and contributions of this dissertation and provides concluding remarks. It presents information regarding the lessons learned while processing live Internet traffic along with information on some of the tools developed to aid in the debugging process. Finally, it presents information on the utility of the TCP-Processor.

Chapter 11 describes future directions for high-performance TCP processing research. This includes extensions to the TCP-Processor, increasing the current capabilities and performance. It also covers integration with TCP flow processing applications.

Appendix A describes usage information for the various TCP processing circuits. It provides specific information on how to build, configure and use the TCP processing circuits described in this dissertation. This information will enable other researchers to easily reproduce and validate the results of this research and provide a starting point for performing other advanced TCP flow processing research in high-speed networking environments.

Appendix B discusses several different methods of capturing traffic and generating simulation input files. It describes several hardware circuits and software-based tools developed as part of this research to provide the functional debugging and verification tools required to validate the operation and performance of the TCP Processor. These include hooks added to all of the TCP processing circuits which allow network traffic and associated context data to be stored into external memory devices. In addition, this appendix

includes a description of software routines that can extract and format this data from memories so it can be used easily by the hardware circuit simulation tool, ModelSim. Finally, this appendix describes the operation and use of these hardware and software data capturing and formatting tools.

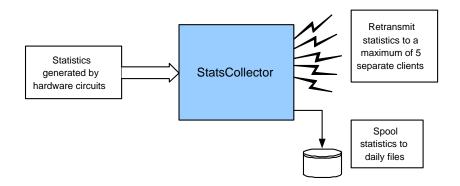

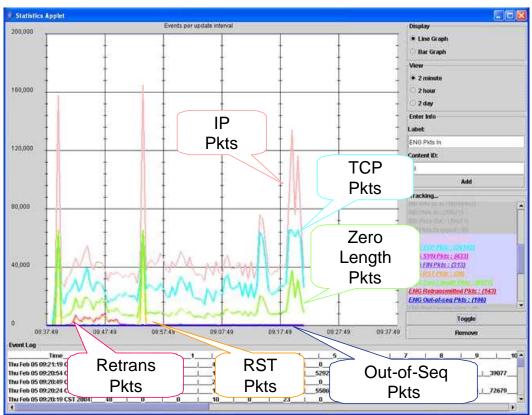

Appendix C describes the statistics gathering and charting routines used in conjunction with the circuits described in this dissertation. A StatsCollector application collects statistics information generated by the various TCP processing circuits and writes the data to daily disk files. A Simple Network Management Protocol (SNMP) sub-agent captures this same statistics information, accumulates ongoing event counters, and republishes the data as SNMP variables which can be accessed easily using industry standard network management tools. A configuration file for the Multi Router Traffic Grapher (MRTG) commands MRTG to generate daily, weekly, monthly and yearly charts of each of the statistics values produced by the TCP processing circuits.

Appendix D contains additional traffic charts obtained by analyzing the Washington University Internet traffic. The charts examine traffic collected on August 27th, 2004 and September 16th, 2004.

# Chapter 2

# **Background and Motivation**

Existing network monitors are unable to both (1) operate at the high bandwidth rates and (2) manage the millions of active flows found in today's high-speed networks. Instead, network monitors typically perform monitoring activities on end systems or in local area networks where the overall bandwidth and the total number of flows to be processed is low. In the future, many other types of network services will require access to the TCP stream data traversing high-speed networks. Such services may include the following applications:

- Worm/virus detection and removal

- Content scanning and filtering

- Spam detection and removal

- Content-based routing

- Data security

- Data mining

- Copyright protection

- Network monitoring

The research outlined in this dissertation enables these services to operate at multigigabit speeds by defining and implementing a hardware-based architecture capable of high-performance TCP processing. The resulting architecture provides a flexible environment in which any high performance data processing application can be implemented.

A service which detects and prevents the spread of Internet worms and computer viruses is ideally suited for this technology. Since worms and viruses spread very quickly, prevention techniques which involve human interaction are essentially ineffective. Humans are not capable of reacting quickly enough to stop worm and virus attacks from spreading.

These types of attacks require automated prevention techniques for containment and prevention of widespread infections [140]. In addition, the direct costs associated with these attacks could negatively affect the global economy. Table 2.1 provides analysis of the costs associated with several recent attacks on the Internet.

|      | Worldwide       |                           |

|------|-----------------|---------------------------|

|      | Economic Impact | Representative            |

| Year | (\$ U.S.)       | Attacks (cost)            |

| 2003 | \$236 Billion   | Sobig.F (\$2 Billion)     |

|      |                 | Blaster (\$1.3 Billion)   |

|      |                 | Slammer (\$1.2 Billion)   |

| 2002 | \$118 Billion   | KLEZ (\$9 Billion)        |

|      |                 | Bugbear (\$950 Million)   |

| 2001 | \$36 Billion    | Nimbda (\$635 Million)    |

|      |                 | Code Red (\$2.62 Billion) |

|      |                 | SirCam (\$1.15 Billion)   |

| 2000 | \$26 Billion    | Love Bug (\$8.75 Billion) |

| 1999 | \$20 Billion    | Melissa (\$1.10 Billion)  |

|      |                 | Explorer (\$1.02 Billion) |

Table 2.1: Cost of Internet Attacks [22, 86, 5, 34, 56, 33, 1, 85]

Detection of intrusions embedded within TCP data flows requires stream reassembly operations prior to scanning for virus signatures. Network-based Intrusion Detection Systems (IDS) and Intrusion Prevention Systems (IPS) typically operate by searching network traffic for digital signatures which correspond to various types of known intrusions, including worms and viruses [67]. To detect intrusions, IDS appliances must perform Deep Packet Inspections (DPI) which scan packet payloads and process packet headers [51].

In recent years, Internet-based worm and computer virus attacks have caused widespread problems to Internet users. This is due to the fact that large numbers of homogeneous computers are interconnected by high-speed network links. When attacks occur, they can rapidly reach epidemic proportions. The SoBig.F virus infected over 200 million computers within a week and accounted for more than 70% of all email traffic on Aug 20, 2003 [76]. The Code Red virus infected 2,000 new machines every minute during its peak [87]. The MSBlast worm infected more than 350,000 computers [75]. Internet worms and viruses typically spread by probing random IP addresses, searching for vulnerable computers. At its peak, the Slammer worm performed over 55 million scans per second [86]. Internet worms and computer viruses consume huge amounts of computing and networking resources and place an enormous burden on the Internet as a whole.

Moore *et al.* analyzed the behavior of self-propagating worms and viruses [88]. They performed simulations using two different containment methodologies in order to determine the relative effectiveness of each approach. The first containment methodology performed address blacklisting (or address filtering) and the second performed content scanning and filtering. They determined that the content scanning and traffic filtering technique is far superior at preventing the spread of malicious code than address blacklisting. Their results also show that content filtering is much more effective at stopping the spread of viruses when filters are distributed throughout the Internet on high-speed links between ISPs. If placed closer to the periphery of the Internet, these filters were ineffective in stopping widespread infection from worms and viruses. Their results highlight the need for devices capable of high performance content filtering and virus containment. The authors of [88] also lament the fact that virus prevention systems of this nature are not currently available.

Several problems currently limit the effectiveness of monitoring end systems for viruses. Popular operating systems, such as Windows, consist of a large volume of software that is often in need of security updates and patches. The end user must diligently apply updates in a timely manner since network-based attacks can be initiated within days of a vulnerability being detected. For a large institution which may have thousands or tens of thousands of end systems at many locations, the task is even more complex. Installing patches and software updates is typically a serial operation, so the time required to distribute new software or configuration information scales linearly with the number of computers that need to be updated. In addition, a central authority may not have complete access to control all of the machines operating in the network. Even if it did, a security hole remains when, for example, a computer is powered off during an update cycle and fails to receive the new version of the software. Universities and Internet Service Providers (ISPs) represent two types of networks where the network administrator does not have administrative control over machines connected to the network. Further, the proliferation of laptop computers, wireless networks and dynamic addressing allow computers to have great mobility which makes network management even harder. Laptops can appear and disappear from the network, only to reappear a short time later at different locations in the network. This complicates the task of securing networks from attacks.

Monitoring flows in high performance networks requires new methodologies of stream scanning. Moore's Law predicts that the number of transistors that fit on a chip

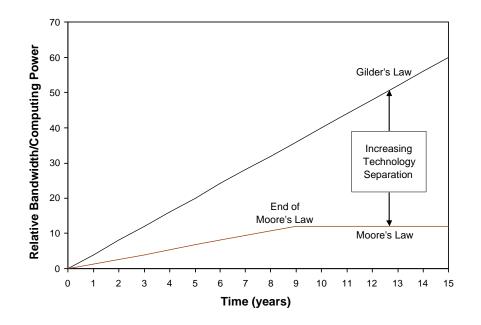

Figure 2.1: Gilder's Law versus Moore's Law

will double every eighteen months [89]. Since transistor count is directly related to computing power, this law implies that computing power will double every eighteen months. This exponential gain is not sufficient to keep pace with advances in communication technology. Gilder's Law of Telecom predicts that bandwidth will grow at least three times faster than computing power [44]. As time progresses, it is reasonable to expect that the gap between network bandwidth and computing power will continue to widen. Moore's Law will cease to hold within the next 10 years due to quantum effects which occur when transistor gate sizes approach 10 nanometers, further exacerbating this gap. The discrepancy between network bandwidth and processing power can clearly be seen in Figure 2.1.

# 2.1 Hardware Processing Technologies

Three classes of processing technologies can be used to satisfy the computational needs of a high performance TCP processing system. The first is a microprocessor, the second is an Application Specific Integrated Circuit (ASIC), and the third is a Field Programmable Gate Array (FPGA). Network processors are considered a subtype classification of microprocessors. Although these processors have been customized for networking applications, they have performance limitations similar to general purpose processors.

#### 2.1.1 Microprocessors

The current generation of general purpose microprocessors is capable of operating at clock frequencies of 3GHz. There is an important distinction, however, between clock frequency and the amount of work performed per unit of time. The ratio of the number of instructions executed versus the number of clock cycles required to execute those instructions  $(\frac{instructions}{clock cycle})$  provides an indication of the amount of work performed per unit of time. For older Complex Instruction Set Computers (CISC), this ratio was less than one, indicating that multiple clock cycles were required to complete the processing for a single operation. In the 1980s, Reduced Instruction Set Computers (RISC) were developed to increase this ratio to 1 such that an operation was completed every clock cycle. The instruction set of a RISC machine typically contains a load and store type architecture with fewer memory addressing modes. In general, a RISC machine requires more instructions than a CISC machine when performing the same amount of work [28].

Pipelining a processor core is a common technique for increasing the amount of work completed per unit of time. By breaking the execution of an instruction into multiple stages (such as fetch, decode, execute, and store), microprocessors operate at higher clock frequencies while still performing the same amount of work per clock cycle. Depending on the instruction sequence, a pipelined architecture can execute one instruction per clock cycle at a much higher clock frequency than can be achieved when there is no pipelining. There are disadvantages associated with a pipelined architecture. The efficiency of a pipeline is not realized until the pipeline is full of instructions. Prior to this point, no work is accomplished for several clock cycles while the pipeline is being primed. Other inefficiencies arise from context switches [97], pipeline stalls, and mispredicted branches [11]. These events cause caches and pipelines to be flushed, which in turn accounts for additional clock cycles where no work is completed. In addition, the more stages there are to a pipeline, the larger the impact of flushing and refilling the pipeline. Super-pipelined architectures [113] further increase the number of pipeline stages by taking long or complex operations and breaking them into several smaller steps. This supports even faster clock frequencies over normal pipelined architectures. Breaking the previous example into the following eight stages is an example of super-pipelining: fetch1, fetch2, fetch3, decode, execute1, execute2, store1, and store2.

Superscalar processing technology [116] allows multiple operations to be performed on each clock cycle which further increases the work per clock cycle. Superscalar architectures have multiple execution units within the core of the microprocessor. Processors which contain multiple execution units are less likely to keep all execution units busy doing useful work, thus reducing the amount of real work performed at each clock cycle.