### Washington University in St. Louis Washington University Open Scholarship

All Computer Science and Engineering Research

**Computer Science and Engineering**

Report Number: WUCSE-2004-40

2004-07-28

## Models, Algorithms, and Architectures for Scalable Packet Classification

David Edward Taylor and Jonathan S. Turner

The growth and diversification of the Internet imposes increasing demands on the performance and functionality of network infrastructure. Routers, the devices responsible for the switch-ing and directing of traffic in the Internet, are being called upon to not only handle increased volumes of traffic at higher speeds, but also impose tighter security policies and provide support for a richer set of network services. This dissertation addresses the searching tasks performed by Internet routers in order to forward packets and apply network services to packets belonging to defined traffic flows. As these searching tasks must be performed for each packet... **Read complete abstract on page 2**.

Follow this and additional works at: https://openscholarship.wustl.edu/cse\_research

#### **Recommended Citation**

Taylor, David Edward and Turner, Jonathan S., "Models, Algorithms, and Architectures for Scalable Packet Classification" Report Number: WUCSE-2004-40 (2004). *All Computer Science and Engineering Research*. https://openscholarship.wustl.edu/cse\_research/1014

Department of Computer Science & Engineering - Washington University in St. Louis Campus Box 1045 - St. Louis, MO - 63130 - ph: (314) 935-6160.

This technical report is available at Washington University Open Scholarship: https://openscholarship.wustl.edu/ cse\_research/1014

### Models, Algorithms, and Architectures for Scalable Packet Classification

David Edward Taylor and Jonathan S. Turner

### **Complete Abstract:**

The growth and diversification of the Internet imposes increasing demands on the performance and functionality of network infrastructure. Routers, the devices responsible for the switch-ing and directing of traffic in the Internet, are being called upon to not only handle increased volumes of traffic at higher speeds, but also impose tighter security policies and provide support for a richer set of network services. This dissertation addresses the searching tasks performed by Internet routers in order to forward packets and apply network services to packets belonging to defined traffic flows. As these searching tasks must be performed for each packet traversing the router, the speed and scalability of the solutions to the route lookup and packet classification problems largely determine the realizable performance of the router, and hence the Internet as a whole. Despite the energetic attention of the academic and corporate research communities, there remains a need for search engines that scale to support faster communication links, larger route tables and filter sets and increasingly complex filters. The major contributions of this work include the design and analysis of a scalable hardware implementation of a Longest Prefix Matching (LPM) search engine for route lookup, a survey and taxonomy of packet classification techniques, a thorough analysis of packet classification filter sets, the design and analysis of a suite of performance evaluation tools for packet classification algorithms and devices, and a new packet classification algorithm that scales to support high-speed links and large filter sets classifying on additional packet fields.

### WASHINGTON UNIVERSITY SEVER INSTITUTE OF TECHNOLOGY DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

### MODELS, ALGORITHMS, AND ARCHITECTURES FOR SCALABLE PACKET CLASSIFICATION

by

David Edward Taylor, M.S.Co.E., M.S.E.E., B.S.Co.E., B.S.E.E.

Prepared under the direction of Dr. Jonathan S. Turner

A dissertation presented to the Sever Institute of Washington University in partial fulfillment of the requirements for the degree of

Doctor of Science

August, 2004

Saint Louis, Missouri

### WASHINGTON UNIVERSITY SEVER INSTITUTE OF TECHNOLOGY DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

### ABSTRACT

### MODELS, ALGORITHMS, AND ARCHITECTURES FOR SCALABLE PACKET CLASSIFICATION

by David Edward Taylor

ADVISOR: Dr. Jonathan S. Turner

August, 2004

Saint Louis, Missouri

The growth and diversification of the Internet imposes increasing demands on the performance and functionality of network infrastructure. Routers, the devices responsible for the switching and directing of traffic in the Internet, are being called upon to not only handle increased volumes of traffic at higher speeds, but also impose tighter security policies and provide support for a richer set of network services. This dissertation addresses the searching tasks performed by Internet routers in order to forward packets and apply network services to packets belonging to defined traffic flows. As these searching tasks must be performed for each packet traversing the router, the speed and scalability of the solutions to the route lookup and packet classification problems largely determine the realizable performance of the router, and hence the Internet as a whole. Despite the energetic attention of the academic and corporate research communities, there remains a need for search engines that scale to support faster communication links, larger route tables and filter sets, and increasingly complex filters. The major contributions of this work include the design and analysis of a scalable hardware implementation of a Longest Prefix Matching (LPM) search engine for route lookup, a survey and taxonomy of packet classification techniques, a thorough analysis of packet classification filter sets, the design and analysis of a suite of performance evaluation tools for packet classification algorithms and devices, and a new packet classification algorithm that scales to support high-speed links and large filter sets classifying on additional packet fields. copyright by David Edward Taylor 2004 Soli Deo Gloria

to God alone be the glory

# Contents

| Li | st of l | Figures   |                                             |    |

|----|---------|-----------|---------------------------------------------|----|

| Ac | cknov   | vledgme   | nts                                         | XV |

| Pr | reface  |           |                                             |    |

| 1  | Intr    | oductio   | <b>n</b>                                    |    |

|    | 1.1     | State o   | f the Internet                              |    |

|    | 1.2     | The "N    | lext Generation" Internet                   |    |

|    | 1.3     | The Pa    | cket Classification Problem                 |    |

|    |         | 1.3.1     | Constraints                                 |    |

|    | 1.4     | Organi    | zation of the Dissertation                  |    |

| 2  | Sing    | gle-Field | Search Techniques                           |    |

|    | 2.1     | Exact 1   | Matching                                    |    |

|    |         | 2.1.1     | B-Trees                                     |    |

|    |         | 2.1.2     | Hashing                                     |    |

|    |         | 2.1.3     | Bloom Filters                               |    |

|    | 2.2     | Longes    | st Prefix Matching (LPM)                    |    |

|    |         | 2.2.1     | Linear Search                               |    |

|    |         | 2.2.2     | Content Addressable Memory (CAM)            |    |

|    |         | 2.2.3     | Trie Based Schemes                          |    |

|    |         | 2.2.4     | Multiway and Multicolumn Search             |    |

|    |         | 2.2.5     | Binary Search on Prefix Lengths             |    |

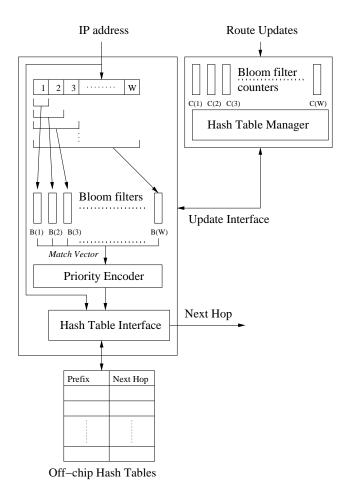

|    |         | 2.2.6     | Longest Prefix Matching using Bloom Filters |    |

|    | 2.3     | All Pre   | fix Matching (APM)                          |    |

|    | 2.4     | Range     | Matching                                    |    |

|    |         | 2.4.1     | Segment Tree                                |    |

|    |         | 2.4.2     | Interval Tree                               |    |

|   |            | 2.4.3   | Range to Prefix Conversion    2 | 29       |

|---|------------|---------|---------------------------------|----------|

|   |            | 2.4.4   | Range Matching Circuits   3     | 30       |

| 3 | Fast       | Intern  | et Protocol Lookup (FIPL)       | 31       |

|   | 3.1        |         |                                 | 31       |

|   | 3.2        |         |                                 | 33       |

|   |            | 3.2.1   |                                 | 36       |

|   | 3.3        | Hardw   |                                 | 37       |

|   |            | 3.3.1   |                                 | 38       |

|   |            | 3.3.2   | -                               | 10       |

|   |            | 3.3.3   |                                 | 11       |

|   |            | 3.3.4   | Memory Configuration            | 12       |

|   |            | 3.3.5   |                                 | 12       |

|   |            | 3.3.6   |                                 | 12       |

|   | 3.4        | Systen  | -                               | 13       |

|   |            | 3.4.1   | -                               | 13       |

|   |            | 3.4.2   | FIPL Memory Manager             | 13       |

|   |            | 3.4.3   | Sockets Interfaces              | 15       |

|   |            | 3.4.4   | Remote User Interface           | 15       |

|   |            | 3.4.5   | Command Flow                    | 15       |

|   | 3.5        | Perform | mance Measurements              | 17       |

|   |            | 3.5.1   | Memory Utilization              | 18       |

|   |            | 3.5.2   | Lookup Rate                     | 18       |

|   | 3.6        | Toward  | ds Better Performance           | 50       |

|   |            | 3.6.1   | Implementation Optimizations    | 51       |

|   |            | 3.6.2   | Root Node Extension & Caching   | 51       |

|   | 3.7        | Relate  | d Work                          | 53       |

|   | 3.8        | Discus  | sion                            | 55       |

| 4 | M1         |         |                                 |          |

| 4 |            | -       |                                 | 56       |

|   | 4.1<br>4.2 |         | 5                               | 57<br>58 |

|   | 4.2        |         |                                 |          |

|   |            | 4.2.1   |                                 | 50       |

|   | 4.2        | 4.2.2   |                                 | 50       |

|   | 4.3        |         |                                 | 52       |

|   |            | 4.3.1   |                                 | 54<br>57 |

|   |            | 4.3.2   |                                 | 57       |

|   |            | 4.3.3   |                                 | 59<br>70 |

|   |            | 4.3.4   | Modular Packet Classification   | 70       |

|   |      | 4.3.5 HyperCuts                                          |

|---|------|----------------------------------------------------------|

|   |      | 4.3.6 Extended TCAM (E-TCAM)                             |

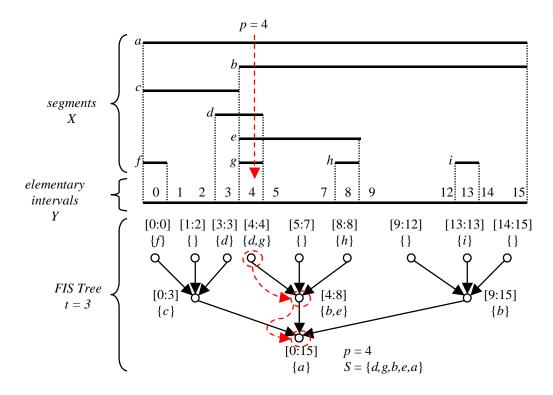

|   |      | 4.3.7 Fat Inverted Segment (FIS) Trees                   |

|   | 4.4  | Decomposition                                            |

|   |      | 4.4.1 Parallel Bit-Vectors (BV)                          |

|   |      | 4.4.2 Aggregated Bit-Vector (ABV)                        |

|   |      | 4.4.3 Crossproducting                                    |

|   |      | 4.4.4 Recursive Flow Classification (RFC)                |

|   |      | 4.4.5 Parallel Packet Classification $(P^2C)$            |

|   |      | 4.4.6 Distributed Crossproducting of Field Labels (DCFL) |

|   | 4.5  | Tuple Space         90                                   |

|   |      | 4.5.1 Tuple Space Search & Tuple Pruning                 |

|   |      | 4.5.2 Rectangle Search                                   |

|   |      | 4.5.3 Conflict-Free Rectangle Search                     |

|   | 4.6  | Caching                                                  |

|   | 4.7  | Discussion                                               |

| 5 | Ana  | lysis of Real Filter Sets                                |

| - | 5.1  | Understanding Filter Composition                         |

|   | 5.2  | Previous Observations                                    |

|   | 5.3  | Application Specifications                               |

|   |      | 5.3.1 Protocol                                           |

|   |      | 5.3.2 Port Ranges                                        |

|   |      | 5.3.3 Port Pair Class                                    |

|   | 5.4  | Address Prefix Pairs                                     |

|   | 5.5  | Scope                                                    |

|   | 5.6  | Filter Overlap                                           |

|   | 5.7  | Field Value Overlap                                      |

|   | 5.8  | Additional Fields                                        |

|   | 5.9  | Impact of IPv6 Migration                                 |

|   |      | 5.9.1 Address Architecture                               |

|   |      | 5.9.2 Address Allocation & Assignment                    |

| 6 | Clas | sBench: A Packet Classification Benchmark                |

| - | 6.1  | Motivation                                               |

|   | 6.2  | Related Work         125                                 |

|   | 6.3  | Parameter Files                                          |

|   | 6.4  | Synthetic Filter Set Generation   129                    |

|   | 0.1  | 6.4.1         Smoothing Adjustment         133           |

|   |      |                                                          |

|    |        | 6.4.2 Scope Adjustment                                                         | 35 |

|----|--------|--------------------------------------------------------------------------------|----|

|    |        | 6.4.3 Filter Redundancy & Priority                                             | 41 |

|    | 6.5    | Trace Generation                                                               | 43 |

|    | 6.6    | Benchmarking with ClassBench                                                   | 45 |

| 7  | Scal   | ble Packet Classification using Distributed Crossproducting of Field Labels 14 | 48 |

|    | 7.1    | Description of DCFL                                                            | 49 |

|    | 7.2    | Aggregation Network    1                                                       | 54 |

|    | 7.3    | Field Splitting                                                                | 56 |

|    | 7.4    | Aggregation Nodes                                                              | 59 |

|    |        | 7.4.1 Bloom Filter Arrays 1:                                                   | 59 |

|    |        | 7.4.2 Meta-Label Indexing                                                      | 61 |

|    | 7.5    | Field Search Engines    10                                                     | 63 |

|    |        | 7.5.1 Prefix Matching                                                          | 63 |

|    |        | 7.5.2 Range Matching                                                           | 64 |

|    |        | 7.5.3 Exact Matching                                                           | 65 |

|    | 7.6    | Dynamic Updates                                                                | 65 |

|    | 7.7    | Performance Evaluation                                                         | 67 |

|    | 7.8    | Related Work                                                                   | 75 |

|    | 7.9    | Discussion                                                                     | 78 |

| 8  | Sum    | nary                                                                           | 79 |

|    | 8.1    | Contributions                                                                  | 79 |

|    | 8.2    | Future Directions                                                              | 81 |

| Aŗ | opend  | x A Additional Data from Real Filter Sets                                      | 83 |

| Re | eferen | es                                                                             | 90 |

| Vi | ta.    |                                                                                | 98 |

# **List of Tables**

| 1.1 | Example filter set of 16 filters classifying on four fields; each filter has an associated                |     |

|-----|-----------------------------------------------------------------------------------------------------------|-----|

|     | flow identifier ( <i>Flow ID</i> ) and priority tag ( <i>PT</i> ) where † denotes a non-exclusive filter; |     |

|     | wildcard fields are denoted with *                                                                        | 8   |

| 3.1 | Memory usage for the Tree Bitmap data structure and next hop information using a                          |     |

|     | snapshot of the Mae-West database from March 15, 2002 consisting of 27,609 routes.                        | 48  |

| 3.2 | Memory usage for root node array optimization.                                                            | 53  |

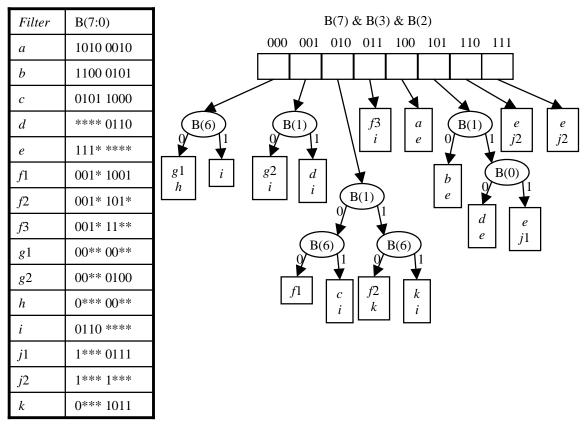

| 4.1 | Example filter set; port numbers are restricted to be an exact value or wildcard                          | 65  |

| 4.2 | Example filter set; address field is 4-bits and port ranges cover 4-bit port numbers                      | 69  |

| 4.3 | Example filter set; address fields are 4-bits and port ranges cover 4-bit port numbers.                   | 91  |

| 5.1 | Observed protocols and filter distribution; values given as percentage (%) of filters                     |     |

|     | in the filter set                                                                                         | 102 |

| 5.2 | Distribution of filters over the five port classes for source and destination port range                  |     |

|     | specifications; values given as percentage (%) of filters in the filter set                               | 103 |

| 5.3 | Number of unique specifications in the Arbitrary Range (AR) and Exact Match                               |     |

|     | (EM) port classes for source and destination port ranges.                                                 | 104 |

| 5.4 | Number of entries required to store filter set in a standard TCAM.                                        | 106 |

| 5.5 | Number of unique address prefix lengths for source address (SA), destination ad-                          |     |

|     | dress (DA), and source/destination address pairs (SA/DA).                                                 | 106 |

| 5.6 | 5-tuple scope measurements, average ( $\mu_{scope}$ ) and standard deviation ( $\sigma_{scope}$ )         | 114 |

| 5.7 | Maximum number of filters matching any packet; partial matches for each field in                          |     |

|     | the 5-tuple, source/destination address prefix pair (SA-DA), and application specifi-                     |     |

|     | cation (SP-DP-PR); full matches on all fields (All); matches; data from 12 real filter                    |     |

|     | sets                                                                                                      | 116 |

| 5.8 | Number of unique field values and combinations of field values specified by filters                       |     |

|     | in 12 real filter sets.                                                                                   | 118 |

| 5.9 | Maximum number of unique field values and combinations of field values matching                           |     |

|     | a packet; data from 12 real filter sets                                                                   | 118 |

# **List of Figures**

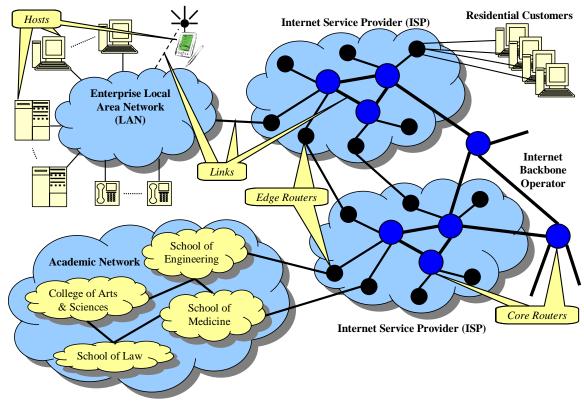

| 1.1  | Simple diagram of Internet architecture                                                 | 3  |

|------|-----------------------------------------------------------------------------------------|----|

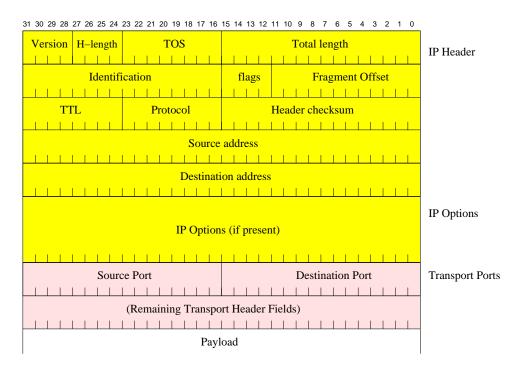

| 1.2  | Format of Internet Protocol Version 4 (IPv4) packet headers with appended transport     |    |

|      | protocol header fields.                                                                 | 4  |

| 1.3  | Internet Protocol Version 4 (IPv4) address space allocation.                            | 4  |

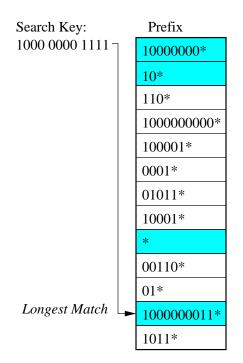

| 1.4  | Example of Longest Prefix Matching for a 12-bit search key; all shaded prefixes         |    |

|      | match the key, but $100000011*$ is the longest matching prefix                          | 7  |

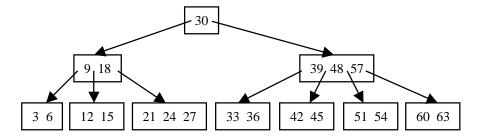

| 2.1  | Example of a B-Tree storing multiples of three, where $t = 3. \ldots \ldots$            | 14 |

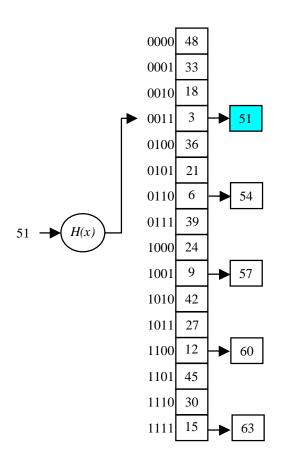

| 2.2  | Example of hashing with chaining using the four low-order bits as a hash index          | 15 |

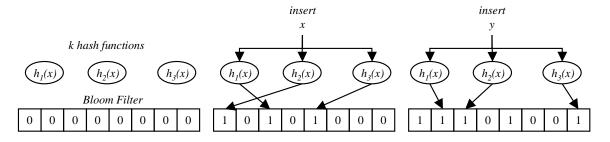

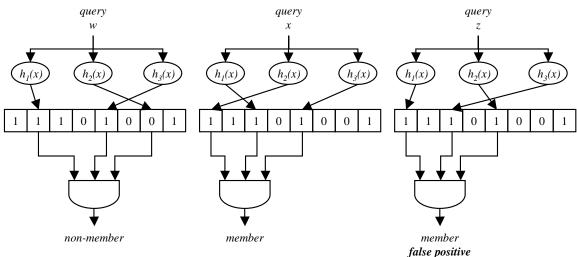

| 2.3  | Example of inserting two keys, $x$ and $y$ , into a Bloom filter                        | 15 |

| 2.4  | Example of querying a Bloom filter; $w$ is a non-member, $x$ is a correct match; $z$ is |    |

|      | a false positive match.                                                                 | 16 |

| 2.5  | Example of Longest Prefix Matching for a 12-bit address using linear search; pre-       |    |

|      | fixes are sorted in decreasing order of prefix length; the first matching prefix is the |    |

|      | longest.                                                                                | 18 |

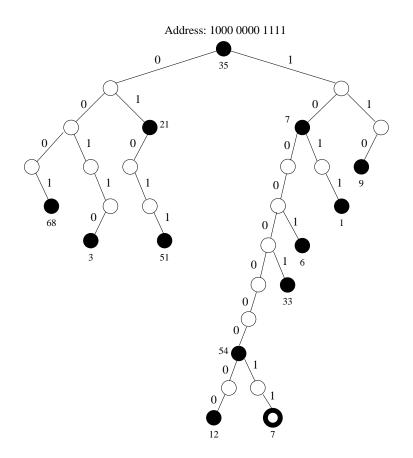

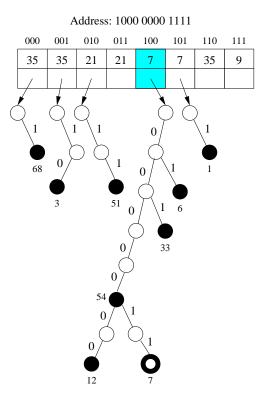

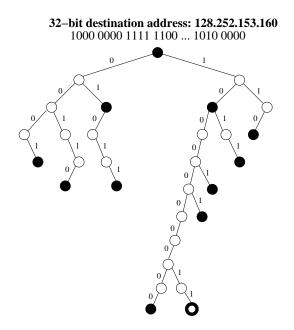

| 2.6  | Example of Longest Prefix Matching using a binary trie.                                 | 20 |

| 2.7  | Example of a direct lookup array for the first three bits                               | 22 |

| 2.8  | Basic configuration of Longest Prefix Matching using Bloom filters, ( <i>BIPL</i> )     | 24 |

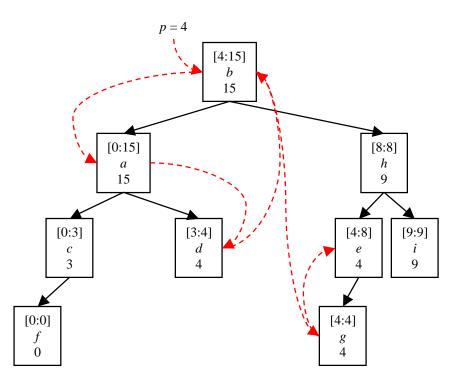

| 2.9  | Nesting tree technique for finding all matching prefixes for a given longest matching   |    |

|      | prefix                                                                                  | 26 |

| 2.10 |                                                                                         |    |

|      | the real line, and using the Fat Inverted Segment (FIS) Tree to search the set of       |    |

|      | segments                                                                                | 27 |

| 2.11 | Example of an Interval Tree where each node stores the maximum endpoint value           |    |

|      | for all intervals in its subtree.                                                       | 29 |

| 3.1  | IP lookup table of next hops. Next hops for IP packets are found using the longest      |    |

|      | matching prefix in the table for the IP destination address of the packet.              | 33 |

| 3.2  | IP lookup table represented as a binary trie. Stored prefixes are denoted by shaded     |    |

|      | nodes. Next hops are found by traversing the trie                                       | 34 |

|      |                                                                                         |    |

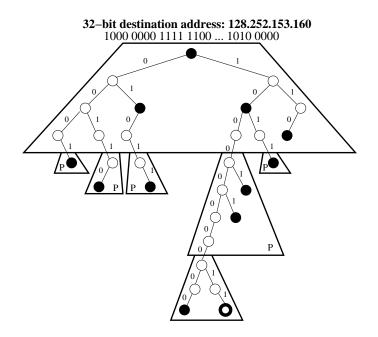

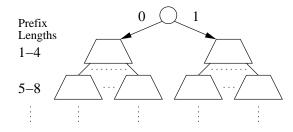

| 3.3  | IP lookup table represented as a multibit trie. A stride, 4-bits, of the unicast desti- |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | nation address of the IP packet are compared at once, speeding up the lookup process.   | 35 |

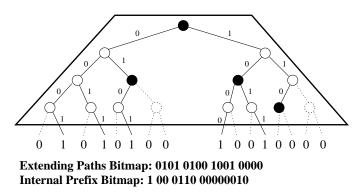

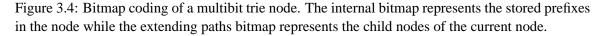

| 3.4  | Bitmap coding of a multibit trie node. The internal bitmap represents the stored        |    |

|      | prefixes in the node while the extending paths bitmap represents the child nodes of     |    |

|      | the current node.                                                                       | 35 |

| 3.5  | IP lookup table represented as a Tree Bitmap. Child nodes are stored contiguously       |    |

|      | so that a single pointer and an index may be used to locate any child node in the the   |    |

|      | data structure.                                                                         | 36 |

| 3.6  | Split-trie optimization of the <i>Tree Bitmap</i> data structure                        | 37 |

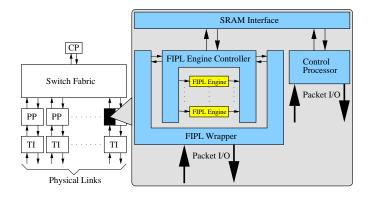

| 3.7  | Block diagram of router with multi-engine FIPL configuration; detail of FIPL sys-       |    |

|      | tem components in the Port Processor (PP).                                              | 38 |

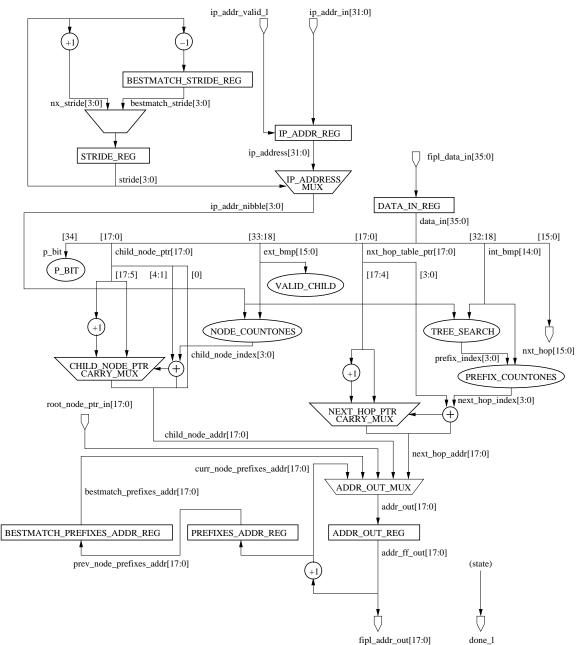

| 3.8  | FIPL engine dataflow; multi-cycle path from input data flops to output address flops    |    |

|      | can be scaled according to target device speed; all multiplexor select lines and flip-  |    |

|      | flop enables implicitly driven by finite-state machine outputs                          | 39 |

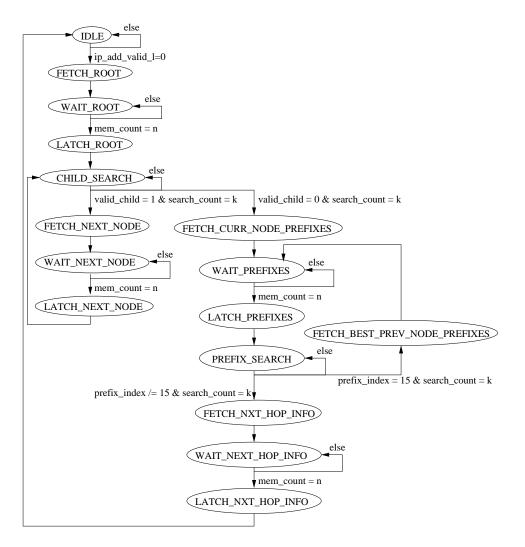

| 3.9  | FIPL engine state transition diagram.                                                   | 41 |

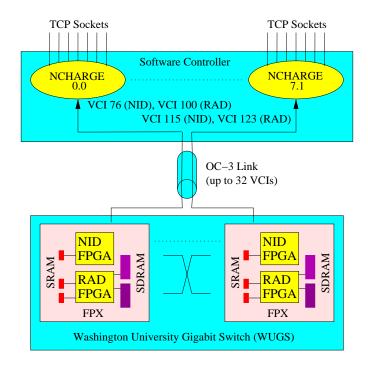

| 3.10 | Control of the Field-programmable Port eXtender (FPX) via NCHARGE software.             |    |

|      | Each FPX is controlled by an instance of NCHARGE which provides an API for              |    |

|      | FPX control via remote software process.                                                | 44 |

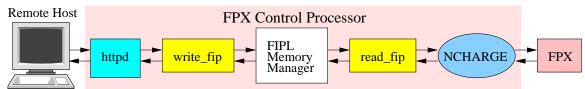

| 3.11 | Command flow for control of FIPL via a remote host.                                     | 46 |

| 3.12 | FPX Web Interface for FIPL route updates.                                               | 46 |

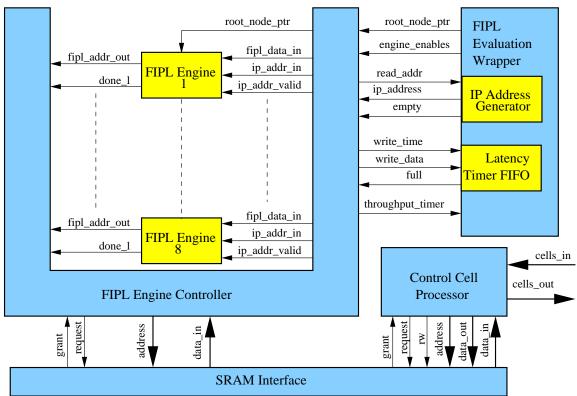

| 3.13 | Block diagram of FIPL evaluation environment.                                           | 47 |

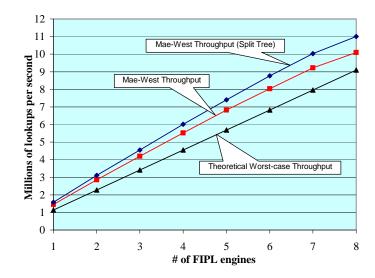

| 3.14 | FIPL performance: measurements used a snapshot of the Mae-West database from            |    |

|      | March 15, 2002 consisting of 27,609 routes. Input IPv4 destination addresses were       |    |

|      | created by randomly selecting 16,384 prefixes from the Mae-West database                | 49 |

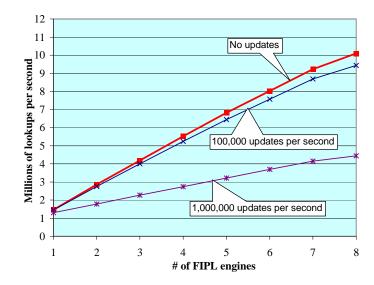

| 3.15 | FIPL performance under update load: measurements used a snapshot of the Mae-            |    |

|      | West database from March 15, 2002 consisting of 27,609 routes. Input IPv4 desti-        |    |

|      | nation addresses were created by randomly selecting 16,384 prefixes from the Mae-       |    |

|      | West database. Updates consisted of alternating addition and deletion of a 24-bit       |    |

|      | prefix                                                                                  | 50 |

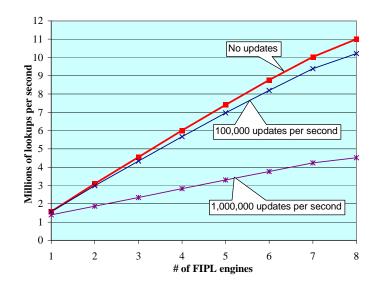

| 3.16 | FIPL Split-Trie performance under update load: measurements used a snapshot of          |    |

|      | the Mae-West database from March 15, 2002 consisting of 27,609 routes. Input            |    |

|      | IPv4 destination addresses were created by randomly selecting 16,384 prefixes from      |    |

|      | the Mae-West database. Updates consisted of alternating addition and deletion of a      |    |

|      | 24-bit prefix                                                                           | 51 |

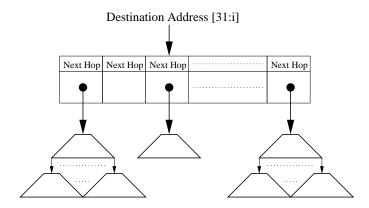

| 3.17 | Root node extension using an on-chip array and multiple sub-tries                       | 52 |

|      |                                                                                         |    |

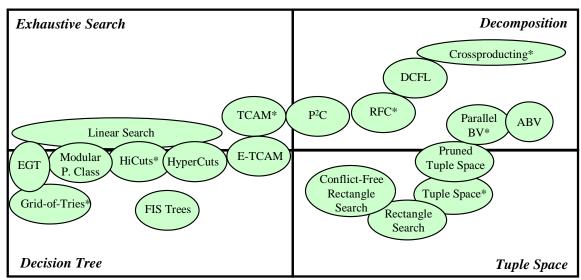

| 4.1  | Taxonomy of multiple field search techniques for packet classification; adjacent        |    |

|      | techniques are related; hybrid techniques overlap quadrant boundaries; * denotes a      |    |

|      | seminal technique.                                                                      | 57 |

| 4.2  | Example of encoding filters by unique field values to reduce storage requirements                | 60 |

|------|--------------------------------------------------------------------------------------------------|----|

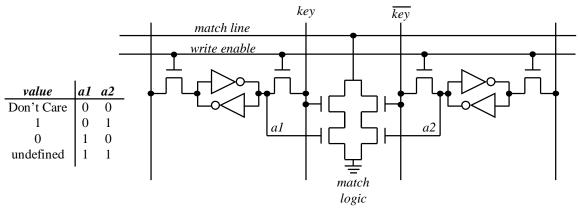

| 4.3  | Circuit diagram of a standard TCAM cell; the stored value (0, 1, Don't Care) is                  |    |

|      | encoded using two registers <i>a1</i> and <i>a2</i>                                              | 61 |

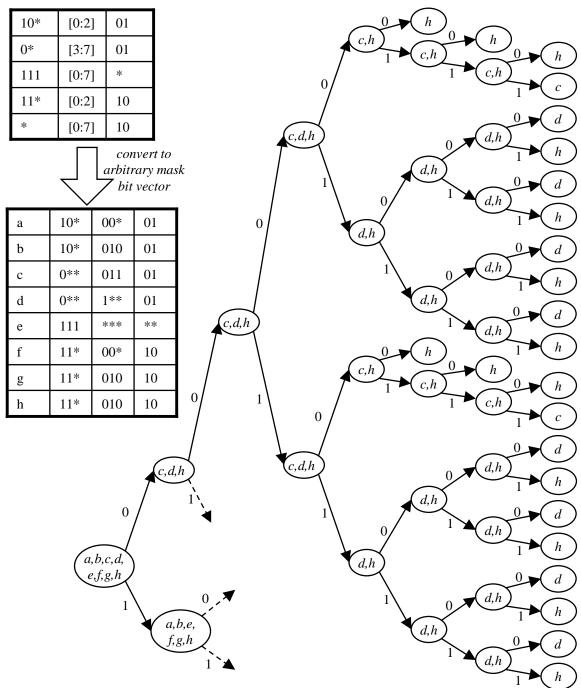

| 4.4  | Example of a naïve construction of a decision tree for packet classification on three            |    |

|      | fields; all filter fields are converted to bit vectors with arbitrary bit masks                  | 63 |

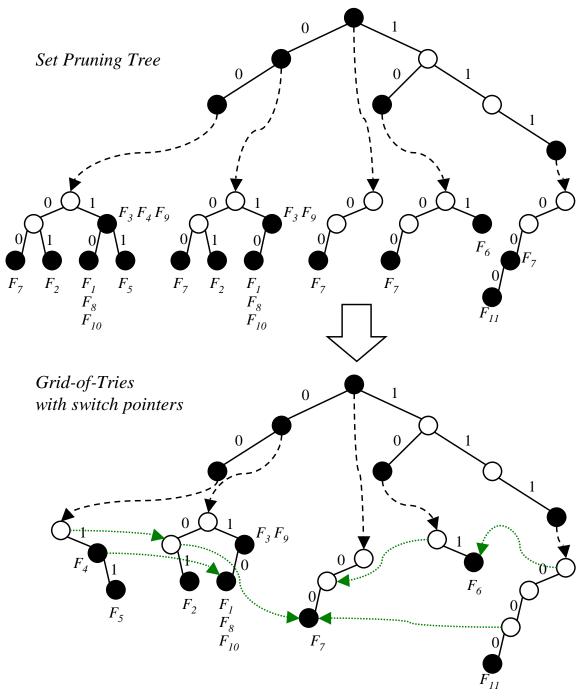

| 4.5  | Example of set pruning trees and Grid-of-Tries classifying on the destination and                |    |

|      | source address prefixes for the example filter set in Table 4.1.                                 | 66 |

| 4.6  | Example of 5-tuple packet classification using <i>Grid-of-Tries</i> , pre-filtering on proto-    |    |

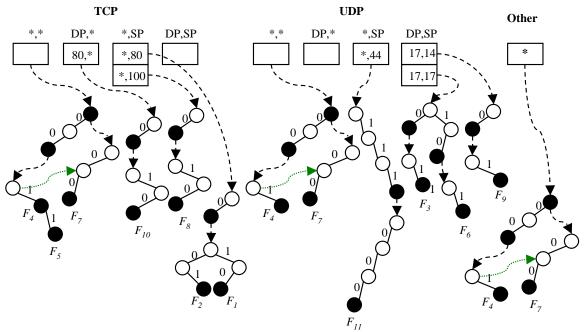

|      | col and port number classes, for the example filter set in Table 4.1.                            | 67 |

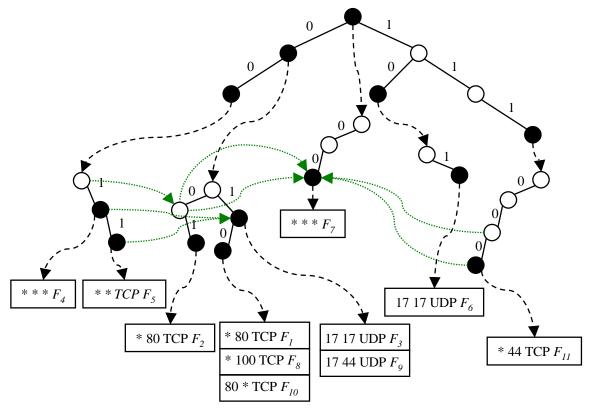

| 4.7  | Example of 5-tuple packet classification using <i>Extended Grid-of-Tries</i> (EGT) for           |    |

|      | the example filter set in Table 4.1.                                                             | 68 |

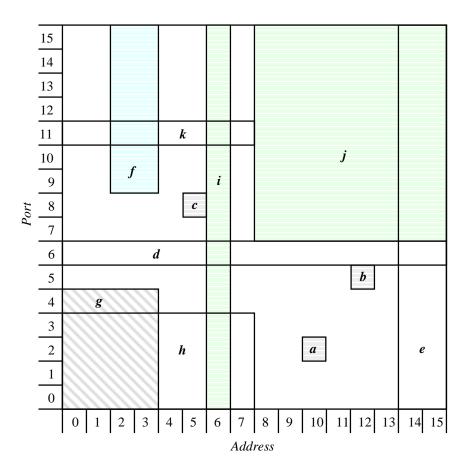

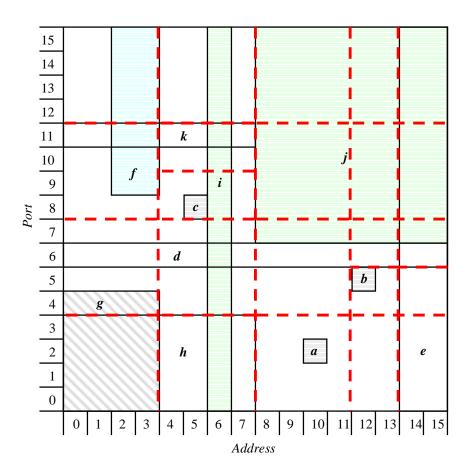

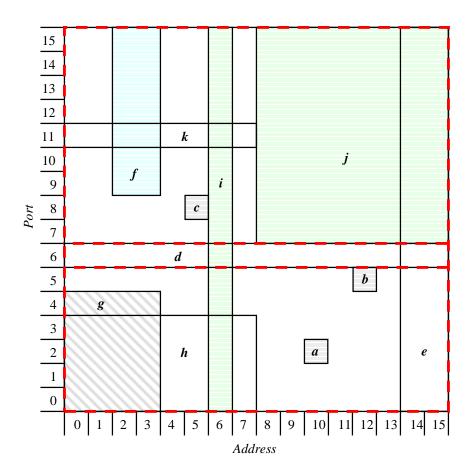

| 4.8  | Geometric representation of the example filter set shown in Table 4.2.                           | 70 |

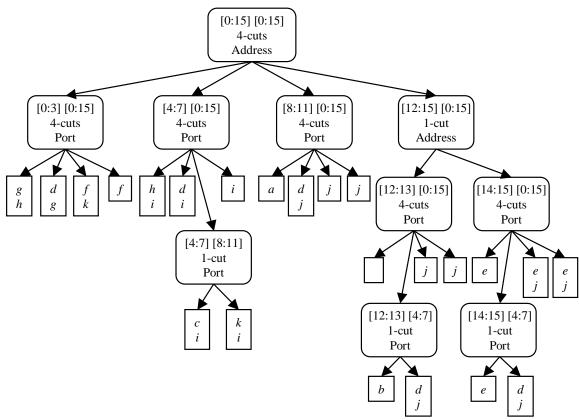

| 4.9  | Example <i>HiCuts</i> data structure for example filter set in Table 4.2.                        | 71 |

| 4.10 | Geometric representation of partitioning created by <i>HiCuts</i> data structure shown in        |    |

|      | Figure 4.9.                                                                                      | 72 |

| 4.11 | Modular packet classification using ternary strings and a three-stage search archi-              |    |

|      | tecture.                                                                                         | 73 |

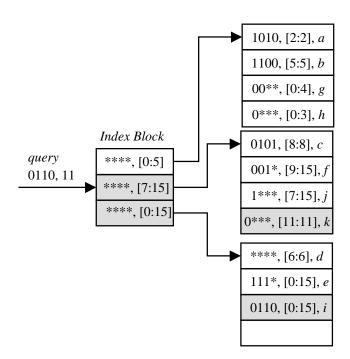

| 4.12 | Example of searching the filter set in Table 4.2 using an <i>Extended TCAM</i> (E-TCAM)          |    |

|      | using a two-stage search and a filter block size of four.                                        | 75 |

| 4.13 | Example of partitioning the filter set in Table 4.2 for an <i>Extended TCAM</i> (E-TCAM)         |    |

|      | with a two-stage search and a filter block size of four.                                         | 76 |

| 4.14 | Example of <i>Fat Inverted Segment (FIS) Trees</i> for the filter set in Table 4.2               | 77 |

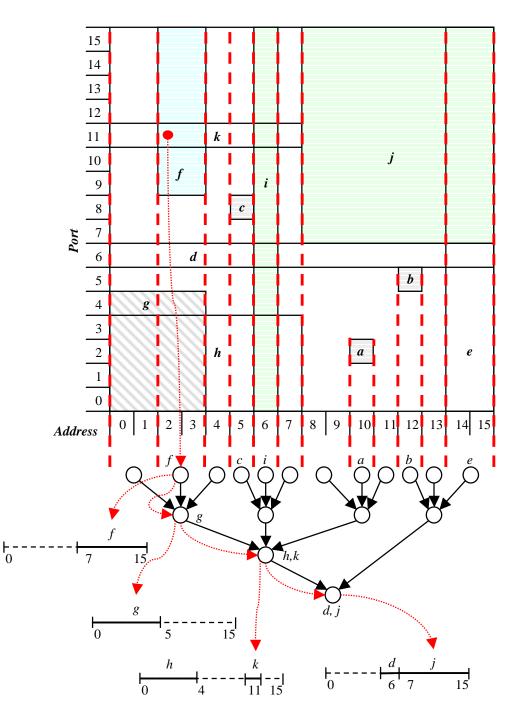

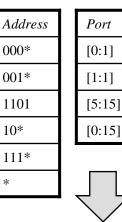

| 4.15 | Example of bit-vector construction for the Parallel Bit-Vectors technique using the              |    |

|      | filter set shown in Table 4.2.                                                                   | 79 |

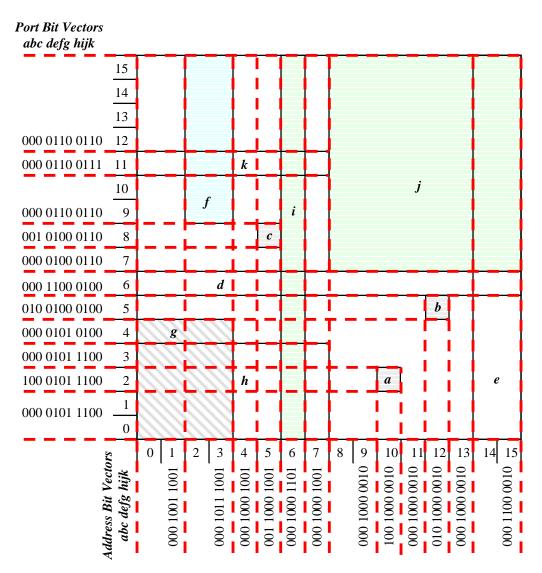

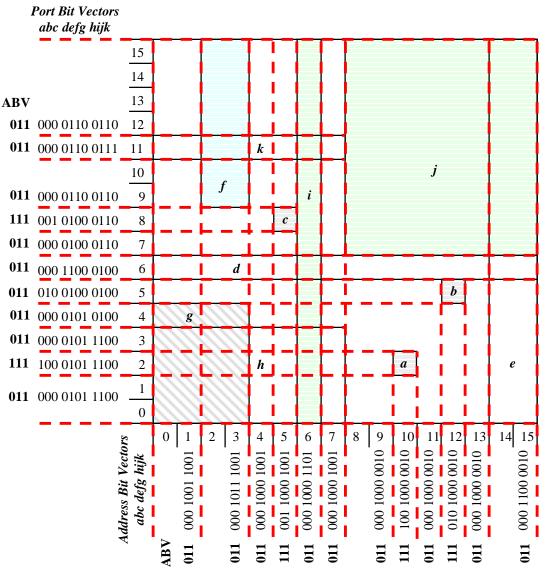

| 4.16 | Example of bit-vector and aggregate bit-vector construction for the Aggregated Bit-              |    |

|      | Vectors technique using the filter set shown in Table 4.2.                                       | 81 |

| 4.17 | Example of <i>Crossproducting</i> technique for filter set with three fields; full crossprod-    |    |

|      | uct table is not shown due to space constraints.                                                 | 83 |

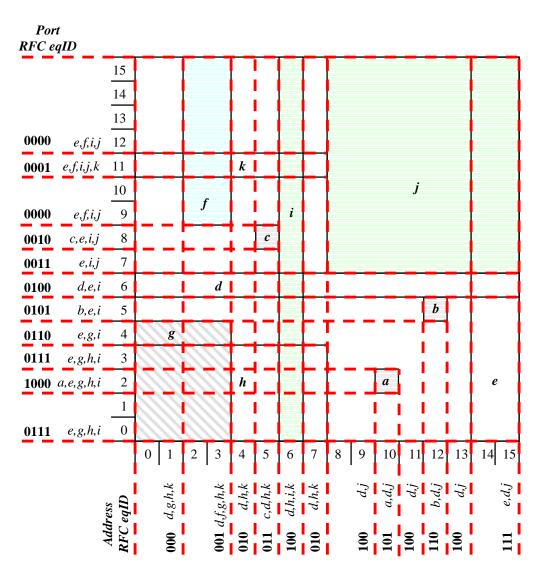

| 4.18 | Example of <i>Recursive Flow Classification (RFC)</i> using the filter set in Table 4.2.         | 85 |

| 4.19 | Example of <i>Parallel Packet Classification</i> $(P^2C)$ using the most update-efficient        |    |

|      | encoding style for the port ranges defined in the filter set in Table 4.2                        | 86 |

| 4.20 | Example of encoding filters with field labels in <i>Distributed Crossproducting of Field</i>     |    |

|      | Labels (DCFL) using same filter table as Figure 4.17; count values support dynamic               |    |

|      | updates                                                                                          | 89 |

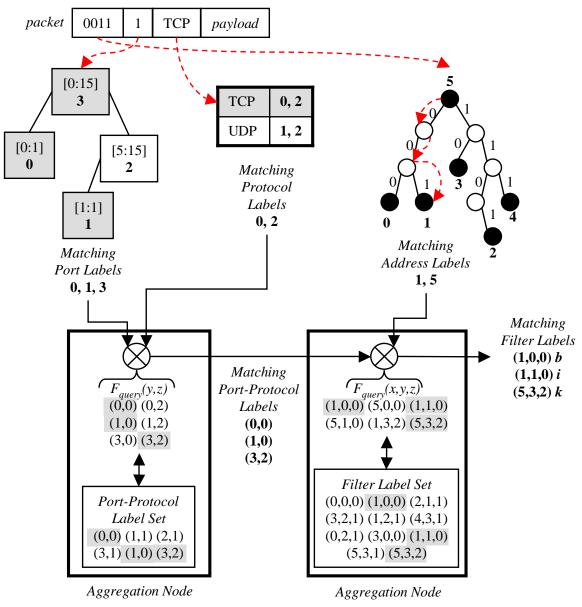

| 4.21 | Example of search using Distributed Crossproducting of Field Labels (DCFL)                       | 90 |

| 4.22 | Example of assigning tuple values for ranges based on <i>Nesting Level</i> and <i>Range ID</i> . | 91 |

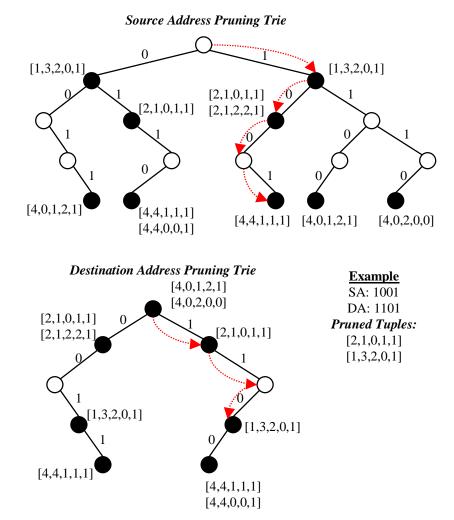

| 4.23 | Example of <i>Tuple Pruning</i> to narrow the scope of the <i>Tuple Space Search</i> ; the set of                                                                                                              |      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | pruned tuples is the intersection of the sets of tuples found along the search paths                                                                                                                           |      |

|      | for each field.                                                                                                                                                                                                | 93   |

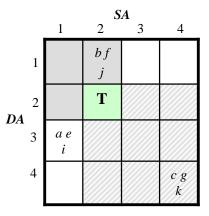

| 4.24 | Example of <i>Rectangle Search</i> on source and destination prefixes of filters in Table 4.3                                                                                                                  | . 94 |

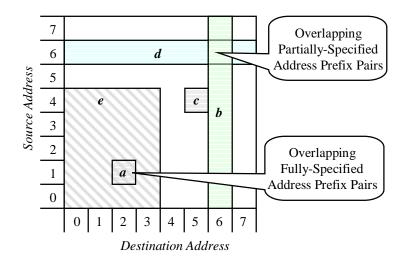

| 5.1  | Example of overlaps formed by fully-specified and partially-specified address prefix                                                                                                                           |      |

|      | pairs                                                                                                                                                                                                          | 101  |

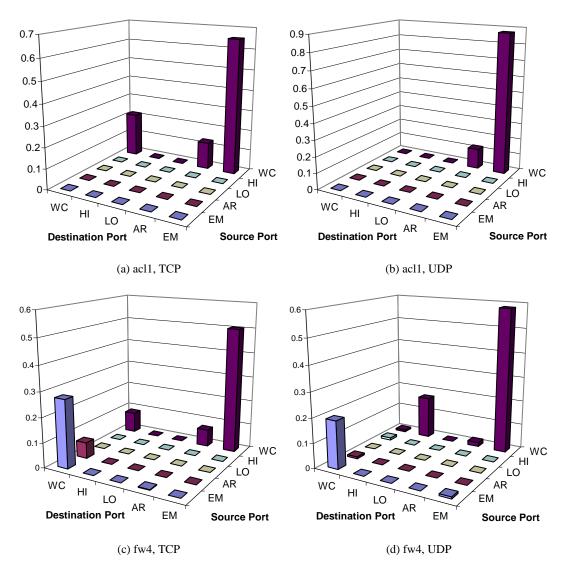

| 5.2  | Port Pair Matrices for two filter sets.                                                                                                                                                                        | 105  |

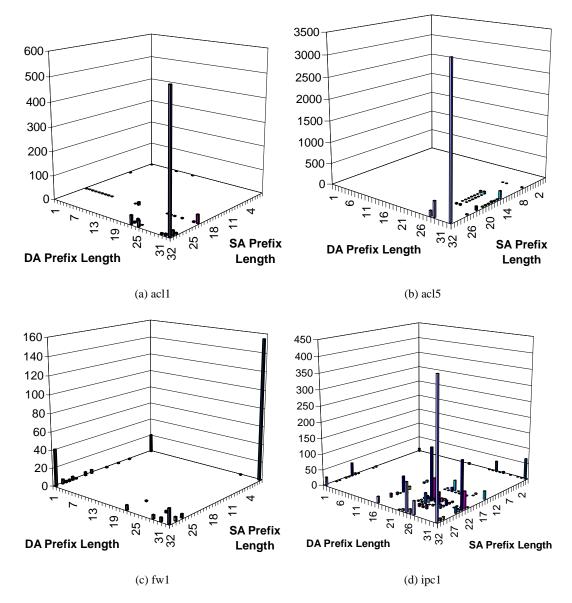

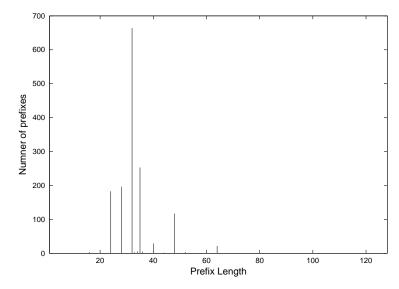

| 5.3  | Prefix length distribution for address prefix pairs.                                                                                                                                                           | 108  |

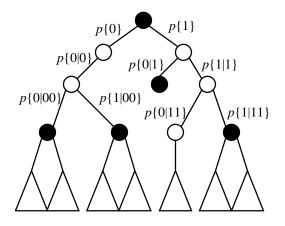

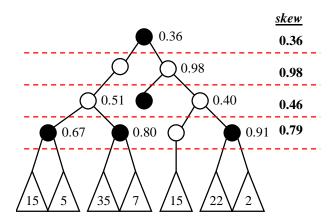

| 5.4  | Example of complete statistical characterization of address prefixes                                                                                                                                           | 109  |

| 5.5  | Example of skew computation for the first four levels of an address trie; shaded                                                                                                                               |      |

|      | nodes denote a prefix specified by a single filter; subtrees denoted by triangles with                                                                                                                         |      |

|      | associated weight                                                                                                                                                                                              | 109  |

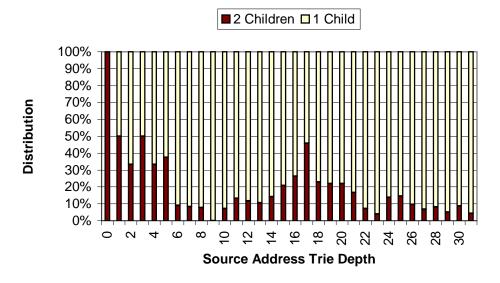

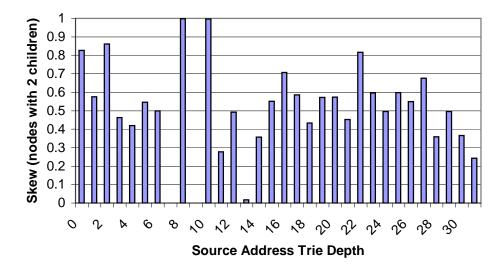

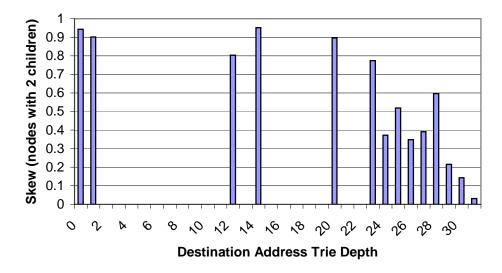

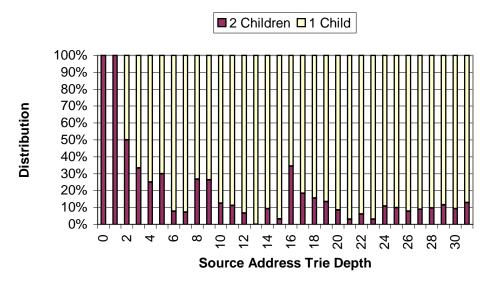

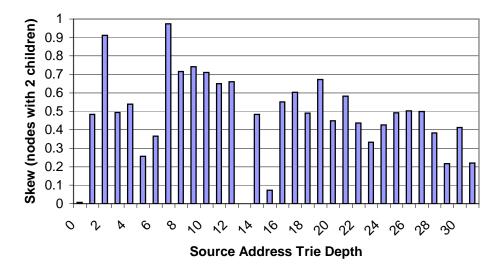

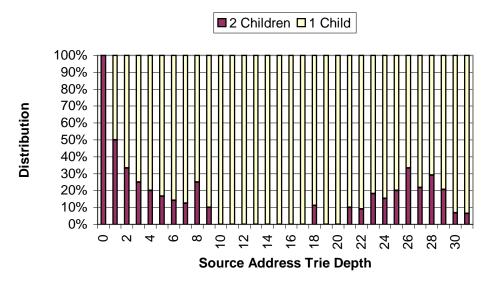

| 5.6  | Source address branching probability and skew for filter set acl5                                                                                                                                              | 110  |

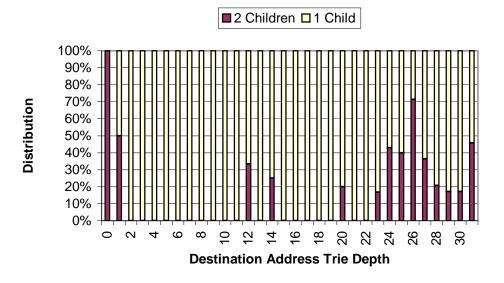

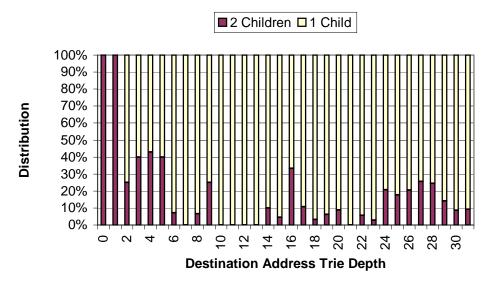

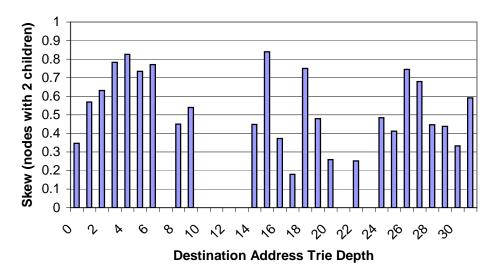

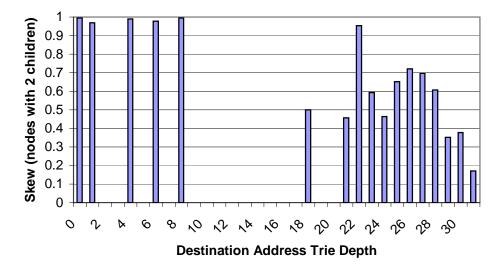

| 5.7  | Destination address branching probability and skew for filter set acl5                                                                                                                                         | 111  |

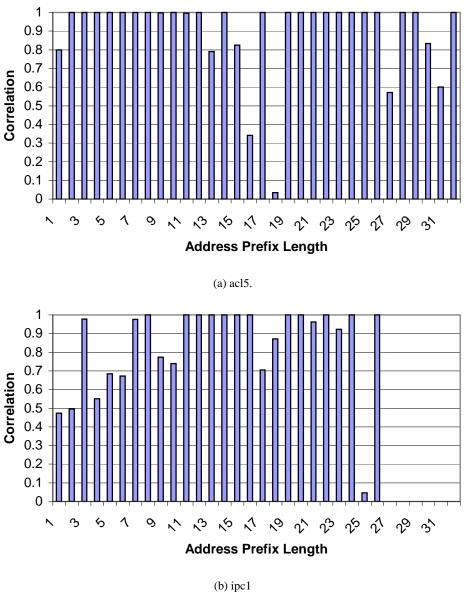

| 5.8  | Address prefix correlation; probability that address prefixes of a filter continue to be                                                                                                                       |      |

|      | the same at a given prefix length                                                                                                                                                                              | 113  |

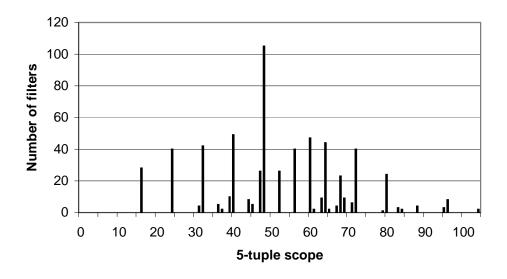

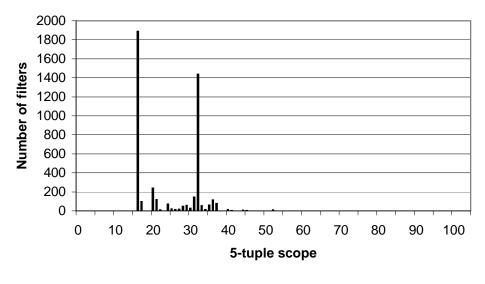

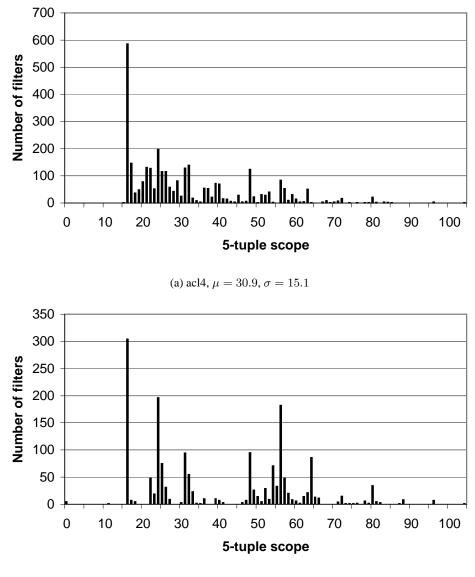

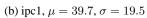

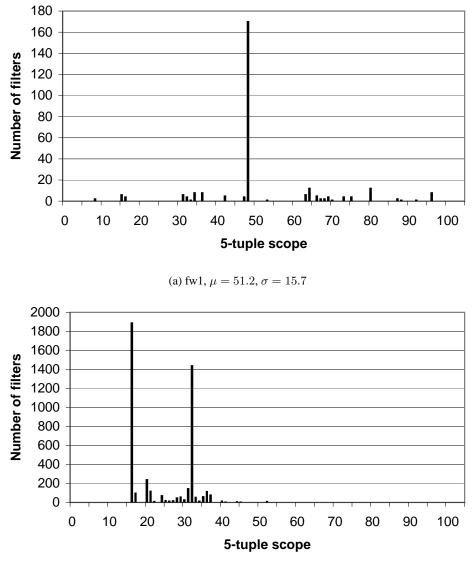

| 5.9  | Distribution of 5-tuple scope for filters in filter sets acl2 and acl5                                                                                                                                         | 115  |

| 5.10 | Combined prefix length distribution for IPv6 BGP route table snapshots                                                                                                                                         | 120  |

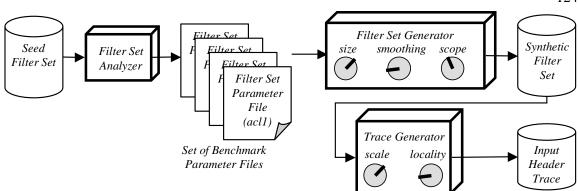

| 6.1  | Block diagram of the <i>ClassBench</i> tools suite. The synthetic <i>Filter Set Generator</i>                                                                                                                  |      |

| 0.11 | has size, smoothing, and scope adjustments which provide high-level, systematic                                                                                                                                |      |

|      | mechanisms for altering the size and composition of synthetic filter sets. The set of                                                                                                                          |      |

|      | benchmark <i>parameter files</i> model real filter sets and may be refined over time. The                                                                                                                      |      |

|      | <i>Trace Generator</i> provides adjustments for trace size and locality of reference                                                                                                                           | 124  |

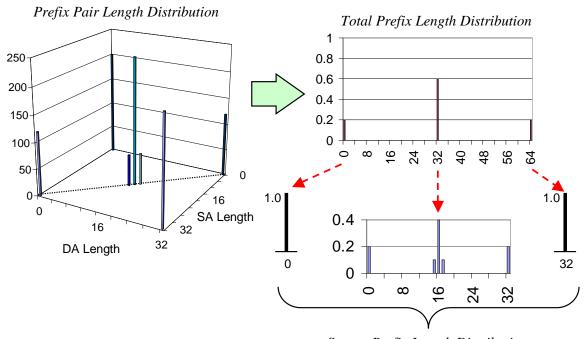

| 6.2  | Parameter files represent prefix pair length distributions using a combination of a                                                                                                                            | 127  |

| 0.2  | total prefix length distribution and source prefix length distributions for each non-                                                                                                                          |      |

|      | zero total length.                                                                                                                                                                                             | 128  |

| 6.3  | Pseudocode for <i>Filter Set Generator</i> .                                                                                                                                                                   | 120  |

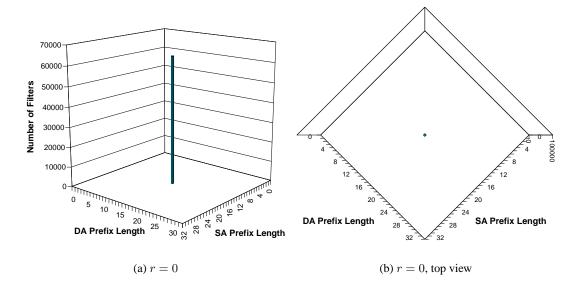

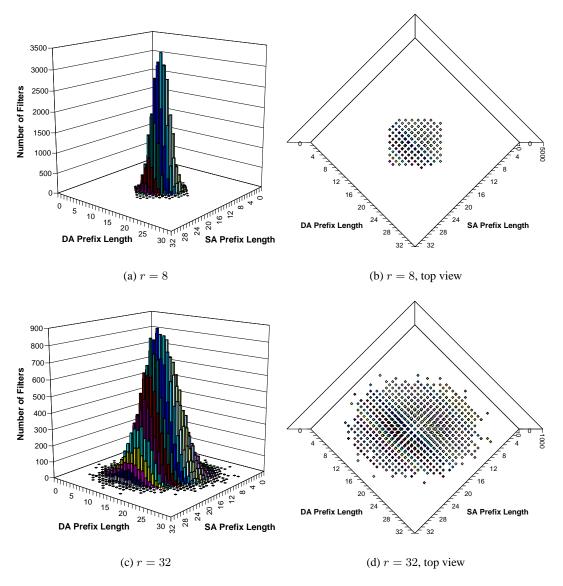

| 6.4  | Prefix pair length distribution for a synthetic filter set of 64000 filters generated with                                                                                                                     | 151  |

| 0.4  | a <i>parameter file</i> specifying 16-bit prefix lengths for all addresses                                                                                                                                     | 134  |

| 6.5  | Prefix pair length distributions for a synthetic filter set of 64000 filters generated                                                                                                                         | 134  |

| 0.5  | with a <i>parameter file</i> specifying 16-bit prefix lengths for all addresses and various                                                                                                                    |      |

|      | values of smoothing parameter $r$ .                                                                                                                                                                            | 136  |

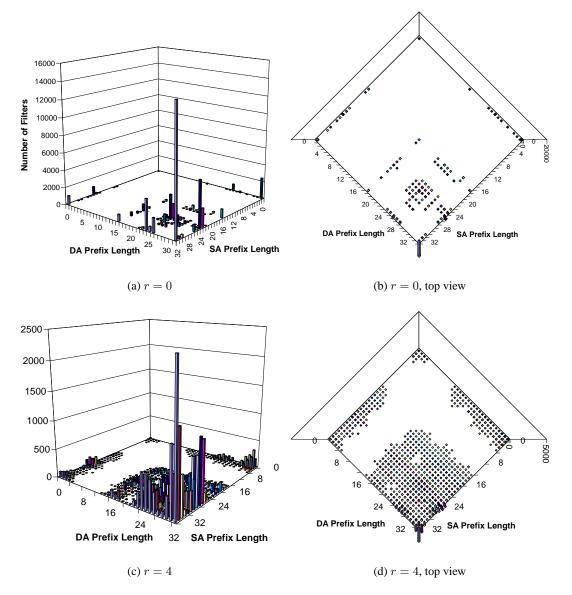

| 66   | Prefix pair length distribution for a synthetic filter set of 64000 filters generated with                                                                                                                     | 150  |

| 6.6  |                                                                                                                                                                                                                | 127  |

| 6.7  | the ipc1 <i>parameter file</i> with smoothing parameters $r = 0$ and $r = 4$                                                                                                                                   | 137  |

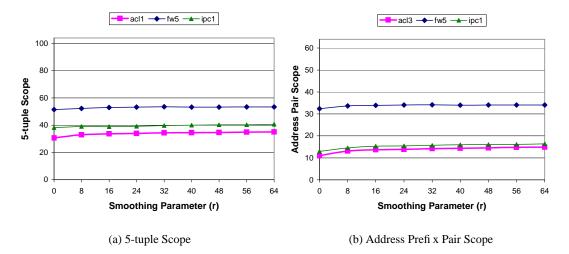

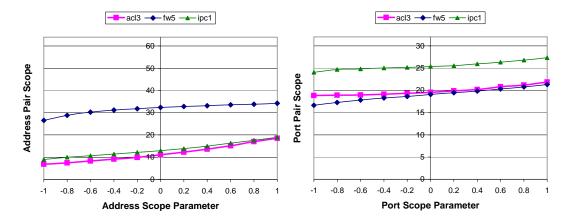

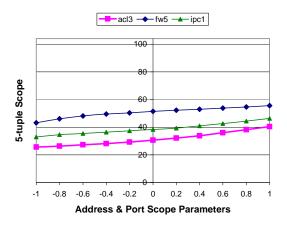

|      | Average scope of synthetic filter sets consisting of 1,000 filters reported with                                                                                                                               |      |

| 0.7  | Average scope of synthetic filter sets consisting of 16000 filters generated with pa-                                                                                                                          |      |

| 0.7  | Average scope of synthetic filter sets consisting of 16000 filters generated with parameter files extracted from filter sets $acl3$ , $fw5$ , and $ipc1$ , and various values of the smoothing parameter $r$ . | 138  |

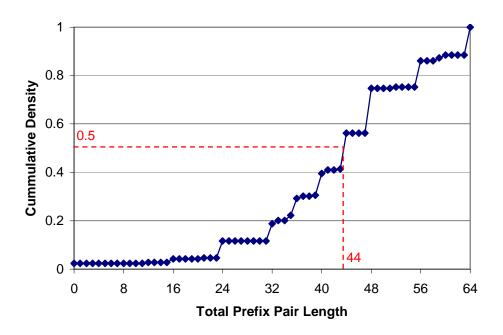

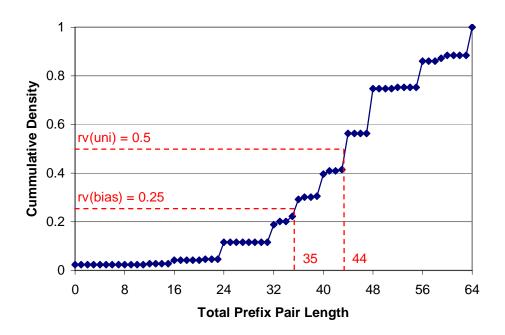

| 6.8  | Example of sampling from a cumulative distribution using a random variable. Dis-                                |     |

|------|-----------------------------------------------------------------------------------------------------------------|-----|

|      | tribution is for the total prefix pair length associated with the WC-WC port pair                               |     |

|      | class of the acl2 filter set. A random variable equal to 0.5 chooses 44 as the total                            |     |

|      | prefix pair length.                                                                                             | 138 |

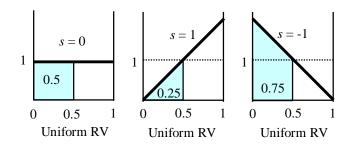

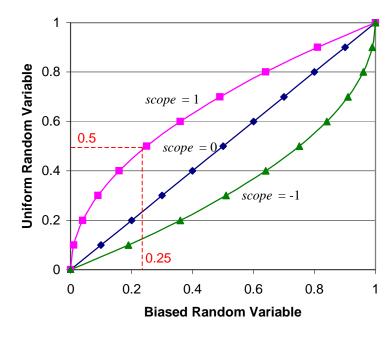

| 6.9  | Scope applies a biasing function to a uniform random variable                                                   | 140 |

| 6.10 | Example of sampling from a cumulative distribution using a random variable. Dis-                                |     |

|      | tribution is for the total prefix pair length associated with the WC-WC port pair                               |     |

|      | class of the acl2 filter set. A random variable equal to 0.5 chooses 44 as the total                            |     |

|      | prefix pair length                                                                                              | 141 |

| 6.11 | Average scope of synthetic filter sets consisting of 16000 filters generated with pa-                           |     |

|      | rameter files extracted from filter sets <i>acl3</i> , <i>fw5</i> , and <i>ipc1</i> , and various values of the |     |

|      | scope parameters                                                                                                | 142 |

| 6.12 | Pseudocode for <i>Trace Generator</i>                                                                           | 144 |

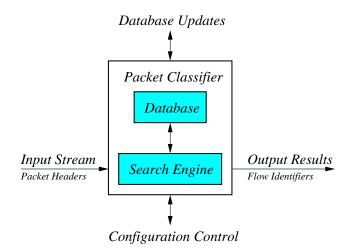

| 6.13 | Generic model of a packet classifier.                                                                           | 146 |

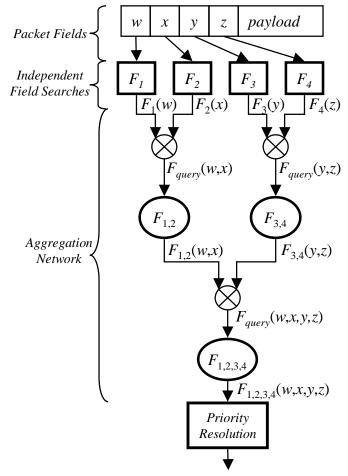

| 7.1  | Example configuration of Distributed Crossproducting of Field Labels (DCFL);                                    |     |

|      | field search engines operate in parallel and may be locally optimized; aggregation                              |     |

|      | nodes also operate in parallel; aggregation network may be constructed in a variety                             |     |

|      | of ways                                                                                                         | 151 |

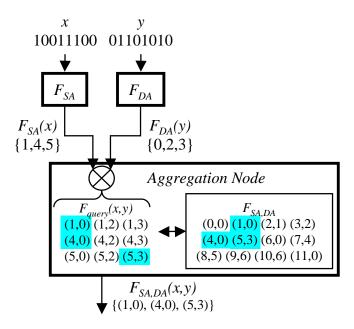

| 7.2  | Example aggregation node for source and destination address fields                                              | 153 |

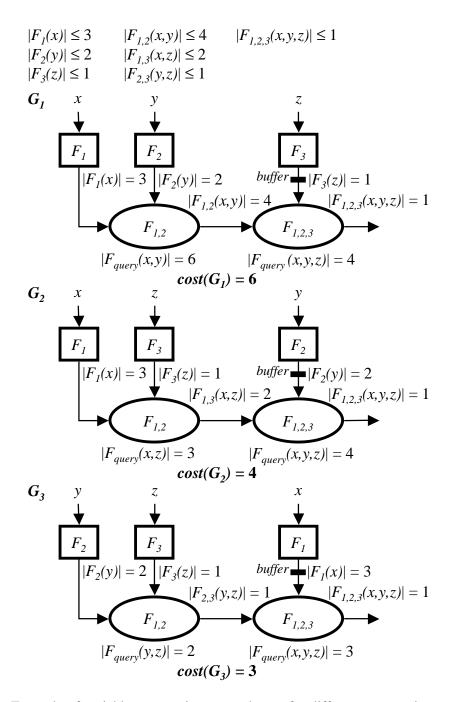

| 7.3  | Example of variable aggregation network cost for different aggregation network                                  |     |

|      | constructions for packet classification on three fields.                                                        | 155 |

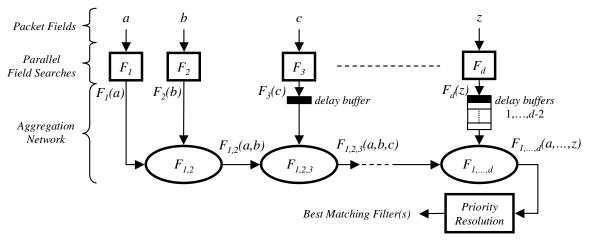

| 7.4  | Generalized DCFL aggregation network for a search on $d$ fields                                                 | 156 |

| 7.5  | An example of splitting a 6-bit address field; maximum number of matching labels                                |     |

|      | per field is reduced from five to three.                                                                        | 158 |

| 7.6  | Example of an aggregation node using a <i>Bloom Filter Array</i> to aggregate field label                       |     |

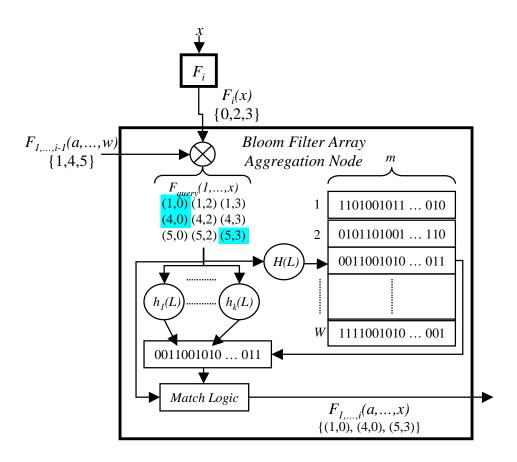

|      | set $F_i(x)$ with label set $F_{1,\dots,i-1}(a,\dots,w)$ .                                                      | 160 |

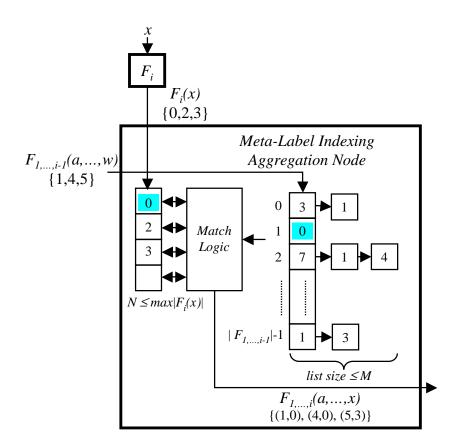

| 7.7  | Example of an aggregation node using <i>Meta-Label Indexing</i> to aggregate field label                        |     |

|      | set $F_i(x)$ with meta-label set $F_{1,\dots,i-1}(a,\dots,w)$ .                                                 | 162 |

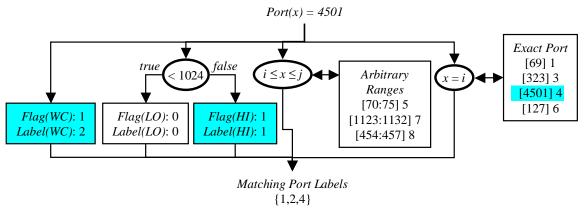

| 7.8  | Block diagram of range matching using parallel search engines for each port class.                              | 164 |

| 7.9  | Pseudocode for <i>DCFL</i> update (add).                                                                        | 166 |

| 7.10 | Pseudocode for <i>DCFL</i> update (delete)                                                                      | 166 |

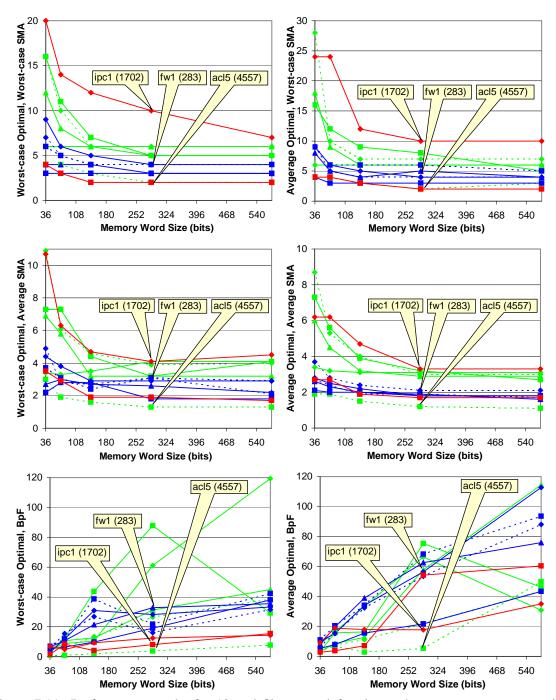

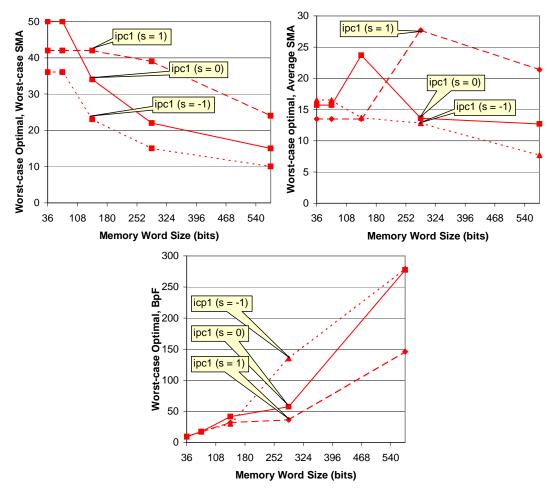

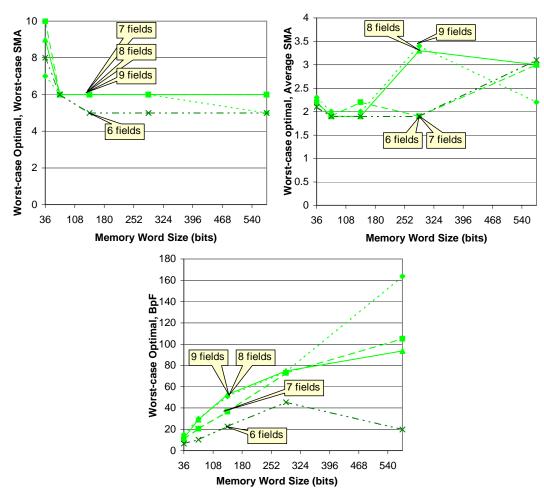

| 7.11 | Performance results for 12 real filter sets; left-column shows worst-case sequential                            |     |

|      | memory accesses (SMA), average SMA, and memory requirements in bytes per                                        |     |

|      | filter (BpF) for aggregation network optimized for worst-case SMA; right-column                                 |     |

|      | shows same results for aggregation network optimized for average-case SMA; call-                                |     |

|      | outs highlight three specific filter sets of various sizes and types (filter set size given                     |     |

|      | in parentheses)                                                                                                 | 169 |

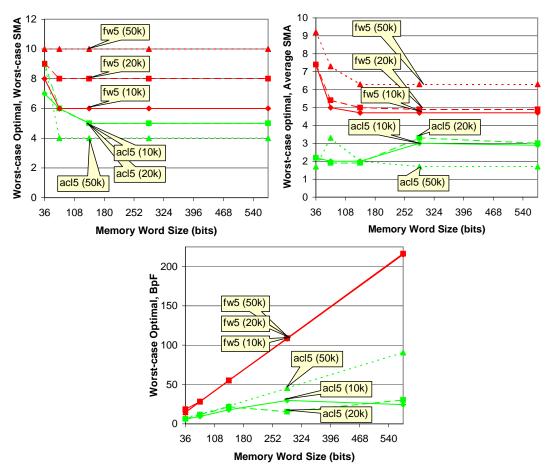

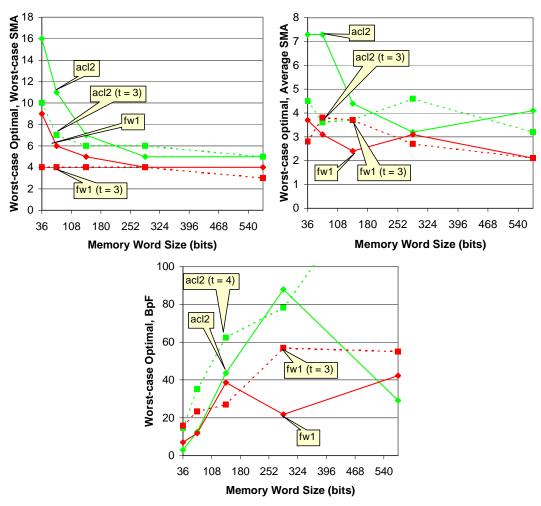

| 7.12 | Performance results for synthetic filter sets containing 10k, 20k, and 50k filters,                   |      |

|------|-------------------------------------------------------------------------------------------------------|------|

|      | generated with parameter files from filter sets acl5 and fw5; call-outs highlight most                |      |

|      | pronounced effects (number of filters given in parentheses)                                           | 170  |

| 7.13 | Performance results for synthetic filter sets containing 16k filters, generated with                  |      |

|      | the <i>ipc1 parameter file</i> with scope parameters $s \{-1,0,1\}$ ; call-outs highlight most        |      |

|      | pronounced effects (scope parameter given in parentheses); note that these filter sets                |      |

|      | are used in the evaluation of the <i>ClassBench</i> tools suite in Figure 6.4.2                       | 172  |

| 7.14 | Performance results for real filter sets (acl2 and fw1) using the Field-Splitting opti-               |      |

|      | mization; call-outs highlight most pronounced effects (field overlap threshold given                  |      |

|      | in parentheses).                                                                                      | 173  |

| 7.15 | Performance results for synthetic filter sets containing 16k filters, generated with                  |      |

|      | parameter file from filter set acl5 with extra filter fields; call-outs highlight most                |      |

|      | pronounced effects (number of filter fields given in parentheses)                                     | 174  |

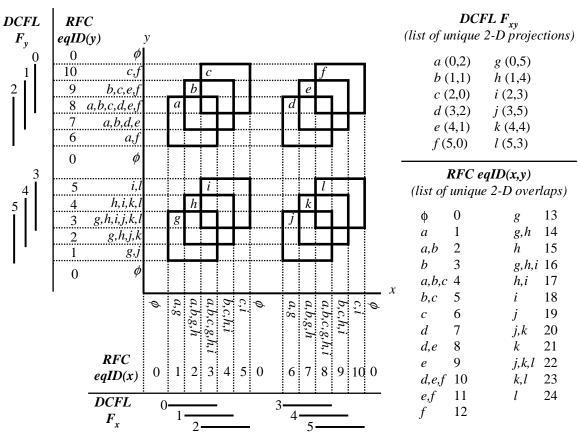

| 7.16 | Contrast between unique field value labels in Distributed Crossproducting of Field                    |      |

|      | Labels (DCFL) and equivalence class identifiers (eqIDs) in Recursive Flow Classi-                     |      |

|      | <i>fication</i> ; example shows two fields of a $d$ field search. Squares $[a \dots l]$ represent the |      |

|      | unique projections of two fields $x$ and $y$ for all filters in a filter table                        | 177  |

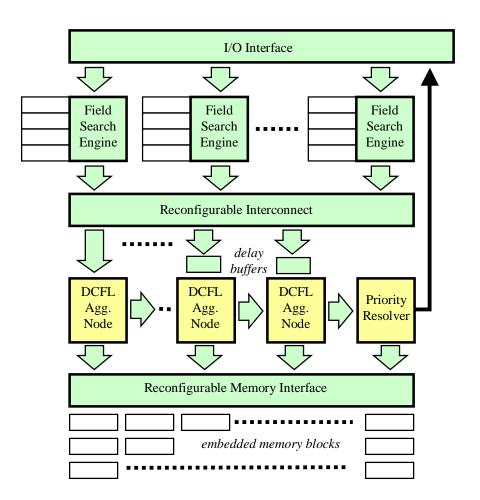

| 8.1  | Potential implementation architecture for Distributed Crossproducting of Field Labels                 | .182 |

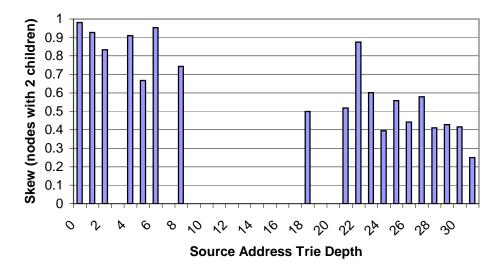

| A.1  | Source address branching probability and skew for filter set ipc1                                     | 184  |

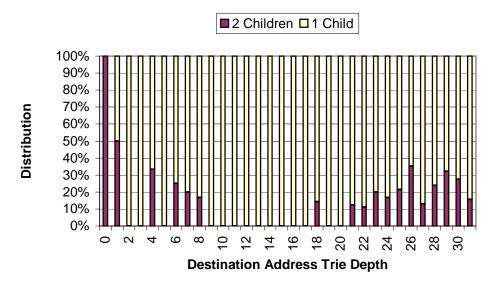

| A.2  | Destination address branching probability and skew for filter set ipc1                                | 185  |

| A.3  | Source address branching probability and skew for filter set fw1                                      | 186  |

| A.4  | Destination address branching probability and skew for filter set fw1                                 | 187  |

| A.5  | Distribution of 5-tuple scope for filters in filter sets acl4 and ipc1                                | 188  |

| A.6  | Distribution of 5-tuple scope for filters in filter sets fw1 and fw5                                  | 189  |

# Acknowledgments

*I not only use all the brains that I have, but all that I can borrow.* Woodrow Wilson, 28th President of the United States of America

My humble measure of intelligence and creativity are not solely responsible for the "novel contributions to the body of knowledge" contained in this dissertation. I have been blessed many times over with loving and supportive family and friends, and a long line of dedicated teachers and mentors. The fruit of this dissertation is a direct result of their selfless acts on my behalf. While it is impossible (and overly tedious) to thank everyone, I will attempt to make mention of those most directly involved in my graduate education and those who kept me sane and happy throughout this adventure.

I would like to start by thanking those serving on my dissertation committee. Inexpressible thanks go to my research advisor, Dr. Jonathan S. Turner, for his tremendous patience and diligent mentorship. I sincerely appreciate the academic freedom he provided throughout my graduate studies, especially early in my studies when I was a rather naïve researcher. His consummate emphasis on clarity and understanding nurtured and encouraged me to produce the highest quality research that I could. Were it not for my academic advisor, trusted friend, and savvy agent, Dr. William D. Richard, I most likely would not have become a graduate student at Washington University. I will forever be thankful for his selfless actions to provide me with wonderful opportunities to learn and contribute. His valued advice always goes well beyond the realms of academics and research; he provides truly useful wisdom. I would like to thank Dr. John Lockwood for offering valuable suggestions and insight, supporting a portion of my graduate studies, involving me in the early development of the Field-programmable Port eXtender (FPX), and demonstrating a commitment and enthusiasm for making concepts "real" in hardware. I would like to thank Dr. Robert E. Morley for serving on my proposal committee. I will always remember his engineering mantra, "there's no such thing as magic", and his probing question about the status of my design projects, "would you get on the airplane?" It has also been an honor to have Dr. Fred U. Rosenberger as a professor and member of my committee. I will always value his insight into fundamental aspects of digital circuit design, healthy skepticism of performance claims (I highly recommend viewing his "Gallery of Perpetual Motion"), and wise advice to employ due caution when designing *anything*. Finally, I would like to thank Dr. Daniel R. Fuhrmann for serving on my committee and offering his insight on short notice.

A number of other Washington University faculty and Applied Research Laboratory staff have generously provided their wisdom, encouragement, and assistance. Specifically, I would like to thank John DeHart for his enthusiasm, patience, and invaluable assistance with verification and performance measurement of the Fast IP Lookup (FIPL) search engine. I am an appreciative beneficiary of his vast engineering talent. Many thanks go to Dave Zar for providing invaluable assistance with Mentor Graphics and Xilinx CAD tools, answering many VHDL questions, and giving me my first research job, publishing opportunity, and conference presentation experience.

My graduate student experience was significantly enhanced by the wonderfully talented group of graduate students in ARL. I would like to sincerely thank Jeyashankher Ramamirtham for being an amiable office-mate and tolerating my numerous interruptions and requests for help with C++ code debugging. I would like to thank Ed Spitznagel for offering his invaluable insight to countless discussions on packet classification techniques, providing assistance with filter set parsing, and being a willing and responsive test case for my *ClassBench* tools. Many thanks to (Dr.) Tilman Wolf for participating in many lively discussions over coffee and fostering a vibrant "culture" in the laboratory and department. Likewise, I would like to thank (Dr.) Dan Decasper and (Dr.) Ralph Keller for fostering a *very* vibrant "culture" when they were at Washington University. Thanks to Anshul Kantawala and the rest of the lunchtime crowd for many enlightening discussions/arguments. Finally, thanks to all the ARL "fools" (you know who you are) for making graduate student life more fun than it ought to be.

I also would like to acknowledge William Eatherton and Zubin Dittia as the developers of the *Tree Bitmap* algorithm. Their design efforts and analyses made a portion of this research possible. I would like to acknowledge Todd Sproull as the developer of the control software and web interfaces for the FIPL search engine. I also would like to thank Tucker Evans and Ed Spitznagel for their contributions to the FIPL Memory Manager software. I would like to thank Sarang Dharmapurikar and Praveen Krishnamurthy for introducing me to Bloom filters and inviting me to work with them in developing the "Longest Prefix Matching using Bloom Filters" technique. I would like to thank Venkatachary Srinivasan, William Eatherton, and others for making several real filter sets available for study.

I would also like to send my sincere thanks "across the pond" to Andreas Herkersdorf and other members of the Network Processor Hardware team at the IBM Zurich Research Laboratory for a rewarding educational and cultural experience. I thoroughly enjoyed my summer in Switzerland and gained a new level of respect for my peers in the international research community.

On a more personal note, I would like to offer my most heartfelt thanks to my wife, Sara Jane Taylor. Her love and companionship have brought me immeasurable joy over the past three years. It has been a tremendous blessing to have someone to empathize with me in the challenges of a doctoral program. I would like to thank my parents who have offered consummate support and encouragement not only in my five years as a graduate student, but throughout my 24 years of formal education. It is impossible to list all that they have done for me, for like God's love, so much of it goes unnoticed and unacknowledged. So, I offer my thanks for everything I have forgotten to thank them for, and specifically: helping me with countless homeworks, lauding my achievements, offering consolation in my defeats, sending me to college, and being shining examples of loving parents. I also offer heartfelt thanks to my dear friends who have been an essential source of inspiration, support, refreshment, and guidance.

Our scientific power has outrun our spiritual power. We have guided missiles and misguided men. Martin Luther King Jr.

I offer my eternal thanks and praise to the Lord Jesus Christ for the saving love and mercy that He demonstrates every day of my life. He has redeemed my life from countless pits, continues to freely extend His grace to me, and showers me with undeserved blessings. All of the contributions and novel ideas in this dissertation are products of His grace in response to my prayers when I reached the end of my natural ability. I also would like to thank my brothers and sisters in Christ at New City Fellowship of St. Louis for their companionship, discipleship, and prayers.

David Edward Taylor

Washington University in Saint Louis August 2004

# Preface

The Internet - a conglomeration of military, academic, and commercial computer communication networks - is arguably the most pervasive technology in recent history. Started as an experimental project by the Defense Advanced Research Projects Agency (DARPA) of the United States Department of Defense in 1973, the Internet continues to expand and diversify [1]. The scope of its use has moved beyond ubiquitous communication and dissemination of information to include new commercial, academic, and private-sector services. Originally the brainchild of the research community and a novelty for the technology hobbyist, the Internet has radically transformed the way the world communicates. It has become essential infrastructure for the global economy, entrenched itself in the cultures of industrialized nations, and penetrated the most remote locations on earth.

While statistics regarding Internet size and use are notoriously difficult to pin down, even the rough estimates are staggering. As of January 2004, there were approximately 233 million Internet hosts [2]. A host refers to any device communicating over the Internet: personal computers, work-stations, servers, Personal Digital Assistants (PDAs), etc. At that time, the United States accounted for 144 million hosts with over seven thousand Internet Service Providers (ISPs). Roughly 945 million people use the Internet world-wide, and the number of users is projected to exceed 1.1 billion in 2005 [3]. Spending for online content increased to \$1.56 billion in 2003 [4], and consumers transacted over \$2.2 billion over the Internet in the one week period following the Thanksgiving holiday in 2003 [5]. These figures could easily double in the next few years as the Internet penetrates the two most populous countries in the world - India and China.

The growth and diversification of the Internet imposes increasing demands on the performance and functionality of network infrastructure. The Internet may be thought of as a global postal system for delivering digital letters, or packets; thus, the task of packet forwarding is akin to sorting mail. In the context of the Internet, the challenge is that packets are transmitted at roughly the speed of light and arrive at rates exceeding a hundred million packets per second. Furthermore, routers, the devices responsible for the switching and directing of traffic in the Internet, may need to sort packets into thousands of different "bins" by consulting a complex directory containing tens of thousands of entries. Routers are being called upon to not only handle increased volumes of traffic at higher speeds, but also impose tighter security policies and provide support for a richer set of network services. A critical issue in realizing the latter set of goals is identifying the traffic belonging to a particular flow or set of flows. A flow may be thought of as the communication traffic generated by a specific application traveling between a specific set of hosts or subnetworks. Flow identification is computationally intensive and the task is complicated by the continually increasing volume and speed of traffic traversing routers.

In this dissertation, we address the packet forwarding and flow identification problems, more commonly known as route lookup and packet classification. Due to their fundamental role in the functionality and performance of Internet routers, both problems are well-studied. Despite the energetic attention of a broad community of researchers in industry and academia, there remains a need for good solutions. In this context, a solution's "goodness" is evaluated along the classical engineering criteria of performance, size, cost, and power consumption. The contributions of this work include a high-performance implementation of a route lookup search engine, an in-depth study of the filter sets used to classify packets, a suite of performance evaluation tools, and a new algorithm for packet classification that scales to larger filter sets and more complex filters.

The value of this work goes beyond prototypes, research tools, and algorithms of academic interest. A number of companies are beginning to offer packet classification search engines as products, and the industry is also gaining interest and investing in algorithmic solutions to the packet classification problem. According to a leading market analyst, the search engine device market grew 14% from \$83 million in 2002 to \$95 million in 2003 [6]. More profound than the total market growth is that the leading company offering algorithmic search engines gained 11% market share while the leading TCAM vendor lost 18% market share. Ternary Content Addressable Memory (TCAM) is a memory technology that searches all entries in the filter set in a single cycle. This strategy results in fast packet classification, but the devices are extremely expensive and power hungry.

## Chapter 1

## Introduction

*Computer Science is no more about computers than astronomy is about telescopes.* Edsger W. Dijkstra

The world is in the midst of a major paradigm shift in the role and importance of communications technology. Many contemporary historians have already dubbed this the "Information Age". Codified by the protocols produced by the DARPA Internet Architecture project begun in 1973, the Internet has emerged as a global communications service of ever increasing importance. The expanding scope of Internet users and applications requires network infrastructure to carry larger volumes of traffic, tightening already challenging performance constraints. This dissertation addresses the searching tasks performed by Internet routers in order to forward packets and apply network services to packets belonging to a particular traffic flows. As these searching tasks must be performed for each packet traversing the router, the speed and scalability of the solutions to these problems largely determine the realizable performance of the router, and hence the Internet as a whole.

### **1.1** State of the Internet

The Internet refers to the global "network of networks" that utilizes the suite of internetworking protocols developed by the DARPA Internet Architecture project initiated in 1973. The original aim of this project was to enable communication across the original ARPANET and the ARPA packet radio network, but the original architects were tasked with developing protocols to enable communication across a wide variety of heterogeneous networks [1]. Due to the nature of the ARPA packet radio network and the set of foreseeable applications, the protocols employ datagrams, or packets, as the fundamental unit of communication, and thus the Internet is a connection-less packet-switched network. The use of datagrams endowed the protocols with a simplicity and flexibility that is largely responsible for the tremendous growth and development that the Internet has enjoyed.

The building blocks of the Internet are essentially networks, each consisting of combinations of possibly heterogeneous hosts, links, and routers. Figure 1.1 provides a simple example of the Internet architecture. Hosts produce and consume packets, or datagrams, which contain chunks of data - a piece of a file, a digitized voice sample, etc. Hosts may be personal computers, workstations, servers, Personal Digital Assistants (PDAs), IP-enabled mobile phones, or satellites. Packets indicate the sender and receiver of the data similar to a letter in the postal system. Links connect hosts to routers, and routers to routers. Links may be twisted-pair copper wire, fiber optic cable, or a variety of wireless link technologies such as radio, microwave, or infrared. There are a variety of strategies for allocating links in a network. These strategies often take into consideration bandwidth and latency requirements of applications, geographical location, deployment and operating costs. The fundamental role of routers is to switch packets from incoming links to the appropriate outgoing links depending on the destination of the packets. Note that a packet may traverse many links, often called hops, in order to reach its destination. Due to the transient nature of network links (failure, congestion, additions, removals), routing protocols allow the routers to continually exchange information about the state of the network. Based on this information, routers decide on which link to forward packets destined for a particular host, network, or subnetwork. Note that the dynamic nature of the routing protocols allows packets from a single host addressed to a common destination to follow different paths through the network.

The original Internet protocol suite was comprised of two protocols: the Internet Protocol (IP) and the Transmission Control Protocol (TCP). The primary function of the Internet Protocol (IP) is to provide an end-to-end packet delivery service. This task is accomplished by including information regarding the sender and receiver with each packet transmitted through the network, much like the forwarding and return addresses on a letter. IP specifies the format of this information which is prepended to the content of each packet. The information prepended by each protocol is referred to as a packet header and the data content of the packet is referred to as the payload. In order to uniquely identify Internet hosts, each host is assigned an Internet Protocol (IP) address. Currently, the vast majority of Internet traffic utilizes Internet Protocol Version 4 (IPv4) which assigns 32-bit addresses to Internet hosts. As shown in Figure 1.2, the IPv4 header prepended to packets includes the IP address of the source and destination host. For the purpose of our discussion, the other IPv4 header field of interest is the *protocol* field which identifies the type of transport protocol used by the sending application. The type of transport protocol determines the format of the transport protocol header following the IP header in the packet.

Rather than individually assign addresses to every host, IPv4 addresses were allocated to organizations in contiguous blocks with the intention that all hosts in the same network share a common set of initial bits. This common set of initial bits is referred to as the network address or prefix; the remaining set of bits is called the host address. This allocation strategy provided decentralized control of address allocation; each organization was free to make allocation decisions for the addresses within its assigned block. As shown in Figure 1.3, IPv4 addresses were originally

Figure 1.1: Simple diagram of Internet architecture.

assigned in blocks of three sizes: Class A (16 million hosts), Class B (64 thousand hosts), and Class C (254 hosts). Note that there are also blocks of Class D addresses for multicast (one-to-many transmission) and reserved Class E addresses. Most organizations which required a larger address space than Class C were allocated a block of Class B addresses, even though their network consumed only a fraction of the addresses. This waste of available address space combined with the explosive growth of the Internet prompted concerns over the impending shortage of unassigned IP addresses. Classless Inter-Domain Routing (CIDR) was introduced in order to prolong the life of IPv4 [7]. CIDR essentially allows a network address to be an arbitrary length prefix of the IP address, thus a network's address space may span multiple Class C networks. CIDR also allows routing protocols to aggregate network addresses in order to reduce the amount of packet forwarding information stored by each router. The wide adoption of CIDR by the Internet community has slowed the deployment of a more permanent solution, Internet Protocol Version 6 (IPv6) [8]. Among other issues, the designers of IPv6 addressed the address space issue via the use of 128-bit addresses. Despite the relief provided by CIDR, adoption of IPv6 is probable given the continued increase in the number of Internet hosts and deployment initiatives by influential research and commercial groups [9].

The second protocol produced by the original Internet Architecture project, the Transmission Control Protocol (TCP), provides a reliable transmission service for IP packets. Through the

Figure 1.2: Format of Internet Protocol Version 4 (IPv4) packet headers with appended transport protocol header fields.

Class 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Figure 1.3: Internet Protocol Version 4 (IPv4) address space allocation.

use of small acknowledgment packets transmitted from the destination host to the source host, TCP detects packet loss and paces the transmission of packets in order to adjust to network congestion. When the source host detects packet loss, it retransmits the lost packet or packets. At the destination host, TCP provides in-order delivery of packets to higher level protocols or applications. After

vog oddad t

initial development of TCP, a third protocol, the User Datagram Protocol (UDP), was added to the original suite in order to provide additional flexibility. UDP essentially allows applications or higher level protocols to dictate transmission behavior. For example, a streaming video application may wish to ignore transient packet losses in order to prevent large breaks in the video stream caused by packet retransmissions.

Typically, the TCP and UDP transport protocols identify applications using 16-bit port numbers carried in the transport header as shown in Figure 1.2. In order to provide services to unknown hosts, servers must have static "contact ports" for each application. Port numbers for widely-used applications fall in the range of well-known *system* ports which are assigned by the Internet Assigned Numbers Authority (IANA). Prior to 1993, the well-known port numbers were in the range [0...255] while port numbers [256...1023] were used in Unix systems for Unix-specific services. Since 1993, port numbers in the range [0...1023] form the set of well-known *system* port numbers managed by IANA. A "living document" of *system* port number assignments is available at http://www.iana.org/assignments/port-numbers. For applications where either TCP or UDP may be used, port number assignments are typically identical. Unlike servers, clients only need to guarantee that running applications use free port numbers. The range of port numbers that may be freely assigned by clients are referred to as ephemeral *user* ports due to their short-lived and unmanaged nature. The set of *user* port numbers span the range [1024...49151] for popular applications which do not have an assigned *system* port.

### **1.2 The "Next Generation" Internet**

While the protocols produced by the Internet Architecture project achieved the original goals set forth by DARPA and the pioneering group of researchers, the use of datagrams also presents challenges for those striving to deploy the next-generation of Internet services, particularly real-time services such as Internet telephony and video conferencing. It is important to note that the choice of datagrams and packet-switching represents a significant departure from the circuit-switched networks originally developed and deployed by the telecommunications industry. While the Internet protocols simplify the task of combining heterogeneous networks, the use of packet-switching complicates the provision of bandwidth and quality of service guarantees. As mentioned above, packets flowing between a fixed set of hosts may take different paths through the network. Due to the heterogeneous nature of the Internet, packets following different paths will likely experience different hop counts and congestion resulting in unpredictable latency and bottleneck link capacity. Circuit-switched networks allow data to flow along a fixed path, offering predictable performance. The major drawback of circuit-switching is the need to negotiate an end-to-end path through the network. In the case of the Internet, this would require coordination across many heterogeneous networks operated by independent parties with potentially competing interests. Enabling quality of service and real-time performance guarantees are just a couple of the challenges facing the community architecting the "next-generation" Internet. As the Internet becomes increasingly essential infrastructure for the global economy, security is a major concern. Due to their roots in academic research, many network protocols were developed and implemented with little if any consideration of security issues. As a result, many academic and commercial institutions have suffered from destructive network intrusions by hackers, viruses, and worms. Those holding a vested interest in the security of the Internet now find themselves in a perpetual "arms race" with nefarious programmers. Furthermore, IP has essentially become a victim of its own popularity. The amount of investment in the IP infrastructure by Internet Service Providers (ISPs) has yielded significant resistance to changing the architecture. This hardening of the Internet architecture also presents a significant challenge to realizing the "next-generation" Internet.

Despite concerns over security and ossification of the Internet protocols, many in the research community have put forth grand visions of the "next-generation" Internet. While specifics invariably differ, common goals include: retaining the flexibility provided by IP while enabling the performance guarantees made available by circuit-switching, providing a level of security that warrants greater economic reliance, and enabling more rapid development and deployment of services. Some go so far as to set forth the goal that the Internet become reliable enough to support the air traffic control system [10].

### **1.3** The Packet Classifi cation Problem

In a circuit-switched network, the task of identifying the traffic associated with a particular application session between two hosts or subnetworks is trivial from the router's perspective. A simple, fixed-length flow identifier can be prepended to each unit of data that identifies the established endto-end connection. For each unit of data, a router simply performs an exact match search over a table containing the flow identifiers for established connections. The table entries for each flow identifier contain the output link on which to forward the data and may also specify quality of service guarantees or special processing the router should perform.

The flow identification task in a packet-switched network is significantly more challenging. The primary task of routers is to forward packets from input links to the appropriate output links. In order to do this, Internet routers must consult a *route table* containing a set of network addresses and the output link or *next hop* for packets destined for each network. Entries in the route tables change dynamically according to the state of the network and the information exchanged by routing protocols. The task of resolving the next hop from the destination IP address is commonly referred to as *route lookup* or *IP lookup*. Finding the network address given a packet's destination address would not be overly difficult if the Internet Protocol (IP) address hierarchy were strictly maintained. A simple lookup in three tables, one for each Class of networks, would be sufficient. The wide adoption of CIDR allows the network addresses in route tables to be any size. Performing a search

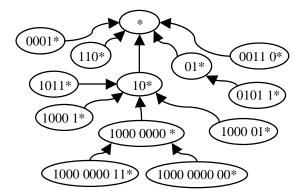

Figure 1.4: Example of Longest Prefix Matching for a 12-bit search key; all shaded prefixes match the key, but 1000000011\* is the longest matching prefix.

in 32 tables, one for each possible network address length, for every packet traversing the router is not a viable option. If we store all the variable-length network addresses in a single table, a route lookup requires finding the longest matching prefix (network address) in the table for the given destination address.

Stated formally, a prefix is a subset of initial bits of a key value, the IP destination address in the case of route lookups. By definition, key values that share a common prefix have the same contiguous subset of bits starting at the most significant bit. Given a search key x of size b bits, Longest Prefix Matching (LPM) is a search technique which selects the prefix  $p_i$  in the set of prefixes P, such that  $p_i$  matches x and  $p_i$  has the most specified bits. Each prefix  $p_i$  can be thought of as the combination of a b-bit key and a corresponding b-bit mask which identifies the valid bits in the key. By definition, the mask is contiguous in LPM; i.e. the most significant invalid bit in the mask must be succeeded by invalid bits. Prefixes can be succinctly represented by simply using the \* character to denote the end of the valid bits in the prefix. An example of Longest Prefix Matching (LPM) for a 12-bit search key is provided in Figure 1.4. Note that the four shaded prefixes match the search key, but 100000011\* is the longest matching prefix. The throughput of an Internet router largely depends upon the speed at which it can perform Longest Prefix Matching (LPM).

If an Internet router is to provide more advanced services than packet forwarding, it must perform finer grained flow identification. In the Internet context, the process of identifying the packets belonging to a specific application session or group of sessions between a source and destination

Table 1.1: Example filter set of 16 filters classifying on four fields; each filter has an associated flow identifier (*Flow ID*) and priority tag (*PT*) where  $\dagger$  denotes a non-exclusive filter; wildcard fields are denoted with \*.

|          | Filter   |      |        | Action | on |  |

|----------|----------|------|--------|--------|----|--|

| SA       | DA       | Prot | DP     | FlowID | PT |  |