## Washington University in St. Louis Washington University Open Scholarship

All Computer Science and Engineering Research

**Computer Science and Engineering**

Report Number: WUCSE-2004-48

2004-08-04

## Pipeline Task Scheduling with Appication to Network Processors

#### Seema Datar

Chip Multi-Processors (CMPs) are now available in a variety of systems and provide the opportunity for achieving high computational performance by exploiting application-level parallelism. In the communications environment, network processors (NPs), designed around CMP architectures, are generally usable in a pipelined manner. This leads to the need for static scheduling of tasks on processor pipelines. This thesis considers problems associated with determining optimal schedules for such pipelines. A collection of algorithms is presented with their utility determined by the size and other characteristics of the system. The algorithms employ heuristics, dynamic programming and statistical methods to schedule tasks derived... Read complete abstract on page 2.

Follow this and additional works at: https://openscholarship.wustl.edu/cse\_research

#### **Recommended Citation**

Datar, Seema, "Pipeline Task Scheduling with Appication to Network Processors" Report Number: WUCSE-2004-48 (2004). *All Computer Science and Engineering Research*. https://openscholarship.wustl.edu/cse\_research/1021

Department of Computer Science & Engineering - Washington University in St. Louis Campus Box 1045 - St. Louis, MO - 63130 - ph: (314) 935-6160.

This technical report is available at Washington University Open Scholarship: https://openscholarship.wustl.edu/ cse\_research/1021

### Pipeline Task Scheduling with Appication to Network Processors

Seema Datar

#### **Complete Abstract:**

Chip Multi-Processors (CMPs) are now available in a variety of systems and provide the opportunity for achieving high computational performance by exploiting application-level parallelism. In the communications environment, network processors (NPs), designed around CMP architectures, are generally usable in a pipelined manner. This leads to the need for static scheduling of tasks on processor pipelines. This thesis considers problems associated with determining optimal schedules for such pipelines. A collection of algorithms is presented with their utility determined by the size and other characteristics of the system. The algorithms employ heuristics, dynamic programming and statistical methods to schedule tasks derived from multiple application flows on pipelines with an arbitrary number of stages. Experimental results indicate that while the dynamic programming algorithm obtains the optimal schedules, heuristics and statistical methods obtain schedules within 10% of the optimal, 95% of the time. Examples are given to show the use of these algorithms for general pipeline/algorithm design and for use in the Network Processor environment with typical networking applications.

#### SEVER INSTITUTE OF TECHNOLOGY

#### MASTER OF SCIENCE DEGREE

### THESIS ACCEPTANCE

(To be the first page of each copy of the thesis)

DATE: August 04, 2004

STUDENT'S NAME: Seema Datar

This student's thesis, entitled <u>Pipeline Task Scheduling with Application to</u> <u>Network Processors</u> has been examined by the undersigned committee of four faculty members and has received full approval for acceptance in partial fulfillment of the requirements for the degree Master of Science.

APPROVAL: Chairman

Short Title: Pipeline Task Scheduling

Datar, M.Sc. 2004

## WASHINGTON UNIVERSITY SEVER INSTITUTE OF TECHNOLOGY DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

# PIPELINE TASK SCHEDULING WITH APPLICATION TO NETWORK

PROCESSORS

by

Seema Datar, B.E.

Prepared under the direction of Dr. Mark A. Franklin

A thesis presented to the Sever Institute of Washington University in partial fulfillment of the requirements for the degree of

Master of Science

August, 2004

Saint Louis, Missouri

## WASHINGTON UNIVERSITY SEVER INSTITUTE OF TECHNOLOGY DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

### ABSTRACT

### PIPELINE TASK SCHEDULING WITH APPLICATION TO NETWORK PROCESSORS

by Seema Datar

ADVISOR: Dr. Mark A. Franklin

August, 2004

Saint Louis, Missouri

Chip Multi-Processors (CMPs) are now available in a variety of systems and provide the opportunity for achieving high computational performance by exploiting application-level parallelism. In the communications environment, network processors (NPs), designed around CMP architectures, are generally usable in a pipelined manner. This leads to the need for static scheduling of tasks on processor pipelines. This thesis considers problems associated with determining optimal schedules for such pipelines. A collection of algorithms is presented with their utility determined by the size and other characteristics of the system. The algorithms employ heuristics, dynamic programming and statistical methods to schedule tasks derived from multiple application flows on pipelines with an arbitrary number of stages. Experimental results indicate that while the dynamic programming algorithm obtains the optimal schedules, heuristics and statistical methods obtain schedules within 10% of the optimal, 95% of the time. Examples are given to show the use of these algorithms for general pipeline/algorithm design and for use in the Network Processor environment with typical networking applications. to my parents

# Contents

| Li            | List of Tables |         |                                     |      |

|---------------|----------------|---------|-------------------------------------|------|

| $\mathbf{Li}$ | st of          | Figur   | $\mathbf{es}$                       | viii |

| A             | ckno           | wledgr  | ments                               | x    |

| 1             | Intr           | coduct  | ion                                 | 1    |

|               | 1.1            | Gener   | ic NP Architecture                  | 2    |

|               | 1.2            | Proble  | em Introduction                     | 3    |

|               | 1.3            | Relate  | ed Work                             | 5    |

|               | 1.4            | Thesis  | s Outline                           | 7    |

| <b>2</b>      | Pip            | eline 7 | Task Scheduling Problem             | 9    |

|               | 2.1            | Proble  | em Formulation                      | 9    |

|               | 2.2            | Assign  | nment Constraints                   | 11   |

|               | 2.3            | Memo    | ory Contention Model                | 12   |

|               | 2.4            | Perfor  | rmance Metrics                      | 17   |

|               | 2.5            | Comp    | lete Enumeration Method             | 18   |

| 3             | Gre            | edypi   | pe - A Heuristic                    | 21   |

|               | 3.1            | Greed   | lypipe Algorithm                    | 21   |

|               |                | 3.1.1   | Greedypipe: Overall Algorithm       | 23   |

|               |                | 3.1.2   | A Simple Example                    | 24   |

|               | 3.2            | Comp    | blexity of <i>Greedypipe</i>        | 26   |

|               |                | 3.2.1   | Multiple Flows with no shared tasks | 26   |

|               |                | 3.2.2   | Multiple Flows with shared tasks    | 27   |

|               | 3.3            | Greed   | yPipe Performance                   | 27   |

| <b>4</b> | Dyı            | namic 1 | Programming                                                                                                              | <b>31</b> |

|----------|----------------|---------|--------------------------------------------------------------------------------------------------------------------------|-----------|

|          | 4.1            | Dynar   | mic Programming for Task Scheduling                                                                                      | 32        |

|          |                | 4.1.1   | Example                                                                                                                  | 35        |

|          |                | 4.1.2   | Multiple Flows with Shared Tasks                                                                                         | 37        |

|          | 4.2            | Comp    | lexity                                                                                                                   | 38        |

| <b>5</b> | $\mathbf{Sim}$ | ulated  | Annealing - A Statistical Approach                                                                                       | 40        |

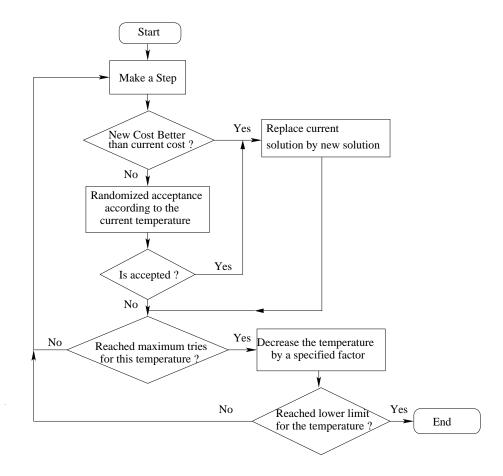

|          | 5.1            | Simula  | ated Annealing for Task Scheduling                                                                                       | 42        |

|          |                | 5.1.1   | Step Change                                                                                                              | 42        |

|          |                | 5.1.2   | Annealing Schedule                                                                                                       | 43        |

|          |                | 5.1.3   | Initial Task Assignment                                                                                                  | 45        |

|          |                | 5.1.4   | Multiple Flows                                                                                                           | 45        |

|          | 5.2            | Comp    | lexity                                                                                                                   | 46        |

|          | 5.3            | Perfor  | mance and Constraints                                                                                                    | 47        |

| 6        | Pip            | eline I | $Design \ldots \ldots$ | 48        |

|          | 6.1            | Pipeli  | ne Design using Scheduling Algorithms                                                                                    | 48        |

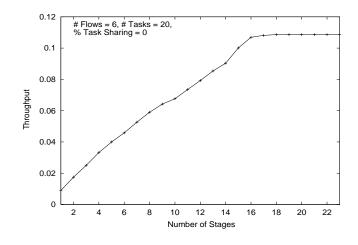

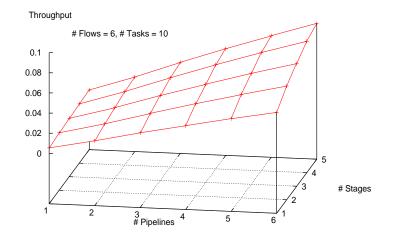

|          |                | 6.1.1   | Number of Pipeline Stages and Number of Pipelines: $\ldots$ .                                                            | 50        |

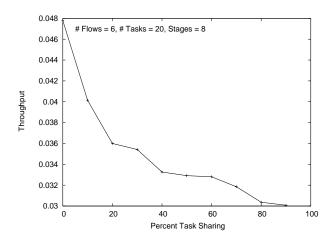

|          |                | 6.1.2   | Sharing of Tasks Between Flows                                                                                           | 51        |

|          |                | 6.1.3   | Task Partitioning                                                                                                        | 52        |

|          |                | 6.1.4   | Number of Memory Banks and Memory Bank Assignment $\ .$ .                                                                | 54        |

|          | 6.2            | A Net   | work Processor Problem                                                                                                   | 55        |

|          |                | 6.2.1   | Longest Prefix Matching (LPM)                                                                                            | 56        |

|          |                | 6.2.2   | AES Encryption - A Pipelined Implementation                                                                              | 59        |

|          |                | 6.2.3   | Data Compression - A Pipelined Implementation                                                                            | 61        |

|          |                | 6.2.4   | NP Example Design Results                                                                                                | 62        |

|          |                | 6.2.5   | Simulated Annealing for Task & Memory Assignment                                                                         | 65        |

| 7        | Cor            | nparat  | ive Study of Solution Approaches                                                                                         | 68        |

|          | 7.1            | Comp    | lexity Analysis                                                                                                          | 68        |

|          | 7.2            | Execu   | tion Time and Accuracy                                                                                                   | 70        |

|          |                | 7.2.1   | SP/SF                                                                                                                    | 71        |

|          |                | 7.2.2   | SP/MF                                                                                                                    | 72        |

|          |                | 7.2.3   | SP/MF/ST                                                                                                                 | 73        |

|          |                | 7.2.4   | SP/SF/SM                                                                                                                 | 75        |

|          |                | 7.2.5   | SP/MF/SM                                                                                                                 | 76        |

|          |                |         |                                                                                                                          |           |

| 8  | Con   | clusions and Future Work                | <b>7</b> 8 |

|----|-------|-----------------------------------------|------------|

|    | 8.1   | Contributions                           | 78         |

|    | 8.2   | Future Work                             | 79         |

| A  | ppen  | dix A Memory Contention Delay           | 81         |

| A  | ppen  | dix B Phoenix Toolset Manual (ver 1.0)  | 84         |

|    | B.1   | Usage                                   | 84         |

|    |       | B.1.1 Command Line Format               | 85         |

|    |       | B.1.2 Configuration File Format         | 87         |

|    |       | B.1.3 Output Format                     | 89         |

|    | B.2   | Example                                 | 90         |

| Aj | ppen  | dix C Phoenix Toolset File Organisation | 94         |

| Re | efere | nces                                    | 96         |

| Vi | ita . |                                         | .01        |

# List of Tables

| 2.1 | A Single Flow, Single Shared Memory Example                                  | 13 |

|-----|------------------------------------------------------------------------------|----|

| 3.1 | A Single Flows with five <i>ordered</i> tasks                                | 24 |

| 3.2 | All possible allocations for Stage 1                                         | 24 |

| 3.3 | Best allocations for Stage 2                                                 | 25 |

| 3.4 | Best allocations, forward direction                                          | 26 |

| 4.1 | A Single Flow with five <i>ordered</i> tasks                                 | 35 |

| 4.2 | Optimal Solutions at Stage 1                                                 | 35 |

| 4.3 | Possible States at Stage 2                                                   | 36 |

| 4.4 | Optimal State Values at Stage 2                                              | 36 |

| 4.5 | Possible States at Stage 3                                                   | 36 |

| 4.6 | Optimal State Values at Stage 3                                              | 37 |

| 4.7 | Optimal allocations                                                          | 37 |

| 6.1 | Task Times ( $\mu sec$ ) for LPM, Encryption & Compression                   | 59 |

| 6.2 | Bandwidths for Best Assignments (Pps=Packets/second; Flow 1 packet           |    |

|     | length=40 Bytes; Flow 2 & 3 packet length=1500 Bytes) $\ldots \ldots \ldots$ | 64 |

| 6.3 | Task Times ( $\mu sec$ ) for AES Encryption assuming 15 clock cycles per     |    |

|     | memory access                                                                | 65 |

| 7.1 | Time Complexities                                                            | 69 |

| B.1 | Sample - Interactive Command Line Option                                     | 84 |

| B.2 | Command Line Options For <i>Phoenix</i>                                      | 84 |

# List of Figures

| 1.1  | Generic Network Processor Architecture                                                                                            |

|------|-----------------------------------------------------------------------------------------------------------------------------------|

| 1.2  | NP Task Scheduling Problem Examples                                                                                               |

| 2.1  | Memory Contention Example                                                                                                         |

| 2.2  | Worst Case Memory Contention Computation                                                                                          |

| 2.3  | Variation in execution time for flows with no shared tasks 19                                                                     |

| 2.4  | Variation in execution time for flows with shared tasks                                                                           |

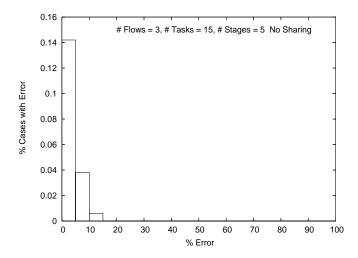

| 3.1  | % Error vs % Cases with Error $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 27$                                        |

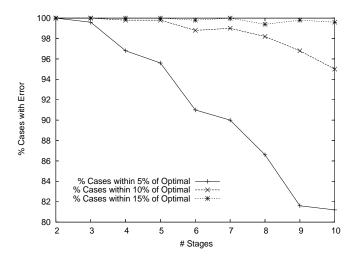

| 3.2  | $\%$ Error vs Number of Stages $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 28$                         |

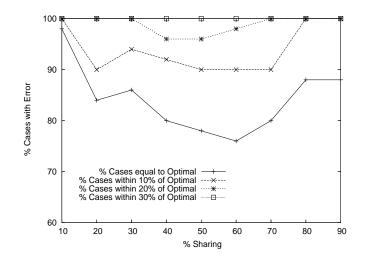

| 3.3  | % Error vs $%$ Sharing                                                                                                            |

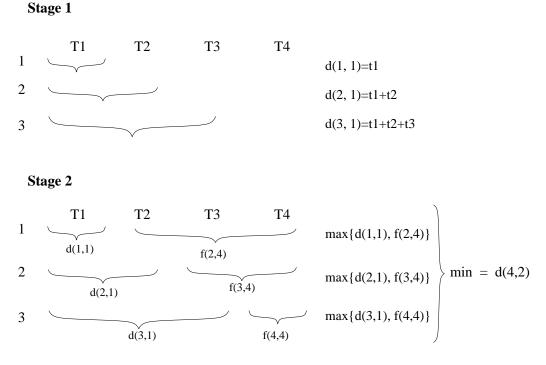

| 4.1  | Dynamic Programming                                                                                                               |

| 5.1  | Simulated Annealing Flow Diagram                                                                                                  |

| 5.2  | A Step in Simulated Annealing 42                                                                                                  |

| 6.1  | Throughput vs number of pipeline stages                                                                                           |

| 6.2  | Throughput vs number of pipelines vs number of stages                                                                             |

| 6.3  | Throughput vs percent shared tasks                                                                                                |

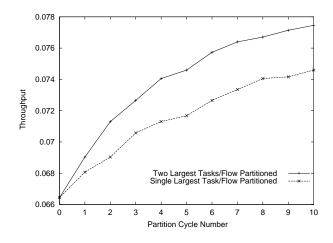

| 6.4  | Throughput vs task partitioning                                                                                                   |

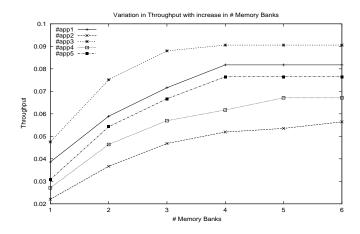

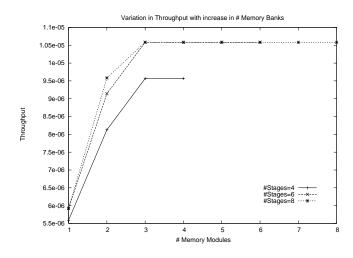

| 6.5  | Throughput versus Number of Memory Banks                                                                                          |

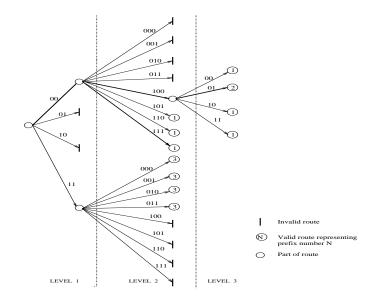

| 6.6  | Example Longest Prefix Match Tree                                                                                                 |

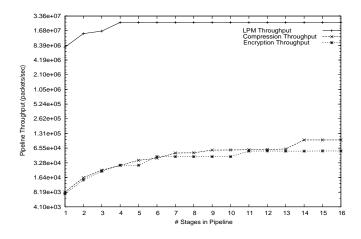

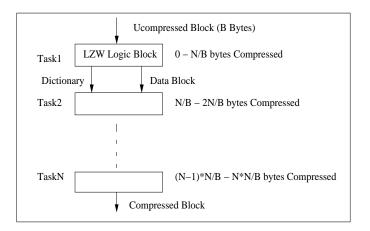

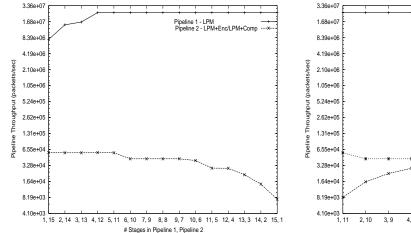

| 6.7  | Throughput vs. Number of Stages (A single separate pipeline for each                                                              |

|      | application) $\ldots \ldots 59$ |

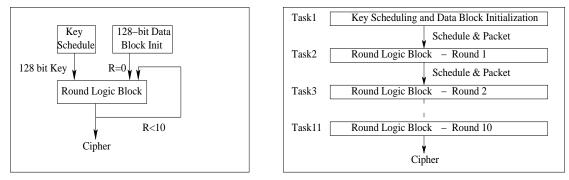

| 6.8  | Rijndael Algorithm Implementation Block Diagram 61                                                                                |

| 6.9  | Pipelined Implementation of the $LZW$ Algorithm                                                                                   |

| 6.10 | Two Pipelines - Throughput vs. Num. Stages $(X, Y \rightarrow X \text{ stages for})$                                              |

|      | Pipe 1 & Y stages for Pipe 2)    65                                                                                               |

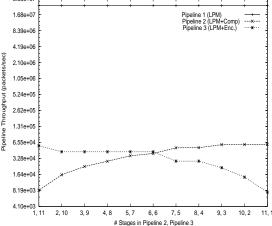

| 6.11 | Three Pipelines - Throughput vs Num. stages for Pipelines 2 & 3;           |    |

|------|----------------------------------------------------------------------------|----|

|      | Pipeline 1=4 stages                                                        | 65 |

| 6.12 | Throughput vs Number Memory Banks                                          | 66 |

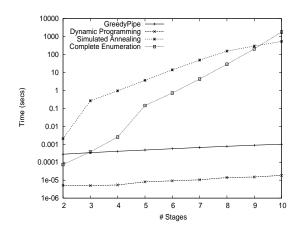

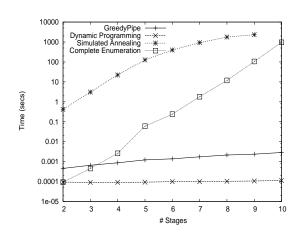

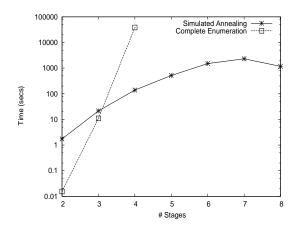

| 7.1  | Execution Time, Single Flow                                                | 71 |

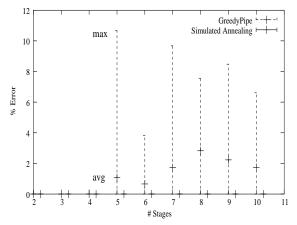

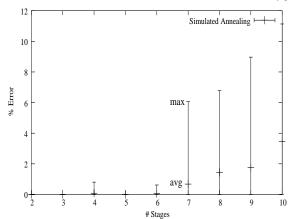

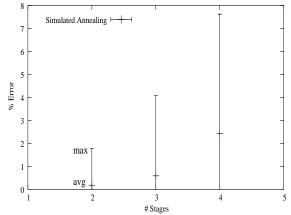

| 7.2  | % Error in Throughput, Single Flow (SA is optimal over all experiments)    | 71 |

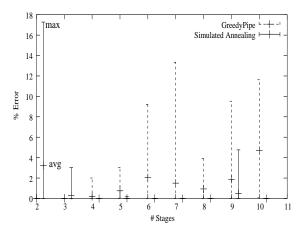

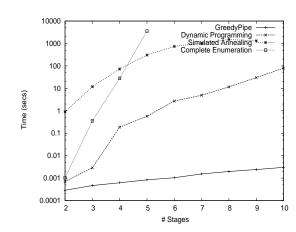

| 7.3  | Execution Time for Multiple Flows.                                         | 72 |

| 7.4  | % Error in Throughput, Multiple Flows.                                     | 72 |

| 7.5  | Execution Time for Multiple Flows, Shared Tasks                            | 73 |

| 7.6  | $\%$ Error in Throughput, Multiple Flows, Shared Tasks $\ \ . \ . \ . \ .$ | 73 |

| 7.7  | Execution Time; Single Flow, Memory Contention                             | 75 |

| 7.8  | % Error in Throughput, Single Flow, Memory Contention                      | 75 |

| 7.9  | Execution Time; Multiple Flows, Memory Contention                          | 76 |

| 7.10 | % Error in Throughput; Multiple Flows, Memory Contention                   | 76 |

| A.1  | Multi-flow Memory Contention                                               | 82 |

| B.1  | Sample - <i>Phoenix</i> Toolset Configuration File                         | 87 |

| B.2  | Sample - <i>Phoenix</i> Toolset Output                                     | 89 |

| B.3  | Sample - <i>Phoenix</i> Interactive Execution                              | 91 |

| B.4  | Example - config.txt                                                       | 92 |

| B.5  | Example - <i>Phoenix</i> Output                                            | 93 |

|      |                                                                            |    |

# Acknowledgments

I would like to thank my advisor, Dr. Mark A. Franklin, for his supervision, guidance, insightful suggestions and support for the last two years. I would also like to thank the other members of my thesis defense committee, Dr. Roger Chamberlain, Dr. Patrick Crowley and Dr. Jason Fritts, who offered their time, experience and expertise in the evaluation of my research.

I would like to thank all my friends in the CSE department for the wonderful time spent at work. I would in particular like to thank Vinayak Joshi and Sarang Dharmapurikar for sharing their time and knowledge throughout the last two years. I would also like to thank Praveen Krishnamurthy, Roopa Pundaleeka and Bharath Madhusudan for the many enjoyable experiences we shared.

The research represented in this thesis was supported in part by NSF under grant CCR-0217334 and I would like to thank the organization for its financial support.

I would also like to acknowledge Jean Grothe, Myrna Harbison, Peggy Fuller, Sharon Matlock and Stella Sung for their efforts in making the CSE department run effectively.

Finally I would like to thank my parents for all their love and support.

Seema Datar

Washington University in Saint Louis August 2004

# Chapter 1

# Introduction

Due to increased data rates and the requirements of more sophisticated networking protocols and functions, networking solutions continue to demand more powerful processing capabilities. These processing requirements are in flux and continue to change and evolve. Thus, another important aspect of satisfying processing needs is that the solution have the flexibility to respond to changing requirements. This has led to the development of the Network Processor (NP), a software programmable device with architecture and features, that are designed for efficient packet processing. It achieves a high programming power by employing multiple programmable processing engines (PEs), by adding special instructions targeted to networking applications, and by having dedicated on-chip logic implementing selected complex functions. Thus, the NP combines the best of both worlds; the flexibility/programmability of a generic processor and the speed of hardwired ASIC solutions. Network Processors (NPs), designed around Chip Multi-Processor (CMP) architectures, may be used in a pipelined manner. This leads to the issue of scheduling tasks on processor pipelines. The research considered in this thesis evaluates problems associated with determining optimal schedules for such pipelines.

Figure 1.1: Generic Network Processor Architecture

### 1.1 Generic NP Architecture

Figure 1.1 shows the layout of a typical Network Processor. The PEs in an NP are typically arranged in a parallel or a pipelined fashion and NPs with as many as sixteen PEs are currently commercially available [20, 21, 27]. The arrangement is configurable and selecting the best one is important in achieving high performance. The data path of a packet begins at the switch fabric interface where the packet is received and passed on to the Packet De-multiplexer and Scheduler unit. The scheduler performs packet classification and allocates the packets to the appropriate PE resources. Note that the NP may be configured to have multiple PE pipelines and packets may require assignment to a particular pipeline depending on their processing requirements. After progressing through a pipeline of PEs, the packet is returned to the switch fabric through the switch scheduler and is transmitted to the next node of the network. NPs have a fast access on-chip RAM in addition to external DRAM

(for large routing and classification tables) and SRAM capabilities. Additionally, the on-chip RAM (i.e., internal shared memory) may consist of multiple modules with one or more PEs being associated with a given module. Note that when memory modules are shared, contention for this resource can result in a loss of performance.

### **1.2** Problem Introduction

This research concentrates on NPs that are configured into one or more PE pipelines. We consider situations where packet applications are segmented into an ordered set of tasks with these tasks assigned to a pipeline of PEs (each PE is a pipeline stage). Thus the packet is processed in parts as it progresses through the pipeline, executing each task of the application in turn. Packet processing may involve multiple applications and different packet types may require different application sets for their processing. We refer to these application sets as *flows*. Certain applications could be common across application sets so that there may be shared tasks between flows. There may also be more than one pipeline available for allocation, so that an effective assignment of flows to pipelines would also need to be done.

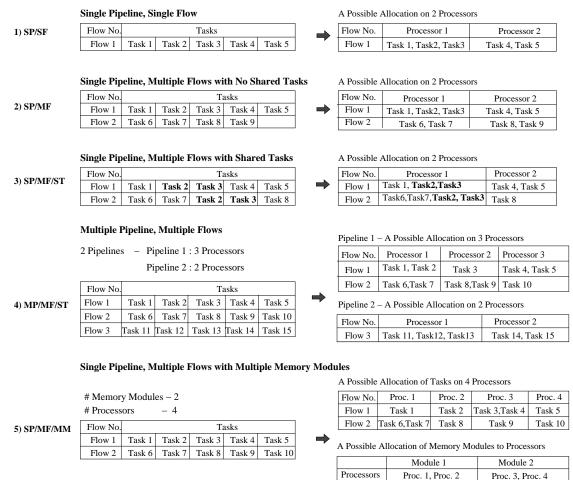

Considering all these factors, we can categorize the scheduling problem in order of increasing complexity as follows. Figure 1.2 illustrates the different scheduling problem types and provides sample task allocations.

- Single Pipeline, Single Flow (SP/SF) Tasks in a single flow are allocated to a single pipeline of processors.

- Single Pipeline, Multiple Flow (SP/MF) Tasks of multiple flows need to be allocated to a single pipeline of processors.

- Single Pipeline, Multiple Flow, Shared Tasks (SP/MF/ST) This is like SP/MF except that there may be shared tasks between the flows.

- 4. Multiple Pipelines, Multiple Flows (MP/MF) More than one pipeline may be available so that while tasks need to be optimally allocated to processors,

Figure 1.2: NP Task Scheduling Problem Examples

flows also need to be effectively mapped to pipelines. A given flow must be implemented entirely within a single pipeline.

5. Single Pipeline, Multiple Flows, Multiple Memory Modules(SP/MF/MM) - While there may be multiple modules of internal memory available, they may need to be shared between processors. This kind of sharing of resources could lead to contention for resources (memory in this case) and affect the performance. The task allocation in this case should be made with consideration to the memory resource contention. Extensions to this problem class include MP/MF/MM and MP/MF/ST/MM.

The line rates that can be supported by the system depend on the pipeline(s) throughput which, in turn, depends on a number of factors including just how application subtasks are assigned to the PEs. In our research, we mainly focus on maximizing the system throughput by effective allocation of tasks to processors. Three different approaches are used towards solving the task scheduling problem; a heuristic approach, dynamic programming and a statistical approach using *Simulated Annealing*. The subsequent chapters describe these approaches and the limitations of each one of them when applying them to the above described classes of problems.

Additionally, we also evaluate the usability of a tool, based on the above mentioned approaches, for designing Network Processors given that there is *a priori* knowledge of the flow types that will be serviced, the performance requirements, and the costs associated with implementation (e.g., chip area). In architectures where there are a limited number of on-chip RAM modules, assignment of these modules to one or more PEs affects performance. Other design issues relate to determining the number of stages a pipeline must have. While this is clearly related to the line rates one would like to achieve, and the complexity of the applications, there are a number of design options available, each of which requires that a good assignment of application tasks to pipeline stages be obtained. Another example is determining whether algorithmic efforts at changing the number of tasks or task durations associated with an application might help in improving system throughput. We demonstrate the effect of various elements of NP design on the performance of an NP by a range of experiments conducted using the scheduling tool-set developed as part of this thesis.

### 1.3 Related Work

There is a long history associated with related problems in deterministic job-shop scheduling [22] and these problems have been investigated from a variety of perspectives including integer programming, heuristics, and other approaches. Similar problems have also been dealt with in the context of finding compilation techniques for general purpose parallel languages on multiprocessors [39, 35]. The primary objective of the compilation techniques is to minimize the response time while simultaneously reducing overhead due to inter-process synchronization and communication over a general parallel processor. Multiprocessor performance in these cases is maximized by identifying potential parallelism and then partitioning the program accordingly to exploit the parallelism.

Scheduling of jobs to processors so that a given cost function is minimized is an important problem in many areas of computer science. In parallel computing, with no special constraints on the jobs or the processors, minimizing the total completion time has been proved to be NP-Hard [14], even for two processors. Thus a number of restricted versions of the scheduling problem have been investigated in order to make it tractable. One such class of problems, referred to as Structured Data Partitioning problems or MinMax problems, impose an implicit order on a sequence of n elements. The objective is to partition the elements into a sequence of p intervals such that the maximal value of the cost function, of each interval is minimized (hence the name MinMax). The first reference to the MinMax problem was made by A.Bokhari for single dimensional partitioning problems in parallel, pipelined and distributed computing in [36] where he presented an  $O(n^3p)$  algorithm using a bottleneck-path algorithm. Anily and Federgruen [33] and Hansen and Lih [18] independently presented the same dynamic programming algorithm reducing the time complexity of the solution to  $O(n^2p)$ . Manne and Sorevik then presented, in [26], an  $O(p(n-p)\log p)$  algorithm based on iteratively improving a given partition. They also described a bisection method for finding an approximate solution which runs in time  $O(n \log(f(0, n - 1/e)))$ , where e is the desired precision. Further improvements to the iterative approach were suggested by Pinar and Aykanat in [31]. They use improved algorithm initialization methods. Olstad and Manne studied the problem in the context of issues related to load balancing when performing sparse matrix computations on parallel computers. They refined the dynamic programming approach to a complexity of O(p(n-p)) and applied it for partitioning of acyclic graphs too.

There exists a rich literature on scheduling of tasks to processors and an overview of it can be found in [16]. The MinMax problem can be generalized to dimensions higher than one however, all the cited solutions are pertinent to single dimensional partitioning problems.

Real-time packet scheduling problems have also been considered in the context of network processors [43]. In this case, however, packets were assumed to be completely processed on a single processor. A primary concern in that work was to assign packets to processors in a manner that minimized the effect of cold cache misses on performance.

Our work aims at maximizing the throughput of a pipelined CMP by effective assignment of flow tasks to pipeline stages. It differs from the prior work cited in a number of ways. Primarily, the problem definition differs from those considered in the past in that we consider multiple flows and pipelines, sharing of tasks on pipeline stages, sharing of resources (e.g., memory) between stages and employing a bandwidth performance metric associated with the requirements of the computer pipeline environment. Thus, while limited problem classes (e.g., 1 - SP/SF) can be solved using some of the existing techniques, the more complex classes noted above have required consideration of new approaches.

### 1.4 Thesis Outline

Chapter 2 presents a model for the assignment of application tasks and memory modules to pipeline stages. Given this formulation, Chapter 3, 4 and 5 indicate how heuristics, dynamic programming and a statistical optimization method (*Simulated Annealing*) can be used to obtain the optimal task and memory assignment. Chapter 6 then illustrates the use of this capability first in a set of synthetic problems, and then by applying it to a specific NP problem where the applications include routing, compression and encryption. Chapter 7 compares the three algorithmic approaches for the task scheduling problem and concludes with a summary and a discussion of future work.

# Chapter 2

# **Pipeline Task Scheduling Problem**

### 2.1 Problem Formulation

In this chapter, we give a formal definition of the task scheduling problem and lay down the constraints associated with it. We also describe a resource (memory in this case) contention model and use it to formulate the performance metrics for the scheduling problem. Network processors (NPs) typically have multiple input flows where, for our research, we define a flow as a set of successive functions that must be performed on packets belonging to the flow<sup>1</sup>. For example, one flow may require that incoming packets be compressed (say using Lempel Ziv) and then routed using a specific LPM (Longest Prefix Match) algorithm. Another flow might require packet encryption, transcoding and then routing. We consider here application algorithms that may be pipelined and are implemented on a pipeline of identical processors. The general issue of how to develop a pipelined algorithm for a given application is not considered here except for the special cases of Longest Prefix Match (LPM), encryption (AES) and compression (LZW) that are discussed in Chapter 7. Each processor in the pipeline operates on a packet, does some partial processing associated with the application, and then passes the packet (generally modified) along with other

$<sup>^1{\</sup>rm Flows}$  correspond to a sequence of functions rather than packets associated with source-destination pairs.

information to the next processor in the pipeline<sup>2</sup>. After passing through the pipeline, the packet is sent into a switch and from there into the network. We assume that there is a steady stream of packets arriving.

Each packet belongs to one flow and flows are represented by the set F:

$$F = \{F_1, F_2, F_3, \dots, F_N\}$$

The processing associated with flow applications can be partitioned into an ordered set of tasks,  $Tasks_j$ . Each task in  $Tasks_j$  is represented by  $T_{ij}$ , where i  $(1 \le i \le M_j)$ , and j  $(1 \le j \le N)$  respectively designate the task and flow number. Thus  $Tasks_j$  is the set of tasks associated with flow j and  $M_j$  is the total number of tasks for flow jgiven by:

$$Tasks_j = \{T_{1j}, T_{2j}, T_{3j}, \dots, T_{M_ij}\}$$

Corresponding to the tasks are task times (i.e., the time for executing the tasks on a given pipeline stage),  $t_{ij}$ . For flow j, the set of task execution times is:

$$TaskTimes_{j} = \{t_{1j}, t_{2j}, \dots, t_{M_{j}j}\}$$

These times will be obtained experimentally using a processor simulator under zero cache miss conditions. This permits us to separate out the effects of memory architecture from the pure computational requirements of the applications. To take application/task memory usage into account, each task has associated with it the number of memory accesses that occur during its execution,  $m_{ij}$ . Each PE in an NP is assumed to have local instruction memory and the memory accesses are primarily required for data accesses. the memory accesses will also be obtained through simulations. Thus, for flow j:

$$MEM_j = \{m_{1j}, m_{2j}, \dots, m_{M_jj}\}.$$

The resources associated with the NP consist of PEs that may be arranged in a pipeline manner (K identical processor stages for a single pipeline) and memory modules (Q modules) with  $Q \leq K$ . Thus, the set of PEs, P, and memory modules,

$<sup>\</sup>frac{M}{2}$  are given by . Note that there is generally an overhead associated with moving data between successive stages. This can be easily dealt within the framework provided. However, for a constant overhead between stages, this typically affects the pipeline latency but not throughput and thus does not impact task scheduling

$$P = \{P_1, P_2, P_3, \dots, P_K\}$$

$$M = \{M_1, M_2, M_3, \dots, M_Q\}$$

The memory modules may be on-chip or off-chip and may be shared between the PEs. The K PEs can also arranged into multiple pipelines. A two pipeline case would be represented as :

$$Pipeline^{1} = \{P_{1}, P_{2}, P_{3}, \dots, P_{l}\}$$

$$Pipeline^{2} = \{P_{l+1}, P_{l+2}, P_{l+3}, \dots, P_{K}\}$$

Initially we present a less complex model, where memory delays are not a significant factor and may be ignored in the task assignment process. Later when memory issues are considered, the association of a processor k with a memory block m is represented by the variable  $A_{km}$ .  $A_{km} = 1$  indicates that the processor k has access to the memory block m, while  $A_{km} = 0$  indicates otherwise. If Q < K, then multiple processors access the same memory block, leading to contention amongst the processors for memory access. This may have a significant effect on system performance and is considered later in the discussion of performance metrics.

### 2.2 Assignment Constraints

The task assignment problem consists of mapping the full set of tasks onto the stages of a pipeline in a manner that preserves task ordering within a flow and optimizes a given performance metric. The assignment of task *i* from flow *j* to processor stage *k* can be expressed using the binary variable  $X_{ijk}$  where  $X_{ijk} = 1$  if the task is assigned to the processor, and  $X_{ijk} = 0$  otherwise. Thus, the number of tasks on a processor *k* is given by:

$$P_{num.k} = \sum_{j=1}^{N} \sum_{i=1}^{M_j} X_{ijk}$$

(2.1)

Additionally, the following three constraints apply:

• The assignment process must maintain sequential task ordering. Thus, for  $l, 1 \le l \le M_j$ , for all i, j, k, r if  $X_{ijk} = 1$  and  $X_{(i+l)jr} = 1$  then  $k \le r$ .

- A task may only be assigned to a single processor. Thus for a given task *i* from flow j,  $\sum_{k=1}^{R} X_{ijk} = 1$ .

- An additional constraint is applied in situations where the same task is associated with multiple flows. Designating tasks to be shared across flows implies that there will be a single instantiation of the shared task and it will be assigned to a single pipeline stage. Thus, for the case of two flows, *j*, *s*, and two tasks, *i*, *r*, that are the same and are to share the same stage (and code):

if

$$T_{ij} = T_{rs}$$

and  $X_{ijk} = 1$  and  $X_{rsm} = 1$  then  $k = m$

This can be extended naturally to more than two flows. If it is not desired to have such sharing even though the tasks are the same, this can be dealt with by giving the tasks different names.

The third constraint helps in conserving code space and instruction cache misses since the application code does not get duplicated. Additionally, in designs employing caches, it can help to reduce cache misses. However this constrains how tasks can be assigned and thus, in certain cases may lead to a loss in performance. The general problem considered therefore is just how to assign the tasks from each flow to the pipeline(s) stages, in a manner that satisfies the above constraints while maximizing an appropriate performance metric. Performance metrics are considered in Section 2.4. The next section presents a model for memory contention in the task scheduling problem.

### 2.3 Memory Contention Model

The assignment of memory modules to pipeline stages may strongly impact system performance. Since each of the pipeline stages that accesses a shared module may encounter a delay due to contention, any task and memory module assignment must include a method for evaluating these contention delays. If, ideally, a very fast simulation of the entire NP along with the flows and associated applications were available, then successive simulation runs could provide performance information from which the best assignment could be derived. This, however, is not practical since such simulations take a long time, and to find the best assignments requires a large number of simulation executions.

| Flow Tasks             | $T_1$            | $T_2$                    | $T_3$            |

|------------------------|------------------|--------------------------|------------------|

| <i>Flow</i> Task Times | $t_1$            | $t_2$                    | $t_3$            |

| Flow Memory Accesses   | $w_{11}, w_{12}$ | $w_{21}, w_{22}, w_{23}$ | $w_{31}$         |

| Pipeline               | $P_1$            | $P_2$                    | $\overline{P_3}$ |

Table 2.1: A Single Flow, Single Shared Memory Example

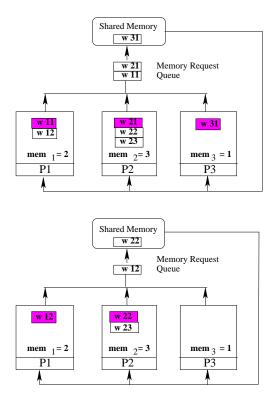

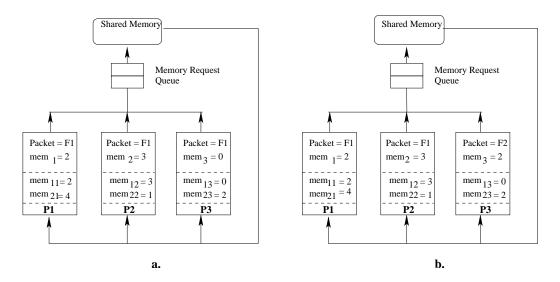

In our research, we adopt a *worst case* memory contention model. This permits simple evaluation of memory contention delays without having to resort to a full NP simulation. It also corresponds to the general requirement that networking components must meet line rates under worst case conditions and, since processors and memory accesses across pipeline stages are not synchronized in time, such worst case conditions may occur. We are concerned here principally with data memory accesses, and assume that sufficient local instruction memory is present on each processor stage so that contention delays are not encountered when accessing instructions. The technique employed may be best explained by use of a simple example where a single memory module is being considered. Assume that the memory module is shared by three processors in a single pipeline and single flow  $F_1$  is present consisting of three consecutive tasks  $T_1$ ,  $T_2$  and  $T_3$ . The tasks are assigned to the processors  $P_1$ ,  $P_2$  and  $P_3$  in the three-stage pipeline. Associated with each task is a set of successive memory accesses that are designated by  $w_{ij}$  where i is the task number and j is the memory access number. Thus,  $w_{12}$  is the second memory access for task 1. These are shown for this system in Table 2.1.

Figure 2.1 shows two possible rounds of data memory accesses for the processors and depicts a worst case scenario for the memory accesses made by  $P_1$ . In the first round, while the memory request by  $P_3$  ( $w_{31}$ ) is being processed the other two processors ( $P_2$  and  $P_1$ ) also make their first memory requests ( $w_{21}$  and  $w_{11}$ ) and these

# Total Contending Memory Accesses from P2 = 1 + 1 = 2

# Total Contending Memory Accesses from P3 = 1 + 0 = 1

# Total Contending Memory Accesses for P1 = # Contending Memory Accesses from (P2 + P 3) = 2 + 1 = 3

Figure 2.1: Memory Contention Example

requests must now wait. So, while  $w_{31}$  is being serviced, requests  $w_{21}$  and  $w_{11}$  get queued up and serviced in a FIFO fashion. In this situation  $w_{11}$  must wait until the two requests  $(w_{31}, w_{21})$  before it are completed, and only after that is  $w_{11}$  processed. Similarly, if there were different orderings of requests ,  $P_2$ 's and  $P_3$ 's requests might also encounter such delays. Given the number of memory requests associated with each task and a given task to stage assignment, the worst case memory delay for a stage can be evaluated. Once this worst case delay is known, the worst case task execution time, W, can be evaluated in terms of two components, the task execution time without data memory delays and the worst case memory waiting time. Thus:

- # Memory Accesses delays for P1 : w11 = 2; (w21 and w31)

- # Contending Memory Accesses from P2 = 1; (w21)

- # Contending Memory Accesses from P3 = 1; (w31)

- # Memory Accesses before P1 : w12 = 1; (w22)

- # Contending Memory Accesses from P2 = 1; (w22)

- # Contending Memory Accesses from P3 = 0

$$W = Task Execution time + Memory Waiting Time$$

(2.2)

We assume that after a memory request has been made, a single threaded processor must stall until the request is satisfied. Therefore, there cannot be more than one pending request from a processor. Thus, the maximum number of memory requests at any point in time will be equal to the number of processors (given that each processor has a memory request) accessing the memory block.

While the example above has a single memory module, in general there may be multiple modules available and part of the assignment task is to assign memory modules to processor stages. Following the example above, for a given memory block m, the maximum memory contention/waiting time for any processor is equal to  $(R_m - m_m)$ 1)  $\times$  t<sub>mem</sub> where  $R_m$  is the number of processors assigned to the memory block m and  $t_{mem}$  is the time required to process a single memory request with no contention. Since in the considered example there is only a single memory module shared between processors, we can drop the subscript m for this case. In this case all the processors are contending, but contention is generally less than  $(R_m - 1) \times t_{mem}$  since the number of memory requests associated with each stage is different and, after a few requests have been satisfied, some processors will not have any requests remaining while others may. This is illustrated by a possible second round of memory accesses shown in Figure 2.1. The number of memory requests required by the processors is represented by  $mem_1$ ,  $mem_2$  and  $mem_3$ . In the first round of memory requests, the waiting time for  $w_{11}$  is  $(R-1) \times t_{mem}$  with R = 3, since all the three processors have made a memory request (the worst case). However, in the second round of memory accesses, again assuming a worst case so that all the processors make memory requests together, since processor  $P_3$  does not have any more memory accesses, the memory request by processor  $P_1(w_{12})$  faces contention only due to the memory request by processor  $P_2$  ( $w_{21}$ ). Note that, after the second round,  $P_1$  is finished with all it's memory requests and thus, does not face any more contention from the remaining memory requests  $(w_{23})$ .

Total\_Rounds = mem k round = 1 while (round < Total Rounds)

#### Begin

$Max\_Contention\_For\_Round = R$ for ( j = 1 to R )

Begin

if (mem<sub>j</sub> == 0) AND ( j != k)

Max\\_Contention\\_For\\_Round = Max\\_Contention\\_For\\_Round - 1

else

mem<sub>j</sub> = mem<sub>j</sub> - 1

End

Total\\_Contention = Total\\_Contention + Max\\_Contention\\_For\\_Round

round = round + 1

End

Total\\_Waiting\\_Time = Total\\_Contention \* t\_{mem}

Figure 2.2: Worst Case Memory Contention Computation

Thus, given the number of memory requests associated with each task and the task to stage assignment, the memory contention can be computed using the algorithm shown in Figure 2.2. In the figure,  $mem_k$  refers to the memory accesses required by processor k. As shown, the total number of rounds (*Total\_Rounds*) of memory access is equal to the number of memory accesses for the processor, k, for which the maximum contention needs to be obtained. At each round the number of contending requests (*Maximum\_Contention\_For\_Round*) is initialized to R (the total number of processors) assuming that all the processors need to make memory requests. Subsequently, the number of remaining memory requests for each processor is checked and if a processor has completed all it's memory requests, *Maximum\_Contention\_For\_Round* is reduced by one since that processor does not contend for memory any more. After each round, the number of memory requests required by each processor. The *Maximum\_Contention\_For\_Round* for all the rounds is added up to obtain the total waiting time for a processor to complete all it's memory requests.

The expression to calculate the worst case memory delay for each processor, for the above described memory contention model is presented in Appendix A.

### 2.4 Performance Metrics

Given the formation above, to determine an optimal assignment it is necessary to specify a performance metric. The metric of interest in the NP environment generally relates to maximizing pipeline throughput (i.e., the number of packets processed per second).

Consider the case where there are one or more flows, flows that may share tasks, and (for simplicity) a single pipeline. Assume that pipeline throughput is limited by the maximum stage execution time taken over all stages in the pipeline. The execution time for a stage is determined by the tasks assigned to each stage and the memory modules assigned to each processor. Thus, the execution time for a single flow j, on a given stage k is given by:

$$s_{jk} = \sum_{i=1}^{M_j} X_{ijk} t_{ij} + (c_{jk} * t_{mem})$$

(2.3)

where  $(c_{jk} * t_{mem})$  is the additional time required due to contention for memory.  $c_{jk}$ as described in the previous section, represents the number of contending memory accesses for tasks of flow j that are assigned to stage k and  $t_{mem}$  is the time required to process a single memory request without contention. The worst case value of  $c_{jk}$  can be determined as described in the previous section. The maximum stage execution time for flow j across all the R stages is:

$$P_{j} = \max_{k=1}^{R} [s_{jk}] = \max_{k=1}^{R} \left\{ \sum_{i=1}^{M_{j}} X_{ijk} t_{ij} + (c_{jk} * t_{mem}) \right\}$$

(2.4)

The maximum stage execution time over all flows and stages is given by:

$$P = \max_{j=1}^{N} P_j = \max_{j=1}^{N} \left\{ \max_{k=1}^{R} \left\{ \sum_{i=1}^{M_j} X_{ijk} t_{ij} + (c_{jk} * t_{mem}) \right\} \right\}$$

(2.5)

To maximize packet throughput, the problem becomes one of finding a task and memory assignment that minimizes P since packet throughput  $\approx 1/P$ .

### 2.5 Complete Enumeration Method

A straight forward method of finding the task and memory assignment that minimizes P is to perform a complete enumeration of all possible assignments, identify feasible assignments (i.e., those that satisfy the constraints discussed above), and select the optimum one. Since the multi-processor pipelines are supposed to be programmed offline, this method may not seem very expensive. However, even restricted versions of this problem have been proven to be NP Hard [22] and for a complex configuration of flows, stages and tasks per flow, it could take years to compute the optimal assignment, using the complete enumeration method. However, the complete enumeration method was implemented and used in evaluation of the other approaches for limited cases when the problem size was small.

Consider first the complexity associated with performing only task assignments for the single flow case where there are M tasks present and R identical pipeline stages. An upper bound on the number of combinations that must be examined for each flow, corresponds to the standard problem of calculating the number of ways of placing M identical balls into (M + R - 1) bins and is given by :

Number of Assignments For Each Flow

$$\leq \begin{pmatrix} M_j + R - 1 \\ M_j \end{pmatrix}$$

(2.6)

With N flows present each flow having  $M_j$  tasks, the number of combinations increases by the product of combinations possible with each flow. Thus:

Number of Assignments

$$\leq \prod_{j=1}^{N} \binom{M_j + R - 1}{M_j}$$

(2.7)

Accordingly, assuming that the complexity of obtaining each assignment is O(1), the time complexity of enumerating all the task assignments will be approximately  $O((\frac{(M+R)!}{M!R!})^N)$ . However if the flows are independent with no shared tasks and a separate memory module for each processor stage, the combinations for each flow can be enumerated independently and the complexity in that case will be given by  $O((\frac{(M+R)!}{M!R!})N)$ . Equation 2.7 results in the worst case count of combinations. This will decrease (sometimes significantly) when there are more tasks common between the flows (i.e., shared), however, even with this reduction, the factorial and product components may result in the complete enumeration approach being infeasible for analyzing practical systems. The complexity increases further if the memory modules are shared between stages. With shared memory modules, the contention for each of the R stages needs to be computed. The complexity for computation of contention for each stage will depend on the memory module sharing. Thus, considering a worst case scenario such that a single memory module is shared between all the R stages, from Equation A.3 (Appendix A), each memory contention computation for a processor requires a comparison of memory accesses with all the other R-1 processors. Given that, the complexity for memory contention for all the R stages is approximately  $O(R^2)$ . Thus, the complexity of enumerating all the task assignments with memory contention calculation with a single memory module shared between all the R processors is given by  $O((\frac{(M+R)!}{M!R!})^N \times (R^2))$ .

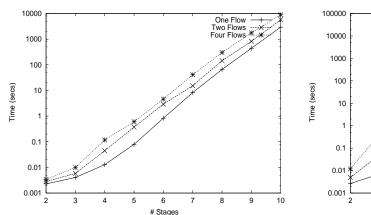

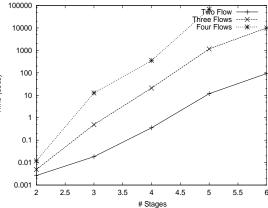

Figure 2.3: Variation in execution time for flows with no shared tasks

Figure 2.4: Variation in execution time for flows with shared tasks

Figures 2.3 and 2.4 illustrate the effect on the execution time of the complete enumeration method when the number of stages in a pipelined processor system is varied. Each datapoint represents an average of 10 experiments. The number of tasks in each flow is equal to twice the number of stages for each experiment. Figure 2.3 shows experiments for systems with independent flows (no shared tasks) while Figure 2.4 shows experiments for flows with shared tasks. With the increase in number of flows in the system, for systems with independent flows, there is a linear increase in execution time whereas for systems with shared tasks the increase in execution time is almost exponential. The figure with shared tasks shows limited experiments due to very high execution times for systems with more than 4 stages.

This chapter provided a formal definition of the task scheduling problem and the constraints associated with it. Additionally, it also presented a memory contention model for the class of problems with limited or shared resources (memory in this case). This model was subsequently used to present the performance metric for the task scheduling problem. Chapters 3, 4, and 5 introduce three different approaches to allocate tasks to processors and use the described metric to demonstrate the effectiveness of the approaches under the given constraints.

# Chapter 3

# Greedypipe - A Heuristic

*Greedypipe* is a heuristic based, in part, on a greedy algorithm. It gives no guarantee of finding an optimal solution, however, it provides solutions quickly and tests indicate that it finds a near optimal solution most of the time. Note also that the algorithm was developed for solving the cases of multiple flows with shared tasks, but does not directly extend to the shared memory environment. Section 3.1 describes the *Greedypipe* algorithm and uses an example to further illustrate the application of the algorithm. Section 3.2 discusses the complexity of *Greedypipe* and Section 3.3 the algorithm's performance.

## 3.1 Greedypipe Algorithm

Ideally, one would like an assignment where, for each flow, the total execution times of flow tasks associated with each stage are equal. Using the notation introduced in Chapter 2, the total time for executing the tasks associated with flow j is given by:

$$TotalTime_j = \sum_{i=1}^{M_j} t_{ij} \tag{3.1}$$

With R stages in the pipeline, as indicated, an optimal allocation of tasks to pipeline stages is one where the execution time for each stage is equal. Under these conditions, the ideal delay per stage for flow j is :

$$Ideal.Delay.per.Stage_i = TotalTime_i/R$$

(3.2)

and the resulting maximized throughput is :

$$Packet.Throughput_j = 1/Ideal.Delay.per.Stage_j$$

(3.3)

Thus, Step 1 of the GreedyPipe is to calculate this ideal delay (Equation 3.2). Actual task times and assignments that satisfy the constraints noted in Chapter 1 will however generally result in unequal execution times associated at each stage. The best of the possible assignments, however, will be the one(s) that come closest to that ideal.

Consider the time for execution of all flow j tasks on stage k as given by:

$$t_{jk} = \sum_{i=1}^{M_j} X_{ijk} t_{ij}$$

(3.4)

Since, throughput is calculated from the inverse of the maximum stage execution time, the optimum assignment for flow j is one that minimizes the value of  $Var_j$  in the expression given by Equation 3.5.

$$Var_j = \max_{k=1}^{R} \{ |[t_{jk}] - Ideal.Delay.per.Stage_j| \}$$

(3.5)

When multiple flows are present there are potentially shared tasks that complicates task assignment. However, various assignments will meet the above constraints and selecting the optimal now requires Equation 3.5 to be expanded so that the throughput across all the flows is maximized. This can be achieved by selecting the task to stage assignment that minimizes the maximum  $Var_j$  across all flows:

$$Var = \max_{j=1}^{N} Var_j = \max_{j=1}^{N} \left\{ \max_{k=1}^{R} \left\{ |[t_{jk}] - Ideal.Delay.per.Stage_j| \right\} \right\}$$

(3.6)

This metric attempts to equalize both the distribution of tasks to stages on a per flow basis and also on an aggregate flow basis. Note that, at a given stage m, potentially there may be multiple allocations for which the minimized Var has the same value. A simple tie breaking algorithm is used that selects the assignment, over all flows, that minimizes the sum, S (Equation 3.7), of the differences between the ideal delays and the assigned delays.

$$S = \sum_{j=1}^{N} \left( \left| [t_{jm}] - Ideal.Delay.per.Stage_j \right| \right)$$

(3.7)

#### 3.1.1 Greedypipe: Overall Algorithm

The overall heuristic begins by calculating the *Ideal.Delay.per.Stage* for each of the flows (*Step 1*). Task to stage allocations start with the first processor stage. Two sets of tasks, satisfying the constraints, are selected from each of the flows for allocation to this processor (*Step 2*). The first set is chosen so that the variation,  $Var_j$ , given by Equation 3.5 is minimized and is also a positive number. The second set is chosen similarly, however,  $Var_j$  is required to be a negative number. Thus the ideal delay value is bracketed. Additional sets that satisfy the constraints may be chosen at the cost of increased complexity and execution time. At this point, there are two allocations associated with each flow for the first processor and thus there are thus  $(2)^N$  possible combinations of flow allocations. Each of these combinations is examined and the "best" two are kept for use in performing task assignments for the next pipeline stage(*Step 3*). The best two correspond to the two that, for this stage, minimize Var as expressed in Equation 3.6 with R = 1.

Assignments for the next pipeline stage are now considered. The process begins by first calculating new *Ideal.delay.per.stage* values based on *unallocated* tasks and the number of remaining pipeline stages. Next, each of the two best allocations from the prior stage is used as a starting point for determining the best task-to-stage assignments for the current stage. For each of these and for each flow, two "best" assignments (positive and negative) are selected. As before, all combinations of these flow assignments are then examined and the two that minimize *Var* (Equation 3.6) with R = 2 are now kept as starting points for considering the next pipeline stage (Stage 3). This process continues until all stages in the pipeline are examined and a complete assignment has been done. The best of the final stage two assignments is now kept.

Notice that the algorithm has an implicit ordering aspect to it such that tasks and stages are considered in their first-to-last order. While in general this does well, given that local conditions determine allocations at each stage, it will not always result in the optimal allocation. To improve the results one can apply the same heuristic, however, start from the last task and stage, and apply the heuristic in a last-to-first order. Thus, in *GreedyPipe* the algorithm is applied in both directions with the final assignment being the best of the two.

#### 3.1.2 A Simple Example

To illustrate operation of the *GreedyPipe* we present a simple single flow example that has five tasks and a three stage pipeline. The task times are given in Table 4.1.

|                      | Task 1 | Task 2 | Task 3 | Task 4 | Task 5 |

|----------------------|--------|--------|--------|--------|--------|

| Flow 1               | $T_1$  | $T_2$  | $T_3$  | $T_4$  | $T_5$  |

| Task Execution Times | 2      | 5      | 3      | 1      | 3      |

Table 3.1: A Single Flows with five *ordered* tasks

Begin by calculating the *Ideal.Delay.per.Stage* as 4.66 (e.g., (2+5+3+1+3)/3 = 4.66). Next consider allocations to stage 1 and calculate  $Var_1$ . This is shown in complete form in Table 3.2 although clearly not all calculations need be done.

| Stage 1                   | $Var_1$                                      | Best       |

|---------------------------|----------------------------------------------|------------|

| Allocation                |                                              | Selections |

| $T_1$                     | $Var_1 = 4.66 - 2 = 2.66$                    | +          |

| $T_1, T_2$                | $Var_1 = 4.66 - (2+4) = -1.34$               | —          |

| $T_1, T_2, T_3$           | $Var_1 = 4.66 - (2 + 4 + 3) = -4.34$         |            |

| $T_1, T_2, T_3, T_4$      | $Var_1 = 4.66 - (2 + 4 + 3 + 1) = -5.34$     |            |

| $T_1, T_2, T_3, T_4, T_5$ | $Var_1 = 4.66 - (2 + 4 + 3 + 1 + 3) = -8.34$ |            |

Table 3.2: All possible allocations for Stage 1

The best positive selection corresponds to a stage 1 assignment of  $T_1$ , while the best negative selection corresponds to  $T_1, T_2$ . Starting with these selections, stage 2 assignments are now considered. Two new *Ideal.Delay.per.Stage* values are now calculated based on stage selections 1 and 2 above. They are:

$$Ideal.Delay.per.Stage_1 = [(5+3+1+3)/2] = 6.0$$

and

$$Ideal.Delay.per.Stage_2 = [(3+1+3)/2] = 3.5$$

A new set of possible allocations is now calculated. Table 3.3 shows the four assignments associated (Equation 3.5) with the starting allocations of stage 1. From these four, the two best are selected for consideration (noted with a \*). The heuristic then breaks the 2.3 tie by employing the tie breaking algorithm. From Equation 3.7, since 1.0 < 2.0, the second entry in the table is selected. Since *GreedyPipe* retains two choices at each stage, the lower two choices are now examined. They are tied both in terms of the Max calculation (1.7) and the use of tie breaker. Thus, for this situation one of them is arbitrarily selected.

| Stage 2 Allocation |                |                              |                      |            |  |  |  |

|--------------------|----------------|------------------------------|----------------------|------------|--|--|--|

| Stage 1            | Stage 2        | $Var_2$                      | Max                  | Best       |  |  |  |

|                    |                |                              | $[ Var_1 ,  Var_2 ]$ | Selections |  |  |  |

| $T_1$              | $T_2$          | $Var_2 = 6.0 - 4 = 2.0$      | 2.3                  |            |  |  |  |

| $T_1$              | $T_{2}, T_{3}$ | $Var_2 = 6.0 - (4+3) = -1.0$ | 2.3                  | *          |  |  |  |

| $T_{1}, T_{2}$     | $T_3$          | $Var_2 = 3.5 - 3 = 0.5$      | 1.7                  |            |  |  |  |

| $T_{1}, T_{2}$     | $T_{3}, T_{4}$ | $Var_2 = 3.5 - (3+1) = -0.5$ | 1.7                  | *          |  |  |  |

Table 3.3: Best allocations for Stage 2

The two stage 2 allocation choices are now the starting point for examining the possible assignments for stage 3 as shown in Table 3.4. Since this is the last stage, all the remaining assignments are dictated by prior stage assignments. For this example, as Table 3.4 indicates, there are two best assignments. The same process is now repeated starting from stage 3 and task 5 and working in the reverse direction. For this case, the best assignments are the same as obtained in the forward direction. Additionally, the maximum stage delay (7) for these is also the same as obtained when using a complete enumeration approach to find the optimal. Thus, in this example the heuristic yielded the optimal assignment.

| Stage 3 Allocation |                    |                        |                 |

|--------------------|--------------------|------------------------|-----------------|

| Stage 1            | Stage 2            | Stage 3                | Max. Stage Time |

| $T_1,  T=2$        | $T_2,  T=5$        | $T_3, T_4, T_5, T = 7$ | 7               |

| $T_1, T_2,  T = 7$ | $T_3, T_4,  T = 4$ | $T_5, \qquad T=3$      | 7 *             |

Table 3.4: Best allocations, forward direction

## 3.2 Complexity of *Greedypipe*

We now determine the time complexity of the *Greedypipe* algorithm. Since the algorithm execution varies depending on whether there are shared tasks between flows, we will find the complexity for two cases:

- Multiple flows with no shared tasks.

- Multiple flows with shared tasks.

#### 3.2.1 Multiple Flows with no shared tasks

In this case, since there is no dependency between flows, each flow can be handled independently. We have seen that *Greedypipe* progresses from the first stage to the last stage and then for better results does a reverse traversal. The operations at each stage are almost the same. Thus, with no dependency between the flows, the allocation can be done for one flow at a time. Since the operations at each stage are almost the same, we will find the complexity for a single stage execution and extend it to include multiple stages and flows. At each stage, except for the first stage, there are two initial starting points and for each one, selections are made in accordance with Equations 3.5 and 3.6. The complexity of these operations per stage is roughly O(1). Now, since the same operation needs to be done for all the stages and flows, the complexity for a complete execution of the algorithm would be given by O(NR), where N is the number of flows and R is the number of stages.

#### 3.2.2 Multiple Flows with shared tasks

The flows in this case cannot be treated independently since the shared tasks need to be allocated to the same stage (third constraint). However, the operations at each stage are almost the same. At each stage, again there are two initial starting points depending on the previous stage allocations. After making the selections using Equation 3.5, each selection is combined with the selections of the other flows which leads to  $2^N$  combinations for N flows, and the "best" two of these combinations are selected. Thus, the complexity of each stage operation would be  $O(2^N)$  and the complexity of execution over all the stages will be  $O(2^N R)$ .

The space complexity for both the cases is of the same order as their time complexity. A performance comparison in terms of complexity, for all the algorithm approaches discussed in this thesis will be done in Chapter 7.

# 3.3 GreedyPipe Performance

Figure 3.1: % Error vs % Cases with Error

There are two elements associated with evaluating GreedyPipe performance. The first concerns how closely GreedyPipe results match the true optimal results. While no analytic bounds on the errors have been developed, extensive experimentation has been performed where the results of GreedyPipe were compared with the true optimal as obtained by running the time consuming complete enumeration method explained in Chapter 2. For each experiment, the task times were randomly selected from a uniform distribution ranging from 0 to 10 time units. Figure 3.1 shows the results for a system with 3 flows and 10 tasks per flow with no sharing between the tasks. The pipeline consisted of 5 stages and the task to stage assignment was done using *Greedypipe*. A total of 500 experiments were conducted on the described system where, as mentioned before, the task times for each experiment were generated randomly. The figure shows that the error is never more than 15% of the optimal and that less than 1% of results produced by *Greedypipe* were non-optimal.

Figure 3.2: % Error vs Number of Stages

Figure 3.2 shows the effect of increase in number of stages on the performance of a system. The system consisted of 3 flows and the number of tasks in each flow was equal to three times the number of stages with no shared tasks between the flows. The number of stages was varied from 2 to 10 and 50 experiments were conducted for each configuration. The results show that the number of non-optimal cases increases with the increase in the number of stages. Almost all experiments result in an error less than or equal to 15% of the optimal. With more stages, the heuristic selection at the earlier stages gets propagated to longer pipeline depths and thus the probability of it leading to an overall optimal solution is reduced.

Figure 3.3: % Error vs % Sharing

Figure 3.3 shows another set of experiments on a system with 3 flows and 9 tasks in each flow with tasks shared between the flows. The percentage sharing of tasks between flows was varied from 10% to 90% and the tasks were assigned to a 3 stage pipeline using *Greedypipe*. The results were averaged over 50 experiments for each configuration. The figure shows that up to a point, the percentage of cases with error increase with the increase in sharing of tasks. With tasks shared between flows, the flows cannot be treated independently and at each stage results for each flow are combined with that of other flows to select a probable allocation for that stage. This leads to more number of choices available at each stage and thus the probability of the selection at a stage leading to an overall optimal allocation reduces. Beyond 60% sharing, the percentage of cases with error decreases with sharing since with extensive sharing, there are very few valid allocations possible.

Overall, over a wide range of randomly generated conditions, 98% of the time GreedyPipe results are within 15% of the optimal and in no case was the GreedyPipe result greater than 25% from the optimal. The results however varied with the number

of stages in the pipeline and the percentage of shared tasks associated with different flows.

The experiments were conducted for systems containing 1 to 3 flows, task sharing varying from 0% to 75% and the number of tasks per flow being equal to three times the number of stages. The number of stages were varied from 1 to 5 for systems with shared tasks while problems with up to 10 stages were considered for systems with no task sharing between the flows. A set of 50 experiments were conducted for each possible combination of the above described parameters. The overall results are as follows:

- For small systems involving 2 or 3 stages; 95% of the time the optimal solution was obtained and 98% of the time the result was within 10% of the optimal.

- For larger systems involving 4 or 5 stages; 72% of the time the optimal solution was obtained and 96% of the time the result was within 10% of the optimal.

- For all systems, when the percentage of task sharing was 25% or less, nearly 100% of the time the result was within 10% of the optimal. When there was no task sharing, more than 99% of the time *GreedyPipe* obtained the optimal result.

The second aspect of performance, execution time, is discussed in Chapter 7.

# Chapter 4

# **Dynamic Programming**

Dynamic Programming (DP) is an important optimization technique [6]. It is efficient in finding optimal solutions for cases with many overlapping subproblems. It solves problems by successively recombining solutions to subproblems and sub-subproblems. In order to avoid solving these sub-subproblems several times, their results are gradually computed and memorized, starting from the simpler problems, until the overall problem itself is solved. Thus, dynamic programming is simply memorization of results of a recurrence, so that time is not spent trying to solve the same subproblem (or problem) repeatedly. Dynamic programming can only be applied when the problem under concern has optimal substructure [19]. Optimal substructure means that the optimal solutions of local problems can lead to the optimal solution of the global problem. In simple terms, that means that the problem can be solved by breaking it down and solving the simpler problems.

In a multi-processor system, if each processor has a separate data memory module associated with it, there will be no memory contention overheads. However, if the number of memory modules is less than the number of processors, the typical case, memory modules will be shared between processors and the overhead due to memory contention needs to be considered when obtaining the optimal allocation. As described in Chapter 2, memory contention overhead can be calculated only after the complete allocation of tasks is known. In this chapter, we describe the application of DP to the task scheduling problem, however since DP divides the problem in to smaller subproblems and deals with one stage at a time it is not possible to consider memory contention while obtaining the optimal solution. Finding the optimal task **and** memory module assignment is considered in Chapter 5 using Simulated Annealing.

## 4.1 Dynamic Programming for Task Scheduling

As indicated above, we consider here a simpler form of the scheduling problem such that each processor has a different memory module allocated to it. Thus, there are no contention overheads and, with  $c_{jk} = 0$ , the performance metric (Equation 2.5) is reduced to:

$$P = \max_{j=1}^{N} P_j = \max_{j=1}^{N} \left\{ \max_{k=1}^{K} \left\{ \sum_{i=1}^{M_j} X_{ijk} t_{ij} \right\} \right\}$$

(4.1)

We further simplify the problem to a single flow,  $F_1$ , with tasks

$T = \{T_1, T_2, T_3, ..., T_M\}$

where M tasks are to be assigned to a pipeline of R processors.

This problem can also be viewed as a partitioning problem where M consecutively ordered tasks are to be partitioned into R intervals such that the maximum time needed to execute the tasks in any interval is minimized. A. Bokhari proposed a dynamic programming solution for this problem in [36] which was further refined by Anily and Federgruen in [33] and Manne and Olstad in [10].

We start by describing the algorithm in [33]. To apply dynamic programming, the optimization problem is first divided into multiple subproblems. Let f be a function that gives the delay associated with the tasks allocated to a stage such that

$$f(i,j) = \sum_{l=i}^{j} t_l \ge 0$$

(4.2)

for  $1 \leq i, j \leq M$ , with equality if and only if j < i. Let d(j, k) represent the maximum processing stage delay over all R stages when tasks  $\{T_1, T_2, ..., T_j\}$  in a flow are assigned to k stages where  $1 \leq j \leq M$  and  $1 \leq k \leq R$ . Then d(M, R) will give the optimal delay of allocating M tasks to R stages (i.e., a task assignment that minimizes the maximum delay). From Equation 4.2, the cost of assigning the first j tasks to a single stage is given by :

$$d(j,1) = f(1,j) = \sum_{i=1}^{j} t_i$$

(4.3)

For any value of j,  $1 \le j \le M$ , d(j, k) can be computed for  $2 < k \le R$  by using the recursion given by Equation 4.4.

$$d(j,k) = \min_{i=k-1}^{j-1} (max[d(i,k-1), f(i+1,j)])$$

(4.4)