### Washington University in St. Louis Washington University Open Scholarship

All Theses and Dissertations (ETDs)

1-1-2011

# High Speed Networking In The Multi-Core Era

Benjamin Wun Washington University in St. Louis

Follow this and additional works at: https://openscholarship.wustl.edu/etd

#### **Recommended** Citation

Wun, Benjamin, "High Speed Networking In The Multi-Core Era" (2011). *All Theses and Dissertations (ETDs)*. 668. https://openscholarship.wustl.edu/etd/668

This Dissertation is brought to you for free and open access by Washington University Open Scholarship. It has been accepted for inclusion in All Theses and Dissertations (ETDs) by an authorized administrator of Washington University Open Scholarship. For more information, please contact digital@wumail.wustl.edu.

#### WASHINGTON UNIVERSITY IN ST. LOUIS

School of Engineering and Applied Science

Department of Computer Science and Engineering

Dissertation Examination Committee: Patrick Crowley, Chair James Buckley Roger Chamberlain David Deal Chris Gill Viktor Gruev

#### HIGH SPEED NETWORKING IN THE MULTI-CORE ERA

by

Benjamin Wun

A dissertation presented to the Graduate School of Arts and Sciences of Washington University in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

December 2011 Saint Louis, Missouri copyright by Benjamin Wun 2011

#### ABSTRACT OF THE THESIS

High Speed Networking in the Multi-Core Era by

Benjamin Wun

Doctor of Philosophy in Computer Engineering Washington University in St. Louis, 2011 Research Advisor: Professor Patrick Crowley

High speed networking is a demanding task that has traditionally been performed in dedicated, purpose built hardware or specialized network processors. These platforms sacrifice flexibility or programmability in favor of performance. Recently, there has been much interest in using multi-core general purpose processors for this task, which have the advantage of being easily programmable and upgradeable. The best way to exploit these new architectures for networking is an open question that has been the subject of much recent research. In this dissertation, I explore the best way to exploit multi-core general purpose processors for packet processing applications. This includes both new architectural organizations for the processors as well as changes to the systems software. I intend to demonstrate the efficacy of these techniques by using them to build an open and extensible network security and monitoring platform that can out perform existing solutions.

## Acknowledgments

I would like to start by thanking my advisor Patrick Crowley for all the advice and support he has given me over the years. His perpetual optimism and practical knowledge have been invaluable.

I have had the opportunity to learn from many of the excellent faculty in this department, including Roger Chamberlain, Jeremy Buhler, and John Turner. I am grateful for the knowledge they and many others imparted to me. I would also like to thank the members of my committee, Chris Gill, Viktor Gruev, David Deal and Jim Buckley.

The CSE office staff have helped to make my life easier in so many ways. Thanks go to Madeline Hawkins, Jayme Moehle, Sharon Matlock, Myrna Harbison and Kelli Eckman.

I would also like to thank the ARL staff, especially John Dehart and Fred Kuhns, who have provided me with excellent advice and practical assistance. This work would have been impossible without their help.

My fellow students have been wonderful to work with, especially Brandon, Eric, Mart, Shakir, Haowei, Michael, Arpith, Michela, Charlie and Mike. I have greatly enjoyed bouncing ideas off of them and mining their practical skills for my own benefit. I hope they have gotten as much out of interacting with me as I have with them. A special thanks goes to Charlie for his assistance with ONL and Mike for collaborating with me on the Scheduler API.

I had the great fortune to spend a year interning at Intel in Oregon where I met and worked with many excellent researchers. I would like to thank them all for the opportunity and for all that they taught me, especially Annie, Arun and Erik, who had a tremendous impact on the work presented here. Finally, my parents have been unwavering in their support of me and taught me to be curious about the world around me. For that, I am forever grateful.

Benjamin Wun

Washington University in Saint Louis December 2011

Dedicated to my parents Lap-Ming and Mei-Na Wun.

# Contents

| A             | Abstract |                                                                                                                                                         |    |  |

|---------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| A             | cknov    | wledgments                                                                                                                                              | ii |  |

| $\mathbf{Li}$ | st of    | Tables                                                                                                                                                  | ii |  |

| $\mathbf{Li}$ | st of    | Figures                                                                                                                                                 | ix |  |

| 1             | Intr     | $\mathbf{oduction}$                                                                                                                                     | 1  |  |

|               | 1.1      | Contributions                                                                                                                                           | 2  |  |

|               | 1.2      | Methodology                                                                                                                                             | 3  |  |

|               | 1.3      | Organization                                                                                                                                            | 3  |  |

| <b>2</b>      | Har      |                                                                                                                                                         | 4  |  |

|               | 2.1      | Packet Processing and the Intel IXP                                                                                                                     | 4  |  |

|               | 2.2      | Linux Network Stack                                                                                                                                     | 6  |  |

|               | 2.3      | Related Work                                                                                                                                            | 7  |  |

|               | 2.4      | Network Acceleration                                                                                                                                    | 8  |  |

|               |          | 2.4.1 Software NIC $\ldots$                                            | 9  |  |

|               |          | 2.4.2 Onloader                                                                                                                                          | 10 |  |

|               |          | 2.4.3 Emulated NIC                                                                                                                                      | 1  |  |

|               | 2.5      | Results                                                                                                                                                 | 11 |  |

|               |          |                                                                                                                                                         | 1  |  |

|               |          | 2.5.2 Receive Path $\ldots$ 1                                                                                                                           | 12 |  |

|               |          | 2.5.3 Transmit Path 1                                                                                                                                   | 15 |  |

|               | 2.6      | Design Improvements                                                                                                                                     | 16 |  |

|               | 2.7      | Conclusion                                                                                                                                              | 17 |  |

| 3             | Para     | allelization of Snort                                                                                                                                   | .8 |  |

|               | 3.1      | Parallel Snort                                                                                                                                          | 19 |  |

|               |          | 3.1.1 Experimental Setup                                                                                                                                | 19 |  |

|               |          | 3.1.2 Evaluation $\ldots \ldots \ldots$ | 20 |  |

|               | 3.2      | Scaling                                                                                                                                                 | 21 |  |

|               | 3.3      | Lessons                                                                                                                                                 | 24 |  |

| <b>4</b>      | Soft     | ware Router API                                                                                                                                         | 25 |  |

|               | 4.1      | Requirements of a Framework                                                                                                                             | 25 |  |

|          |       | 4.1.1    | Performance                                                                                    | 26 |

|----------|-------|----------|------------------------------------------------------------------------------------------------|----|

|          |       | 4.1.2    | Backwards Compatibility                                                                        | 27 |

|          | 4.2   | Existir  | ng Frameworks                                                                                  | 28 |

|          | 4.3   |          |                                                                                                | 30 |

|          | 4.4   | Perform  | mance Evaluation                                                                               | 36 |

|          |       | 4.4.1    | Test Setup                                                                                     | 36 |

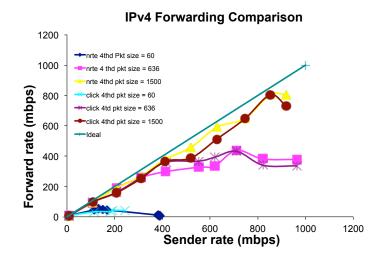

|          |       | 4.4.2    | IPv4 Forwarder                                                                                 | 37 |

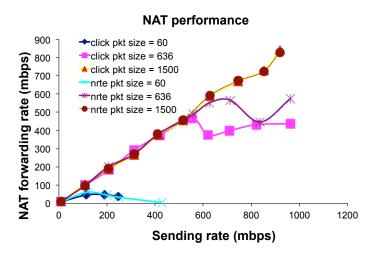

|          |       | 4.4.3    | NAT                                                                                            | 38 |

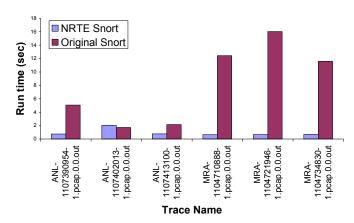

|          |       | 4.4.4    | Snort                                                                                          | 39 |

|          |       | 4.4.5    | Latency                                                                                        | 41 |

| <b>5</b> | Sch   | eduler   | API                                                                                            | 43 |

|          | 5.1   | NRTE     |                                                                                                | 43 |

|          |       | 5.1.1    | Application Interface                                                                          | 44 |

|          |       | 5.1.2    | Scheduler Interface                                                                            | 45 |

|          | 5.2   | Schedu   | ulers                                                                                          | 48 |

|          | 5.3   | Synthe   | etic Benchmark                                                                                 | 50 |

|          | 5.4   | Regex    | Application                                                                                    | 53 |

|          |       | 5.4.1    | Evaluation                                                                                     | 54 |

|          | 5.5   | Relate   | ed Work                                                                                        | 55 |

|          | 5.6   | Conclu   | usion                                                                                          | 56 |

| 6        | Con   | clusior  | <b>n</b>                                                                                       | 57 |

|          | 6.1   | Summa    | ary                                                                                            | 57 |

|          | 6.2   | Future   | e Directions                                                                                   | 57 |

| A        | ppen  | dix A    | NRTE API                                                                                       | 59 |

|          | A.1   | Termir   | nology                                                                                         | 59 |

|          | A.2   | Comm     | non Data Types                                                                                 | 60 |

|          | A.3   | Initiali | ization and Shutdown API                                                                       | 63 |

|          | A.4   | Queuir   | ng API                                                                                         | 66 |

| A        | ppen  | dix B    | Schedule Builder API                                                                           | 68 |

|          | B.1   |          | $0  \text{pre-instantiation}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 68 |

|          | B.2   | Phase    | 1- Topology Creation                                                                           | 69 |

|          | B.3   |          | 2- Scheduling                                                                                  | 71 |

| Re       | efere | nces .   |                                                                                                | 74 |

# List of Tables

| 3.1 | Two Stage Snort Scaling Data                                     | 21 |

|-----|------------------------------------------------------------------|----|

| 3.2 | Queuing Simulation Scaling with Runtimes Clamped to 31200 Clocks | 23 |

|     | Processor Characteristics                                        |    |

| 4.2 | NRTE API Summary                                                 | 33 |

| 5.1 | SchedulerBuilder Class Member Functions                          | 46 |

| 5.2 | Statistics Class Member Functions                                | 47 |

| 5.3 | Scheduler Benchmark Data                                         | 52 |

# List of Figures

| 2.1 | Organization of the IXP 2350 NP                                  | 5  |

|-----|------------------------------------------------------------------|----|

| 2.2 | Architecture Comparison                                          | 9  |

| 2.3 | Receive Throughput Comparison                                    | 13 |

| 2.4 | Receive Percentage Difference                                    | 14 |

| 2.5 | Receive Components                                               | 14 |

| 2.6 | Transmit Throughput                                              | 15 |

| 3.1 | Flow Pinning vs. Simple Threading                                | 20 |

| 3.2 | Two Stage Snort Scaling vs. Ideal                                | 21 |

| 3.3 | Packet Processing Time Distribution                              | 22 |

| 3.4 | Queuing Simulation Scaling with Runtimes Clamped to 31200 Clocks | 23 |

| 4.1 | Pipeline (top) and Pool of Threads (bottom)                      | 28 |

| 4.2 | Queuing Benchmark                                                | 32 |

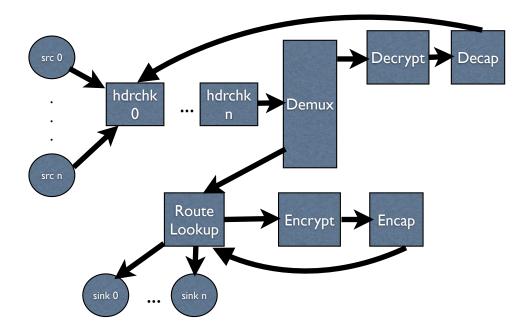

| 4.3 | NRTE Dataflow                                                    | 35 |

| 4.4 | IPv4 Forwarding Comparison                                       | 38 |

| 4.5 | NAT Comparison                                                   | 39 |

| 4.6 | Snort Comparison                                                 | 40 |

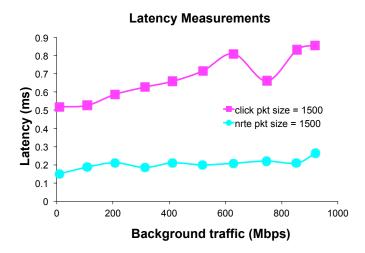

| 4.7 | Latency Measurements                                             | 41 |

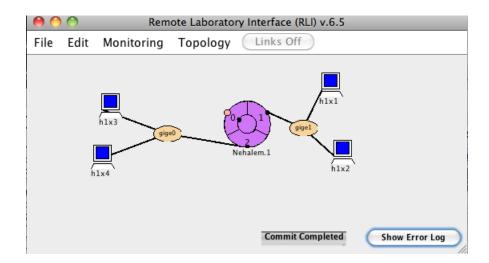

| 5.1 | ONL Configuration                                                | 50 |

| 5.2 | Benchmark Logical Topology                                       | 51 |

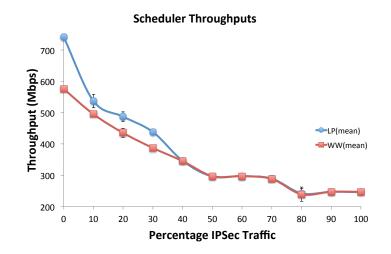

| 5.3 | Scheduler Benchmark                                              | 51 |

## Chapter 1

## Introduction

High speed packet processing is a demanding but important task that is usually performed in dedicated, purpose built hardware. As networks get more complex, additional tasks such as network security and monitoring, or the deployment of research protocols, have created a demand for programmable network devices that can be extended by the end user to perform new tasks or test new ideas. The existing solutions to this problem range from software routers based on general purpose processors, to specialized network processors and extensions to commercial routers. No single solution delivers the combination of flexibility, programmability and high performance required in this domain.

Recently, general purpose processors (GPPs) have been adopting characteristics common to network processing, especially the use of multi-threaded processing cores and multiple cores on a chip. These additions make conventional processors better able to meet the requirements of high speed networking applications; furthermore, general purpose processors are easier to program than network processors (NPs). GPPs can use standard operating systems and programming languages, and do not expose architectural details to the extent that NPs do. However, the software frameworks on GPPs are often not optimized for multi-core environments, or for the demanding and specialized task of line rate network processing. Many projects have tried to make it easier to write networking code on GPPs, but none seem to offer the definitive solution.

In this dissertation, I will explore new architectures, both software and hardware, for designing programmable high speed network processing platforms. I will further demonstrate the effectiveness of such an architecture for creating network monitoring applications.

The first part of this study will investigate architectural additions to general purpose processors to support networking. I propose and evaluate a heterogeneous multi-core architecture that moves network stack processing to a series of specialized cores on the same processor die as the main CPU.

The second part of this study will examine the best way to create programmable packet processing platforms in the context of existing general purpose platforms. I examine the efficacy of various parallelization strategies on Snort, an example of a complex and stateful network application. I present an API for writing complex, stateful, pipelined network applications and examine its efficacy by porting the Snort intrusion detection system to use it. Finally, I take the lessons learned from parallelizing Snort and apply them to the design of a scheduler API for network centric applications.

## **1.1** Contributions

This thesis makes several contributions.

First, we propose a novel hardware architecture that uses a cluster of specialized cores to perform networking tasks on behalf of a host processor, a technique known as network onloading. We evaluate this architecture by building a prototype using the IXP network processor as a starting point. We demonstrate an improvement in packet reception throughput from 40 to 100 % depending on the incoming packet size.

Second, we propose an API for writing networking applications on multi-core architectures. We evaluate the effectiveness of this API by porting the Snort intrusion detection system to use it.

Finally, we extend the API to include provisions for writing new schedulers that dynamically adapt the application mapping to the underlying hardware based on changes in the workload. We use this API to evaluate the effectiveness of two different scheduling algorithms and demonstrate the usefulness of each under different scenarios.

## 1.2 Methodology

We test the proposed ideas by building working prototypes. Evaluating the prototypes can happen in a variety of ways. When possible, systems were tested using the Open Network Laboratory, a reprogrammable network testbed [51]. Other systems were evaluated in a more ad-hoc fashion. The details of each experiment are described in further detail in the appropriate chapter.

## **1.3** Organization

This document is organized around a series of projects in which ideas are proposed and prototypes built to test them. Each chapter represents a project organized around a single idea, and as such, background information and related work for each project are presented in the relevant chapter. The remainder of this document is organized as follows. Chapter 2 proposes a novel architecture for network onloading. Chapter 3 presents an evaluation of a parallelized version of Snort and an analysis of the bottleneck encountered by it. Chapter 4 presents an API for writing parallelized network applications. Chapter 5 extends this API to allow the writing of new packet schedulers and evaluates the efficacy of two different schedulers, one of which has not previously been published.

## Chapter 2

## Hardware Acceleration

In this section, we examine the proposition that the addition of small, simple cores to a general purpose CPU can accelerate standard sockets network I/O, either by employing the techniques of server NICs or through network onloading, which moves network protocol processing from the host CPU (which must be shared with other applications) to a set of dedicated resources. The goal of this proposed architecture is to find a way to preserve traditional network programming semantics while bringing performance in line with modern demands. To evaluate this proposal, we have built a prototype system using the Intel IXP network processor [22]. We will begin this section by providing some background about the IXP, then provide some further background on network processing on general purpose processors, discuss related work, and finish by describing our proposed architecture.

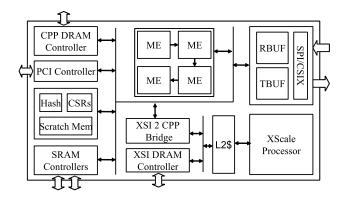

### 2.1 Packet Processing and the Intel IXP

IXP Network Processors (NPs) feature two types of processors. The first is an ARM based XScale which boots a traditional OS and is typically used in management and slow path processing. The second processor type, the microengine (ME), is a small embedded core for line-rate packet processing. IXP NPs have a single XScale, and 4, 8, or 16 MEs, depending on the specific chip. In this work, we use the IXP2350, which is illustrated in Figure 2.1.

In our prototype, the XScale is the host CPU, and the MEs provide I/O acceleration. This is an atypical use of the XScale. In most application, the XScale would only

Figure 2.1: Organization of the IXP 2350 NP

receive exception packets, a relatively small fraction of traffic. In our system, an application on the XScale is the source and destination for every packet. We use the IXP for its convenient approximation of our architectural model. The XScale represents a high-performance GPP for which the MEs accelerate network I/O.

Each IXP ME provides hardware support for 8 hardware thread contexts, including register storage, multi-threading ISA extensions, and a thread arbiter. Each ME has its own local data and instruction storage, both implemented as SRAMs. An ME communicates asynchronously with other units via I/O commands and transfer registers. A DRAM read, for example, is carried out by sending a read operation to the DRAM controller (via the Command Outlet FIFO) that specifies the desired address as well as the target incoming transfer registers to which the data should be delivered. Hardware signals are specified in the ISA and are asserted when requested operations have completed. This message-passing style and the use of hardware signals allow ME software to initiate multiple external requests without blocking, as long as subsequent computation does not depend on the completion of these requests. This interface provides both a more efficient way to access memory and a way to hide memory latencies.

Other units provide critical functions or resources in hardware, including a configurable hash unit, 16KB of on-chip scratch memory and 128KB of message SRAM. The IXP 2350 include a DDR SDRAM and a QDR SRAM controller on-chip as channels for bulk and latency-sensitive data storage, respectively. A separate channel of SDRAM is used by the OS and programs on the XScale. Both the MEs and XScale are clocked at 900 MHz.

All IXP processors contain a Media Switch Fabric (MSF) to facilitate high speed communication between the MEs and MACs. The IXP2350 uses the MSF to interface to its two, 1Gbps on-chip MACs. Having the MAC located on-chip over a high speed interface is a great advantage for scalable, high speed networking [10].

### 2.2 Linux Network Stack

On general purpose processors, network processing is split between the network interface card (NIC) and the network stack running in the operating system kernel on the host CPU. In this section we provide some brief background on how packets flow through a modern system.

First, we take a look at packet reception. When a packet arrives at the NIC, it raises an interrupt, which causes the host to stop whatever program it is executing in order to run the network receive code. The host copies the packet from the NIC to a buffer in main memory. From there, the headers and checksums are verified, the packet is classified and the payload is copied to the buffer of the user program that is waiting for it.

On the transmit side, the host copies packets from a program's buffer into a protected kernel space buffer. From there, it adds the proper headers and computes checksums. It then copies the packet into the NIC's buffer and tells it to transmit the packet.

With this data flow, all processing is done on the host processor, which cannot execute other programs while it is handling network traffic. Since network processing shares the CPU with other programs, under load, the system may drop a large number of packets or become so dominated by network processing that other programs are starved of resources. Modern NICs include accelerators to offload or streamline parts of this process, including interrupt moderation, receive rings and checksum offload. These are discussed in more detail in our description of our prototype system in section 2.4. In network onloading, we take this a step further and move all network protocol processing to dedicated resources, freeing the host CPU to perform other tasks, as discussed in section 2.4.2.

A further bottleneck in this scenario is the movement of data from user to kernel space. Not only does it require moving a potentially large amount of data, it requires a context switch from kernel to user space and back, which can be very costly- up to 36 percent in some scenarios [23]. However, this is unavoidable if we are to preserve the sockets programming model, which is an explicit goal of this part of the project.

### 2.3 Related Work

TCP offload engines (TOEs), which move protocol processing from the host CPU to the NIC, are being used to accelerate specific tasks, such as storage area networking or for use with protocols such as RDMA [33] [48]. Though commercial implementations exist, it is inconclusive whether TOEs are actually an effective solution, with some studies showing the TOE itself to be the actual bottleneck [5] [43]. Our approach differs from that taken with TOEs, as IXP MEs are on-chip, fully-programmable, and closely coupled with the CPU, thus bypassing the major problems with TOEs and providing additional opportunities for optimization. Furthermore, our interest is in accelerating general purpose networking, whereas most TOEs are used to accelerate a specific task.

Binkert et al., in a simulation based study, have examined the efficacy of moving the NIC's location relative to the CPU [10]. They found that putting the NIC on a direct HyperTransport like channel and eliminating the I/O bus bottleneck greatly increased system throughput. Locating the NIC on chip produced further improvements for the receive path and also allowed packet data to be directly written into cache, a potential accelerator for certain network workloads. While the IXP has no mechanism for direct cache access by the MEs, the MEs, MSF, and MACs are located on-chip with a dedicated off-chip connection to the PHY. The ETA [41] project demonstrates a new interface for communication between a host processor and an associated packet processing engine (PPE). Their interface allows for asynchronous operation, whereby a user program can send off a packet for transmission or request notification of arriving packets without blocking. The traditional sockets interface semantics require a program to block until the packet is sent or until a packet arrives. For the prototype ETA system, the PPE was a Xeon processor in an SMP system. This prototype showed both improved network throughput and an increase in surplus cycles for the host processor. This differs from our research because ETA uses a state of the art superscalar out of order processor with a high clock rate, deep pipeline and prodigious amounts of cache as the packet processing engine, whereas our project uses the smaller, in order, single issue MEs of the IXP. The smaller, simpler MEs are more power and area efficient for this task than the Xeon.

The authors of ETA have advocated TCP Onloading by combining ETA with a memory aware reference stack (MARS) [41]. MARS is an attempt to mitigate memory access latencies by using asynchronous memory copies, light-weight threading, and direct cache access. The first two are already present in the IXP.

Finally, recent advances in NIC architectures for virtualization have produced commercial NICs with multiple receive queues and the ability to classify packets at the NIC. This pushes some functionality traditionally performed in the CPU to the NIC and provides an alternative approach to exploiting multi-core processors. This approach is implemented in homogeneous multi-core environments (though it does not have to be) and packets are still processed in a traditional network stack (either in the OS or VM) and only yields real performance gains when there are a large number of flows involved which can be processed in parallel.

### 2.4 Network Acceleration

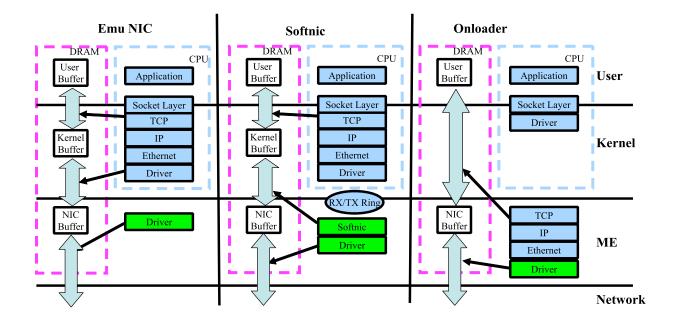

In order to evaluate the effectiveness of our onloading proposal, we have explored two ways of using the MEs to accelerate network processing in the Linux kernel running on the XScale. The first, which we term the **softnic** approach, is to have the MEs emulate a high end server NIC [11], while leaving the networking stack

Figure 2.2: Architecture Comparison

on the XScale unmodified. Our second system is an onload engine that moves the networking stack to the MEs, and only performs high level interface functions on the XScale. Both systems either enhance or replace the kernel's networking stack and support the sockets interface for communicating with user programs.

#### 2.4.1 Software NIC

Figure 2.2 contains an illustration of the **softnic's** architecture. To transmit a packet from the **softnic**, a user program calls the *sendmesg* system call. The upper, unmodified layers of the network stack in the Linux kernel will copy the data to be

sent into a kernel space buffer, determine the interface the packet should be sent out on, and add headers. At this point, the fully formed packet is passed to the driver layer code, which is where our softnic modifications take over. The driver code places the buffer on a ring to the MEs for transmission. The kernel on the XScale is now finished with this packet and can go on to process the next one. An ME is constantly polling this ring (a hardware controlled scratchpad ring) for work. When it dequeues a packet buffer, it copies the contents into an internal buffer and raises an interrupt, letting the Xscale know it can now free that buffer. The internal buffer is then passed to another ME in a pipelined fashion for transmission. When a packet arrives at the MEs in the **softnic**, its checksum is verified, and it is copied into a kernel packet buffer, a pool of which has been preallocated for the MEs' use. The filled buffer is put on a ring for delivery to the XScale, and an interrupt is raised. The interrupt handler on the XScale will turn off interrupts, pull packets off the receive ring, and enqueue them for processing by higher levels in the kernel. Interrupts are re-enabled when the receive ring has been emptied. This is the adaptive polling technique. Control devolves to the unmodified Linux stack and a soft interrupt is raised, invoking the protocol processing code.

#### 2.4.2 Onloader

Figure 2.2 also illustrates the organization of the **onloader**. When *sendmsg* is called in the onloader, the kernel prepares the user buffer for DMA and signals the MEs that a buffer is ready for processing. The MEs copy data directly from the user buffer into an internal buffer. The MEs then add headers and transmit the packet.

When a packet arrives at the **onloader**, an ME verifies the checksum, examines the headers, looks up the control block for that connection, and enqueues the packet for the proper connection. An interrupt is raised only if there is an idle process waiting for that packet to arrive. The only work the Xscale needs to do is to notify the waiting process that a packet is now available.

Our onload engine currently only supports UDP over IP. We believe that our results will also apply to TCP, as most of the OS infrastructure, such as interrupts, DMA, sockets interface etc. are common between them. The only major difference is the protocol processing step, which is a demonstrably small component of packet processing [14].

#### 2.4.3 Emulated NIC

To determine how well the **softnic** and onload engine accelerate networking, we compare them to a base case wherein the MEs perform the minimum possible work to get packets to and from the MSF and most tasks are left to the XScale (called the **emu nic** in the graphics). The left side of Figure 2.2 illustrates the organization of the emulated nic. The **emu nic** corresponds to a low end NIC in a desktop system. The main difference between the **softnic** and this base case is that the driver code on the XScale must compute checksums and do all data copies between kernel buffers and device buffers. Additionally, interrupt handling is more expensive, because interrupts are raised for every packet on reception instead of adaptively polling after the first one.

### 2.5 Results

This section describes the experiments we ran to evaluate the effectiveness of the onloader in accelerating networking operations.

#### 2.5.1 Experiment Setup

Our hardware setup consists of an IXP2350 system, connected through a gigabit Ethernet switch to a PC running Linux 2.4.19. The PC sends packets to the IXP to test the IXP's receive throughput, and receives packets from the IXP to determine the IXP's send throughput. We have determined by sending packets between two PCs that the PC does not represent a bottleneck.

As will be seen, applications executing on the 900 MHz XScale processor cannot receive or transmit packets at rates greater than 500 Mbps. While the packet processing code on the MEs can sustain approximately 2 Gbps, this rate cannot be delivered to the XScale and the applications it hosts. The main challenge facing the end-host system is data copying. Data not only has to be copied from the network into internal buffers and out again, but also into and out of user buffers within the system. As we will see, the cost of this is due not only to moving bytes, but also to pinning and aligning with virtual pages. Normally, router applications implement their fast path on the MEs alone and use the XScale for exceptions, but since we must interface with user programs on the XScale, we incur the overheads of sharing it with other OS functions, such as timer interrupts, or task scheduling.

While the XScale on the IXP2350 cannot perform end-host network processing tasks at gigabit rates, we note that our goal is not absolute performance, but to validate our idea that small, simple, efficient cores attached to a general purpose processor can accelerate network processing. Hence, our use of the emu nic as a base case for performance.

We ran our experiments using the Iperf benchmark [37] in UDP mode. In server mode, Iperf waits for a client to connect, and counts the number of bytes received until a termination packet is received. A timestamp is taken after reception of the first packet and reception of the termination packet for determining the achieved throughput. The client program sends fixed sized packets for a given amount of time, followed by a termination packet, and keeps track of the number of bytes sent and the elapsed time. This is a test of throughput in a bulk data movement application.

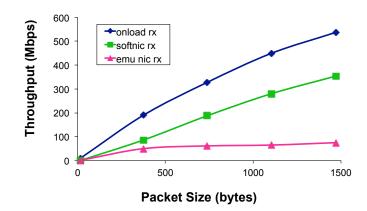

#### 2.5.2 Receive Path

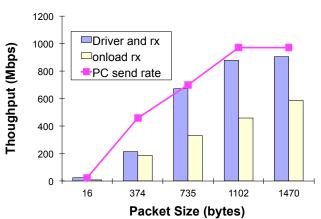

Figure 2.3 shows the achievable receive throughput for the 3 cases. We can see that both the **softnic** and **onloader** are clearly superior to the base case. For large packets, a nearly 10-fold improvement is seen. This is mainly due to the MEs' superior ability to move memory from buffer to buffer. The base case NIC suffers from the XScale's more limited bandwidth when copying between two buffers. Furthermore, while the number of data copies is the same between the base NIC and the **softnic** (from the MSF to an internal buffer, to a kernel buffer, to a user buffer), the **softnic** handles the copy from the internal to kernel buffer asynchronously on the MEs. The

#### **RX** Throughput Comparison

Figure 2.3: Receive Throughput Comparison

**onloader** avoids the copy to a kernel buffer altogether and copies data directly from its internal buffers into the user program's buffers.

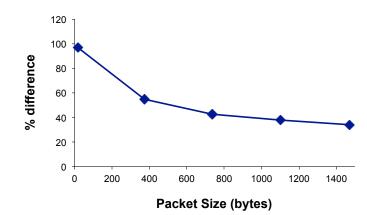

Figure 2.4 shows the percentage improvement of the **onloader** over the **softnic** for different packet sizes. Between the **softnic** and the **onloader**, the **onloader** has superior receive performance, with throughput increase between 100% and 40%. This difference is especially true for smaller packets, where per packet overheads, such as header processing and control buffer lookups, dominate execution time. The main reason for the improvement is that the **onloader** can asynchronously receive and enqueue packets while the XScale can be dedicated to other tasks, such as running the userspace benchmarking program. For the **softnic**, the XScale must split its time between packet processing and other tasks. With larger packets, the per byte costs of checksumming and data copying are dominant, and as this is done on the MEs in both the **softnic** and **onloader**, the difference between them becomes quite small, about 20%.

Figure 2.5 shows the throughput of various onloader receive components. The top line shows the sending rate of the PC. The first set of bars is the receive throughput of the driver and receive blocks of the onloader, with no user program consuming the received packets. These blocks receive packets from the network, move them into an internal buffer, verify checksums, parse the headers, look up control blocks and

RX % improvement of onload vs. softnic

Figure 2.4: Receive Percentage Difference

**Receive Component Analysis**

Figure 2.5: Receive Components

Figure 2.6: Transmit Throughput

enqueue the packets for future reference. They achieve a receive throughput very close to the sender's sending rate. The second set of bars shows the throughput of the entire **onloader** system, including the driver and receive block, as well as an XScale component that calls the *recvmsg* system call and moves the packet payloads into a user buffer. As the driver and receive blocks receive packets about as fast as they are being sent, we must conclude that the movement of data into user space using sockets is our receive bottleneck.

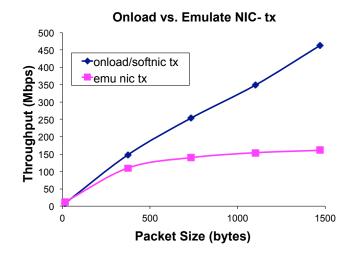

#### 2.5.3 Transmit Path

On the transmit side, the **onloader** and **softnic** are again superior to the base case, as demonstrated in Figure 2.6. The main reason is because the **onloader** and **softnic** take advantage of the MEs' superior ability to move memory, whereas the base case is hampered by the XScale's limited memory throughput. There is no clear advantage for either the **softnic** or **onloader** on the transmit side, as the main bottleneck here is memory copying and checksumming, which are offloaded to the MEs in both cases. As with the receive path, the **softnic** on transmit has the advantage of asynchronously performing a DMA from kernel buffers to ME buffers on the MEs while the onloader copies directly from user buffers to internal ME buffers.

### 2.6 Design Improvements

Our experience designing the **onloader** has demonstrated some aspects of the IXP design that should be modified in a system designed for onloading. These observations apply to any on-chip I/O acceleration technique. One such weakness is the lack of a Memory Management Unit (MMU). In order for the MEs to copy data directly to and from user space buffers into internal buffers, achieving the equivalent of zero copy semantics, the kernel on the XScale must first ensure that all pages of the user buffer exist in memory, walk the system's page tables to find their locations, and clean or invalidate the cache in order to keep consistency. This is very inefficient; in early implementations, we found this cost to account for a third of the per packet overhead. In order to get around this problem, we cached previous mappings of user space buffers for each connection, so that if a program reuses the same buffer (as the Iperf benchmark does), this costly overhead does not have to be incurred again. This resulted in a 1.5X increase in throughput for the receive path, which is reflected in our numbers for the previous section. Without this optimization, the onloader is actually slower than the softnic, despite eliminating one buffer to buffer copy. Giving the MEs a Translation Lookaside Buffer (TLB) would effectively do the same job in hardware, without having to incur page walking overheads on the XScale.

Another optimization would be to have the MEs participate fully in the XScale's cache coherence protocol. The ability of the MEs to push data into the L2 on writes to DRAM was a big improvement for both the **onloader** and **softnic**. If, instead of using the push feature (which is optional), the XScale were to invalidate those addresses in its cache and reload the data from memory, our experiments show that the softnic would suffer a 35% degradation in performance. As of the current model IXP2350s, this is the only feature available for cache coherence. A full coherence protocol, which would include letting the MEs snoop the XScale cache on a memory read, would prove advantageous for the transmit path.

One problem with supporting the sockets interface is that the system has no control over where the application allocates its user buffers. Thus when moving data into these buffers, the DMA mechanism must contend with both crossing page boundaries and DRAM word alignment. For DRAM alignment, a read-modify-write may be necessary to avoid overwriting other data that shares a given DRAM word with the user buffer.

## 2.7 Conclusion

The architecture proposed in this section is a set of hardware and software changes that we believe represent the best way to preserve traditional socket programming semantics in modern multi-core systems. In the next section, we examine strategies for parallelizing applications on existing hardware and apply those lessons to the design of a network API targeted at writing efficient, parallel networking applications on multi-core processors.

## Chapter 3

## **Parallelization of Snort**

The Snort [42] intrusion detection program is a popular tool for securing networks using deep packet inspection to detect the signature of malicious packets. For Snort to be effective, it must be able to keep up with increasing line rates. Future processors will improve performance through the addition of more cores, and high performance programs such as Snort need to be parallelized to take advantage of these newly available resources.

We parallelize Snort by running a full copy of the Snort detection engine on each core in the system. Packets of the same flow are processed in order on the same core and parallelism is achieved by processing packets from different flows in parallel on different cores.

We further contribute a study of the efficacy of a static flow pinning scheme under realistic scenarios. We test our parallel Snort implementation against real world packet traces collected from multiple sources, including the internal and external Intel web servers, and publicly available traces of connections between university networks and the internet core from the National Laboratory for Applied Networking Research (NLANR). Results from the Intel servers are not presented directly for privacy reasons, but were used to confirm results obtained using the other traces. The NLANR traces are no longer available on the web, but this paper [29] gives a good overview of their characteristics. The lessons learned from this case study will be applied in the following chapters to the design of an API for writing efficient parallel networking code.

## 3.1 Parallel Snort

We parallelize Snort by replicating its functions across multiple cores and processing multiple packets from different flows in parallel on different cores. Packets in the same flow are processed sequentially on the same core to preserve in order delivery and limit the sharing of per flow data across cores, which reduces lock and cache contention between cores. We use a two stage pipeline to process packets- the first stage, running in a dedicated core, receives packets (using libpcap), performs classification on those packet and passes them to the second stage. The second stage contains the rest of Snort's functionality, such as stream reassembly, regular expression matching, and event logging. This second stage can be replicated in multiple threads, with each instance pinned to a particular CPU core. Flows are pinned to a particular thread in order to increase cache locality and reduce context switching overheads. Flow pinning also allows us to eliminate locks for flow specific data structures. Another optimization is the per thread packet pool- using separate buffer pools increases cache locality and allows the queues to be implemented as lockless ring buffers. Furthermore, using preallocated buffers improves performance by eliminating expensive *malloc* calls from the fast path. While there have been other attempts to parallelize Snort [6] [27] [46] [7], we are aware of only one other that does so in a flow aware manner [45]. Their methodology differs from ours in that they do dynamic reassignment of flows and and do not have a thread dedicated exclusively to flow classification. It is hard to compare our results to theirs, as we use different packet traces, different versions of Snort and different hardware. However, they observe a roughly 3x speedup when moving from 1 to 4 threads, which, as demonstrated in the next section, is what we observe as well.

#### 3.1.1 Experimental Setup

Our experiments were run on an 8 core Xeon system (dual quad core CPUs), with packet traces read off a disk to avoid having the network become a bottleneck, since we are interested in the performance of the Snort program, not the network stack. Furthermore, dropping packets can cause major changes in Snort's behavior and reading the trace from a file allows Snort to throttle its own input rate. We measured

Figure 3.1: Flow Pinning vs. Simple Threading

the total time Snort requires to process a trace and used that as the metric for comparison.

Our traces were collected from multiple sources, including the internal and external Intel web servers, and connections between university networks and the internet core (NLANR), described earlier in this chapter. We believe these to be a good sampling of real world workloads likely to be encountered by Snort. Since these traces only include packet headers, synthetic packet bodies were inserted for testing. These packet bodies contain random data and are not meant to simulate any particular attack signature.

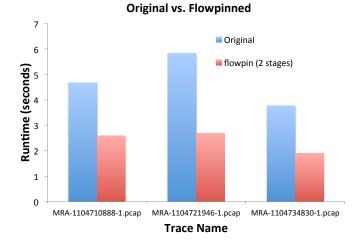

#### 3.1.2 Evaluation

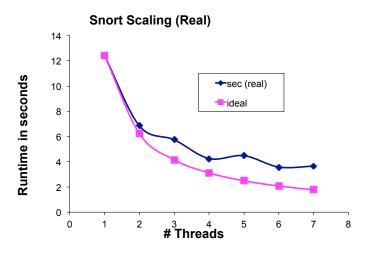

Our first experiment was to examine the efficacy of flow pinning. For this we had 2 versions of Snort- one that does flow pinning, and one that does not and has locks inserted for the access of per flow data structures. The result, as demonstrated in Figure 1, is that flow pinning is an important and effective optimization, though the level of effectiveness depends on the particular workload. This being the case, we focused our work on the flow pinned version of Snort. Next, we tested the scalability of this scheme by running Snort over several workloads using different numbers of cores. Figure 3.2 illustrates the scaling of 2 stage Snort for one of the workloads

Figure 3.2: Two Stage Snort Scaling vs. Ideal

(MRA-1104710888-1), along with a curve representing ideal scaling (i.e. time to run Snort using one core divided by N). As more cores are added, Snort's performance deviates further and further from ideal. For some traces (not shown), performance even degrades above a certain number of cores. Table 3.1 shows the data used to make that graph as well as well as the actual % difference from ideal.

| Num Threads | Seconds | Ideal | % difference |

|-------------|---------|-------|--------------|

| 1           | 12.4    | 12.4  | 0            |

| 2           | 6.8     | 6.2   | -9.6         |

| 3           | 5.7     | 4.4   | -29.5        |

| 4           | 4.2     | 3.1   | -35.4        |

| 5           | 4.5     | 2.5   | -80.0        |

| 6           | 3.6     | 2.1   | -71.4        |

| 7           | 3.6     | 1.8   | -100.0       |

Table 3.1: Two Stage Snort Scaling Data

## 3.2 Scaling

We found that failure to scale as expected was caused by an uneven distribution of work among the threads. Some packets take much longer to process than average,

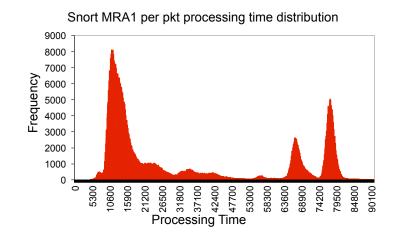

Figure 3.3: Packet Processing Time Distribution

and those packets can cause a single thread to be continually busy while the others clear their queues and sit idle. This is true even if the number of packets processed by each thread is similar. Figure 3 shows the distribution of time required to process individual packets in Snort when only a single thread is used. Using only one thread eliminates variables such as lock contention and competition between threads for resources (buses, L2 cache space, etc). As can be seen from the distribution, most packets take around 12000 clock cycles to process, but there are plenty of packets that take more, with clusters around 68000 and 77000 clock cycles. Not shown on the graph are 3 additional packets that take several orders of magnitude more processing time. These longer packets might cause a single thread to become backed up and block the entire program, especially if they occur in bursts and are correlated on specific flows. We believe the latter behavior to be likely, but have not tested it.

In order to confirm our suspicion that uneven packet times are the cause of our poor scaling, we wrote a simulator that takes a trace of packet runtimes from the two stage Snort using 1 process thread, and simulates the queuing behavior. This allows us to eliminate lock contention and other possible factors. We wanted to see if we could replicate the scaling issues in the simulator, and if clamping the runtimes of all packets to not exceed a maximum value, we could improve the scaling.

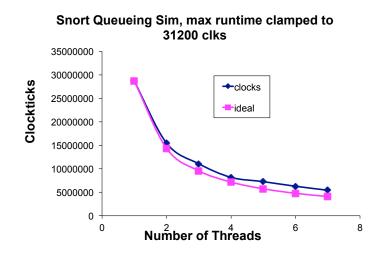

Figure 3.4: Queuing Simulation Scaling with Runtimes Clamped to 31200 Clocks

| Num Threads | Clocks   | Ideal    | % difference |

|-------------|----------|----------|--------------|

| 1           | 28693218 | 28693218 | 0            |

| 2           | 15475780 | 14346609 | -7.871       |

| 3           | 11071555 | 9564406  | -15.758      |

| 4           | 8175468  | 7173304  | -13.971      |

| 5           | 7264940  | 5738643  | -26.597      |

| 6           | 6282468  | 4782203  | -31.372      |

| 7           | 5434540  | 4099031  | -32.581      |

Table 3.2: Queuing Simulation Scaling with Runtimes Clamped to 31200 Clocks

We ran our simulator using an unmodified packet trace and received results similar to what we saw in practice. Next, we clamped the max runtime for any packet to be 31200 simulated clock ticks (which are NOT directly convertible to real clock ticks as they have been scaled to speed up simulation runs). Looking at the packet processing time distribution, 31200 is at the high end of the first peak in the graph, and we consider anything above that to be an excessively long processing time. Thus, clamping the runtimes to 31200 clocks should effectively eliminate the effects of excessively uneven packet processing times from the simulation, while maintaining the same number of packets and their distribution to the threads. The result, shown in Figure 3.4 is scaling that is much closer to ideal. For exact numbers, compare the % difference from ideal in table 3.2 to the one in table 3.1. We feel that the results of this simulation study confirm our theory that uneven packet processing times are the main reason for Snort's lack of scaling. If poor packet distribution is indeed a problem, it would seem to be a lesser one.

### 3.3 Lessons

The experience of programming and benchmarking Snort has taught us several lessons that we will apply to the design of a parallel network programming API in the following chapters.

First is the efficacy of flow-pinning in reducing lock contention in complex, stateful programs. Our experiments clearly show that this is an effective strategy and should be incorporated in future applications.

Second, the fact that Snort's performance is being gated by the relatively few exceptional packets is an interesting result. Head of line blocking by exceptional packets becomes a major concern with the static scheduling scheme currently in use. In the next chapter, we develop new scheduling strategies that might behave better under these circumstances. Unfortunately, we were unable to apply them to the parallelized Snort implementations we have been using throughout this chapter, as they are owned by Intel and were no longer available to us at the time of the following experiments.

## Chapter 4

## Software Router API

Network devices are becoming ever more complex. The demand for new capabilities in routers has lead to an interest in programmable network devices that are capable of high speed packet processing. However, the traditional programming tools for general purpose processors are not designed for the specific and demanding task of network packet processing. In our view, no current programming environment provides the ideal set of characteristics for a networking device. These include good performance, reuse of familiar languages, ease of use, and backwards compatibility. Because the needs of the network programming community are not being met by existing solutions, we see an opportunity to provide a programming environment that will be beneficial to network operators, system vendors, semiconductor vendors, and software developers alike.

In this chapter, we will present our API for writing high performance packet processing applications that run on general purpose processors.

## 4.1 Requirements of a Framework

The goal of this chapter is to present a framework for writing network centric programs. We believe the most important considerations for such a framework are performance and backwards compatibility, which we discuss in this section.

| Processor   | Clock | CPU   | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ | Packet | Mem    | Processoi | Core  | Peak  | Peak   |

|-------------|-------|-------|--------------------------------------------------------|--------|--------|-----------|-------|-------|--------|

| (NP=Network | (MHz) | Power | Power                                                  | I/O    | I/O    | Cores     | Issue | BIPS  | BIPS/W |

| Processor   |       | (W)   | (W)                                                    | (Gbps) | (Gbps) |           | Width |       |        |

| GP=General  |       | . ,   | . ,                                                    |        |        |           |       |       |        |

| Purpose     |       |       |                                                        |        |        |           |       |       |        |

| Processor)  |       |       |                                                        |        |        |           |       |       |        |

| Cisco SPP   | 250   | 35    | 0                                                      | 192    | 175    | 188       | 1     | 47    | 1.34   |

| (NP)        |       |       |                                                        |        |        |           |       |       |        |

| Intel       | 1500  | 27    | 0                                                      | 25     | 121.16 | 16        | 1     | 24    | 0.89   |

| IXP2855     |       |       |                                                        |        |        |           |       |       |        |

| (NP)        |       |       |                                                        |        |        |           |       |       |        |

| Cavium      | 1000  | 40    | 0                                                      | 25     | 102.4  | 16        | 2     | 32    | 0.8    |

| Octeon      |       |       |                                                        |        |        |           |       |       |        |

| CN5860      |       |       |                                                        |        |        |           |       |       |        |

| (NP)        |       |       |                                                        |        |        |           |       |       |        |

| Raza XLR    | 1000  | 32    | 0                                                      | 25     | 230.4  | 8         | 1     | 7     | 0.25   |

| 732         |       |       |                                                        |        |        |           |       |       |        |

| Cavium      | 600   | 30    | 0                                                      | 25     | 102.4  | 16        | 2     | 19.2  | 0.64   |

| Octeon      |       |       |                                                        |        |        |           |       |       |        |

| CN3860      |       |       |                                                        |        |        |           |       |       |        |

| (NP)        |       |       |                                                        |        |        |           |       |       |        |

| Intel Quad- | 2330  | 80    | 30                                                     | 0      | 85.6   | 4         | 4     | 37.28 | 0.34   |

| Core Xeon   |       |       |                                                        |        |        |           |       |       |        |

| 5300, In-   |       |       |                                                        |        |        |           |       |       |        |

| tel 5000P   |       |       |                                                        |        |        |           |       |       |        |

| chipset     |       |       |                                                        |        |        |           |       |       |        |

| (GPP)       |       |       |                                                        |        |        |           |       |       |        |

| AMD         | 2600  | 65    | 0                                                      | 192    | 85.6   | 2         | 3     | 15.6  | 0.24   |

| Dual-Core   |       |       |                                                        |        |        |           |       |       |        |

| Opteron     |       |       |                                                        |        |        |           |       |       |        |

| 1218 HE     |       |       |                                                        |        |        |           |       |       |        |

| (GPP)       | 1.100 | 0.4   |                                                        | 10     |        |           |       | 22.4  | 0.05   |

| Niagara 2   | 1400  | 84    | 0                                                      | 40     | 307.2  | 8         | 2     | 22.4  | 0.27   |

| (NP)        |       |       |                                                        |        |        |           |       |       |        |

Table 4.1: Processor Characteristics

## 4.1.1 Performance

Modern processors have enough raw performance to process packets at high rates. Even general purpose processors of the newest generation, such as a 4-core Nehalem, can process minimum sized packets at close to line rate for gigabit connections. Table 4.1 shows the peak performance (expressed in billions of instructions per second) for a variety of NPs and GPPs (data from [22] [35] [20] [2] [24] [15] [4]). NPs tend to use less power and are designed to be able to achieve that peak, but GPPs tend to have the best peak performance, leading us to believe that they should be able to compete with NPs if properly harnessed. A poor software layer can significantly reduce performance. A major goal of a good framework should be that it can be easily implemented on a number of systems without unduly strangling performance. For example, a major shortcoming of the NP-Click [47] project is that small-packet performance is greatly reduced compared with that on an application written in the IXPs native C-derivative.

Our proposed API, the Network Runtime Environment (NRTE) uses a pipelining approach that has several advantages for getting the most performance out of a general purpose processor. Pipelining allows us to reduce the cache footprint on each core by reducing the working set of each core. Secondly, pipelining allows us to process multiple packets in different stages in parallel. Finally, the use of flow-pinning takes advantage of cache locality by keeping per flow data structures on the same core and its associated cache. This reduces cache thrashing and lock contention.

#### 4.1.2 Backwards Compatibility

We expect future generations of networking devices to get a performance boost from additional threading and fixed-function accelerators, and the ability to take advantage of these new features automatically is paramount. How this can be done is an open question. Some attempts have been made to find ways to automatically map program components to hardware threads [16] [12]. None of these solutions is perfect. First, there is a tradeoff between static mapping at compile time and automatic remapping at runtime. The former obviates the need to have a runtime system that can remap program components, which can potentially require significant overhead. The latter would be better at adapting to changing workloads. As demonstrated in [39] the ability to adapt to different workloads can significantly improve performance in the face of changing workloads.

Future proofing is difficult; if we make the assumption that future performance comes from greater parallelism, the proper way to exploit that parallelism automatically is not clear. One possibility is to organize programs in a pool of worker threads, and to scale up the number of program threads as the available number of hardware threads increases, but not all applications are amenable to this type of parallelization.

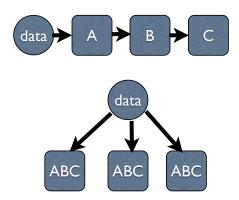

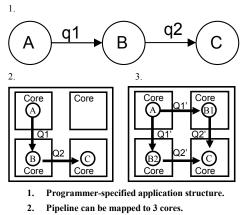

Figure 4.1: Pipeline (top) and Pool of Threads (bottom)

Programs that use pipelined parallelism and distribute their stages among multiple hardware threads can only scale to a point; once the number of hardware threads exceeds the number of explicit stages in the program, these applications will no longer automatically benefit without programmer intervention. Figure 4.1 illustrates the two different types of organization. At the very least, programmers must either change their code to create more duplicate threads, or write extra code to allow their programs to adapt automatically, but this is cumbersome and done on a case-by-case basis. The NRTEs solution is to duplicate pipeline stages at runtime, which allows it to use both strategies in a straightforward manner without the need to rewrite or recompile the application.

## 4.2 Existing Frameworks

There exist many APIs and programming frameworks that solve some aspect of the problem we are examining. We examine their characteristics in this section. RouteBricks [19] defines a vision for using a cluster of PCs to process up to 35 Gbps of traffic in a software router. We aim at more modest targets using a single PC. Routebricks exploits parallelism in multi-core architectures by having each core dedicated to performing network processing for a single NIC queue rather than pipelining. They are targeting applications where there is little processing at each node and network I/O is the bottleneck. We are more concerned with applications that are dominated by application processing.

The Click [30] framework provides a library of predefined elements for common networking tasks that can be composed into a complete application using the Click language. Additional functionality can be added by writing new elements in C++that conform to the Click framework. One disadvantage is that it requires a programmer to learn the Click language to write applications. Another disadvantage of Click is that the framework for writing new elements is written in C++, which is not usually available for embedded platforms such as network processors. While Click configurations are potentially portable if a Click implementation that includes the elements used in the configuration is already available for the target platform, the implementation of new elements is not. Implementing new protocols (for example, [49]) not supported by existing Click elements is difficult to do in a portable fashion. The NP-Click [47] project created a Click implementation for the IXP network processors, but the underlying element implementations were rewritten in IXP-C, and the interface for writing new elements is incompatible with the original Click.

There are various solutions for easing the programming of NPs that abstract away some of the difficulties of programming in a low-level environment. These include Shangri-la [12] and the Intel auto-partitioning compiler [16]. These are C-based solutions, but they both run only on Intel's IXP network processor. Shangri-la's Baker programming language is platform-independent, but it is not truly portable because no implementations exist for other platforms.

Another proposed solution is NetVM [17], a virtual machine for network processing. NetVM attempts to define a virtual machine with its own virtual instruction set. An interpreter or compiler can take this generated byte code and run it on a specific platform. The authors define an architecture for this virtual machine, but not a programming model. Moreover, the prototype performs rather poorly. It took 2236 clock cycles to perform an IPv4 filtering task that took a Berkeley Packet Filter implementation 124 clocks to perform.

Recently, Juniper began offering third parties the ability to program their routers through their Partner Solution Development Platform (PSDP) [36], which provides a framework on top of the JUNOS operating system running on their routers. This solution apparently provides a uniform framework for all Juniper routers, but there is not much information publicly available. However, it demonstrates that companies are beginning to see the advantages of opening up their router platforms to thirdparties.

Finally, projects such as XORP [28] pursue a complementary goal. XORP is an interface for control-plane processing, which runs above the data plane. XORP can work using different data-plane implementations, including Click. It could also potentially implement the data plane using the interface we will introduce in this chapter.

## 4.3 NRTE

The Network Runtime Environment (NRTE) is our implementation of a multi-core oriented, network programming environment. It is implemented as a C library, which presents programmers with a familiar programming language that is portable across many platforms. It is explicitly designed to allow programmers to expose as much parallelism as possible in their programs while leaving the details of mapping to the underlying hardware threads up to the runtime.

The NRTE requires the user to handle parallelism. It is the programmer's responsibility to break the application into stages and to make these stages thread-safe. The application is organized as a pipeline with stages communicating with each other over queues. The runtime is responsible for mapping these stages onto the underlying hardware. Additional parallel computing resources are taken advantage of by duplicating stages and splitting the incoming packet flows among these duplicates. The user specifies the hardware mapping using a control program. The NRTE provides two types of stages: explicit and implicit. The explicit stages are threads under explicit user control; they launch and run to completion much like a thread created using the pthreads library. Implicit stages are registered as callback functions on an associated queue. The registered function is called by the runtime to process elements on that queue. The instantiation of implicit stages is left to the runtime; if the user indicates that the implicit stage is safe to duplicate (i.e., is thread-safe), the runtime can create duplicates of that stage to run on multiple hardware threads. Packets are distributed among the duplicates using flow-pinning. The user specifies the flow definition via a classification function. The runtime uses this function to send packets of the same flow to the same stage, so they can be processed in order and take advantage of cache locality for flow-specific data structures. Parallelism is achieved by processing different flows on different threads. The use of implicit stages in this manner allows us to scale the application to take advantage of increasing numbers of cores on future processors.

The NRTE's strategy for dealing with multi-threading differs from Click's. Click creates a task list for its configuration and load-balances the tasks across cores. This does not take into account caching effects, and it has a fixed amount of parallelism. If there are more hardware threads than tasks, Click cannot make use of them. By repeatedly duplicating the bottleneck stage(s), the NRTE actually creates parallelism, which can potentially scale to as many threads as are provided by the hardware.

We confirmed the usefulness of flow-pinning by creating an application that mimics the access pattern of stateful packet-processing applications. This application receives incoming elements and accesses and modifies state associated with that elements flow. We measured the time it took the application to process a fixed number of elements; we found that when flow-pinning was used to distribute the incoming data, the application ran in 12.04 seconds. When the incoming data was distributed without regard to flow, it took 16.19 seconds. This is due mostly to cache-thrashing. Our micro-benchmark does not include the cost of locking, which would likely be needed to prevent data corruption in a real application. Including this would further improve the flow-pinning results because it eliminates the lock synchronization overheads incurred without flow-pinning when multiple threads attempt to access the same flow state.

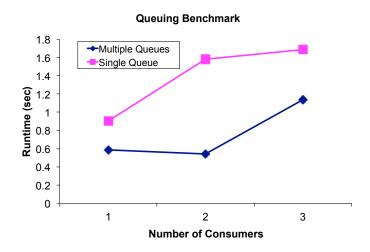

Figure 4.2: Queuing Benchmark

When a stage is duplicated, the underlying queues used to connect that stage to the rest of the pipeline are also duplicated. This is done to prevent synchronization overheads that would result if there were only one underlying queue with multiple replicas trying to read from it. When an implicit stage is duplicated by the runtime, there will be more than one consumer on that stage's queue. A simple way to maintain integrity of the underlying queue would be to use mutual exclusion locks to allow atomic access to a single producer or consumer at a time, but we observed that this quickly became the program's bottleneck. Instead, by implementing the logical queue abstraction as a set of point-to-point queues with a single producer and a single consumer each, we remove this necessity. The underlying physical queues do not require locks. Figure 4.2 shows a micro-benchmark we constructed comparing the use of the NRTE's queuing strategy of single consumer/producer circular buffers with an implementation where a single queue (still a circular buffer) is shared among multiple consumers, requiring synchronization with locks. The program has a single producer enqueuing items onto a queue and we measured the time it took for the consumers to dequeue all of them. The producer was producing while the consumer was simultaneously consuming. We varied the number of consumers from one to three, mapping a single producer or consumer to each core in our test system until we ran out of cores. The data points shown are representative of the observed performance but are not deterministic. The data show that the single-queue implementation, which requires lock synchronization for each enqueue or dequeue, performs far worse than the multiple-queues implementation. In addition, as we vary the number of consumers, the single-queue implementation scales poorly. The multiple-queues implementation scales well; no change in performance is observed between the one- and two-consumer cases. When moving to three consumers, performance degrades, but not for queuing reasons; the third consumer is placed on a core that shares an L2 cache with the producer, resulting in cache-capacity problems.

The NRTE also includes a packet abstraction and libraries to deal with common packet-processing tasks. Packet-handling abstractions allow the user to write platformindependent code, so that running NRTE-derived programs that must run in different environments does not require extensive rewrites. For example, in different situations, the same application may be run as a user space program that manipulates packets using sockets; or as a Linux kernel module that directly manipulates packets in *skbuffs*, the kernel's data structure for storing packet and meta data information. Libraries that provide common functions such as check-summing or efficient algorithms for longest prefix match will allow programmers to concentrate on what is unique to their programs rather than reinventing the wheel. Finally, putting efficient implementations for common data structures into the framework provides both the convenience and the ability to take advantage of underlying hardware support without programmer intervention. An example of this is data encryption. Hardware support exists for this on specialized platforms such as the Tolopai [3]. On older x86 platforms this is not present, but efficient software implementations, will be substituted.

| Function Name                        | Description                                       |

|--------------------------------------|---------------------------------------------------|

| rte_register_explicit_input_function | Create a stand-alone thread                       |

| rte_register_queue                   | Create a queue and register it's handler function |

| rte_enqueue                          | Enqueue an element to a queue                     |

| rte_start                            | Start runtime after all elements are registered   |

Table 4.2: NRTE API Summary

Table 4.2 contains a summary of the NRTE API. A complete listing is given in appendix A. We will illustrate the workings of the NRTE with an example. Our example begins with the following code snippet:

$\min()$  {

a = A();

```

b = B(a);

C(b);

```

Where A(), B(), and C() are functions that perform packet-processing operations. This can be turned into a pipeline, with dataflow illustrated in Figure 4.3 using the NRTE with the following code:

```

nrte_queue_id_t q1, q2;

void A(void *ignored)

//Do A's work, then send on

{

uint64_t A_elem;

nrte_enqueue(q1, A_elem);

}

void B(uint64_t stage_id, unsigned int flow_id, uint64_t A_elem)

//Do B's work, then send on

{

uint64_t B_elem;

nrte_enqueue(q2, B_elem);

}

void C(uint64_t stage_id, unsigned int flow_id, uint64_t B_elem)

//Do C's work

ł

}

unsigned int flow_classifier(uint64_t elem)

//dummy function. Simply returns input

{

return (unsigned int)elem;

}

main()

{

//Create the flow graph in the NRTE

q2=nrte_register_queue(C, flow_classifier);