### Washington University in St. Louis Washington University Open Scholarship

All Computer Science and Engineering Research

Computer Science and Engineering

Report Number: WUCS-2006-23

2006-05-01

# Timed Automata Models for Principled Composition of Middleware

Venkita Subramonian

Middleware for Distributed Real-time and Embedded (DRE) systems has grown more and more complex in recent years due to the varying functional and temporal requirements of complex real-time applications. To enable DRE middleware to be configured and customized to meet the demands of different applications, a body of ongoing research has focused on applying model-driven development techniques to developing QoS-enabled middleware. While current approaches for modeling middleware focus on easing the task of as-assembling, deploying and configuring middleware and middleware-based applications, a more formal basis for correct middleware composition and configuration in the context of individual applications is needed.... Read complete abstract on page 2.

Follow this and additional works at: https://openscholarship.wustl.edu/cse\_research

#### **Recommended Citation**

Subramonian, Venkita, "Timed Automata Models for Principled Composition of Middleware" Report Number: WUCS-2006-23 (2006). *All Computer Science and Engineering Research*. https://openscholarship.wustl.edu/cse\_research/914

Department of Computer Science & Engineering - Washington University in St. Louis Campus Box 1045 - St. Louis, MO - 63130 - ph: (314) 935-6160.

This technical report is available at Washington University Open Scholarship: https://openscholarship.wustl.edu/ cse\_research/914

#### Timed Automata Models for Principled Composition of Middleware

Venkita Subramonian

#### **Complete Abstract:**

Middleware for Distributed Real-time and Embedded (DRE) systems has grown more and more complex in recent years due to the varying functional and temporal requirements of complex real-time applications. To enable DRE middleware to be configured and customized to meet the demands of different applications, a body of ongoing research has focused on applying model-driven development techniques to developing QoS-enabled middleware. While current approaches for modeling middleware focus on easing the task of as-assembling, deploying and configuring middleware and middleware-based applications, a more formal basis for correct middleware composition and configuration in the context of individual applications is needed. While the modeling community has used application-level formal models that are more abstract to uncover certain flaws in system design, a more fundamental and lowerlevel set of models is needed to be able to uncover more subtle safety and timing errors introduced by interference between application computations, particularly in the face of alternative concurrency strategies in the middleware layer. In this research, we have examined how detailed formal models of lower-level middle-ware building blocks provide an appropriate level of abstraction both for modeling and synthesis of a variety of kinds of middleware from these building blocks. When combined with model checking techniques, these formal models can help developers in composing correct combinations of middleware mechanisms, and configuring those mechanisms for each particular application.

Department of Computer Science & Engineering

2006-23

### Timed Automata Models for Principled Composition of Middleware, Doctoral Dissertation May 2006

Authors: Venkita Subramonian

Corresponding Author: venkita@ieee.org

Web Page: http://www.cse.wustl.edu/~venkita/mw\_models/

Abstract: Middleware for Distributed Real-time and Embedded (DRE) systems has grown more and more complex in recent years due to the varying functional and temporal requirements of complex real-time applications. To enable DRE middleware to be configured and customized to meet the demands of different applications, a body of ongoing research has focused on applying model-driven development techniques to developing QoS-enabled middleware.

While current approaches for modeling middleware focus on easing the task of assembling, deploying and configuring middleware and middleware-based applications, a more formal basis for correct middleware composition and configuration in the context of individual applications is needed. While the modeling community has used application-level formal models that are more abstract to uncover certain flaws in system design, a more fundamental and lower-level set of models is needed to be able to uncover more subtle safety and timing errors introduced by interference between application computations, particularly in the face of alternative concurrency strategies in the middleware layer.

In this research, we have examined how detailed formal models of lower-level middleware building blocks

Notes: This research was supported in part by NSF CAREER award CCF-0448562. The timed automata models in

Type of Report: Other

Department of Computer Science & Engineering - Washington University in St. Louis Campus Box 1045 - St. Louis, MO - 63130 - ph: (314) 935-6160

### WASHINGTON UNIVERSITY THE HENRY EDWIN SEVER GRADUATE SCHOOL DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

### TIMED AUTOMATA MODELS FOR PRINCIPLED COMPOSITION OF MIDDLEWARE

by

Venkita Subramonian

Prepared under the direction of Professor Christopher Gill

A dissertation presented to the Henry Edwin Sever Graduate School of Washington University in partial fulfillment of the requirements for the degree of

DOCTOR OF SCIENCE

May 2006

Saint Louis, Missouri

### WASHINGTON UNIVERSITY THE HENRY EDWIN SEVER GRADUATE SCHOOL DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING

#### ABSTRACT

### TIMED AUTOMATA MODELS FOR PRINCIPLED COMPOSITION OF MIDDLEWARE

by

Venkita Subramonian

ADVISOR: Professor Christopher Gill

May 2006

Saint Louis, Missouri

Middleware for Distributed Real-time and Embedded (DRE) systems has grown more and more complex in recent years due to the varying functional and temporal requirements of complex real-time applications. To enable DRE middleware to be configured and customized to meet the demands of different applications, a body of ongoing research has focused on applying model-driven development techniques to developing QoS-enabled middleware.

While current approaches for modeling middleware focus on easing the task of assembling, deploying and configuring middleware and middleware-based applications, a more formal basis for correct middleware composition and configuration in the context of individual applications is needed. While the modeling community has used application-level formal models that are more abstract to uncover certain flaws in system design, a more fundamental and lower-level set of models is needed to be able to uncover more subtle safety and timing errors introduced by interference between application computations, particularly in the face of alternative concurrency strategies in the middleware layer.

In this research, we have examined how detailed formal models of lower-level middleware building blocks provide an appropriate level of abstraction both for modeling and synthesis of a variety of kinds of middleware from these building blocks. When combined with model checking techniques, these formal models can help developers in composing correct combinations of middleware mechanisms, and configuring those mechanisms for each particular application.

# Contents

| Li            | st of | Tables   ····································                        | vi  |

|---------------|-------|----------------------------------------------------------------------|-----|

| $\mathbf{Li}$ | st of | Figures                                                              | vii |

| A             | cknov | wledgments                                                           | xii |

| 1             | Intr  | $\mathbf{roduction}$                                                 | 1   |

|               | 1.1   | Motivation                                                           | 2   |

|               | 1.2   | Interference example                                                 | 4   |

|               |       | 1.2.1 Interference from DOC middleware                               | 6   |

|               |       | 1.2.2 ORB Reply Wait Strategies                                      | 7   |

|               | 1.3   | Challenges in Modeling DRE systems                                   | 12  |

|               | 1.4   | Research Contributions                                               | 13  |

|               | 1.5   | Dissertation Organization                                            | 16  |

| <b>2</b>      | Sur   | vey of Related Work                                                  | 18  |

|               | 2.1   | Model Integrated Computing                                           | 19  |

|               |       | 2.1.1 Applying MIC to DRE systems modeling                           | 19  |

|               | 2.2   | Model-driven Middleware                                              | 22  |

|               | 2.3   | Formal techniques in concurrent and component-based systems          | 24  |

|               | 2.4   | Middleware Frameworks and Execution Environments                     | 26  |

| 3             | Mic   | Idleware Modeling Overview                                           | 29  |

|               | 3.1   | System Model and Problem Definition                                  | 30  |

|               | 3.2   | Middleware Modeling Architecture                                     | 35  |

|               | 3.3   | Summary                                                              | 39  |

| 4             | Mo    | dels in UPPAAL                                                       | 40  |

|               | 4.1   | Realization of the Middleware Modeling Architecture in UPPAAL $$ .   | 40  |

|               | 4.2   | Modeling Foundational Data Structures and Functions $\ .\ .\ .\ .$ . | 42  |

| 4.3 Modeling Issues in UPPAAL |     | ing Issues in UPPAAL |                                                                                                                                                      |

|-------------------------------|-----|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

|                               |     | 4.3.1                | Maximal Progress in UPPAAL 45                                                                                                                        |

|                               |     | 4.3.2                | Constraining the State Space with Maximal Progress 48                                                                                                |

|                               | 4.4 | UPPA                 | AL Models of Middleware Building Blocks                                                                                                              |

|                               |     | 4.4.1                | IPC Channel                                                                                                                                          |

|                               |     | 4.4.2                | Select Reactor                                                                                                                                       |

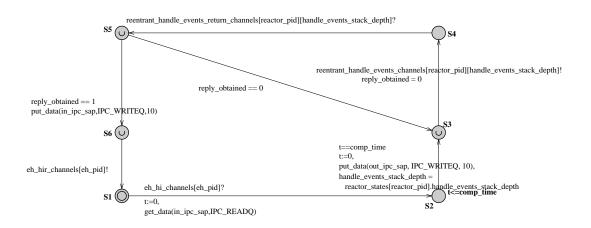

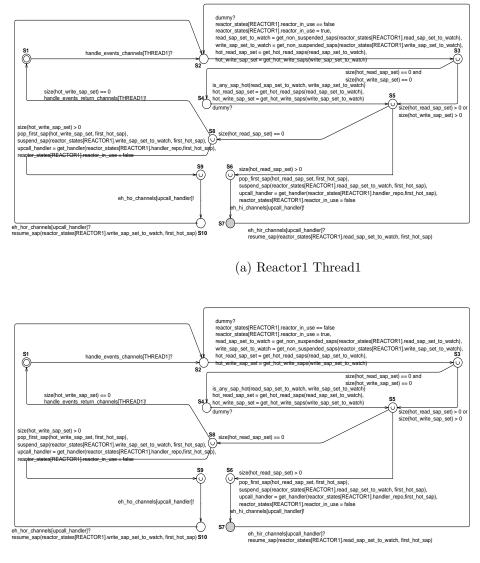

|                               |     | 4.4.3                | Reentrant Select Reactor                                                                                                                             |

|                               |     | 4.4.4                | ThreadPool Reactor                                                                                                                                   |

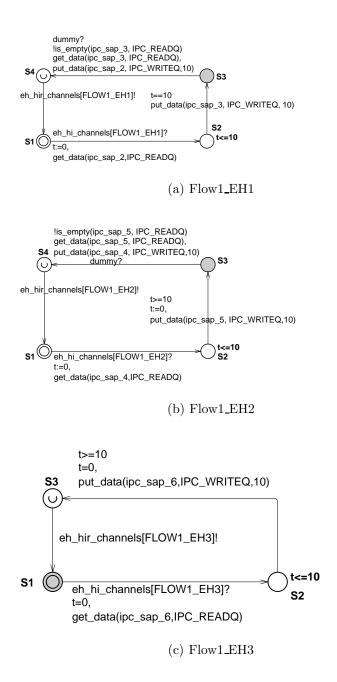

|                               |     | 4.4.5                | Event Handler $\ldots \ldots \ldots$ |

|                               |     | 4.4.6                | Composition of models                                                                                                                                |

|                               | 4.5 | Limita               | ations of Modeling Middleware in UPPAAL                                                                                                              |

|                               | 4.6 | Summ                 | $ary \ldots \ldots$           |

| <b>5</b>                      | Mo  | dels in              | the IF Toolset                                                                                                                                       |

| 0                             | 5.1 |                      | ation of the Middleware Modeling Architecture in IF 66                                                                                               |

|                               | 5.2 |                      | ing of Foundational Data structures and Operations                                                                                                   |

|                               | 0.1 | 5.2.1                | Foundational Operations Using IF ADTs                                                                                                                |

|                               |     | 5.2.2                | Foundational Operations Using IF procedures                                                                                                          |

|                               |     | 5.2.3                | Use of procedure calls as guards                                                                                                                     |

|                               | 5.3 | Model                | ing Middleware Building Blocks in IF                                                                                                                 |

|                               |     | 5.3.1                | IPC Channel                                                                                                                                          |

|                               |     | 5.3.2                | Select Reactor                                                                                                                                       |

|                               |     | 5.3.3                | Thread Pool Reactor                                                                                                                                  |

|                               |     | 5.3.4                | Event Handler                                                                                                                                        |

|                               | 5.4 | Prope                | rty specifications for verification                                                                                                                  |

|                               | 5.5 | Issues               | for Modeling Concurrent Object-Oriented Systems in IF 84                                                                                             |

|                               |     | 5.5.1                | Modeling Object Interactions in IF                                                                                                                   |

|                               |     | 5.5.2                | Modeling Threads in IF                                                                                                                               |

|                               |     | 5.5.3                | Modeling Priority Based Thread Scheduling in IF 86                                                                                                   |

|                               |     | 5.5.4                | Modeling Run-to-Completion Semantics                                                                                                                 |

|                               |     | 5.5.5                | Ordering Optimizations                                                                                                                               |

|                               | 5.6 | Summ                 | ary                                                                                                                                                  |

| 6                             | Rep | oresent              | ative examples                                                                                                                                       |

|                               | 6.1 | Exper                | imental Setup                                                                                                                                        |

|                               |     |                      |                                                                                                                                                      |

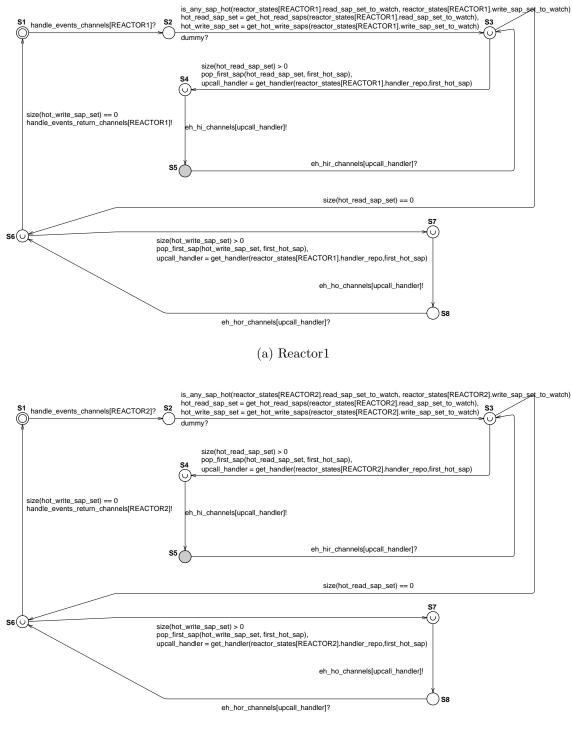

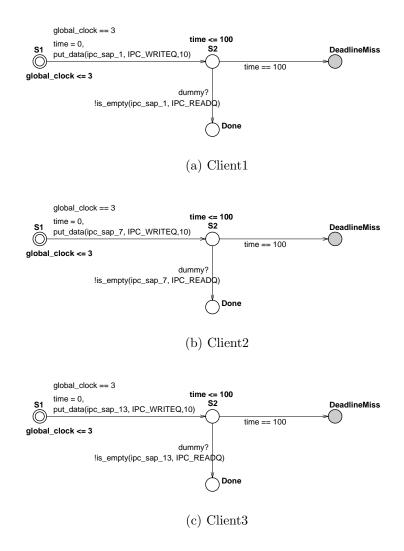

|   |     | 6.1.1   | Modeling the Scenarios in UPPAAL                                                                                                                   |

|---|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 6.1.2   | Modeling the Scenarios in IF                                                                                                                       |

|   | 6.2 | Execu   | tion Traces $\ldots \ldots \ldots$ |

|   |     | 6.2.1   | Execution Traces in UPPAAL                                                                                                                         |

|   |     | 6.2.2   | Execution Traces in IF                                                                                                                             |

|   | 6.3 | Scenar  | $ios \dots \dots$                            |

|   | 6.4 | Scenar  | tio 1 - Blocking in a Single Reactor                                                                                                               |

|   |     | 6.4.1   | Formal Analysis of Scenario 1 in UPPAAL                                                                                                            |

|   |     | 6.4.2   | Formal Analysis of Scenario 1 in IF                                                                                                                |

|   | 6.5 | Scenar  | tio 2 - Multiple Reactors, <i>WaitOnConnection</i> strategy 117                                                                                    |

|   |     | 6.5.1   | Formal Analysis of Scenario 2 in UPPAAL                                                                                                            |

|   |     | 6.5.2   | Formal Analysis of Scenario 2 in IF                                                                                                                |

|   | 6.6 | Scenar  | tio 3 – Multiple reactors, <i>WaitOnReactor</i> strategy                                                                                           |

|   |     | 6.6.1   | Formal Modeling of WaitOnReactor in UPPAAL 132                                                                                                     |

|   |     | 6.6.2   | Formal Modeling of WaitOnReactor using IF                                                                                                          |

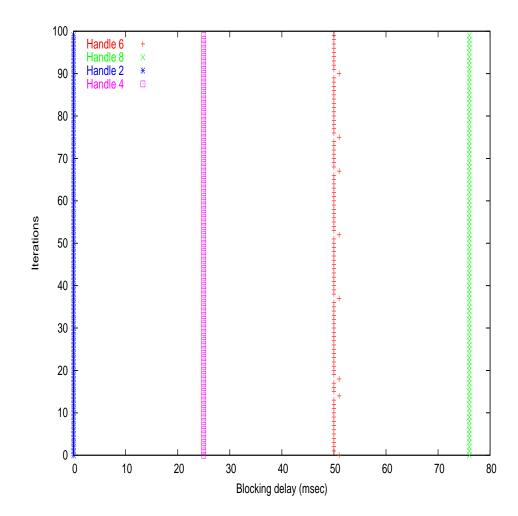

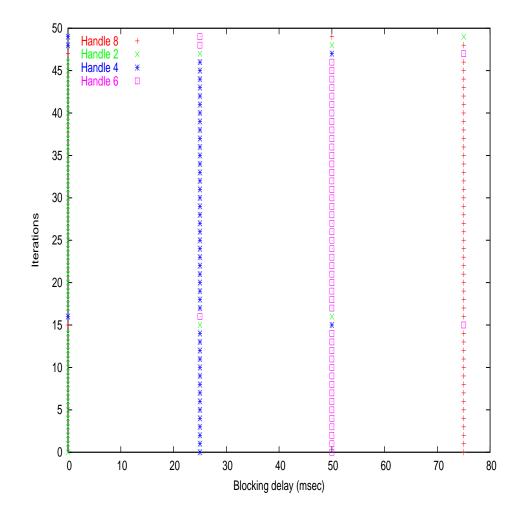

|   |     | 6.6.3   | Blocking Factors When Using WaitOnReactor                                                                                                          |

|   |     | 6.6.4   | Formal Analysis of WaitOnReactor Blocking Factor in UPPAAL140                                                                                      |

|   |     | 6.6.5   | Formal Analysis of WaitOnReactor Blocking Factor in IF 143                                                                                         |

|   | 6.7 | Scenar  | tio 4 – Multiple Reactors, Multiple threads                                                                                                        |

|   |     | 6.7.1   | Formal Analysis of Scenario 4 in UPPAAL                                                                                                            |

|   |     | 6.7.2   | Formal Analysis of Scenario 4 in IF                                                                                                                |

|   |     | 6.7.3   | Timing Anomaly and Solution                                                                                                                        |

|   | 6.8 | Model   | Checking Costs                                                                                                                                     |

|   |     | 6.8.1   | Impact of Data Structures in IF                                                                                                                    |

|   |     | 6.8.2   | Impact of State Space Optimization in IF 156                                                                                                       |

|   | 6.9 | Summ    | ary                                                                                                                                                |

| 7 | Mo  | del val | m idation                                                                                                                                          |

|   | 7.1 | Experi  | imental Setup $\ldots \ldots 159$                |

|   | 7.2 | Model   | Validation for Scenario 1                                                                                                                          |

|   |     | 7.2.1   | Co-Engineering of Model and Software                                                                                                               |

|   |     | 7.2.2   | Blocking Delay                                                                                                                                     |

|   | 7.3 | Model   | Validation of Scenario 2                                                                                                                           |

|   | 7.4 | Model   | Validation for Scenario 3                                                                                                                          |

|    | 7.5   | Model Validation for Scenario 4                                                                                                     |

|----|-------|-------------------------------------------------------------------------------------------------------------------------------------|

|    | 7.6   | Summary 166                                                                                                                         |

| 8  | Cas   | e Study 1 - Deadlock Avoidance Protocol                                                                                             |

|    | 8.1   | Overview of Deadlock Avoidance Protocols                                                                                            |

|    | 8.2   | Modeling and Implementation of DA Protocols                                                                                         |

|    |       | 8.2.1 Implementation of DA Protocols                                                                                                |

|    |       | 8.2.2 Modeling DA Protocol Support using IF                                                                                         |

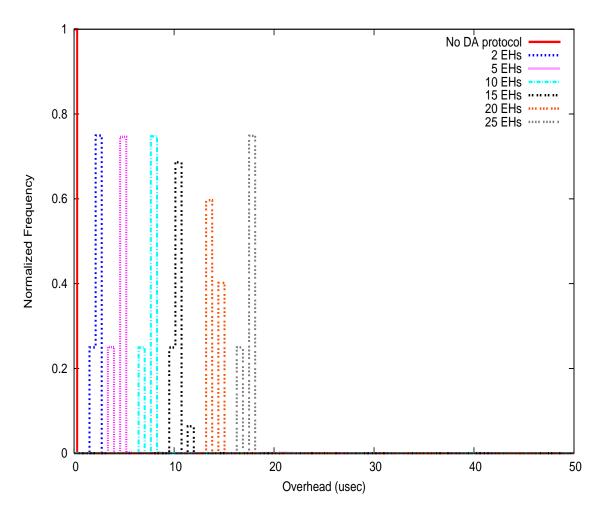

|    |       | 8.2.3 Deadlock Avoidance Protocol Overhead                                                                                          |

|    | 8.3   | Model Checking Deadlock Avoidance Protocols                                                                                         |

|    |       | 8.3.1 Model Verification of DA with BASIC-P                                                                                         |

|    | 8.4   | Deadlock Avoidance Blocking Delays 184                                                                                              |

|    | 8.5   | Summary 18                                                                                                                          |

| 9  | Cas   | e Study 2 - Application Gateway                                                                                                     |

|    | 9.1   | Overview of Application-level Gateway 189                                                                                           |

|    | 9.2   | Real-time Gateway                                                                                                                   |

|    |       | 9.2.1 High Level Modeling Using RMA                                                                                                 |

|    |       | 9.2.2 Design and Implementation                                                                                                     |

|    |       | 9.2.3 Evaluating Design Alternatives                                                                                                |

|    |       | 9.2.4 Empirical Validation                                                                                                          |

|    | 9.3   | Reliable Gateway with Control-Push-Data-Pull                                                                                        |

|    |       | 9.3.1 Reply Wait Using WaitOnConnection                                                                                             |

|    |       | 9.3.2 Reply Wait Using WaitOnReactor                                                                                                |

|    | 9.4   | Summary                                                                                                                             |

| 10 | ) Con | clusions and Future Work                                                                                                            |

|    | 10.1  | Summary of Contributions                                                                                                            |

|    |       | Future Work                                                                                                                         |

| R  | efere | $ m nces \ldots 214$                            |

| V  | ita . | $\ldots \ldots 22!$ |

# List of Tables

| 1.1 | Challenges and Solution Techniques Presented in This Research | 14  |

|-----|---------------------------------------------------------------|-----|

| 6.1 | Naming Conventions Used in Discussion of Scenarios            | 98  |

| 6.2 | Naming Convention in Post-processed Traces                    | 106 |

| 6.3 | Impact of data structures in IF on state space                | 154 |

| 6.4 | Impact of State Space Optimization                            | 156 |

| 9.1 | Periodic Tasks in the Gateway Example                         | 192 |

# List of Figures

| 1.1  | Remote Function Call as a Time and Event-driven Interaction $\ldots$ . | 4  |

|------|------------------------------------------------------------------------|----|

| 1.2  | Timeline for Mode1                                                     | 5  |

| 1.3  | Timeline for Mode2                                                     | 5  |

| 1.4  | Deployment Topology                                                    | 5  |

| 1.5  | Deadlock with WaitOnConnection Strategy                                | 9  |

| 1.6  | No Deadlock with WaitOnReactor strategy                                | 10 |

| 1.7  | Cause of Blocking Delay - Local view at ORB1                           | 11 |

| 1.8  | Effect of Blocking Delay - Global View                                 | 12 |

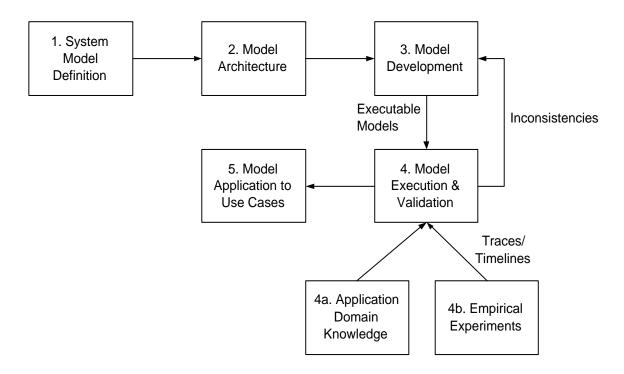

| 3.1  | Middleware Modeling Methodology                                        | 29 |

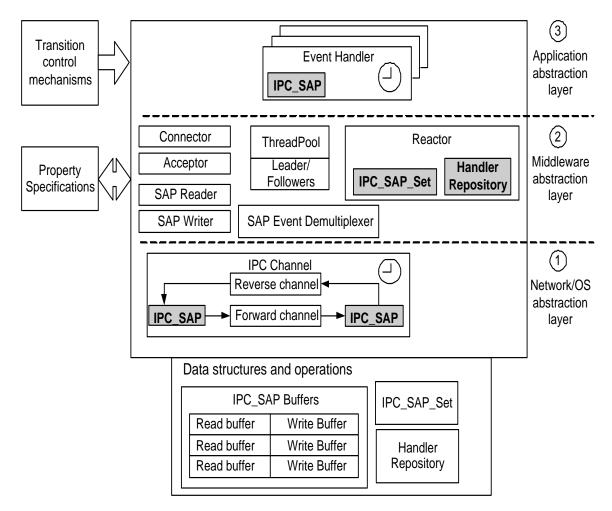

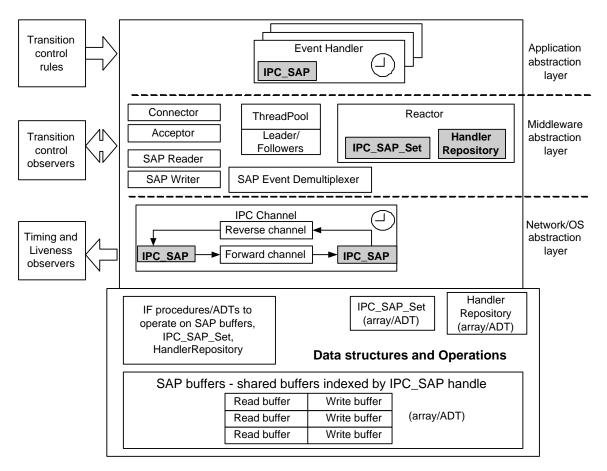

| 3.2  | Middleware Modeling Architecture                                       | 36 |

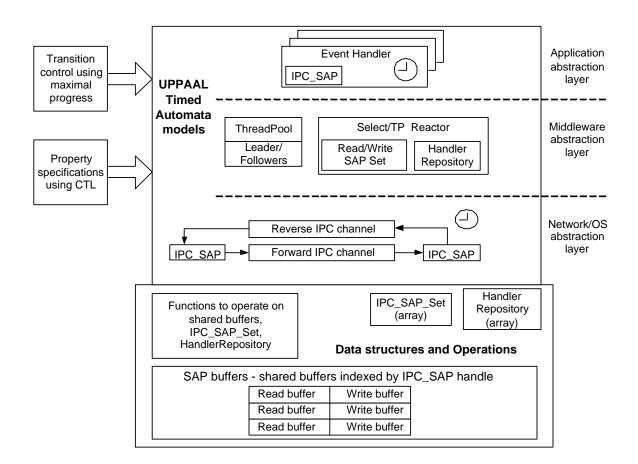

| 4.1  | Realization of the Modeling Architecture in UPPAAL                     | 41 |

| 4.2  | A Sampling of Foundational Data Structures                             | 43 |

| 4.3  | A Sampling of Foundational Functions                                   | 44 |

| 4.4  | Maximal Progress Example                                               | 47 |

| 4.5  | Maximal Progress Solution                                              | 50 |

| 4.6  | Model of an IPC Channel                                                | 51 |

| 4.7  | Instantiation of IPC Channel Automaton                                 | 52 |

| 4.8  | Model of Select Reactor                                                | 53 |

| 4.9  | Instantiation of Select Reactor Automaton                              | 53 |

| 4.10 | Model of a Reactor Thread                                              | 55 |

| 4.11 | Model of Reentrant Select Reactor                                      | 56 |

| 4.12 | Instantiation of Reentrant Select Reactor Automaton                    | 57 |

| 4.13 | Selecting from a Reentrant Select Reactor Stack                        | 57 |

| 4.14 | Model of ThreadPool Reactor                                            | 58 |

| 4.15 | Instantiation of ThreadPool Reactor Automaton                          | 59 |

| 4.16 | Event Handler                                                          | 60 |

| 4.17 | Composition of Models - Global Data Structures                         | 61 |

| 4.18 | Composition of Models - Channel Declarations                          | 61  |

|------|-----------------------------------------------------------------------|-----|

| 4.19 | Composition of Models - Instantiation of SAPs                         | 62  |

| 4.20 | Composition of Models - Event Handler Registration                    | 62  |

| 4.21 | Composition of Models - Instantiation of Models                       | 63  |

| 5.1  | Realization of the Modeling Architecture using IF                     | 67  |

| 5.2  | Modeling IPC SAP Buffers with ADTs in IF                              | 70  |

| 5.3  | C++ implementation of IPC SAP Buffers ADT outside IF model $\ . \ .$  | 71  |

| 5.4  | Modeling of IPC SAP Buffers with procedures in IF                     | 73  |

| 5.5  | Restrictions to Procedure Usage in IF                                 | 73  |

| 5.6  | Limitation with Usage of Procedures for Condition Wait                | 74  |

| 5.7  | Our solution to Condition Wait in IF                                  | 75  |

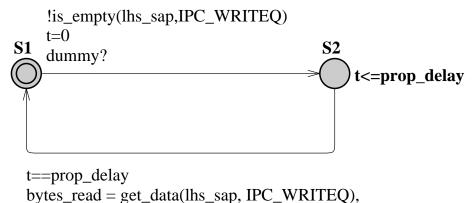

| 5.8  | Extracts from Channel Propagating Data between Two SAPs               | 76  |

| 5.9  | Extracts of Foundational Operations used by Select Reactor Model .    | 77  |

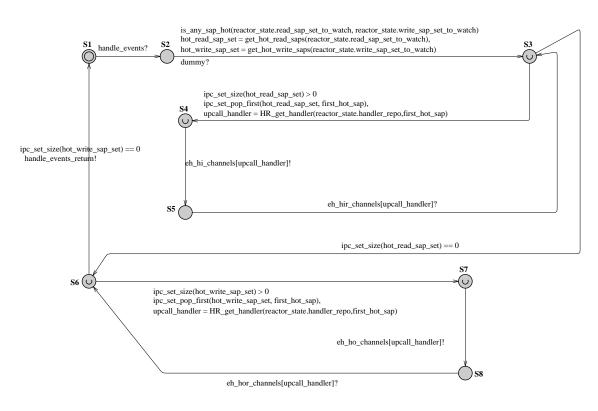

| 5.10 | Extracts from the IF Based Model for Select Reactor                   | 78  |

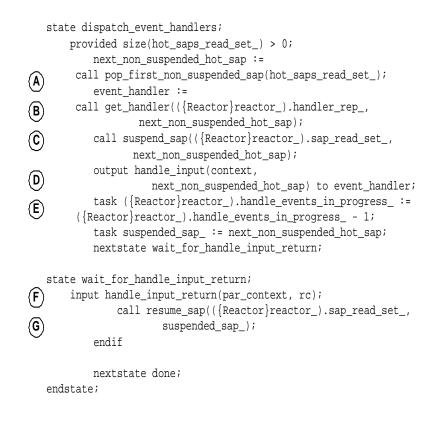

| 5.11 | Extracts from Thread Pool Reactor Model                               | 79  |

| 5.12 | Extracts from the Model of a Service Handler                          | 81  |

| 5.13 | Cut Observer Based System Property Specifications                     | 83  |

| 5.14 | IF Observer to Propagate Threadid                                     | 87  |

| 5.15 | IF Priority Rules to Model Thread Scheduling                          | 88  |

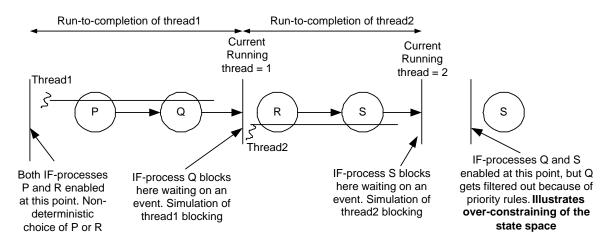

| 5.16 | Run-to-Completion Semantics for Two Threads                           | 89  |

| 5.17 | Priority Rules to Achieve Run-to-completion Semantics                 | 90  |

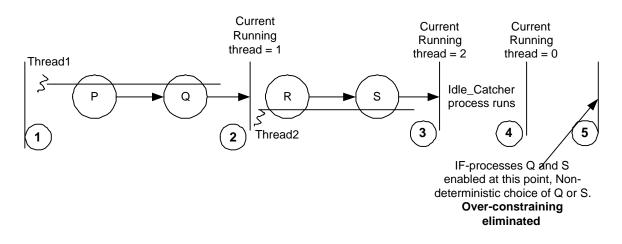

| 5.18 | Idle Catcher                                                          | 92  |

| 5.19 | Initialization Mode Priority Rule in IF                               | 94  |

| 5.20 | Priority Rule in IF for Leader/Followers ThreadPool                   | 95  |

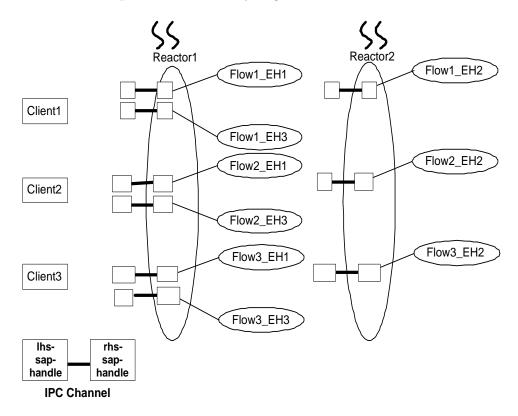

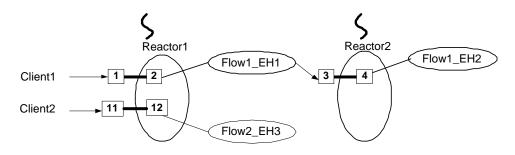

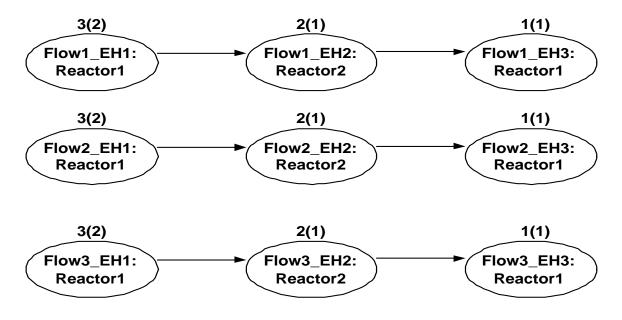

| 6.1  | Execution Setup for Scenarios                                         | 97  |

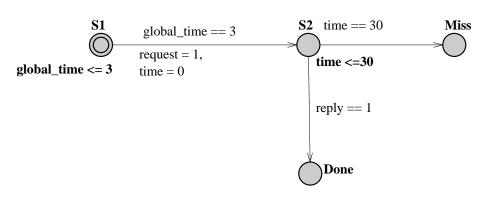

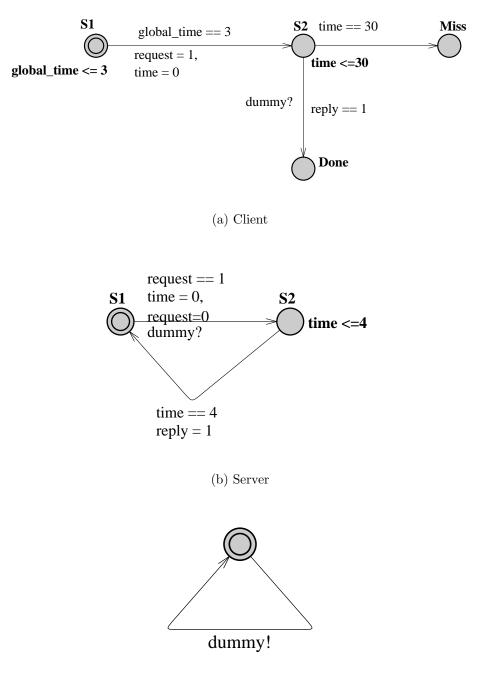

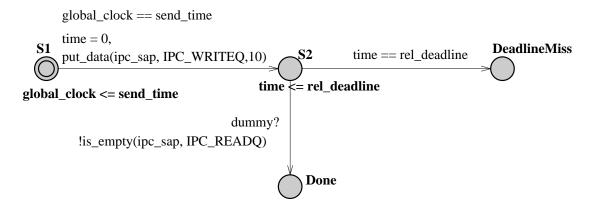

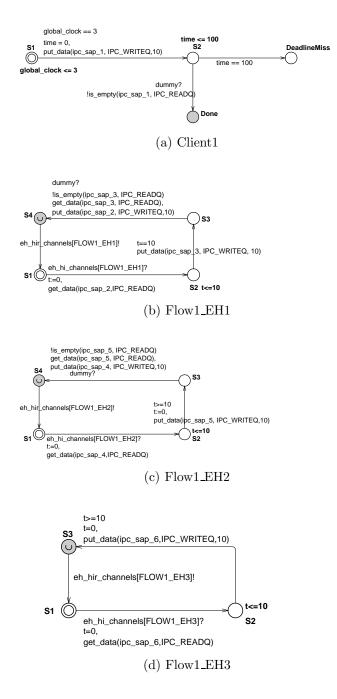

| 6.2  | Model of Client in UPPAAL                                             | 100 |

| 6.3  | IF based Test Harness                                                 | 101 |

| 6.4  | Trace Output from IF Model Execution                                  | 104 |

| 6.5  | Trace Output from IF Model Execution After Post-processing $\ldots$ . | 105 |

| 6.6  | Signal to Map IF Processid to a Name                                  | 106 |

| 6.7  | IF Trace Before Pid to Name Mapping                                   | 107 |

| 6.8  | IF Trace After Pid to Name Mapping                                    | 107 |

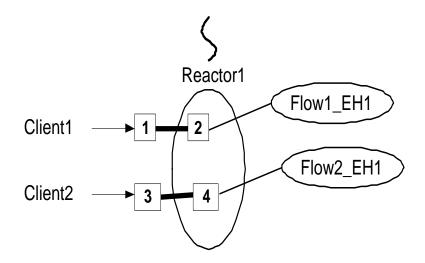

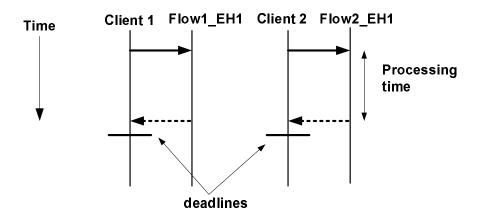

| 6.9  | Scenario 1 Setup                                                      | 108 |

| 6.10 | Call Sequence for Scenario 1                                              | 109 |

|------|---------------------------------------------------------------------------|-----|

| 6.11 | Instantiating Scenario 1 in UPPAAL                                        | 110 |

| 6.12 | Scenario 1 Trace in UPPAAL                                                | 112 |

| 6.13 | Scenario 1 Exhaustive Exploration in UPPAAL                               | 113 |

| 6.14 | Scenario 1 Trace in IF                                                    | 114 |

| 6.15 | Scenario 1 Trace in IF with Later Deadline                                | 115 |

| 6.16 | A Different Scenario 1 Trace in IF with Later Deadline                    | 116 |

| 6.17 | Scenario 1 Traces with New Log Event Added                                | 117 |

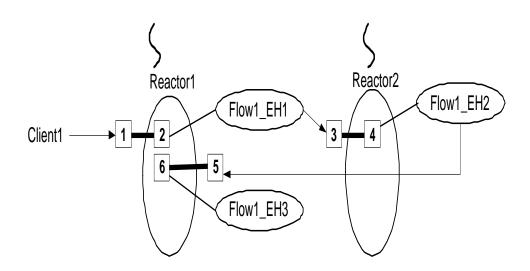

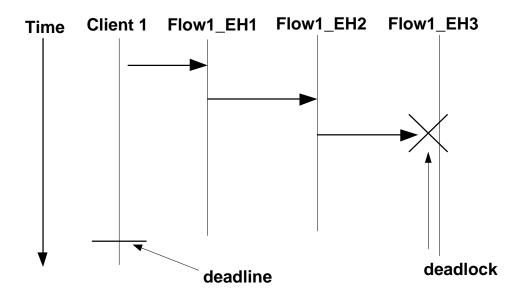

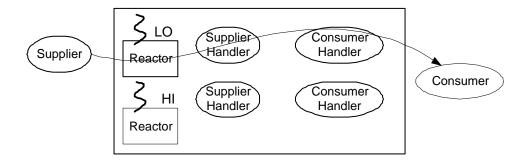

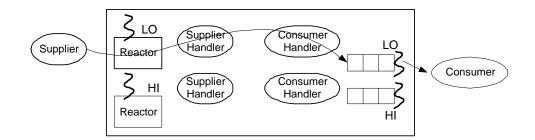

| 6.18 | Setup for Scenario 2                                                      | 118 |

| 6.19 | Call sequence for Scenario 2                                              | 119 |

| 6.20 | Scenario 2 Instantiation in UPPAAL                                        | 120 |

| 6.21 | UPPAAL verifyta output for Scenario 2 with 1 Thread                       | 120 |

| 6.22 | UPPAAL Trace Showing Sequence Leading to Deadlock                         | 121 |

| 6.23 | Scenario 2 Deadlock in UPPAAL - Reactor Automata States                   | 123 |

| 6.24 | Scenario 2 Deadlock in UPPAAL - Client and Event Handler Automata         |     |

|      | States                                                                    | 124 |

| 6.25 | Instantiation in UPPAAL for Scenario 2 with 2 Threads                     | 125 |

| 6.26 | Scenario 2 Deadlock in UPPAAL - TP-Reactor Automata States                | 126 |

| 6.27 | Scenario 2 in UPPAAL with No Deadlock - Client and Event Handler          |     |

|      | Automata States                                                           | 127 |

| 6.28 | Extracts from UPPAAL Trace Output for Scenario 2 with No Deadlock         | 128 |

| 6.29 | IF Trace Output for Scenario 2 Leading to Deadlock                        | 129 |

| 6.30 | IF Trace Output for Scenario 2 with 2 Threads - No Deadlock $\ . \ . \ .$ | 130 |

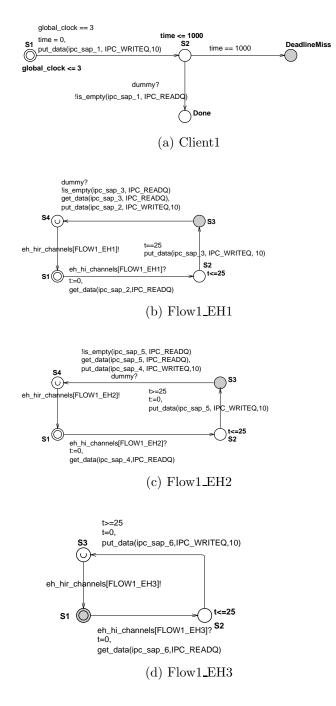

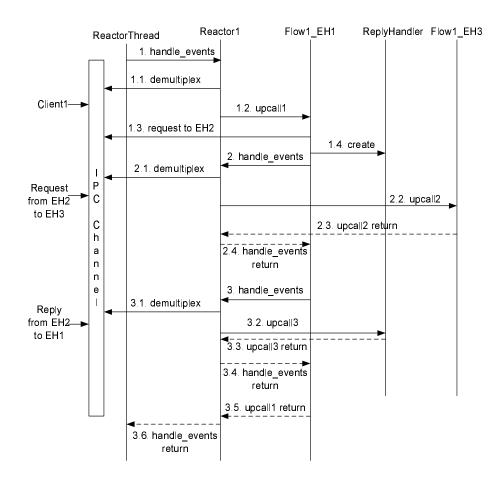

| 6.31 | Interaction diagram with WaitOnReactor strategy                           | 131 |

| 6.32 | Instantiation in UPPAAL for Scenario 2 with WaitOnReactor $\ . \ . \ .$   | 133 |

| 6.33 | Event Handler EH1 Waiting on Reactor for Reply from EH2 $\ . \ . \ .$     | 133 |

| 6.34 | UPPAAL verifyta output for Scenario 2 with WaitOnReactor                  | 134 |

| 6.35 | Extracts from the IF Model for an Event Handler using WaitOnReactor       |     |

|      | Reply Wait Strategy                                                       | 136 |

| 6.36 | IF Trace Output for Scenario 2 with WaitOnReactor                         | 137 |

| 6.37 | Setup for Scenario 3                                                      | 139 |

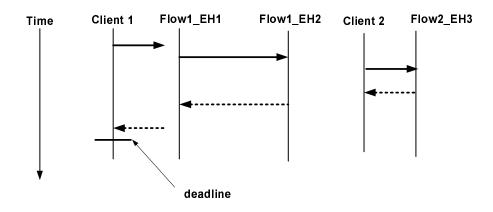

| 6.38 | Timeline for Scenario 3                                                   | 139 |

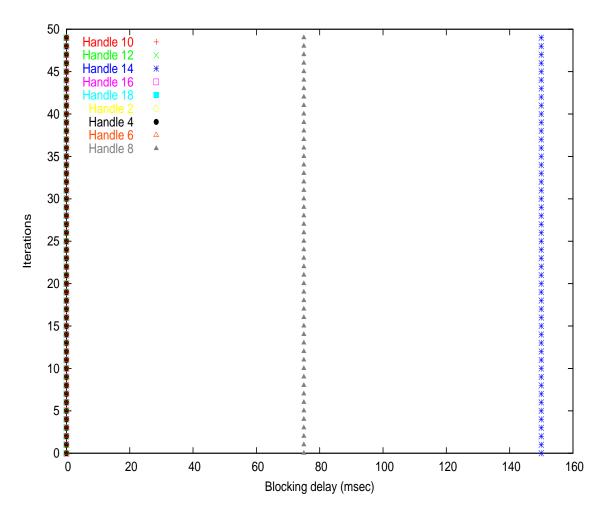

| 6.39 | Blocking delay with WaitOnReactor                                         | 141 |

| 6.40 | Model Instantiation in UPPAAL for Scenario 3                              | 141 |

| 6.41 | UPPAAL Trace Output for Scenario 3 Leading to a Deadline Miss                       | 142 |

|------|-------------------------------------------------------------------------------------|-----|

| 6.42 | IF Trace for Scenario 3 Leading to Deadline Miss with Reply in User                 |     |

|      | Buffer                                                                              | 143 |

| 6.43 | IF Trace for Scenario 3 Leading to Deadline Miss with Reply in Kernel               |     |

|      | Buffer                                                                              | 143 |

| 6.44 | Setup for Scenario 4                                                                | 144 |

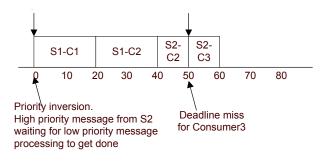

| 6.45 | Timeline for Scenario 4                                                             | 145 |

| 6.46 | Scenario 4 Deadlock in UPPAAL - Client Automata States                              | 146 |

| 6.47 | Scenario 4 Deadlock in UPPAAL - Reactor Automata States                             | 147 |

| 6.48 | Scenario 4 Deadlock in UPPAAL - Event Handler Automata States .                     | 148 |

| 6.49 | IF Trace for Scenario 4 Leading to Deadlock                                         | 150 |

| 6.50 | Model Modifications in IF to Fix Timing Anomaly                                     | 151 |

| 6.51 | IF Trace for Scenario 4 after Timing Anomaly Fix                                    | 152 |

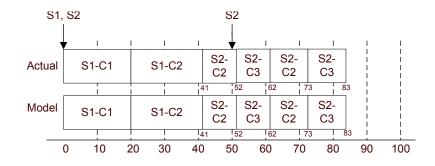

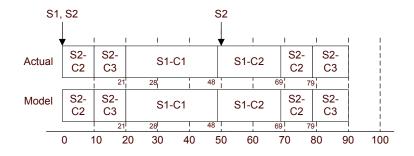

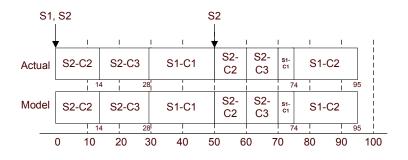

| 7.1  | Comparison of Timelines - Scenario 1                                                | 161 |

| 7.2  | Scenario 1 Blocking Factor from Actual Timeline                                     | 163 |

| 7.3  | Scenario 1 Blocking Factor from Simulation Timeline                                 | 164 |

| 7.4  | Comparison of Timelines - Scenario 2 Deadlock                                       | 165 |

| 7.5  | Comparison of Timelines - Scenario 2 No Deadlock                                    | 165 |

| 7.6  | Comparison of Timelines - Scenario 3 No Deadlock                                    | 166 |

| 7.7  | Comparison of Timelines - Scenario 4 Deadlock                                       | 167 |

|      |                                                                                     | 101 |

| 8.1  | Call graph annotations as per DA protocol                                           | 170 |

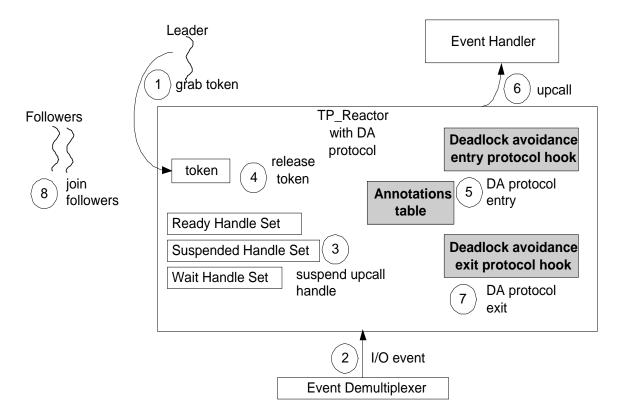

| 8.2  | Thread Pool Reactor with Deadlock Avoidance                                         | 172 |

| 8.3  | Extracts from the IF Model for TP Reactor with Deadlock Avoidance                   | 175 |

| 8.4  | DA Protocol Experiment Setup                                                        | 176 |

| 8.5  | DA Protocol Overhead                                                                | 177 |

| 8.6  | IF Trace Showing Deadlock in Scenario 2 with No DA Protocol                         | 178 |

| 8.7  | IF Trace Revealing a Bug in Our Model                                               | 180 |

| 8.8  | IF Trace Showing DA Protocol Avoiding Deadlock - Part 1                             | 181 |

| 8.9  | IF Trace Showing DA Protocol Avoiding Deadlock - Part 2                             | 182 |

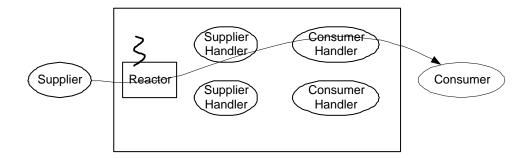

| 8.10 | Scenario 4 blocking delay Prediction from a Model Execution Trace $% \mathcal{A}$ . | 185 |

| 8.11 | Empirical confirmation of Scenario 4 blocking delay                                 | 186 |

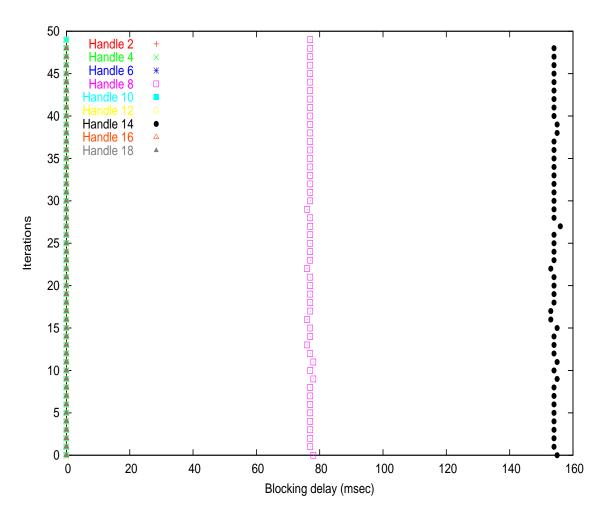

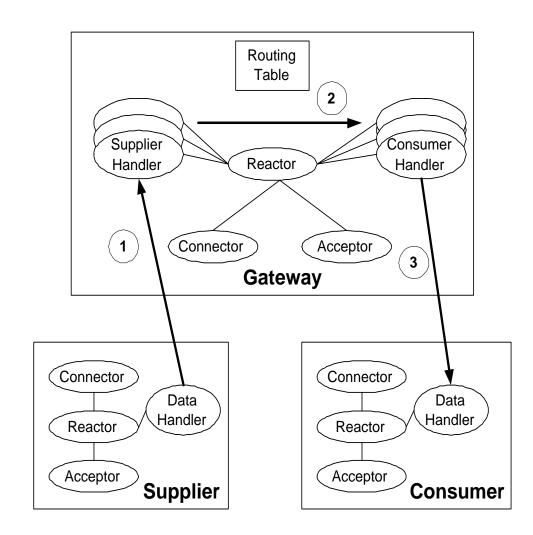

| 9.1  | Software Architecture of a Gateway                                                  | 190 |

| 9.2 | Gateway design alternatives                         | 195 |

|-----|-----------------------------------------------------|-----|

| 9.3 | Timelines from Model Execution                      | 196 |

| 9.4 | Comparision of Actual and Model Execution Timelines | 201 |

| 9.5 | Model Execution Trace with WaitOnConnection         | 203 |

| 9.6 | Relevant States at Deadlock with WaitOnConnection   | 204 |

| 9.7 | Actual Execution Trace with WaitOnConnection        | 204 |

| 9.8 | Model Execution Trace with WaitOnReactor            | 206 |

| 9.9 | Actual Execution Trace with WaitOnReactor           | 207 |

## Acknowledgments

First of all, I'd like to thank the lord of Guruvayoor who is the guiding light of my life. Thanks to my parents who taught me how to be a good human being. I am not sure how I would pay my wife back for her endless patience and support during the past five years during which we have seen several ups and downs in our lives. Radhika, thanks for being with me. Thanks to my son Keshav, who brought the utmost happiness in our lives when we needed it the most.

I am greatly indebted to my advisor Dr. Christopher Gill for giving me the opportunity to come to Washington University as a research staff member and do my PhD simultaneously. If not for his constant encouragement, patience and countless hours of discussions with him, I would not have surpassed this phase of my life. Thanks, Chris, for being a sincere friend and mentor. I thank my other committee members - Dr. Douglas Niehaus, Dr. Ron Cytron, Dr. Aaron Stump and Dr. Ron Indeck for their insightful questions and comments on my thesis. I thank Dr. Niehaus and his students Tejasvi Aswathanarayana, Hariharan Subramaniam, Noah Watkins and Andrew Boie for all their help and support with the DSKI/DSUI instrumentation toolset which was of immense help in my thesis. I would not be doing justice if I did not mention a special thanks to Tejasvi Aswathanarayana for acceding to my innumerable requests to reboot the testbeds at ITTC.

I thank Dr. Marius Bozga, Dr. Iulian Ober and Dr. Joseph Sifakis who helped me with the IF toolkit. I thank the UPPAAL newsgroup members who helped me with the UPPAAL toolkit. I would like to thank my collaborators Dr. Douglas Schmidt, Dr. Henny Sipma, Cesar Sanchez, Dr. Chenyang Lu, Dr. Kirby Keller, Dr. Douglas Stuart, Jeanna Gossett, Tom Corcoran and Gan Deng for their insightful discussions and suggestions regarding the projects on which we worked together.

I would like to thank Huang-Ming Huang for his support and especially for his numerous suggestions on my final defense presentation. Finally, I would like to thank my friends - Yuanfang Zhang, Xiaorui Wang, Terry Tidwell, Morgan Deters, Stephen Torri, Radu Handorean, Delvin Defoe, Nanbor Wang, Yamuna Krishnamurthy, Irfan Pyarali, Bala Natarajan, Jeff Parsons, Krishnakumar Balasubramaniam, Jaiganesh Balasubramaniam, Angelo Corsaro, Joe Hoffert, Dennis Noll, Roopa Pundaleeka, Pawan Mandalkar, Praveen Krishnamurthy, Cheng Huang and Frank Hunleth.

Venkita Subramonian

Washington University in Saint Louis May 2006

# Chapter 1

### Introduction

The following quote extracted from [2] gives a concise definition of modeling and design which is well applicable to the work in this dissertation.

"Modeling is the act of representing a system or subsystem formally. A model might be mathematical, in which case it can be viewed as a set of assertions about properties of the system such as its functionality or physical dimensions. A model can also be constructive, in which case it defines a computational procedure that mimics a set of properties of the system. Constructive models are often used to describe behavior of a system in response to stimulus from outside the system. Constructive models are also called executable models.

*Design* is the act of defining a system or subsystem. Usually this involves defining one or more models of the system and refining the models until the desired functionality is obtained within a set of constraints."

The research presented in this dissertation deals with the development of executable or constructive models of reusable middleware building blocks that are commonly used to implement distributed real-time and embedded (DRE) systems. These executable models of middleware building blocks, when used in conjunction with higher level application models, enables a faithful analysis of timing and liveness properties during system design.

### 1.1 Motivation

Significant research over the past decade has made middleware more customizable through the use of pattern-oriented software frameworks [51, 50]. Although this has made middleware solutions suitable for a wider range of applications, managing the resulting multiplicity of customization options has become an increasing concern. To allow middleware to be customized to meet the stringent demands of different distributed real-time and embedded (DRE) applications, recent research has focused on applying model-driven techniques to DRE middleware [6]. Although current modeldriven middleware approaches *facilitate* the correct assembly, deployment and configuration of DRE applications and middleware, we argue in this dissertation that a more detailed and formal basis for reasoning about timing and liveness properties in a variety of different middleware configurations is both desirable and possible.

Application-specific formal models have been used to uncover high-level design flaws early in system development [76, 108]. However, such models are currently difficult to maintain adequately as the system's specification is refined successively throughout the system development life-cycle. For example, decisions regarding the deployment of application components onto endsystems, or the choice of middleware concurrency strategies, often are not reflected in these high-level models. This may result in subtle timing and liveness hazards due to unexpected side-effects from *interference* from the middleware policies and mechanisms used by a set of distributed computations.

Interference. In general, the kind interference in DRE systems that we study occurs when part of a computation shares resources with or otherwise interacts with another part of a computation and in doing so impedes or obstructs its required progress. The interaction could happen at different levels - application level (*e.g.*, monitor objects), middleware level (*e.g.*, reactor, threadpool), OS level (*e.g.*, kernel buffers, file system data structures), or hardware level (CPU, network cards, CPU registers). Interference, if not controlled properly can produce undesirable side-effects in an application. For example, a non-critical computation executing on a CPU could interfere with a critical computation requiring the same CPU resource and thus cause the critical computation to miss a deadline. To control interference, the causes of interference at each layer must first be identified and analyzed and then appropriate steps must be taken to mitigate its effects. For example, schedulability analysis techniques like RMA [64, 58, 15, 62, 99] analyze the effects of interference among a set of periodic computations sharing a CPU. Register allocation techniques [16] in a compiler analyze the interference among variables that are live at the same time and hence cannot be allocated to the same CPU register. The focus of this research is to capture and analyze two specific forms of interference occurring because of sharing of reactors [91, 90] and thread pools in the middleware layer - (1) blocking delays at a reactor and (2) exhaustion of threads in a reactor thread pool. (1) occurs when a I/O event is being dispatched by a reactor to the appropriate event handler [91, 90] and another I/O event is waiting to be dispatched to its event handler by the same reactor. (2) occurs when all threads in a reactor thread pool are occupied processing events dispatched by that reactor and none of them are available further for the reactor to dispatch pending events. We provide a more formal definition of these forms of interference in Chapter 3.

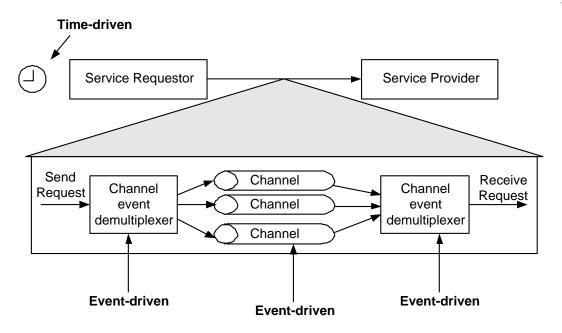

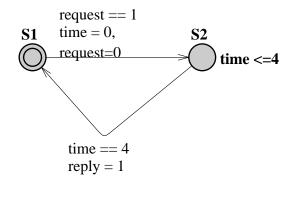

Figure 1.1 illustrates how a system that is specified with only time-driven constraints in its high-level model may be refined into a time and event-driven system during its design and implementation phases. In the high-level model, a purely time-triggered request is sent from a service requestor to a service provider through a middlewareimplemented remote function call. However, the implementation of this remote function call goes through multiple middleware, OS and network processing stacks, each of which likely contains event-driven system elements. For example, Figure 1.1 shows middleware based event demultiplexers on the sender and receiver side endsystems, which enable a single thread on each side to be used to demultiplex I/O events (e.q., packet arrivals and transmissions) from and onto multiple interaction channels (e.q., sockets and pipes). Even the interaction channels are likely to be event driven, for example when IP packets arrive and are moved from the network interface card into an application-accessible transport-layer buffer. This dissertation addresses the problem of modeling and analyzing interference arising from the semantically rich interactions between system software components of the middleware layer of the system software architecture, which we now illustrate using a concrete example in the context of an Object Request Broker (ORB) [75].

Figure 1.1: Remote Function Call as a Time and Event-driven Interaction

### **1.2** Interference example

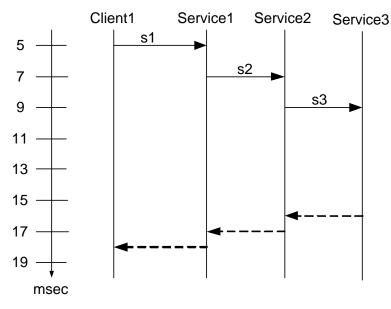

Consider an example application that consists of two clients and three services with two modes of operation - Mode1 and Mode2. In Mode1, illustrated in Figure 1.2, at 5msec from the start of system execution, Client1 calls Service1. After performing a computation that takes 2ms, Service2 calls Service3. Service3 performs a computation that takes 7ms and then replies back to Service2. Service2 does a computation for 1ms before replying back to Service1. Service1 also performs a computation for 1ms before replying back to Client1.

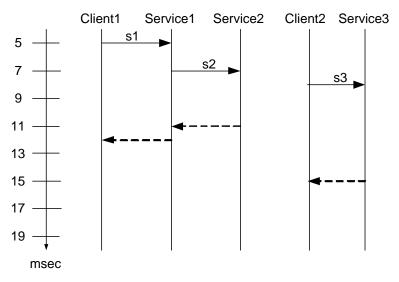

In Mode2, illustrated in Figure 1.3, the sequence of events and actions is similar to Mode1, except that Service2 does not call Service3. Instead, it does a computation for 4ms and replies back to Service1. Moreover, Client2 makes a call to Service3 at 8ms after the start of system execution (Note that Client2 does not run in Mode1).

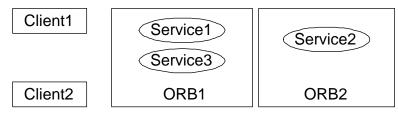

The example so far shows high-level models of interactions between concurrent system components. No decisions have been shown so far regarding the middleware/OS platform or the deployment topology. In this example, we choose the deployment topology shown in Figure 1.4.

Figure 1.2: Timeline for Mode1

Figure 1.3: Timeline for Mode2

Figure 1.4: Deployment Topology

In this deployment topology, Service1 and Service3 are hosted together and Service2 is hosted on another machine. We choose ORB middleware (e.g., TAO [50]) as the communication mechanism between the distributed components. Note that the decision to choose the deployment topology could be based on a variety of factors including resource constraints or application requirements. We contend that a gap exists between the high level model and the actual system, since the high level model does not consider the underlying infrastructure model, which as we describe next could result in problems because of interference in the middleware layer.

#### **1.2.1** Interference from DOC middleware

Middleware typically offers different strategies to configure infrastructure mechanisms. The correct choice of strategies is crucial not only for the functional behavior (delivering messages across sockets, waiting for replies, *etc.*) of the infrastructure, but also is required to maintain timing and liveness properties of the application. Some combinations of infrastructure strategies may have adverse impacts on the functioning of the application and yet current middleware modeling approaches do not consider the alternative configurations at a fine enough level of detail to be able to detect some forms of interference. In particular, the middleware infrastructure may itself introduce interference among computations in the application, possibly resulting in violation of application safety and liveness properties. In this section, we illustrate interference occurring in the ORB middleware layer in the context of a simple example that uses distributed objects communicating with each other to realize applicationlevel goals. Although the discussion here is based in particular on configurations of middleware mechanisms seen in the ORB core implementations in TAO [50] and nORB [105], such *interference* could occur in other implementations and other forms of middleware as well.

CORBA [74] based ORBs are used in many distributed systems with real-time constraints. Implementation of an ORB [50] involves mechanisms like Reactors and Leader-Follower thread pools (see Sidebar 1). While modeling DRE systems, it is necessary to consider key infrastructure mechanisms like the ORB core reactor, the pool of threads used to receive incoming GIOP [21] requests, and the topology of method invocations that generate outgoing GIOP requests. In this section we explain why this level of detail is important to verify correctness of the system with respect to timing and liveness properties. To support reuse of ORB middleware across a variety of domains and applications in those domains, ORB middleware often provides a wide set of configuration options so that it can be customized to suit the requirements of the application. In this section, we describe one such strategy used to configure the ORB core infrastructure – *Reply Wait Strategy* – to illustrate the importance of including this level of detail in a system model. In the course of this example, we show that the type of reply wait strategy chosen at one end-system affects the real-time characteristics as well as liveness properties of the application, and hence the reply wait strategy may contribute to interference in the system.

#### 1.2.2 ORB Reply Wait Strategies

In CORBA, when a client makes a remote two-way function call, the caller's thread needs to wait until it receives a reply back from the server before continuing to execute the calling method. This is in accordance with the semantics of a two-way function call. There are different strategies to wait for the reply, each having different implications for safety and liveness. To motivate the need for modeling and analysis of middleware mechanism configurations, consider two different strategies used in TAO and nORB to allow a client to wait for the reply from a server.

- WaitOnConnection the thread that sends the request waits directly on the connection for the reply

- WaitOnReactor the thread that sends the request waits on a subsequent upcall from the ORB core reactor, when the reply has arrived.

We now illustrate the impact of these strategies on the timing and liveness properties of the example distributed application. In the ORB literature, this kind of sequence of calls is termed "Nested Upcalls". Without loss of generality, we first assume that there is a single thread of execution in each of the servers.

#### Sidebar 1: Key Design Patterns in TAO and nORB

The architecture of TAO and nORB is based on the network programming patterns described in [97]. We outline the following fundamental patterns used in TAO and nORB that are relevant to the discussion in this dissertation:

- **Reactor** is an event handling design pattern used in network programming to demultiplex events from multiple sources, possibly using just a single thread. This design pattern is used in ORBs to demultiplex and dispatch incoming requests and replies from peer ORBs. Event handlers like request and reply handlers are registered with a reactor. The reactor uses a synchronous event demultiplexer, *e.g.*, the UNIX *select* system call, to wait for data to arrive from one or more ORBs. When data arrives, the synchronous event demultiplexer notifies the reactor, which then dispatches the appropriate registered event handler based on the event source.

- The Acceptor-Connector design pattern decouples connection establishment between ORBs and request/reply processing in an ORB end-system once a connection is established. A Connector actively establishes a connection with a remote acceptor component and an Acceptor passively waits for connection requests from remote connectors, establishing a connection upon arrival of such a request, and initializing a service handler to process data exchanged on the connection.

- Leader/Followers is an architectural design pattern that provides an efficient concurrency model where multiple threads take turns detecting, demultiplexing, dispatching, and processing requests and replies from peer ORBs.

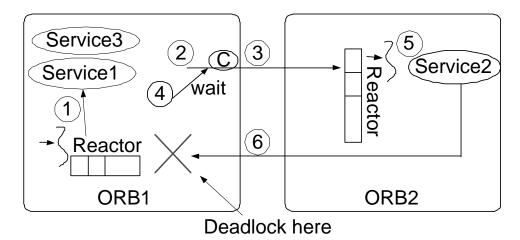

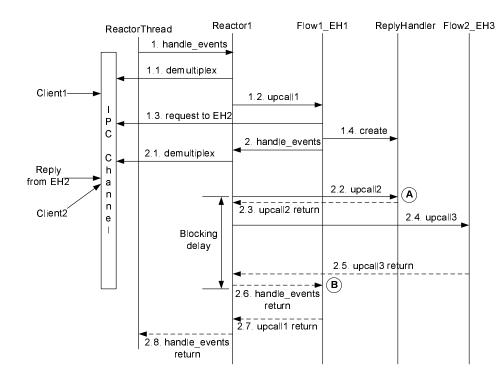

Wait on Connection. In this strategy, illustrated in Figure 1.5, the following sequence of events takes place within the ORB layer:

- 1. As the remote call from application component Client1 is processed by ORB1, it makes an upcall to the servant implementation for Service1. In the subsequent discussion, we assume that the upcall is made in the same thread as the I/O thread that was listening on connections for remote calls.

- 2. As part its implementation, Service1 makes a remote call to Service1. Internally, ORB1 actively establishes a connection C to ORB2.

Figure 1.5: Deadlock with WaitOnConnection Strategy

- 3. The parameters to the remote call are marshaled, a GIOP Request is formed and sent to ORB2 using connection C.

- 4. The sole I/O thread (that is also the upcall thread) in ORB1 waits for the reply on connection C using a blocking **recv** call.

- 5. The request is received by ORB2 and dispatched to the skeleton code for Service2. Service2 skeleton code marshals the parameters and the *upcall* is made to the servant.

- 6. The servant implementation for Service2 calls Service3. Internally ORB2 tries to establish a connection to ORB1 so that it could send this request.

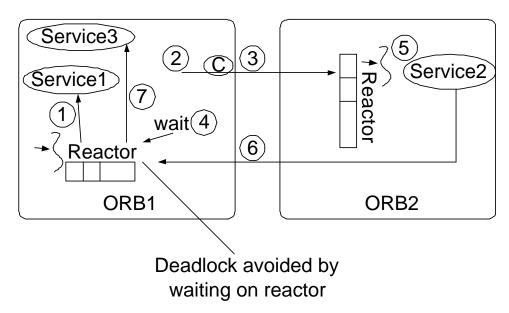

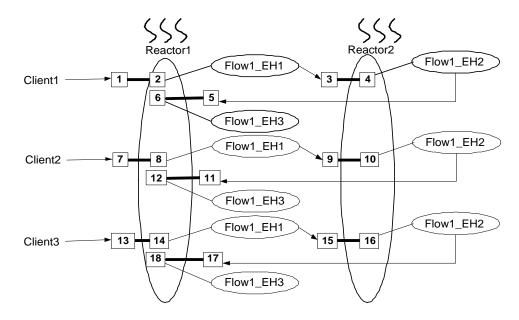

Since the sole I/O thread in ORB1 is blocked on a system call waiting for a reply from Service2, there is no thread to accept the incoming request. This results in a deadlock, where the ORB1 thread is waiting for a reply from Service2 and the ORB2 reactor thread executing Service2 is waiting for a reply from ORB1. Note that this situation occurs *only* because of interference in the middleware and *not* because of any conditions occurring in the OS layer. The situation can be improved by having a pool of threads listening for input requests using the Leader-Follower model (see Sidebar 1). But even with this model, when the number of outstanding requests exceeds the number of threads, the ORB ceases to accept any more requests and this can result in a deadlock as well, as we show in Section 6.7 in Chapter 6. Wait on Reactor. In this strategy, the sequence of calls is the same as the previous strategy until the request is written to the connection stream. After that, instead of waiting on the connection for the reply, the caller thread waits on the ORB core reactor, which provides synchronous demultiplexing of I/O events. This demultiplexing allows incoming requests to be accepted while waiting for replies (see Sidebar 1). The (nested) callback request from Service2 is accepted (7) and the call is completed eventually, thus avoiding deadlock (see Figure 1.6).

Figure 1.6: No Deadlock with WaitOnReactor strategy

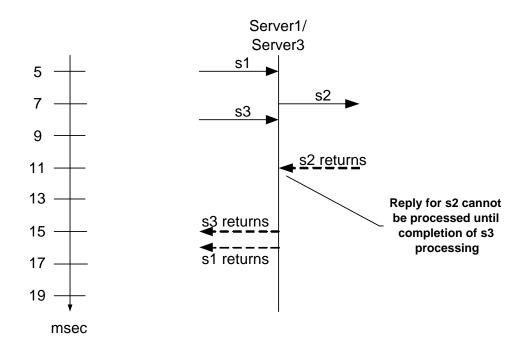

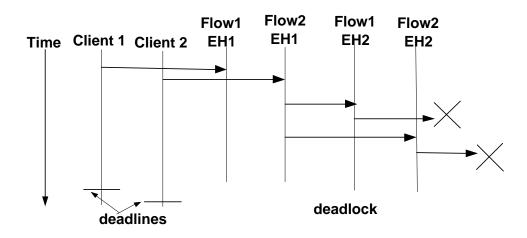

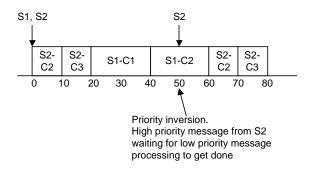

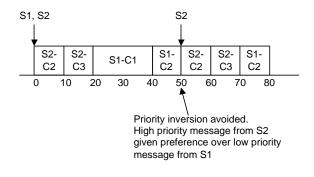

However this strategy introduces another form of interference in terms of *blocking delays*. It should be noted that the upcall for the incoming request is made in the same thread context as that of the outgoing call. There could be multiple incoming requests before the reply for the initial outgoing call arrives. The processing of the reply for the initial outgoing call can be done only after processing of all the incoming requests that arrived before its reply, is completed. This results in blocking delays in completion of outgoing remote calls. This is illustrated in Figure 1.7 in the context of the example application running in Mode2.

The timeline in Figure 1.7 shows the sequence of events that occurs at ORB1. When the reply from Service2 arrives at 11ms, there is no thread to process that reply, since the upcall thread is already servicing the request from Client2 to Service3. The reply from Service2 is processed only after the reply from Service3 is sent to

Figure 1.7: Cause of Blocking Delay - Local view at ORB1

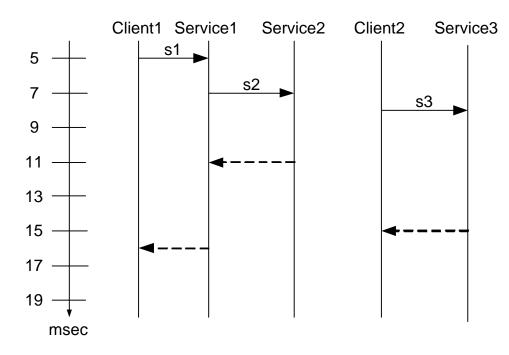

Client2. This introduces a blocking factor of 4ms in the processing of the reply from Service2 resulting in a delayed reply to Client1, which may violate a timing property of the application. The new timeline illustrating the interaction between the different services is shown in Figure 1.8, which shows the effect of the blocking delay shown in Figure 1.7. Figure 1.8 shows that only after the reply from Service3 is sent to Client2, the pending reply from Service2 is processed and a reply sent to Client1.

The above example illustrates two typical kinds of interference issues encountered in DRE middleware - interference in the form of (1) deadlock caused by a combination of factors *e.g.*, WaitOnConnection reply wait strategy and a single reactor thread in ORB1 and (2) blocking delays caused by WaitOnReactor strategy. This example reinforces the need to consider such issues when modeling real-time systems. It is therefore important to choose appropriate strategies carefully and at fine levels of detail in a middleware infrastructure. Depending on application characteristics, such as use of nested upcalls, this choice may affect liveness and timing properties as was shown in this example. Therefore, such details need to be taken into consideration to give a more faithful analysis of system models.

Figure 1.8: Effect of Blocking Delay - Global View

### **1.3** Challenges in Modeling DRE systems

The example in Section 1.2 illustrates the general concern that many of the abstractions used during high-level modeling, such as the notion of a purely time-driven or even a time-and-priority mediated interaction between the service requestor and the service provider, may become decreasingly representative of the system during its design and implementation. This may in turn result in a chasm between the high-level model and the actual implementation, *unless the abstractions used in the high level model can be refined during design and implementation*. Thus, a foundational set of formal models that can express both (1) high-level abstractions such as timed remote method invocations, and (2) low-level refinements such as concurrency and interaction semantics between the objects that implement the high-level model, is needed to support accurate verification of the high level model in terms of its low-level design and implementation.

Furthermore, the insights obtained from modeling and analysis should be made available and used while making design and development decisions, and vice-versa. Such a close correspondence between the system modeling, analysis, design and development activities offers the following benefits: (1) more complete, detailed and executable models of systems, including their middleware infrastructure, can be composed and checked; (2) timing and liveness properties can be verified with greater precision; (3) a more rigorous and formal style of documentation can be used to capture and communicate detailed middleware engineering expertise that is currently represented less formally, *e.g.*, as *design patterns* [97]; (4) with more representative models and more powerful verification techniques, the extent to which systems must be "over-designed" can be reduced due to greater insight into the possible behaviors of the system.

Performing such verification at a realistic scale will require an approach that combines analysis using both static and dynamic models of the system. This involves the use of protocols [88, 89] that are provably correct using static analysis with respect to certain properties, *e.g.*, deadlock avoidance in systems with nested upcalls. As part of collaborative research with Dr. Henny Sipma, Cesar Sanchez and Dr. Zohar Manna from the Theory Group at Stanford University, we have investigated the static analysis approach [88, 89] as a complement to the executable models that were developed in the research presented in this dissertation.

The focus of the research presented in this dissertation is the development of dynamic or executable models of middleware and use model checking to verify the composition of middleware. These models enable us to model-check a variety of different middleware protocols including the deadlock avoidance protocols described in [88, 89]. In order to reduce the gap between high-level formal models and actual system implementation, this research addresses the key technical challenges outlined in Table 1.1.

### **1.4** Research Contributions

This dissertation makes the following major contributions to the state of the art in modeling DRE systems.

| Challenges                                                                                                                                                                                                                                                       | Solution Techniques                                                                                                                                                                                                                                                                                                                                                                                                         | Effects and Results                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ChallengesModels of middleware shouldbe at a sufficient level ofabstraction such that theyshould be able to capture se-mantics of middleware build-ing blocks and their interfer-ence effects such as the onesdescribed in Section 1.2Modeling of concurrent ob- | Solution Techniques<br>A computational model and<br>a modeling architecture based<br>on timed automata, described<br>in Chapter 3 in which the<br>key models are of middleware<br>building blocks that are reified<br>in the ACE [51] framework.<br>We present concrete engineer-                                                                                                                                           | Effects and Results<br>The examples discussed in<br>Chapters 6, 8 and 9 demon-<br>strate that our models are ca-<br>pable of capturing a combina-<br>tion of concurrency semantics<br>in middleware that includes<br>the interference effects seen in<br>Section 1.2.<br>The empirical validation de- |

| ject middleware using a low-<br>level formalism like automata<br>is non-trivial - <i>e.g.</i> , modeling<br>OS thread abstraction, map-<br>ping from an object model to<br>a process model, state space<br>explosion problem.                                    | ing challenges and solutions<br>for modeling concurrent ob-<br>ject middleware using UP-<br>PAAL and IF in Chapters 4<br>and 5.                                                                                                                                                                                                                                                                                             | scribed in Sections 6.8.1 and 6.8.2 shows the effectiveness of our techniques in dealing with these challenges.                                                                                                                                                                                       |

| The models of middleware<br>building blocks should be<br>reusable and composable                                                                                                                                                                                 | We use communicating timed<br>automata as our modeling for-<br>malism and tools that allow<br>composition of these models.<br>The level of abstraction of our<br>models is similar to that of the<br>reusable middleware building<br>blocks in the ACE toolkit<br>and hence our models can be<br>reused to model most systems<br>that are built using commu-<br>nication primitives in ACE as<br>the middleware substrate.  | The examples that we present<br>in Chapters 6, 8 and 9<br>use a subset of middleware<br>building blocks that are most<br>commonly used in develop-<br>ing communication middle-<br>ware. We modeled all these<br>examples using those models.                                                         |

| The models should reflect the<br>actual system closely and pin-<br>point any design flaws ahead<br>of actual implementation                                                                                                                                      | Our models are executable<br>models that can be checked.<br>We use model checking tools<br>like IF and UPPAAL that<br>generate detailed execution<br>traces if there is a violation<br>of the specified system re-<br>quirements. We have devel-<br>oped tools and techniques de-<br>scribed in Chapter 6 and 7<br>that further enable close cor-<br>respondence between analysis<br>of the model and the actual<br>system. | The detailed execution and<br>timing traces are used in the<br>context of the various exam-<br>ples described in Chapters 6,<br>8 and 9 and have served as<br>a valuable aid in debugging<br>models, verifying hypotheses<br>and uncovering design flaws.                                             |

It demonstrates the need for low-level middleware models. First, using illustrative example scenarios in the context of a distributed example using ORB middleware, it illustrates the need for including lower-level middleware details to adequately verify correctness of DRE systems middleware configurations.

It defines a reusable and relevant middleware modeling architecture. This dissertation defines a middleware-level modeling architecture to establish a common basis for developing concrete models of middleware using different modeling tools. To show the genericity of our proposed architecture, we realize this architecture using two different modeling tools that support timed automata - UPPAAL [7] and IF [12].

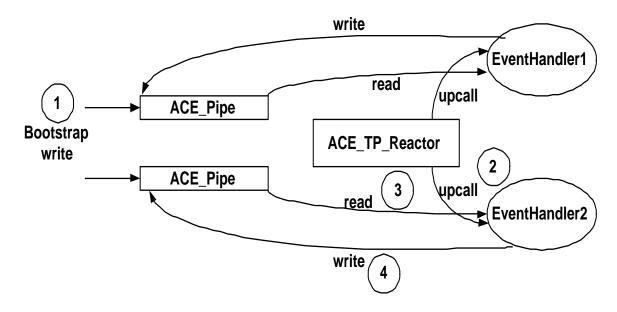

It provides executable models of middleware building blocks. This research develops executable timed automata [4] models of middleware building blocks in UP-PAAL and IF, and demonstrates how liveness and timing analysis can be performed using model checking on system models that include the middleware infrastructure elements also. These timed automata models can then be used in conjunction with higher-level formal models to provide a faithful model of a system including the middleware platform on which the system is deployed, such that the composite models can be verified for correctness with higher fidelity to the system itself. In this research, we develop timed automata models of the following building blocks in ACE - select reactor, thread pool reactor with leader/followers, acceptor, connector, event handler, barrier synchronizer, and wrapper facades such as ACE\_Pipe and ACE\_SOCK\_Stream for inter-process communication. We also demonstrate the modeling of the Half-sync Half-async and Active Object patterns, and the WaitOnReactor and WaitOnConnection reply wait strategies in the context of various examples described in Chapters 6, 8 and 9.

It provides new techniques for modeling middleware. This research also identifies key engineering challenges associated with building models of concurrent object middleware using the timed automata formalism in the context of UPPAAL [7] and IF [12] and also presents solutions to address these challenges. The following novel techniques are presented in this dissertation:

- Modeling objects and threads in the absence of native support for these abstractions in UPPAAL and IF.

- Modeling run-to-completion semantics in IF.

- Ordering rules and an idle catcher process to optimize the state space without over-constraining it, in IF.

- Workarounds for a limitation in IF to use procedures for waiting on condition satisfaction.

- Post-processing trace outputs from the IF model checker to produce object interaction traces and timeline traces that ease the process of model debugging and validation.

Though we have identified these challenges and devised solutions to them in the context of UPPAAL and IF, the solutions may find applicability in other modeling environments also.

It validates the effectiveness of this approach for realistic middleware configurations. We have demonstrated the effectiveness of the tools and techniques that we developed, in the context of various illustrative examples. Our research contributions include the modeling and implementation of a Deadlock Avoidance (DA) protocol [88, 89] that was invented as part of collaborative research conducted with Dr. Henny Sipma, Cesar Sanchez and Dr. Zohar Manna from the Theory Group at Stanford University. We implemented the BASIC-P DA protocol in the ACE TP Reactor, and also modeled and verified the protocol using our models. Our contributions also include modeling and verification of variants of the Gateway example that is available as part of ACE.

### **1.5** Dissertation Organization

This dissertation is organized as follows. Chapter 2 surveys related work in the area of modeling middleware. Chapter 3 presents a middleware-level system model

and a modeling architecture that forms the basis of our models. Realizations of this architecture using two different modeling environments - IF and UPPAAL - are presented in Chapters 4 and 5 respectively. Chapter 6 presents an application of our models by using simple but illustrative example scenarios and uses middleware domain expertise to validate the outcome of the analysis from the model execution. We also compare the effectiveness of different modeling techniques that we developed, in the context of these examples. Chapter 7 presents an evaluation of the fidelity of our models and compares the output from our models with that from actual execution. Chapter 8 presents a case study using our models in the verification of a deadlock avoidance protocol and Chapter 9 presents a case study using our models in the context of an application level gateway example. Chapter 10 presents concluding remarks about this research and its impact, and outlines future research directions.

# Chapter 2

### Survey of Related Work

We now survey related work from several perspectives of the modeling and middleware research communities. Integration of distributed embedded systems using different components, software as well as hardware, requires a great deal of *a priori* modeling and analysis followed by methodical implementation. Modeling enables the system designer to identify and analyze key design decisions that influence both functional and para-functional [22] aspects of a system. While the idea of using models for analysis and design of applications has been prevalent for some time, recently there has been significant ongoing research on applying model-based approaches to the middleware domain. Middleware is becoming an important and in many cases even an inevitable part of distributed real-time system implementations. More and more reusable services find their place in the middleware layer, contributing to the increased complexity of middleware and thus motivating the need for models of middleware building blocks that can be (re)used by the modeling community to model systems with a higher degree of fidelity.

Meanwhile from the perspective of the middleware community, some of the traditional software engineering principles like pattern-oriented [14, 97] development fall under the purview of good software engineering. These techniques are formal only to the extent that they enable a common vocabulary to communicate designs using standard notations like UML [111] and hence provide a means to understand designs. Although there is ongoing research in modeling middleware, a more rigorous and formal approach to middleware composition is needed therefore. The work in this dissertation contributes to the application of formal model-based approaches to the middleware domain. In this chapter we survey four main areas of research that form the background for our research - (1) Model integrated computing (MIC) in DRE systems (2) Model-driven middleware (3) Formal techniques in concurrent and component based systems and (4) Middleware frameworks and execution environments.

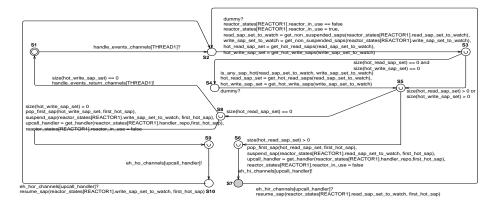

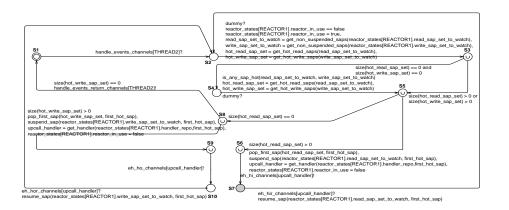

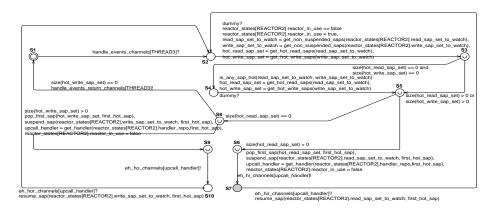

### 2.1 Model Integrated Computing