# FLEXIBLE MULTIPLE-PRECISION FUSED ARITHMETIC UNITS FOR EFFICIENT DEEP LEARNING COMPUTATION

A Thesis Submitted to the

College of Graduate and Postdoctoral Studies

in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy

in the Department of Electrical and Computer Engineering

University of Saskatchewan

Saskatoon, Saskatchewan, Canada

Ву

Hao Zhang

© Hao Zhang, September 2019. All rights reserved.

# Permission to Use

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Electrical and Computer Engineering 3B48 Engineering Building University of Saskatchewan 57 Campus Drive Saskatoon, Saskatchewan S7N 5A9 Canada

Or

Canada

Dean of College of Graduate and Postdoctoral Studies 116 Thorvaldson Building University of Saskatchewan 110 Science Place Saskatoon, Saskatchewan S7N 5C9

# Abstract

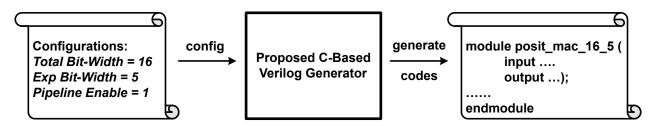

Deep Learning has achieved great success in recent years. In many fields of applications, such as computer vision, biomedical analysis, and natural language processing, deep learning can achieve a performance that is even better than human-level. However, behind this superior performance is the expensive hardware cost required to implement deep learning operations. Deep learning operations are both computation intensive and memory intensive. Many research works in the literature focused on improving the efficiency of deep learning operations. In this thesis, special focus is put on improving deep learning computation and several efficient arithmetic unit architectures are proposed and optimized for deep learning computation. The contents of this thesis can be divided into three parts: (1) the optimization of general-purpose arithmetic units for deep learning computation; (2) the design of deep learning specific arithmetic units; (3) the optimization of deep learning computation using 3D memory architecture.

Deep learning models are usually trained on graphics processing unit (GPU) and the computations are done with single-precision floating-point numbers. However, recent works proved that deep learning computation can be accomplished with low precision numbers. The half-precision numbers are becoming more and more popular in deep learning computation due to their lower hardware cost compared to the single-precision numbers. In conventional floating-point arithmetic units, single-precision and beyond are well supported to achieve a better precision. However, for deep learning computation, since the computations are intensive, low precision computation is desired to achieve better throughput. As the popularity of half-precision raises, half-precision operations are also need to be supported. Moreover, the deep learning computation contains many dot-product operations and therefore, the support of mixed-precision dot-product operations can be explored in a multiple-precision architecture. In this thesis, a multiple-precision fused multiply-add (FMA) architecture is proposed. It supports half/single/double/quadruple-precision FMA operations. In addition, it also supports 2-term mixed-precision dot-product operations. Compared to the conventional multiple-precision FMA architecture, the newly added half-precision support and mixed-precision dot-product only bring minor resource overhead. The proposed FMA can be used as general-purpose arithmetic unit. Due to the support of parallel half-precision computations and mixed-precision dot-product computations, it is especially suitable for deep learning computation.

For the design of deep learning specific computation unit, more optimizations can be performed. First, a fixed-point and floating-point merged multiply-accumulate (MAC) unit is proposed. As deep learning computation can be accomplished with low precision number formats, the support of high precision floating-point operations can be eliminated. In this design, the half-precision floating-point format is supported to provide a large dynamic range to handle small gradients for deep learning training. For deep learning inference, 8-bit fixedpoint 2-term dot-product computation is supported. Second, a flexible multiple-precision MAC unit architecture is proposed. The proposed MAC unit supports both fixed-point operations and floating-point operations. For floating-point format, the proposed unit supports one 16-bit MAC operation or sum of two 8-bit multiplications plus a 16-bit addend. To make the proposed MAC unit more versatile, the bit-width of exponent and mantissa can be flexibly exchanged. By setting the bit-width of exponent to zero, the proposed MAC unit also supports fixed-point operations. For fixed-point format, the proposed unit supports one 16-bit MAC or sum of two 8-bit multiplications plus a 16-bit addend. Moreover, the proposed unit can be further divided to support sum of four 4-bit multiplications plus a 16-bit addend. At the lowest precision, the proposed MAC unit supports accumulating of eight 1-bit logic AND operations to enable the support of binary neural networks. Finally, a MAC architecture based on the posit format, a promising numerical format in deep learning computation, is proposed to facilitate the use of posit format in deep learning computation.

In addition to the above mention arithmetic units, an improved hybrid memory cube (HMC) architecture is proposed for weight-sharing deep neural network processing. By modifying the HMC instruction set and HMC logic layer, the major part of the deep learning computation can be accomplished inside memory. The proposed design reduces the memory bandwidth requirements and thus reduces the energy consumed by memory data transfer.

# Acknowledgements

The research works presented in this thesis are sponsored by the Natural Sciences and Engineering Research Council (NSERC) of Canada and the Department of Electrical and Computer Engineering at the University of Saskatchewan.

I wish to express my sincere thanks to my supervisor, Dr. Seok-Bum Ko, for his guidance and support during my Ph.D. program. At the beginning of my Ph.D. program, Dr. Ko allowed me to carry on the computer arithmetic research from my master program and he gave me much freedom in specific research topic selection. I could connect computer arithmetic with deep learning computation. During the period of my study, Dr. Ko gave me much help not only in academic research but also in daily life.

I would like to place on record my gratitude to Dr. Dongdong Chen. We started working together from the beginning of my master program. Our cooperation continued during my Ph.D. program. We discussed research ideas every week. His experience in research really gave me great help and we have a great period of cooperation.

My sincere thanks also go to Dr. Li Chen, Dr. Anh V. Dinh, Dr. Francis M. Bui, and other professors at the University of Saskatchewan who had taught me. I learned many advanced knowledges from their lectures which not only broadened my horizon but also gave me many research ideas.

Thanks to my committee members Dr. Keshab K. Parhi, Dr. Raymond J. Spiteri, Dr. Li Chen, Dr. C.Y. (Tony) Chung and Dr. Anh V. Dinh for their time and effort to review my thesis and for their suggestions to imporve the quality of this thesis.

I also thank every technical staffs in the Department of Electrical and Computer Engineering who helped me setup my research environment and helped me solve the technique issues I encountered when using the development softwares.

Finally, a big thanks to my parents, my family, and my friends for their moral support throughout the years.

This is the thesis dedicated to my beloved parents.

# Contents

| Permis  | ssion to Use                            | i   |

|---------|-----------------------------------------|-----|

| Abstra  | $\operatorname{act}$                    | ii  |

| Ackno   | wledgements                             | iv  |

| Conter  | nts                                     | vi  |

| List of | f Tables                                | X   |

| List of | f Figures                               | xi  |

| List of | f Abbreviations                         | iii |

| Part :  | I Preface                               | 1   |

| Chapte  | er 1 Introduction                       | 2   |

| 1.1     | Deep Learning Advantages and Potentials | 2   |

| 1.2     | Motivation of Research Works            | 4   |

| 1.3     | Overview of Research Works              | 7   |

| 1.4     | Summary of Contributions                | 10  |

| Chapte  | er 2 Background                         | 13  |

| 2.1     | Numerical Formats                       | 13  |

|         | 2.1.1 Floating-Point Format             | 13  |

|         | 2.1.2 Fixed-Point Format                | 18  |

|         | 2.1.3 The Posit Format                  | 19  |

| 2.2     | Fused Arithmetic Units                  | 21  |

| 2.3     | Mixed-Precision Arithmetic Units        | 24  |

| 2.4     | Deep Learning Computing                 | 25  |

|       | 2.4.1  | Overview                                             | 25 |

|-------|--------|------------------------------------------------------|----|

|       | 2.4.2  | Reduced Precision Computations                       | 27 |

|       | 2.4.3  | Range vs Precision                                   | 28 |

| 2.5   | Hybrid | d Memory Cube                                        | 30 |

| Part  | II A   | rithmetic Unit for General Purpose Computation .     | 32 |

| Chapt | er 3 N | Multiple-Precision Floating-Point Fused Multiply Add | 33 |

| 3.1   | Introd | luction                                              | 33 |

| 3.2   | The P  | roposed Design                                       | 36 |

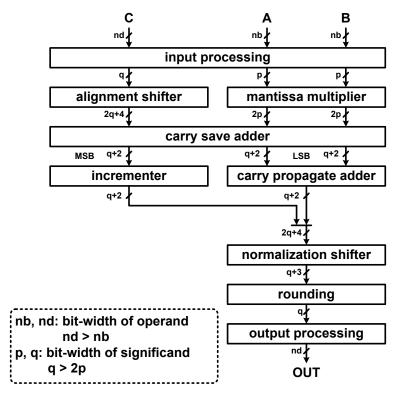

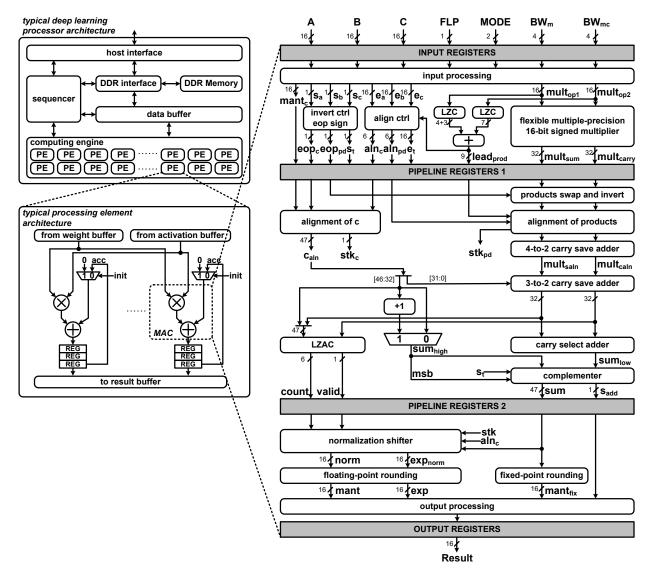

|       | 3.2.1  | Input Processing                                     | 39 |

|       | 3.2.2  | Mantissa Multiplier                                  | 40 |

|       | 3.2.3  | Alignment Shifter                                    | 43 |

|       | 3.2.4  | Adder                                                | 50 |

|       | 3.2.5  | Leading Zero Anticipation and Counting               | 51 |

|       | 3.2.6  | Normalization                                        | 53 |

|       | 3.2.7  | Rounding                                             | 54 |

| 3.3   | Result | s and Analysis                                       | 54 |

| 3.4   | Summ   | ary                                                  | 62 |

| Part  | III 4  | Arithmetic Unit for Deep Learning Computation        | 63 |

| Chapt | er 4 N | Multiple-Precision Multiply Accumulate Unit          | 64 |

| 4.1   | Introd | luction                                              | 64 |

| 4.2   | The P  | Proposed Design                                      | 65 |

|       | 4.2.1  | Floating-Point Mode                                  | 67 |

|       | 4.2.2  | Fixed-Point Mode                                     | 68 |

|       | 4.2.3  | Merged Multiplier Design                             | 68 |

| 4.3   | Result | s and Analysis                                       | 70 |

| 1.1   | Summ   | arv                                                  | 72 |

| Chapte | er 5 Flexible Multiple-Precision Multiply Accumulate Unit | <b>7</b> 3 |

|--------|-----------------------------------------------------------|------------|

| 5.1    | Introduction                                              | 73         |

| 5.2    | Supported Numerical Formats                               | 78         |

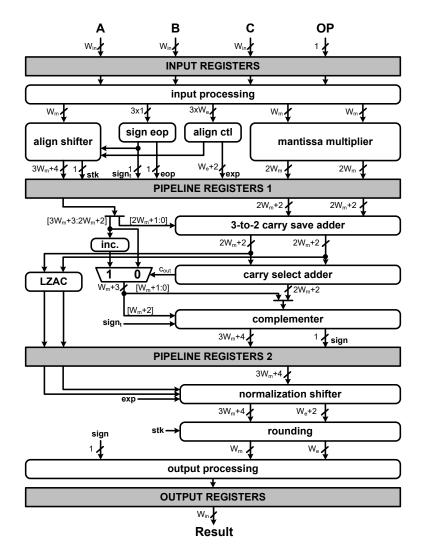

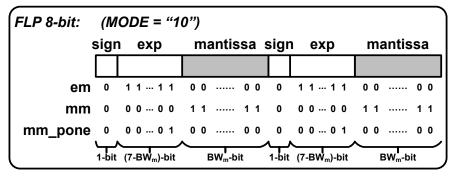

|        | 5.2.1 Numerical Format                                    | 78         |

| 5.3    | The Proposed Design                                       | 79         |

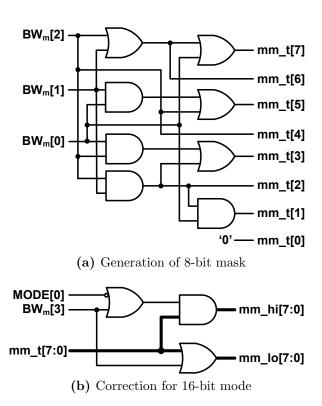

|        | 5.3.1 Input Processing                                    | 82         |

|        | 5.3.2 Flexible Multiple-Precision Multiplier              | 85         |

|        | 5.3.3 Alignment Control and Shifter                       | 89         |

|        | 5.3.4 Addition                                            | 91         |

|        | 5.3.5 Leading Zero Anticipator and Counting               | 92         |

|        | 5.3.6 Normalization Shifting                              | 92         |

|        | 5.3.7 Rounding                                            | 93         |

|        | 5.3.8 Output Processing                                   | 94         |

| 5.4    | Results and Analysis                                      | 94         |

| 5.5    | Case Study                                                | 100        |

| 5.6    | Discussion                                                | 103        |

| 5.7    | Summary                                                   | 106        |

|        |                                                           | 100        |

|        |                                                           | 108        |

| 6.1    | Introduction                                              | 108        |

| 6.2    | •                                                         |            |

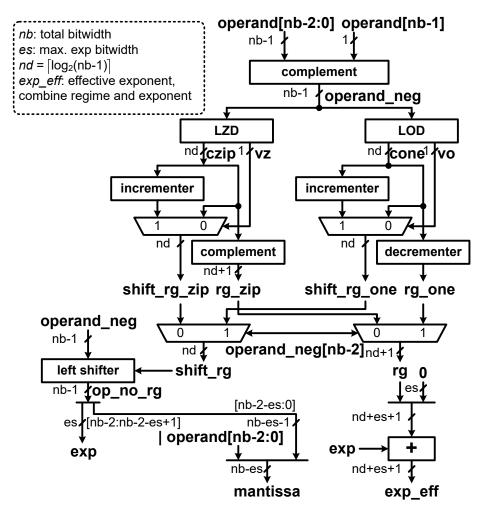

|        | 6.2.1 Posit Component Extraction                          | 111        |

|        | 6.2.2 Mantissa Multiplier                                 | 112        |

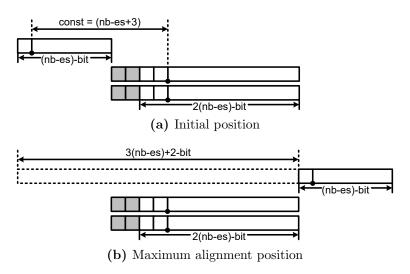

|        | 6.2.3 Alignment Shifter                                   | 112        |

|        | 6.2.4 Adder                                               | 113        |

|        | 6.2.5 Leading Zero Anticipator                            | 113        |

|        | 6.2.6 Normalization Shifter                               | 113        |

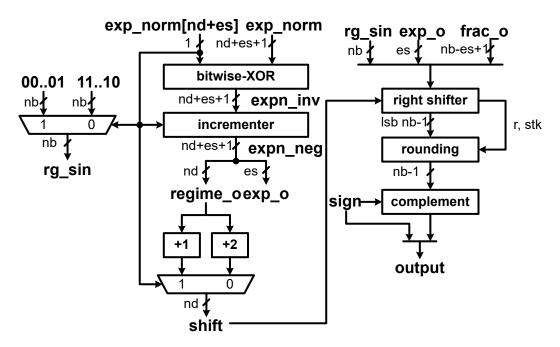

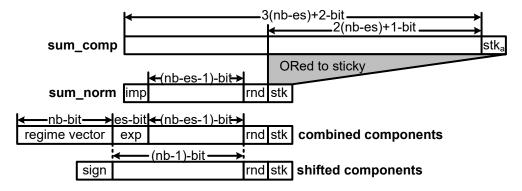

|        | 6.2.7 Posit Output Process and Rounding                   | 114        |

| 6.3    | Results and Analysis                                      | 115        |

| 6.4    | Summary                                                   | 118        |

| Part 1 | $\mathbf{IV}$ | Deep Learning Computation using 3D Memory 119 |

|--------|---------------|-----------------------------------------------|

| Chapte | er 7          | Improved Hybrid Memory Cube Architecture      |

| 7.1    | Intr          | oduction                                      |

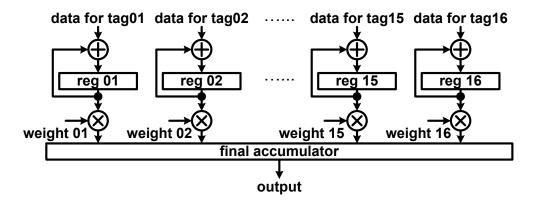

| 7.2    | Wei           | ght-Sharing Deep Neural Network               |

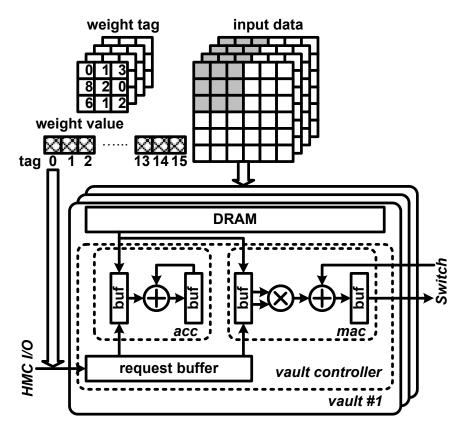

| 7.3    | The           | Proposed HMC Architecture                     |

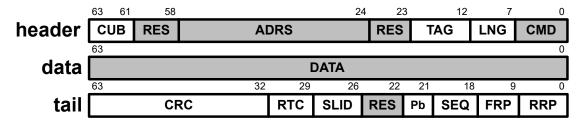

|        | 7.3.          | 1 Instruction Set                             |

|        | 7.3.2         | 2 HMC Request Format                          |

|        | 7.3.3         | 3 HMC Memory Control                          |

|        | 7.3.4         | 4 HMC Weight-Sharing Operation                |

| 7.4    | Res           | ults and Analysis                             |

| 7.5    | Sum           | nmary                                         |

| Part ' | V             | Conclusion                                    |

| Chapte | er 8          | Summary and Future Work                       |

| 8.1    | Sun           | nmary                                         |

| 8.2    | Futi          | ure Work                                      |

| Refere | nces          | 14                                            |

# List of Tables

| 1.1 | Memory and computation requirements of various deep neural networks         | 4   |

|-----|-----------------------------------------------------------------------------|-----|

| 2.1 | Floating-Point format defined in IEEE 754-2008                              | 14  |

| 2.2 | Results when both addition/subtraction operands are zeros                   | 17  |

| 2.3 | Comparison of the dynamic range of Posit format and floating-point format . | 21  |

| 2.4 | HMC Specifications                                                          | 31  |

| 3.1 | Synthesis results of each pipeline stage of the proposed FMA                | 55  |

| 3.2 | Area and energy comparison of the proposed FMA with standalone FMA designs  | 56  |

| 3.3 | Comparison of functionality with multiple-precision FMA designs             | 58  |

| 3.4 | Comparison of the proposed FMA with previous works                          | 59  |

| 4.1 | Synthesis results of the combinational logic of each pipeline stage         | 70  |

| 4.2 | Comparison of the proposed multiply-accumulate unit with single-mode mul-   |     |

|     | tiply accumulate unit                                                       | 71  |

| 5.1 | Supported formats of the proposed MAC unit                                  | 77  |

| 5.2 | Synthesis results of each pipeline stage of the proposed design             | 95  |

| 5.3 | Comparison of the proposed MAC unit with standard arithmetic units          | 98  |

| 6.1 | Comparison of the Posit MAC with floating-point MAC                         | 117 |

| 6.2 | Delay of each pipeline stage of Posit MAC                                   | 117 |

| 7.1 | Newly added instruction sets                                                | 124 |

| 8.1 | Functions supported by the proposed MP-FMA and their applications           | 134 |

| 8.2 | Functions supported by the proposed MP-MAC and their usage                  | 135 |

| 8.3 | Functions supported by the proposed Flex-MAC unit                           | 136 |

# List of Figures

| 1.1  | Performance comparison of deep learning methods with previous methods                       | ્  |

|------|---------------------------------------------------------------------------------------------|----|

| 2.1  | Binary floating-point format defined in IEEE 754-2008                                       | 13 |

| 2.2  | Binary fixed-point format                                                                   | 18 |

| 2.3  | Format of posit number                                                                      | 20 |

| 2.4  | Implementing floating-point $A \times B + C$ with separate arithmetic units and             |    |

|      | fused arithmetic unit                                                                       | 22 |

| 2.5  | Datapath of a mixed-precision FMA                                                           | 24 |

| 2.6  | Architecture of AlexNet                                                                     | 25 |

| 2.7  | Process of convolution computation in deep neural network                                   | 26 |

| 2.8  | Weights and activations distribution of Alex<br>Net Convolution Layer 2 $\ \ldots \ \ldots$ | 27 |

| 2.9  | Normalized neural network accuracy under different exponent and mantissa                    |    |

|      | bit-width                                                                                   | 29 |

| 2.10 | Basic hybrid memory cube architecture                                                       | 30 |

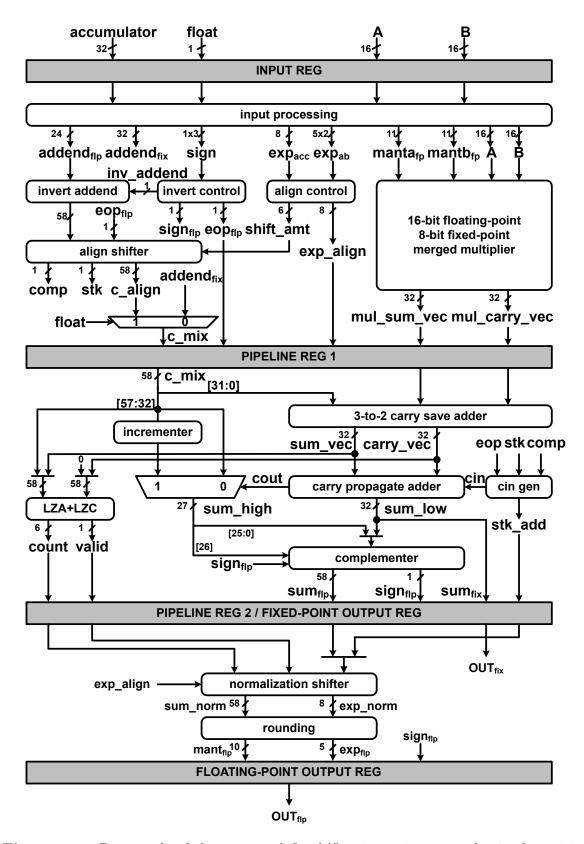

| 3.1  | Datapath of the proposed multiple-precision fused multiply-add unit                         | 37 |

| 3.2  | Unified mantissa format for different precisions                                            | 40 |

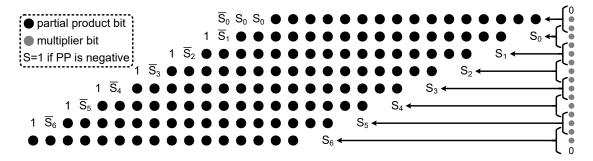

| 3.3  | Partial products of the $15 \times 15$ radix-4 Booth multiplier                             | 40 |

| 3.4  | Enabled multipliers and product regions in different precision modes                        | 41 |

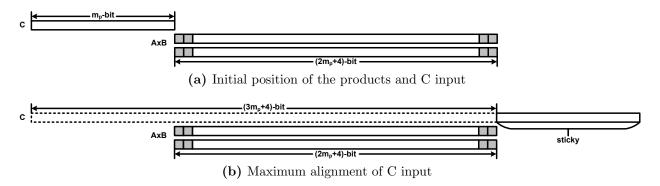

| 3.5  | Alignment of C operand in the proposed fused multiply-add unit                              | 44 |

| 3.6  | Unified input format for the alignment shifter of the proposed fused multiply-              |    |

|      | add unit                                                                                    | 45 |

| 3.7  | Design details of the alignment shifter of the proposed fused multiply-add unit             | 46 |

| 3.8  | Alignment of products in mixed-precision dot-product mode                                   | 48 |

| 3.9  | Unified input format of products alignment in mixed-precision operation mode                | 50 |

| 3.10 | Diagram of the adder used in the proposed fused multiply-add                                | 51 |

| 3.11 | Unified input format for the leading zero anticipator and counting of the pro-              |    |

|      | posed fused multiply-add unit                                                               | 52 |

| 4.1  | Data-path of the proposed fixed/floating-point merged mixed-precision multiply- |     |

|------|---------------------------------------------------------------------------------|-----|

|      | accumulate unit                                                                 | 66  |

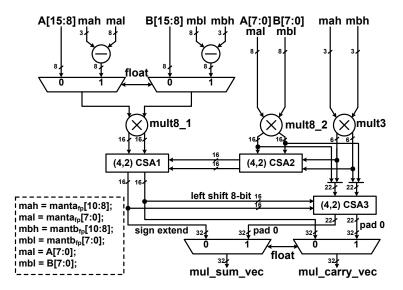

| 4.2  | Architecture of the proposed fixed/floating-point merged multiplier             | 68  |

| 4.3  | Partial products arrangement of modified booth multiplier                       | 69  |

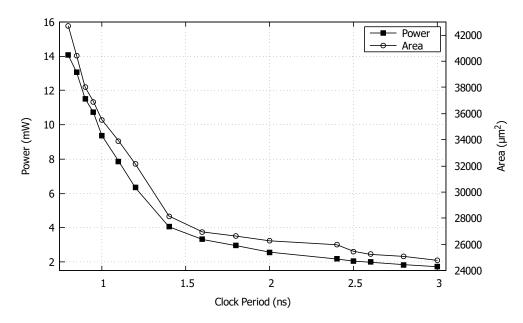

| 4.4  | Area-Delay and Power-Delay curve of the proposed design                         | 72  |

| 5.1  | Datapath of the proposed flexible multiple-precision multiply-accumulate unit   |     |

|      | and its usage in deep learning processor                                        | 79  |

| 5.2  | Datapath of conventional multiply-accumulate unit based on standard floating-   |     |

|      | point format                                                                    | 81  |

| 5.3  | Circuit to generate the mantissa mask $mm\_hi$ and $mm\_lo$                     | 83  |

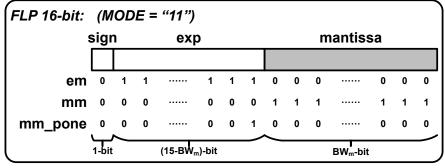

| 5.4  | Format of mantissa mask $mm$ , exponent mask $em$ , and implicit bit mask       |     |

|      | mm_pone                                                                         | 84  |

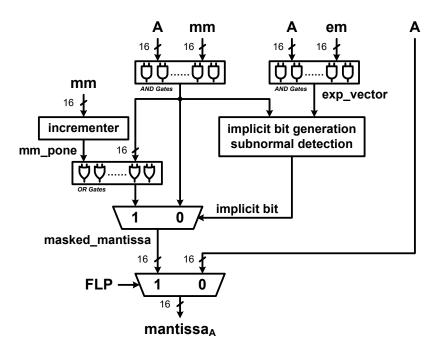

| 5.5  | Diagram of input processing for $A$ operand                                     | 85  |

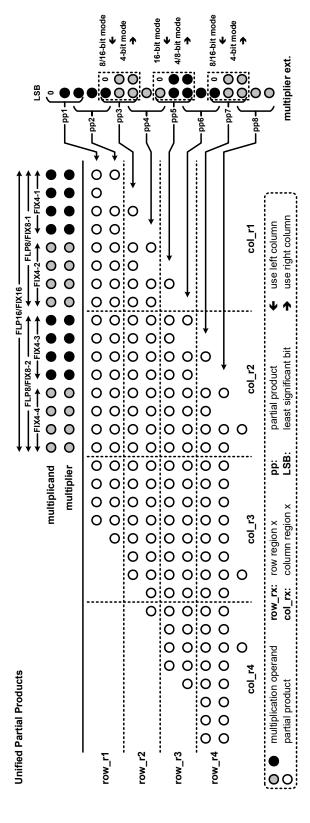

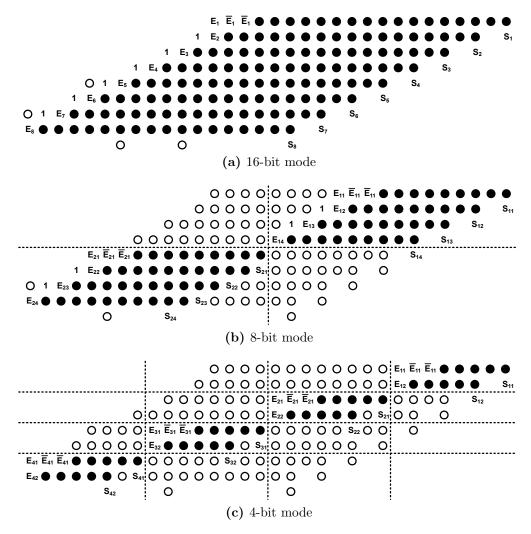

| 5.6  | Partial product generation and partial product array of the proposed flexible   |     |

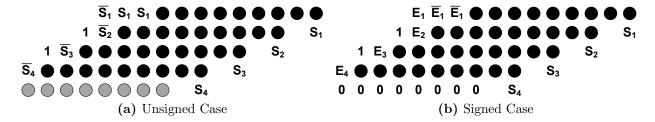

|      | multiple-precision multiplier                                                   | 86  |

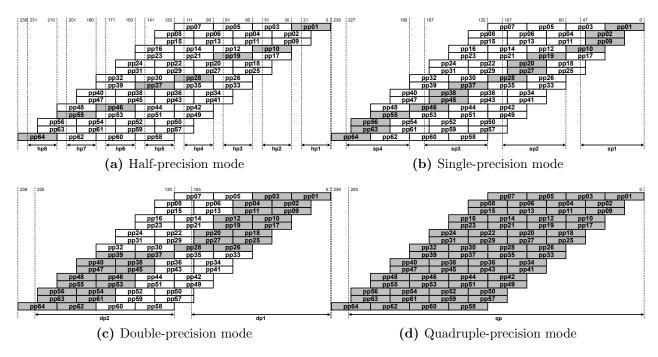

| 5.7  | Partial product array of each precision mode (white dots represent the bits     |     |

|      | not used; black dots represent partial products)                                | 87  |

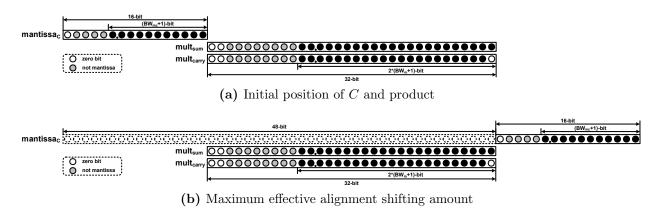

| 5.8  | Alignment shifting of $C$ with product in FLP16 mode                            | 88  |

| 5.9  | Alignment shift of $C$ and two products in 8-bit floating-point mode            | 89  |

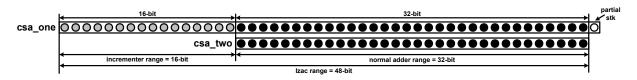

| 5.10 | Addition arrangement and the leading zero anticipator and counting (LZAC)       |     |

|      | range of the proposed unit                                                      | 91  |

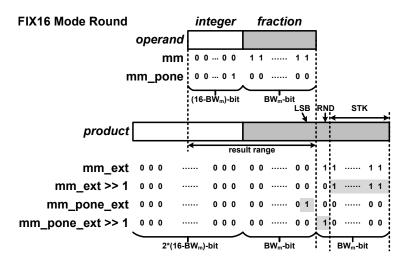

| 5.11 | Rounding method for floating-point modes                                        | 91  |

| 5.12 | Rounding method for 16-bit fixed-point mode                                     | 93  |

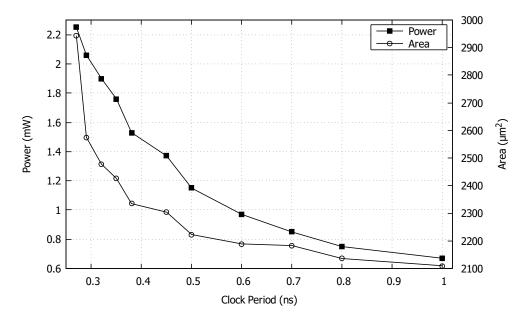

| 5.13 | Power-Delay curve and Area-Delay curve of the proposed design under STM-        |     |

|      | 28nm                                                                            | 96  |

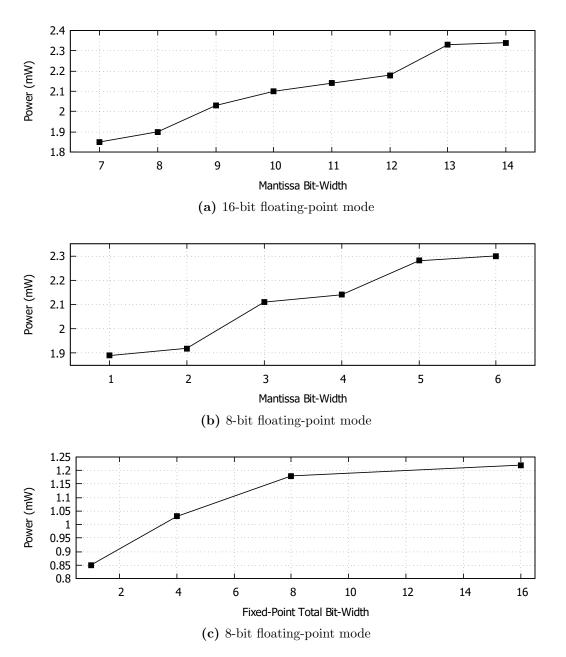

| 5.14 | Power consumption of the proposed design in various operational modes (with     |     |

|      | timing constraint 0.27 $ns$ )                                                   | 97  |

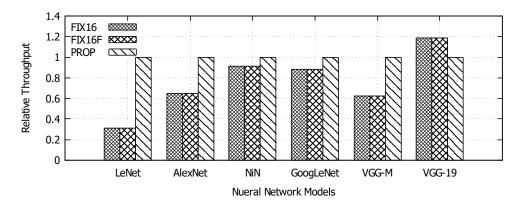

| 5.15 | Relative throughput of three implementations for six neural networks            | 102 |

| 5.16 | Relative power efficiency of three implementations for six neural networks      | 102 |

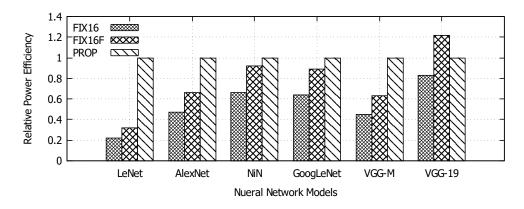

| 6.1 | Datapath of the proposed posit multiply-accumulate unit architecture (The             |      |

|-----|---------------------------------------------------------------------------------------|------|

|     | proposed generator will give combinational design. Pipeline in this figure is         |      |

|     | just an example.)                                                                     | 110  |

| 6.2 | Diagram of posit format component extraction                                          | 111  |

| 6.3 | Datapath of the alignment shifter                                                     | 112  |

| 6.4 | Diagram of posit output processing and rounding                                       | 114  |

| 6.5 | Rounding of the posit result                                                          | 114  |

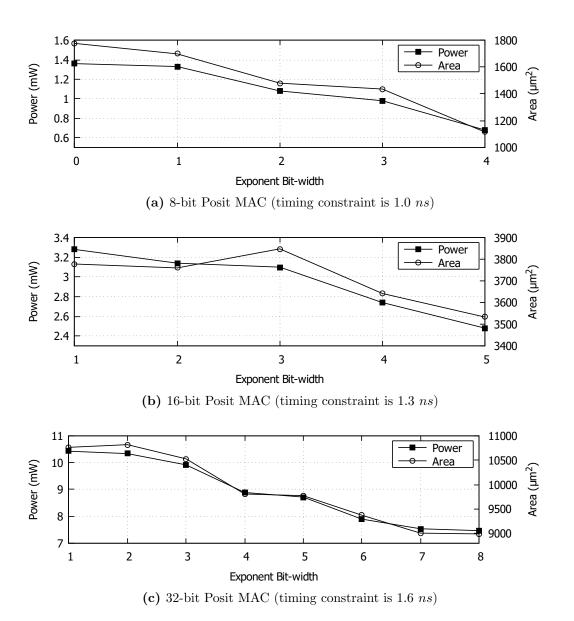

| 6.6 | Area and power of 32-bit Posit MAC with various exponent bit-width (timing            |      |

|     | constraint is 1.6ns)                                                                  | 116  |

| 7.1 | Process of convolution using weight sharing method                                    | 123  |

| 7.2 | Architecture of the modified HMC                                                      | 124  |

| 7.3 | HMC memory request packet format                                                      | 125  |

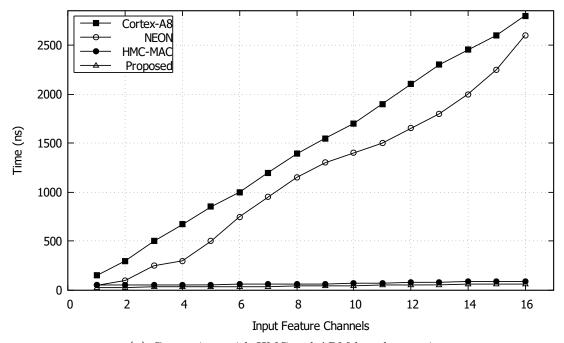

| 7.4 | Timing of performing convolution with $3\times3$ kernel under different input channel | s129 |

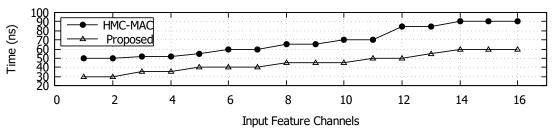

| 8.1 | Organization of the thesis and the deep learning computation features sup-            |      |

|     | ported by each proposed design                                                        | 133  |

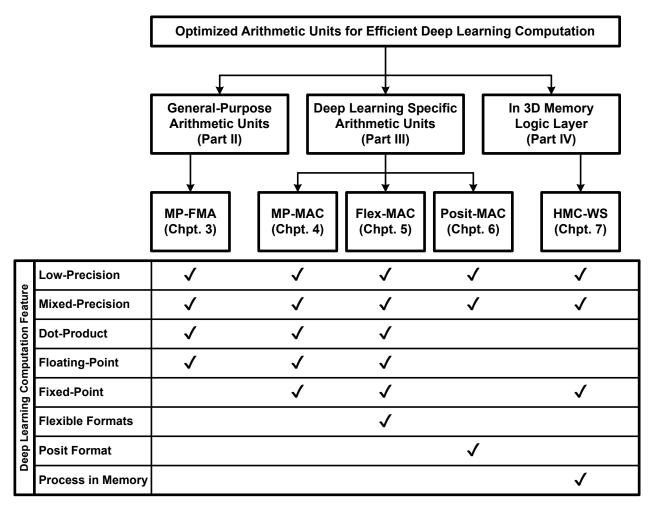

| 8.2 | Using the proposed posit MAC generator to generate Verilog code                       | 137  |

# List of Abbreviations

AI Artificial Intelligence

ASIC Application-Specific Integrated Circut

CNN Convolutional Neural Network

CONV Convolutional Layer

CPA Carry-Propagate Adder

CPU Central Processing Unit

CSA Carry-Save Adder

CT Computer Tomography

DOT Dot-Product

DP Double Precision

DRAM Dynamic Random Access Memory

FC Fully-Connected Layer

FFT Fast Fourier Transform

FIX Fixed-Point Number Format

FLP Floating-Point Number Format

FMA Fused Multiply-Add

FPU Floating-Point Unit

GPU Graphics Processing Unit

HBM High Bandwidth Memory

HDL Hardware Description Language

HMC Hybrid Memory Cube

HP Half Precision

LSB Least Significant Bit

LZA Leading Zero Anticipator

LZAC Leading Zero Anticipation and Counting

LZC Leading Zero Counting

MAC Multiply-Accumulate

MIX Mixed Precision

MP Multiple Precision

MSB Most Significant Bit

PIM Processing in Memory

QP Quadruple Precision

SoP Sum of Product

SP Single Precision

TSV Through Silicon Via

VCD Value Change Dump

VHDL Very High Speed Hardware Description Language

Part I

Preface

# Chapter 1

# Introduction

This chapter presents the performance advantage and the popularity of deep learning in many fields of applications. Due to the superior performance and the popularity, optimizing hardware deep learning operations becomes necessary. This motivates the research works to be presented in this thesis that are to design arithmetic units based on the requirements of the deep learning computation. Section 1.1 presents the performance advantage and the potential of deep learning applications. The motivation of the research works are presented in Section 1.2. Section 1.3 presents the overview of the research works. The contributions of these research works are summarized in Section 1.4.

# 1.1 Deep Learning Advantages and Potentials

The idea to make an intelligent system dates back to 1950s when the term artificial intelligence (AI) was coined by John McCarthy. After that, many significant algorithms were proposed by AI researchers. However, due to the limitation of the computation power in the early days, training a large scale AI model may take months, and thus AI algorithms still stayed in small scale. In early 2000s, the development of computation power made the research on large scale AI algorithms and deep learning algorithms becoming possible. Around the same time, many large database became available which boosted the development of deep learning. A major breakthrough happens in 2012 when the AlexNet [1] achieved significant improvements on image classifications over preceding methods.

After that many research works have been done on applying deep learning methods in many applications. In 2015, the ResNet [2] achieves the image classification accuracy that is even higher than human. In the field of medical imaging analysis, deep learning methods

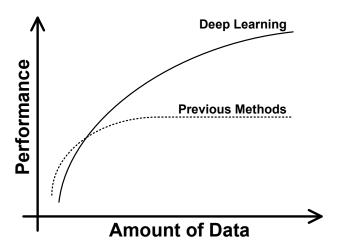

**Figure 1.1:** Performance comparison of deep learning methods with previous methods (Reproduced from: B. Catanzaro, "Computer Arithmetic in Deep Learning [Keynote Talk]," in ARITH26, 2016.)

are also extensively investigated. In 2017, researchers from Stanford University proposed and trained a convolutional neural network to perform skin cancer classification [3] and the network achieved a performance that was at the same level as dermatologists. In more complex tasks, such as the Go game, the deep learning method, the AlphaGo [4], can already beat the human champion. In addition to the above mentioned achievements, deep learning techniques are also widely applied in applications such as natural language processing, bigdata analysis and autonomous driving.

Deep learning methods are quickly applied in many fields of applications because of two main advantages: (1) promising performance in large database, as shown in Figure 1.1. The performance of many conventional AI methods become saturated with the amount of available data goes higher. This may be limited by the computation and analysis capability of small scale models. However, in deep learning, as the model can have much larger scale, the potential of analyzing big database is also expected to be significant. (2) Reducing human workload. On one hand, deep learning is running in an end-to-end way so that the features required by performing classification or other tasks are hierarchically extracted from the input data in deep learning methods. Whereas, in conventional AI methods, features extraction and selection needs to be done manually which take a lot of time. On the other hand, in some applications, with the same level of accuracy, deep learning model can perform a task much faster than human. One example is the computer tomography (CT) image analysis.

Table 1.1: Memory and computation requirements of various deep neural networks

|                         | LeNet-5 | AlexNet | Overfeat | VGG16 | ${\bf GoogLeNet}$ | ResNet-50 |

|-------------------------|---------|---------|----------|-------|-------------------|-----------|

| Top-5 Error             | N/A     | 16.4    | 14.2     | 7.4   | 6.7               | 5.3       |

| # of weights            | 60K     | 61M     | 146M     | 138M  | 7M                | 25.5M     |

| $\#$ of MACs $^\dagger$ | 341K    | 724M    | 2.8G     | 15.5G | 1.43G             | 3.9G      |

<sup>&</sup>lt;sup>†</sup> MAC refers to the multiply-accumulate operation, and it includes one multiplication followed by one addition.

A human radiologist usually needs 5 to 10 minutes to read and analyzes a CT scan while a deep learning model can do the same task in only several seconds. Therefore, deep learning can significantly reduce the human radiologists' workload.

Deep learning can provide promising results in many fields of applications. However, the cost of implementing deep learning operations is expensive. As shown in Table 1.1, a deep neural network may have millions of parameters and a single operation may require billions of computations. As the popularity of deep learning methods raises, many recent hardware designs target to optimizing deep learning operations, both in reducing the energy consumption and in improving the speed performance. In recent years, many research works have been done on optimizing the datapath for deep learning operations [5]. As the core of computation, the arithmetic unit can determine the efficiency and functionality of the whole hardware design. In this thesis, special focuses are put on the design of arithmetic units for efficient deep learning computation. Several novel arithmetic unit architectures are proposed based on the characteristics of deep learning computation.

# 1.2 Motivation of Research Works

Deep neural networks are usually trained on graphics processing units (GPUs). Many deep learning frameworks, such as Tensorflow [6] and Caffe [7], perform deep neural network computations using 32-bit single-precision (SP) floating-point numbers [8] by default. However, the data-path of single-precision floating-point units is complex and the hardware cost of implementing single-precision units are expensive. These lead to a high energy consumption and a large latency when implementing deep neural networks in customized hardware. In order

to reduce the hardware cost, some research works in recent years are focused on reducing the numerical precision required by deep neural network computation. In [9], the authors successfully implemented deep neural networks with 16-bit half-precision numbers [8]. In some other works, half-precision numbers are also used in deep learning training and inference operations.

In the floating-point unit (FPU) of general-purpose processors, single-precision and higher precision formats are well supported in order to provide a better accuracy for scientific computations. However, for deep learning computation, on one hand, using low precision formats (half-precision) is able to maintain high accuracy. On the other hand, deep learning is computation intensive and thus low precision computation is desired to improve the overall speed performance. Considering these factors, the support of half-precision operations in FPU should be added to speed up deep learning computation in general-purpose processors.

In deep learning computation, the reduced precision computation is usually applied together with the mixed-precision computation in order to manage the accuracy [10]. Reduced precision method is usually applied to the multiplication because the multiplication operation is slow and the multiplier consumes large amount of resources. With reduced precision multiplication, the area of the multiplier can be reduced and the speed of the multiplication operations can be improved. When performing accumulation, a high precision adder is applied. In deep learning computation, a high precision data is kept. Before multiplication, this data is truncated to low precision in order to perform low precision multiplication. When performing accumulation, the product will be accumulated to the higher precision copy so that the accuracy can be recovered. In conventional multiple-precision FPU, both low precision multiplication data-path and high precision accumulation data-path already exist. Therefore, the support of mixed-precision computation in a multiple-precision FPU can be explored. When designing deep learning specific arithmetic unit, the mixed-precision computation feature should also be considered.

For deep neural network training, a number format with large dynamic range, such as floating-point format, is required to handle very small gradient values during the last few iterations of training. For deep neural network inference, as there is no gradient computation, the numerical precision can be further reduced. In many cases, fixed-point format can provide

enough accuracy in inference [11] [12]. When performing fixed-point computations, compared to floating-point computations, both energy consumption and speed performance can be improved. Therefore, for a deep learning processor that needs to handle both training and inference operations, both floating-point operations and fixed-point operations are required to be supported.

Reduced precision computation is feasible for deep learning computation. However, the minimum required precisions for different deep neural networks or different layers of a deep neural network are not identical [11] [13] [14]. Therefore, using a computation unit that supports only one numerical precision to perform all computations is not efficient and in this case, a multiple-precision computation unit is desired. For example, if only one 16-bit fixed-point unit is used, when one layer can be computed with 4-bit number, the other 12-bit of the computation unit is not utilized. However, if a multiple-precision 16-bit unit, that can be reconfigured to dual 8-bit units or quad 4-bit units at runtime, is applied, for 4-bit computation, four parallel computations can be performed and thus the throughput can be improved. In addition, the improvement in throughput can also be helpful to improve energy efficiency. Therefore, for a computation unit that is designed specific for general purpose deep learning computation, multiple-precision unit is preferred.

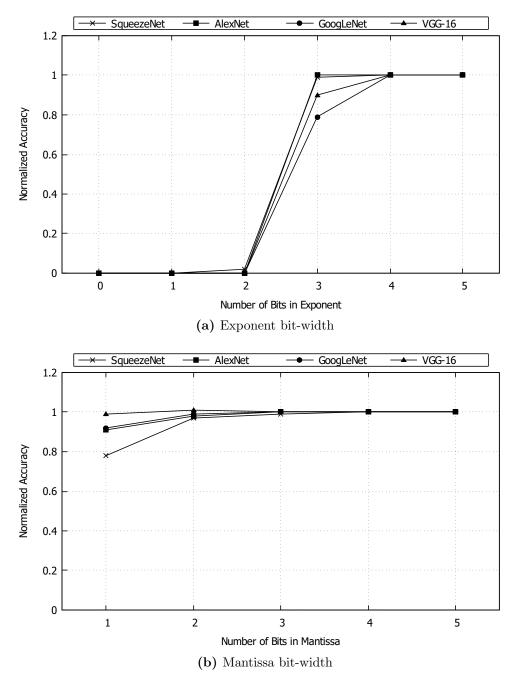

The floating-point format defined in [8] contains a sign, an exponent, and a mantissa. The bit-width of the exponent corresponds to the dynamic range of the numerical format while the bit-width of the mantissa corresponds to the representation precision of the format. In deep learning computation, the importance of exponent and mantissa to the neural network accuracy is different [13] [15]. According to the results in [15], the dynamic range is more important than representation precision for neural network accuracy. By using this finding, the deep neural network computation unit can be designed with a constant total bit-width but the bit-width of exponent and mantissa can be dynamically exchanged. So that the requirement of exponent can be met first and the remaining bits can be allocated to the mantissa. By designing with this method, more flexibility can be provided for deep learning computation.

The research on deep learning computation focuses not only on the conventional computation system such as fixed-point and floating-point computation system. In recent years,

deep learning computation using logarithmic number system and other new number formats are also investigated. The recent proposed posit number system [16] is one of them. Posit encodes numbers in a non-uniform way which fits well with the deep neural network data distribution. In addition, with the same total bit-width, the posit format can provide much larger dynamic range than floating-point format. Therefore, the use of posit in deep learning computation is promising. As posit is relatively new, there is only hardware adder and hardware multiplier available in the literature. In order to facilitate the use of posit in deep learning applications, a posit based multiply-accumulate (MAC) unit or other fused unit is required.

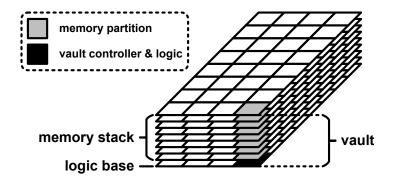

In recent years, the 3D memory architectures, such as hybrid memory cube (HMC) [17] and high-bandwidth memory (HBM) [18], are proposed. In 3D memory, the storage layers are stacked vertically and the communication among storage layers is achieved by the through silicon via (TSV). At the bottom of the 3D memory architecture, there is a logic layer where the memory controller and some simple logic functions are implemented. Due to the integration of the logic layer, data processing inside memory, termed processing-in-memory (PIM), becomes possible. With PIM, the bandwidth requirements of the memory interface can be significantly reduced. Memory data transfer is also reduced because some data processing can be done inside memory. Both of these reduces the energy consumed by memory data transfer. As deep learning is memory and computation intensive, using 3D memory in deep learning processing is expected to significantly improve the energy efficiency of deep learning computation.

# 1.3 Overview of Research Works

In this thesis, based on the computation characteristics discussed in Section 1.2, several arithmetic unit architectures optimized for deep learning computation are proposed. We provide the solutions both to optimize general-purpose FPU for deep learning computation and to design deep learning specific computation units. The arithmetic units proposed in this thesis are based on multiple-precision arithmetic unit architectures and are target for general support for as many neural network models and operations as possible. This is

different from the design of an architecture that is optimized for a specific model or operation. Therefore, the proposed arithmetic units are more useful in application specific integrated circuit (ASIC) based processor designs that are used in servers and datacenters. The whole thesis is composed of five parts with eight chapters shown as follows:

#### • Part I Preface includes:

- Chapter 1 Introduction: presents the importance of deep learning and the motivations,

the overview, and the contributions of the research works.

- Chapter 2 *Background*: introduces the background information required to present the proposed research works.

#### • Part II Arithmetic Unit for General Purpose Computing includes:

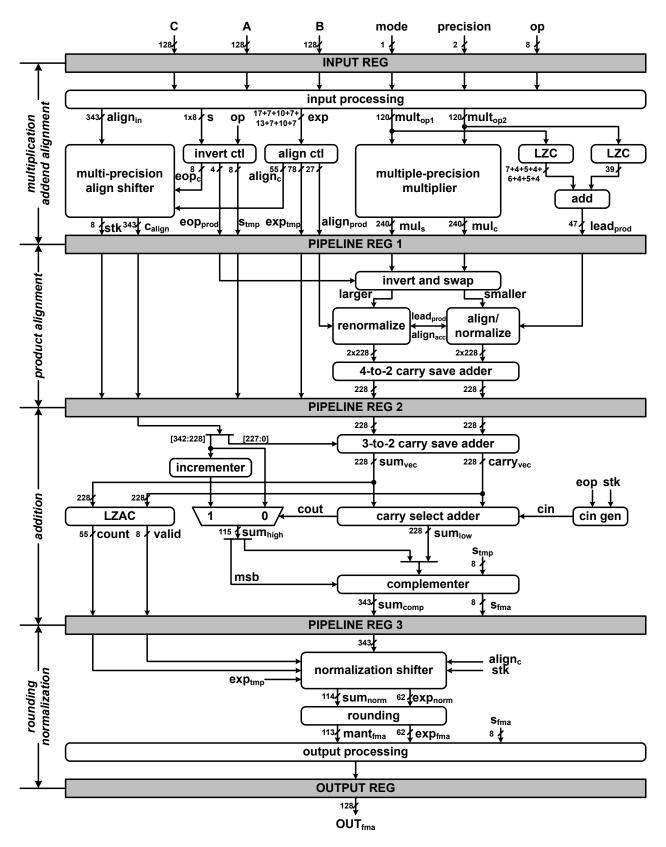

- Chapter 3 Multiple-Precision Floating-Point Fused Multiply Add: presents the design of a multiple-precision floating-point fused multiply add (FMA) architecture. In this chapter, the solution to optimize general purposed FPU for deep learning computation is presented. The architecture presented is designed for general purposed FPU. However, the newly added parallel half-precision supports and mixed-precision dot-product supports make the proposed design especially suitable for deep learning computation. Compared to the state-of-the-art multiple-precision floating-point FMA architectures, the newly added features make the proposed FMA supporting more functions with only minor resource overhead.

#### • Part III Arithmetic Unit for Deep Learning Computing includes:

- Chapter 4 Multiple-Precision Multiply Accumulate Unit: presents an efficient fixed-point and floating-point merged MAC unit architecture. This unit is proposed for deep learning processors that need to handle both deep learning training and inference operations. The support for floating-point computations can be used in deep learning training and the support for fixed-point computations can be used in deep learning inference. In addition, the mixed-precision computation feature is introduced to this

unit to make it more suitable in deep learning computation. Compared to a floatingpoint MAC unit, the proposed design has negligible resource overhead but enables the deep learning processors to support both training and inference operations.

- Chapter 5 Flexible Multiple-Precision Multiply Accumulate Unit: presents a flexible multiple-precision MAC unit architecture. The proposed unit also supports both floating-point operations and fixed-point operations. In floating-point mode, both 16-bit or dual 8-bit operations are supported. In fixed-point mode, 16-bit or dual 8-bit or quad 4-bit operations are supported. At the lowest precision, the proposed unit also supports logic operations for binary neural networks. In order to make the proposed unit more flexible, in floating-point mode, the bit-width of exponent and mantissa can be mutually exchanged. In fixed-point mode, the bit-width of integer and fraction can also be exchanged. Compared to a 16-bit floating-point MAC unit, the proposed unit provides more flexibility for deep learning computation with only minor resource overhead.

- Chapter 6 Posit Multiply Accumulate Unit: presents an MAC architecture designed based on the posit number format. Posit number format encodes the numbers in a non-uniform way which fits well with the deep learning data distribution. In addition, with the same bit-width, posit can provide much larger dynamic range than the floating-point format. As the range is more important than precision for deep learning accuracy, posit is expected to be promising in deep learning applications. The proposed posit MAC unit in this chapter is intended to facilitate the use of posit format in deep learning applications.

#### • Part IV Arithmetic Unit for 3D Memory includes:

- Chapter 7 Improved Hybrid Memory Cube Architecture: presents an improved HMC architecture for deep neural network processing. The proposed architecture is designed based on the original HMC architecture with minimal modification in order to avoid thermal problem. Two new instructions are added for weight-sharing deep learning computation. The memory vault controller is also modified to support parallel vault operations. Moreover, a simple MAC unit is added to the logic layer for

each memory vault to achieve deep learning computation. A software simulation of the proposed architecture is performed and the results show a reduced memory bandwidth requirement and thus an improved speed performance.

#### • Part V Conclusion includes:

Chapter 8 Summary and Future Work: includes the summary of all presented research works and the plan for future works.

# 1.4 Summary of Contributions

In this thesis, several new arithmetic unit architectures are designed and implemented for efficient deep learning computation. Some of them are the first published designs which introduced new computation features or combined multiple features into a single architecture. Those proposed arithmetic units are ready to be combined with memory module and control module into a flexible and efficient deep neural network processors. For each of the proposed arithmetic units, the hardware design merits, including timing, area, power, and energy, are analyzed in detail. The designs are also compared with related designs available in the literature to show their advantages and improvements. For the flexible MAC design, a simplified neural network case study is included to show its performance under different application scenarios. Finally, a hybrid memory cube architecture is proposed to overcome the limitations of the conventional memory interface to achieve better speed performance and energy efficiency for deep learning computation. Moreover, our proposed posit based MAC unit could be a starting point of research works that utilize the posit number system in deep learning applications.

Below is the list of publications, arranged according to the order of appearance in this thesis:

- Chapter 3 Multiple-Precision Floating-Point Fused Multiply Add:

- H. Zhang, D. Chen and S. Ko, "Efficient Multiple-Precision Floating-Point Fused Multiply-Add with Mixed-Precision Support," in *IEEE Transactions on Computers*, vol. 68, no. 7, pp. 1035-1048, Jul 2019.

- Chapter 4 Multiple-Precision Multiply Accumulate Unit:

- H. Zhang, H. J. Lee and S. Ko, "Efficient Fixed/Floating-Point Merged Mixed-Precision Multiply-Accumulate Unit for Deep Learning Processors," 2018 IEEE International Symposium on Circuits and Systems (ISCAS), May 2018, pp. 1-5.

- Chapter 5 Flexible Multiple-Precision Multiply Accumulate Unit:

- H. Zhang, D. Chen and S. Ko, "New Flexible Multiple-Precision Multiply Accumulate Unit for Deep Neural Network Training and Inference," *IEEE Transactions on Computers*, accepted August 2019.

- Chapter 6 Posit Multiply Accumulate Unit:

- H. Zhang, J. He and S. Ko, "Efficient Posit Multiply-Accumulate Unit Generator for Deep Learning Applications," 2019 IEEE International Symposium on Circuits and Systems (ISCAS), May 2019, pp. 1-5.

- Chapter 7 Improved Hybrid Memory Cube Architecture:

- H. Zhang, J. He and S. Ko, "Improved Hybrid Memory Cube for Weight-Sharing Deep Convolutional Neural Networks," 2019 IEEE International Conference on Artificial Intelligence Circuits and Systems (AICAS), March 2019, pp. 1-5.

- Other publications that are not included in this thesis:

- H. Zhang, D. Chen and S. Ko, "Area- and Power-Efficient Iterative Single/Double-Precision Merged Floating-Point Multiplier on FPGA," in *IET Computers and Digital Techniques*, vol. 11, no. 4, pp. 149-158, Jul 2017.

- H. Zhang, D. Chen and S. Ko, "High Performance and Energy Efficient Single-Precision and Double-Precision Merged Floating-Point Adder on FPGA," in *IET Computers and Digital Techniques*, vol. 12, no. 1, pp. 20-29, Jan 2018.

- Y. Wang, K. Shahbazi, H. Zhang, K. Oh, J. Lee and S. Ko, "Efficient Spiking Neural Network Training and Inference with Reduced Precision Memory and Computing," accepted by *IET Computers and Digital Techniques*, Jun 2019.

- K. Chae, G. Jin, S. Ko, Y. Wang, H. Zhang, E. Choi and H. Choi, "Deep Learning for Classification of A Small (≤ 2cm) Pulmonary Nodule on CT Imaging: A Preliminary Study," accepted by *Elsevier Academic Radiology*, May 2018.

- Z. Jiang, H. Zhang, Y. Wang and S. Ko, "Retinal Blood Vessel Segmentation Using Fully Convolutional Network with Transfer Learning," in *Elsevier Computerized Medical Imaging and Graphics*, vol. 68, pp. 1-15, Sep 2018.

- L. Han, H. Zhang and S. Ko, "Decimal Floating-Point Fused Multiply-Add with Redundant Internal Encodings," in *IET Computers and Digital Techniques*, vol. 10, no. 4, pp. 147-156, Jul 2016.

- L.Han, H.Zhang and S. Ko, "Area and Power Efficient Decimal Carry-Free Adder,"

in IET Electronics Letters, vol. 51, no. 23, pp. 1852-1854, Nov 2015.

- Y. Wang, H. Zhang, K. Chae, G. Jin and S. Ko, "Novel Convolutional Neural Network Architecture for Improved Pulmonary Nodule Classification on Computed Tomography," under review Multidimensional Systems and Signal Processing, submitted Mar 2019.

- Y. Wang, E. Choi, H. Zhang, G. Jin and S. Ko, "Breast Cancer Classification in Automated Breast Ultrasound using Multi-View CNN with Transfer Learning," under review *Ultrasound in Medicine and Biology*, submitted Jul 2019.

# Chapter 2

# Background

This chapter presents the background information of the proposed works in this thesis. Various numerical formats that are used in the proposed works are presented in Section 2.1. Section 2.2 presents the basic architectures of fused arithmetic units including fused multiply add unit and multiply accumulate unit. Section 2.3 presents the concepts and advantages of mixed-precision computing. Section 2.4 presents the characteristics of deep learning computing in detail which motivate the research works in this thesis. Section 2.5 presents the architecture of a hybrid memory cube.

## 2.1 Numerical Formats

## 2.1.1 Floating-Point Format

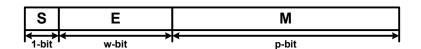

The binary floating-point number formats defined in IEEE 754-2008 contain three components: 1-bit sign (S), w-bit biased exponent (E), and p-bit mantissa (M), as shown in Figure 2.1. The biased exponent E is obtained by e + bias, where e is the actual exponent value and  $bias = 2^{w-1} - 1$ . There is always an implicit bit in front of the mantissa.

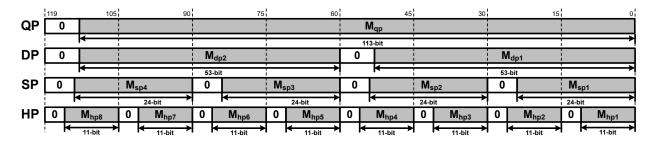

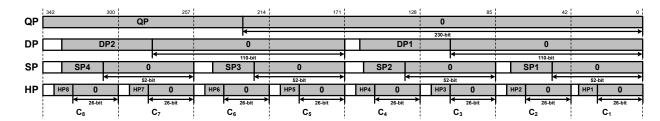

The basic precision formats defined in IEEE 754-2008 are 16-bit half-precision (HP), 32-bit single-precision (SP), 64-bit double-precision (DP), and 128-bit quadruple-precision (QP). For these four formats, the bit-width of each component, the bias value, and the maximum and minimum exponent for normal number is summarized in Table 2.1.

Figure 2.1: Binary floating-point format defined in IEEE 754-2008

Table 2.1: Floating-Point format defined in IEEE 754-2008

| Format     | Sign | Exponent | Mantissa | Bias  | $e_{max}$ | $e_{min}$ |

|------------|------|----------|----------|-------|-----------|-----------|

| 16-bit HP  | 1    | 5        | 10       | 15    | 15        | -14       |

| 32-bit SP  | 1    | 8        | 23       | 127   | 127       | -126      |

| 64-bit DP  | 1    | 11       | 52       | 1023  | 1023      | -1022     |

| 128-bit QP | 1    | 15       | 112      | 16383 | 16383     | -16382    |

The IEEE 754-2008 floating-point format also reserves some special values for exceptional cases handling. The floating-point number T represented in IEEE 754-2008 format and its actual value v can be summarized as follows:

- If  $E = 2^w 1$  and  $M \neq 0$ , then T is not a number (NaN).

- If  $E = 2^w 1$  and M = 0, then T is infinity (Inf) and  $v = (-1)^S \times (+\infty)$ .

- If  $1 \le E \le 2^w 2$ , then T is normal number and  $v = (-1)^S \times (1 + M) \times 2^{E-bias}$ . Normal number has an implicit bit of 1.

- If E=0 and  $M\neq 0$ , then T is subnormal number and  $v=(-1)^S\times M\times 2^{1-bias}$ . Subnormal number has an implicit bit of 0.

- If E = 0 and M = 0, the T is zero and  $v = (-1)^S \times (+0)$ .

#### Rounding in IEEE 754-2008

When performing floating-point operations, such as addition and multiplication, the infinitely precise intermediate results will usually have larger bit-width than the format defined bit-width. In order to make these results be accommodated into the IEEE 754-2008 defined formats, rounding operations are required. In IEEE 754-2008, five rounding modes are defined:

• roundTiesToEven: the infinitely precise result should be rounded to the nearest representable floating-point number. If two numbers are equally near to the result, the one with an even least significant bit (LSB) should be used. This is the default rounding mode of IEEE 754-2008 standard.

- round Ties To Away: the infinitely precise result should be rounded to the nearest representable floating-point number. If two numbers are equally near to the result, the one with a larger magnitude should be used.

- roundTowardPositive: the infinitely precise result should be rounded to the floatingpoint number that is closet to and no less than the result.

- roundTowardNegative: the infinitely precise result should be rounded to the floatingpoint number that is closet to and no greater than the result.

- roundTowardZero: the infinitely precise result should be rounded to the floating-point number that is closet to and no greater in magnitude than the result.

#### Exception Handling in IEEE 754-2008

IEEE 754-2008 standard also defines several default exception handling: invalid operation, division by zero, overflow, underflow, and inexact. When these exception cases happen, the corresponding flags are required to be raised.

- Invalid operation: this exception is signaled when there is no definable result.

- any computational operation on a signaling NaN.

- multiplication in a form of  $0 \times \infty$  or  $\infty \times 0$ .

- fused multiply-add in a form of  $0 \times \infty + c$  or  $\infty \times 0 + c$  unless c is a quiet NaN.

- addition, subtraction, or fused multiply-add: magnitude subtraction of infinities.

- division:  $0 \div 0$  or  $\infty \div \infty$ .

- remainder: remainder(x, y) when y is zero or x is infinite and neither is NaN.

- square root if the operand is less than zero.

- quantize when the result does not fit in the destination format or when one operand

is finite and the other is infinite.

- conversion of a floating-point number to an integer format, when the source is NaN, infinity, or a value that would convert to an integer outside the range of the result format under the applicable rounding attribute.

- comparison by way of unordered-signaling predicates when operands are unordered.

- $-\log B(NaN), \log B(\infty), \text{ or } \log B(0) \text{ when the output of } \log B \text{ is an integer format.}$

- Division by zero: this exception is signaled when an exact infinite result is defined for an operation on finite operands.

- for division, when the divisor is zero and the dividend is a finite non-zero number,

the sign of the infinity is the exclusive OR of the operands' signs.

- -log B(0) when result of log B is a floating-point format, the sign of the infinity is minus  $(-\infty)$ .

- Overflow: this exception is signaled when the format's largest finite number is exceeded in magnitude. The default result is determined by the rounding method and the sign of the intermediate result:

- round TiesToEven and round TiesToAway carry all overflow to  $\infty$  with the sign of the intermediate result.

- roundTowardZero carries all overflows to the format's largest finite number with the sign of the intermediate result.

- roundTowardNegative carries positive overflows to the format's largest finite number and carries negative overflows to  $-\infty$ .

- roundTowardPositive carries negative overflows to the format's most negative number and carries positive overflows to  $+\infty$ .

- Underflow: this exception is signaled when a tiny non-zero result is detected. A rounded result should be provided which might be zero, subnormal, or  $\pm b^{emin}$ .

- after rounding: a non-zero result computed as though the exponent range were unbounded would lie strictly between  $\pm b^{emin}$ .

- before rounding: a non-zero result computed as though both the exponent range and the precision were unbounded would lie strictly between  $\pm b^{emin}$ .

- Inexact: this exception is signaled when the rounded result is different from what would have been computed if both exponent range and precision were unbounded.

**Table 2.2:** Results when both addition/subtraction operands are zeros

| $x 	ext{ op } y$ | Rounding 2                   | Mode                 |

|------------------|------------------------------|----------------------|

| w op y           | RTN, RTZ, RTPos $^{\dagger}$ | $ m RTNeg^{\dagger}$ |

| (+0) + (+0)      | +0                           | +0                   |

| (+0) + (-0)      | +0                           | -0                   |

| (-0) + (+0)      | +0                           | -0                   |

| (-0) + (-0)      | -0                           | -0                   |

| (+0) - (+0)      | +0                           | -0                   |

| (+0) - (-0)      | +0                           | +0                   |

| (-0) - (+0)      | -0                           | -0                   |

| (-0) - (-0)      | +0                           | -0                   |

<sup>†</sup> RTN: roundTiesToEven; RTZ: roundTowardZero; RTPos: roundTowardPositive; RTNeg: roundTowardNegative.

#### The Sign of the Operational Result

In IEEE 754-2008 standard, the sign is not interpreted if either an input or result is NaN. If neither the inputs nor results are NaN, the sign of a product or quotient is the exclusive OR of the operands' signs.

The sign of an addition or subtraction is determined by the relationship between the two operands. When the sum of two operands with opposite signs (or the difference of two operands with the same sign) is exactly zero, the sign of the sum is positive except roundTowardNegative where the sign of an exact zero sum is negative. However, x + x = x - (-x) retains the same sign as x even when x is zero. When both operands are zero, depending on the rounding methods, the results are summarized in Table 2.2.

For FMA operations, if the infinite precise result is exactly zero, the sign of the result should be determined by the rules for a sum of operands. When the exact result is non-zero but the result is zero because of rounding, the resulting zero takes the sign of the exact result.

In this thesis, the research work presented in Chapter 5 uses customized floating-point formats. Although they may have different bit-width from the standard ones, the floating-point conventions defined in IEEE 754-2008, such as the biased exponent, implicit mantissa bit, and subnormal cases handling, still apply.

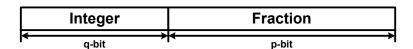

Figure 2.2: Binary fixed-point format

#### 2.1.2 Fixed-Point Format

Fixed-point format is much simpler than the floating-point format. It does not have the exponent field and all bits belong to the significand as shown in Figure 2.2. Therefore, with the same total bit-width, the fixed-point format has smaller representation range than that of the floating-point format.

There are two categories of fixed-point format: signed and unsigned. For unsigned number, its value can be determined by

$$v = \sum_{i=0}^{q-1} I_i \times 2^i + \sum_{j=0}^{p-1} F_j \times 2^{-(p-j)}$$

(2.1)

where  $I_i$  represents the *i*-th bit of the integer and  $F_j$  represents the *j*-th bit of the fraction.

For signed number, the most significant bit (MSB) represents its sign. For zero and positive number, the sign is equal to 0 and for negative number, the sign is equal to 1. For signed number, its value can be determined by

$$v = (-1)^{I_{q-1}} \times 2^{q-1} + \sum_{i=0}^{q-2} I_i \times 2^i + \sum_{j=0}^{p-1} F_j \times 2^{-(p-j)}$$

(2.2)

The signed fixed-point formats used in this thesis use the two's complement encoding which is widely used in modern computer systems. In two's complement encoding, a non-negative number has the same notation as the number written in unsigned notation. For a negative number, the encoding can be obtained by inverting all bits of the notation of its absolute value and then adding one to the LSB.

For fixed-point numbers, extension is often required when converting from one numerical format to another format with larger bit-width. For a pure fractional number, the extension can be done by simply adding multiple zero bits to the right of the LSB. When extending the integer part, there is some differences between the unsigned number and signed number. For unsigned numbers, the extension can be done with prefixing zero bits. For signed numbers

represented in two's complement format, the extension is done with replicating the sign bit. On the other hand, when converting a number with large bit-width to a format with smaller bit-width, the rounding process that is used in floating-point operations can be used for fractional part. For integer part, usually a truncation is performed to remove the unused most significant several bits.

In deep neural networks, weights contain both positive and negative values and should be represented with signed numbers if fixed-point format is used. For activations, as most current deep neural networks use rectified linear unit (ReLU) as their activation function, the activations are always non-negative numbers and thus can be represented with unsigned fixed-point format. For hardware design, the unsigned format can always be prefixed with one more bit zero to be converted to signed format. In this thesis, the fixed-point units are designed with signed format.

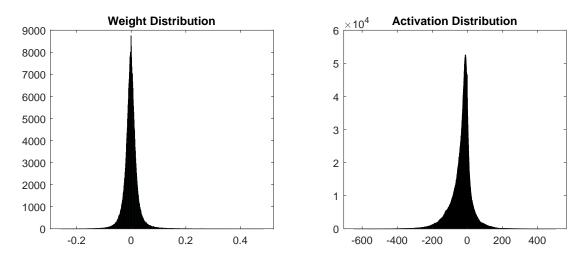

#### 2.1.3 The Posit Format

The floating-point format and fixed-point format described in the above sections use uniformed encoding for all numbers. In this way, after the format is determined (for example 32-bit floating-point numbers with 8-bit exponent and 23-bit mantissa), all the numbers within the representation range are represented using the same format. This is fine for general-purpose computing. However, for some applications with non-uniformed data distribution, such as deep learning (this will be discussed in Section 2.4), uniformed encoding become inefficient. For these applications, on one hand, data with small values are densely appeared so that a high precision (large bit-width of mantissa) is required to distinguish these small values. On the other hand, data with large values and tiny values can also appear, and thus a large dynamic range (large bit-width of exponent) is required to correctly represent these numbers. Consequently, a large floating-point format is required to meet these two requirements which leads to an expensive cost in arithmetic and memory operations. However, in these applications, the large exponent bit-width and large mantissa bit-width are not always required at the same time. For densely distributed small values, a large bit-width mantissa is needed but the exponent bit-width can be small. For sparsely distributed large or tiny values, a large bit-width exponent is needed but the mantissa bit-width can be small.

| sign | regime, exponent, fraction                                    |

|------|---------------------------------------------------------------|

| s    | (r, r,, ~r), (e <sub>es-1</sub> ,e <sub>0</sub> ), (fraction) |

Figure 2.3: Format of posit number

Therefore, the encoding for the numerical values in these applications can be improved.

In posit number system [16], a non-uniformed encoding method is applied where the total bit-width is a constant but the bit-width of components can be changed. This characteristic fits well with the data distribution of deep learning applications. For densely distributed small values, more bits can be allocated to the mantissa. For sparsely distributed large or tiny values, the exponent can occupy more bits. Therefore, the total bit-width of posit numbers when compared to the conventional floating-point numbers can be reduced in deep learning applications.

The general format of a posit number is shown in Figure 2.3. A posit format, Posit(nb, es), is defined with the total bit-width nb and the maximum exponent bit-width es. Except the sign bit has a fixed 1-bit bit-width, the bit-width of all other components, the regime, the exponent, and the mantissa, are flexible. Exponent and fraction appear only when there is remaining bits for them. A sign bit of zero represents a positive number and a sign bit of one represents a negative number. If a number is negative, two's complement will be taken before decoding components.

The regime part is first considered. It is a series of 0s or 1s followed by a bit with an opposite value. The number of 1s or 0s is corresponding to the regime value rg. If the regime bits start with m-bit zeros followed by a one bit, then rg = -m. On the other hand, if the regime bits start with m-bit ones followed by a zero bit, then rg = m - 1. Then if the sign and regime do not occupy the whole nb-bit, the exponent is followed. Its maximum bit-width is defined with es. Exponent is an unsigned value without bias. Then the remaining bits are allocated to fraction frac. There is always an implicit one bit for the frac. The value of a number represented in posit format is:

$$v = (-1)^s \times useed^{rg} \times 2^{exp} \times (1 + frac)$$

(2.3)

where  $useed = 2^{2^{es}}$ . Zero is represented as all zero bits and infinity is represented as 1-bit one followed by all zeros. There is no subnormal in posit format.

**Table 2.3:** Comparison of the dynamic range of Posit format and floating-point format

| Format                  | Min. Value <sup>†</sup>                    | Max. Value <sup>†</sup>                  | Dynamic Range*                              |

|-------------------------|--------------------------------------------|------------------------------------------|---------------------------------------------|

| Std FP8 Posit(8,4)      | $2 \times 10^{-3} \\ 1 \times 10^{-29}$    | $3 \times 10^2$ $8 \times 10^{28}$       | $1.5 \times 10^5 \\ 8.0 \times 10^{57}$     |

| Std FP16<br>Posit(16,5) | $6 \times 10^{-8} \\ 1 \times 10^{-135}$   | $7 \times 10^4$<br>$7 \times 10^{134}$   | $1.2 \times 10^{12}$ $7.0 \times 10^{269}$  |

| Std FP32<br>Posit(32,8) | $1 \times 10^{-45} \\ 8 \times 10^{-2309}$ | $4 \times 10^{38} \\ 8 \times 10^{2311}$ | $4.0 \times 10^{83}$ $1.0 \times 10^{4620}$ |

<sup>†</sup> absolute value.

The comparison of the dynamic range of some posit formats with standard floating-point formats is shown in Table 2.3. Due to the use of a dynamic regime component, the representation of posit is much larger than the conventional floating-point format with the same bit-width. However, due to the bit-width of each component is dynamic during runtime, extra hardware is required to correctly extract each component from input operands and to correctly pack the resulting components into the output format. The details of the posit hardware designs will be discussed in Chapter 6.

#### 2.2 Fused Arithmetic Units

Multiplier and adder are two common operators used in many applications. Conventionally the multiplier and adder are usually designed as separate hardware units. However, consecutive multiplication and addition operations (for example,  $y = \sum x \times w + b$ ) are commonly used in many applications, such as signal processing and machine learning. In these applications, a fused arithmetic unit is desired to improve the computing performance.

There are three categories of fused arithmetic units that are popularly used: the FMA, MAC, and dot-product (DOT, or sum of product, SoP). FMA is usually referred to floating-point operations while MAC is usually referred to fixed-point operations. Both of them are designed to perform the operations in the form of  $A \times B \pm C$ . For FMA, three operands, A, B, and C, are in the same numerical precision, while in MAC, the precision of C is usually higher than A and B. DOT is common for both fixed-point and floating-point. The i-way

<sup>\*</sup> dynamic range = max. value / min. value.

**Figure 2.4:** Implementing floating-point  $A \times B + C$  with separate arithmetic units and fused arithmetic unit

DOT is designed to perform the operation of  $\sum_{i} (A_i \times B_i) + C$ .

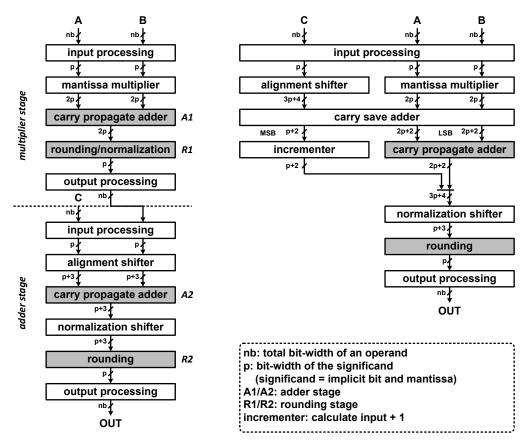

The first floating-point FMA architecture was proposed and used in IBM RS/6000 processor [19]. It combined the floating-point multiplication and addition into a single operation. The right part of Figure 2.4 shows a simplified FMA data-path when computing  $A \times B + C$ . The p-bit mantissa of A and B are multiplied. The multiplier contains a partial product generation unit and partial product accumulate unit and a carry-save format product is generated. In parallel to the multiplication, the alignment of C is performed. After the product is generated, the aligned C should also be available. The aligned C and the product then go through one stage of (3,2) carry save adder (CSA) to be accumulated into two vectors. Then the generated two vectors are added using a carry propagate adder (CPA). Only the LSB 2p + 2-bit vectors should go into the CPA. The MSB p + 2-bit only contains one vector and can be added with an incrementer. Then the addition result is normalized and rounded and the output is generated.

Figure 2.4 also compares the whole data-path when implementing  $A \times B + C$  using separate multiplier and adder and FMA unit. In the separate units implementation, the multiplier and the adder use separate adders (A1 and A2) while in the FMA unit, the multiplication and addition can share one CPA. This will lead to a reduction in hardware area. Moreover, FMA can generate a result with better accuracy than separate multiplier and adder. On one hand, in the separate units implementation, rounding operations are performed twice while FMA only performs one rounding. On the other hand, the addition data-path of the FMA is larger than that of the separate adder. Therefore, more bits can be reserved to participate the future computation stages. In addition, the FMA unit can also be used to perform normal multiplication operation or addition operation: by setting B=1, the FMA can compute A+C and by setting the absolute value of C to 0, the FMA can compute  $A\times B$ . In order to ensure the multiplication is compliant with IEEE 754-2008 standard [8], the sign of C must be determined according to the sign of  $A \times B$  and the rounding mode. In roundTiesToEven, roundTowardZero, or roundTowardPositive modes, if the sign of  $A \times B$  is positive, then C can be set to +0 or -0. However, when the sign of  $A \times B$  is negative, C also needs to be set to -0. Moreover, in roundTowardNegative mode, the sign of C must be the same as that of  $A \times B$ .

Due to the above mentioned advantages, FMA was added into the IEEE 754-2008 standard and many processors use FMA as their basic FPU architecture. The MAC unit has similar data-path to the FMA except that the bit-width of the carry propagate adder may be larger since the precision of C is larger than A and B in MAC. DOT unit can be designed by implementing multiple multipliers followed by a large carry propagate adder. When floating-point formats are used, the products are needed to be aligned with each other before the final addition.

For those arithmetic units proposed in this thesis, if only floating-point formats are supported, such as the design discussed in Chapter 3, the design is called FMA unit. When both floating-point and fixed-point are supported, such as the ones in Chapter 4 and Chapter 5, the design is termed as MAC unit. The posit based design discussed in Chapter 6 is termed as MAC unit since the format of A, B and C could be different.

Figure 2.5: Datapath of a mixed-precision FMA

#### 2.3 Mixed-Precision Arithmetic Units

Mixed-precision arithmetic units use different precisions at different computation phases. The conventional MAC architecture is a mixed-precision unit since C has different precision from A and B. The FMA unit can be modified by extending the precision of C and the adder data-path to realize mixed-precision operations. Mixed-precision arithmetic units are usually used in application-specific computing system designs. Due to the mixed-precision feature, it usually designed in a fused arithmetic unit. The use of mixed-precision arithmetic unit has mainly two advantages: (1) the multiplication can be done with low precision to improve the computing speed. (2) the addition is done with high precision to maintain a highly accurate result.

Mixed-precision operations are suggested to be used in deep learning together with reduced precision computing in [10]. Many reduced precision deep neural network training methods require the mixed-precision computing to maintain the accuracy [9] [20]. In the field of linear algebra, the mixed-precision method is also widely used to perform the itera-

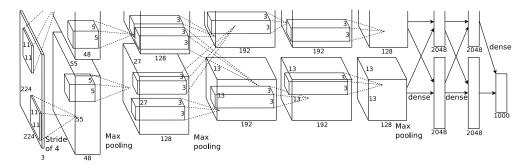

Figure 2.6: Architecture of AlexNet (From: Figure 2 of reference [1].)

tive refinement operations. In [21], a two precisions mixed-precision method is proposed and in [22], a three precisions mixed-precision method is proposed. Both methods can maintain the same level of accuracy as the one when computing with only high precision numbers while achieving significant speedup.

A simplified hardware mixed-precision FMA architecture is shown in Figure 2.5. It is also used to compute  $A \times B + C$  but now C has higher numerical precision than A and B. The data-path shown in Figure 2.5 assumes the mantissa bit-width of C is larger than twice the mantissa bit-width of A and B. (For other cases, the data-path bit-width should be modified accordingly.) The multiplication is done in p precision while the alignment, addition, normalization, and rounding are done with q precision.

## 2.4 Deep Learning Computing

#### 2.4.1 Overview

Deep neural networks are usually composed of convolutional layers (CONV), fully-connected layers (FC), activation layers, and pooling layers. The architecture of AlexNet, which is a popular convolutional neural network (CNN) architecture, is shown in Figure 2.6. It consists of 5 CONVs followed by 3 FCs. Activation layers are used after each FC and CONV and pooling layers are applied after the second, third and fifth CONVs.

The majority of the computations happens in convolutional layers [5]. For AlexNet, to generate one output, a total of 724 million multiply-accumulate operations are required where the five CONVs contain 665 million MAC operations.

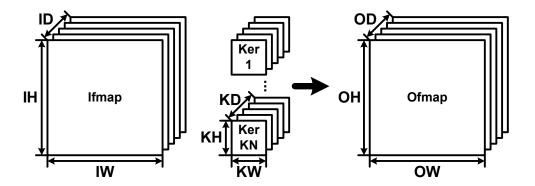

Figure 2.7: Process of convolution computation in deep neural network

The process of calculating a convolution in a deep neural network is shown in Figure 2.7. There are ID input feature maps (Ifmap) of size  $IH \times IW$  and KN kernels (Ker) of size  $KD \times KH \times KW$ . They are used to generate OD output feature maps (Ofmap) of size  $OH \times OW$ . In deep neural network, KD = ID and OD = KN. Assume the amount of zero padding is P for input feature maps and the stride of kernel, which is the amount of pixels of each kernel sliding, is represented with S, then size of the Ofmap can be generated from the size of Ifmap with equation (2.4):

$$OH = (IH + 2P - KH)/S + 1$$

$OW = (IW + 2P - KW)/S + 1$  (2.4)

Then, the value of each pixel in Ofmaps can be calculated with equation (2.5):

$$O[m][x][y] = act(B[m] + \sum_{i=0}^{KW-1} \sum_{j=0}^{KH-1} \sum_{k=0}^{ID-1} I[k][Sx+i][Sy+j] \times W[m][k][i][j])$$

$$0 \le m < OD, \ 0 \le x < OW, \ 0 \le y < OH$$

$$(2.5)$$

where O, B, I, W represent output feature map, bias, input feature map (after padding), and kernel, respectively, and act() represents the activation function. When the feature map size is large or the number of feature maps is large, the amount of required computations will be large. In addition, the majority of computations is in the form of multiply-accumulate. For FC layer computation, similar equations can be applied with KW = IW and KH = IH.

Figure 2.8: Weights and activations distribution of AlexNet Convolution Layer 2

#### 2.4.2 Reduced Precision Computations

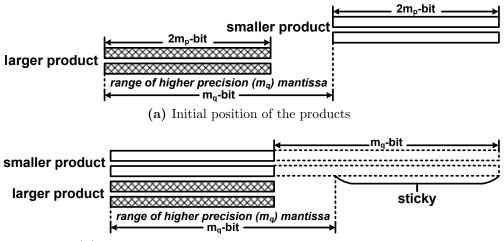

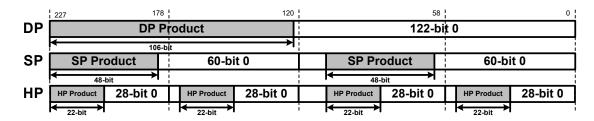

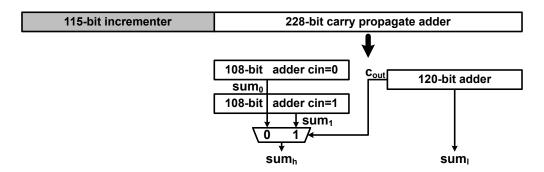

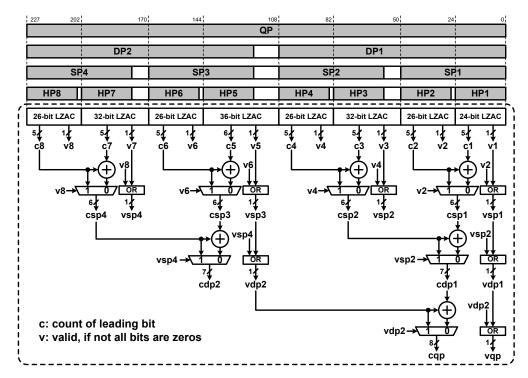

Deep neural networks are usually trained using GPUs where the 32-bit single-precision floating-point format is the default computing format. Therefore, many pre-trained neural network models come with single-precision floating-point parameters. However, the costs of implementing single-precision operators are expensive. For deep neural networks, they are computationally intensive. Therefore, the overall cost, including timing and energy, of implementing deep neural network with single-precision format is high. In order to reduce the implementation cost, many research works focus on reduced precision computations for deep neural networks.