### Old Dominion University ODU Digital Commons

**Computer Science Theses & Dissertations**

**Computer Science**

Fall 1991

## Approaches to High Speed Networks

Frank Charles Paterra Old Dominion University

Follow this and additional works at: https://digitalcommons.odu.edu/computerscience\_etds Part of the <u>Computer Sciences Commons</u>

### **Recommended** Citation

Paterra, Frank C.. "Approaches to High Speed Networks" (1991). Doctor of Philosophy (PhD), dissertation, Computer Science, Old Dominion University, DOI: 10.25777/0djz-a286 https://digitalcommons.odu.edu/computerscience\_etds/122

This Dissertation is brought to you for free and open access by the Computer Science at ODU Digital Commons. It has been accepted for inclusion in Computer Science Theses & Dissertations by an authorized administrator of ODU Digital Commons. For more information, please contact digitalcommons@odu.edu.

Approaches to High Speed Networks

by

Frank Charles Paterra B.S. Computer Science, May 1986, Frostburg State College M.S. Computer Science, August 1989, Old Dominion University

A Dissertation submitted to the Faculty of Old Dominion University in Partial Fulfillment of the Requirements for the Degree of

### DOCTOR OF PHILOSOPHY

**Computer Science**

#### OLD DOMINION UNIVERSITY

November, 1991

Approved by:

C. Michael Overstreet LAdvisor?

7

Kurt J. Maly (Advisor)

Ravi Mukkamala

Mark Pardue

Copyright by Frank Charles Paterra 1991 All Rights Reserved

.

This work is sponsored in part by grants from Sun Microsystems.

### Acknowledgements

Few accomplishments can really be claimed by a single person. I would like to acknowledge some of the people who made this effort possible. First I would like to thank my advisors. Mike Overstreet and Kurt Maly. Mike, you have been more than a friend to me. and your true kindness has given me comfort many times. Kurt your drive for work has been an inspiration to me. I am sure that without it, I could never have completed this research. I would also like to thank the other members of my committee. Ravi Mukkamala and Mark Pardue, for their thoughtful comments and guidance.

I would like to recognize my fellow graduate students, especially Sanjay Khanna and David Game. David, thank you for your advice and your friendship. Sanjay, you have more than generous to me, I wish you success in the pursuit of your degree.

The one teacher has made the largest impact on my life was Dr. Robin Kranz of Frostburg State College. You taught me that it is ok to admit when I don't know something.

To my parents, Frank and Mary Elizabeth, I would like to thank you for teaching me that there is really nothing a person cannot do as long as they are willing to work for it. Thank you for letting me try my wings and for letting me fall on my own. You have taught me the most important lessons of my life.

Finally, I would like to thank my wife and best friend, Norizan. You have been a source of energy and encouragement to me and have sacrificed so much to allow me to complete my degree. I love you very much and I hope that I can be of as much support to you in fulfilling your dreams and goals.

iii

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

# Contents

.....

| 1 | Int         | troduc        | tion and Problem Statement                                      | 1         |

|---|-------------|---------------|-----------------------------------------------------------------|-----------|

|   | 1.1         | Wha           | t is High Speed Networking                                      | 1         |

|   | 1.2         | Prob          | lems in High Speed Communication                                | $^{2}$    |

|   | 1.3         | Why           | High Speed, Reliable. Data Communication is Important           | 5         |

|   | 1.4         | Focu          | s of This Research                                              | 7         |

| 2 | Sui         | rvey          |                                                                 | 8         |

|   | 2.1         | Solut         | ions to Communication Problems                                  | 8         |

|   |             | 2.1.1         | Media                                                           | 9         |

|   |             | 2.1.2         | Media Access Control Protocols                                  | 9         |

|   |             | 2.1.3         | Transport and Network Protocols                                 | 13        |

| 3 | Opt         | tions in      | n Parallel Communication                                        | 19        |

|   | <b>3.</b> 1 | Introd        | luction                                                         | 19        |

|   | 3.2         | Taxon         | omies in Parallelism                                            | 20        |

|   | 3.3         | Оррог         | tunities and Problems in Parallelism                            | 24        |

|   |             | <b>3.3</b> .1 | Application Layer                                               | 25        |

|   |             | 3.3.2         | Alternative Architectures to Parallelism at the Transport Layer | <b>26</b> |

|   |             | 3.3.3         | Network Layer                                                   | 32        |

|   |             | 3.3.4         | Media Access Layer                                              | 3:;       |

|   |                            | <b>3.3.</b> 5 Physical Media                           | <b>3</b> 4 |

|---|----------------------------|--------------------------------------------------------|------------|

|   |                            | 3.3.6 Parallelism in the Complete Communication System | 34         |

|   | 3.4                        | Sensitivity Analysis                                   | 38         |

|   | <b>3</b> .5                | Description of System Components                       | 38         |

|   | <b>3</b> .6                | Study Environment                                      | 39         |

|   | 3.7                        | Analysis Definitions                                   | 40         |

|   | <b>3</b> .8                | The Analysis                                           | 47         |

|   | <b>3</b> .9                | Discussion                                             | 52         |

| 4 | $\mathbf{E}\mathbf{x}_{j}$ | perimental Results                                     | 54         |

|   | 4.1                        | Scope and Objective                                    | 54         |

|   | 4.2                        | Design of the Case Study                               | 56         |

|   |                            | 4.2.1 Testbed Description                              | 56         |

|   |                            | 4.2.2 The Experiment – Parameters and Environment      | 60         |

|   | 4.3                        | Performance                                            | 62         |

|   | 4.4                        | System Implementation                                  | 67         |

|   | 4.5                        | Discussion                                             | 69         |

| 5 | Sim                        | ulation Results                                        | 72         |

|   | 5.1                        | Introduction                                           | 72         |

|   | 5.2                        | Simulation Environment and Goals                       |            |

|   | 5.3                        | Approach                                               | 73         |

|   | 5.4                        | Software Design Issues - The Transport Layer           | 74         |

|   |                            | 5.4.1 Application-Transport Layer Interface            | 75         |

|   |                            | 5.4.2 Segment Processing at the Transport Layer        | 77         |

|   |                            | 5.4.3 Transport-Network Layer Interface                | 78         |

|   | 5.5                        | Software Design Issues - The Network Layer             | 79         |

|   |                            |                                                        | -          |

|   | 5.6  | Archi   | itectural Design Considerations        | 80     |

|---|------|---------|----------------------------------------|--------|

|   |      | 5.6.1   | Performance Evaluation                 | 86     |

| 6 | Co   | nclusio | ons                                    | 93     |

| A | Tes  | tbed S  | Software Operations                    | 101    |

|   | A.1  | Trans   | mission Protocol                       | 101    |

|   |      | A.1.1   | Master and Slave Program Functionality | 101    |

|   |      | A.1.2   | Master and Slave Interactions          | 102    |

|   | A.2  | Receiv  | ing Protocol                           | 104    |

|   |      | A.2.1   | Master and Slave Program Functionality | 104    |

|   |      | A.2.2   | Master and Slave Interactions          | 105    |

| в | Test | bed A   | nalytical Model                        | 109    |

|   | B.1  | Model   | Definition                             |        |

|   |      |         | Used in the Model                      |        |

|   |      |         |                                        | 1 1 () |

.

## List of Tables

| 1.1         | Estimated Instruction Counts                            | 4          |

|-------------|---------------------------------------------------------|------------|

| 2.1         | The OSI Communication Stack                             | 8          |

| 3.1         | Application of Flynn's Classifications to Communication | 21         |

| 3.2         | Retransmission and Acknowledgments                      | 22         |

| 3.3         | Sending Scheduler for Transport to Application Mapping  | 29         |

| <b>3.</b> 4 | Timers and Retransmission Options                       | <b>3</b> 0 |

| <b>3.</b> 5 | Reordering and Acknowledgment Generation                | 31         |

| <b>3</b> .6 | Parallel Network Layer Problems                         | <b>3</b> 3 |

| 3.7         | Expected Component Performance                          | 40         |

| <b>3.</b> 8 | Expected Resource Demands                               | 41         |

| 3.9         | Component Utilization – Baseline Assumptions            | 41         |

| 3.10        | Component Utilization – Sustained Bus Speeds            | 48         |

|             | Component Utilization - Realistic Instruction Counts    | 49         |

|             | Component Utilization - Realistic Cache Hit Rate        | 50         |

|             | Component Utilization - With Local Memory               | 51         |

|             | Component Utilization - With Eight Processors           |            |

|             | Component Utilization - With Fast Memory                | 51<br>52   |

|             |                                                         |            |

vii

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

# List of Figures

| 2.1         | Before and After PDDID: DU                                          |            |

|-------------|---------------------------------------------------------------------|------------|

| 2.1         | Before and After FDDI Ring Failure                                  | 11         |

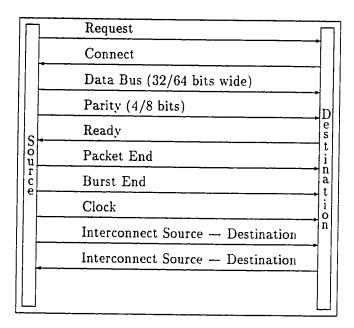

| 2.2         | The HiPPI Interface                                                 | 14         |

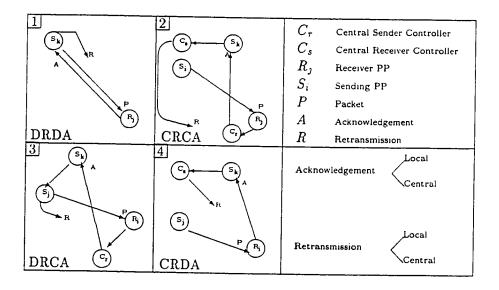

| 3.1         | Acknowledgement and Retransmissions                                 | 22         |

| 3.2         | Scheduler Placement Options                                         | 28         |

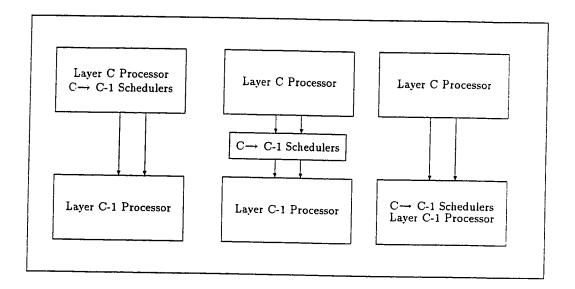

| <b>3</b> .3 | Levels and Scheduling                                               | 37         |

| 3.4         | Sun MP Architecture                                                 | 39         |

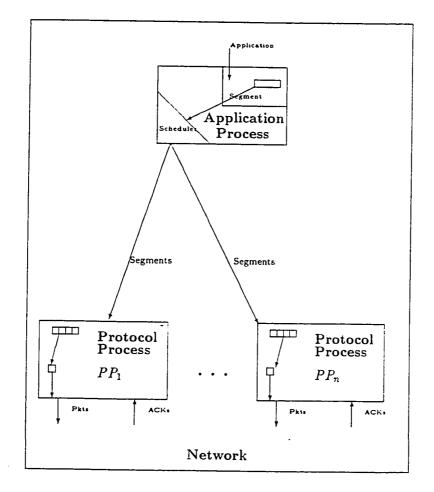

| 4.1         | Scheduling and Control – Application $\rightarrow$ Protocol Process | 57         |

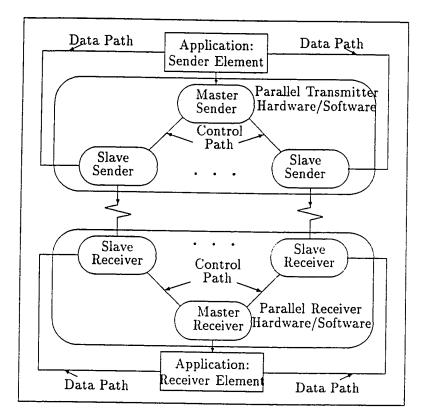

| 4.2         | End to End System Design                                            | 59         |

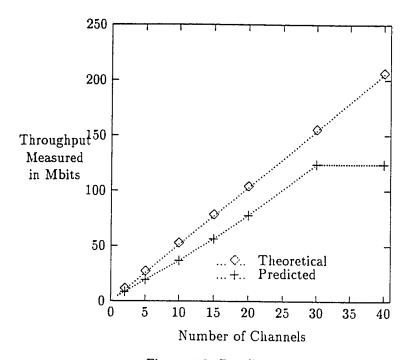

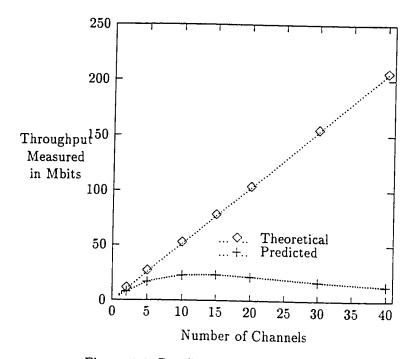

| 4.3         | Baseline Performance for Testbed                                    | 63         |

| 4.4         | Baseline Performance for Multiprocessor Architecture                | 6-4        |

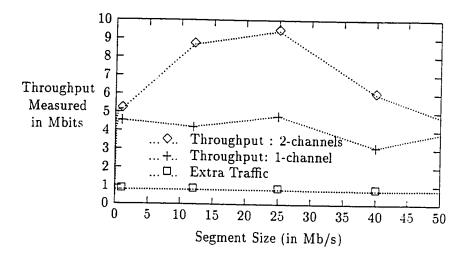

| 4.5         | Single vs multi-channel under bursty network traffic                | 65         |

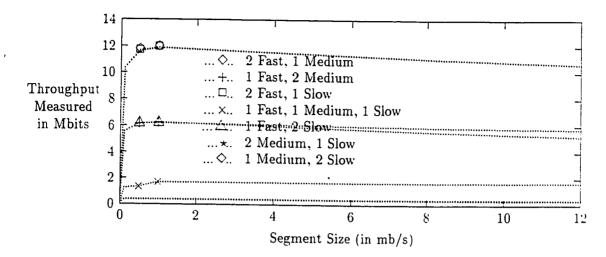

| 4.6         | Three channel testbed with Different Channel Latencies              | <b>6</b> 6 |

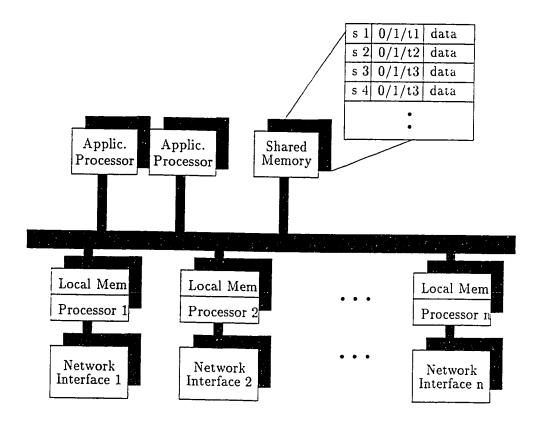

| 4.7         | MultiProcessor Protocol Processing Architecture                     | 68         |

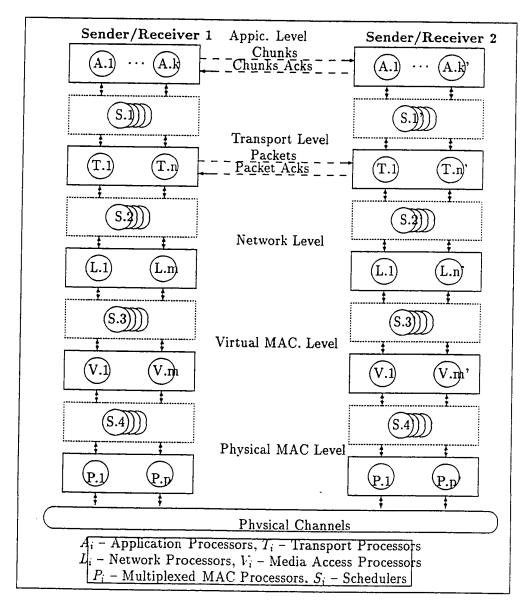

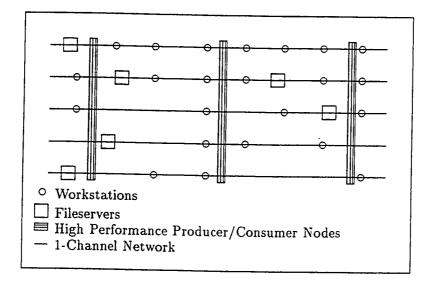

| 5.1         | Target Network Architecture                                         | 73         |

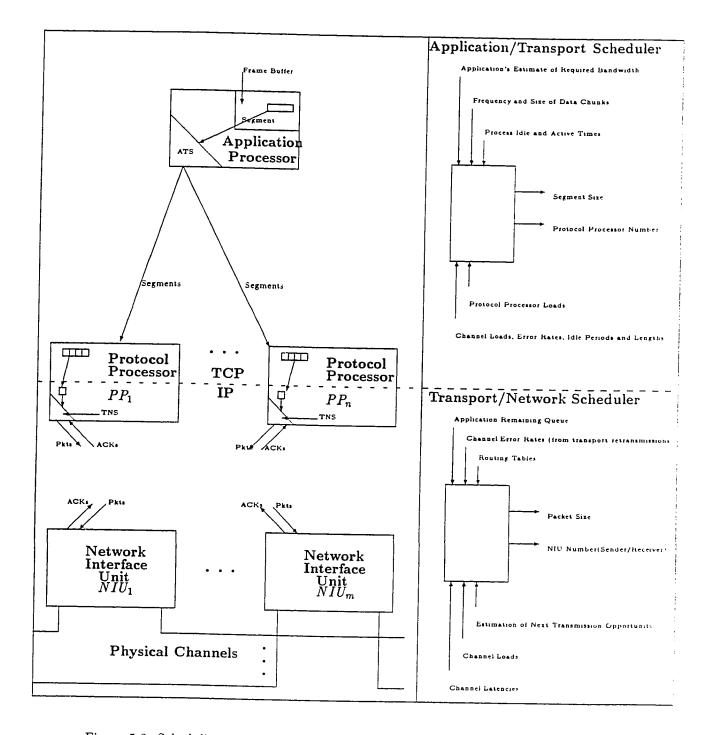

| 5.2         | Scheduling and Control – Application – Protocol Processors          | 81         |

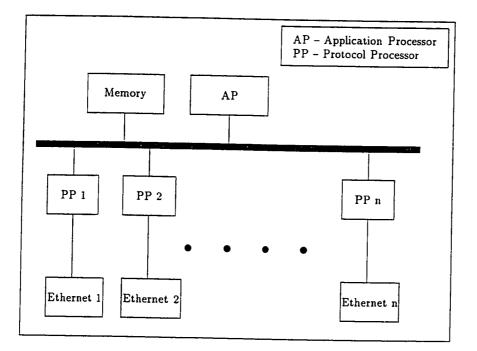

| 5.3         | Architecture A: Low Cost                                            | 83         |

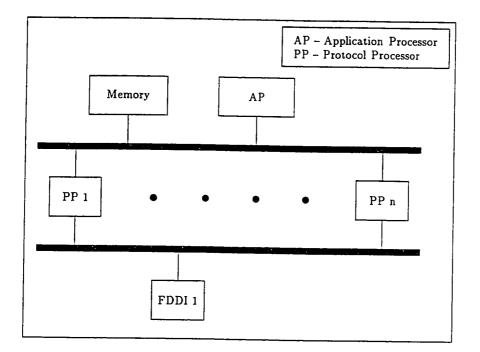

| 5.4         | Architecture B: Medium Cost                                         | 84         |

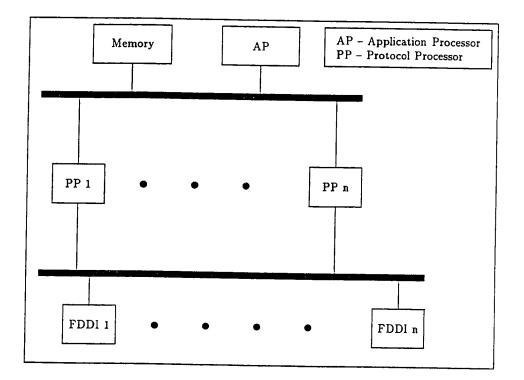

| 5.5         | Architecture C: High Cost                                           | 85         |

|             |                                                                     |            |

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

. .

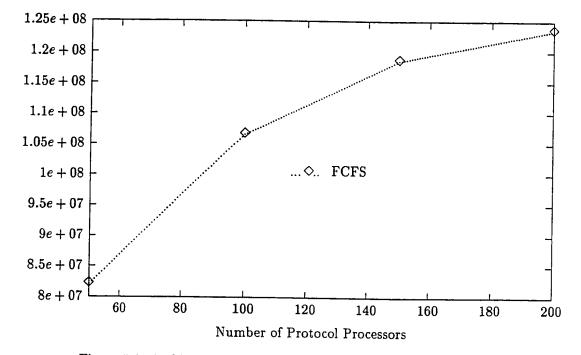

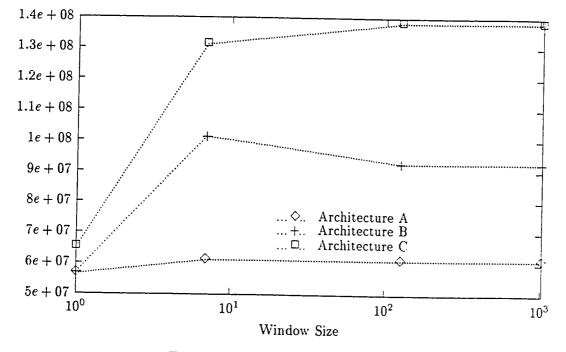

| 5.6  | Architecture A – Throughput with Large Number of Processors              | 88  |

|------|--------------------------------------------------------------------------|-----|

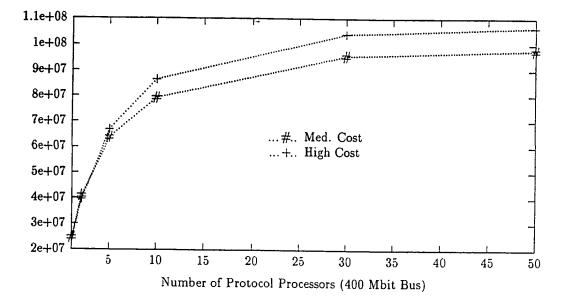

| 5.7  | Architecture B and C – Throughput vs Number of Processors (400 Mbits/sec |     |

|      | Bus)                                                                     | 88  |

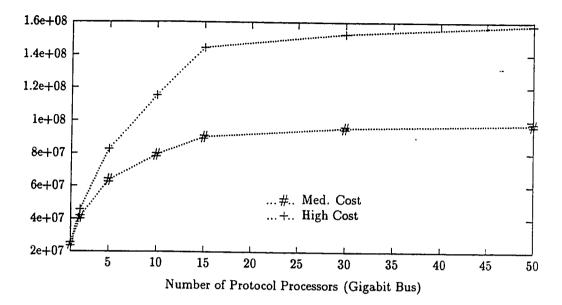

| 5.8  | Architectures B and C – Throughput vs Number of Processors               | 89  |

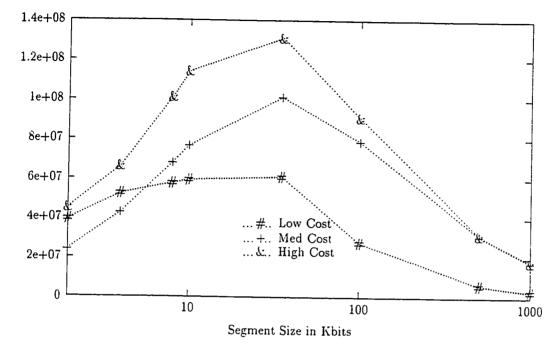

| 5.9  | Throughput vs Segment Size                                               | 90  |

| 5.10 | Throughput vs Window Size                                                | 92  |

| A.1  | Transmitter Pseudocode                                                   | 107 |

| A.2  | Receiver Pseudocode                                                      | 108 |

#### ABSTRACT

### Parallelism in High Speed Networking

Frank Charles Paterra

Department of Computer Science

Old Dominion University

Norfolk, VA 23529-0162

Advisors: C. Michael Overstreet and Kurt J. Maly

This work investigates possible methods by which existing potentially available communication bandwidth can be used by communication intensive applications. Presently fiber optic media are available that can provide multiple gigabits of throughput. Unfortunately, because of the computation overhead required to insure that data are reliably transmitted. this capacity has not be tapped.

A survey of work toward enabling the use of the potential bandwidth is presented. The parallel paradigm is identified as a strong candidate for providing significant increases in system usable bandwidth. Performing communication processing in parallel, however, presents the developer with several implementation options. These options are considered and categorized. This categorization represents a framework that is used in later analysis to compare different approaches and architectures.

Because the number of options available represents a combinatorial explosion in the number of software and hardware architectures that could be implemented, a sensitivity analysis is performed to exclude obvious failures, as well as to identify those components that need further study and close consideration. Some components are identified as limiters to total throughput obtainable: these components warrant special attention when implementing a parallel communication system.

Building on results obtained through the sensitivity analysis, a testbed was then built

and used to obtain performance data for one promising architecture and approach. The results for two and three channels implementations show near linear speedups. These results were then used to verify a model of the system used to calculate throughput values for systems with higher numbers of channels.

In order to more fully examine other promising architectures, a simulation program was developed and exercised. The simulation examined the impact of traditional communication parameters, such as window size and timer length, on performance in a parallel system. Further, the simulation confirmed some of the results of the sensitivity analysis and provided insight to the viability of two algorithms to implement flow control in a parallel environment. Additionally, scheduling algorithms to allocate processors to the communication tasks are examined and performance results are presented.

### Chapter 1

# Introduction and Problem

## Statement

The field of computer science called data communication encompasses several research areas. This chapter introduces some problems faced in this field and identifies the specific areas of study addressed in this work.

### 1.1 What is High Speed Networking

Computer to computer communication at rates of kilobit to low megabit per second speeds are commonly available in network computer systems today. This communication speed, however, is inadequate for many distributed applications, as well as the remote use of some high performance computing resources. Research directed toward increasing the speed of communication has, until recently, focused mainly on the physical media used to link computers together and on the access methods needed to utilize that media. Work in these areas has been successful; one can currently purchase fiber optic media capable of carrying multiple gigabits of data, and media access controllers that can provide 100 megabits of

throughput. One popular media access control method is Fiber Distributed Data Interface. or FDDI, a fiber optic based network designed to provide 100 megabits of data transfer per second. As a network for connecting several computers with relatively low network demands, FDDI represents at least a 10 fold increase in the communication bandwidth currently available with popular local area networks such as Token Ring and Ethernet. Allowing a single node on a network to use a significant fraction of this bandwidth, however. requires nontrivial computation power to insure that the data are reliably delivered. Some applications, such as remote visualization, can require multiple hundreds of megabits or even gigabits of bandwidth, making even FDDI too slow.

The media are only one of the problems to providing high speed reliable data communication. The computational power required to perform protocol processing is significant. The amount of time spent waiting for packets to traverse the network and be acknowledged before communication can progress is another problem. Performing high speed communication requires that new approaches be developed to address these and other problems.

### 1.2 Problems in High Speed Communication

The areas of research called data communication include:

- Physical media used to transmit data among computers,

- Methods for accessing the media to insure that fair and timely communication can take place,

- Methods for determining computer addresses and the routes data take when traversing a network,

- Problems of transferring data among networks.

- Methods for controlling and limiting congestion in a network.

- Insuring that data arrive at the destination in a timely manner, complete and uncorrupted, and,

- Protocols used to specify how data are to be used and how they are to be displayed.

Fiber optic media for data communication can be used to provide bandwidths in the multi-gigabit range. Sending data rates of one gigabit or even hundreds of megabits, however, introduces new problems to the communication process. As communication rates approach gigabit speeds, the time available to place data on, and read or remove them from, the media becomes exceedingly small. In fact at one gigabit per second transmission rate, each bit must be physically placed on the media in no more than one nanosecond  $(1 * 10^{-9} \text{ seconds})$ . Hardware can be built to place and read data at that speed, but the speed at which data can be accessed from the sender's memory in order to place it on the network presents a new bottleneck. For example, fast static memory, normally only used as cache because of its high cost, has access times of five to ten nanoseconds per byte, barely fast enough to keep up at one gigabit. The speed of memory can be effectively increased by using multiple independent banks of memory, each feeding the network in turn, but as network speeds increase the number of banks required becomes large and present a problem.

Placing data on the network is only part of the problem. Once data have reached the receiver, they need to be examined to identify the intended recipient and then, if they are for the local host, they must be copied from the network to a buffer for protocol processing. As with the transmitter, at gigabit speeds the receiver only has one nanosecond to read and act on each bit of the data. The time required to identify the recipient becomes critical, and, because buffering data at gigabit speeds for any length of time requires significant memory, once the data have been read they must be processed quickly. Because more than one action is performed on arriving data, less than one nanosecond of time can be allocated to each bit. This means that the instruction time for the receiving processor can be at most sub-nanosecond. Again, this speed is achievable, but the costs may be prohibitive.

| Direction | Transport | Network |

|-----------|-----------|---------|

| sending   | 191       | 61      |

| receiving | 186       | 57      |

Table 1.1: Estimated Instruction Counts

Once data have been read from the network, additional processing is required to insure that the data are received by the intended process, have been received as sent, and are in the original order. Two protocol layers, called network and transport, are responsible for these tasks. Table 1.1 gives the values that Clark et al. in [7] estimated to be the minimum number of instructions required to perform TCP/IP, or transport and network layer processing. If the standard transport layer packet size of 2048 bytes is used, gigabit communication requires more than 15 million instructions per second to send data and 9.5 million instructions per second to receive them. These numbers do not include the additional processing required to processes packet acknowledgments, estimated to be one third of the total processing time. Additionally, Clark's optimized instruction count assume a CISC computer and should be increased for RISC computers. For realistic computations a factor of two for RISC computer instruction counts over those of a CISC can be assumed, indicating that a 40 MIP RISC computer would be needed to perform just the transmitting functions of the transport layer protocol processing.

At the network and transport layer, not all bits received need to be directly accessed. Even so, Jain et al. in [19], estimated that memory access times of less than 10 ns would still be required for TCP/IP receiver operations at gigabit speeds. Finally, to support a 40 MIP processor and the required memory cycle time, a sub-nanosecond system clock and support circuitry would also be required.

If data are corrupted during transmission, the transmitting station needs to resend them. Often, the mechanism within a protocol to notify the sender of lost or corrupted data is for the receiver to simply not acknowledge the receipt of data. Because the sender

maintains a timer for each packet it sends, it assumes an error in the data occurred if no acknowledgment is received before the timer expires. This solution, while acceptable for lower speed networks, is very expensive for high speed networks because of the loss of potential to transmit data while waiting for a timer to expire. As an example, in a long distance terrestrial network of 5000 km, the round trip time for a packet is 30 ns. The round trip time is the shortest time in which a packet can be received at the destination, and an acknowledgment can be received at the sender. If this number is used for the timer length, a lost packet will cause the sender to wait at least 30 ns after the packet was lost before resending it. During this time the sender continues to send data, but after the timer expires the sender must resend the lost packet and then either wait for the packet to be acknowledged, or resend all of data after the lost packet. In either case this represents 30 megabits in lost transmission capability. Netravali, et al., [27] suggests that with a more reasonable timer length would be two times round trip time, making the loss 60 megabits. At slower transmission speeds the loss would have been much less, making the waiting time less of an issue. As is discussed in Chapter 2, this is a problem that needs to be faced in protocols designed to operate at gigabit rates.

## 1.3 Why High Speed, Reliable, Data Communication is Im-

### portant

The computing needs of applications in the fields of medicine. chemistry, aerospace, and remote sensing are immense. The end product of much of these computations is often visual images that are best viewed as a continuous animated movie [8]. Supercomputers are capable of computing the data required for these images in real time, but these computers are expensive and not available everywhere. The user of a supercomputer must either find a way to purchase a machine of their own, or must travel to a supercomputer facility.

Because of cost, the first option is not viable for many users. For time critical applications, such as medical imaging and remote sensing, travel may not be feasible. Another possible solution is to use a supercomputer remotely by supplying it with raw data, and viewing the results over a network. The amount of data involved, however, make this approach unrealistic without faster networks. To give an example of the amount of data that must be transferred, current scientific images typically used for visualization are 1024 by 1024 pixels in size, with each pixel represented by 8, 16, or 24 bits to enable the viewing of different colors. In order for images to be viewed as continuous animation, a new image needs to be delivered to the viewer approximately every 30 ms. For visualization to occur in real time, as is often required for medical and satellite sensed data [13], these specifications represent bandwidth requirements of between 250 and 750 megabits of application data per second. These numbers are likely to increase as higher resolution displays become available.

Remote visualization is not the only application that would benefit from high speed reliable data communication. In the area of high performance computing data often must be shared among processors in order to compute a single result. Physically distributed simulations, where the components contributing to a simulation are not resident on a single computer, is such an application and would be enhanced by access to high speed networking. An example simulation would be that of a tank battle field where humans are in the loop competing against simulated opponents. Often these simulations are performed with tank drivers operating simulated or actual tanks in one location, while the opponent tanks are being simulated elsewhere. The speed at which data can be collected by the simulating computer(s) about each of the tank groups determines the level of realism that can be achieved, both as training for the tank drivers and in the computed outcome of the battle.

Other high data rate applications are becoming evident as our society moves to a more global information based one. For example, stock market operations typically occur during local business hours. However, as more companies become international, and local governmental and commercial actions have global implications, the questions of whose business hours becomes an issue. The idea of truly international stock markets, where transactions no longer occur within national borders alone, is currently being discussed. This sort of market will require that information be made available nearly instantaneously, rather than just when the newspaper comes out the next morning. This need implies high bandwidths and reliability.

Another new user of high data rate networks is the application called virtual reality. This application involves the presentation of sound and video images to a user, to simulate a particular environment or area of the universe. The displays have to appear as three dimensional and, as the user moves with in the simulated environment, must change to represent current simulated views. As with remote visualization, the bandwidth required for high resolution, real time, color displays will be immense.

### 1.4 Focus of This Research

The raw bandwidth for each of these applications can be provided with a single fiber optic cable. Unfortunately, fiber optic cables are only the first step to providing higher bandwidths. This work addresses the problems of providing reliable communication at gigabit speed. The focus will be in the transport layer of the ISO communication stack, and will review proposed and existing monolithic protocols and extend parallel methods for solving these problems. Current workstation class RISC computers, such as Sun SparcStations, provide an application with the ability to transmit approximately six megabits of reliable data per second. This work discusses hardware and software architectures that can be used improve that number.

7

### Chapter 2

## Survey

As discussed in the previous chapter, several subareas in the domain of data communication need to be rethought in the light of high speed networking. This chapter presents approaches that have been suggested and investigated and gives an outline to the specific work performed in this thesis.

### 2.1 Solutions to Communication Problems

Traditionally the communication problem has been represented by a layered concept called the OSI communication stack. The layers in this stack are shown in Table 2.1; the lower four are examined in the following sections of this chapter.

| Layer        | Description                                             |

|--------------|---------------------------------------------------------|

| Application  | Application to application, such as sendmail            |

| Presentation | Syntax and semantic compatibility                       |

| Session      | Simple program interfaces, such as FTP                  |

| Transport    | Provide reliable end to end communication               |

| Network      | Provide address resolution and routing                  |

| Media Access | Provide access to the physical media                    |

| Physical     | The media and its physical and electrical specification |

Table 2.1: The OSI Communication Stack

#### 2.1.1 Media

An area that has been successful in providing high bandwidths is media. Fiber optic media have the ability to provide bandwidths in the multiple gigabit range. Local area networks (LANs), and metropolitan area networks (MANs), have been developed with fiber optics as the connecting media. Long distance networks, such as inter-continental phone links, have been successfully implemented via the use of undersea fiber optic cables. For data networks, however, the bandwidth capacity of fiber optics has barely been tapped. As discussed later, this is mainly due to other problems in the data communication domain.

For short distances, 25 meters or less, twisted pair copper wire is also a viable medium. In fact, as is discussed below, twisted pair has been used as a base for one high speed media access control protocol called High Performance Parallel Interface or HiPPI, and modifications to one fiber optic based media access control protocol. FDDI. have been proposed to allow it be to implemented with twisted pair as well.

### 2.1.2 Media Access Control Protocols

In order for any media to be of use. a protocol is needed to access it. Common desirable attributes of a media access control protocol, called a MAC. often include: fairness. low latency, the ability to handle synchronous as well as asynchronous data, and physical fault tolerance. This section discusses three relatively new MAC protocols. Modifications to one to provide higher throughput are also discussed.

#### FDDI

As discussed previously, FDDI is a fiber optics based protocol capable of delivering 100 megabits of data per second. Formed from work performed to develop the IEEE 802.5 LAN [29], FDDI is a token ring network that employs two counter rotating fiber optic rings. Because fiber connections are really point to point, with a receiving and sending pair in

each station enabling a ring, and the FDDI specification allows only 1000 ring connections. up to 500 stations can be attached. The maximum length for an FDDI network is 200km. There are no minimum station count or network length requirements [29].

When a station has data to transmit, it waits for and acquires a token before sending them. Internal to each station are timers that are used to determine the target token rotation time, and control how long a station can hold the token once it had received it. These two timers provide fairness and the ability to handle synchronous traffic. The token holding time determines how long a station can transmit once it has the token, and the target token rotation time, the time that a token takes before completely traversing the ring, makes the token arrival rates deterministic.

Of the two fiber optic rings forming a FDDI network, only one is normally in use for data transmission, with the second only being used in case of a primary ring failure. If a ring breaks, a new ring is formed by each of the two stations on either side of the break forming a loop internally, using the second fiber. This newly formed ring is approximately twice as long as the original. Figure 2.1 shows two FDDI networks. The first is the normal configuration. and the second shows a healed ring after the line between two stations failed. If a station had failed, the ring would be healed by the two stations on either side of the failed station. FDDI represents a significant increase in bandwidth over existing LANs, but falls short of the needs outlined for remote visualization and distributed computing.

Game in [14] proposed modifications to the basic FDDI network to enable gigabit operations. His work centered on modifications to the timer values, removal of data from the ring by the receiver, use of both fibers concurrently, and reuse of slots on the network, created by the removal of data at the receiving station. Game showed that these modifications allow transmission at rates of 400 to 500 megabits, and could make FDDI viable at gigabit speeds.

| FDDI<br>Station<br>FDDI<br>Station | FDDI<br>Station<br>FDDI<br>FDDI<br>Station |

|------------------------------------|--------------------------------------------|

| FDDI<br>Station                    | FDDI<br>Station<br>FDDI                    |

Figure 2.1: Before and After FDDI Ring Failure

#### CSMA/RN

Carrier Sensed Multiple Access/Ring Network, or CSMA/RN[12], is also a fiber optic based network. However, unlike FDDI, CSMA/RN is a carrier sensed, multiple access network, rather than token based, allowing it to exploit the fact that multiple transmission packets. with different source and destination addresses, can be physically resident on the fiber ring concurrently. CSMA/RN was designed to operate at a nominal speed of one gigabit, but because it employs destination removal of transmitted data, an average throughput of two gigabits is actually possible.

Because data are removed from the ring when they are received, and must not be removed before they arrive at their destination, the destination address of the data must be determined before they passes a station. As discussed previously, buffering data in computer memory when communicating at gigabit speeds is not reasonable. In order to determination of destination of data before they pass a node, CSMA/RN employs delay loops at each station. These delay loops, easily realized as coils of fiber cable, have connections to the controller at each end of the coil. As data enter the loop, they are read by the controller. If they are addressed to the local host, they will be read and removed from the network upon exiting from the loop. These loops allow CSMA/RN to enjoy zero loss of data due to collision on the media. Normally, in a CSMA network, stations sense to see if the network is free before they begin transmitting, and then they attempt to transmit a complete frame. If two stations sample the network at the same time, both will transmit concurrently and the result will be a collision of data and loss of bandwidth. By presampling the network at the beginning of the delay loop, the transmitting station can be sure that enough free space exists on the fiber for it to transmit at least a packet header and an abort flag. If, after beginning a transmission, data are sensed to be entering the delay loop, the transmitting station can transmit an abort flag and stop transmitting until more free space is detected on the network. Of course, if data entering the delay loop are for the transmitting station, the station can continue to transmit and simply remove incoming data as they enter the receiving portion of the station.

Additionally, CSMA/RN provides synchronous data transmission through the use of a circulating reservation packet (CRP) [11]. When a station requires synchronous transmission service, it accesses a CRP currently on the ring, adds information about its needs to that packets and places it back on the network. When the CRP passes a station, it is examined to determine when unallocated space on the ring for asynchronous traffic will exist.

CSMA/RN enforces no limits as to network lengths or number of stations, and represents a viable MAC for gigabit networks.

#### HiPPI

HiPPI is a media access protocol that was originally designed to connect a host computer to peripherals such as disks or printers. It was later expanded, however, to allow multiple hosts to be connected to each other or to share peripherals. Working as a point-to-point

network. HiPPI can be used to provide single or multiple 800 and 1,600 megabit simplex channels. For most applications, duplex operations are desirable so separate interfaces are provided for input and output. As can be seen in Figure 2.2, the interface consists of several control lines and a set of parallel data lines. The control lines are used to setup a connection, indicate that a host is ready receive data, provide a synchronizing clock, and test the circuit. Two additional control lines are used to indicate the end of a burst of words, and the end of a packet of bursts. These are labeled Burst End and Packet End in the figure respectively.

Because of its original design goals. to connect one host to its peripherals, the length of a HiPPI network is only 25 meters. This, and the fact that it operates as a point to point network, requiring processor attention for each data transfer that passes through, makes it impractical for traditional LANs and MANs.

What the HiPPI interface does provide, and indeed was its design goal, is a standard interface that can be used to link processors to peripherals. The peripheral of interest for this work would be a high speed network interface. The HiPPI interface would make the addition of new types of hardware to an existing network a simpler task.

#### 2.1.3 Transport and Network Protocols

The processing required to perform reliable communication has been identified as a bottleneck for high speed data communication networks [21, 7]. Reduction of this bottleneck has been the focus of much research interest and efforts fall into two broad categories. monolithic and parallel. In both of these categories multiple approaches have been proposed. Independent work by several researchers has resulted in performance gains in both categories. The next two sections of this chapter discuss some of the approaches taken in each category.

Figure 2.2: The HiPPI Interface

### Monolithic Approaches

Monolithic approaches attempt to either optimize existing protocols, or developing new protocols that reduce the amount of processing required to insure reliability.

Working towards optimization. Clark et al. [7] gives a thorough analysis of the processing required at the transport and network layers of the OSI stack, and then goes on in [6] to identify other bottlenecks in communication layers and supporting hardware. One solution suggested by Clark was to move some of the processing, currently being performed by the transport and network layer, to the application. This has the advantage allowing the application program to decide which functions it requires and to use the available processing power accordingly. The obvious disadvantage is that the clean interface between layers of the OSI stack become blurred. As discussed earlier, a highly optimized version of TCP/IP has been estimated by Clark et al. to potentially produce as much as 800 megabytes of throughput using a modern RISC processor. Clark's work, however, did not address hardware bottlenecks other than processor speed. Van Jacobson [18] implemented a somewhat optimized version of TCP/IP and was able to verify that throughput as high as 8 megabits could be achieved with a Motorola 68020 and existing hardware.

Silicon Graphics' optimizing approach. XTP. resulted in a new protocol that places much of the transport layer processing into VLSI hardware [4]. This dedicated hardware's performance is not limited by the speed of a host CPU, and the CPU is not burdened with transport layer processing. The result is an increase in throughput independent of CPU speed and load, and only limited by the speed of the protocol VLSI hardware. PSi is another protocol that is being developed for implementation in VLSI [1]. Krishnakumar et al. [20] describe work toward the automatic translation of a protocol specification into VLSI design.

Delta-t [33] and NETBLT [5] are optimized transport layer protocols which speed the communication process by reducing the amount of processing required. In the case of NET-BLT, this reduction has been achieved by providing two unidirectional paths, separating the data and control information flow. This allows the most efficient implementation for each, rather than a compromise for both. Additionally, NETBLT supports a selective acknowledgment strategy which allows individual packets to be resent as soon as their loss is detected, rather than the go-back-N algorithm found in TCP.

La Porta and Schwartz in [28] suggest that bunching packets into larger blocks and setting only one timer for each block would result in faster communication. They justify this approach by saying that new networks, especially fiber optic based networks, are significantly quieter than previously achievable so less loss will be observed.

In most new protocols, the fact that waiting for notification of lost packets represents a significant loss in bandwidth has played a significant part in their development.

One additional monolithic approach that has been examined is the use of a supercomputer, such as a Cray, to perform transport processing. This approach, while very expensive to implement, was shown by Borman in [3] to produce throughputs as high as 750 megabits per second.

### Parallel Approaches

In the arena of parallel protocol processing, Jain et al. in [19] and my work in [22] has examined the potential of providing multiple processors at the transport layer, each performing a complete transport processing task.

Jain et al. classify several schemes by type of memory, granularity of parallelism, and scheduling policies used. In their selected proposed implementation they use a pool of specialized protocol processors to transmit and receive data from a single high speed source. Each of the protocol processors operates independently on individual packets but maintain context records in a global memory so that acknowledgments, retransmissions, and resequencing can be handled properly by a centralized processor. In their implementation, special attention must be given to insure that the two common buses, the common memory, and the centralized queue processor do not become a bottleneck for communication because all packets must pass through each of these at least once. Existing memory speeds, as discussed in Chapter 1, will limit the throughput in their proposed architecture because of the need for context records in a global memory.

Maly, Wiencko et al. in [21] initially proposed a general solution that provides parallelism at the transport, media access, and physical layers of the communication stack. They kept the functionalities of the traditional protocol stack and introduced parallelism at some points where performance bottlenecks could develop. Independent of network layers, all protocol functions are viewed as processes to which multiple general purpose processors and channels are allocated to maximize throughput. The key concept is to structure the processes so that full advantage can be taken of parallelism at all levels. This provides additional benefits of increased reliability and graceful degradation in the case of a processor failure. Additionally, this approach allows the use of existing protocol standards and hardware technologies. This method is extended in Chapter 3 to include the network and application layers.

In [16], Haas describes an approach to parallel communication that uses multiple processors to work on each transport layer packet. In this protocol, called Horizontally Oriented Protocol or HOPs, the traditional OSI stack is recast into three layers. The first three layers of the OSI stack, media, media access control, and network, becomes the first layer of HOPS, called the network access layer. The transport, session, and presentation layers of OSI are combined into the new second layer, called communication interface, or CI. Finally the application layer of OSI becomes the third new layer. The most important layer for performance improvements is the CI. To obtain this improvement, parallelism is used by assigning separate processors to each of the tasks that must be performed for each incoming or outgoing packet. For example, one processor could be dedicated to packetization, while another is dedicated to performing flow control functions. A similar approach was briefly discussed by Jain in [19], and it was noted that, with packet structures such as is found in OSI TP4 (TCP), little parallelism can be achieved. Haas has found success by developing his protocol based on functions rather than a layered concept. Because functions can be performed independently, little communication is required among processors, so parallelism on the packet level can be achieved. This approach has an implicit limitation on the degree of parallelism that can be achieved because there are only so many tasks to be performed for each packet. If each of the tasks functions are replicated for multiple packets, higher parallelism can be achieved but only if parallel data streams of data are present.

Netravali et al. in [27] discuss a hybrid approach, first optimizing the protocol and then implementing it on a parallel computer platform. The optimization presented by Netravali et al. was based on the observation that the sooner an error is detected, the less bandwidth is lost waiting. To take advantage of this they exchange state information from the sender and receiver with every packet sent. This information transfer requires little bandwidth when included with normal data packet transmissions and results in near immediate notification

of lost packets. The protocol was also simplified because the need for active timer processing was eliminated.

Each of the above parallel communication methods are software proposals. Little has been done to measure their true performance, to examine the hardware implications of their implementations, nor to classify their approaches so they can be compared and extended. In the remainder of this work I classify the options available to parallel communication systems and identify the components that are of particular concern when performing high speed communication.

### Chapter 3

# **Options in Parallel**

## Communication

The previous chapter introduced some of the approaches taken to perform protocol processing in parallel. In order to evaluate these methods, a categorization scheme is needed to assist in analyzing and discussing them. This chapter identifies and examines the options available in parallel communication to form a basis for that comparison. Because so many options exist, and their potentials and limitations are not always immediately evident, it is important to carefully select candidates for detailed analysis. A model was built which allows a quick first look at possible option combinations to aid in identifying those that seem promising. A sensitivity analysis is performed with this model to quickly identify promising approaches for further study.

### 3.1 Introduction

Comparing methods used in parallel communication protocol processing is difficult because researchers use different terminology to describe the functions being performed, and use

different grouping of subfunctions and approaches. Classification of the methods and the results observed by each approach would be beneficial.

The objective of this chapter is to identify the different options, approaches. algorithms available when implementing parallelism at single and multiple levels of the communication process. Section two of this chapter evaluates classifications of parallelism in other applications and specifically defines the terms used in parallel computation and how they relate to parallel communication. Section three examines options opportunities for parallelism of different stages of the communication process. Section four uses these opportunities and options in a sensitivity analysis to identify promising approaches and to indicate which components need further study.

### 3.2 Taxonomies in Parallelism

Parallelism to increase performance and fault tolerance in computation has been studied for more than 20 years [10, 30, 9]. Early work by Flynn resulted in four major categories for describing parallel computing architectures. These are:

- SISD Single Instruction, Single Data

- SIMD Single Instruction, Multiple Data

- MISD Multiple Instruction, Single Data

- MIMD Multiple Instruction, Multiple Data

Working at any single level in the traditional OSI communication stack. Flynn's categorization can be applied as shown in Table 3.1. This classification describes the relationship of CPUs to packets, but is incomplete in that the granularity of computation as it relates to the number of data streams and in the allocation of CPUs to data streams as well as the

| Flynn | Communication                                              |

|-------|------------------------------------------------------------|

| SISD  | Single CPU performing all protocol processing              |

| SIMD  | Multiple CPUs working on multiple packets in lockstep      |

| MISD  | Multiple CPUs working on a single packet at a single layer |

| MIMD  | Multiple CPUs working on multiple packets, independently,  |

|       | at one or more layers                                      |

Table 3.1: Application of Flynn's Classifications to Communication

interface between multiple communication levels. Additionally, this classification is incomplete for parallel communication as it does not address the interaction among processors within each layer.

In [19]. Jain discusses three categories of granularity for processors to data streams. The finest level of granularity provides for multiple CPUs operating on a single packet within a stream. This relates to my use of Flynn's MISD, as well as work by Haas in [16] and Netravali et al. in [27]. The medium level granularity Jain et al. discuss has the individual packets being processed on individual processors as a single stream of data. In this method, processors are given packets as they arrive from the input stream and. once they have been processed, the data and control information is passed to a separate processor for resequencing and maintenance of data stream information prior to deliver of data to application layer. This level of granularity is most closely related to my use of Flynn's MIMD category. The most course level of granularity discussed by Jain assigns individual processors to specific data streams. This method reduces the need for a separate processor to maintain data stream control information, and reduces the amount of interprocessor communication required to properly handle packet timeouts and acknowledgments. This level of granularity also falls into my use of the MIMD category. Jain's work however, was only at the transport layer, so the issues of communication, control, and scheduling between layers still have not been addressed.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

| Classification | Description                                              |

|----------------|----------------------------------------------------------|

| DRDA           | Distributed Retransmissions, Distributed Acknowledgments |

| CRCA           | Centralized Retransmissions, Centralized Acknowledgments |

| DRCA           | Distributed Retransmissions, Centralized Acknowledgments |

| CRDA           | Centralized Retransmissions, Distributed Acknowledgments |

Table 3.2: Retransmission and Acknowledgments

Figure 3.1: Acknowledgement and Retransmissions

Working with Maly et. al in [22], I addressed some of the issues of interlevel communication. Specifically, the placement of scheduling mechanism, the type of scheduling available, and the supporting hardware that may be required for each. In this paper I also described four categories of methods to generate acknowledgments and retransmissions, enabling reliable communication when multiple processors are being used at the transport layer. The four categories are show in Figure 3.1, and are defined in Table 3.2.

DRDA requires that a separate data stream is present between a sender  $S_k$  and a receiver  $R_j$ , and as such can be considered to fall into Jain's course grain classification. In this solution, sender  $S_k$  maintains timers and performs any required retransmissions for the packets that it sends, while receiver  $R_j$  is responsible for generating acknowledgments for

the packets it receives. My work in [22], falls into this category.

CRCA employs separate processors to perform retransmission and acknowledgment generation. In this solution, timers for packets sent by sender  $S_k$  can be maintained either by  $S_k$ , or the centralized processor  $C_s$ . In the former case, when a timer has expired, sender  $S_k$  notifies  $C_s$  and  $C_s$  forces a retransmission if an acknowledgment was not received by any other  $S_i$ . The retransmission can be performed by any  $S_i$ . In the later case, once sender  $S_k$  has sent a packet, it discards the packet information and begins sending its next packet. If the timer for a packet expires,  $C_s$  forces the packet to be retransmitted by some  $S_i$ . Because with CRCA the  $S_k$  does not receive the acknowledgment, its window size must be very large or it will be stuck waiting for window movement. In the later case all of the timer processing is off loaded to a single processor, because timer processing is a significant part of the transport processing overhead, it would be advantageous if this task can be parallelized. This classification fits the medium granularity model that Jain et. al concentrated on in [19].

DRCA requires that the sending processor perform their own timing task, but the acknowledgments are generated by a single processor on the receiving side. In this scheme, sender  $S_k$  sends a packet to any receiver  $R_i$ . When a packet is received by some  $R_i$ , the centralized acknowledgment processor  $C_r$  is notified and it sends an acknowledgment to any  $S_i$ . When the acknowledgment is received, it is forwarded to the particular  $S_i$  that sent the packet and the packet's timer is stopped. Sender  $S_k$  will resend any packets for which its timers have expired.

The final classification, CRDA provides a centralized processor to perform retransmission of lost packets, but the receiving processor  $R_k$  generates the acknowledgments for any packets it receives. The problems outlined for the sending side of CRCA need to be addressed for this solution as well. The problem of resequencing received packets has not been addressed in CRDA nor DRDA. This work only relates to the transport layer where acknowledgments are needed.

As can be seen, there are several issues in parallel communications and existing classification schemes for parallel processing and none are complete. It is tempting to simply use all of the classification schemes available, as a collection, to describe each system. However this may result in ambiguous classifications, and incomplete descriptions. For example, two ways to define a system with processors on the sending and receiving side maintaining multiple transport layer connections were presented. Jain et al. call this a course grain system and my work calls it DRDA. Further a majority of the work in parallel communication has been at the transport and media layers, and little has been done at the network and application layers, so existing classification schemes may not adequately address the other layers. Finally, none of the above systems can be used to completely describe the work done by Haas [16] and Netravali [27], where the protocol has been defined based on functionality rather than on the layers of the OSI stack.

### 3.3 **Opportunities and Problems in Parallelism**

A majority of work in the published literature has been in the area of parallelizing the transport layer. Some work was done earlier to enable parallel media access, but little has been done at other layers of the ISO stack. In this section the layers of the ISO stack from the application to the media are evaluated and the opportunities for parallelism at each level are described.

Performance gains should be achievable from the application and network layers. In [15] Gitlin shows that when using a Sun Sparcstation. 20 MIP machine, if a single FDDI interface is provided(100 Mbits/second), the throughput of the network layer (IP) is a little more than 20 Mbits/second, the throughput of the transport layer is only about 15 Mbits/second. and the throughput of the application layer with the application being file transfer (FTP) is only about 1.3 Mbits/second. The higher layers are actually a greater bottleneck than the

transport layer, so if an increase can be seen there, total system throughput will benefit.

#### 3.3.1 Application Layer

At the application layer, consider applications running on a single CPU and those running on parallel machines. First, for those running on a single CPU, when block transfers of data, such as file transfer applications are running, other CPUs resident in the machine can be used to perform the application's data communication functions. In previous work [23]. I observed near linear speedups of throughput by simply replicating the communication processors. This means that a pool of processors could be used to speed this type of application.

In the case of a parallel processor machine with a single application running on multiple CPUs, spare processors or cycles on application processors can be used to send data in parallel as was described for the single CPU application. With parallel applications, however, additional opportunities for parallelism exist. To exploit these opportunities the following questions need to be answered.

- Do data generated by one application CPU need to be delivered to a specific CPU on the receiving end, or will any CPU suffice?

- Can received data produced by one CPU be consumed before data produced by another CPU have been received?

- How does the parallelism available at the transport layer affect the use of parallelism at the application layer, both for the application and its communication?

While the answers to these questions are primarily driven by the application being considered, some are also partially application independent. For example, regardless of the application, some form of scheduling of application processor data to transport protocol

processors will need to be provided. This will have an impact in so far as computing resources may be needed for this control and scheduling.

## 3.3.2 Alternative Architectures to Parallelism at the Transport Layer

The transport layer has been the focus of significant research recently. As discussed in the first and second sections of this chapter, numerous ways to exploit parallelism at the transport layer exist. The transport layer, identified as a significant bottleneck for high speed communication, also represents one of the most interesting processes to parallelize. Because the transport layer is responsible for providing reliable communication, all data must be delivered to the receiver correctly, and data must be delivered from the receiver's transport layer to its application layer in the same order as sent. These two attributes would initially seem to require that either the sending processors maintain some sort of global information or maintain separate data streams in order to insure that all data are accounted for. On the sending side, because data are being sent on more than one path the transport layer must have a large buffer so that data can be resequenced before it is delivered to the application. Specifically, if each sending processor is maintaining a separate transmission window, the receiving transport layer needs to have n \* (window size) \* (packet size) bytes of storage, where n is the number of transmitting transport layer processors. As is discussed below, this is not the only way to perform these tasks.

#### Scheduling Issues

As introduced above when discussing the application layer, the resources of the transport layer must be scheduled to fit the needs of the application layer. This problem is multifaceted, and several solutions for each dimension can be examined. Table 3.3 gives some of the issues to be considered and some broad option categories for each. The location of the scheduler has an impact on the supporting hardware used, the amount of processing

that needs to be performed at each level in addition to communication, and the amount of interprocessor communication required. As shown in Figure 3.2, the scheduler can be in any of three locations. The location chosen has an impact on the utilization of processors, buses, and memory. Additionally, the location determines if the scheduling process is a single processor or a distributed process, and it can indicate the sophistication of the scheduling mechanism.

The scheduling algorithm has an impact on the system's performance. In [22]. I showed that when data channels are evenly loaded, FCFS and Round Robin performed nearly equally. However, if the transport processor loads are very different, neither of these solutions could exclude a slow processor from being assigned the final segment. This could result in higher system latency and slower throughput if a nearly complete transmission had to wait a significantly long time for its final segment to be completely sent. A more intelligent algorithm could exclude slower processors from participating in the transmission of the final segments, thereby increasing throughput. The slower processors could be used them early in the transmission. This has the potential to exact higher throughput by using each of the processors when they can make a contribution to the communication task.

#### **Data Sizes**

The data blocks generated by the application should be sized to meet the processing speed and memory storage capacity of the transport processors. If block sizes are too small, more communication between the layers is required and if block sizes are too large, the application layer may be forced to wait until data is sent from the transport processors before it can begin producing more data. Adaptive block sizes could change with application types and needs, as well as anticipated network capacity. As with adaptive algorithms discussed earlier, the availability and cost of additional information needs to be considered.

The size of a segment of data from a block that is given to the transport layer processors

Figure 3.2: Scheduler Placement Options

must also be determined. If segments consist of only one packet of data, the use of each transport processor can be finely adjusted with its load to insure that the complete transmission is not waiting for a slow processor. Unfortunately, this fine tuning comes at the cost of additional interprocessor communication, and possibly wasted wait time. If segments are too large, little fine tuning can be done, and in fact, some processors may be excluded from the transport processing because all data has been allocated to just a few of the available processors. If timely information about processor load and previous performance can be obtained, the size of the segment given to a particular processor can be tailored so that all the processors complete their segments at nearly the same time, resulting in a higher degree of parallelism.

## Timer Maintenance and Packet Retransmission

In addition to scheduling processors at the transport layer and determining the correct data sizes to generate and assign, issues of timer maintenance and retransmission need to be addressed. Both of these problems can be solved in several ways. The specific

| Attribute                     | Options     | Implementation          |

|-------------------------------|-------------|-------------------------|

| Location of Scheduler         | Application | Centralized/Distributed |

|                               | Transport   | Distributed             |

|                               | In Between  | Centralized             |

| Type of Scheduler             | Simple      | FCFS/Round Robin        |

|                               | Intelligent | Adaptive                |

| Block Size (data size         | Fixed       |                         |

| used by application)          | Variable    | Remainder/Adaptive      |

| Segment Size (size of         | Fixed       | <u> </u>                |

| data used at transport layer) | Variable    | Adaptive                |

Table 3.3: Sending Scheduler for Transport to Application Mapping

problems and categories of solutions are given in Table 3.4. Because the transport layer must insure reliable transmission. timers or some other way of insuring that lost packets are eventually resent must be incorporated. Maintenance of timers normally require some processing to update and react when a packet has been lost. The task of maintaining this information can be performed in a central location, or distributed among the processors performing the transport processing. This task in particular is a large part of the overhead of transport processing and distributing is potentially beneficial. To determine the desired solution for this problem one must also decide where the incoming acknowledgments will be received and what processors will be responsible for acting on them. If the timers are located centrally, any transport processor can receive the acknowledgments and forward them to a dedicated acknowledgment processor. Alternatively a dedicated acknowledgment processor can receive all the acknowledgments directly and then stop the timers. If the timers are located in the sending processors, the acknowledgment for a packet either has to be received directly by the sending processor, or received by any processor and then forwarded to the sending processor. Alternatively if the sending processor keeps timers in a global memory and acknowledgments are received by any processor, the processor receiving the acknowledgment can stop the timer directly and the sending processor will simply check the global memory when a window movement is needed.

| Task                         | Options                                           |

|------------------------------|---------------------------------------------------|

| Timer Execution              | Centralized/Distributed                           |

| Receipt of Acknowledgment    | Sender $S_k$ , Any $S_i$ , Dedicated              |

| Location of Window           | Individual Windows for each $S_k$ . Single Window |

| Generation of Retransmission | Original Sender, Any $S_i$                        |

Table 3.4: Timers and Retransmission Options

Placement and size of the sending processor window is also an issue that needs to be addressed. In the last example, it was implicitly assumed that each sending processor maintained a separate window. An alternative implementation, however, could have a single, large global window that is used by all processors. The solution selected for this problem also has an impact on the other issues in Table 3.4

#### Acknowledgment Generation

The receiving end of the transport processing is responsible for generating acknowledgments for received packets, and for reordering the data received before passing them to the application layer. The categories of solutions to these problems in a parallel implementation are given in Table 3.5. As packets are received by a processor, the single processor may not be able to determine if a packet should be acknowledged. For example, if a single stream of data is received by several processors, before any one packet can be acknowledged all the packets sent prior to the packet must have been received. Without the use of some global memory, the individual processor may not know if all the packets prior to its packet have been received, so an acknowledgment cannot be sent. If on the other hand each processor receives a separate stream of data, it knows what packets it has and has not received for that stream and can act accordingly without communicating with the other receiving processors. A third alternative would be to provide a separate processor responsible for the generation of acknowledgments, and have each of the receiving transport processors report to it when they receive a packet. This solution simplifies the acknowledgment problem, but

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

| Attribute         | Options                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------|

| Number of Streams | Receiving $R_i$ / Central Processor $C_r$<br>Single shared, Multiple to be Merged<br>Global, Local to one Processor |

Table 3.5: Reordering and Acknowledgment Generation

could require that a significant global memory is available to store all of the packets as they are received. Because all protocol processors must in some way access the global memory. memory access may be a performance bottleneck.

#### **Reordering of Data**

Once data have been received, they need to be ordered correctly before they can be passed to the application layer. This can be accomplished by using a single queue processor as suggested by Jain et al. in [19], or by having a single processor poll the receiving processors for complete segments and selecting the lowest available one to pass to the application layer. These solutions, while not the only ones, demonstrate the dependence of the issues at the transport layer. The first solution selected by Jain assumes that all the receiving processors are working on a single stream of data and that they do not build complete segments themselves. The second solution assume that each processor is working on a separate data stream and can store a complete segment locally before passing it to the application layer. Additionally, both of these solutions require completely different supporting hardware. In the former case a large global memory is prescribed, in the later, a significant local memory must be available at each of the protocol processors and a separate processor must be available to poll for the next segment to be passed. The later solution could also implement this polling function as a distributed process among the transport processors.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

#### 3.3.3 Network Layer

In addition to breaking data blocks into data segments and scheduling these segments to transport processors, packets generated by the transport layer need to be scheduled to network layer processors. As with the transport and application layers, the number of processors assigned to network layer processing may be different than the number assigned to other layers. As discussed earlier, Gitlin [15] showed that the network layer represents a factor of five reduction in available bandwidth from that offered at the media level, so extracting speedups from it would be beneficial.

Parallel network layer processing introduces new problems and issues over those in serial communication systems. Some of these problems, shown in Table 3.6, are similar to those of the transport layer. As with the scheduling between the application and transport layer, the scheduler between the transport and network layer can reside either in the transport layer, the network layer, or in a processor between the two layers. Additionally, media access processors must be scheduled to network processors. As with the scheduling mechanism discussed for the transport layer, the algorithms can be simple FCFS or Round Robin, or they can incorporate information about system and component performance to attempt to increase throughput. Unlike the transport layer, reliability is not guaranteed for the network layer, so the issues of acknowledgments and retransmission do not need to be addressed. Also, data can be delivered to the transport layer in the order it was received by the network layer, so there is no need to buffer incoming data for resequencing. However, if transport layer packets are fragmented at the network layer and multiple paths are used to send a single transport packet, it is important that the complete transport packet is delivered to one transport processor on the receiving end. If this is not done, many packets could be successfully sent, but thought to be lost because several transport processors are holding a small part of each packet. This implies that the fragments must be reassembled at the receiving network layer. This can be done by requiring that all network packets from a

| Task          | Options                                      |

|---------------|----------------------------------------------|

| Scheduling    | Simple, Adaptive                             |

| Fragmentation | Yes or No                                    |

| Recombination | Single Network Layer Processors, Distributed |

| Addressing    | Single Address, Multiple Addresses           |

Table 3.6: Parallel Network Layer Problems

single transport packet be sent to the same network processor on the receiving side, or that the fragments forming a single transport packet be address to a particular receiving transport processor. In the later case, some mechanism to resequence the single transport packet must also be provided.

If the transport layer cannot accept data from a network layer processor, the data can simply be discarded. This means that the problems of timer and acknowledgment maintenance, and buffer memory are not imposed at this layer. Interprocessor communication may still be needed however, because the incoming data packets need to be scheduled to the available network layer processors, and the network layer processor may want to communicate to determine the best route to transmit a particular packet.

#### 3.3.4 Media Access Layer

Multiple media access processors or controllers can be used to provide high throughput by aggregating the throughput of each. Parallelism at this layer is significantly easier than at the network and above layers because not only is there no concern for proper delivery and reordering of data, any fragmentation that occurs at this layer is handled at the receiving end by the receiving media access controller. In many computer systems multiple media access controllers are already in used, but no real parallelism can occur because normally only one is processor performing the communication protocol processing, and it can only use one media access controller at a time. As the throughput of the higher layers increase, the data are more quickly available to the network layer and, hence, to the media access

controllers. Multiple media access controllers can then be driven by the parallel network layer. This is not meant to imply that the efficient use of multiple media access controllers is a trivial problem. Mukkamala et al. in [26], however, showed improvement in throughput when multiple FDDI channels were provided.

#### 3.3.5 Physical Media