# University of Louisville

# ThinkIR: The University of Louisville's Institutional Repository

**Electronic Theses and Dissertations**

8-2019

# Formally designing and implementing cyber security mechanisms in industrial control networks.

Mehdi Sabraoui University of Louisville

Follow this and additional works at: https://ir.library.louisville.edu/etd

Part of the Computer and Systems Architecture Commons, Controls and Control Theory

Commons, Information Security Commons, OS and Networks Commons, Other Computer

Engineering Commons, Software Engineering Commons, Systems Architecture Commons, and the

Theory and Algorithms Commons

# Recommended Citation

Sabraoui, Mehdi, "Formally designing and implementing cyber security mechanisms in industrial control networks." (2019). *Electronic Theses and Dissertations*. Paper 3271.

https://doi.org/10.18297/etd/3271

This Doctoral Dissertation is brought to you for free and open access by ThinkIR: The University of Louisville's Institutional Repository. It has been accepted for inclusion in Electronic Theses and Dissertations by an authorized administrator of ThinkIR: The University of Louisville's Institutional Repository. This title appears here courtesy of the author, who has retained all other copyrights. For more information, please contact thinkir@louisville.edu.

# FORMALLY DESIGNING AND IMPLEMENTING CYBER SECURITY MECHANISMS IN INDUSTRIAL CONTROL NETWORKS

## BY

Mehdi Sabraoui B.S., University of Louisville, 2013 M.Eng., University of Louisville, 2014

A Dissertation

Submitted to the Faculty of the

J. B. Speed School of Engineering

in Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy in Computer Science and Engineering

Department of Computer Science and Engineering

J.B Speed School of Engineering

University of Louisville

Louisville, Kentucky

August 2019

# FORMALLY DESIGNING AND IMPLEMENTING CYBER SECURITY MECHANISMS IN INDUSTRIAL CONTROL NETWORKS

# BY

Mehdi Sabraoui B.S., University of Louisville, 2013 M.Eng., University of Louisville, 2014

A Dissertation Approved on

July 23, 2019

| By the following Dissertation Committee members |

|-------------------------------------------------|

|                                                 |

| Dr. Adrian P. Lauf, Dissertation Director       |

| Dr. Jeffrey L. Hieb, Dissertation Co-Director   |

| Dr. Roman V. Yampolskiy                         |

|                                                 |

| Dr. Michael Losavio                             |

| Dr. Adel Elmaghraby                             |

# DEDICATION

This dissertation is dedicated to my parents

Rebecca Sabraoui and Ben Sabraoui

whose hard work and constant support have granted me this privilege.

# **ACKNOWLEDGEMENTS**

I cannot understate how much the support of my advisors, Dr. Jeff Hieb and Dr. Adrian Lauf, have helped me through the academic, professional, and emotional ups and downs of this journey. I would also like to extend my deepest gratitude to Dr. Adel Elmaghraby for his clever administrative support for me and all the students in the department who come to him for help and guidance. I am grateful to the rest of my committee members, Dr. Roman Yampolskiy and Dr. Michael Losavio, for their invaluable insights and friendly conversations through the tough times. Finally, I want to recognize all the friends and family who have been patient and understanding with my occasional absences through the past few years.

#### **ABSTRACT**

# FORMALLY DESIGNING AND IMPLEMENTING CYBER SECURITY MECHANISMS IN INDUSTRIAL CONTROL NETWORKS

## Mehdi Sabraoui

July 23, 2019

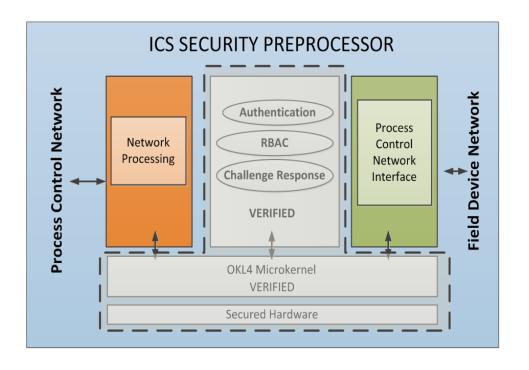

This dissertation describes progress in the state-of-the-art for developing and deploying formally verified cyber-resilient devices in industrial control networks. It begins by detailing the unique struggles that are faced in industrial control networks and why concepts and technologies developed for securing traditional networks might not be appropriate. It uses these unique struggles and examples of contemporary cyber-attacks targeting control systems to argue that progress in securing control systems is best met with formal verification of systems, their specifications, and their security properties. This dissertation then presents a development process and identifies two technologies, TLA+ and seL4, that can be leveraged to produce a high-assurance embedded security device.

The method presented in this dissertation takes an informal design of an embedded device that might be found in a control system and 1) formalizes the design within TLA+, 2) creates and mechanically checks a model built from the formal design, and 3) translates the TLA+ design into a component-based architecture of a native seL4

application. The later chapters of this dissertation describe an application of the process to a security preprocessor embedded device that was designed to add security mechanisms to the network communication of an existing control system. The device and its security properties are formally specified in TLA+ in chapter 4, mechanically checked in chapter 5, and finally its native seL4 architecture is implemented in chapter 6. Finally, the conclusions derived from the research are laid out, as well as some possibilities for expanding the presented method in the future.

# TABLE OF CONTENTS

| PA                                                | GE.              |

|---------------------------------------------------|------------------|

| EDICATIONCKNOWLEDGEMENTSBSTRACTIST OF TABLESx     | . iv<br>v<br>xii |

| HAPTER I INTRODUCTION                             | 1                |

| 1.1 Industrial Control Systems                    | 3                |

| 1.2 Components of Industrial Control              | 7                |

| 1.3 ICS Network Devices and Requirements          | 8                |

| 1.4 Cyber Security for Industrial Control Systems | . 11             |

| 1.5 Vulnerabilities                               | . 13             |

| 1.6 ICS Policies & Best Practices                 | . 17             |

| 1.6.1 Systems Design                              | . 17             |

| 1.6.2 Configurations                              | . 20             |

| 1.6.3 Patch Management and Disaster Recovery      | . 23             |

| 1.6.4 Hardware Device Solution                    | . 24             |

| 1.7 Cyber Attacks                                 | . 26             |

| 1.8 Summary                                       | . 31             |

| CHAPTER II LITERATURE SURVEY                      | . 32             |

| 2.1 Introduction                                  | . 32             |

| 2.2 Formal Methods                                | 33               |

| 2   | .2.1   | Model Checking.                                                        | 34             |

|-----|--------|------------------------------------------------------------------------|----------------|

| 2   | .2.2   | Theorem Proving                                                        | <del>1</del> 0 |

| 2   | .2.3   | Standards and Certifications                                           | <del>1</del> 0 |

| 2   | .2.4   | Limits of Formal Methods                                               | 13             |

| 2.3 | Verifi | cation                                                                 | 14             |

| 2   | .3.1   | Verification of a Cryptographic Primitive: SHA-256                     | <del>1</del> 5 |

| 2   | .3.2   | Verified correctness and security of OpenSSL HMAC                      | <del>1</del> 6 |

| 2   | .3.3   | HACL*: A Verified Modern Cryptographic Library                         | 18             |

| 2   | .3.4   | Breaking and fixing the Needham-Schroeder Public-Key Protocol using    |                |

|     |        | FDR                                                                    | <del>1</del> 9 |

| 2   | .3.5   | Implementing TLS with Verified Cryptographic Security                  | 51             |

| 2   | .3.6   | The Temporal Logic of Actions, TLA+                                    | 53             |

| 2   | .3.7   | Use of Formal Methods at Amazon Web Services                           | 54             |

| 2.4 | Mode   | ling and Verification of Operating Systems                             | 55             |

| 2   | .4.1   | The Bell-La Padula model                                               | 56             |

| 2   | .4.2   | The transfer of information and authority in a protection system       | 58             |

| 2   | .4.3   | seL4: formal verification of an OS kernel                              | 50             |

| 2   | .4.4   | The HACMS program: using formal methods to eliminate exploitable       |                |

|     |        | bugs                                                                   | 52             |

| 2.5 | Cyber  | Security for Control Systems                                           | 54             |

| 2   | .5.1   | Formal Vulnerability Analysis of a Security System for Remote Fieldbus |                |

|     |        | Access                                                                 | 54             |

| 2   | .5.2   | Towards Formal Security Analysis of Industrial Control Systems         | 56             |

| 2.   | .5.3   | Anomaly detection in cyber-physical systems: A formal methods approach | a  |

|------|--------|------------------------------------------------------------------------|----|

|      |        | 6                                                                      | 7  |

| 2.   | .5.4   | Formal modelling and analysis of DNP3 secure authentication            | 8  |

| 2.   | .5.5   | Attack taxonomies for the Modbus protocols                             | 0  |

| 2.6  | Sumn   | nary                                                                   | 1  |

| CHAF | PTER I | II HIGH ASSURANCE CYBER-SECURITY DEVICES FOR INDUSTRI                  | AL |

| CON  | TROL   | SYSTEMS USING TLA+ AND SEL4                                            | 2  |

| 3.1  | Introd | duction                                                                | 2  |

| 3.2  | Indus  | trial Control Systems (ICS)                                            | 4  |

| 3.3  | TLA    | +7c                                                                    | 6  |

| 3.4  | seL4   | and CAmkES78                                                           | 8  |

| 3.5  | Appli  | cation of Verified Systems for Control Systems Security 80             | 0  |

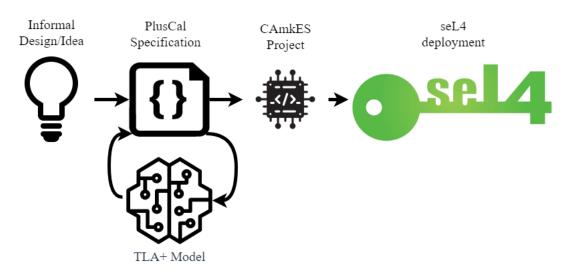

| 3.6  | Trans  | lation of TLA+ and PlusCal into CAmkES                                 | 2  |

| 3.7  | Secur  | ity Preprocessor as Previously Designed80                              | 6  |

| 3.8  | Sumn   | nary90                                                                 | 0  |

|      |        | V MODELING A BUMP-IN-THE-WIRE SECURITY                                 |    |

|      |        | SOR 92                                                                 |    |

| 4.2  | Assur  | mptions93                                                              | 3  |

| 4.3  | Form   | al TLA+ Specifications for Components and Properties95                 | 5  |

| 4.   | .3.1   | Modeling the Trusted Network Component                                 | 5  |

| 4.   | .3.2   | Modeling the Untrusted Network Component                               | 4  |

| 4.   | .3.3   | Modeling the Protocol Checking Component                               | 0  |

| 4    | 3.4    | Modeling the Cryptographic Component                                   | 7  |

| 4.    | .3.5 Modeling the System                                       | 23  |

|-------|----------------------------------------------------------------|-----|

| 4.    | .3.6 Additional Operators and Functions in TLA+                | 26  |

| 4.4   | Summary                                                        | 32  |

| СНАР  | PTER V MODEL CHECKING, INPUT VALUES, STATES                    | 33  |

| 5.1   | Introduction                                                   | 33  |

| 5.2   | TLC Model Checker                                              | 33  |

| 5.3   | State Explosion Considerations 13                              | 35  |

| 5.4   | Trusted Network Component States and Inputs                    | 38  |

| 5.5   | Untrusted Network Component States and Inputs                  | 10  |

| 5.6   | Protocol Checking States and Inputs                            | 11  |

| 5.7   | Cryptographic Component States and Inputs                      | 11  |

| 5.8   | System Model States and Inputs                                 | 12  |

| 5.9   | Summary                                                        | 13  |

| СНА   | PTER VI CAMKES ARCHITECTURE FOR A BUMP-IN-THE-WIRE SECUR       | ITY |

| PREPR | ROCESSOR                                                       | 14  |

| 6.1   | Introduction                                                   | 14  |

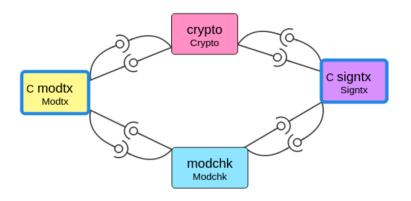

| 6.2   | CAmkES Definitions for Components, Interfaces, and Connections | 15  |

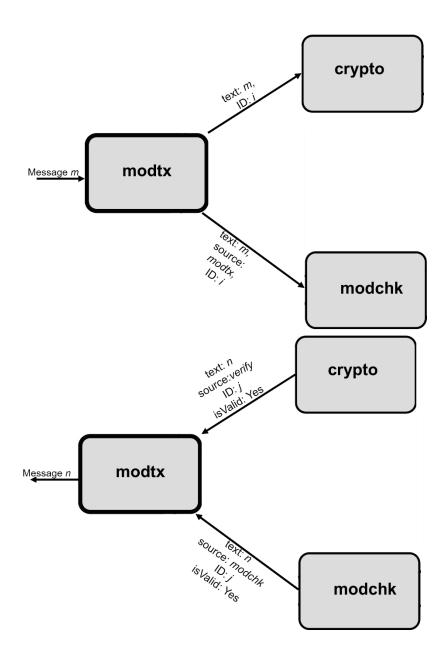

| 6.    | .2.1 Modtx: The Trusted Network Interface                      | 16  |

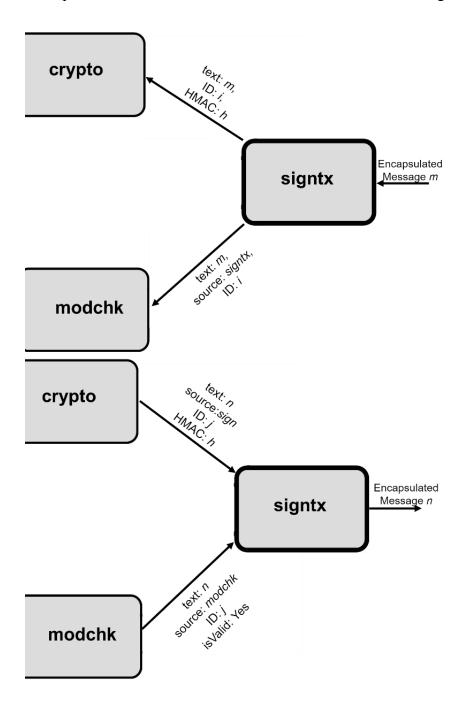

| 6.    | .2.2 Signtx: The Untrusted Network Interface                   | 18  |

| 6.    | .2.3 Modchk: The Protocol Checker                              | 52  |

| 6.    | .2.4 Crypto: The Cryptographic Service                         | 54  |

| 6.    | .2.5 Pre-defined RPC Connections                               | 56  |

| 63    | Summary 15                                                     | 57  |

| CHAPTER VII CONCLUSIONS AND FUTURE WORK | 159 |

|-----------------------------------------|-----|

| REFERENCES                              | 162 |

| APPENDICIES                             | 171 |

| CURRICULUM VITA                         | 172 |

# LIST OF TABLES

| TABLE                                                                    | PAGE |

|--------------------------------------------------------------------------|------|

| Table 1: A Modbus ASCII message                                          | 9    |

| Table 2: Priorities of IT and ICS Networks                               | 13   |

| Table 3: Stuxnet Capabilities and Targeted Vulnerability                 | 28   |

| Table 4: EAL descriptions and example products                           | 41   |

| Table 5: Criticality Levels of DO-178B Standard                          | 42   |

| Table 6: Benefits of TLA+ in Amazon's Ecosystem. Adapted from [103]      | 55   |

| Table 7: Comparison of attacker profiles, from [118]                     | 67   |

| Table 8: Sample of Possible Attacks against Modbus                       | 70   |

| Table 9: CAmkES primitives                                               | 82   |

| Table 9: The desired properties of the Trustnet_in thread                | 98   |

| Table 10: TLA+ symbols used in the property definitions for trustnet_out | 99   |

| Table 11: The desired properties of the Trustnet_out thread              | 101  |

| Table 12: Properties of the Untrustnet_in thread                         | 106  |

| Table 13: The desired properties of the Unrustnet_out thread             | 109  |

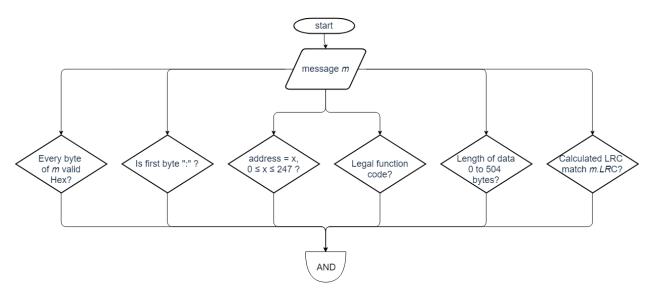

| Table 14: A Modbus ASCII message                                         | 112  |

| Table 15: Modbus function codes. Adapted from [123]                      | 113  |

| Table 16: The desired properties of the Modchk thread                    | 115  |

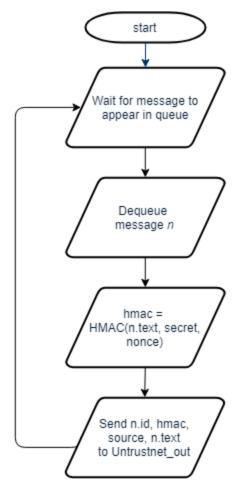

| Table 17: The desired properties of the Sign thread                      | 119  |

| Table 18: Desired properties of the Verify thread                        | 121 |

|--------------------------------------------------------------------------|-----|

| Table 19: Desired informal properties of the security preprocessor       | 124 |

| Table 20: The desired formal properties of the security preprocessor     | 125 |

| Table 21: TLC Running Statistics for the trusted network component       | 139 |

| Table 22: Test messages for Trustnet_in                                  | 139 |

| Table 23: TLC Running Statistics for the untrusted network component     | 141 |

| Table 24: TLC Running Statistics for the protocol checking component     | 141 |

| Table 25: TLC Running Statistics for the cryptographic component         | 142 |

| Table 26: TLC Running Statistics for the security preprocessor           | 142 |

| Table 27: Relationship between TLA+ specifications and CAmkES components | 146 |

| Table 28: A Modbus ASCII message                                         | 153 |

# LIST OF FIGURES

| FIGURE                                                                              | GE   |

|-------------------------------------------------------------------------------------|------|

| Figure 1: A PLC field device setup                                                  | 5    |

| Figure 2: A PLC process network setup                                               | 6    |

| Figure 3: Proposed network design for a unidirectional gateway. Taken from [49]     | 26   |

| Figure 4: An example Kripke structure. Taken from [69]                              | 36   |

| Figure 5:A FIFO queue capped at 3 elements                                          | 37   |

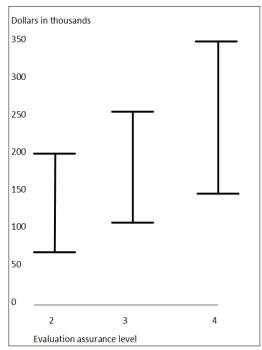

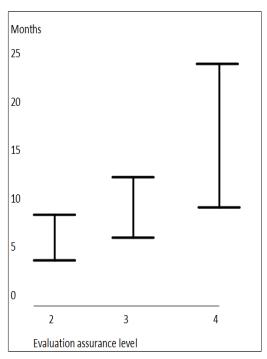

| Figure 6: Range of costs required for completing product evaluations at varie       | ous  |

| evaluation assurance levels. Adapted from GAO report [24]                           | 44   |

| Figure 7: Range of sample cost of NIAP evaluations to vendors by evaluation assuran | nce  |

| level. Adapted from GAO report                                                      | 44   |

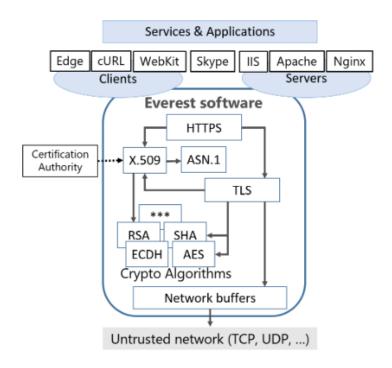

| Figure 8: The verified components of the TLS1.3 suite. Image from https://proje     | ect- |

| everest.github.io/                                                                  | 52   |

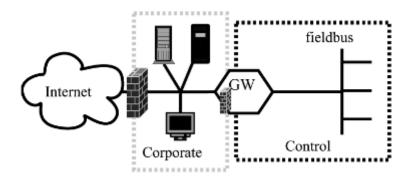

| Figure 9: A sample fieldbus architecture, from [116]                                | 65   |

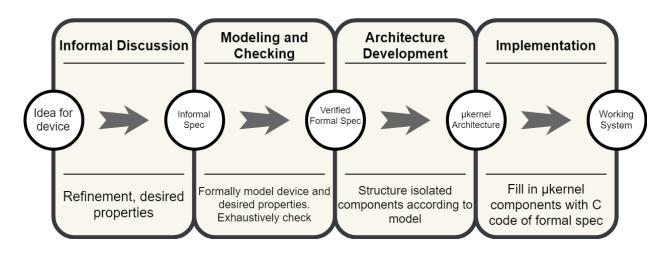

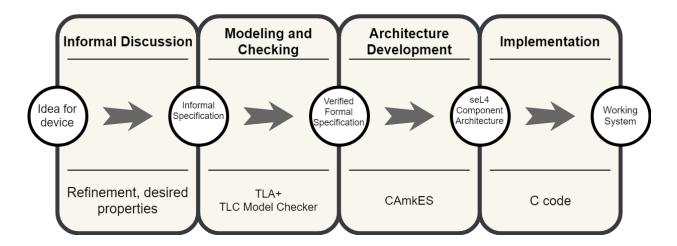

| Figure 10: Development steps for verifying embedded control system devices          | 74   |

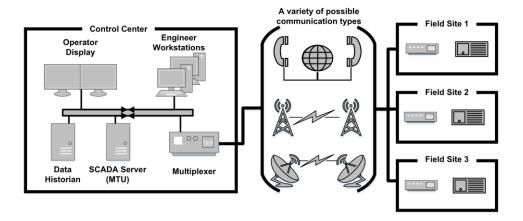

| Figure 11: A typical ICS network topology, adapted from [130]                       | 75   |

| Figure 12: Development steps for verifying seL4 designs using TLA+                  | 81   |

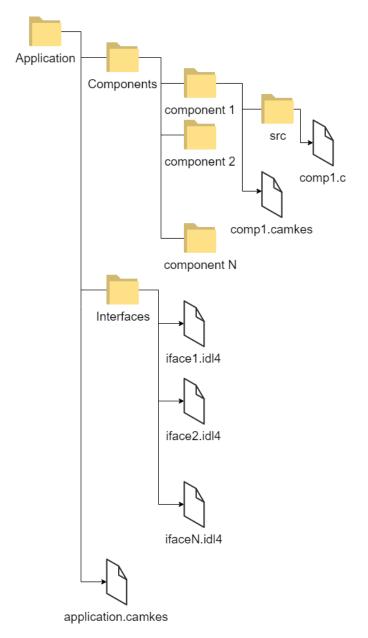

| Figure 13: CAmkES directory setup for an example application. Each component has    | its  |

| own directory housed within the "Components" directory. Each component directory l  | has  |

| a camkes file and a src folder containing C code                                    | 83   |

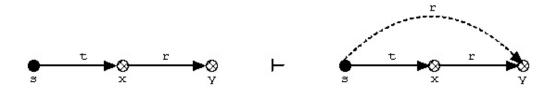

| Figure 14: PlusCal definitions for Send and Receive macros                             |

|----------------------------------------------------------------------------------------|

| Figure 15: Send macros in TLA+ and their translations into CAmkES connections          |

| Declarations of seL4RPCCall connections from the Modtx component to the protoco        |

| checking component (conn1) and the crypto component (conn2)                            |

| Figure 16: A Send macro in TLA+ and its translation to a CAmkES interface              |

| Figure 17: Translation of a PlusCal send macro to a CAmkES component definition 85     |

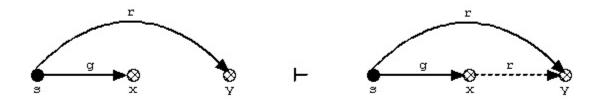

| Figure 18: Connection from the control center (left) to RTU (right) on a typical SCADA |

| network                                                                                |

| Figure 19: Connection from the control center to RTU with the FD-SPP installed 88      |

| Figure 20: FD-SPP architecture                                                         |

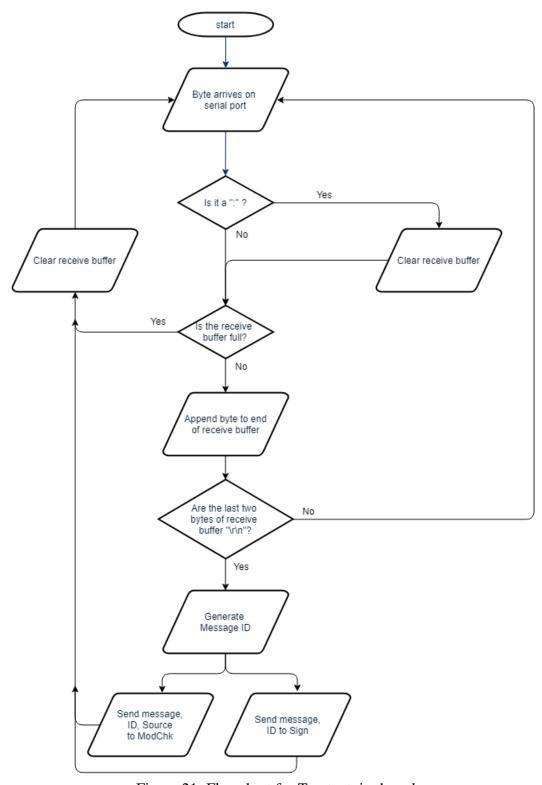

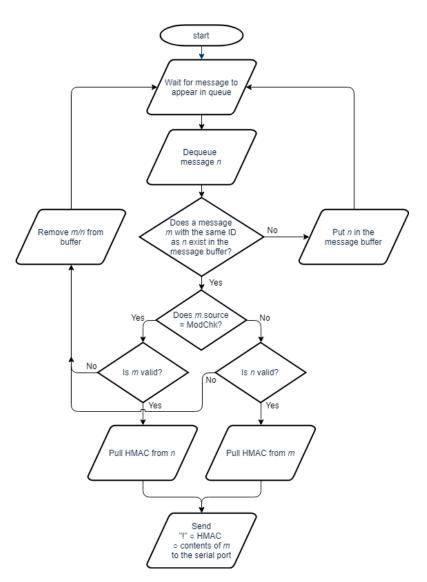

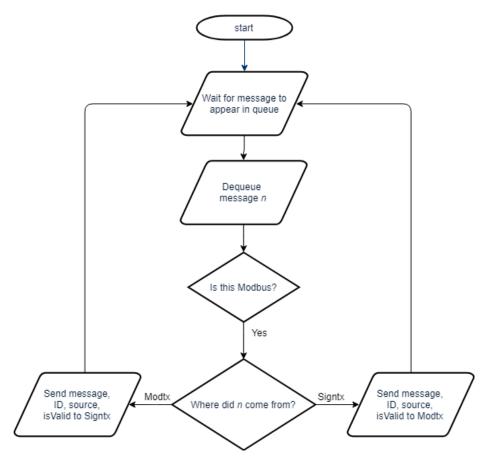

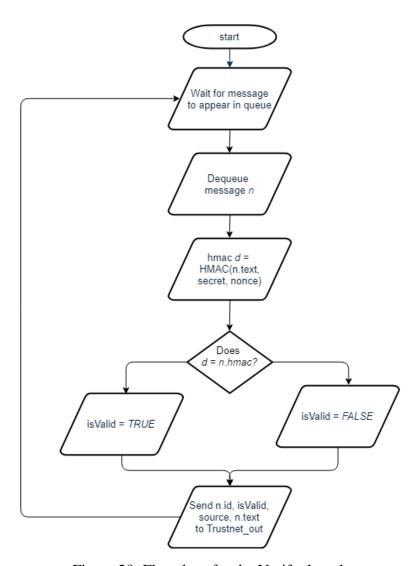

| Figure 21: Flowchart for Trustnet_in thread                                            |

| Figure 22: Flowchart for Trustnet_out thread                                           |

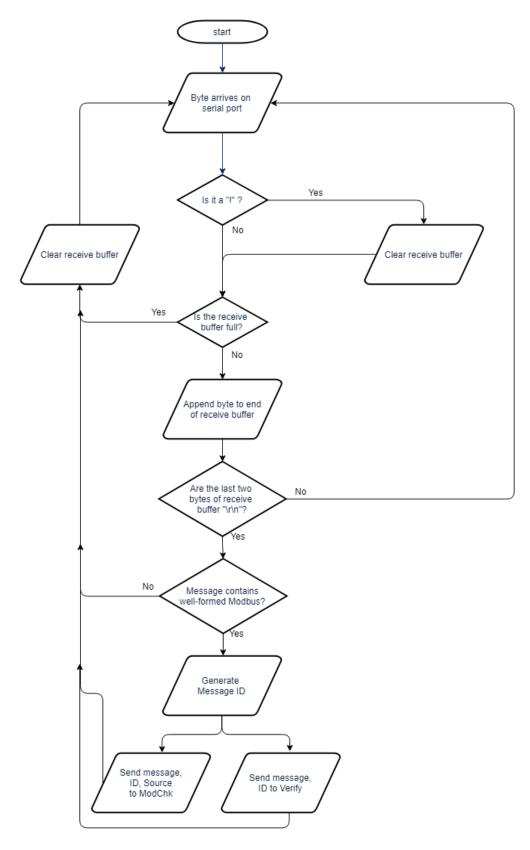

| Figure 23: Flowchart for untrustnet_in thread                                          |

| Figure 24: Flowchart for Untrustnet_out thread                                         |

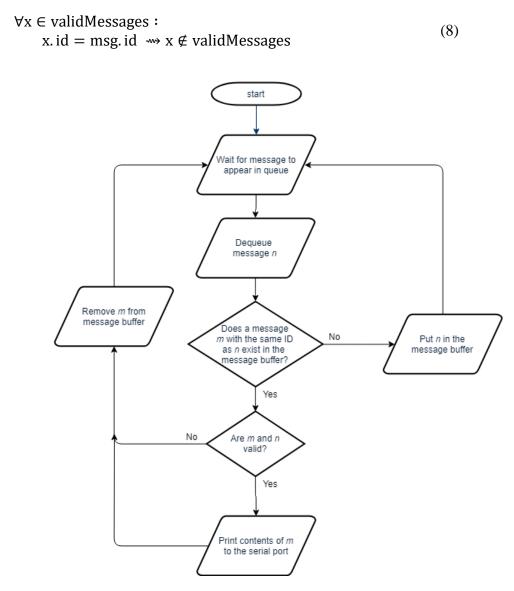

| Figure 25: Flowchart for the Modchk component                                          |

| Figure 26: Flowchart for the IsModbus operator                                         |

| Figure 27: Flowchart for the Sign thread                                               |

| Figure 28: Flowchart for the Verify thread                                             |

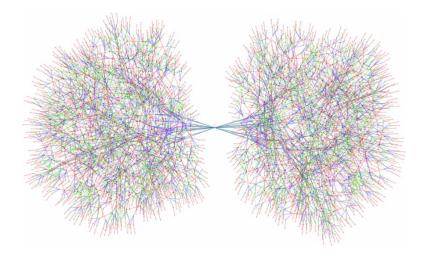

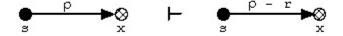

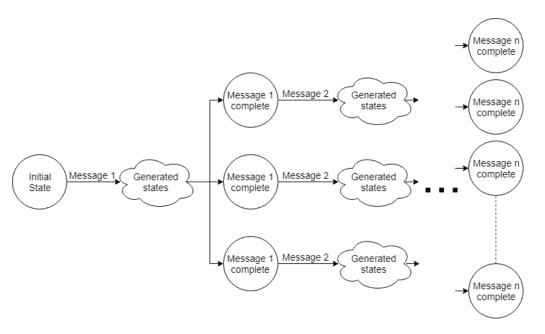

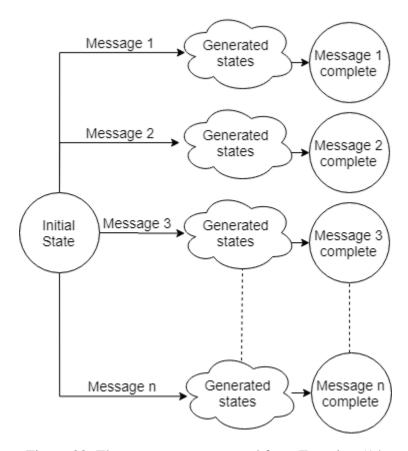

| Figure 29: The state space generated from (13)                                         |

| Figure 30: The state space generated from Equation 14                                  |

| Figure 31: Development steps for verifying seL4 designs using TLA+ 145                 |

| Figure 32: CAmkES output for the system architecture                                   |

| Figure 33: Flow of messages through Modtx                                              |

| Figure 34: The Modtx component definition       | 149 |

|-------------------------------------------------|-----|

| Figure 35: The ModtxIface interface definition  | 149 |

| Figure 36: Flow of messages through Signtx      | 151 |

| Figure 37: The Signtx component definition      | 152 |

| Figure 38: The SigntxIface interface definition | 152 |

| Figure 39: The Modchk component definition      | 154 |

| Figure 40: The ModchkIface interface definition | 154 |

| Figure 41: The Crypto component definition      | 156 |

| Figure 42: The CryptoIface interface definition | 156 |

| Figure 43: The system composition definition    | 157 |

## CHAPTER I

#### INTRODUCTION

Industrial control system (ICS) is a general term describing multiple configurations of networked industrial computer systems [1]. ICSs regulate factory floors and utilities such as power grids, dams, water-treatment facilities, and many more. Unlike typical corporate IT networks, ICS engineers value availability above confidentiality [2]. Keeping the data in the system private is not as important as keeping the system running. Threats to an ICS reflect this priority: an attacker seeks to disturb and disrupt the controlled process. Disrupting these processes could lead to physical consequences affecting the surrounding area like the attack on Maroochy Water Services, a water-treatment plant in Australia. A disgruntled employee manipulated the control systems to seize control from plant engineers and dump sewage into surrounding parks and rivers [3]. The importance of availability disincentivizes ICS engineers making regular changes or updates to the systems for fear of unscheduled downtime.

A variety of factors have led to the current challenge-riddled state of ICS cyber security. One of the primary reasons for lack of security is that ICS networks have historically been physically isolated from the greater internet [4][5]. SCADA communications protocols were therefore designed to prevent accidental corruption from a well-meaning operator rather than a purposeful attack. Incidents like Stuxnet have shown that air-gapping a SCADA network is no longer enough protection [6]. Many

industry-standard protocols such as MODBUS, EtherNet/IP, Profibus, and others have no means for ensuring the validity of messages [7], [8], [5]. This presents an opening for a malicious user to pretend to be either an operator controlling a Programmable Logic Controller (PLC) directly or an intermediate PLC controlling a device located at a remote substation. Once an attacker is inside a network any message the attacker sends is trusted and processed by the devices --- to potentially disastrous effects. A layering of multiple defensive strategies is required to mitigate this vulnerability and adding security to the communication protocols can cover some of the security holes. The need for security in protocols is shown in DNP3's efforts to create Secure Authentication (SA) within the DNP3 specification. The expanded capability of DNP3 SA currently offers protection against many common attacks by adding a challenge-response system for ensuring validity of communication across the DNP3 network[9]. DNP3 Secure Authentication is limited in its coverage of security concerns: it applies only to infrastructure currently using DNP3 and can be troublesome on networks using a variety of networking technologies to connect central control facilities to remote substations.

Formal methods are techniques for adding a high level of assurance to designs and implementations[10]–[14]. Human languages are ambiguous by nature and thus are not suited to describing software beyond the planning phases. Formal modeling can be used not only to create explicit designs, but also to logically prove certain properties of the designs. Proofs of security and fail-safety can be very useful in an ICS environment. This paper looks to use formal modeling and logic to prove security and assurance properties of a protocol designed to encapsulate SCADA traffic.

This chapter seeks to provide the reader with enough background information on the fields of Industrial Control Systems (ICS), ICS security, and formal methods to understand the context behind the research presented in the following chapters. The practical aspects of this research require a mix of resources from peer-reviewed academic papers, established industry standards, and white papers.

# 1.1 Industrial Control Systems

Industrial control extends it reach across electrical grids, wastewater treatment facilities, dams, water distribution systems, agricultural irrigation systems, pipelines for oil and natural gas, railroads, manufacturing plants, and air traffic control. The physical processes in these systems are controlled using electrical, mechanical, hydraulic, or pneumatic components [1]. Historically, such processes were operated by humans using analog mechanisms. Advances in digital technology offered new opportunities for control systems as integrated circuits and microprocessors started to replace old analog control loops and their human operators. As more of the controls became digital, the value of an interconnected control system became apparent. New communication mediums and protocols were developed to extend the reach of the system to geographically distant substations such as a neighborhood water tower located miles away from the city's central distribution facility.

While advancements in ICS technology sometimes mirror that of a traditional corporate network, its requirements and operation do not. ICS networks are seeing more use of Ethernet, however, the protocols selected allow for some level of determinism, real-time collection, and low overhead [15]. Traditional networks are shallow in their functionality with a very limited set of protocols and standards. ICS networks are more

varied with separate entities performing separate duties with physical goals in mind [16]. Knowledge of a traditional IT network will help in understanding an ICS network, but some key terminology explained below helps illustrate the difference.

Supervisory Control and Data Acquisition (SCADA) systems are used to control and monitor physical systems spread over a wide geographical region [15], [17], [18]. The first SCADA systems were simple configurations of sensors connected to dials, lights analog strip charts organized on a panel. Changes in the physical system would be picked up by the sensor and turn a dial or register on the chart in real time. A human would read the panel then act to adjust the system as needed. This basic system, while admirably fulfilling its purpose of getting the operator information about the system in real time, had some key shortcomings: an operator had to be present and monitoring the system at all times, each output on the panel was directly connected to a sensor so wiring new sensors became unwieldy, everything was local – substations could not be monitored from a central location, reconfiguring the system became increasingly difficult as the system grew, the type of data that could be collected and displayed was basic, and storage of the data was virtually non-existent.

Modern SCADA systems utilize advancements in communication to operate over distances of a few hundred yards to thousands of miles. Modern visual displays and microcontrollers/microcomputers allows more flexibility in the data collected and the control that can be exerted upon the system. There are three configurations for modern SCADA systems: *open loop* where the controls on the system are defined in advance and the state of the system has no bearing on the automated instructions, *closed loop* where the data acquired from the physical system is fed into the control modules and

instructions are adjusted accordingly, and *manual systems* in which a human manually controls the system based on the data collected.

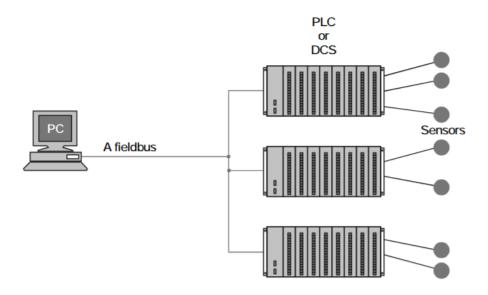

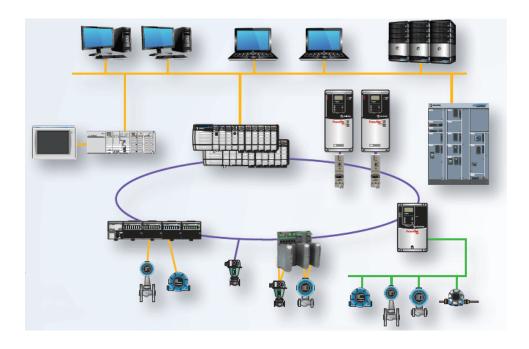

Distributed control systems (DCS) are used to control the automation of industrial processes at a single location. DCS oversee multiple subsystems that each have separate responsibilities at individual points in a process. Through a DCS these subsystems can be integrated with feedback and/or feed forward loops to compensate for variability at each stage of the process. This allows the process as a whole to self-correct in the event a single point misbehaves. DCS are widespread in oil refineries and food, chemical, and automotive production plants. These connect with programmable logic controllers (PLCs) that governs industrial equipment and processes. PLCs can be used as field devices on SCADA and DCS systems as seen in Figure 1 or as primary control devices in smaller systems like in Figure 2.

Figure 1: A PLC field device setup

Figure 2: A PLC process network setup

Understanding the manufacturing needs of the industries that use ICS helps to understand the ICS configurations. There are *manufacturing* industries and *distribution* industries [16]. Manufacturing industries typically involve a single location such as a factory and are further split into *continuous manufacturing process* wherein the process from raw materials to finished product runs continuously and *batch manufacturing process* where the process is broken into distinct steps producing a specific amount of the product. Examples of continuous manufacturing processes include petroleum and distillation in a chemical plant. Food and consumer goods are examples of batch manufacturing. The small area of operation allows for greater reliability and performance in the networking technology used within the factory. Distribution industries, on the other hand, control devices spread over large distances such as oil and water pipelines and railway systems and offer less assurance in communication. These systems use leased lines, radio frequency, and satellite links [15] to overcome these great distances, each of

these with their own security and reliability concerns. Distribution industries are typically designed to handle the reliability and timing challenges that come with long distance communications.

# 1.2 Components of Industrial Control

The differences between IT networks and control networks can further be detailed in the devices and protocols that make up the environment. A *Remote Terminal Unit* (RTU) interface with machinery and sensors in modern ICS networks. RTUs govern industrial equipment and processes. They are lower cost and lower capability than a PLC and are used in remote stations where less functionality is required and less user interaction is desired. RTUs often comes equipped with radio capabilities for wireless communications to the central stations. A *control server* (or *master* server) hosts the control software and sends instructions to the PLCs and RTUs around the network. This is usually located at the central control facility and is used to collect and process information relayed from field devices. An *Intelligent Electronic Device* (IED) is a "smart" sensor/actuator that may sit between the RTU and the machinery or it may replace the RTU entirely and communicate directly with the control server. IEDs have functionality to run simple routines to react to changes in the parameters of the system, but are usually polled by RTUs or PLCs and given instructions from there.

ICS operators manipulate the system through a *Human Machine Interface* (HMI). An HMI is software that allows the control engineers to monitor the elements of the processes under control. A typical HMI can allow an engineer to set alarms in case certain limits are exceeded, modify the processes, take manual control in case of emergency, and read reports on runtime information. HMIs can be located in the control

center, on engineer workstations or laptops, and more recently on mobile devices. The data that is collected or calculated and any triggered events or alarms are usually saved and stored for later analysis. This data can be collected in a *data historian* that can reside on the control network or an outside network with security restrictions in place to prevent it from communicating in any way with the control network other than receiving information. A slave historian can be used to duplicate the historian's data onto a server on the corporate network for the business to access and analyze.

# 1.3 ICS Network Devices and Requirements

ICS networking concepts and requirements evolved from a need to rein in the wiring of early control systems. As described earlier, each sensor used to be wired directly to the meter displaying its reading to the operator. Each sensor required a separate wire for each binary digit it was expected to record [19]. This method of wiring was quickly outgrown and the industry requested a solution from its vendors and university researchers. The solution was a Fieldbus, a network that connected devices in the field such as RTUs and IEDs to the central facilities. Fieldbus is a broad term to describe all the communication technologies that solve this wiring problem. Many protocols, such as Modbus[20]–[22], Distributed Network Protocol (DNP3)[23][24]– [26], and Common Industrial Protocol (CIP) family of protocols [27], [28] are used on a fieldbus network. These protocols are responsible for handling any device identification in place of individual wires for each sensor. The medium for communication is undefined for a fieldbus and may include multiple technologies such as Ethernet, serial, satellite link, telephone lines, or radio frequency [15]. To this end, a modem is a device that can translate a digital signal into analog for easier transmission over any number of longdistance mediums. One modem would be connected at a remote substation to translate digital signals from the RTU into analog and another would be located at the central facility to translate the analog signal back into digital for use.

This research makes heavy use of Modbus, so it may benefit the reader to have a longer explanation of Modbus in particular. Modbus is an open communication protocol developed in 1979 by Modicon for use in ICS networks. ICS are difficult to install and difficult to upgrade and have longer lifecycles relative to corporate networks. This lead to operators preferring open standards and the proliferation of protocols like Modbus [16]. As described in the specification guide in [29], the base Modbus is a simple, stateless, call-and-response protocol. It contains a simple addressing scheme allowing for up to 247 devices on a common bus, a field for a function code that tells the target devices which procedure to run, and a data field that can contain up to 252 bytes for the target device to act on. There are two versions of Modbus: Modbus RTU and Modbus ASCII. Modbus RTU transmits raw bytes and uses a specific minimum time between bytes sent over the bus to distinguish between frames and a Cyclic Redundancy Check (CRC) to detect errors in transmission. Modbus ASCII operates on ASCII-encoded messages, utilizing two bytes where Modbus RTU would only require one. Modbus ASCII distinguishes frames with a colon. Whenever a device receives a ":" it knows a new message has started, regardless of where the previous message left off. To detect transmission errors, Modbus ASCII makes use of a Longitudinal Redundancy Check (LRC). The structure of a Modbus ACSII message is presented in Table 1. This research uses Modbus ASCII for simplicity.

Table 1: A Modbus ASCII message

| \$<br>Start | Address | Function<br>Code | Sub code           | Data               | LRC     | End    |

|-------------|---------|------------------|--------------------|--------------------|---------|--------|

| ··.;        | 2 bytes | 2 bytes          | 2 bytes (optional) | Up to 504<br>bytes | 2 bytes | "\r\n" |

The growing interconnectedness of ICS networks with corporate networks and devices have led to incorporation of corporate network technologies. A *router* is a networking device that allows communication between logically separated networks. These are used to allow access to the control network from the corporate network and vice-versa. A *firewall* allows a network engineer to closely regulate the connections that are made across networks. A firewall (sometimes multiple [30], [31]) located at strategic points such as between the ICS and the corporate network or between the engineers terminal and the fieldbus can block unwanted network traffic from reaching the ICS. A *remote access point* is a device that allows control over the ICS remotely. Such devices include laptops, tablets, and smartphones that access the control network from anywhere through a *Virtual Private Network* (VPN), which encrypts traffic and "tunnels" through a public network.

Special considerations must be made when designing an ICS network. Each system is unique in its requirements and goals, and these factors inform the decisions made in selecting technologies and topologies. Depending on the nature of the industry, the timing requirements may range from 250 microseconds to 10 milliseconds. A response time that is less than the sensor's sample time is recommended [16]. This can necessitate processing power at a remote substation, as performing computations remotely might incur too significant of a delay. A distribution industry such as an oil pipeline would have SCADA components spread over thousands of miles with different

options for communications at different substations. The complexity of control needed for the system might allow simple controllers with predefined routines or might require high-level decision making from a human operator such as in air traffic control [1]. The need for high uptime, 99.999% or 5 minutes and 35 seconds per year of allowable downtime per year in some cases [32], and reliability would push for a system with more redundancy and alternate forms of communication should one fail. To go along with availability, the impact of a failure in the system must be considered. A failure in a nuclear reactor could have significant environmental impacts and would require both redundant control systems and physical safety mechanisms. Finally, operator safety must be considered. A control network in a car must be able to detect a sudden application of the brakes to tighten the seatbelt, apply the automatic braking system, and deploy airbags if needed.

# 1.4 Cyber Security for Industrial Control Systems

Industrial Control Systems (ICS) regulate processes that, if compromised, can have a physical effect on the environment around them. A broken ICS process can cause damages to the facilities containing the machinery and/or endanger human life [33]. As with the design considerations varying across industry, so too do the means by which an attacker can cause harm. Strict timing requirements mean that slowing down response time would disrupt the system. This is especially true of close-loop systems, where a transmission time exceeds the sample time. This error can propagate and amplify over cycles to force the system into an unstable state [34], [35]. Programmable Logic Controllers (PLCs), Remote Terminal Units (RTUs) and Intelligent Electronic Devices (IEDs) are designed to be programmed and reprogrammed as needed to suit changing

requirements in the system. An attacker could reprogram one of these devices to modify its behavior or adjust thresholds to effectively disable alarms. An attacker could modify or fake information being sent to PLCs and Human-Machine Interfaces (HMIs) to disguise unauthorized changes in the system or cause the operator to initiate inappropriate actions. As with a corporate or home network, malware-infected workstations can have degraded system performance or actively disrupt the system by modifying configurations. An attacker can also interfere with the safety mechanisms such as emergency shutdown systems, safety shutdown systems, or safety interlock systems [1], [36].

The design of ICS networks makes manipulating SCADA components simple. ICS networks were originally isolated from corporate networks and the greater networks, thus network traffic moving across the lines is inherently trusted. Early systems used specialized software and hardware with proprietary protocols. Modern systems are using cheap commercial off the shelf (COTS) hardware with open protocols and IT design principles that promote connectivity with corporate networks and erode the isolation that control networks used to enjoy [1][5]. While this integration of IT technology allows corporate network security measures to be utilized, the special considerations discussed in the previous section can limit their viability. These special considerations can also require new technologies to be developed.

When considering the CIA triad [37], the priorities for an ICS are different than traditional IT as seen in Table 2 [2]. Confidentiality is paramount for most IT systems. Trade secrets, banking information, employee personal information, and other sensitive data are stored on the IT network. The greatest cost to the organization is in this information leaking out, so the highest priority is confidentiality. Availability is last

because a traditional IT staff would rather have their system go down than have sensitive information compromised.

Table 2: Priorities of IT and ICS Networks

| Priority | IT              | SCADA/ICS       |

|----------|-----------------|-----------------|

| 1        | Confidentiality | Availability    |

| 2        | Integrity       | Integrity       |

| 3        | Availability    | Confidentiality |

Availability is the highest priority for ICS. Downtime of an ICS network could potentially damage expensive equipment as seen in the Stuxnet attack[6], damage the surrounding environment as seen in the Maroochy attack [3], deprive the community of critical utilities as seen in the Ukraine attacks[38], damage the company's reputation, or cause a loss of metering data, damaging the company's profits. Confidentiality is last because an ICS operator would rather have an attacker in the system snooping than to have any downtime. These factors present the challenge to security professionals. Security professionals face an infrastructure that was built before security was a concern, equipment that is old enough to be vulnerable to common attacks, and a zero-downtime mindset that makes applying updates and security patches difficult.

## 1.5 Vulnerabilities

The National Institute of Standards and Technology (NIST) separates ICS vulnerabilities into 6 categories: Policy and Procedural, Configuration and Maintenance, Architecture and Design, Physical, Software Development, and Communication and Network. Causes of security failures might overlap across categories. Specific systems may also have unique vulnerabilities as each ICS is specially designed. Some

vulnerabilities can be removed or mitigated, while others must simply be accepted. See Special Publications 800-82[1] and 800-53A[39] for detailed analysis.

Policy and Procedural vulnerabilities are introduced into ICS through lack of security policies and a relaxed security posture in the organization. Security policies govern staff and stakeholders on proper use of systems to reduce the attack surface of the system. As shown above, security of ICS is often not the top priority so such policies can be scarce. Mitigations of this class of vulnerability include awareness and training programs to educate employees on proper upkeep of a secure environment, as well as maintaining a proper written security policy and plans for breaches. Proper authentication policies for employees such as smart cards and strictly enforced access policies, as well as proper authorization policies following the *principle of least privilege* as described in [37].

Misconfigured or default-configured devices make up Configuration and Maintenance vulnerabilities. NIST describes this class of vulnerabilities as those that would be similar to challenges faced by a corporate IT network; namely up-to-date patches of software and proper use of security controls available from vendors such as access control policies and firewall rules. The uptime requirements of some ICS networks as described in the previous sections can make patching and upgrading difficult, with some vendors recommending staying on outdated versions of software to ensure functionality or contractually obligating asset owners to involve the vendors in upgrades or risk voiding warrantees [32]. Legacy ICS components may be no longer supported, but still in production. Malicious software, or *malware*, is a common method of attack which can be mitigated. To go along with access control configurations, deficiencies in logging

can prevent detection of abnormal behavior and make forensic analysis of attacks impossible.

Architecture and Design vulnerabilities arise from inadequate planning of ICS growth and failure to incorporate security priorities from the beginning of development. Legacy systems may have been designed before security technologies were widely available or may have expanded and changed without evaluating the effects of new capabilities on the organizations security posture. Loosely defined security perimeters around ICS networks make proper enforcement of security policies difficult. Intermixing of control and non-control network services and can cause control networks to be vulnerable to common non-control issues. A control network that depends on services such as Domain Name System (DNS) on an IT network might see reduced availability as an IT network typically does not conform to the same uptime standards.

Physical vulnerabilities range from physical access to control equipment to natural disasters. Improper access to network or control equipment could lead to theft, damage of hardware, unauthorized changes or additions to software and configurations of devices on the network, or installation of new unauthorized devices. Most devices, while properly access controlled from networked ports, have local ports with no access control capabilities to aid in maintenance. Consideration must be taken when securing safety-critical equipment to not make access to emergency shutdown functions too difficult for authorized personnel. Certain natural phenomena such as Electromagnetic Pulses, Radio Frequency (RF) interference, and power dips and spikes can cause temporary loss of service or permanent damage to devices and networks.

Software Development vulnerabilities cover errors in the design and implementation of the software running in the environment. Fragile or bug-ridden software that has not been developed to high-assurance standards (or was developed before such standards existed) leave holes open for malicious or erroneous behavior to impact operation [40][41]. Specially designed ICS networks and components make patch release cycles difficult for vendors of ICS devices. Specific requirements for systems mean unique software patches made available for certain customers, each with their own testing cycles, leaving vulnerable components with no mitigations for extended periods of time. Software lacking security tools such as separate privileges and access controls also fit into this category.

Communication and network vulnerabilities that are present in traditional IT networks are present in ICS networks. Unsecured communication across the network or lack of a managed solution for restricting communication (such as proper firewalls) can open an ICS network to attack. There are cases specific to ICS networks though; such as use of proprietary protocols or encryption and simple embedded device drivers that are unable to handle anything but the most expected network traffic [41]. Previous sections described ICS networking protocol such as Modbus, but notably absent from the discussion of the base protocol was any form of authorization or authentication. These protocols are vulnerable to *Man in the Middle* attacks wherein a malicious actor intercepts communications, and to *spoofing* attacks wherein an attacker masquerades as a legitimate network device sending fake traffic. There have been efforts to retroactively add security to open protocols [7] and to update standards to include secure operating

modes [23], but these still succumb to errors in design leading to more vulnerabilities [42].

Each of these classes of vulnerabilities have seen significant effort toward mitigation from both the private and public sector. Some of the mitigations include new technology and software developed to fill a hole in security capabilities, while others involve new methods for applying existing technology. There are numerous best-practices guides [32], [1], [15], [39], [43] and whitepapers addressing each class that will be described in the next section.

## 1.6 ICS Policies & Best Practices

The vulnerabilities described in the previous section have mitigating controls via both additional technologies and more strict policies. This section describes some of the industry standard best practices for software configurations, infrastructure designs, and human policy to harden Industrial Control System (ICS) networks against attack. The goal of policies is to reduce the effectiveness of attacks against existing vulnerabilities. As such they can be considered mitigating controls for cases where a security fix cannot be applied or does not exist. These also follow a *defense-in-depth* philosophy, working in tandem to boost the effective mitigation of the system as a whole. These recommendations come from National Institute of Standards and Technology (NIST) [1], [39], and industry group whitepapers.

# 1.6.1 Systems Design

The engineering of a system is more complex than ensuring each technical component is operating as intended. The definition of a system can change depending on

context. Ross Anderson describes a variety of definitions in [44] and summarized below and applied to ICS.

- 1. A component such as a network card or cryptographic hardware.

- 2. A collection of the above plus an operating system, physical networking devices, and networking protocols.

- 3. The above plus applications that run on the nodes of the network such as an HMI.

- 4. The above plus operators.

- 5. The above plus management and corporate users

- 6. The above plus venders and customers

A system is more than its individual components. How the components interact with one another and how a system might allow the human element to compromise its integrity must be carefully considered.

The *Physical Topology* is the physical location and design of facilities in and around components of an ICS. In an ICS just as in traditional IT, if an attacker has physical access to a device then that device should be considered compromised. Physical security is just as important as electronic security and should be closely monitored. All doors should have locks, locks should be controlled with card readers, and physical security logs should be monitored just as closely as firewall logs. In highly critical systems armed guards may be necessary. Similarly, any computer devices used in the day to day operation of the ICS such as engineering laptops or PLC programming tools should never leave the area. Just as no unauthorized personnel should be allowed in, no operations equipment should be allowed out.

Physical topology can extend to environmental considerations for protections against mistake or malice. In the event a process is disrupted, having physical safeguards such as spillways to direct overflowing liquid materials and natural berms to prevent

contamination outside of the area of operation. Designing physical systems to fail safe is an integral part of safety considerations, and can act as a means to mitigate certain security vulnerabilities.

Logical Topology, or Network Topology, is the design for the system's behavior and how a system's components interact with one another. This includes considerations for how networks are divided, restrictions on network access to certain areas and certain devices, and policies governing behavior of humans interacting with the ICS. ICS must be logically separated from any other network it is connected to. A demilitarized zone is recommended as a buffer between the corporate network and the ICS. This prevents traffic from flowing directly between the two networks. To further the separation separate sets of authentication credentials should be used for both networks. If a control engineer's credentials on the corporate network are compromised then the impact to the ICS is limited, if there is any impact at all.

The ICS itself must be split into multiple layers. An attacker should have to penetrate multiple levels of security before reaching the critical systems. This can be accomplished with firewalls on the drop of the ICS, between the control server and PLCs/RTUs, and between the historian and the remote substations. Individual components of an ICS must also be separated from one another. Traffic between the control server and a pump at one end of the plant should have no business touching the assembly line at the other end of the plant. Similarly the pump operator should not have access to send commands to the assembly line.

Traffic on an ICS can be more strictly defined than traffic on a traditional IT corporate network. With this in mind any extra functionality provided by devices on the

ICS that is not being used such as extra radios, open ports, and web interfaces should be disabled. Not only does this reduce the attack surface of the ICS, but it also reduces the amount of monitoring and logging that needs to be done. The simpler nature of ICS also means operator roles can be more rigorously defined. Roles for operators should be designed according to the principle of least privilege [45][44]. If a lower level operator's credentials are compromised the breach will only affect the systems that operator is authorized to use.

# 1.6.2 Configurations

Components of an ICS network must be configured to suit their roles sufficiently within the design of the system. While many devices might not support security-specific features such as cryptography or access controls, they can be configured intelligently to reduce their attack surface and improve the security of the system as a whole. Additionally, for the devices that *do* support security specific features, special efforts should be made to ensure these features are properly enabled, configured, and tested. This section describes some of these configuration options and considerations.

Address Space Layout Randomization (ASLR) seeks to render shell code and return-oriented programming exploits difficult by reordering the memory addresses of elements of a program each time the program is run. ASLR is a setting that affects software in development. The software must have a specific linker flag at compile time to enable ASLR. ASLR is supported on Windows operating systems from Vista onward, FreeBSD, OpenBSD, Linux, Solaris, and OS X 10.7 onward. ASLR compliments data execution prevention (DEP) technologies. Where ASLR randomizes memory locations, DEP prevents execution of code from certain parts of memory that are commonly

targeted by attackers, such as the heap and the stack. Support for ASLR and DEP is not common in embedded devices, with only 22% of devices supporting ASLR and 44% supporting DEP [46].

Application whitelisting is a method to eliminate the problem of having to track the changing malware trends by only allowing applications to run which have been given specific permission. Whitelisting software allows an administrator to specify which executables she wants enabled on the system. Malware that infects the system would never get a chance to execute. A case study from the Amor Group in 2012 reviewed the results of applying application whitelisting in the North Sea oil and gas industry [47]. Implementing whitelisting on the oil rigs, ships, and other assets revealed the presence of previously unidentified malware and helped the team catalog all of the legitimate software running on the multitude of computer systems. After whitelisting, no reinfections of systems were detected and a stricter management of applications was enabled.

As control systems gradually become less isolated, the edge of the network (or subnetworks if the control system is divided) must enforce proper access controls through firewalling. If the ICS cannot be air-gapped from the corporate network then strict control over all physical connections is essential to protecting the network. Firewall strategy for an ICS is similar to firewall strategy for a traditional IT network. When deciding on a firewall solution at minimum the firewall should require authentication before any configuration changes are made, be able to perform self-testing, and be able to perform logging. Firewall rules must be made according to the whitelist philosophy: traffic is denied unless it is explicitly allowed. This is vitally important because even the most

innocent of traffic can cause problems to an ICS. A simple network enumeration, a perfectly harmless operation on a corporate network, can cause system outages. Considering how time-sensitive an ICS can be this "harmless" traffic can consume enough processing time to effectively render the nodes in the network unavailable. A firewalling strategy can be split between two separate methods, ingress and egress.

Ingress filtering means filtering network traffic coming into the network from the outside. Filtering incoming traffic is the first line of defense against malware infiltrating the ICS. There is very little traffic that should be entering the ICS. Traffic allowed to enter an industrial control system (ICS), if there is to be any allowed, can be clearly defined. Consideration can be given to the purpose of incoming traffic, from where the traffic originates, the communication protocols necessary, whether these operations can be done locally, and the time of day or week this traffic can be expected. These questions allow strict rules to be implemented and policies for temporary rules to be enforced.

Egress filtering involves filtering the network traffic leaving the network and originating from the inside. Since no system is unbreakable, it is important to implement firewall rules under the assumption that the system has already been compromised. A compromised system often makes outbound connections to a control server, either to push data or to receive further instructions. To this end it is necessary to filter outbound traffic just as much as inbound traffic. If malware finds its way onto the system through USB, such as described earlier with Stuxnet, then its damages can be limited by blocking its attempts to make connections outside the network. The same consideration should be made for egress filtering as ingress, with traffic leaving the network clearly defined before allowing traffic to egress. Another important consideration is whether the traffic

needs to be part of a session, with packets traveling both in and out of the network to complete transactions. Special hardware, such as the unidirectional gateway described later, can be used to physically limit data to a single direction should this not be required.

# 1.6.3 Patch Management and Disaster Recovery

Because of the extremely high importance of uptime, change and patch management of ICS can be more daunting than traditional IT. Protecting the individual components of the ICS, the field devices, the historians, and the operation centers at the operating system and firmware level adds to the security of the ICS as a whole. If an attacker can compromise a single device by exploiting outdated or misconfigured firmware then that attacker is now in control of a trusted node and is now operating at that node's trust level across the network. However, an improperly tested patch can bring just as much harm as an outdated patch that has been compromised.

Proper testing of patches is necessary before the patches reach the production system. One of the major challenges in keeping an ICS up to date is the sheer number of variables that can be unique to a specific ICS environment. A vendor may not be able to tailor patches specifically enough to support a given deployment. It is possible a patch may do more harm than good if not tested well enough. A security patch released by a vendor must be thoroughly tested on a system as close to production as possible in functionality before deployment. This problem is not solely the responsibility of the control engineers. Vendors should be held to a higher standard in creating software and patches robust enough to handle the vast variability from system to system.

Disaster recovery is the ability for a system to return to normal operation after an incident, whether accidental or by malice. Adverse conditions and disasters will happen and having procedures in place for these events is crucial to protecting the uptime of the ICS. This policy solution takes place in the planning stages of the ICS. The ICS must be designed in such a way that an unforeseen event can safely take down a part of the network with minimal effect on other parts of the system. To accomplish this each component of the system should be made redundant. If the first component goes down the second should be ready to instantly pick up the workload. An often missed component of redundancy is that components should fail in a way that does not result in diverted traffic overloading other systems either at the same stage of the process, upstream, or downstream. A graceful failure should be tested before the system goes into production. Should the entire system go down it is important to have a disaster recovery plan in place to get the system producing again. This can mean having a store of product in reserve while production is restored, or having multiple plants dispersed across multiple geographic regions which would be unlikely to be hit by the same natural disaster.

## 1.6.4 Hardware Device Solution

## 1.6.4.1 Blue Coat ICS Protection Station Scanner

Blue Coat's ICS Protection is a software and hardware solution that mitigates the risk of using USB storage devices on industrial networks. Stuxnet spread so successfully through removable drives and ICS Protection Station Scanner is designed to limit this specific attack surface. ICS Protection Station Scanner combines a hardware solution that resides outside the ICS and a software solution that runs on all Windows workstations

within the ICS. Under Blue Coat's recommended policies any USB removable storage must be verified by its dedicated appliance before it can be used within the ICS[48]

# 1.6.4.2 *Unidirectional Security Gateway*

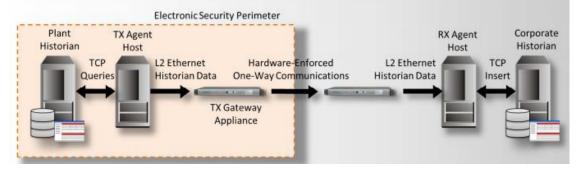

Waterfall Security's Unidirectional Security Gateway [49] addresses the problem of securely isolating the control network while also allowing business users on the corporate network to perform their job functions. This technology has been used to safely replicate the plant historian outside the network for the business to read. Transfer (TX) equipment sits inside the control network and queries the plant historian. The TX gateway then sends this data through a one-way fiber communication channel to an RX gateway sitting on the corporate network. The receive (RX) equipment then builds a faithful replica of the plant historian called a corporate historian on the corporate network. Corporate users and applications connect to the corporate historian to process the operating data. The one-way communication is enforced in the hardware of the gateways. The TX gateway only comes equipped with a laser, the RX gateway with only a photocell, and data is transferred through fiber. Sending data to the plant through this technology is not possible. A proposed network design for a unidirectional gateway is shown in Figure 3.

Another proposed use of this technology is allowing vendor support to troubleshoot problems on the control network without any actual remote access. A program records the local engineer's screen and sends that data through the unidirectional gateway to the vendor screen. The vendor directs any troubleshooting steps through telephone to the local engineer. In this scenario the vendor gets visual, real-time feedback from the system while also ensuring any actions are performed by a local plant engineer.

- TX agent software queries servers & gathers data

- Data & metadata is sent to RX host

- RX agent software uses data to populate replica servers

- Faithful replica, tracks all changes, new tags, alerts in replica

- Corporate users and applications connect to replica

Figure 3: Proposed network design for a unidirectional gateway. Taken from [49]

## 1.6.4.3 Tofino Xenon Security Appliance

Tofino developed a security appliance specifically for SCADA environments that resembles a plug-and-play firewall. It is designed to operate between a process network and the business network. It is capable of filtering messages at layers 2, 3, and 4 of the OSI model, as well as performing deep-packet inspection to make filtering decisions based on the specifics of the control network protocol (Modbus, DNP3, Profibus, and the like) in use. The deep packet inspection of control network protocols is what separates the Tofino security appliance from a typical corporate firewall solution [50].

# 1.7 Cyber Attacks

The instances of the aforementioned vulnerabilities being exploited has been increasing recently as more Industrial Control Systems (ICS) have lost their isolation from their corporate network counterparts [40][30], [51]. This section describes some select attacks with information gathered from technical reports and forensic analyses of

the attacks after the fact. This section describes three attacks: Maroochy water treatment facility attacks, the STUXNET attacks, and the Ukrainian power grid attacks. These incidents were chosen to highlight different threat actors, different vulnerabilities exploited, and different industries affected.

The Maroochy attacks in 2000 involved a formal employee of the asset owner using stolen equipment to remotely manipulate water treatment facilities. Vitek Boden, a disgruntled former employee of Hunter Watertech in Queensland, Australia, compromised sewage equipment to dump 800,000 litres of raw sewage into local parks and rivers [3]. Boden used intimate knowledge of the sewage system his former employer installed to enact revenge on both Hunter Watertech and Maroochy Shire Council. Boden drove from site to site over a 2 month period using stolen radio equipment to interfere with signals being sent between the control server and the RTUs in the remote substations. Boden would craft communication packets to spoof a station on the SCADA network and send out commands as though he were that station. Because there was no authentication processes present in the system Boden was able use this method to shut off pumps, disable communications between components in the system, and disable the alarms that would have alerted the plant operators to any suspicious activity. After an investigation, Hunter Watertech determined the problems were caused by a malicious attacker rather than faulty equipment. Boden was put under surveillance and eventually caught when stolen radio equipment was found in his car during a routine traffic stop [3]. This attack exploited poor or non-existent security measures from the Configuration and Maintenance class of vulnerabilities described above. Its complexity was relatively low; a former employee was able to exploit stolen equipment without needing to develop new

software exploits or circumventing many security controls. As demonstrated with STUXNET, attacks on ICS networks can get significantly more complex.

Stuxnet was an elaborate malware targeting a specific configuration of ICS in 2009 and 2010. It is a definitive example of network isolation not guaranteeing safety [52]. Stuxnet gained infamy through its unprecedented level of complexity and because of its notable target in nuclear facilities. Roughly 60% of all infected hosts were found in Iran, with the remaining hosts spread across Europe, Asia, and the US. The worm was designed to reprogram a specific set of Siemens PLCs in such a way that the system being controlled would operate outside of its limits and degrade. It would also forge the operating data seen on the plant monitors so plant operators would not be able to detect any differences in the system. The complexity of the malware is readily apparent in the sheer breadth of its functionality. Symantecs Stuxnet Dossier lists the functionality described in Table 3, along with the category or categories of vulnerabilities the capability targeted.

Table 3: Stuxnet Capabilities and Targeted Vulnerability

| Stuxnet Capability                                                                                                                                                                                      | NIST Vulnerability Category                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Self-replicates through removable drives<br>exploiting a vulnerability allowing auto-<br>execution. Microsoft Windows Shortcut<br>LNK/PIF Files (Automatic File Execution<br>Vulnerability (BID 41732)) | Configuration and Maintenance                                               |

| Spreads in a LAN through a vulnerability in the Windows Print Spooler. Microsoft Windows Print Spooler Service Remote Code Execution Vulnerability (BID 43073)                                          | Configuration and Maintenance<br>Communication and Network<br>Configuration |

| Spreads through SMB by exploiting the Microsoft Windows Server Service RPC Handling Remote Code Execution Vulnerability (BID31874).                                                                     | Configuration and Maintenance                                               |

| Copies and executes itself on remote                                                                                                                                                                    | Configuration and Maintenance                                               |

| computers through network shares.                                                                                                                                                                                                    | Policy and Procedure<br>Architecture and Design                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Copies and executes itself on remote computers running a WinCC database server.                                                                                                                                                      | Policy and Procedure Communication and Network Configuration Architecture and Design |

| Copies itself into Step 7 projects in such a way that it automatically executes when the Step 7 project is loaded.                                                                                                                   | Software Development                                                                 |

| Updates itself through a peer-to-peer mechanism within a LAN.                                                                                                                                                                        | Configuration and Maintenance Policy and Procedure Architecture and Design           |

| Attempts to bypass security products.                                                                                                                                                                                                | Configuration and Maintenance Policy and Procedure                                   |

| Exploits a total of four unpatched Microsoft vulnerabilities, two of which are previously mentioned vulnerabilities for self-replication and the other two are escalation of privilege vulnerabilities that had yet to be disclosed. | Software Development                                                                 |

| Contacts a command and control server that allows the hacker to download and execute code, including updated versions                                                                                                                | Configuration and Maintenance<br>Policy and Procedure                                |

| Contains a Windows rootkit that hid its binaries.                                                                                                                                                                                    | Software Development                                                                 |

| Fingerprints a specific industrial control system and modifies code on the Siemens PLCs to potentially sabotage the system                                                                                                           | Configuration and Maintenance<br>Policy and Procedure                                |

| Hides modified code on PLCs, essentially a rootkit for PLCs.                                                                                                                                                                         | Software Development                                                                 |

This robustness suggest an immense amount of resources and person-hours poured into the product and perhaps hints at just how high value the target in Iran was to the authors. Symantec estimates a team of 5-10 developers and a team of management and QA engineers were required to produce the malware [52]. Not only did it require a lot of developers it also required a lot of ground work. Stuxnet used two compromised digital certificates and four 0-day vulnerabilities. It required a significant amount of reconnaissance on systems that were never connected to the internet. This means physical

access to the systems was required to gather information on the infrastructure, then again to deploy the worm [6], [52]–[54]. STUXNET targeted state nuclear facilities and was not meant to spread outside of its specific target. Its collateral damage was limited and damage to civilian systems was limited. This care is not always taken as shown with power grid attacks in Ukraine.

A more recent attack on utility infrastructure occurred on the 23rd of December, 2015 [38], [55], [56]. This attack, launched in Ukraine, was the first publicly known cyber-attack targeting power infrastructure. The attack was able to disrupt power to 225,000 customers spread over 3 different service territories. The attack started off with a spear fishing campaign and an infected Microsoft Excel document loaded with BlackEnergy 3 [57], a malware toolkit that allows for connection to a command and control server. With BlackEnergy 3 the attackers were able to gain persistence on the power companies' business network and find their way through the VPN connecting the business and ICS networks. This attack involved at least 6 months of network reconnaissance and many steps of non-ICS related activities to reach the intended target. Once on the control network the attackers used built-in commands of the entity's RTUs to open the breakers in at least 27 substations to cause the outage. The attackers also overwrote the firmware of serial-to-Ethernet devices on the network to translate traffic from the operator's Human Machine Interface (HMI) to the Remote Terminal Units (RTUs) to block plant operators from issuing commands to restore the substations remotely. A telephone denial-of-service attack was subsequently launched on the companies' call centers to restrict the flow of information to the customers affected. On a global scale this attack was relatively small; only affecting 225,000 citizens for roughly 3

hours. On a local scale this attack was catastrophic to the power networks and operators [38].

# 1.8 Summary