University of Kentucky UKnowledge

Theses and Dissertations--Electrical and Computer Engineering

**Electrical and Computer Engineering**

2019

# A Compiler Target Model for Line Associative Registers

Paul S. Eberhart University of Kentucky, pseber2@uky.edu Digital Object Identifier: https://doi.org/10.13023/etd.2019.141

Right click to open a feedback form in a new tab to let us know how this document benefits you.

#### **Recommended Citation**

Eberhart, Paul S., "A Compiler Target Model for Line Associative Registers" (2019). *Theses and Dissertations--Electrical and Computer Engineering*. 138. https://uknowledge.uky.edu/ece\_etds/138

This Master's Thesis is brought to you for free and open access by the Electrical and Computer Engineering at UKnowledge. It has been accepted for inclusion in Theses and Dissertations--Electrical and Computer Engineering by an authorized administrator of UKnowledge. For more information, please contact UKnowledge@lsv.uky.edu.

# STUDENT AGREEMENT:

I represent that my thesis or dissertation and abstract are my original work. Proper attribution has been given to all outside sources. I understand that I am solely responsible for obtaining any needed copyright permissions. I have obtained needed written permission statement(s) from the owner(s) of each third-party copyrighted matter to be included in my work, allowing electronic distribution (if such use is not permitted by the fair use doctrine) which will be submitted to UKnowledge as Additional File.

I hereby grant to The University of Kentucky and its agents the irrevocable, non-exclusive, and royalty-free license to archive and make accessible my work in whole or in part in all forms of media, now or hereafter known. I agree that the document mentioned above may be made available immediately for worldwide access unless an embargo applies.

I retain all other ownership rights to the copyright of my work. I also retain the right to use in future works (such as articles or books) all or part of my work. I understand that I am free to register the copyright to my work.

# **REVIEW, APPROVAL AND ACCEPTANCE**

The document mentioned above has been reviewed and accepted by the student's advisor, on behalf of the advisory committee, and by the Director of Graduate Studies (DGS), on behalf of the program; we verify that this is the final, approved version of the student's thesis including all changes required by the advisory committee. The undersigned agree to abide by the statements above.

Paul S. Eberhart, Student Dr. Henry G. Dietz, Major Professor Dr. Aaron Cramer, Director of Graduate Studies

# A COMPILER TARGET MODEL FOR LINE ASSOCIATIVE REGISTERS

THESIS

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering in the College of Engineering at the University of Kentucky

> By Paul Selegue Eberhart Lexington, Kentucky

Director: Dr. Henry G. Dietz, Professor of Electrical and Computer Engineering Lexington, Kentucky 2019

$\operatorname{Copyright}^{\textcircled{O}}$  Paul Selegue Eberhart 2019

# ABSTRACT OF THESIS

# A COMPILER TARGET MODEL FOR LINE ASSOCIATIVE REGISTERS

LARs (Line Associative Registers) are very wide tagged registers, used for both register-wide SWAR (SIMD Within a Register )operations and scalar operations on arbitrary fields. LARs include a large data field, type tags, source addresses, and a dirty bit, which allow them to not only replace both caches and registers in the conventional memory hierarchy, but improve on both their functions. This thesis details a LAR-based architecture, and describes the design of a compiler which can generate code for a LAR-based design. In particular, type conversion, alignment, and register allocation are discussed in detail.

KEYWORDS: computer, architecture, compiler, SWAR, cache, register, memory, alias

Author's signature: Paul Selegue Eberhart

Date: May 3, 2019

# A COMPILER TARGET MODEL FOR LINE ASSOCIATIVE REGISTERS

By Paul Selegue Eberhart

Director of Thesis: Henry G. Dietz

Director of Graduate Studies: \_\_\_\_\_ Aaron Cramer

Date: May 3, 2019

# ACKNOWLEDGMENTS

The many people who have been patient with my many distractions.

# TABLE OF CONTENTS

| Acknowledgments                                                                                                                                                               | iii                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Table of Contents                                                                                                                                                             | iv                         |

| List of Figures                                                                                                                                                               | vi                         |

| List of Tables                                                                                                                                                                | vii                        |

| Chapter 1    Introduction    Introduction      1.1    Introduction    Introduction                                                                                            | 1<br>1                     |

| 1.2 The Memory Hierarchy                                                                                                                                                      | 1                          |

| Chapter 2 History       2.1 CRegs         2.1 CRegs       2.2 SIMD and SWAR         2.2 SIMD and SWAR       2.3 Tagged Architectures         2.4 Compiler-Managed Data Motion | 5<br>6<br>8<br>10          |

| 3.1DLARs                                                                                                                                                                      | 12<br>12<br>14<br>14<br>27 |

| <ul> <li>4.1 Input Language</li></ul>                                                                                                                                         | 29<br>30<br>30<br>33<br>33 |

| Chapter 5 Results                                                                                                                                                             | 35                         |

|                                                                                                                                                                               | 36                         |

| Appendix A LARKem                                                                                                                                                             | 38                         |

| Appendix B lark1.aik                                                                                                                                                          | 84                         |

| Appendix C larc                                                                                                                                                               | 87                         |

| Bibliography                                                                                                                                                                  | 94                         |

| Vita | • | • | • |  | • | • | • |  | • |  | • | • | • |  | • |  |  | • | • |  | • |  | • | • | • |  |  |  |  |  |  |  | • |  |  | • | • |  |  |  |  |  | 98 | 3 |

|------|---|---|---|--|---|---|---|--|---|--|---|---|---|--|---|--|--|---|---|--|---|--|---|---|---|--|--|--|--|--|--|--|---|--|--|---|---|--|--|--|--|--|----|---|

|------|---|---|---|--|---|---|---|--|---|--|---|---|---|--|---|--|--|---|---|--|---|--|---|---|---|--|--|--|--|--|--|--|---|--|--|---|---|--|--|--|--|--|----|---|

# LIST OF FIGURES

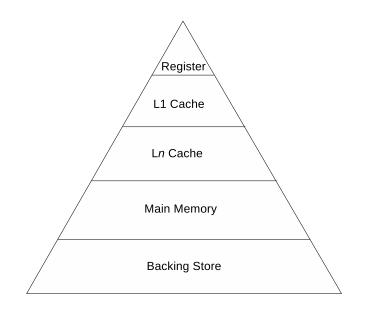

| 1.1  | The traditional computer memory hierarchy | 2  |

|------|-------------------------------------------|----|

| 3.1  | Data LAR structure                        | 12 |

| 3.2  | DLARs cache specified sections of memory  | 13 |

| 3.3  | Instruction LAR structure                 | 14 |

| 3.4  | Data LAR Structure                        | 16 |

| 3.5  | Instruction LAR Structure                 | 17 |

| 3.6  | LARK memory instruction format            | 18 |

| 3.7  | LARK utility instruction format           | 22 |

| 3.8  | Behavior of LOAD16I D3 D0 D5 0            | 24 |

| 3.9  | Behavior of subsequent LOADF32 D6 D3 D0 2 | 25 |

| 3.10 | Performing a copy with LARs               | 25 |

| 3.11 | Sample code compiled for MIPS and LARK    | 26 |

|      |                                           |    |

# LIST OF TABLES

| 3.1 | Word Size Encodings                          | 16 |

|-----|----------------------------------------------|----|

| 3.2 | Type Encodings                               | 16 |

| 3.3 | LARK Memory Instructions                     | 19 |

| 3.4 | LARK Arithmetic Instruction Behaviors        | 20 |

| 3.5 | LARK Arithmetic Instruction Encodings        | 20 |

| 3.6 | LARK Flow Control Instructions               | 22 |

| 3.7 | LARK Utility Instruction                     | 22 |

| 3.8 | DLAR1 Contents                               | 23 |

| 3.9 | Instruction Count Comparison for Sample Code | 26 |

|     |                                              |    |

# **Chapter 1 Introduction**

"Surely there must be a less primitive way of making big changes in the store than by pushing vast numbers of words back and forth through the von Neumann bottleneck. Not only is this tube a literal bottleneck for the data traffic of a problem, but, more importantly, it is an intellectual bottleneck that has kept us tied to word-at-a-time thinking instead of encouraging us to think in terms of the larger conceptual units of the task at hand. Thus programming is basically planning and detailing the enormous traffic of words through the von Neumann bottleneck, and much of that traffic concerns not significant data itself, but where to find it." -John Backus ACM Turing Award Speech, 1977

John Backus was focused on the effects of the Von Neumann design on the programmer [1] - however, the matter is fundamentally a problem of hardware design. This document proposes an architecture based on Line Associative Registers, discusses the implications of that design, and situates it in terms of other efforts to ameliorate the bottleneck.

### 1.1 Introduction

LARs (Line Associative Registers) are a memory structure designed to be used as the upper levels of the memory hierarchy in a new class of architectures. The chief objective of LARs-based designs is to provide a general-purpose model of computation in which memory accesses are minimized by explicitly managing a large pool of data and meta-data at the top of the memory hierarchy. Line Associative Registers fill the role of both registers and caches in a traditional memory hierarchy, bringing many of the advantages of each while avoiding their more egregious faults. This work chiefly deals with the development of software tools for programming a LAR-based design, but also details new advancements in the architecture, and software simulation tools for testing these tools and features.

#### 1.2 The Memory Hierarchy

In the majority of recent computer designs, memory is laid out in an increasingly deep hierarchy, with a small, fast memory near the CPU at the top in the form of registers, a series of increasingly large and slow caches, and eventually a large DRAM bank for main memory. There is also typically an option to page inactive segments of the DRAM bank to slow secondary storage.

At the top of the memory hierarchy is a small register file consisting of no more than a few kilobytes of extremely fast memory, typically SRAM. For example, a naive implementation of the x86-64 architecture common in modern PCs would feature six-

Figure 1.1: The traditional computer memory hierarchy.

teen 64 bit integer registers, and an additional sixteen 128 bit floating point registers, for a total of only 384 bytes of addressable register file.

Even the visible register files have grown considerably in size. For example, Intel's traditionally register-starved x86 architecture has sprung a series of extensions: a series of width extensions bringing the sixteen basic registers from sixteen to thirty-two, and subsequently 64 bits, eight 80-bit x87 floating point registers, and eight 64-bit vector registers added with the MMX instruction set, and extended at lest three times, once with SSE, to 128 bits, again with the transition to x86-64, to 16 registers, and again with AVX [2], to 256 bits per register.

At the very large end for designs in common use, Intel's Itanium architecture [3] features 128 64-bit registers, 128 82-bit floating point registers, and an additional 64 one-bit predicate registers, for a total of 2344 bytes of addressable register file. This propensity for extremely small register files has a number of valid rationale: high speed memory, typically SRAM on the same die as the processor functional units, is extremely expensive in terms of die area and hence cost, and the simple reality that it is much easier to sustain fast addressing on smaller memories.

The register file in almost all computers is addressed separately from main memory, which creates problems with *aliasing*; the inability to determine whether indexed accesses point to the same location, creating unnecessary traffic over the memory bus to guarantee synchronization after changes. In modern systems, the register file will often support *renaming*, which allows for a larger number of physical registers than are specified in the instruction set. This allows the system to keep more data resident at the top of the memory hierarchy, as well as opportunities to hide or eliminate false dependencies, while maintaining instruction-level compatibility. This practice comes at a cost of significant complexity and power consumption, and is opaque to the software.

Many designs considerably extend the size of their register file internally with various register renaming schemes, however, this extended space is available only for automated micro-optimization, rather than programmer or compiler managed optimizations, as it is not explicitly manageable and varies wildly between implementations of the same ISA.

Typical modern computers use a large bank of DRAM as main memory. This DRAM bank is larger, slower, lower power, and far less expensive than SRAM used for the upper levels of the hierarchy, and in many early computers. A large DRAM is necessarily slower than smaller static memories because it requires a relatively complicated decoding scheme to address and route from a large memory, as well as timing instability due to required refresh cycles. Furthermore, in a system supporting virtual memory (paging or segmentation), there will be a translation layer (page table) mapping between virtual and physical addresses which adds further delays and timing variability to accessing main memory. To improve performance without dramatically increasing costs, a system of smaller, faster caches is placed between the main memory and the processor. These caches are generally on the order of hundreds of kilobytes to a few megabytes, and may be managed by a wide variety of increasingly sophisticated automatic mechanisms, and are most often implemented in SRAM. Because the cache represents an extremely small fraction of the system memory, any automated replacement scheme is susceptible to unpredictable and/or pathological conditions, in which the access pattern and the replacement scheme interact unfavorably. Finally, caches exacerbate the nondeterministic timing of memory accesses; a datum fetched from cache will arrive orders of magnitude faster than a datum fetched from main memory, and it is impossible (or, at very least, impractical) to accurately statically predict whether a particular datum will be in cache prior to a particular read. Analogous to the use of caches to attempt to improve memory fetch performance, the address translation process is typically also cached, employing a translation lookaside buffer (TLB) to cache probable page table lines in a smaller, faster memory close to the CPU. Also like the caching of data, the TLB accelerates properly-predicted address translations (hits), but further slows down misses, and introduces a large variability in the time it will take for a memory access to complete.

The Register-Cache-Memory hierarchy is not the only memory layout which has seen widespread use. A variety of computer designs employ a small *scratchpad memory* [4]. Scratchpads are small, fast memories, generally of the same scale and technology as Caches, but are explicitly managed. This allows scratchpads to be managed with far more accurate but computationally expensive static techniques, which can, in theory, dramatically improve their utility relative to a cache of the same size. Unfortunately, because a scratchpad is explicitly managed, it requires that the scratchpads must be consistent in size and access behavior among compatible machines, or code must be recompiled to specifically target the different sizes of scratchpad.

There is a common addendum to Moore's law [5] noting that while the speed of central processing units tends to increase at an exponential rate, DRAM speeds and sizes have only grown roughly linearly. This has created a large disparity of perhaps 400 clock cycles between the speed of a system's CPU and main memory, which has been the impetus for the ever deeper memory hierarchy.

$\operatorname{Copyright}^{\textcircled{O}}$  Paul Selegue Eberhart, 2019.

#### Chapter 2 History

The LARs design has its roots in a variety of previous projects. It descends most directly from three existing areas of research: CRegs [6], a type of tagged registers, SWAR (SIMD Within A Register) designs [7] such as Intel's SSE, and compiler-managed memory hierarchies [8].

Research into LARs began with the master's thesis of Krishna Melarkode [9], in 2004, and has since developed in scope and complexity, to include a number of hardware verification models, designs for software tooolchains and simulators, and a considerable amount of theoretical work into the implications of such a design.

LARs-like features have appeared in many recent commercial designs - wider, more comprehensive SIMD extensions like Intel's AVX [2] approach a general-purpose SWAR architecture. Likewise, a weak implementation of an explicitly managed tagged file can be found in the Itanium architecture's ALAT (Advanced Load Address Table)[3]. However, in insuring that the design failed safe if improperly managed, many of it's potential benefits have been lost.

Similarly, the idea of decoupling of instruction fetch and execution to confront the Von Neumann bottleneck has been in practice since at least the mid 1960s. Most of these efforts, such as the use of scoreboarding in the CDC6600 (1964) and Tomosulo Algorithm in the IBM S360 Model 91 (1967) have been primarily focused on the efficient use of execution units, and only tackled memory access behavior insomuch as they have been required to to meet their goals. More explicit, generalized decoupling of fetch and execution has also appeared in a number of designs, perhaps most radically in the CSPI MAP 200 array processors of the early 1980s[10]. These designs, however, tend to, in one designer's own words "place a great deal of responsibility for resource scheduling and interlocking on software." [10], and practicable implementations are largely a question of re-automating these issues into automatic (typically hardware-driven) mechanisms.

A major issue in working with LARs, or other architectural changes that significantly alter long-held assumptions, is that they are not readily miscible with current practice. An incremental approach to introducing LAR-like features is impossible as effectively utilizing LARs requires fundamental changes to accepted practice. Efforts to introduce them to existing designs or apply existing tooling is doomed to be awkward and ineffective; the extent of this incompatibility was not fully appreciated at the beginning of this project. In fact, as discussed below, one attempt to employ a structure very similar to a LAR in the form of the Itanium ALAT has already failed, likely because it was compromised to improve compatibility with a conventional memory hierarchy. It is hoped that this research will yield concepts and techniques which which will be necessary to build computer systems employing LARs or similar structures.

#### 2.1 CRegs

A direct predecessor project to LARs was cache-registers, CRegs [6]. CReg is pronounced "C-Reg," and is a portmanteau of "Cache Registers." CRegs are scalar storage elements that operate in their own distinct address space, much like conventional registers. The primary CReg contribution is the load-time addition of address tags to datum near the top of the memory hierarchy. CRegs were introduced in 1989 by Henry Dietz and Chi-Hung Chi, with the primary intention of providing hardware support to resolve *ambiguous aliasing*. Ambiguous aliasing is the situation in which it is impossible to statically determine whether two names refer to the same value. Ambiguous aliases present a significant problem for systems that rely on conventional registers, as every aliased datum must be flushed from the register to a level of the memory hierarchy where the source addresses can be compared any time any aliased value is written to, creating large, correlated, and unpredictable memory traffic.

To borrow an example from the original CRegs publication, the snippet of pascallike pseudocode below is a trivial case of an ambiguous alias.

readln(i,j);

b := a[i]+a[j];

Because i and j are read from user input, it is entirely impossible to statically determine if a[i] and a[j] refer to the same memory location, and so they must either be operated on in-memory, or, if a[i] and a[j] have been loaded into registers, both be evicted from their registers and re-read whenever either is written to in order to maintain consistency. CRegs solve the problem of ambiguous aliases in all cases, by use of an address tag on each element, and associativity in the storage elements. LARs retain the address tag and associativity properties of CRegs, but extend them with vector behavior from another contemporary memory technology, described in the next section.

## 2.2 SIMD and SWAR

Another major predecessor technology for LARs is SWAR (SIMD Within A Register). SWAR is a form of low-level parallelism, in which SIMD (Single Iinstruction Multiple Data) operations are performed on collections of data packed into a single wider register. Like the vector machines they are derived from, SWAR instructions enable machines to perform operations over a set of similar data. As these extensions develop, they often lead to the introduction of wider registers into to the datapath of the enhanced processors. Most SWAR implementations are extensions to an existing scalar architecture, such as the AltiVec extensions to PowerPC, or NEON extensions to ARM. Intel's x86 platform has endured an entire series of SWAR additions to the instruction set, starting with MMX in 1997, and accreting no fewer than 17 sets of additional vector instructions since.

This after-the-fact design model comes with a variety of implications and compromises in the functionality and generality of SWAR extensions. Most implementations of SWAR extensions have extensive, and sometimes curious, limitations. For example, Intel's MMX contains instructions for adding eight 8-bit, four 16-bit or two 32-bit signed or unsigned integers packed into a single 64-bit register, and an instruction for multiplying four 16-bit integers packed into a 64-bit register, but not eight 8-bit integers in the same configuration [11]. Likewise, there are generally strict alignment constraints on SIMD extensions, both for in-memory structures which interact with the cache hierarchy to speed or slow loading the vector registers, and on the contents of the vector registers themselves [12], which tend to create additional bookeeping operations and memory traffic in order to use the vector instructions. Worse, the practice of using different register sets for scalar and vector operations exacerbates the aliasing problems discussed above, forcing loads and stores simply to maintain consistency when data is proximally handled by both the scalar and vector hardware.

Even systems designed primarily around custom very-wide SIMD engines have tended to rely heavily on conventional (and typically commodity) scalar processors to run the host operating system. These heterogeneous designs offer several advantages, especially in reducing the required complexity and keeping scheduler noise from the operating system away from the high-performance vector processors. These system architectures also force several design decisions, such as requiring special language and platform support to program and schedule the vector processors, which results in certain limitations, such as an awkward split memory space, and limiting the applicability of code developed against them to comparatively rare systems hosting the same variety of vector coprocessor.

For example, perhaps the archetypal accelerator-based machine, the Ardent Titan [13], relied on vector processors whose vector register file held 8192 64-bit values (addressable as anything from one vector of length 8192 to 32 vectors of length 256) in 1988. It, however, used a MIPS R2000 (and later R3000) processor per vector unit to run the operating system, and used the vector units only for compute offload. Being marketed as a graphics workstation, this design rather directly predicts the eventual evolution of systems with conventional host processors and attached GPUs.

Despite vector extensions being a somewhat awkward bolt-on, modern performance tuning and optimization guides suggest using the vector extensions, often almost to the exclusion of the host scalar instruction set [12]. Similarly, recent trends in high performance computing have concentrated on various derangements of vector co-processor, such as GPUs, whose pipelines are very SWAR-like.

LARs are designed with a modified SWAR model as the *primary* mode of computation, with designed-in accommodations for scalar operations. This corresponds to the ideal/desired behavior for many computing applications, where some amount of scalar operations for addressing and edge cases must be interspersed with the vectorizable primary computational work to be performed in a SIMD execution mode. Unlike SIMD coprocessor designs, LARs allows these interspersed instructions to be performed on the same, without any expensive memory transfers between host and coprocessor, realignents or corner-turns to suit the relative alignment constraints of the host and coprocessor or extension, or aliasing/timing concerns between data touched by the scalar and vector execution units. Likewise, LARs accept arbitrary base addresses, reducing the amount of effort required to massage data into position for vector operations.

## Packed SIMD/Vector Registers

Perhaps the closest current designs to LARs are efforts to add flexible vector extensions to modern ISAs. The dominant example, RISC-V's proposed Vector Extensions [14] offer a sort of generalized length-independent vector support instead of fixedwidth SWAR. These designs make a number of decisions which place them in a slightly different design space than traditional vector machines, SWAR extensions, or LARs. The RISC V proposal does employ something resembling tagged registers; a set of configuration registers specify the type and vector length of items stored in a re-configurable register file, and must be appropriately manipulated before using the vector units. Like LARs, this allows for polymorphic instructions based on the tags. A major distinction in this design is that the lengths (in operands) of vector operations are also determined by a vector length register, set with setvl, essentially providing hardware-parameterized vectors suitable for allocation via strip-mining [15]. Unfortunately, these vectors do not have any form of alias analysis or scheduling support beyond simple predicates, so they can not tolerate dependencies between data in a vector operation. Worse, because of the parameterization, inherently scalar, or at best mapped onto a multi-issue pipeline, in actual execution.

## 2.3 Tagged Architectures

A final major influence on LARs design are tagged architectures. Tagged architectures are computer architectures in which metadata, such as type information, is stored with the data, rather than inferred form the instructions used to manipulate that data [16]. Tagged architectures offer a number of theoretical advantages over conventional designs, and historically incur a number of practical drawbacks, which LARs attempt to eliminate.

To enumerate a few of tagged architectures' purported advantages, tags provide an opportunity for a smaller, simpler instruction sets, as they enable generic instructions. This allows for more compact instruction encodings and, in principle, simpler code generation and greater code reuse. Tags also enable unusual addressing modes, such as field-and-offset to allow word-oriented machines to address bytes [17]. Tagging also provides automated type checking and conversion, making most operations inherently type safe, and avoiding complicated subroutines to convert between types. Many tagging systems also enable data protection, by marking data with some form of access descriptor.

Tagged architectures have generally fallen into two categories; fixed tagging, in which each memory location is associated with a tag, and distributed tagging, in which each logical object is associated with a tag. Fixed tagging allows tags to be retrieved in a regular pattern, that is without additional address calculations, while dynamic tagging allows for fewer tags and tagging of irregularly sized objects. However, both systems still require that tags be moved in and out of main memory along with the

objects they describe, creating additional memory traffic through the Von Neumann Bottleneck, which is increasingly untenable as increases in processing speed continue to outstrip improvements in memory access.

A number of commercial designs have employed tagged architectures, most famously the Burroughs Large Systems family [18](1961), IBM System/38[17] (1979) and SWARD [19], LISP machines [20] (1981), and Intel iAPX 432 [21] (1981). While several of these machines were commercially successful, they were all eventually outcompeted [16] by simpler untagged designs. Even those machines developed expressly to execute dynamically typed languages, like the LISP machines, which have the most to gain as they must constantly perform type checking at runtime, were eventually superseded by simpler untagged designs and software support. This decline has given tagged architectures something of a bad name in modern times, particularly by association with Intel's iAPX project [21], which was an high-profile expensive failure [22], due in part to its use of a tagging system. The iAPX tags were exceptionally long - it employed 128-bit object descriptors and 32-bit access descriptors which had to be handled during almost all memory accesses [17].

The Burroughs Large Systems offer some similarities to the tags proposed for LARs. The B5000 [18] reserved a single bit of each (48 bit) machine word, to distinguish "control" and "numeric" data, though it did not use this tag system in the case of character data or code. The B6500 and later expanded to three bits of tag, which allowed for a considerably richer description; for example, the low bit is used to distinguish words which belong to the system state (low bit set) from those which belong to the user code (low bit unset). While the Burroughs Large System architecture was a stack machine, and their tag system was primarily as a security measure, comparable to a more fine-grained NX (No-Execute) bit found in the paging hardware in many modern designs, these latter members of the family also used their tags to distinguish data types. Another historical machine whose memory handling can be used as a point of reference for LARs is the Harris H500/800 family [23] and their progenitor the Datacraft 6024, marketed in the late 1970s. The Harris' distinguishing feature was its sophisticated-for-the-time cache-backed virtual memory system operating on 48-bit words. Like the IBM System/38 above, these machines were word-oriented, and used their tagging system to allow for subword addressing when operating on byte or 24-bit word oriented data. LARK is designed with a generalization of this idea, in which memory accesses are always line-at-a-time, and the low bits of addresses for smaller data objects are performed by treating the low bits of addresses as offsets into a LAR.

The major weakness of historical tagged designs is that the addition of tags in main memory creates additional memory traffic with each datum. As computer performance in the modern era is typically constrained chiefly by the memory system, this is an unacceptable compromise. Another major problem for tagged architectures is language support; most general-purpose programming languages do not offer native facilities that match up with the tags on a particular architecture, which results in stilted use of tags and/or additional load on the toolchain to determine the mapping. Relatively successful tagged architectures have tended to be co-developed with a programming language; n the case of the LISP Machines, the machine was designed specifically to support the needs of the existing LISP language family. Similarly, the System/38 uses a layered ISA, where the user-facing software toolchain produces a high-level intermediate language, which is then translated by what we would now refer to as a firmware layer [17] - in many ways presaging the now-common design of dynamically translating a high-level ISA into microps in microcode.

The tagging employed in LARK, and intended for use in any LARs based architecture, is different than any of the prior designs - instead of tagging in memory, LARK's LOAD and STORE instructions set and manipulate tags on data in the DLAR file, giving the benefits of a tagged architecture, without incurring the penalty in memory traffic suffered by designs which maintain tags in RAM. To do this, data is tagged when loaded into a LAR from main memory, and the tags remain attached to the data in the LAR file even if moved or duplicated, but are never written back to main memory.

#### 2.4 Compiler-Managed Data Motion

There are a number of approaches present in commercial designs to allow the software toolchain to guide or control the movement of data up and/or down the memory hierarchy, rather than relying directly on automated, heuristic cache management.

The general solution to compiler-managed control of fast memories is to simply expose the fast memories to the architecture as a memory segment - typically the small fast memories in this arragement are called "scratchpads." The most recent successful architecture to use a scratchpad was the SPU in the IBM Cell processor [24], though it is certainly not unique in this arrangement. This explicitly-managed separate memory offers a number of challenges. The scratchpad memory itself must be managed with additional instructions. The size of the scratchpad is exposed in the ISA, which restricts portability; a larger scratchpad cannot be utilized without altering the code, as is possible with caches. One feature which is neither a clear advantage or disadvantage is that while in a cache hierarchy, data in the cache is a copy of data in main memory; while in a scratchpad, the data in the scratchpad is not backed by main memory unless expressly transferred.

The most common solution to offer limited software control of the memory hierarchy are the cache control instructions are present in the majority of modern architectures. A typical example is the x86 family PREFETCHh and CLFLUSH [25] instructions, which hint a promotion of the line containing a data byte up the cache hierarchy, and invalidate a line evicting it from the entire cache hierarchy respectively. These instructions do not offer complete programmatic control of caches; the cache control logic can 'choose' to ignore a promotion hint, and cache occupants must still obey the associativity rules of the cache, so promotions may inadvertently evict needed data.

Prefetching is also something of a leak in abstraction layers, exposing implementationspecific details and behaviors which "do[es] not affect program behavior" [25] at the level of the ISA. This variation among implementations also makes the effective use of prefetch instructions non-portable in much the same way as explicitly managed memory structures, like scratchpads, leading to the same concerns about requiring recompilation for specific targets. There is some variety in the cache control instructions offered among ISAs, PowerPC in particular has a relatively powerful set of cache control primitives exposed through a mixture of instructions and status registers. The PowerPC cache controls allow a range of interesting features, and in fact the cache hierarchy is typically in a disabled state until initialized by software [26]. Configuration includes completely disabling particular instruction or data caches to avoid coherency contention, manipulating manipulating the prediction policies among a set of platform-defined alternatives, whole-cache or specific-way locking, and separate flushing and invalidation, the use of which incurs state-tracking within the program, as there is hardware-enforced protection to prevent the flushing of data which has been modified but not written back, a complication not incurred by LARs.

Like most designs, typical PowerPC cache hierarchies have specific instruction and data caches for L1, but shared caches for higher levels. Unlike most designs, PowerPC cache control allows for control of how the shared caches are used, such as marking the entire L2 cache as an instruction cache, and forcing all data traffic onto the bus.

Speaking in generalities about ARM caches is not productive because there is an extensive diversity of cache hierarchies employed in ARM compatible designs [27].

Prefetching can also be performed automatically. A downside of automatic prefetching in most modern architectures is the risk of poisoning caches with speculative loads; because most cache mechanisms are automated and associative, an incorrect speculative load may not only generate spurious memory traffic, but evict a piece of data which was actually needed from cache. This may cascade into more than a single fetch of stall, for example if the evicted data was both dirty and immediately needed, the process will have to wait as the line is written back, then read again. Worse, if the data in the page table was used for indirection, whole chains of otherwise unnecessary memory accesses may be triggered as accesses cascade. LARs avoid this entirely by exclusively explicitly managing the memory hierarchy, such that "accidental" algorithmic eviction is not a threat.

The structure most similar to LARs in a modern commercial designs is the Advanced Load Address Table (ALAT) present in the Intel Itanium architecture [28]. The ALAT is a 32-entry associative memory which is used to perform speculative data loads. An 1d.a instruction can be generated by the compiler, which will produce an entry in the ALAT listing the source address, size, destination register, and state of the load. In the Itanium architecture, the ALAT is used as a supplement to a conventional automated cache memory hierarchy, which allows a limited degree of compiler-guided pre-fetch without risking poisoning associative caches with speculative loads. Results obtained by modifying a compiler to perform as much speculative loading as possible indicate that compiler-managed (pre)fetch, even driven by naive but extremely aggressive speculative loading, will perform well under most circumstances, and cause only very rare, minor performance regressions [28].

LARK, like any realizable LAR-based architecture, relies *entirely* on statically scheduled prefetching for all instruction loads - and all data loads.

Copyright<sup>©</sup> Paul Selegue Eberhart, 2019.

#### Chapter 3 LARK

This chapter attempts to explain both the general properties of LAR-based designs, and specifically discusses the LARK architecture, a straw-man design used across the current generation of LARs research. The first two major sections are dedicated to explaining the LAR structures themselves - DLARS (Data Line Associative Registers), and their simpler peer, ILARS (Instruction Line Associative Registers)

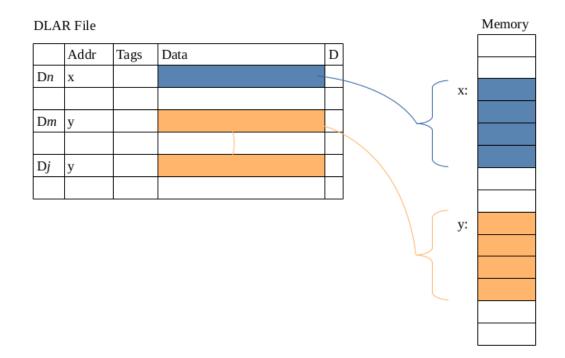

#### 3.1 DLARs

The defining element of a LARs-based design is the DLAR. A file of DLARs fills the roles of both the register file and data cache in a fully LAR-based architecture. Each DLAR consists of a wide data field, on the order of kilobits, and a set of meta-data fields, which include a source address, dirty bit and type information to indicate the interpretation of the data field. Type tagging at the register level is a best case compromise. It allows for an extremely regular instruction set via context sensitivity, and eliminates the need for explicit type conversion instructions. It also avoids the common problems of type tagged architectures, such as those famously experienced by Intel's iAPX432 [21] which employed a fully tagged object oriented memory system, and in turn created a massive penalty in terms of memory traffic, exactly the thing LARs are intended to minimize. A generic diagram of a file of DLARs is shown below.

| LAR NR | Data         | Addı     | ress   | WDSZ  | TVD | р     |

|--------|--------------|----------|--------|-------|-----|-------|

| LAGING | Data         | TAG      | OFFSET | W DSZ |     | D     |

|        | $2^m$ blocks | n-m bits | m bits |       |     | 1 bit |

| D0     |              |          |        |       |     |       |

| D1     |              |          |        |       |     |       |

| D2     |              |          |        |       |     |       |

|        |              |          |        |       |     |       |

| Dxx    |              |          |        |       |     |       |

Figure 3.1: Data LAR structure

A LAR file of useful size requires a considerable quantity of fast memory to implement. However, LARs can replace both caches and registers in the memory hierarchy, and with features such as register renaming and the continuing growth of caches, require no more high-speed memory than a conventional modern design.

The tagging in LARs is, again, dissimilar to most predecessors in that it performs tagging at load time, and tags only the register file, not the main memory, thus avoiding the space inefficiency and, more importantly, additional memory bus bandwidth of a tagged-in-memory system. The address tags on DLARs importantly allow for associativity; two DLARS pointed at the same base address will present a consistent view of their contained data.

Figure 3.2: DLARs cache specified sections of memory

In use, DLARs are best thought of as annotated windows into main memory. A DLAR, once loaded, caches a line-size segment of main memory, to which it guarantees extremely fast access (reads and writes) through a convenient handle (the DLAR number). It also provides type annotations to simplify specifying operations inside the window. The associativity property of DLARs guarantee that any change made to the DLAR-masked area of memory will be consistent; all accesses to that range will necessarily go through the DLAR file, so there is no risk of aliasing. The version of the data in main memory is *eventually* written back via the lazy write-back mechanism, but particular changes which are subsequently overwritten while still resident in the DLAR file may never reach main memory. An illustration of this behavior is illustrated in figure 3.2, showing one DLAR caching the memory block at base address x, and two caching the same block at location y.

It would be possible but likely unwise to combine a LAR file with caches; it is in principle possible for a designer to back a LAR file with a cache. However, caches are most likely not a good use of circuitry in a design with a LAR file the relatively low effective utilization and added data life-cycle complexity do not make caches a practical use of chip area in a design already equipped with LARs. Furthermore, adding a cache to a LAR-based system would likely ruin the ability to make reasonable static scheduling decisions - statically scheduling instructions around memory timing is already difficult, effectively statically scheduling instructions in the face of order-of-magnitude nondeterminism in memory access timing is impossible, a problem experienced by existing VLIW designs.

# 3.2 ILARs

The other possible major use for a LAR-like structure is in the instruction path. The requirements for a LAR in the instruction path are slightly different than those in a data path, and thus practical implementations of LAR based architectures will require differently-structured LARs for use in the instruction path. The basic LAR structure described earlier is appropriate for a Data LAR (DLAR), while ILARs (Instruction LARs) hold only blocks of instruction-sized units, are indexed by the program counter, and are not directly mutatable, removing the need for most of the metadata fields.

| LAR NR | Data     | Address  |

|--------|----------|----------|

|        | linesize | addrsize |

| IO     |          |          |

| I1     |          |          |

| I2     |          |          |

|        |          |          |

| D255   |          |          |

Figure 3.3: Instruction LAR structure

An useful side-effect of the line oriented nature of a LAR-based memory hierarchy is that in-memory instructions could easily be stored in a compressed form. ILARsized could reasonably be compressed in-memory, and decompressed at load time, saving both storage space and memory bandwidth. This adds a minor complication in that it violates the assumption of an injective mapping between the contents of the LAR file and the contents of memory, and a major complication in that constant-time decompression, ideally with a constant ratio, would be required for this to be practicable. Exploring and designing the compression scheme and load mechanism is roughly an MS worth of work in itself - a thesis exploring exactly that already exists in the work of Nien Lim [29]. Others have explored this sort of block-oriented instruction compression in the context of VLIW architectures [30] with moderate promise. Compressing ILARs also creates restrictions on self-modifying or otherwise dynamically generated code, though not a significantly higher barrier than Harvard architectures' separate instruction and data memories, or even the separate instruction and data caches found in most modern designs.

# 3.3 Architecture Specification

A major porition of this work is the development of a straw-man design, called LARK (Line Associative Register architecture from Kentucky, also a pun on "on a lark") which is a large and complete enough architecture to provide a practical common

target for research and development, but be no more complicated than is necessary for that function.

The LARK architecture is specified to allow software tools, such as simulators, compilers, and system support code, to be written for a LARs-based design. LARK is intended to be small and simple to use, and is specifically designed to privilege easy leveraging of LAR advantages over supporting either common practices or hardware implementation concerns. LARK features 64-bit direct memory addressing, a dozen native data type primitives, and only 18 instructions in three basic formats. The instruction set is somewhat richer than it first seems, as may of the basic instructions can be modified with type flags and even more unusually, a vector/scalar switch bit.

LARK does not support a number of features expected in a modern architecture, such as privileged execution, virtual memory, or specific input/output management. While most of these features could be straightforwardly amended into the design, input/output will require additional special consideration, as the native lazy write-back semantics would need to be selectively defeated, though that is not particularly complicated by the standards of modern [IO]MMU behavior. Nor does LARK include some of the possible advanced features of a LAR-based design, eschewing enhancements like instruction compression in favor of a simpler, more general design.

#### Memories

The most distinctive feature of LARK is its storage elements; a pair of LAR files which supplant both registers and caches as the sole architectural memory element. LARK contains two 255 entry LAR files, on for instruction and one for data, which with their metadata contain 1082624 bits (roughly 132 kilobytes) of memory, which is at once quite large as compared to named architectural register files, and extremely modest when compared to renamed register files or caches. Hierarchically below the LAR files, there is a conventional 64-bit address space, without virtual memory, as exposed by a commodity memory controller and RAM modules.

#### **DLAR File**

The primary distinguishing structure of LARK is its data LAR (DLAR). DLARs contain a 2048-bit data field, a 64-bit address field, two bits each to specify the size and type of each datum in the data field, and a dirty bit. LARK has 256 such DLARs numbered D0-D255, comprising 256 \* (2048 + 64 + 2 + 2 + 1) = 541952 bits, roughly 66 kilobytes of memory for the DLAR file.

The type and word-size fields hold the values in table 3.1, which are always encoded in the same way where they appear elsewhere in the ISA, such as in instruction encodings.

The nonstandard IEE754-style 8 bit quarter-precision float is encoded as a (1 + 4 + 3) - one bit for the sign, four bits for the exponent, and three bits for the mantissa. It is otherwise extended to match IEE754-style encoding; a bias of  $(2^4)/2) = 7$ is applied to the exponent, an all-0 exponent is understood to denote a zero value,

| LAR NR | Data      | Add      |        | WDSZ   | TVP    | D     |

|--------|-----------|----------|--------|--------|--------|-------|

| LAN NI | Data      | TAG      | OFFSET |        |        | D     |

|        | 2048 bits | n-m bits | m bits | 2 bits | 2 bits | 1 bit |

| D0     |           |          |        |        |        |       |

| D1     |           |          |        |        |        |       |

| D2     |           |          |        |        |        |       |

|        |           |          |        |        |        |       |

| D255   |           |          |        |        |        |       |

Figure 3.4: Data LAR Structure

Table 3.1: Word Size Encodings

| Value | Object Size |

|-------|-------------|

| 00    | 8           |

| 01    | 16          |

| 10    | 32          |

| 11    | 64          |

Table 3.2: Type Encodings

| Value | Туре                            |

|-------|---------------------------------|

| 00    | Reserved                        |

| 01    | Unsigned Integer                |

| 10    | Signed Integer (2's compliment) |

| 11    | Float (IEEE754-ish)             |

and an all-1 exponent is  $\infty$  with a zero mantissa or NaN with a non-zero mantissa. This atypical format is included partly for the sake of orthogonality, and are likely of limited utility, but also act as acknowledgement of the variety of algorithms appearing in fields like machine learning, in which very fast, high-range, low-precision calculations are desirable.

The Address field is a single value, but is dynamically reinterpreted into a base and offset based on the value of wdsz; when wdsz is set to 8 (00) the low 8 bits are treated as a word offset to index each of the 256 words in the line, likewise, when wdsz is set to 64 (11), only the low 5 bits are understood as offset to index each of the 32 words in the line.

# ILAR File

The second architectural memory of LARK is its Instruction LAR (ILAR) file. The ILAR file is also composed of 256 2048-bit data fields supplemented with metadata, making up 540672 bits (again, roughly 66 kilobytes) of memory. However, ILARs are structurally simpler and include only the data and address fields; the contents of an ILAR is always assumed to be 32, 64-bit instructions, so the type and word-size fields are unnecessary. Likewise, ILARs are not directly writable, so the dirty bit can be omitted; the non-writability of the active instruction memory (the ILAR file) is one of several non-Von Neumann properties in a strictly LAR based architecture.

| LAR NR | Data      | Address |

|--------|-----------|---------|

|        | 2048 bits | 64 bits |

| IO     |           |         |

| I1     |           |         |

| I2     |           |         |

|        |           |         |

| D255   |           |         |

Figure 3.5: Instruction LAR Structure

# Instruction Set

The LARK instruction set consists of 54 instructions broken into four groups: Memory, Arithmetic, Flow Control, and Utility. Opcodes are eight bits, and encodings are chosen for simplicity, readability, and orthogonality rather than compactness. This is in keeping with LARK's design as a proof of concept architecture - simple implementation and easy manipulation by humans are valued over compactness or performance.

# Memory

The LARK instruction set contains only two kinds of operation loads and, somewhat misleadingly, stores. These basic instructions are modified by a byte of type data used to set the type and wdsz fields of the destination LAR. The load instructions, intuitively, load a 2048-bit block of data from memory into a DLAR, and set the address, type, wdsz fields of the target LAR. DLARS are always loaded aligned to a DLAR-width, but the low bits of the address can point anywhere inside the line as an offset. The store instructions, less intuitively, do not trigger a writeback to main memory, but *change the tags* on a target DLAR. The only writeback mechanism in LARK is lazy; the DLAR file is continuously scanned, and the next DLAR with the dirty bit set is written back during idle memory bus cycles, giving a simple roundrobin opportunistic write-back scheme. There is some possibility that certain code sequences with rapid load-and-write to widely spaced addresses could eventually force a stall when DLARs targeted for loads are marked dirty, but this scheme is sufficient

for evaluation. Different LARs experiments have handled attempting to overwrite a dirty DLAR differently. The simplest scheme, as specified for LARK, is to stall, leaving guaranteed free memory bus cycles until the round-robin writeback system clears it. This has the potential advantage of reducing pressure on the memory bus when it has become congested, but the disadvantage of potentially long stalls of unknown length as the round robin write back comes around to the desired DLAR. Another option is to "cut" the dirty DLAR being written to the front of the write back order, bounding the stall to the time for a single extra memory write, but risking more frequent stalls. More sophisticated options, such as buffers or queues for reads and/or writes offer advantages for scheduling, and this was the method employed in the LOON LARs demonstrator [31]. To determine the most advantageous scheme for attempting to load to a dirty DLAR would require analyzing , which is not yet possible.

Memory instructions are prefixed with 0b01, followed by a 0b00 for loads and a 0b01 for stores. The next two bits encode the type of the tag to be set on the target DLAR, with the same patterns used in the TYPE field of a DLAR as documented in 3.2. The final two bits encode the wordsize for the contents of the target DLAR, analogously using the same encodings as the wdsz field of a DLAR as documented in 3.1. This scheme not only uses the same encodings for instruction fields as for corresponding DLAR fields, but creates a conveniently compact and human readable sequential numbering within the groups of instructions.

| OP | DST | SRC1 | SRC2 | IMM |

|----|-----|------|------|-----|

| 8  | 8   | 8    | 8    | 32  |

Figure 3.6: LARK memory instruction format

**OP** - Opcode Field - 8 Bits.

DST - Destination LAR - 8 Bits.

SRC1 - First Operand Source LAR (Address field of this LAR used as base address for load) - 8 Bits.

SRC2 - Second operand source LAR (Data field of this LAR used for effective address calculation) - 8 Bits.

IMM - Immediate value, added for effective address calculation (Signed) - 32 Bits.

The addressing mode is as follows: Base Addr = SRC1.Address + SRC2.Data + (IMM\*WDSZ)

This results in the encodings shown in table 3.3.

#### Arithmetic

The LARK instruction set contains only 13 arithmetic instructions, with two variants each, which cover conventional arithmetic operations, as well as comparisons and logical and bitwise operations. Such a small number of instructions are adequate because

| Mnemonic | Encoding (Bin) | Encoding (Hex) |

|----------|----------------|----------------|

| LOAD8U   | 0b01000100     | 0x44           |

| LOAD16U  | 0b01000101     | 0x45           |

| LOAD32U  | 0b01000110     | 0x46           |

| LOAD64U  | 0b01000111     | 0x47           |

| LOAD8I   | 0b01001000     | 0x48           |

| LOAD16I  | 0b01001001     | 0x49           |

| LOAD32I  | 0b01001010     | 0x4A           |

| LOAD64I  | 0b01001011     | 0x4B           |

| LOAD8F   | 0b01001100     | 0x4C           |

| LOAD16F  | 0b01001101     | 0x4D           |

| LOAD32F  | 0b01001110     | 0x4E           |

| LOAD64F  | 0b01001111     | 0x4F           |

| STORE8U  | 0b01010100     | 0x54           |

| STORE16U | 0b01010101     | 0x55           |

| STORE32U | 0b01010110     | 0x56           |

| STORE64U | 0b01010111     | 0x57           |

| STORE81  | 0b01011000     | 0x58           |

| STORE16I | 0b01011001     | 0x59           |

| STORE32I | 0b01011010     | 0x5A           |

| STORE64I | 0b01011011     | 0x5B           |

| STORE8F  | 0b01011100     | 0x5C           |

| STORE16F | 0b01011101     | 0x5D           |

| STORE32F | 0b01011110     | 0x5E           |

| STORE64F | 0b01011111     | 0x5F           |

Table 3.3: LARK Memory Instructions

type distinction is achieved from the type and wdsz fields of the destination DLAR rather than the issued instruction. The only variants for arithmetic instructions is whether the instruction is scalar, operating on a single field of a DLAR, or vector, operating on an entire DLAR in parallel. All arithmetic instructions are encoded with prefix 0b10 in the high two bits, and the scalar/vector distinction is denoted by the third highest bit of the opcode, which is set to 0 for scalar operations, and 1 for vectors. This encoding is reasonably compact and leads to a human-readable prefix property. The mnemonics are written with a S or V postfix to denote if the operation is scalar or vector.

The format for arithmetic instructions is as follows. OP DST[DESTOFF], SRC1[OFF1], SRC2[OFF2], IMM Where offsets and the immediate are optional, and assumed zero if not defined.

OP - Opcode Field, 8 bits DST - Destination LAR, 8 bits SRC1 - First Operand Source LAR, 8 bits

SRC2 - Second operand source LAR, 8 bits

OFF1 - Field offset in the first source LAR (for scalar ops), 8 bits

OFF2 - Field offset in the second source LAR (for scalar ops), 8 bits

DESTOFF - field offset in the destination LAR (for scalar ops), 8 bits

IMM - Immediate value, 8 bits

Table 3.4: LARK Arithmetic Instruction Behaviors

| Instruction | Function                                |

|-------------|-----------------------------------------|

| ADD         | DST=S1+S2                               |

| SUB         | DST=S1-S2                               |

| MUL         | DST=S1*S2                               |

| DIV         | DST=S1/S2                               |

| MOD         | DST=S1%S2                               |

| AND         | DST=S1&S2                               |

| OR          | DST=S1 S2                               |

| XOR         | DST=S1^S2                               |

| NEG         | DST=~S1                                 |

| SLL         | DST=S1< <imm< td=""></imm<>             |

| SRA         | DST=S1>>IMM (always sign extend result) |

| SRL         | DST=S1>>IMM                             |

| SLT         | DST=S1>S2                               |

Table 3.5: LARK Arithmetic Instruction Encodings

| Mnemonic  | Encoding (Bin) | Encoding (Hex) |

|-----------|----------------|----------------|

| ADDS/ADDV | 0b10x00000     | 0x80/0xA0      |

| SUBS/SUBV | 0b10x00001     | 0x81/0xA1      |

| MULS/MULV | 0b10x00010     | 0x82/0xA2      |

| DIVS/DIVV | 0b10x00011     | 0x83/0xA3      |

| MODS/MODV | 0b10x00100     | 0x84/0xA4      |

| ANDS/ANDV | 0b10x00101     | 0x85/0xA5      |

| ORS/ORV   | 0b10x00110     | 0x86/0xA6      |

| XORS/XORV | 0b10x00111     | 0x87/0xA7      |

| NOTS/NOTV | 0b10x01000     | 0x88/0xA8      |

| SLLS/SLLV | 0b10x01001     | 0x89/0xA9      |

| SRAS/SRAV | 0b10x01010     | 0x8A/0xAA      |

| SRLS/SRLV | 0b10x01011     | 0x8B/0xAB      |

| SLTS/SLTV | 0b10x01100     | Ox8C/OxAC      |

To convert the bits of a line, rather than just change the tags, a two-operation sequence must be performed. First, a dummy load must be performed to prime a LAR with the desired type information. For an in-place conversion, load the SAME address as the source line with the desired type. Then, perform an identity operation on the line, to trigger the ALU's internal type conversion hardware.

When up-converting (ie. 8-bit to 16-bit types), values are read from the position specified by the corresponding OFF until the target LAR size is filled. When down-converting, or converting from an offset too far into the line to supply enough values to fill the target, results are placed starting from DESTOFF, until the number of output bits are exhausted, and the remaining fields are padded with 0.

For vector operations, the SRC1OFF and SRC2OFF offsets are ignored for DLARs with the largest wdsz fields set in the operation, as they operate on an entire line of values at once. For source DLARs with wdsz set to d

DSTOFF determines were in the destination line the results are placed. This means the DSTOFF MUST be low enough in the line to fit the destination, and aligned to the number of values coming from the source (IE. If SRC is 32i, DST is 8u, DSTOFF must fall on a 64-place boundary. Use the OFF field in a vector op to specify which portion of a line is converted when up-converting types.

#### Flow Control

LARK uses only three instructions for flow control. These instructions have prefix 0x11 in the high bits. SEL, read "Select" is the lone branching instruction in LARK. As emitted by the compiler, the instruction encodes a LAR and offset to test for condition, and two labels. Control flow jumps to the first label if the condition is nonzero, and the second if it is zero.

OP - Opcode Field, 8 bits

COND - Condition LAR, 8 bits

CONDOFF - Offset into condition LAR, 8 bits

TGT1 - Target ILAR for nonzero condition, 8 bits

OFF1 - Field offset in the nonzero target ILAR, 8 bits

TGT2 - Target ILAR for zero condition, 8 bits

OFF2 - Field offset in the zero target ILAR, 8 bits

PAD - Pad bits, 8 bits

In the assembler, the labels are converted to the block and offset instruction format supported by the architecture. In conjunction with SLT and XOR, any common flow pattern can be implemented with SEL.

CALL and RETURN manipulate the hardware call stack described in 3.3.

#### Utility

In LARK there is only one utility instruction - FETCH. FETCH and is conveniently encoded as 0x00, which simplifies bootstrapping the system. FETCH copies a block of

| Mnemonic | Encoding (Bin) | Encoding (Hex) |

|----------|----------------|----------------|

| SEL      | 0b11000000     | 0xC0           |

| CALL     | 0b11000001     | 0xC1           |

| RETURN   | 0b11000010     | 0xC2           |

Table 3.6: LARK Flow Control Instructions

instructions from memory and load into the target ILAR. At this time LARK does not include any form of instruction compression. As the benefit of this compression is less assured than other features of a LAR-based architecture, is explored elsewhere, and it's inclusion imposes significant design complexity, the current design makes no attempt to impose a compression scheme. However, because it is written with modular instructions, it would be relatively simple to replace the **fetch** instruction with one or several compressed-mode alternatives.

| OP | DST | SRC1 | SRC2 | NUM | IMM |

|----|-----|------|------|-----|-----|

| 8  | 8   | 8    | 8    | 16  | 16  |

Figure 3.7: LARK utility instruction format

OP - Opcode, 8 bits DEST - Destination ILAR, 8 bits SRC1 - ILAR who's address field acts as a base address, 8 bits SRC2 - DLAR to use for the offset, 8 bits NUM - Number of contiguous ILARs to be loaded, 16 bits IMMEDIATE - Immediate value for address calculation, 16 bits Addressing is again performed by the rather odd: Address=SRC1.Address+Src2.Data+Immediate

This operation is, however, not generated by the compiler. Instead, it is inserted as part of the packing and alignment process in during assembly.

Table 3.7:

LARK Utility Instruction

| Mnemonic | Encoding (Bin) | Encoding (Hex) |

|----------|----------------|----------------|

| FETCH    | 0Ъ0000000      | 0x00           |

#### Calling Convention, Persistent Pointers

In order to execute useful code, a set of calling conventions must be established. These conventions are to meet similar requirements to any architecture; provide access to constants, ensure orderly transitions between functions, and generally provide guidelines for the use of shared resources. First, and similar to several established architectures like MIPS, DLAR0 is a constant 0. All of the native number encodings understand a field full of logic 0 as 0 in their number system, and the ALU features type conversion hardware, so the 0 register is inherently polymorphic.

DLAR1 is kept tagged as a 64bit unsigned integer, to hold vector of important, frequently accessed values. These include the following pointers:

CP - Points to the beginning of the current constant pool.

SP - Points to the top of a stack of return blocks (one LAR, supports offsets)

**FP** - Frame pointer, Points to a DLAR (Possibly more than one) containing the current context.

| 0  | 1  | 2  | 3 | 4 | 5 | 6 | 7 |

|----|----|----|---|---|---|---|---|

| CP | SP | FP |   |   |   |   |   |

Table 3.8: DLAR1 Contents

This document does not establish exactly how the stack will work; because of the same problem as packing data of differing types in general, no overwhelmingly satisfactory solution has been discovered, straightforward possibilities either burn an excessive number of DLAR names to map a contiguous memory used for a set of variously-typed data, or require complicated indirected addressing schemes to separate data in differing types.

Bootstrapping a machine with ILARs is not significantly more difficult than a conventional architecture. In particular for LARK, because the FETCH opcode is 00, placing a single ILAR-sized chunk of instructions at the bottom of the memory space and executing an all-0 instruction at startup will load the block from the bottom of memory into ILAR 0, which gives 8 initial instructions to FETCH some bring-up code and SEL to it.

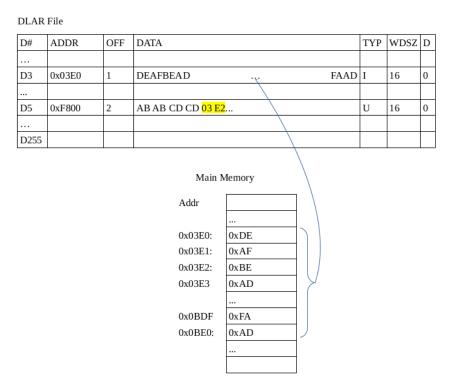

### Examples

Beginning with a single-instruction example, figure 3.8 shows the behavior of a typical load operation. Specifically, figure 3.8 shows the critical parts of the DLAR file during the execution of the instruction LOAD161 D3 D0 D5 0. This instruction specifies that DLAR D3 be type-tagged for 16-bit signed integers, and loads the 2048-bit-aligned block containing the memory specified by the other operands. Note the addressing mode allows for a datum in an already-loaded LAR to be used as an absolute pointer by setting SRC1 to D0, specifying the DLAR whose offset is currently pointed at the desired address as SRC2, and leaving the immediate value as 0. Because it is an aligned load, though the base address is two bytes into the range, the base address is written to the address field, the data is copied on aligned boundaries, and the low bits are interpreted as an offset in terms of WDSZ-sized items, stored in the offset field;

in this case, 1. This example shows a byte-addressed memory with 16-bit addresses for brevity, though LARK is specified with a 64-bit address space.

Figure 3.8: Behavior of LOAD16I D3 D0 D5 0

Figure 3.9 illustrates a load of an already-cached segment of memory. This instruction would cause no additional memory bus traffic. Instead, it will tag the target DLAR with the type and wordsize specified in the instruction and same address as an already-in-use DLAR, and alter the DLAR file map to point the target DLAR's data section (D6) to the *same* piece of memory already mapped for that base address (in this case, D3) – thus providing two differently-annotated handles on the same line of data. Also note that here the addressing scheme is used to take the base address of another DLAR plus an immediate offset by specifying a DLAR holding the desired base address as the first source operand, D0 as the second source operand, and an immediate value.

To demonstrate one of the most confusing aspects of LARK, figure 3.10 shows the a copy being performed with a sequence of instructions ending in a store. This is performed in several steps to first set up the addresses, then associatively copy the desired values into a DLAR to re-tag with an aliased load as in the previous example, and finally to issue a store to change the address tag of the copy. The first operation is once again treating D5 as a line containing pointers, set its offset appropriately to the desired target address before this store with a LOAD D5 D5 D0 3 instruction. The copy is much like the previous example, in this case a LOADF32 D9 D3 D0 0 to prime D9 as the location for the copy. Finally, issuing a STORE16U D9 D0

| D#   | ADDR   | OFF | DATA     |          | TYP | WDSZ | D |

|------|--------|-----|----------|----------|-----|------|---|

|      |        |     |          |          |     |      |   |

| D3   | 0x03E0 | 1   | DEAFBEAD | <br>FAAD | Ι   | 16   | 0 |

|      |        |     |          |          |     |      |   |

| D6   | 0x03E0 | 2   |          |          | F   | 32   | 0 |

|      |        |     |          |          |     |      |   |

| D255 |        |     |          |          |     |      |   |

Figure 3.9: Behavior of subsequent LOADF32 D6 D3 D0 2

D5 0 will set DLAR D9's address to the address indicated by the arguments, the type tags to the values indicated in the instruction, and *copy* the data in source DLAR (D3) to the storage of the destination DLAR (D9), breaking the associativity. This operation will set the dirty bit on the destination line D9 to mark it for write-back to main memory in the same way as any other operation requiring main memory be eventually updated due to a change in the stored data.

| D#   | ADDR   | OFF | DATA                                 | TYP | WDSZ | D |

|------|--------|-----|--------------------------------------|-----|------|---|

|      |        |     |                                      |     |      |   |

| D3   | 0x03E0 | 1   | DEAFBEAD FAAD                        | Ι   | 16   | 0 |

|      |        |     |                                      |     |      |   |

| D5   | 0xF800 | 3   | AB AB CD CD 03 E2 <mark>04 E6</mark> |     |      |   |

|      |        |     |                                      |     |      |   |

| D9   | 0x04E0 | 3   | DEAFBEAD FAAD                        | U   | 16   | 1 |

|      |        |     |                                      |     |      |   |

| D255 |        |     |                                      |     |      |   |

Figure 3.10: Performing a copy with LARs

For a larger demonstration, the below describes a a trivial example program as pseudo-C, with the body compiled to both LARK and MIPS-like assembly. Remember, like a conventional register, LARs are able to hold values being operated on. Like a cache line, LARs can contain a number of spatially proximal scalar values. As in SWAR, a LAR is able to hold a vector of values to be operated on in parallel. Like their progenitor CRegs [6] LARs are able to transparently resolve ambiguous aliases in hardware.

Which yields the following counts:

The reason there are ranges on the LARs memory access counts is because if the used locations are aliased to any "live" value, the memory access is replaced with a

| <pre>nasty(int* i, i {     i=j+k;     k=j&amp;k }</pre>                                                                                                   | int* j, int* k)  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| LARs                                                                                                                                                      | MIPS             |

| LOADSW D1 D31 0 j<br>LOADSW D2 0 D1 0<br>LOADSW D3 D31 0 k<br>LOADSW D4 0 D3 0<br>LOADSW D5 D31 0 i<br>LOADSW D6 0 D5 0<br>ADDS D6 D2 D4<br>ANDS D4 D2 D4 | LW \$t6, 0(\$t4) |

Figure 3.11: Sample code compiled for MIPS and LARK

Table 3.9: Instruction Count Comparison for Sample Code

|                         | LARs | MIPS |

|-------------------------|------|------|

| Memory Accesses         | 0-5  | 9    |

| Reads                   | 0-3  | 7    |

| Writes                  | 0-2  | 2    |

| Total Instruction Count | 9    | 11   |

simple associative update. Even if we allow that the MIPS version may have passed it's parameters in registers, it would only reduce the number of instructions to parity at eight, and there would still be eight assured memory accesses for the MIPS version. While it is true that some or all of these memory accesses may be satisfied from cache, this would still require traffic across the memory interface. An associative update in the LARs version is entirely internal to the processor, and does not incur any bus traffic. It is also worth noting that the LARs version could operate on entire vectors, each the length of the data field, by only changing the ADD and AND operations to their vector forms. There would be no additional memory references nor additional cycles in processing the operations.

In an ideal case, a LAR based architecture as currently conceived would be able to execute nearly 128 operations per cycle, presuming a predictably ordered instruction stream, and 8-bit data which comes in at least LAR-width vectors. A task with such a high degree of regularity and parallelism is extremely unlikely outside of certain highly specialized multimedia applications. A more realistic estimate will still provide excellent execution density, for several reasons. Firstly, because of the inherently parallel nature of LAR loads, and complete absence of explicit stores, there will be a large savings on memory access instructions. Likewise, where ILP is available it can be easily and transparently exploited with exactly the same mechanisms used for scalar operations, with no mode changes as are inherent to many SWAR designs [7]. Finally, the LAR's use of dirty tags and alias analysis precipitously reduce the number of loads from main memory, preventing stalls while waiting for main memory.

#### 3.4 The Simulator

In order to explore a full-datatype LAR-based system, a simple simulator matching the LARK spec has been implemented.

The simulator, LARKem (LARK-Emulator), is written in in standard C, with a sprawling collection of macros to hide the relatively complicated struct used to represent each DLAR, and associated selection logic to perform typed operations. Like LARK itself, LARKem is designed to be as simple as possible to manipulate, rather than performance or accuracy, and it has many internal decisions that reflect this bias. The source code for LARKem is attached as appendices beginning with A.1.