## University of Kentucky **UKnowledge**

University of Kentucky Master's Theses

Graduate School

2009

## **COLLECTIVE COMMUNICATION AND BARRIER** SYNCHRONIZATION ON NVIDIA CUDA GPU

Diego Alejandro Rivera-Polanco University of Kentucky, diegi.rivera@uky.edu

Right click to open a feedback form in a new tab to let us know how this document benefits you.

#### **Recommended Citation**

Rivera-Polanco, Diego Alejandro, "COLLECTIVE COMMUNICATION AND BARRIER SYNCHRONIZATION ON NVIDIA CUDA GPU" (2009). University of Kentucky Master's Theses. 635. https://uknowledge.uky.edu/gradschool\_theses/635

This Thesis is brought to you for free and open access by the Graduate School at UKnowledge. It has been accepted for inclusion in University of Kentucky Master's Theses by an authorized administrator of UKnowledge. For more information, please contact UKnowledge@lsv.uky.edu.

#### **ABSTRACT OF THESIS**

## COLLECTIVE COMMUNICATION AND BARRIER SYNCHRONIZATION ON NVIDIA CUDA GPU

GPUs (Graphics Processing Units) employ a multi-threaded execution model using multiple SIMD cores. Compared to use of a single SIMD engine, this architecture can scale to more processing elements. However, GPUs sacrifice the timing properties which made barrier synchronization implicit and collective communication operations fast.

This thesis demonstrates efficient methods by which these aggregate functions can be implemented using unmodified NVIDIA CUDA GPUs. Although NVIDIA's highest "compute capability" GPUs provide atomic memory functions, they have order N execution time. In contrast, the methods proposed here take advantage of basic properties of the GPU architecture to make implementations that are both efficient and portable to all CUDA-capable GPUs. A variety of coordination operations are synthesized, and the algorithm, CUDA code, and performance of each are discussed in detail.

KEYWORDS: GPU, barrier synchronization, CUDA, constant time race resolution, global block synchronization

# COLLECTIVE COMMUNICATION AND BARRIER SYNCHRONIZATION ON NVIDIA CUDA GPU

Ву

Diego Alejandro Rivera-Polanco

Dr. Henry (Hank) Dietz, Ph.D. Director of Thesis

Dr. Stephen D. Gedney, Ph.D. Director of Graduate Studies

09/09/2009

#### RULES FOR THE USE OF THESES

Unpublished theses submitted for the Master's degree and deposited in the University of Kentucky Library are as a rule open for inspection, but are to be used only with due regard to the rights of the authors. Bibliographical references may be noted, but quotations or summaries or parts may be published only with the permission of the author, and with the usual scholarly acknowledgments.

Extensive copying or publication of the thesis in whole or in part also requires the consent of Dean of the Graduate School of the University of Kentucky.

A library that borrows this thesis for use by its patrons is expected to secure the signature of each user.

| <u>Name</u> | <u>Date</u> |

|-------------|-------------|

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             | •           |

## **THESIS**

Diego Alejandro Rivera-Polanco

The Graduate School University of Kentucky 2009

## COLLECTIVE COMMUNICATION AND BARRIER SYNCHRONIZATION ON NVIDIA GPU

#### **THESIS**

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering in the College of Engineering at the University of Kentucky

By

Diego Alejandro Rivera-Polanco

Lexington, Kentucky

Director: Dr. Henry G. Dietz, Professor of Electrical and Computer Engineering

Lexington, Kentucky

2009

To my dear parents, and siblings Nata and Sergio, for their support and love.

To Alvaro and Yolanda.

Without their effort and patience this goal would have not been possible to achieve.

To my beloved Sharon, for her love, company and help.

Thank to all of them, this dream was possible...

#### **ACKNOWLEDGMENTS**

It was an honor to work with my advisor, Dr. Hank Dietz. I want to give him my sincerest thanks for his guidance, advice, support and patience. Also would like to express my gratitude to Dr. Robert Heath and Dr. Ingrid St. Omer for their suggestions and advices as part of my defense committee.

Finally, I would like to thank Sharon, my family, and friends who always supported me and motivated me to reach this goal.

## TABLE OF CONTENTS

| ACKNOWL   | LEDGMENTS                                  | iii  |

|-----------|--------------------------------------------|------|

| LIST OF T | ABLES                                      | vii  |

| LIST OF F | IGURES                                     | viii |

| CHAPTER   | 1 - INTRODUCTION                           | 1    |

| 1.1 ld    | entification of the problem                | 1    |

| 1.2 M     | otivation and proposed solution            | 3    |

| 1.3 R     | elated Work                                | 4    |

| 1.4 TI    | nesis outline                              | 5    |

| CHAPTER   | 2 - NVIDIA GPU ARCHITECTURE                | 7    |

| CHAPTER   | 3 - METHODS OF SYNCHRONIZATION WITHIN GPUs | 12   |

| 3.1 N     | VIDIA provided operations                  | 13   |

| 3.1.1     | NVIDIA atomic native functions             | 13   |

| 3.1.2     | Wait-free and t-resilient objects          | 16   |

| 3.1.3     | Built-in barrier synchronization           | 17   |

| 3.2 C     | onstant Time Race Resolution (CTRR)        | 18   |

| 3.2.1     | Native kernels                             | 22   |

| 3.2.2     | Reduction operations                       | 26   |

| 3.3 G     | lobal Block Synchronization (GBS)          | 31   |

| 3.3.1     | Global state restoring                     | 34   |

| 3.3.2     | GBS library                                | 35   |

| CHAPTER   | 4 - PERFORMANCE RESULTS                    | 36   |

|   | 4.1   | Native kernel p_any() using NVIDIA atomic operations | . 38 |

|---|-------|------------------------------------------------------|------|

|   | 4.2   | CTRR native kernels                                  | . 40 |

|   | 4.3   | GBS kernel                                           | . 46 |

|   | 4.4   | Using GBS to implement AFAPI functions               | . 56 |

| С | HAPTI | ER 5 - CONCLUSIONS AND FUTURE WORK                   | . 60 |

| Α | PPENI | DIX A - CUDA CODE FOR KERNELS                        | . 63 |

|   | A.1   | atom_p_any()                                         | . 64 |

|   | A.2   | p_warp_any()                                         | . 64 |

|   | A.3   | p_selectOne()                                        | . 65 |

|   | A.4   | p_any()                                              | . 65 |

|   | A.5   | p_all()                                              | . 66 |

|   | A.6   | syncblocks()                                         | . 66 |

|   | A.7   | reduceAdd() – GBS                                    | . 67 |

|   | A.8   | reduceOr() – GBS                                     | . 69 |

|   | A.9   | reduceAnd() – GBS                                    | . 70 |

|   | A.10  | reduceMax() – GBS                                    | . 72 |

|   | A.11  | reduceMin() – GBS                                    | . 74 |

|   | A.12  | reduceAnd() – Using CTRR and GBS                     | . 76 |

|   | A.13  | reduceOr() – Using CTRR and GBS                      | . 77 |

|   | A.14  | reduceMax() – Using CTRR and GBS                     | . 78 |

|   | A.15  | reduceMin() – Using CTRR and GBS                     | . 79 |

|   | A.16  | p_bcast()                                            | . 80 |

|   | A.17  | p count()                                            | . 81 |

| A.18   | p_first()    | . 83 |

|--------|--------------|------|

| A.19   | p_quantify() | .84  |

| A.20   | p_vote()     | . 85 |

| BIBLIO | GRAPHY       | . 86 |

| VITA   |              | . 88 |

## LIST OF TABLES

| Table 3.1 – Atomic operations available in NVIDIA CUDA GPUs | 14 |

|-------------------------------------------------------------|----|

| Table 4.1 – Test machines information                       | 36 |

| Table 4.2 – GPU specifications                              | 37 |

### LIST OF FIGURES

| Figure 2.1 – CUDA application stack                                               |

|-----------------------------------------------------------------------------------|

| Figure 2.2 – Threads, Blocks and Grids in NVIDIA GPUs9                            |

| Figure 2.3 – NVIDIA CUDA GPU hardware model                                       |

| Figure 4.1 – atom_p_any() Execution time                                          |

| Figure 4.2 – atom_p_any() early vs late finish condition, input data all 0 39     |

| Figure 4.3 – atom_p_any() early vs late finish condition, input data all 1 39     |

| Figure 4.4 – p_selectOne() execution time41                                       |

| Figure 4.5 – p_any() execution time41                                             |

| Figure 4.6 – p_any() early vs late finish condition, input data all 0. GTX-280 43 |

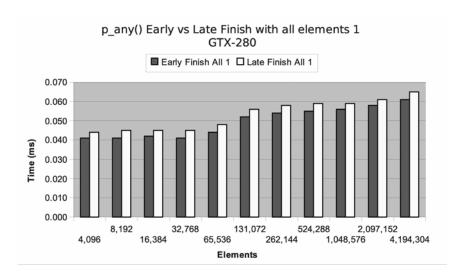

| Figure 4.7 – p_any() early vs late finish condition, input data all 1. GTX-280 43 |

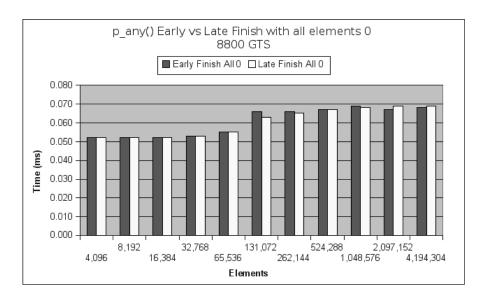

| Figure 4.8 – p_any() early vs late finish condition, input data 0. 8800 GTS 44    |

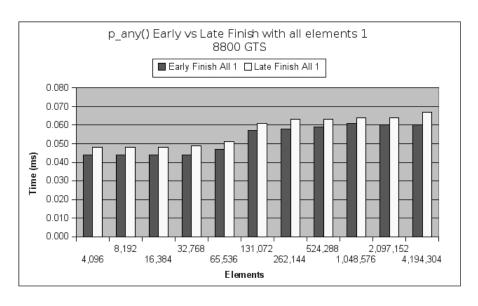

| Figure 4.9 – p_any() early vs late finish condition, input data 1. 8800 GTS 44    |

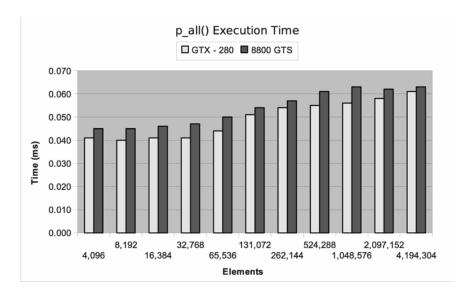

| Figure 4.10 – p_all() execution time45                                            |

| Figure 4.11 –syncblocks() execution time47                                        |

| Figure 4.12 – reduceAdd() using Global Block Synchronization                      |

| Figure 4.13 – reduce0r() using Global Block Synchronization 50                    |

| Figure 4.14 – reduceAnd() using Global Block Synchronization 50                   |

| Figure 4.15 – reduceMax() using Global Block Synchronization51                    |

| Figure 4.16 – reduceMin() using Global Block Synchronization51                    |

| Figure 4.17 – reductionAdd() using NVIDIA optimized algorithm [15]52              |

| Figure 4.18 – reduceAnd() using CTRR within a block - GBS across blocks 54        |

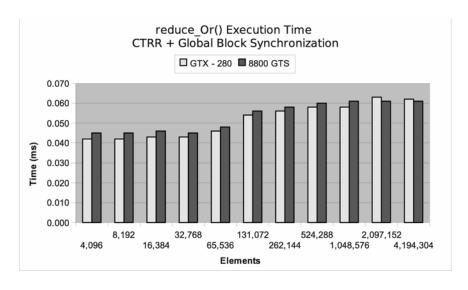

| Figure 4.19 – reduce0r() using CTRR within a block - GBS across blocks  | . 54 |

|-------------------------------------------------------------------------|------|

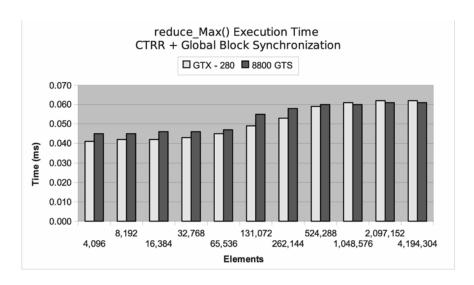

| Figure 4.20 – reduceMax() using CTRR within a block - GBS across blocks | . 55 |

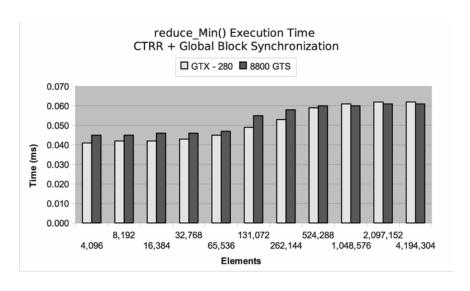

| Figure 4.21 – reduceMin() using CTRR within a block - GBS across blocks | . 56 |

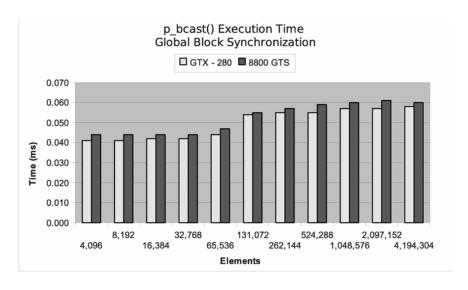

| Figure 4.22 – p_bcast() execution time                                  | . 57 |

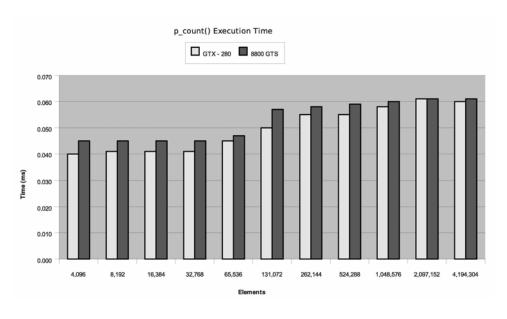

| Figure 4.23 – p_count() execution time                                  | . 57 |

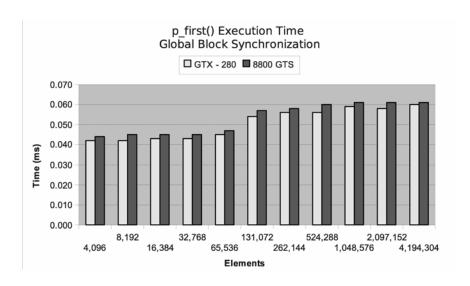

| Figure 4.24 – p_first() execution time                                  | . 58 |

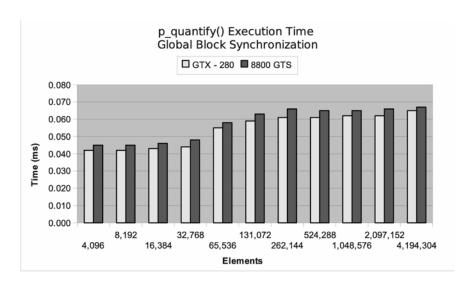

| Figure 4.25 – p_quantify() execution time                               | . 59 |

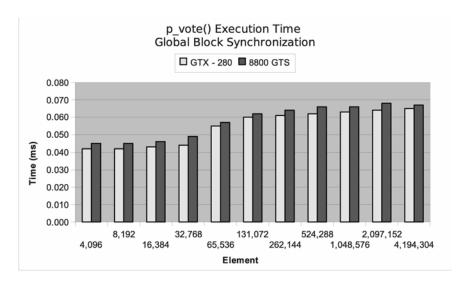

| Figure 4.26 – p vote() execution time                                   | . 59 |

#### **CHAPTER 1**

### 1 INTRODUCTION

With the explosive growth of new high-end GPU systems and architectures, the use of GPUs is no longer restricted to graphic processing applications. General-purpose parallel computation using a GPU is now a common technique due to the good price to performance ratio, the large number of processing elements they offer, and the emergence of high level GPU programming languages and tools such CUDA [1], Brook+ [2], and BSGP [3]. Unfortunately, there is not yet a clear path to implementing complex applications on a GPU; there are a variety of issues associated with each of the alternative approaches. The primary issue that is addressed in this thesis is common to nearly all of these approaches: the lack of efficient barrier synchronization and collective communications.

## 1.1 Identification of the problem

GPU architectures are no longer designed as pure Single Instruction Multiple Data (SIMD) systems, but as a set of multiple SIMD multiprocessors glued together. Each one is capable of performing a different instruction at the same time. Each SIMD multiprocessor also is heavily multi-threaded to hide memory access latency. Thus, this model implicitly results in a lack of synchronization and

communication between multiprocessors and traditional coordination primitives between SIMD cores which are not always available.

On the other hand, GPUs are now widely used to execute high performance applications; hence it is highly desirable that efficient methods for synchronization and communication are provided. Different GPU architectures provide different tools to reach synchronization. For example, NVIDIA and ATI have very different approaches to handling cache coherence; NVIDIA simply does not cache global memory, whereas ATI caches but restricts writes to simplify coherence. Thus, synchronization using global memory will behave differently across these two architectures.

NVIDIA CUDA GPU support for explicit atomic operations has gradually evolved with higher compute capability <sup>1</sup> devices. GPUs with compute capability 1.0 do not support any of them, devices with compute capability 1.1 support atomic functions operating on 32-bit words in global memory, and devices with compute capability 1.2 and 1.3 support atomic functions operating on memory shared within a SIMD core and atomic functions operating on 64-bit words in memory shared across SIMD cores as well [1].

Although including support for atomic operations as a tool to reach synchronization in general purpose parallel computation using GPUs was desired and expected, it is still not clear how to achieve efficient synchronization between processing elements across different SIMD multiprocessors. The lack of portability associated with use of these constructs was a major motivation for

2

<sup>&</sup>lt;sup>1</sup> Compute capability is defined by NVIDIA [1] as the version of the core architecture presented in their systems and the minor improvements of new features added to new GPUs. Thus, the most basic device has compute capability 1.0 and the highest performance device has compute capability 1.3

finding alternative software solutions upon which the desired high-level operations could be efficiently implemented.

## 1.2 Motivation and proposed solution

GPUs offer the best price to performance ratio to execute parallel computation, either graphics applications, or general purpose. However, GPU architectures are not designed as purely SIMD machines nor MIMD, but rather something in between, and target applications to be optimized by the use of GPUs are mostly SIMD oriented, despite the fact that most of the emerging programming models and languages<sup>2</sup> are based on MIMD programming paradigms using C [3].

This mixing of styles involved in the whole GPU system environment should make it feasible to execute MIMD programs in those new SIMD-like machines, and more specifically, in the GPU. The concept is called MOG – MIMD On GPU.

However, to make the MIMD environment run efficiently inside the GPU, it is necessary to provide tools to the new instruction set, compiler, or interpreter. Such tools include methods for thread synchronization (like barrier synchronization and atomic functions), algorithms for reduction operations like Min, Max, Sum, And, Or, and algorithms for Voting and Scheduling operations.

This thesis designs, efficiently implements, and evaluates the performance of algorithms to:

-

<sup>&</sup>lt;sup>2</sup> CUDA, ATI CAL, Brook+, OpenCL, BGSP

- Reach synchronization between threads within the GPU even if they exist in different SIMD engines.

- 2. Execute reduction and voting scheduling operations within a GPU.

Although generally targeting NVIDIA GPUs, the algorithms are intended to provide solutions to the synchronization problem that are somewhat independent of the hardware capabilities of the systems. They are intended to be as simple and efficient as possible.

#### 1.3 Related Work

The highly evolving architecture of GPUs offers the best computational power per dollar ratio systems [5]. However, since most of the transistors on a GPU are dedicated to data processing and few of them deal with cache and control flow [1], some features had to be compromised. One of features is the synchronization between processing elements (PEs) or threads (virtual PEs) within different SIMD engines on a GPU.

The lack of synchronization mechanisms in recent GPUs and the need of synchronization in parallel applications were also identified in other publications [6], where a pair of synchronization mechanisms were suggested, both of them based in atomic operations. Each thread of a SIMD core accesses the shared memory across cores using atomic read/write and then a wait-free and t-resilient synchronization objects are created. More of this paper is discussed further in Section 3.1.

It was also found that it is possible to reach synchronization between SIMD cores, using the coalesced global memory access capability of the GPU [7]. Handling the architectural restrictions, H. Phuong et al. [7] have shown that threads on different SIMD engines can reach synchronization. Three different memory accesses models were built by the researchers and the corresponding synchronization capabilities were evaluated.

Unfortunately, none of the methods discussed in the literature is particularly efficient and there are various portability constraints.

The main contribution of this thesis is the algorithm design, testing and performance analysis of several key global communication operations. Barrier synchronization between PEs across different SIMD engines in the GPU is a fundamental algorithm by itself, and also within the implementation of other operations. Various reductions and voting-scheduling algorithms were also implemented. All of these implementations are designed to work on any NVIDIA CUDA GPU regardless the compute capability, even if they do not have support for atomic operations. Everything was tested using a compute capability 1.0 system.

#### 1.4 Thesis outline

Chapter 2 of this thesis document presents the technical background and architecture information available for the most important high-end GPU vendors. It clarifies the concepts and the vocabulary used by them and shows the key points explored in the development of this research. Chapter 3 introduces a

summary of some commonly used methods of synchronization between PEs and also presents the theory of the different synchronization methods proposed as an alternative multi-thread solution when using GPUs for general purpose computation. The results obtained when running kernels implementing a variety of synchronization methods are presented in Chapter 4, graphs of the execution time are shown there. The final Chapter presents the conclusions and suggestions for future work in this research area.

CUDA code for all the kernels used as benchmarks to produce the results presented in Chapter 4 are included in Appendix A. Although they are not structured for release at this time, the intent is that these routines will be packaged and released as open source from Aggregate.Org in the near future.

#### **CHAPTER 2**

#### 2 NVIDIA GPU ARCHITECTURE

This Chapter introduces the most important architectural features found in the NVIDIA CUDA GPUs. It is not intended to be a complete description of the NVIDIA architecture; it serves primarily as a review of the model used here to develop the synchronization and reduction mechanisms proposed in this thesis. For a more detailed description of all the features of the NVIDIA CUDA GPUs, please refer to NVIDIA CUDA official programming guide [1].

Before introducing the architecture details, it is necessary to explain some concepts and terminology used with CUDA and the programming environment.

As defined by NVIDIA [1], CUDA is a general-purpose computing architecture which includes a programming environment that allows developers to use simple extensions to the standard C and C++ languages to develop applications for parallel computing on GPUs. In the future, it is claimed that CUDA will support other programming interfaces, such as FORTRAN. There are other non-CUDA environments as well [8], but this thesis restricts itself to the CUDA environment because it is the official native environment. Figure 2.1<sup>3</sup> shows the application stack layers used in a CUDA environment.

7

<sup>&</sup>lt;sup>3</sup> Figure 2.1 is based on the application stack graph described by NVIDIA in the CUDA programming guide [1]

## APPLICATION

HIGH LEVEL LANGUAGES

**CUDA ARCHITECTURE**

Figure 2.1 - CUDA application stack

The way that the CUDA programming environment identifies that a function must be executed by the GPU is by defining a kernel function inside a C program. A kernel is the equivalent of a C function that declares the variables and computations that a GPU must execute for the current program on the top of the application stack. The kernel invocation is used by the system in order to differentiate between the two environments (CPU and GPU), so when a kernel is invoked it is executed simultaneously by every active thread within the GPU. Each thread is mapped to a virtual processing element within the GPU for execution.

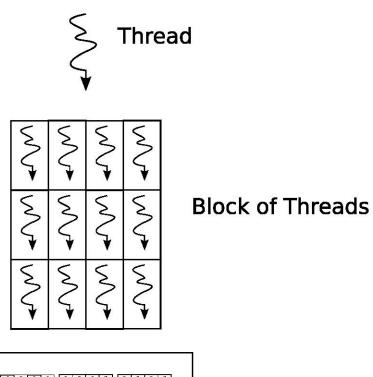

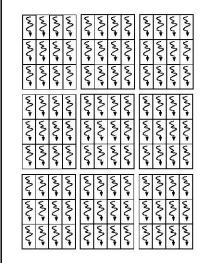

Thus, treads in a GPU are seen as the basic unit of computation. As said above, every instruction declared inside a kernel is executed simultaneously by multiple threads, and threads can be organized such that they form a one-, two-, or three-dimensional block. In this thesis, only one-dimensional blocks are analyzed. At the same time, multiple blocks are put together in a one or two

dimensional grid. Figure 2.2 clarifies the relationship between threads, blocks, and grids.

**Grid of Blocks**

Figure 2.2 – Threads, Blocks and Grids in NVIDIA GPUs

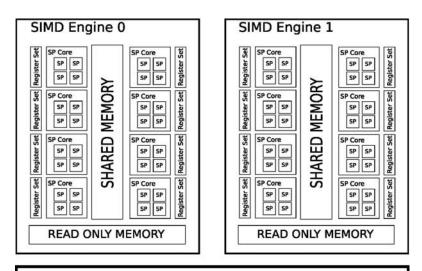

With respect to the hardware architecture, NVIDIA GPU systems were designed as an array of multi-threading processors or SIMD engines, each one having eight scalar processor cores and each core having four single processing elements which are the physical fundamental computational units. Beside the scalar processors, each SIMD engine also includes an on-chip shared memory, a set of 32-bit registers per processor, a read only constant cache, and a read only texture cache.

Figure 2.3 shows the GPU hardware model. Every SIMD engine creates, manages, schedules, and executes threads in groups of 32 threads each. To be precise, a group of 32 threads is actually performed by multi-threading over 8 physical processing elements within a SIMD engine rather than being executed truly simultaneously, but this minimum level of multi-threading cannot be avoided. Each group of 32 threads is called a warp. A warp executes one common instruction at a time – like a pure SIMD machine – so peak performance is reached when all threads within the warp agree in the instruction path. Hence, if one thread within a warp wants to execute a branch instruction, then this thread is put in a hold and the diverged instructions are executed serially. Once every branch path has been completed, the entire warp is released.

This document follows the terminology used by NVIDIA with respect to the different types of memory. The term global memory refers to the memory shared between SIMD engines. In contrast, the term shared memory refers to the memory that is associated with a single SIMD engine, and hence shared only between processing elements within that SIMD engine.

# **GLOBAL MEMORY**

Figure 2.3 – NVIDIA CUDA GPU hardware model

#### **CHAPTER 3**

### 3 METHODS OF SYNCHRONIZATION WITHIN GPUS

In order to achieve efficient parallel execution, synchronization between PEs has to be reached either by software native functions or by hardware capability. Barrier synchronization is one of the most common coordination strategies used to synchronize multiple PEs within a parallel system. A barrier forces all PEs to wait until every PE reaches the synchronization point and then releases all of them [9]. The barrier could be defined as a synchronization mechanism in which no PE is allowed to proceed beyond the barrier until all other PEs have reached it. When the barrier is hardware implemented, PEs have to be somehow physically connected with each other to perform the synchronization as in KAPERS – Kentucky Adapter for Parallel Execution and Rapid Synchronization – [10]. When the barrier is software implemented, the synchronization is achieved as the compound effect of a set of primitive hardware operations.

Beside barriers, another popular type of synchronization used specially in operating systems to coordinate between processes is the atomic transaction model. This model comes from the concept of mutual exclusion in critical transactions performed by processes that may request access to a shared resource simultaneously; only one process should be allowed access at any given time. Basically, an atomic transaction is an indivisible transaction unit that forces concurrently-issued instructions to behave as if they were performed serially if they would interfere, thereby maintaining atomicity for each action. The

next Section presents an overview of the barrier synchronization and atomic function operations present in NVIDIA hardware<sup>4</sup>.

#### 3.1 NVIDIA provided operations

Various synchronization tools have been proposed and widely implemented to coordinate PEs or multi-processes entities such as those within the operating system or multi-threaded computations within a GPU, either directly using primitive atomic operations or through the use of different strategies based on higher-level atomic operations such as locks or semaphores. But what exactly is an atomic operation? Silberschatz et al. [11] define an atomic operation as a program unit that must be executed atomically. That is, either all the operations associated with it are executed to completion or none of them are performed.

#### 3.1.1 NVIDIA atomic native functions

Although the first release of NVIDIA CUDA GPUs – Compute Capability 1.0 – actually has a number of operations it performs atomically, it explicitly did not include support for any of the best known atomic operations. The second generation of GPUs – compute capability 1.1 (and higher<sup>5</sup>) – includes a set of atomic operations aimed to be used as synchronization tools. This evolution was driven by NVIDIA's desire to lead in general-purpose computing on GPUs; these atomic operations were frequently requested by users.

<sup>4</sup> Atomic operations are available in devices with compute capability 1.1 and above.

<sup>&</sup>lt;sup>5</sup> NVIDIA CUDA programming guide [1] describes the specifications for devices with compute capability 1.2, however they are not yet available in the market.

Atomic operations within an NVIDIA GPU perform a Read-Modify-Write uninterruptedly cycle for 32-bit or 64-bit words in shared or global memory depending upon the compute capability supported. The atomicity of those operations lean on the fact that it is guaranteed that no other thread can read or write on the memory address used by the atomic operation until it is completed. Table 3.1 presents a summary of the available atomic operations along with its restrictions in NVIDIA CUDA GPUs.

Table 3.1 – Atomic operations available in NVIDIA CUDA GPUs

| ATOMIC                 | ATOMIC DESCRIPTION RESTRICTION                                                                |                                                 |

|------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------|

| FUNCTION               |                                                                                               |                                                 |

| atomicAdd()            | Add                                                                                           | 64-bit word is only                             |

|                        |                                                                                               | supported for global memory                     |

| atomicSub()            | Subtraction                                                                                   | Only supported for 32-bit words                 |

| atomicExch()           | Exchanges the value in memory with a new value                                                | 64-bit word is only supported for global memory |

| <pre>atomicMin()</pre> | Finds the min between value in memory and a new value                                         | Only supported for 32-bit words                 |

| atomicMax()            | Finds the max between value in memory and a new value                                         | Only supported for 32-bit words                 |

| atomicInc()            | <pre>((val_in_mem &gt;= new_val) ? 0 : (val_in_mem + 1))</pre>                                | Only supported for unsigned 32-bit words        |

| atomicDec()            | <pre>(((val_in_mem == 0)     (val_in_mem &gt; new_val)) ?   new_val : (val_in_mem - 1))</pre> | Only supported for unsigned 32-bit words        |

| atomicCAS()            | Compare and swap                                                                              | 64-bit word is only supported for global memory |

| atomicAnd()            | Bitwise And                                                                                   | Only supported for 32-bit words                 |

| atomicOr()             | Bitwise Or                                                                                    | Only supported for 32-bit words                 |

| atomicXor()            | Bitwise Xor                                                                                   | Only supported for 32-<br>bit words             |

Based on the built-in functions presented in Table 3.1, it is possible to implement an atomic version of the global OR function p\_any(). It is called p\_atom\_any(). The goal of this function is to determine if at least one of the threads has set its datum value to "1" – in other words, the goal is to implement a one-bit-wide global OR using atomic functions.

The kernel p\_atom\_any() was implemented using the built-in function atomicOr(). Each thread within a block executes a bitwise atomic OR operation having as inputs the value stored in its own shared memory cell address and the value of the designated shared memory address where the accumulated result is stored. This way the value returned in global memory by the kernel is guaranteed to be logic high when any location of the input data stream analyzed by the treads has a true (non-zero) flag value. In the kernel implemented, for example, the flag true value is represented by an integer value of "1". Algorithm 3.1 presents the CUDA kernel of the p\_atom\_any() code.

Algorithm 3.1 - p\_atom\_any() CUDA code

There have been various methods published that would allow an operation like atomicOr() to execute without blocking resources such as Fetch-and-Op [12] which permits highly concurrent execution of synchronization primitives. Fetch-and-Op also has the property that when multiple processing elements simultaneously fetch and write a variable in memory, the result of these operations is the same as if they would be executed serially. Unfortunately, those implementations are somewhat hardware intensive, and hence less likely to be used in a GPU. Current implementations of NVIDIA CUDA GPUs cause the atomic operations to lock system resources while executing operations to guarantee that no other thread will interfere with the memory read-modify-write process. The result is that this function has O(N) execution time, much slower than the constant-time race resolution concept proposed in Section 3.2 which has constant time execution time. Chapter 4 presents a summary of the results achieved performance test and the comparison between p atom any() and the constant time race resolution version of the function ANY as well.

#### 3.1.2 Wait-free and t-resilient objects

Other proposed solutions to reach coordination and synchronization between SIMD cores in NVIDIA GPUs have been proposed before by using atomic operations [6], where the GPU was modeled as N-SIMD machines sharing a shared memory. Each SIMD machine can process M threads in one clock cycle, each of the M threads inside a core can read/write one memory location in one

atomic step, and then each core can read/write M memory location per atomic step.

After identifying the atomic capability of the model, researchers constructed a set of wait-free and t-resilient synchronization objects aimed to provide synchronization tools to programmers of parallel applications. Those objects are:

- Wait-free long lived consensus object

- Wait-free read-modify-write object

- t-resilient read-modify-write object

The terminology used by the researchers to explain their theory is presented here as it was presented in the original paper [6].

Consensus number refers to the maximum number of PEs for which the object can solve a consensus problem. An n-consensus number allows n-PEs to propose their values and return only one of these values back to all of the n-PEs. Long-lived consensus object is a consensus object in which the variables are used more than once during the object life time. An object implementation is wait-free if any PE can complete any operation on the object in a finite number of steps regardless the execution speed of the other PEs. An object implementation is t-resilient if non-faulty PEs can complete their operations as long as no more than t PEs fails.

### 3.1.3 Built-in barrier synchronization

As part of the synchronization tools available in GPU systems, all NVIDIA CUDA GPUs include a built-in primitive called \_\_syncthreads() used to synchronize threads within a block [1]. Basically, the primitive

\_\_syncthreads() acts as a barrier synchronization point where no thread within that block is allowed to proceed until the \_\_syncthreads() has completed. Once this point is reached, the threads' execution continues normally. This synchronization primitive was built to coordinate thread communication within a block and make it the way to avoid data hazards such as read-afterwrite, write-after-read, or write-after-write when multiple threads want to access the same address in shared or global memory.

However, since \_\_syncthreads() works only within a block and NVIDIA GPUs allocate one block per SIMD multiprocessor, this primitive does not synchronize threads residing in different blocks or across different multiprocessors.

The description of the synchronization mechanisms implemented by using the hardware and software features presented in the GPUs are described within the next two Sections.

## 3.2 Constant Time Race Resolution (CTRR)

What happens when multiple threads want to write simultaneously a value in memory? According to the CUDA programming guide, it is not possible to know the number of serialized writes but it is guaranteed that at least one of the threads writes the value in memory. Empirically we found that the execution time of such kernels is constant rather than O(N).

Although it is not exactly clear how the hardware handles the simultaneous writes to memory and which thread gains the right to do it – the fastest, the slowest, or a random thread – this fact lead us to better understand the functionality of the NVIDIA CUDA GPUs and was the key to open a new optimal method of synchronization between threads for simple operations such p\_any(), p\_all(), used to determine the global OR or global AND state of the system, and p\_selectOne() which returns the thread ID number (IPROC) of any active thread. The motivation to implement these native function kernels in NVIDIA CUDA GPUs arose from the fact that they were available on the MasPar MP-1 SIMD machine [13] as part of the support for running MIMD code on SIMD hardware [14]. As expressed in Chapter 1, part of the motivation to research the functionality of high end GPUs was to be able to use them to implement a MIMD environment.

However, in the beginning it was not clear how NVIDIA CUDA GPUs managed the process of multiple threads writing simultaneously to a single shared memory cell. Since the CUDA programming guide [1] does not mention how the hardware handles this, at least two possibilities were assumed. The first possibility was that the hardware enforced every single thread to write its content into the memory cell, just as the original design of the MasPar MP-1. As one can imagine, following this method to write data into memory would be extremely inefficient and would hurt the overall performance of any process calling any of those simple functions. The second possibility was that the hardware somehow identifies multiple writers and handles the situation. Fortunately, that was the

case and when a number of elements within a block try to write data to the same memory location, the hardware guarantees that one of them will have access to do it and somehow picks a thread to write its value in memory. This property is what we have called constant time race resolution CTRR.

The fact that the hardware identifies when multiple threads are trying to access data at the same location is the key to make this mechanism have constant execution time independent of the number of threads involved in the operation. The documentation makes it clear that this filtering is applied to convert multiple simultaneous reads from the same location into a single read and broadcast. However, it is easy to use this same hardware to detect write races and pick a winner for each race, so that each race takes only one unit of time to complete. Empirically, this is what NVIDIA seems to have done.

Both writing and reading constant time race resolution are used to implement the p\_any() kernel. The logic behind the function kernel is simple. As soon as a thread identifies that its value is equal to the passed argument, it immediately decides to write the output value in memory. So it or any of the other threads (but only one) for whom the comparison with the argument was true is selected by the memory hardware to write the output value in the corresponding cell address. When a thread reads that the value held in memory matches the anticipated value, the process is interrupted. In other words, when the solution is reached, it is broadcast to the other threads preventing them from continuing to work toward a solution. Appendix A presents the CUDA kernel codes.

The CTRR is an extremely fast mechanism when the nature of the solution can be adapted to picking a winner thread that carries a solution value. Questions like "Does any thread have the value d?" can be solved easily by using CUDA kernels implementing CTRR. Following this logic, common global functions like global Or, global And, and first IPROC efficiently could be executed by CUDA GPUs regardless of the compute capability. Such algorithms are discussed later in this Chapter.

Using CTRR to execute simple functions like p\_any(), p\_all(), or p\_selectOne() is fast enough in terms of execution time, even taking into account the restriction imposed by the GPU architecture of being designed with multiple SIMD cores and claiming that it is better to use virtualization to divide the input data stream into multiple blocks of data, each block executed by an available SIMD engine, which forces it to recursively execute the kernel. That is, since CTRR acts so fast within a block of threads and the solution of such kernels can be reached without actually processing the whole array of input data, CTRR is the most efficient mechanism known to process such functions using CUDA GPUs.

However, CTRR is not suitable for every kind of algorithm. For example, in those functions where the kernel needs to make sure that every single thread had been evaluated, it is necessary to include a control mechanism. This extra mechanism inside the kernel implies more conditional instructions adding more clock cycles to the execution. It also could serialize thread execution when the control generates divergence between threads, further degrading performance.

In general, CTRR is very likely to be efficient with functions that often can take advantage of an early termination condition like ALL, ANY, MAX or MIN. Although verifying the early termination condition implies the use of an extra conditional instruction, it does not hurt the overall performance of the program because when an application needs to evaluate the kernels p\_any() or p\_all() it is very common to find that at least a subset of elements meet the primitive condition, that is a group of elements are zeros or ones. In opposition, the early finish condition would hurt the performance of those functions that require arithmetic execution over all the stream elements or those where the early finish condition would not occur very often, e.g. 32-bit OR, or 32-bit AND. It is not very likely to find all 32 bits being zero or all 32 bits being one. In this case, evaluating the extra branch condition to verify the early finish state would cost more clock cycles to execute without gaining any advantage.

#### 3.2.1 Native kernels

Functions implemented using the CTRR concept are the simplest aggregate functions used in GPUs to read special features of the global state of the system at a determined point and are called native kernels. The main characteristic of those functions is that as soon as one of the threads reaches a positive solution for the function and writes the result back to the designated address in memory, all other threads stop evaluating the input data parameters. In most cases, they do not have to evaluate the whole stream of input data they receive, making them very efficient and suitable to the architecture of NVIDIA GPUs.

Based on the CTRR concept introduced in the last Section, it is possible to construct code for the native kernels p\_selectOne(), p\_any(), p\_all(), and p\_warp\_any() successfully. As an example, a description of the algorithms and highlights of the code for such functions is presented here as well. However, the complete sequence of code is shown in Appendix A.

The easiest way to see how CTRR works on NVIDIA GPUs is by understanding how the p\_selectOne() native kernel works. Although it is a fairly simple CUDA kernel, it practically shows how threads race for access to memory when they need to write data there.

Algorithm 3.2 shows the kernel function for p\_selectOne(). The idea is to identify the first thread that will write in memory. The way in which this is done is by letting the threads write the thread Id number. The value left in memory is the thread Id of the GPU chosen thread.

```

p_selectOne(volatile int *g_odata) {

int i = blockIdx.x * blockDim.x + threadIdx.x;

__syncthreads();

g_odata[0] = i;

}

```

Algorithm 3.2 – p\_selectOne()

Algorithm 3.3 and Algorithm 3.4 show the CUDA code for the p\_any() and p\_all() native kernels respectively.

```

if (g_odata[blockIdx.x] == 0) {

while (sdata[0] == 0 && i < n) {

sdata[threadIdx.x] |= g_idata[i] | g_idata[i +

blockIdx.x];

sdata[0] = (sdata[threadIdx.x] == 1);

i += gridsize;

}

g_odata[blockIdx.x] = sdata[0];

}</pre>

```

Algorithm 3.3 – p\_any() kernel

```

if (g_odata[blockIdx.x] == 1) {

while (sdata[0] == 1 && i < n) {

sdata[threadIdx.x] &= g_idata[i] & g_idata[i +

blockIdx.x];

if (sdata[threadIdx.x] != 1) sdata[0] = 0;

i += gridsize;

}

g_odata[blockIdx.x] = sdata[0];

}</pre>

```

Algorithm 3.4 - p\_all() kernel

These functions were implemented following four basic steps. First, an initial condition verifies that any previous thread has not written the solution to the designated address cell of global memory. If no thread has reached the solution, then it is safe for the threads to keep searching for one. In the second step, every thread verifies that no other thread within the block has reached the solution before. It is also verified if the thread needs to process more data from the input stream. If both conditions are met, then input stream data from global memory is loaded into the block shared memory. An optimization suggested by NVIDIA [15] is that the first level of reduction could be executed while loading data from global

to shared memory. The third step executes the kernel function by making each thread compare the value held in shared memory with the reference value. If a match is found, then the thread tries to write the solution in shared memory. The final step is writing the solution value in global memory. The kernel is executed recursively until a final solution is found or the whole input data was analyzed.

Both  $p_any()$  and  $p_all()$  kernels follow the same structure, the only difference between them is the comparison with the reference value done in step three. For  $p_any()$  the solution is found when the value in shared memory is equal to the reference value, while for  $p_all()$  the solution is found when the value in shared memory is not equal to the reference value.

```

if (g_odata[blockIdx.x] == 0) {

while ( i < n && sdata[0] == 0) {

sdata[threadIdx.x] |= g_idata[i] | g_idata[i +

blockDim.x];

sdata[0] = ( __any(1) != 0);

i += gridsize;

}

g_odata[blockIdx.x] = sdata[0];

}</pre>

```

Algorithm 3.5 - p\_warp\_any() kernel

Algorithm 3.5 implements a version of the global OR kernel by using the NVIDIA built-in function \_\_any()<sup>6</sup>. The \_\_any() function compares the reference value passed as parameter against the value held by all the threads of

25

<sup>&</sup>lt;sup>6</sup> According to NVIDIA [1], the function \_\_any() is only supported by devices with compute capability 1.2 or higher. As from the best of our knowledge, compute capability 1.2 devices are not available in the market

the warp and returns a non zero value if the comparison is true for any of them. Having the \_\_any() function available makes it easy to implement a p\_warp\_any() kernel.

Basically, the algorithm follows the same steps implemented in p\_any() or p\_all(), except that the comparison made in step 3 is made by the \_\_any(), which implies that the evaluation is made warp by warp instead of block by block. Although the function works fine and could be seen as a viable solution, the overhead of working warp by warp and not block by block, plus the fact that the function \_\_any() is not available for all the devices, makes this approach undesirable.

## 3.2.2 Reduction operations

Reductions are aggregate operations which have a single output value which is the result of applying an associative function to the input data. As opposed to the CTRR native kernels, reduction operation kernels have to process the whole input data stream in order to reach an accurate solution and in most cases including an early finish condition will affect the performance rather than make the execution faster. This is because for some reduction operations there are required arithmetic operations, while for some others the early finish condition rarely occurs. However, the principle over CTRR is based on the random race access that threads have when reading from or writing to memory. This characteristic makes the execution of the kernels easier and faster in the Section

above because the threads carrying the solution run to write the right value in the corresponding cell of memory.

When implementing the reduction algorithms, it is necessary to know which thread has already taken into account the operation to avoid duplicity and also know which thread is pending to be included for the operation to make sure that the final result includes everybody's data. Adding the thread participation control into the kernel code reduces the overall performance of the reduction operation under CTRR.

The aggregate reduction operations implemented using the CTRR technique are reduceOr(), reduceAnd(), reduceMax(), and reduceMin(). As in the above Section, a description of the algorithms and the highlights of the CUDA code are presented here. The complete code is shown in Appendix A.

Or reduction using CTRR can be achieved by letting each thread provide their data value to a specific cell in memory, sdata[0] in this case. Since CTRR is used here, the mechanism to implement the reduction operation is almost identical to that used with the native kernels. However, there is a major difference. Native kernels do not require all of the input data stream to be analyzed and most of the time as soon as one thread reaches the solution, the rest of them stop processing. With the reduction operations every thread has to be analyzed in order to get the final solution, hence a thread control must to be added to the kernel in order to deactivate threads that have already provided the information or those who carry redundant data already written to memory.

This control was implemented by comparing the data stored previously in sdata[0] with the data stored by each thread in a local register through the XOR operator. If the result of the value in register XOR the value in sdata[0] is not equal to 0, then the thread still needs to write some information to memory. Once every thread has written its value in memory, then a solution is reached. Algorithm 3.6 and Algorithm 3.7 present the CUDA code for the reduceOr() and reduceAnd() kernels respectively.

```

unsigned int t = 0xFFFFFFF;

sdata[0] = 0;

while (i < n){

reg_thread |= g_idata[i] | g_idata[i + blocksize];

i += gridsize;

}

While ((reg_thread & t) != 0){

Sdata[0] |= reg_thread;

__syncthreads();

T = sdata[0] ^ reg_thread;

}</pre>

```

Algorithm 3.6 - CTRR reduceOr() CUDA fragment code

```

unsigned int t = 0xFFFFFFFF;

unsigned int temp = 0xFFFFFFFF;

while (i < n) {

temp &= g_idata[i] & g_idata[i + blockSize];

i += gridsize;

}

while ((~temp & t) > 0){

sdata[0] &= temp;

__syncthreads();

t = sdata[0] ^ temp;

}

```

Algorithm 3.7 - CTRR reduceAnd() CUDA fragment code

Again and as suggested by NVIDIA [15], the first level of reduction was executed during the initial load of data from global memory to local registers.

The overhead of having to implement the thread control and the repeated call of the kernel (simulating recursive application) to reach the solution makes this mechanism a viable but not an optimal choice. However, it is possible to find positive results by mixing the CTRR algorithms with the Global Block Synchronization (GBS) mechanism explained later in this document. Timing results for the execution of reduction kernels are found later in Chapter 4.

Finding the minimum and maximum of a data stream is also a kind of reduction algorithm implemented in CUDA using the CTRR mechanism. Again, every single element of the input data array has to be analyzed to reach the solution, so thread control has to be implemented.

This time, the control was implemented using a flag which was turned off every time the thread attempted to write the value in memory and turned back on again when the thread finds out that the value written in memory was not its own. Another difference with the reductions explained before is that the reduction executed in the initial load step requires a temporary variable to be able to compare if the new loaded value is greater (smaller in the case of minimum reduction) than the previous value loaded for this particular thread.

Algorithm 3.8 and Algorithm 3.9 present the highlights of the CUDA code written for maximum and minimum reductions respectively.

```

int flag = 1;

int temp = 0;

sdata[tid] = 0;

while (i < n) {

temp = sdata[tid];

sdata[tid] = (g idata[i] > g idata[i+blockSize]) ?

g_idata[i] : g_idata[i+blockSize];

sdata[tid] = (sdata[tid] > temp) ? sdata[tid] : temp;

temp = 0;

i += gridsize;

while (flag == 1) {

sdata[0] = (sdata[0] < sdata[tid]) ? sdata[tid]</pre>

: sdata[0];

syncthreads();

flag = 0;

flag = (sdata[tid] > sdata[0]);

Flag = 1;

```

Algorithm 3.8 – CTRR reduceMax() CUDA fragment code

```

int flag = 1;

int temp

sdata[tid] = 0x7FFFFFFF; // sdata is type int

while (i < n) {

temp = sdata[tid];

sdata[tid] = (g_idata[i] < g_idata[i + blockSize]) ?</pre>

g_idata[i] : g_idata[i+blockSize];

sdata[tid] = (sdata[tid] < temp) ? sdata[tid] : temp;</pre>

temp = 0x7FFFFFFF;

i += gridsize;

}

while (flag == 1) {

sdata[0] = (sdata[0] <= sdata[tid]) ? sdata [0]</pre>

: sdata[tid];

syncthreads();

flag = 0;

flag = (sdata[tid] < sdata[0]);</pre>

flag = 1;

```

Algorithm 3.9 - CTRR reduceMin() CUDA fragment code

# 3.3 Global Block Synchronization (GBS)

The benefits of using barrier synchronization in parallel systems are widely known, but it is not clear how this concept could be applied to multicores SIMD GPUs. NVIDIA suggests [1, 15] the use of multiple thread blocks to maximize the performance of the system and synchronize blocks within the GPU by making the host CPU simulate recursive calls to CUDA kernels. Therefore, communication between thread blocks is possible at block invocation boundaries.

The problem with this type of interaction between blocks is simply that returning control to the CPU is expensive and, even more significantly, doing so flushes all local state in the processing elements. The cost of reloading registers and per-block shared memory can be very significant. Thus, the ability to interact across blocks without ending a code fragment often will be critical in achieving acceptable performance. In particular, barrier synchronization between blocks is very useful when executing operations like reduction of very large arrays, voting functions, or even scans (parallel prefix) as well; without barrier synchronization, the CPU must get involved.

The concept of global block synchronization implemented within GPUs was derived from a previous design of a barrier synchronization function included in the AFAPI library [16] and used to perform multiple aggregate computation algorithms including reduction, scans, voting, scheduling, and communications functions implemented for the SHared Memory Adapter for Parallel Execution and Rapid Synchronization (SHMAPERS) [17]. AFAPI [16] is an abstract program interface library which provides multiple aggregate functions and

operations intended to be run in Unix/Linux multiprocessor systems with shared memory.

In the barrier synchronization primitive included in SHMAPERS AFAPI, every time a barrier is reached each processing element places his barrier counter value and the data value in two separate buffers in the same dedicated cache line. Then, each processing element grabs data from cache and linearly performs local computations for the corresponding operation (reduction, scans, voting, scheduling or communications) grabbing data from cache after the barrier counter and data value are loaded in shared memory. The barrier is executed by the p\_wait() primitive which basically assigns a barrier counter to each processing element. This counter is incremented every time a barrier is reached and no PE is able to perform computation unless it determines that all other PEs have reached the value. If a PE finds a barrier counter value greater that of its own, it means that another PE found the barrier was already reached hence it is safe to continue with computations. Since the cache lines fetched to detect the barrier hold the data as well, execution of the aggregate functions can be started while reading the barrier synchronization values [17].

Following the AFAPI concept, a block synchronization kernel called \_\_syncblocks() was implemented for NVIDIA CUDA GPUs even though the same concept could be applied generically for other cards. The syncblocks() kernel and the logic behind it is presented now.

By using \_\_syncblocks(), every block running the kernel is assigned a barrier counter which is incremented every time a barrier is passed. Thus, when

all the counters hold the same value means a barrier is completed. However, if a block sees that the value held by another block is greater than its own value then another block is currently waiting at the next barrier. The actual block understands that the current barrier has completed and proceeds to update its counter without having to read every other block's counter. This logic prevents a block from looping all the way around when a barrier was already passed. Algorithm 3.10 presents the code for syncblocks().

```

syncblocks(register volatile unsigned int *barvec) {

/* Make all threads sync within each block */

__syncthreads();

/* Only one PE represents the block */

if (threaded.x == 0) {

register int i = ((blockIdx.x + 1) % gridDim.x);

register int barno = barvec[blockIdx.x] + 1;

register int hisbarno;

barvec [blockIdx.x] = barno;

/* Keep looking at others until all are here

or somebody else is past

do {

/* Wait for this one to arrive */

do {

hisbarno = barvec[i];

} while (hisbarno < barno);</pre>

/* Bump to next, wrapping if needed */

if (++i >= gridDim.x) i = 0;

} while ((hisbarno == barno) && (i != blockIdx.x));

/* We are past. Tell everybody */

Barvec[blockIdx.x] = barno + 1;

}

```

Algorithm 3.10 - \_\_syncblocks() CUDA kernel

How exactly are \_\_syncblocks() and the block synchronization used? The idea is to execute the computation within each block, and once each block reaches its own result it is loaded to global memory. Next, \_\_syncblocks() is invoked to set the synchronization point. When the block synchronization is completed and every block has written its value in memory, then the first block is in charge of collecting the temporary results previously found by all blocks to perform the final computation and find the global solution. It should be noted that CUDA can be forced to maintain memory access order within a thread by using the volatile keyword in declarations.

As an example, algorithm p\_reduceAdd() follows the optimization path for the summation reduction operation using CUDA suggested by NVIDIA [15], and a final step is inserted calling the \_\_syncblocks() function, resulting on better execution times for large arrays and slightly less efficient for small arrays of data. The description of p\_reduceAdd() in included in Appendix A.

### 3.3.1 Global state restoring

The GBS mechanism restores the data held in global memory at a determined time which is equivalent to restoring the global state. In order to compare the performance of the GBS mechanism, a global state restoring algorithm was implemented.

This algorithm allows each thread in a block to read the value from global memory and transfer it to a local set of registers, where the set of data would be available for computation. Then, data is loaded back to global memory.

#### 3.3.2 GBS library

By using the kernel \_\_syncblocks() as a barrier synchronization mechanism and using the same concept used when implementing AFAPI in SHMAPERS [17], one could implement and execute within the GPUs most of the AFAPI library algorithms. Here, we introduce a fraction of the AFAPI library version implemented using the GBS for NVIDIA GPUs.

The first kernel implemented was \_\_syncblocks(), which performs the barrier synchronization between blocks. The reduce\_Or(), reduce\_And(), reduce\_Max(), and reduce\_Add() kernels execute the corresponding types of aggregate reductions. The p\_bcast() function corresponds to the broadcasting function. Kernel p\_count() counts how many elements voted for a given value, and kernel p\_vote() returns an array of bits with bit 2<sup>k</sup> set if only if element k voted for the given value. Finally, p\_quantify() returns 0 if no element voted for the given value, returns 1 if only one element voted for the given value.

Chapter 4 presents the performance results found after running the following algorithms using the GBS mechanism and Appendix A presents the detail of the CUDA code.

## **CHAPTER 4**

## **4 PERFORMANCE RESULTS**

To verify the effectiveness of the concepts presented in this thesis, a set of micro-benchmarks were run in two different machines and the execution times for each of the programs were measured. Each of the machines has a different type of GPU system. The first test machine, uses an NVIDIA GPU GTX-280 with compute capability 1.3 while the second test machine uses an NVIDIA GPU 8800-GTS with compute capability 1.0. Both machines run under Linux operation system Ubuntu 8.04 "hardy" with a 2.6.24 kernel.

Table 4.1 presents a summary of the CPU and Memory specs for both test machines and Table 4.2 presents the specifications of the GPU cards included in the test machines.

Table 4.1 – Test machines information

|            | TEST MACHINES SPECIFICATIONS                   |  |  |

|------------|------------------------------------------------|--|--|

| Processor  | AMD Athlon™ 64 X2 Dual Core<br>Processor 4200+ |  |  |

| CPU MHz    | 1000                                           |  |  |

| Cache size | 512 KB                                         |  |  |

| Cores      | 2                                              |  |  |

| RAM memory | 1 GB                                           |  |  |

Table 4.2 – GPU specifications

|                                | MACHINE 1    | MACHINE 2 |

|--------------------------------|--------------|-----------|

| GPU System                     | GTX-280      | 8800 GTS  |

| Compute capability             | 1.3          | 1.0       |

| Global memory                  | 1 GB         | 320 MB    |

| Shared memory per block        | 16 KB        | 16 KB     |

| Memory Clock                   | 1107 MHz     | 800 MHz   |

| Memory bandwidth               | 141.7 GB/sec | 64 GB/sec |

| Multiprocessors (SIMD engines) | 30           | 12        |

| Cores (Scalar processors)      | 240          | 96        |

| Core clock                     | 1296 MHz     | 500 MHz   |

| Registers per block            | 16384        | 8192      |

| Max threads per block          | 512          | 512       |

| Clock rate (card)              | 1.3 GHz      | 1.19 GHz  |

After having described the technical specifications of the test machines and the GPU systems they included, it is necessary to describe how the benchmark programs were implemented and executed to measure the execution time of the CTRR and GBS algorithms. In order to obtain the simulation graphics and make the results comparable with each other some restrictions were set. The number of threads per block and the number of blocks were fixed to 128 and 64 respectively. Since the main objective of this thesis was to probe the functionality of the new CTRR and GBS concepts and not to find the optimal parameters under which these concepts reach the peak optimal, fixing the values of threads and blocks seemed like a valid procedure. Although the parameters for the number of threads per block and the number of blocks per grid were chosen

arbitrarily, there are still representative numbers and they match the parameters used by NVIDIA to present their simulation results [15].

The number of elements in the input data stream was used as a variable parameter to run the benchmark programs. Eleven different values were used from 4K to 4M and the programs were executed 50 times for each parameter value in the two test machines. The CUDA program determines the average execution time using the cutGetAverageTimerValue() CUDA function [1], then the mean value out of the 50 average time results was chosen.

# 4.1 Native kernel p\_any() using NVIDIA atomic operations

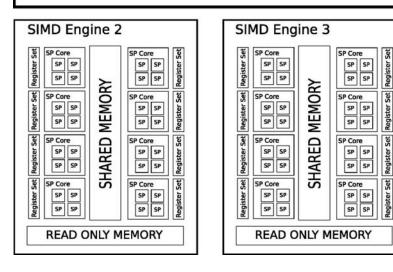

Figure 4.1, Figure 4.2, and Figure 4.3 show the execution time of the atom p\_any() kernel when it was run on test machine 1 using a GTX-280 GPU. The input data for this test was a random vector with values 0 or 1 and the kernel included an early finish termination condition.

Figure 4.1 – atom\_p\_any() Execution time

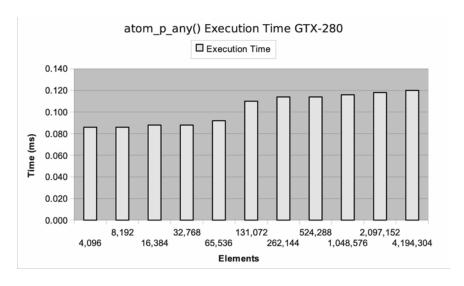

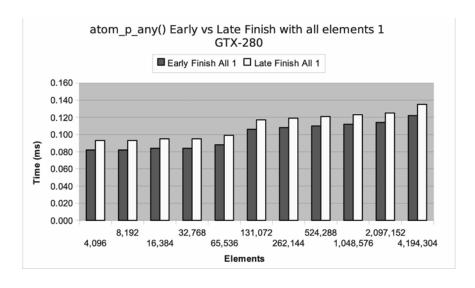

To validate the improvement achieved with the early finish condition, four more benchmarks were run combining early and late termination when the input stream was all 1 or all 0. The results are presented in Figure 4.2 and Figure 4.3. This set of tests could not be performed in test machine 2 because the 8800 GTS system does not include atomic operation support (it is compute capability 1.0).

Figure 4.2 – atom\_p\_any() early vs late finish condition, input data all 0

Figure 4.3 – atom\_p\_any() early vs late finish condition, input data all 1

It is interesting to see that for fewer than 64K elements to reduce, the execution time is relatively stable and below 90 µs; for 128K or more elements, the execution time slowly increases, going up to 120 µs in the worst case. It is likely that this slow increase is due to the way in which accesses can collide for all threads within a block, but across blocks only a representative member of each block could be involved in each collision. Additionally, there may be scheduling variability across blocks that cause accesses made by different blocks to have near misses rather than collisions. The slight bumps at 131,072 and 4,194,304 are repeatable, and are most likely due to scheduling issues.

As expected, the early termination condition was very useful when the stream input was all 1 and saved some execution time compared with the results achieved for the late termination. Also, it was shown that when input data is all 0, there is no gain on using the early termination condition since the whole stream has to be read anyway.

#### 4.2 CTRR native kernels

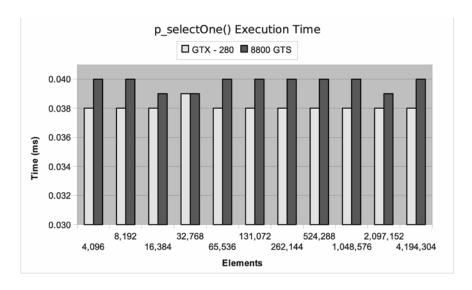

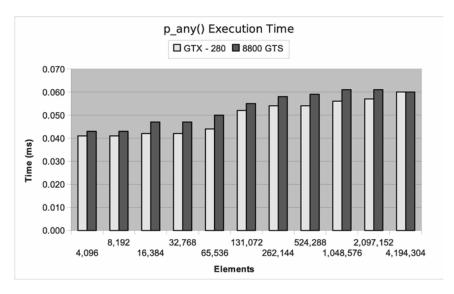

Figure 4.4 and Figure 4.5 present the results of testing the basic CTRR native functions in both types of GPUs. It is clearly shown that the time used to find the solution by the kernel is mostly constant and very efficient compared with the performance reached with the NVIDIA built in atomicOr() function.

Figure 4.4 - p\_selectOne() execution time

Figure 4.5 – p\_any() execution time

Figure 4.4 shows the execution time of running the function p\_selectOne(). This graph makes it very easy to understand and verify the functionality of the NVIDIA GPU system when multiple threads try to reach the same address in memory. The solution time is essentially constant, independent of the number of elements in the input data stream. It is also possible to see that the GTX-280 card is slightly faster than the 8800 GTS card. However, the

difference in execution time between them is only about 2  $\mu$ s. This execution time difference could be due to the higher clock rate of the single processors included in the GTX-280, but the difference is surprisingly small no matter what the reason.

Figure 4.5 presents the execution found after running the p\_any() native function in the test machines. The results follow the trend of constant time execution seen in the p\_selectOne() algorithm; however, there are some differences. The data showed that for 64K elements or less the constant time resolution stands between 40 and 50  $\mu$ s and for over 128K elements the time is between 50 and 60  $\mu$ s. The difference between the values found here and those shown before in Figure 4.4 are explained by the fact that threads in p\_any() and p\_all() performs a little computation, while threads in p\_selectOne() do not make any.

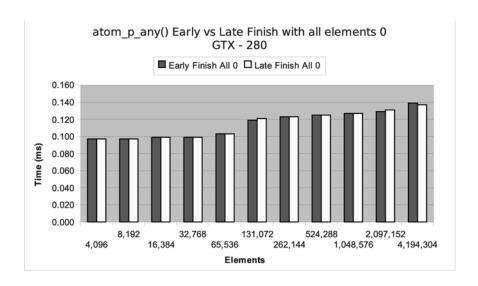

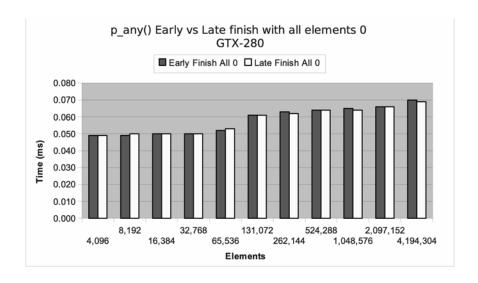

Figure 4.6, Figure 4.7, Figure 4.8 and Figure 4.9 present the results obtained when running the early and late termination conditions with input data stream either all 0 or all 1 for the  $p_any()$  native function for the two test machines. The same test could have been run for the  $p_all()$  kernel but since  $p_any()$  and  $p_all()$  only differ in the evaluation condition, we believe that the results found with  $p_any()$  also apply for  $p_all()$ .

Figure 4.6 – p\_any() early vs late finish condition, input data all 0. GTX-280

Figure 4.7 - p any() early vs late finish condition, input data all 1. GTX-280

The execution times obtained by running the benchmarks confirm the expected behavior. As in the atom  $p_any()$  test, the early termination condition kernel with input data stream being all 1 was the fastest function in both GTX-280 and 8800 GTS systems. There was no effect on runtime for the kernel with early termination condition and input data stream being all 0 as compared to the performance obtained when running the kernel without the early termination

verification and the same input data stream. Thus, the early termination test appears to be harmless even in the case in which it logically serves no purpose.

Figure 4.8 - p\_any() early vs late finish condition, input data 0. 8800 GTS

Figure 4.9 - p\_any() early vs late finish condition, input data 1. 8800 GTS

An interesting observation was found after running the p\_any() benchmarks. In both test systems the difference between the execution times obtained with the high end machine and those found with the low end GPU are not significantly different. In fact for some of the tests, execution times found for the compute capability 1.0 machine were slightly faster that those found on the GTX-280 with compute capability 1.3. This observation demonstrates that the CTRR mechanism appears to be a fundamental component of the GPU architecture and one would expect to obtain similar results with different machines even if they have different compute capabilities.

The fact that the execution time is mostly independent of the number of threads or elements that are executing the kernel is also seen in the graphics. In all of them, the shape of the curve is mostly flat and the execution time does not considerably increase with a very high number of threads executing the kernel.

Figure 4.10 - p\_all() execution time

Figure 4.10 presents the results of running  $p_all()$  in the test machines. The results are almost identical to those findings in Figure 4.5. It is interesting to see how for 4M elements the execution time for the GTX-280 and the 8800 GTS are very close in the case of  $p_all()$  and exact in the case of  $p_all()$ .

Comparing the Figure 4.1, atom\_p\_any() and Figure 4.5 p\_any(), one can see the difference of using the atomic method of synchronization with the CTRR. The major difference between the performance of these two methods is that the execution time of atom\_p\_any() increases considerably with the number of elements, while this is not the case for p\_any(). The big gap existing between execution times suggests that the system locks from the atomic nature of atom\_p\_any() definitely hurts the performance of running atom\_p\_any() over big input data streams. Another large difference between the two schemes is that atomic operations cannot be executed in systems with compute capability 1.0, like the 8800 GTS, whereas p\_any() does not present any hardware restriction.

#### 4.3 GBS kernel

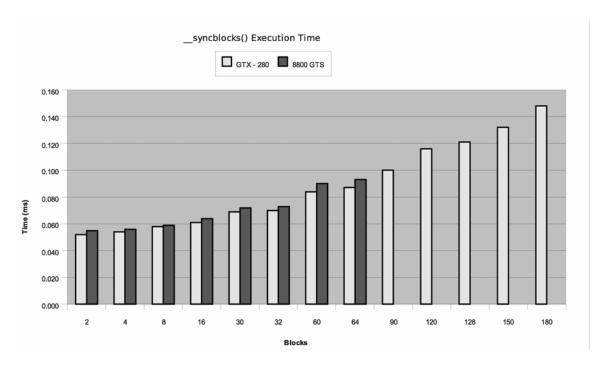

The basic unit of the global block synchronization mechanism is the \_\_syncblocks() kernel. The execution time performance reached when running the function in the test machines is presented in Figure 4.11.

Figure 4.11 – \_\_syncblocks() execution time

Unlike the rest of the benchmarks run in this thesis, the test for the \_\_syncblocks() kernel took into account the variable number of blocks to synchronize rather than the number of elements to reduce. This was done due to the nature of the kernel and the objective wanted to reach with it which is to synchronize multiple blocks using global memory. The kernel test for \_\_syncblocks() reached 10 synchronization points per run.

By seeing the performance data, it was shown that the execution time increases almost linearly with the number of blocks to synchronize. This behavior was expected since the kernel runs a barrier synchronization counter within each block or SIMD engine, hence it is valid to assume that the more blocks to synchronize the more counters to evaluate, and more time computing the operation.

However, there was an interesting result found when running the test. For the 8800 GTS system the execution time raised up to almost 8 seconds when the number of blocks needed to synchronize was over 90. Although it is not completely clear why this happens, it is believed that the number of SIMD engines within the GPU affects the behavior of \_\_syncblocks(), suggesting that for a tuned performance, a parametric optimum number of blocks must be set.

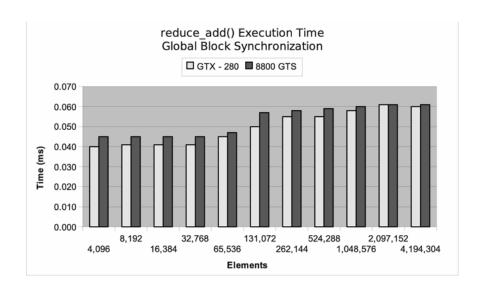

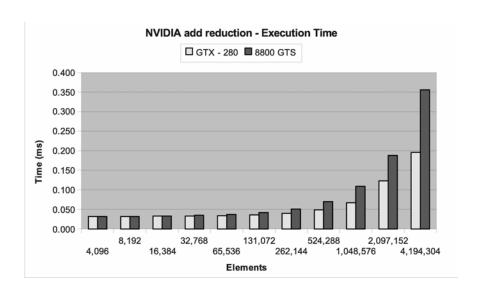

Figure 4.12 to Figure 4.16 present the performance results of the reduction operations Add, Or, And, Max and Min respectively. These algorithms used the GBS mechanism to find the reduced value. However, the reduction within each block was computed using the optimized reduction algorithm developed by NVIDIA [15]. A comparison between the pure NVIDIA reduceAdd() algorithm and the GBS reduceAdd() was also done and presented.

Figure 4.12 – reduceAdd() using Global Block Synchronization

Figure 4.12 corresponds to the execution time of running the reduceAdd() function on the test machines. Beside the optimizations explained by NVIDIA [15] in the process of finding the reduced value inside each block, the GBS algorithm presents an extraordinary performance almost matching the time values reached by the CTRR kernels.

The final solution is reached in two barriers. During the first barrier, each block computes its own result and writes it back to the designated cell memory in global memory. During the second barrier only the first block is in charge of gathering the partial results, computing the final result, and placing it in global memory.

It is interesting to see how for 2M elements and above, the timing results of running the benchmark in the 8800 GTS GPU almost ties the execution time reached with the GTX-280 GPU.

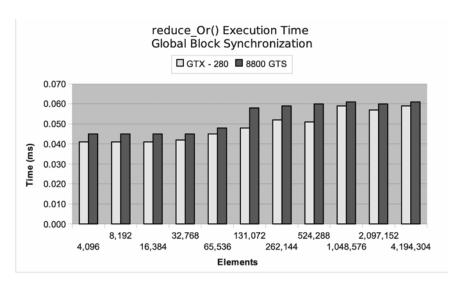

Figure 4.13 presents the performance results of running the reduceOr() benchmark on the test machines. The results are consistent with the findings in previous GBS algorithms presented here.

Figure 4.13 – reduceOr() using Global Block Synchronization

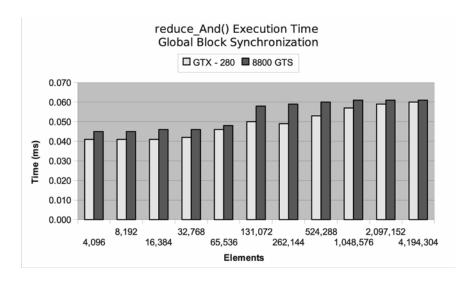

Figure 4.14 shows the results of the execution time of running the reduceAnd() benchmark. Once again, since the techniques used by the algorithms are exactly the same, the results were expected to be similar.

Figure 4.14 – reduceAnd() using Global Block Synchronization

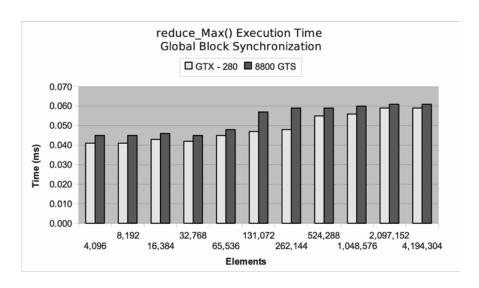

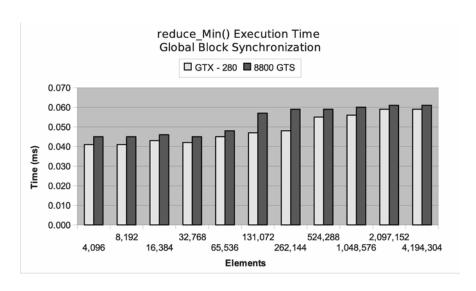

Figure 4.15 and Figure 4.16 include the execution time of running the reduceMax() and reduceMin() algorithms respectively.

Figure 4.15 – reduceMax() using Global Block Synchronization

Figure 4.16 – reduceMin() using Global Block Synchronization

Figure 4.17 was included here as a reference value used to compare the effectiveness of the GBS mechanism. The main difference between the two concepts is that while the NVIDIA algorithm reaches global synchronization by recursively calling and executing the kernel, GBS uses a barrier synchronization function \_\_syncblocks() to coordinate blocks – thus avoiding kernel recursion calls.

Figure 4.17 – reductionAdd() using NVIDIA optimized algorithm [15]

Comparing the results of Figure 4.12, reduceAdd() using GBS with Figure 4.17, reduceAdd() using NVIDIA style, it is clearly seen that for larger input data streams GBS produces a speedup of 13%, 50% and 69% for input data streams of 1M, 2M and 4M respectively with the GTX-280. For smaller input data streams (4K to 512K), NVIDIA reduction style is about 28% faster. Note that these numbers are biased in favor of NVIDIA's methods, because the (usually

very significant) cost of saving and restoring the state of GPU registers and shared memory is present with their algorithms, but not accounted here.

When testing the 8800 GTS system, GBS produces a speedup of 16%, 45%, 68% and 83% for input data streams of 512K, 1M, 2M and 4M respectively and NVIDIA style is approximately a 32% faster for 4K to 128K input data stream reductions.

This result confirms the fact that recursively calling the kernel hurts the overall performance of a computation and, because fewer input elements implies fewer kernel recursive calls; it is expected to reach better performance results for smaller input data streams.

Another observation made from this performance comparison is the confirmation of the trend followed by NVIDIA in terms of adjusting the architecture of their new systems to make kernel recursion less frequent in order to obtain better results. The old 8800 GTS system efficiently reduces up to 128K elements and the new GTX-280 efficiently reduces up to 512K elements.

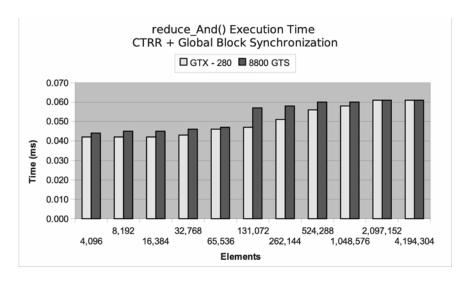

Figure 4.18 to Figure 4.21 present the performance results of testing the reduction operations And, Or, Max and Min combining the two methods, CTRR mechanism to find the partial reduction result within each block, and GBS to coordinate blocks in global memory to find the final result. The idea was to compare how different the execution time results between CTRR and NVIDIA styles are when reducing elements within a block of 128 threads.

First, reduceAnd() is analyzed in Figure 4.18. The performance information says that both methods of finding the partial reduction result within a