University of Kentucky UKnowledge

Graduate School

University of Kentucky Master's Theses

2009

# **MPI WITHIN A GPU**

Bobby Dalton Young University of Kentucky, bdyoun0@engr.uky.edu

Right click to open a feedback form in a new tab to let us know how this document benefits you.

### **Recommended Citation**

Young, Bobby Dalton, "MPI WITHIN A GPU" (2009). *University of Kentucky Master's Theses*. 614. https://uknowledge.uky.edu/gradschool\_theses/614

This Thesis is brought to you for free and open access by the Graduate School at UKnowledge. It has been accepted for inclusion in University of Kentucky Master's Theses by an authorized administrator of UKnowledge. For more information, please contact UKnowledge@lsv.uky.edu.

## ABSTRACT OF THESIS

### MPI WITHIN A GPU

GPUs offer high-performance floating-point computation at commodity prices, but their usage is hindered by programming models which expose the user to irregularities in the current shared-memory environments and require learning new interfaces and semantics.

This thesis will demonstrate that the message-passing paradigm can be conceptually cleaner than the current data-parallel models for programming GPUs because it can hide the quirks of current GPU shared-memory environments, as well as GPU-specific features, behind a well-established and well-understood interface. This will be shown by demonstrating a proof-of-concept MPI implementation which provides cleaner, simpler code with a reasonable performance cost. This thesis will also demonstrate that, although there is a virtualization constraint imposed by MPI, this constraint is harmless as long as the virtualization was already chosen to be optimal in terms of a strong execution model and nearly-optimal execution time. This will be demonstrated by examining execution times with varying virtualization using a computationally-expensive micro-kernel.

KEYWORDS: message-passing, virtualization, data-parallel, virtualization MPI, GPU

Bobby Dalton Young

August 4, 2009

## MPI WITHIN A GPU

By

Bobby Dalton Young

Henry G. Dietz, Ph.D. Director of Thesis

Stephen D. Gedney, Ph.D. Director of Graduate Studies

August 4, 2009

Date

## RULES FOR THE USE OF THESES

Unpublished theses submitted for the Master's degree and deposited in the University of Kentucky Library are as a rule open for inspection, but are to be used only with due regard for the rights of the authors. Bibliographical references may be noted, but quotations or summaries of parts may be published only with the permission of the author, and with the usual scholarly acknowledgments.

Extensive copying or publication of the thesis in whole or part also requires the consent of the Dean of the Graduate School of the University of Kentucky.

A library that borrows this thesis for use by its patrons is expected to secure the signature of each user.

| Name | Date |

|------|------|

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

THESIS

Bobby Dalton Young

The Graduate School

University of Kentucky

2009

## MPI WITHIN A GPU

## THESIS

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in the College of Engineering at the University of Kentucky

By Bobby Dalton Young Lexington, Kentucky Director: Dr. Henry G. Dietz, Professor of Electrical Engineering Lexington, Kentucky 2009 Copyright <sup>©</sup> Bobby Dalton Young 2009

# TABLE OF CONTENTS

| List of Tablesi                                        | iv |

|--------------------------------------------------------|----|

| List of Figures                                        | .v |

| List of Files                                          | vi |

| Chapter 1: Introduction                                | .1 |

| Chapter 2: Background, Methodology, and Related Work   | .2 |

| 2.1: Background                                        | .2 |

| 2.2: Methodology                                       | .4 |

| 2.3: Related Work                                      | .5 |

| Chapter 3: GPU Hardware Review and Performance Factors | .7 |

| 3.1: Review of Current GPU Hardware                    | .7 |

| 3.2: The NVIDIA CUDA Architecture                      | .9 |

| 3.3: NVIDIA CUDA Performance Considerations1           | 2  |

| Chapter 4: Virtualization Constraints                  | 5  |

| 4.1: Background and Definitions                        | 5  |

| 4.2: Performance Analysis of Virtualization1           |    |

| 4.3: Optimal Virtualization and the MPI Constraints2   |    |

| Chapter 5: The MPI Implementation                      | 27 |

| 5.1: Introduction to the Message-Passing Interface     |    |

| 5.2: Design Philosophies and Restrictions              |    |

| 5.3: The Point-to-Point Communication Interfaces       |    |

| 5.4: Point-to-Point Communication Performance          |    |

| 5.5: The Collective Communication Interfaces           | 18 |

| 5.6: Collective Communication Performance              |    |

| 5.7: Other Implemented Interfaces                      |    |

| 5.8: Costs and Benefits of the Message-Passing Model   |    |

| Chapter 6: Conclusions and Future Work                 | 58 |

| Appendix A: CUDA Code for the Functions                | 59 |

| Bibliography                                           | 35 |

| Vita                                                   |    |

# LIST OF TABLES

| Table 3.1: Some NVIDIA GPUs and various properties                | 10 |

|-------------------------------------------------------------------|----|

| Table 3.2: Compute Capabilities and their properties         [23] |    |

# LIST OF FIGURES

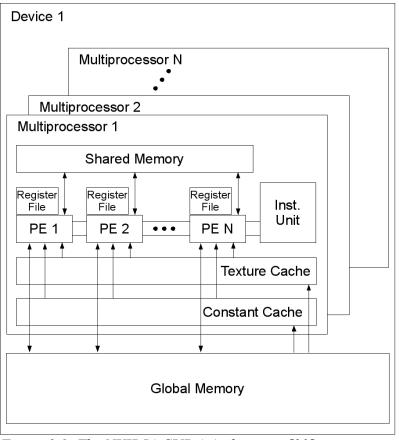

| Figure 3.1: The NVIDIA CUDA Architecture[23]1                                      | 10 |

|------------------------------------------------------------------------------------|----|

| Figure 4.1: Pseudo-code for the micro-benchmark1                                   | 18 |

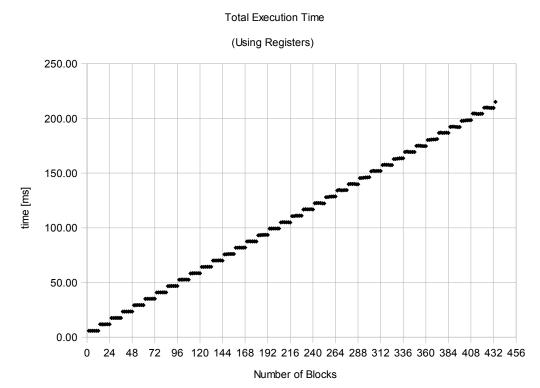

| Figure 4.2: The register micro-benchmark1                                          | 19 |

| Figure 4.3: Total execution time of the register micro-benchmark2                  |    |

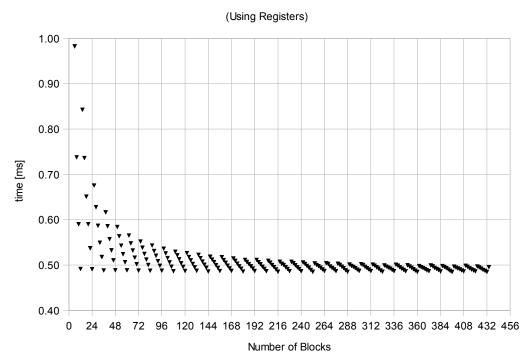

| Figure 4.4: Per-block execution time of the register micro-benchmark2              | 20 |

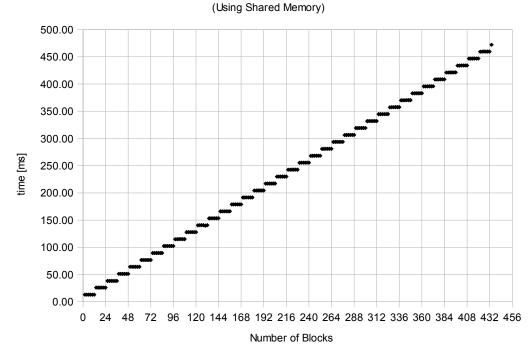

| Figure 4.5: The shared-memory micro-benchmark2                                     | 22 |

| Figure 4.6: Total execution time of the shared-memory micro-benchmark2             | 23 |

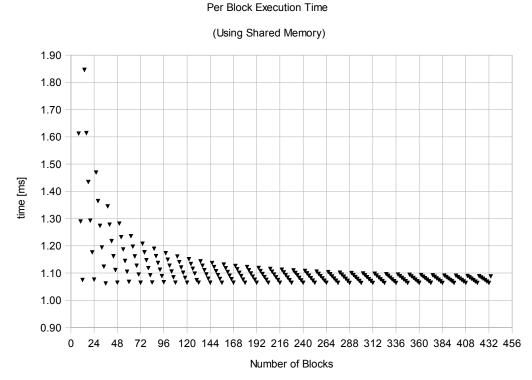

| Figure 4.7: Per-block execution time of the shared-memory micro-benchmark2         | 23 |

| Figure 5.1: MPI_Send prototype                                                     | 34 |

| Figure 5.2: Pseudo-code for MPI_Send                                               | 35 |

| Figure 5.3: MPI_Recv Prototype                                                     |    |

| Figure 5.4: Pseudo-code for MPI_Recv                                               | 38 |

| Figure 5.5: Algorithm for sequential estimation of PI4                             | 43 |

| Figure 5.6: Point-to-point MPI implementation of the test algorithm                | 44 |

| Figure 5.7: Point-to-point CUDA-only implementation of the test algorithm, part 14 | 45 |

| Figure 5.8: Point-to-point CUDA-only implementation of the test algorithm, part 24 | 46 |

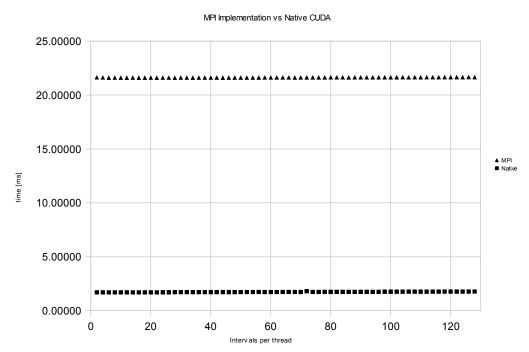

| Figure 5.9: Execution time of both implementations of the test algorithm4          | 47 |

| Figure 5.10: MPI_Barrier prototype4                                                | 49 |

| Figure 5.11: Pseudo-code for MPI_Barrier                                           | 50 |

| Figure 5.12: MPI_Reduce prototype macro                                            | 52 |

| Figure 5.13: MPI_Reduce prototype                                                  | 52 |

| Figure 5.14: MPI_Reduce translation macro                                          | 53 |

| Figure 5.15: Pseudo-code for MPI_Reduce                                            | 54 |

| Figure 5.16: Algorithm for sequential estimation of PI5                            | 59 |

| Figure 5.17: Collective MPI implementation of the test algorithm                   | 51 |

| Figure 5.18: Collective CUDA-only implementation of the test algorithm, part 1     | 52 |

| Figure 5.19: Collective CUDA-only implementation of the test algorithm, part 2     | 53 |

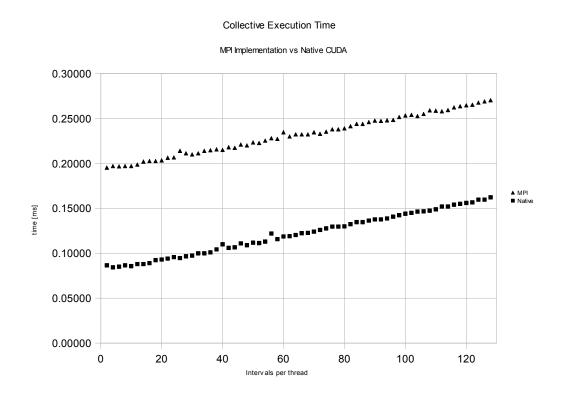

| Figure 5.20: Execution time of both implementations of the test algorithm          | 54 |

# LIST OF FILES

| BDYthesis.pdf |  |

|---------------|--|

|               |  |

### **Chapter 1: Introduction**

GPUs have gained attention for their impressive floating-point price/performance ratio. The consumer demand for realism and resolution in traditional graphics applications has effectively created scalable, high-performance floating-point hardware at commodity prices. GPUs have already been used to accelerate some numericallyintensive high-performance computing applications, but limitations imposed by current GPU programming methodologies, including a lack of code portability between GPU platforms, have hindered the use of GPUs in a wider class of programs and relegated them to a second-class co-processor status.

This thesis aims primarily to demonstrate that the message-passing programming model can be conceptually cleaner than the vendor-supplied data-parallel models by hiding the quirks of current shared-memory environments. This is accomplished by demonstrating a proof-of-concept implementation of a message-passing model on a GPU and providing performance comparisons between two GPU programs, one of which utilizes the message-passing implementation and the other of which does not, on a parallel test algorithm computing the value of pi. The message-passing implementation will be a subset of MPI[1] (the Message Passing Interface), which is a popular message-passing library specification, and the implementation and test algorithms will be developed and tested in NVIDIA CUDA[2] (the Compute Unified Device Architecture), which is NVIDIA's parallel architecture and model for general-purpose computing on a GPU.

This thesis also aims to demonstrate that, although there is a virtualization constraint for using message-passing (and more specifically MPI) within the GPU, the constraint is actually harmless if the amount of virtualization chosen is already optimal in terms of its interaction model and per-block execution time. This is accomplished by ignoring the amount of virtualization needed by MPI and profiling different amounts of virtualization on a simple micro-kernel benchmark. The resulting execution times demonstrate that the amount of virtualization needed to obtain the optimal performance, with optimal performance as defined above, is compatible with the MPI virtualization constraint.

The rest of this thesis is structured as follows. Chapter 2 (Background,

Methodology, and Related Work) provides a brief review of the message-passing and data-parallel programming paradigms discussed above, describes the relevant classes of architectures and how they apply to GPUs, describes an important philosophy which underlies this thesis, and cites related work. Chapter 3 (GPU Hardware Review and Performance Factors) provides a hardware overview which compares current-generation GPU architectures and then provides an in-depth review of the NVIDIA CUDA architecture and important performance considerations for it. Chapter 4 (Virtualization Constraints) discusses the ideas of virtualization, multi-threading, global-memory coherence, and interaction models, presents empirical data regarding the optimum amount of multi-threading and virtualization, and finally examines how the virtualization constraints imposed by MPI within a GPU are satisfied at the optimum amount of virtualization. Chapter 5 (The MPI Implementation) introduces the Message Passing Interface standard, discusses some design philosophies underlying the proof-of-concept implementation, and examines key function implementations which provide point-topoint and aggregate communication operations. Chapter 5 also provides performance comparisons between canonical NVIDIA CUDA and the MPI implementation for two implementations of an algorithm computing the value of pi in parallel and discusses the costs and benefits of using the message-passing implementation. Chapter 6 (Conclusions and Future Work) presents conclusions and future work for the research.

#### Chapter 2: Background, Methodology, and Related Work

This section first defines the data-parallel and message-passing paradigms and discusses how they apply to the thesis. This section also defines SIMD, SPMD, SIMT, and MIMD, since these architecture classifications are used extensively in the thesis. The overarching philosophies of this thesis are then discussed after clarifying the definitions and applications of these background concepts. Finally, related work is discussed.

### 2.1: Background

Two of the popular paradigms for programming parallel machines are the dataparallel paradigm and the message-passing paradigm. These programming models are described in detail below. The data-parallel paradigm, exemplified by HPF[3] and current GPU programming environments such as CUDA[2], BrookGPU[4], and CAL[5], typically consists of a single program controlling execution of all processing elements. In this paradigm, program data is typically stored in arrays, and processing elements work on subsets of arrays in their local memories.

Historically, GPU programming methods and environments have been based on the data-parallel paradigm. This is largely due to the fact that GPUs have evolved to process pixels of an image in parallel. Maintaining the same paradigm for generalpurpose programming has not been widely questioned, largely because the majority of GPU users are still performing graphics-processing applications (as opposed to generalpurpose computation). While general-purpose computation on GPUs is gaining popularity, it is still a small portion of the total market share of current GPUs. While this has allowed GPU vendors to both continue normal product development cycles and broaden marketability by advertising GPUs for non-graphics applications, it has restricted the use of the GPU to programs where data-parallelism is easily exposed. If GPUs can support the message-passing paradigm in addition to the data-parallel paradigm, though, then a wider range of execution models can be supported on current GPUs.

Message-passing is not the opposite of data-parallelism; the opposite is actually task-parallelism. This thesis will show that message-passing is compatible with data-parallelism. The message-passing paradigm, exemplified by the MPI standard[1] and various implementations of it such as OpenMPI[6] and LAM-MPI[7], typically consists of individual programs on each processing element controlling local execution. In this paradigm, program data is typically passed between processing elements via cooperative send and receive mechanisms.

Before continuing with the idea of message-passing on a GPU, some basic architectural ideas must be mentioned. Parallel computer architectures have long been classified as SIMD (Single-Instruction stream, Multiple-Data stream) and MIMD (Multiple-Instruction stream, Multiple-Data stream)[8]. As the names imply, SIMD hardware typically consists of a collection of processing elements, sometimes little more than Arithmetic Logic Units, all executing a single instruction on multiple data. MIMD hardware, in contrast, typically consists of processing elements with their own

3

instruction-fetch, decode, and execute logic, each executing a potentially different instruction on multiple data.

In addition to the SIMD and MIMD classifications, there are also SPMD systems, and the term "SIMT" should be discussed since NVIDIA uses it. SPMD (Single Program, Multiple-Data stream) are akin to SIMD systems, except that the processing elements are potentially much less synchronized because they are executing programs rather than instructions[9]. These are also akin to MIMD systems where every processing element is executing an identical program. SIMT is a term coined by NVIDIA, and stands for Single-Instruction, Multiple-Thread[2]. While it attempts to describe the scheduling of threads to available processor cores, it can best be thought of as SIMD with virtualization at the thread level.

GPUs have traditionally been classified as SIMD-like or SPMD-like architectures. As the hardware review section will illustrate, though, GPUs are a strange hybrid of the two, and behave differently at different granularities. This plays a role in enabling the implementation of a message-passing system. More importantly, though, the multiple potential classifications of GPU architectures can and should be leveraged to further expand the set of execution models which are viable within a GPU.

#### 2.2: Methodology

In chapter 1, the idea of the GPU being relegated to an attached co-processor role was mentioned. The majority of GPU research approaches the GPU as a second-class processing element and utilizes the GPU as an attached accelerator, but this thesis approaches the GPU as a future first-class parallel processor, which motivates the idea of needing a message-passing system within a GPU. If the GPU will internally be a separate entity, then it will need to perform synchronization and communication without assistance. The work in this thesis is not merely about using more execution models within a GPU, it is about which models will be needed as GPUs become independent.

We envision the use of the GPU taking the same path as the use of traditional floating-point co-processors, such as the Intel 8087 floating-point co-processor. While floating-point math was originally only available via an attached co-processor accessed with OS calls, it is now an integral part of the chip design and instruction set. Intel's Larrabee, scheduled for a 2009 or 2010 release, will be an explicitly standalone GPU

with many CPU features, including x86 processing cores[10]. Additionally, Larrabee's SIMD extensions will be opcode-compatible with the specification for extending SSE[10]. The Cell processor already includes SIMD SPEs (Synergistic Processing Elements) which work alongside a Power-architecture based PPE (Power Processing Element)[11]. AMD's FUSION project originally proposed "Accelerated Processing Units" (CPUs with a GPU on-die) as early as 2007[12], and these are now scheduled for a 2011 release in the Llano and Ontario cores[13].

Since this thesis holds that the models for GPUs are converging to this single environment, the performance benchmarks in this thesis are focused on examining performance in the context of a self-contained world, with the GPU behaving as normal computing systems generally behave. Since there is not much existing work with this viewpoint to benchmark performance against, and since benchmarking performance against a sequential code would be unfair, the benchmarks in this thesis focus on describing and quantifying the performance penalty or cost for the more-general model provided by MPI. Hopefully, future GPU research will yield competing models so that better performance comparisons can be accurately made.

#### 2.3: Related Work

There is considerable interest in GPGPU (General-Purpose Computation on GPUs), which generally refers to using graphics cards to perform computations which are not strictly limited to manipulating graphics on the screen. Although this work is related to many GPGPU efforts described below, note that this work is focused on developing a more-general programming model within the actual GPU. As stated in chapter 2.2, this research is aimed at developing a first-class processing element.

Early GPGPU programming revolved around graphics programming languages such as DirectX[14] and OpenGL[15]. These languages developed programmable shader pipelines, controlled by the HLSL[16] and GLSL[17] languages, and programmers used the shader languages to process non-graphical data. Some higher-level languages, such as Cg[18], were also used. Because of the awkwardness of expressing non-graphical computations in graphically-oriented languages, general-purpose languages which could hide the underlying nature of the hardware and programming model began to emerge. These included Sh[19], which made the GPU hardware appear as a simple resource via a

C++ library, and BrookGPU[4], which focused on programming in streams with a C++ dialect. Microsoft research also worked on an advanced system called Accelerator[20], which performed advanced just-in-time compilation with an OpenGL backend. Some companies also provided proprietary solutions, such as RapidMind's Multi-Core Platform[21].

As GPGPU became popular, vendors began to provide languages which allowed better access to the underlying hardware. ATI released CTM[22], which included the assembly language of the GPUs and driver-level codes to operate them. NVIDIA released CUDA[23], which provided a general-purpose abstraction of the underlying hardware, but did not release instruction set architectures. The development of these languages also lead to the development of more companies providing GPU acceleration services, such as PeakStream[24]. ATI's CTM was later obsoleted in favor of CAL[25], which provides similar low-level access to CTM, but with a modified version of the BrookGPU compiler which allowed users to avoid low-level programming. Efforts are currently underway to develop a vendor-independent specification for a GPGPU programming language called OpenCL[26].

Currently, many research efforts related to GPU programming environments are underway. CUDASA[27] is a system for networking clusters of machines with GPUs together, and it extends CUDA with new language constructs to do so. Zippy[28] provides similar functionality via library routines and classes which abstract the underlying GPUs. More recently, DCGN[29] abstracted GPUs in clusters, but allowed dynamic communication patterns during execution between GPUs. All of these efforts are related to using message-passing across clusters of GPUs and abstracting the hardware, whereas this research is interested in exploring the message-passing model within the hardware.

The most closely-related work is actually the BSGP project[30], which focuses on a set of extensions and very advanced compiler techniques to transform and execute sequential code on a GPU. BSGP still lacks inter-thread communication, though, and implements such mechanisms by generating individual kernels and using the edges as synchronization points. This mechanism still relies on a host processor, and still leaves the GPU as a second-class processing element. Although virtualization is not the main focus of this research, it is worth noting that virtualization in SIMD machines has been well studied before. The PARIS language[31] utilized by Thinking Machines SIMD computers is a good example.

#### **Chapter 3: GPU Hardware Review and Performance Factors**

To understand the proof-of-concept MPI implementation and the virtualization test results, it is necessary to understand the underlying CUDA hardware. This section first provides a high-level overview of current GPU hardware, which demonstrates the applicability of this work to other GPUs beyond just NVIDIA targets. Next, it provides an overview of the CUDA hardware and the scaling or scheduling parameters used to control the hardware. This section concludes with a discussion of performance factors within an NVIDIA CUDA GPU; this information needed to understand the virtualization test results in chapter 4 and some design decisions used in the MPI implementation in chapter 5.

#### 3.1: Review of Current GPU Hardware

Modern GPUs are composed of a collection of virtualizing SIMD processors. Note that these are not multiprocessors, since they do not support multiprocessing. These are relatively narrow virtualizing SIMD engines which support multi-threading over a set of processing elements, and support no MIMD behavior aside from virtualization and multi-threading.

The individual virtualizing SIMD processors are composed of some number of physical processing elements, each with its own registers and all sharing some local shared memory. Each virtualizing SIMD processor possesses local control logic for its processing elements, and all SIMD processors in a GPU can execute a different instruction at the same time. All processing elements on the SIMD processors can access a global shared memory, and all SIMD processors are connected through some global control and scheduling logic. The processing elements within a single SIMD processor can also access a local shared memory inside that multiprocessor.

The smallest unit of work in a modern GPU is a sequence of instructions executing on a single processing element. Note that this unit of work is not a thread in

the traditional sense (although the word has been appropriated to describe it), but rather a "slice" of a traditional thread executing a SIMD program. A thread in the traditional sense is either a group of work units which execute simultaneously on the processing elements or a group of work units which form a single schedulable entity.

The units of work are typically grouped at two granularities visible to the user. At the smaller granularity, some number of parallel work units form a single schedulable unit, with the size of the group usually determined by the number of logical processing cores inside a SIMD engine (which may be more than the number of physical cores). At the larger granularity, the aforementioned groups which are executed together on a single SIMD processor are grouped again. In some sense, the architecture is MIMD at the device or higher granularity level, since SIMD processors can execute unique instructions simultaneously; and virtualizing SIMD or SPMD at the SIMD processor or lower granularity level, since instruction execution is overlapped and scheduled on the processing cores.

From reviewing the NVIDIA CUDA Programming Guide[23], the above concepts are clearly seen in NVIDIA GPUs. In a CUDA GPU, the virtualizing SIMD processors are the SMs (Streaming Multiprocessors). Each SM consists of eight physical SP (Scalar Processor) cores executing 32 work units (called threads) in four clock cycles, and all SPs in an SM have access to a shared memory. Groups of 32 work units are called warps (the smaller granularity and smallest schedulable entity), and their execution is scheduled to hide memory latency. The work units are grouped into what NVIDIA calls thread blocks (the larger granularity, inside of which execution is virtualizing SIMD or SPMD) which are distributed to the SMs by some global control logic, and multiple thread blocks can execute on a single SM. Between SMs, divergence in code causes no performance penalty and is effectively MIMD. As work units execute within an SM, only divergence (due to control flow instructions) within a warp is implemented by masking and serialization; divergence between warps is implemented by scheduling from the local control logic.

From reviewing the ATI Stream Computing User Guide[22], the concepts are also seen in ATI GPUs. In a CAL GPU, the virtualizing SIMD processors are called SIMD engines. The SIMD engines are composed of what ATI calls thread processors, with all thread processors executing the same instruction in unison. Work units (again called threads) are grouped into wavefronts (the smaller granularity and smallest schedulable entity), with the size of a wavefront determined by the number of thread processors times 4, since each thread processor can issue 4 instructions in 4 clock cycles. All thread processors within a SIMD engine share a LDS (Local Data Store) shared memory (which is owner-writes) as well as shared registers which can communicate data between wavefronts. The work units executed on the processors are arranged into groups at the software level (the larger granularity, inside of which execution is virtualizing SIMD or SPMD), and multiple wavefronts are overlapped in each SIMD engine to hide memory latency. During execution, only divergence within a wavefront is implemented by thread masking and serialization. Divergence between SIMD engines has no performance penalty, and the execution is effectively MIMD at this granularity.

From the above descriptions, it should be obvious that the results obtained using an NVIDIA GPU are applicable to other GPUs. This is not to say that no differences exist, especially since the next few sections on hardware and performance apply mainly to NVIDIA GPUs. The differences between these architectures, however, are minor, and any impacts they would be expected to cause in the implementation are noted as they arise in the thesis.

Note that the rest of this thesis will use NVIDIA terminology (threads instead of work units, and SMs instead of SIMD processors), since the research utilizes an NVIDIA CUDA GPU.

#### 3.2: The NVIDIA CUDA Architecture

Now, an overview of the NVIDIA CUDA architecture is needed. Figure 3.1 shows a simple overview of hardware used by a CUDA program in an NVIDIA GPU. All NVIDIA GPUs share a similar hardware structure, but may have different clock rates, SM counts, shared memory sizes, etc. Table 3.1 shows some of these differences for the NVIDIA GPUs used in this work.

Figure 3.1: The NVIDIA CUDA Architecture[23]

Table 3.1: Some NVIDIA GPUs and various properties

| GeForce GPU        | 8800 GT[32] | 9800 GT[33]   | 280 GTX[34] |

|--------------------|-------------|---------------|-------------|

| Number of SMs      | 14          | 16            | 30          |

| Number of SPs      | 112         | 128           | 240         |

| Device Global Mem  | 512 MB      | 512 MB – 1 GB | 1 GB        |

| Compute Capability | 1.1         | 1.1           | 1.3         |

| Processor Clock    | 1500 MHz    | 1500 MHz      | 1296 MHz    |

| Memory Clock       | 900 MHz     | 900 MHz       | 1107 MHz    |

As can be seen in Figure 3.1, the device architecture is composed of a collection of virtualizing SIMD processors (the Streaming Multiprocessors, or SMs), all of which share access to a global device memory. Each SM is composed of SIMD processing elements (the Scalar Processors, or SPs) which execute instructions issued by the

instruction unit. Each SP possesses a separate register file, and all SPs in a block share access to a multi-banked shared memory, texture cache, and constant cache. The sizes of the various memories and caches, as well as the register and SP counts, vary with what NVIDIA terms the "compute capability" of the device. Specifications for the various compute capabilities are shown in Table 3.2. Note that the device used for the research in this thesis is a compute-capability 1.0 device, which is the most restrictive of the compute capabilities. This was necessary to guarantee that the results in this thesis are portable.

| 1.0 & 1.1 | 1.2 & 1.3                                                                                                     |

|-----------|---------------------------------------------------------------------------------------------------------------|

| 8         | 8                                                                                                             |

| 64k       | 64k                                                                                                           |

| 16k       | 16k                                                                                                           |

| 8192      | 16384                                                                                                         |

| 8k        | 8k                                                                                                            |

| 6k - 8k   | 6k - 8k                                                                                                       |

| 32        | 32                                                                                                            |

| 512       | 512                                                                                                           |

| 8         | 8                                                                                                             |

| 24        | 32                                                                                                            |

| 768       | 1024                                                                                                          |

|           | 8         64k         16k         8192         8k         6k - 8k         32         512         8         24 |

Table 3.2: Compute Capabilities and their properties[23]

In this system, what NVIDIA calls threads are the smallest unit of work. Each thread executes a copy of the kernel, and groups of threads are scheduled in a SIMD fashion on the SPs inside the individual SMs. More specifically, the eight physical SPs in current CUDA devices appear as 32 logical SPs to the scheduler, and each physical SP executes an instruction from each of four threads in four clock cycles. This appears logically as 32 threads executing one instruction every four clock cycles. A group of 32 threads is called a "warp" in NVIDIA terminology, and each SM overlaps execution of the warps of 32 threads on the SPs in order to hide memory fetch latency.

Warps of threads are grouped into thread blocks (commonly referred to as blocks), and thread blocks are the basic element of virtualization. A single SM may execute many blocks at once (up to a compute-capability defined limit, as shown in Table 3.2), but only if the combined thread count of the blocks does not exceed the SM's limit, and the resource requirements of the blocks can be met. Resource requirements for a block include the amount of shared memory and the number of registers used by the threads in the block, and the compute capability of the device determines the available resources. For example, if an SM will overlap execution of 4 thread blocks, then it must possess at least 4 times the total resources needed by each thread block.

Scheduling parameters (or scaling parameters, since they tightly constrain the number of kernels active at once on a GPU) govern the creation of thread blocks, and are provided by the user when a kernel program is invoked in host CPU code to execute on the GPU hardware. These parameters include the dimensions of a thread block (in threads), the dimensions of the grid (in thread blocks), and the amount of dynamically shared memory allocated per thread block. NVIDIA calls this collection of parameters the "execution configuration" of a kernel. These parameters are often chosen by the user to allow easy mapping of the desired algorithm to the available GPU resources.

If more thread blocks are created by a kernel invocation than can be executed on the GPU's SMs, due either to a lack of resources or to more combined threads than the SMs can execute, some thread blocks are queued to wait. These thread blocks do not execute until another thread block has executed to completion. Lacking provision to save and restore state, there is no yield() or sleep() command which a block can issue to voluntarily de-schedule itself, although one would be extremely useful.

### 3.3: NVIDIA CUDA Performance Considerations

Now that all the fundamentals are established, it is important to discuss the key performance characteristics in the CUDA architecture. These are essentially the points from chapter five of the NVIDIA CUDA Programming Guide[23], and they concern instruction performance and memory performance.

Instruction performance falls loosely into three categories: arithmetic performance, flow-control performance, and memory instruction performance. By examining each, a scale of relative expense should be established in the reader's mind, and this scale is required to understand design decisions described later in this thesis.

The shortest arithmetic instructions execute in four clock cycles, and these include

floating-point add, multiply, multiply-add, integer add, 24-bit integer multiply, bitwise operations, minimum, maximum, comparison, and type-conversion instructions. 32-bit integer multiply executes in 16 clock cycles, and floating-point reciprocal square root executes in 32 clock cycles. Floating-point division executes in 20 or 36 clock cycles (depending on the version used), and some versions of sin, cos, and exponentiation execute in 32 clock cycles. The instructions which are specified with the longest execution time are other versions of sin and cos, tan, and sincos, which may take around 320 clock cycles to execute.

Flow-control instructions are not specified with execution times, and are primarily important in that divergent code can cause serious performance degradation or deadlock. In particular, divergence between warps is not problematic, because it is implemented by scheduling. Within a warp, though, divergence is implemented by masking off processing elements and serializing the branches. The performance penalty can be high in such instances. An example: if a single processing element in each warp wished to execute instructions requiring 10,000 clock cycles, while all other processing elements in the warp would be 10,010 clock cycles. Worse still is the possibility of livelock. If a processing element inside of a flow-control statement which diverged within a warp attempts a blocking operation (such as a spin-lock) while waiting for other processing elements in the warp to signal a result, the result may never arrive due to the masking-off of the processing elements which send it, and the hardware may live-lock until the watchdog timer aborts the kernel execution.

Memory instructions are simple in that they always issue in 4 clock cycles. The problem, as shown next, is the memory latency.

Memory performance in a CUDA GPU is the single most important performance consideration short of outright deadlock. A fetch from global or local memory locations has a 400-600 clock cycle latency, and global memory is not cached. Shared memory accesses which are fully-coalescing and conflict-free (across the banks) have a four-cycle latency which is hidden by the warp-at-a-time scheduling. Similarly, dependency-free register accesses have a four-cycle latency hidden by the scheduling. Texture and constant cache reads are also four-cycle unless the read is a cache miss, and cache misses incur the 400-600 clock cycle global memory latency.

Memory performance can be improved considerably by arranging memory accesses to be coalesced. As described in the NVIDIA CUDA Programming Guide[23], CUDA devices are capable of fetching 32-byte, 64-byte, and 128-byte blocks aligned on 32-byte, 64-byte, and 128-byte boundaries respectively, in single instructions. This occurs only under certain conditions based on the device compute-capability and for each half-warp (group of 16 consecutive threads). For compute-capability 1.0 and 1.1 devices (such as the GeForce 8800 GTS used in this thesis), conditions for coalescing include threads accessing consecutive words in sequence, with each access being a 4-byte or 8-byte object (16-byte object accesses are coalesced into two 128-byte load instructions). It should be noted that coalesced on 4-byte objects, around an order of magnitude higher bandwidth than non-coalesced on 4-byte objects. On compute-capability 1.2 or higher devices, coalescing happens under a much broader set of conditions and is more flexible.

After examining the relative costs of operations, it should be clear that memory accesses are the most critical of the performance considerations. NVIDIA GPUs are high-latency, high-bandwidth devices which rely on computation to hide latency from non-cached global memory, and fast local memory is a scant resource. More specifically, the GeForce 8800GTS, a compute capability 1.0 card, only has 8196 registers and 8196 bytes (2048 words) of shared memory per SIMD processor, as shown in Table 3.2. At 64 threads per block (minimum recommended in the CUDA Programming Guide[23]), this amounts to 128 registers per thread with one block on the SIMD processor and 64 registers per thread with two blocks on the SIMD processor. At the limit of eight blocks per SIMD processor, this amounts to only 16 registers per thread and 256 words of shared memory available to each block. At 256 threads per block, this amounts to 32 registers per thread at one block per SIMD processor, and four registers per thread (along with 256 words of shared memory between the threads) at the maximum of 8 blocks per SIMD processor.

For comparison, the MasPar MP-1, a classical SIMD machine from 1990, had 16k bytes of memory per processing element[35], and this machine was decidedly more

"silicon-challenged" than a current GPU. A more modern comparison could be made with the Cell BE (Broadband Engine), which has 256k per SPE[11]. Given the scarcity of local GPU memory compared to similar architectures, along with the aforementioned high-latency, high-bandwidth nature of the device, extra attention must be paid to local memory usage. Expensive re-computation of intermediate values may be relatively cheap compared to caching. Also, prioritizing coalesced memory accesses over full PE utilization can yield better performance.

#### **Chapter 4: Virtualization Constraints**

One claim of this thesis is that, although there is a virtualization constraint for using message-passing within the GPU, the constraint is actually harmless if the amount of virtualization chosen is already optimal in terms of its interaction model and per-block execution time. More specifically, optimal virtualization is virtualization such that the performance per unit time is nearly as high as possible, and the interaction model between processes is not limited by the choice of the virtualization. This section first describes the ideas of multi-threading and virtualization inside of GPUs, as well as the memory coherence and interaction models. This section next describes a micro-kernel and presents empirical data which suggests that the optimum amount of threading fully populates the GPU's processing resources some integral number of times, and that virtualization beyond that amount yields no measurable benefits and weakens the interaction model. This section concludes by describing the performance benefits reaped by using an optimum amount of threading, focusing on the implications of having a stronger interaction model and a less-awkward coherence model and how these are required by a message-passing implementation executing within a GPU.

### 4.1: Background and Definitions

GPUs have evolved a SIMD-based, multi-threaded execution model which relies heavily on virtualization. Multi-threading makes perfect sense in the context of graphicsprocessing because it allows memory latency to be hidden behind Pixel processing, which increases throughput. More precisely, multi-threading allows data fetches from a slow, non-cached GPU global memory (as discussed in Chapter 2.3) to be hidden behind useful computations by having a thread de-scheduled while waiting for its memory request to complete. Virtualization also makes perfect sense in the context of graphics-processing because most images processed contain more pixels than available processors. A modern HDTV image, for example, has roughly two million pixels, while a current NVIDIA GPU (the GeForce GTX 280) has 240 processor cores, as shown in Table 3.1. Since each pixel can be processed (more or less) independently, large-scale virtualization of the pixels over the available processors has been (and will remain) an obvious performance win. Large-scale virtualization has also created a nice abstraction between the hardware and the images it processes (since drivers can handle the virtualization), and this abstraction has allowed new generations of GPUs to be developed by merely taking an existing architecture and adding more processing pipelines, tweaking the clock speeds, optimizing the core floating-point units, adding hardware features, etc., rather than inventing a new architecture.

The memory coherence or memory consistency model of global memory in NVIDIA GPUs is slightly awkward. Global memory is the only true shared memory for all the processors on the device, but the only real guarantee about global memory is that specific kinds of transactions are performed atomically. This is not referring to just the atomic operations provided by higher compute-capabilities, but also coalesced memory accesses[23]. Unfortunately, the model provides no rules governing the order of writes, when data written becomes available to other processes, or the fairness of the writer scheduling. Here, fairness refers to threads being guaranteed a chance to write their data, and it is possible that one or more threads will never get a chance to write.

Because of these uncertainties, the interaction model of the processes is relatively weak. A process cannot safely wait on another process, because it is possible that the other process may not be able to run due to a lack of resources. For example, imagine that each process wants to contribute an element to a global array, and then wait until another specific process has contributed before continuing. The interaction model does not allow this, because there could be enough processes created so that all the executing processes wait on contributions from processes queued to wait at the software level, and this would obviously cause a live-lock.

#### 4.2: Performance Analysis of Virtualization

The established method for boosting application performance with GPUs is to write kernels with wide parallelism and allow the GPU to virtualize the computations over the available GPU processing elements. For example, in the NVIDIA CUDA Programming Guide[23] developers are informed that using a large number of thread blocks amortizes the overhead from device memory reads and thread synchronizations better than a small number of thread blocks, and that the number of thread blocks is usually dictated by the size of the data being processed, which can greatly exceed the number of processors in the GPU.

There are established rules which govern the choices of multi-threading and virtualization parameters. CUDA developers are instructed to carefully choose the number of threads per block and/or number of blocks to maximally utilize the device resources[23]. In terms of multi-threading, the CUDA programming guide suggests 64 threads per block (twice the size of a warp) as a minimum, and further suggests that 192 or 256 threads per block is a better number[23]. Obviously, these sizes create some integral number of fully-populated warps. In terms of virtualization, the CUDA Programming Guide states that "It is therefore usually better to allow for two or more blocks to be active on each multiprocessor to allow overlap between blocks that wait and blocks that can run," and that "More thread blocks stream in pipeline fashion through the device and amortize overhead even more. The number of blocks per grid should be at least 100 if one wants it to scale to future devices; 1,000 blocks will scale across several generations."[23]. Because there is no clear message stating "how much is enough," this section presents a micro-kernel which is used to test the benefits of large-scale virtualization.

The NVIDIA CUDA Programming Guide[23] suggests a typical processing pattern of <sup>1</sup>)reading data from global device memory into shared memory, <sup>2</sup>)synchronizing all threads in each block to make sure that all global memory entries have been fetched into shared memory, <sup>3</sup>)processing the data in shared memory, <sup>4</sup>)synchronizing all threads in each block to ensure that all processing results are present in shared memory, and <sup>5</sup>) writing the results back to global device memory. Using the above ideas, a very simple, ideal kernel can be constructed which tests the benefits of large-scale virtualization. The

pseudo-code for this kernel is shown in Figure 4.1.

```

float a,b;

int main()

{

float ta,tb;

int i = 10000;

do {

ta += tb * 1.11; tb += ta * 1.11;

ta += tb * 1.11; tb += ta * 1.11;

ta += tb * 1.11; tb += ta * 1.11;

ta += tb * 1.11; tb += ta * 1.11;

ta += tb * 1.11; tb += ta * 1.11;

} while (--i);

a = ta;

b = tb;

}

```

#### *Figure 4.1: Pseudo-code for the micro-benchmark*

Note that this kernel is not intended to mimic a complicated or realistic GPU kernel, because realistic kernels introduce extra factors and lack performance transparency. This kernel is arithmetically intensive, providing 10 floating-point multiply-adds in a loop iterating 10,000 times, which provides roughly 400,000 cycles of arithmetic for the two memory reads and two memory writes performed by each thread. The data is aligned in global device memory so that maximum bandwidth can be utilized, and the code requires a minimal number of registers. Under these minimal conditions, the benefits of virtualization are clearly seen.

Two versions of the kernel are tested below with varying block counts (amounts of virtualization): one with ta and tb in registers, the other with ta and tb in shared memory. Both kernel versions use 256 threads per block (BNPROC is the number of thread blocks). The test GPU is an NVIDIA GeForce 8800 GTS (a compute capability 1.0 card with 12 SMs), and the kernels are executed with varying thread-block counts from 2 blocks to 434 blocks (more than 434 blocks becomes unstable during some tests). After each kernel listing, the average execution time of 10 iterations of the kernel is plotted against the block count. The per-block execution time is then plotted from this data.

Kernel 1, shown in Figure 4.2, performs the operations with the values read into

registers prior to entering the do-while loop and writes the register contents back to global memory before exiting. Both execution time plots are shown following the kernel code, and plots are marked in increments of 24 because this is two times the number of SMs in the test card.

```

#define BNPROC 256

global void

myperf(register volatile float *a, register volatile float *b)

{

register int IPROC = (blockIdx.x * BNPROC) + threadIdx.x;

register float a reg = a[IPROC];

register float b_reg = b[IPROC];

syncthreads();

int i = 10000;

do {

a reg += b reg * 1.11; b reg += a reg * 1.11;

a reg += b reg * 1.11; b reg += a reg * 1.11;

a reg += b reg * 1.11; b reg += a reg * 1.11;

a reg += b reg * 1.11; b reg += a reg * 1.11;

a_reg += b_reg * 1.11; b_reg += a_reg * 1.11;

} while (--i);

a[IPROC] = a reg;

b[IPROC] = b reg;

____syncthreads();

}

```

Figure 4.2: The register micro-benchmark

Figure 4.3: Total execution time of the register micro-benchmark

Per Block Execution Time

Figure 4.4: Per-block execution time of the register micro-benchmark

Figure 4.3 may be surprising in that execution time is obviously a stair-step function for computationally-intensive code looping in registers. Note that the NVIDIA 8800 used in the test has 12 SMs; not surprisingly every time a multiple of 12 blocks is exceeded the execution time "steps". This is because adding that extra block causes one SM to execute another set of kernels while the other 11 SMs are idle. Adding additional blocks populates the idle SMs, which does not cause any increase in execution time. The important idea is simply that the stair-step characteristic comes from populating the SMs unevenly, and therefore the number of blocks should be chosen based on the number of SMs in a device.

Figure 4.4 shows the execution times normalized to the number of blocks. The actual smallest execution time in this chart occurs at 396 blocks (33 blocks/SM) with a time per block of 0.48499 ms. It should be noted that the time per block at 12 blocks (1 block/SM) of 0.4915 ms is still smaller than the time per block at 390 blocks (0.4934 ms), 388 blocks (0.4959 ms), and 386 blocks (0.4981 ms). Moreover, the percent difference between the time at 12 blocks and the time at 396 blocks is only 1.33%.

From the above data, it can clearly be seen that the near-optimal execution time per block is obtained any time the execution configuration runs a multiple of 12 blocks total, which is the same as running an identical number of blocks on every SM or fully populating the device some integral number of times. However, running a large multiple of 12 yields little additional performance benefit over running a small multiple of 12.

Kernel 2, shown in Figure 4.5, performs the same operations as kernel 1, but reads the global data into shared memory, uses pointers in registers to volatile shared memory inside the loop, and writes the shared-memory values back to global memory upon completion. Both execution time plots are shown following the kernel code, and plots are marked in increments of 24 because this is two times the number of SMs in the test card.

```

#define BNPROC 256

typedef struct {

float a s[BNPROC];

float b s[BNPROC];

} my_shared_t;

_global__ void

myperf(register volatile float *a, register volatile float *b)

{

register int IPROC = (blockIdx.x * BNPROC) + threadIdx.x;

extern __shared__ my_shared_t shared[];

register volatile float *a_shr = &((*shared).a_s[IPROC]);

register volatile float *b shr = &((*shared).b s[IPROC]);

*a shr = a[IPROC];

*b shr = b[IPROC];

syncthreads();

int i = 10000;

do {

*a_shr += *b_shr * 1.11; *b_shr += *a_shr * 1.11;

*a shr += *b shr * 1.11; *b shr += *a shr * 1.11;

*a shr += *b shr * 1.11; *b shr += *a shr * 1.11;

*a shr += *b shr * 1.11; *b shr += *a shr * 1.11;

*a_shr += *b_shr * 1.11; *b_shr += *a_shr * 1.11;

} while (--i);

syncthreads();

a[IPROC] = *a shr;

b[IPROC] = *b shr;

____syncthreads();

}

```

*Figure 4.5: The shared-memory micro-benchmark*

#### Total Execution Time

Figure 4.6: Total execution time of the shared-memory micro-benchmark

Figure 4.7: Per-block execution time of the shared-memory micro-benchmark

Figure 4.6 shows the same stair-step function for execution time as Figure 4.3. Since conflict-free shared memory accesses are as fast as register accesses in CUDA[23], it is expected that the shared memory behaves in a similar manner to the register file with regards to scheduling behavior. Note that the kernel does not attempt to stride shared memory reads or prevent bank conflicts, since the presence or absence of such conflicts should not change the scheduling behavior of the kernels. While the scheduling unit in an SM may swap blocks to cover global memory latency, the overhead of such a swap would likely swamp a shared-memory conflict completely.

As mentioned before, the NVIDIA 8800 used in the test has 12 SMs; not surprisingly every time a multiple of 12 blocks is exceeded the execution time "steps". This is again because adding that extra block causes one SM to execute another set of kernels while the other 11 SMs are idle. Adding additional blocks populates the idle SMs, which does not cause any increase in execution time. The important idea is again that the stair-step characteristic comes from populating the SMs unevenly, and therefore the number of blocks should be chosen based on the number of SMs in a device.

Figure 4.7 shows the execution time normalized to the number of blocks. The smallest execution time occurs at 36 blocks (3 blocks/SM) with a time per block of 1.06187 ms. This can be compared to the largest execution time at a multiple of 12 blocks, which is 24 blocks at a time per block of 1.075 ms. The percent difference is 1.31%, and again the worst choice of a multiple of 12 (24 blocks at 1.075 ms/block) is better than a naive choice of a large number of blocks (424 blocks at 1.0838 ms/block or 426 blocks at 1.079 ms/block).

Again, the data clearly shows that the near-optimal execution time per block is obtained any time the execution configuration runs a multiple of 12 blocks total, which is the same as fully populating the device some integral number of times. As before, running a large multiple of 12 is not necessary to get nearly-optimal execution time per block, and does not appear to provide much benefit.

At this point, it is clear that running a number of thread blocks which is an integer multiple of the number of SMs is required for near-optimal performance. But at what point does more virtualization result in less performance? In terms of execution time, there appears to be no point where adding another 12 thread blocks results in noticeable performance loss. In terms of the interaction model, however, there is a very noticeable performance loss as soon as any blocks are queued to wait.

In the introductory material of this section, the interaction model of the CUDA GPU was described as relatively weak, primarily because processes cannot wait on each other due to the uncertainty about what processes are currently executing and the awkward global memory coherence model. If it is known that all thread blocks are executing, however, then blocks can wait on each other by polling, and be assured that a write by one process will eventually be visible by all other processes. This constitutes a much stronger interaction model, and is possible if the virtualization is kept within the limits of what can execute concurrently on a given device. This would be dictated by the number of SMs in the device, the number of active blocks per SM or threads per SM supported by the device, and the per-block resource usage.

While the number of SMs, threads-per-SM constraint, and blocks-per-SM constraint are each device-dependent, the per-thread resource usage is programdependent. The per-thread resource utilization can be calculated prior to execution by using the built-in nvcc compiler option --ptxas-options=-v to determine register and shared memory usage, and resource usage can also be partially controlled by using the compiler option --maxrregcount *amount*, where *amount* is the maximum number of registers a GPU function can use[23]. By using this compiler output alongside the information from NVIDIA's deviceQuery program provided with the default CUDA SDK installation (the compute capability information and number of SMs in the installed devices), scaling parameters which populate the device without queuing any thread blocks to wait can be automatically predicted for a particular kernel.

In this sense, GPU code could be autonomously optimized for a strong interaction model and nearly-best execution time on new GPU hardware by recompilation or dynamic hardware detection at runtime. This would be similar to ATLAS[36], where the software tests various implementations of linear algebra routines and then uses the results to seed a search for the best implementation on a specific machine. In ATLAS, a large time investment at compile-time pays a large performance dividend at run-time. GPU code can also be automatically tuned at compile-time to use optimal virtualization.

#### 4.3: Optimal Virtualization and the MPI Constraints

Optimal virtualization obviously boasts a performance boost over a poor choice of virtualization (a non-multiple of the number of SMs) in terms of execution time per operation, as shown above. The more important benefit, though, is that the stronger interaction model provided by the virtualization allows communication within a GPU.

Since processes are guaranteed to eventually see values written by other processes, inter-process communication and inter-process synchronization become possible without the need for the traditional kernel stop and restart. Communication can be provided by simple data structures declared volatile in global device memory, or by a more advanced mechanism such as message-passing. The benefit of the latter is that it completely hides the remaining shared-memory semantics issues associated with global memory, mainly the non-determinism associated with writes, since there is no guaranteed ordering between processes. Synchronization can be provided by an established single-writer, multiple-reader algorithm, originally proposed and utilized in the SHMAPERS library[37] and adapted to an NVIDIA CUDA GPU within this research group.

There is also a performance impact of the new capabilities: the kernel can continue execution. NVIDIA has stated that kernel launches have low overhead and should be used as global thread synchronization points[23]. The problem is that the hardware overhead may be low, but the software overhead for a kernel stop and restart is not. In the CUDA system, no local processor state is maintained across kernel invocations, so data must be written to global memory at the end of one invocation, and then read from global memory at the beginning of the next invocation[23]. Unpublished experiments conducted within this research group have shown that restoring state from global memory quickly becomes prohibitively expensive, partially due to the lack of computation available to cover the latency from the extra memory reads. In BGSP, the researchers were content with a 4x performance penalty for having to include save and restore state mechanisms, even when not in use[30].

In addition to the cost of restoring state after synchronization, the stop/restart model complicates programming. Currently, if communication is required, then data must either be copied to the host between kernels and altered appropriately before being copied back, or another kernel must perform the communications using the global memory between invocations. Any code requiring multiple synchronizations must be rewritten into separate kernels, with the host providing the glue logic to invoke the correct kernels as necessary, and synchronizations nested within control structures exacerbate the problem of restoring state and continuing. One simple example of this would be an iterative solver which is looping through a data structure and needs to check against a quality metric at the end of a set of iterations.

## **Chapter 5: The MPI Implementation**

The primary claim of this thesis is that the message-passing programming model can be conceptually cleaner than the currently ubiquitous data-parallel model by hiding rather than dealing with the quirks of current shared-memory environments. This section first provides a brief introduction to MPI (the Message-Passing Interface), which is the standard used in this research to implement the message-passing model on the GPU. It then describes which parts of the standard are actually implemented and what design considerations are involved in the proof-of-concept implementation. Details are also provided on the key point-to-point communication function implementations. А performance comparison to the native NVIDIA CUDA code on a sample algorithm which computes the value of pi in parallel is then presented for the point-to-point communication functions. This section then provides the same details and performance analysis for the key collective communication function implementations. Some of the other MPI functions which were implemented are briefly discussed. This section concludes by describing the key benefits of the message-passing model compared to the data-parallel model, as demonstrated by the proof-of-concept MPI implementation and the example implementations of the sample algorithm.

### 5.1: Introduction to the Message-Passing Interface

MPI, the Message-Passing Interface, is a parallel-programming standard which provides a message-passing library interface specification[1]. That is, MPI provides a detailed specification of the various functions and data structures which are externally available in a message-passing library implementation which conforms to the standard. The standard does not specify the implementation details under the interface, and so MPI can be implemented on a variety of hardware architectures. The main benefit of MPI is therefore the ability to easily write portable code utilizing the message-passing model in C, C++, or Fortran.

As seen in the MPI standard[1], MPI specifies several general categories of functionality which contain the various MPI functions. These include point-to-point communication, data-type creation and management, collective or aggregate operations, process group management, communication context management, process topology descriptions, environmental management and environmental query, info object management, process creation and management, one-sided communication, external interfaces management, parallel file I/O, and a profiling interface[1]. Each category of functionality contains both the functions, whose interfaces are defined in C, C++, and Fortran, and any data-types or constants which must be exposed to the user to interact with the functions.

### 5.2: Design Philosophies and Restrictions

Since the goal of this research is to provide a proof-of-concept MPI implementation rather than a full one, only some functions from some of the categories above are actually implemented. The emphasis is on proving the viability and benefits of the message-passing model, so point-to-point communications and aggregate operations are the main focus of this work. In addition, a handful of data-type creation and management, environmental management and environmental query, communication context management, and one-sided communications functions are implemented.

The functions implemented are chosen because they represent a large portion of what can be done with MPI, and they conceptually cover what is most often done with MPI. The functions are not just the functions which naturally fit a GPU's programming model and architecture; they are a representative set of functions which should demonstrate the benefits of MPI within a GPU in a relatively complete fashion. The functions implemented are also similar to those in other subset implementations such as AFMPI[38], where the goal is to prove the viability and benefits of MPI on unusual hardware.

The following sections describe the implementation in greater detail, but there are a handful of overarching restrictions which mandate design decisions affecting the entire implementation. Each of these restrictions is described briefly here, and then in greater detail below. The first restriction is the aliasing of the hierarchical groups inside a GPU, which refers to the interdependence of threads, warps, and thread blocks within an NVIDIA CUDA GPU. This restriction affects the choice of what constitutes an MPI process in the implementation. The second restriction is the inability to read from or write to an SM's local shared memory, and this restriction forces all communication to travel through slow global memory. The third restriction is the scarcity of local resources, and this restriction forces some potential optimizations within thread blocks to be ignored and forces a simple name-space for all MPI processes. The fourth restriction forces the alteration of some MPI semantics to avoid potential live-locked, and this restriction causes all operations to be naturally word-oriented, and prevents some MPI interfaces involving double-precision floating-point numbers from being implemented. Each of these ideas is described in more detail below.

The first restriction, the interconnection of the hierarchical groups inside a GPU, is simply referring to the fact that thread blocks are aliases for groups of warps, and warps are aliases for groups of threads. A single thread never exists if it does not belong to a warp, and that warp never exists if it does not belong to a thread block. This is different than a cluster of workstations, for example, where a single workstation can exist without being part of a cluster.

The implications of this restriction become clear when deciding what exactly constitutes an MPI process or rank. In DCGN[29], Stuart and Davis discuss the problems with choosing either an entire kernel or single threads as a rank, noting that each mapping can have benefits. In this research, though, the focus is on communication within a GPU, rather than communication across GPUs. Within any GPU, the basic blocks mentioned in chapter 3.2 are present. In the NVIDIA CUDA GPU used here, the obvious choice for what constitutes a rank or process would be a thread, a warp, or a thread block. This research chooses to implement processes as threads, since threads are the smallest units performing work inside a GPU. This has the benefit of making kernel code look relatively normal (rather than always collective across warps or thread blocks), and

keeping the programming model easy to use, as opposed to forcing the user to write vector-oriented code for warps or thread blocks. The obvious penalty for this choice is that all potential SIMD divergence issue are exposed by this choice and must be taken into consideration (this will be illustrated in the test algorithm implementations). The future work for this research includes examining other MPI implementations with processes mapped onto warps and thread blocks. Warps could hide SIMD divergence issues while still providing a low-level, vector-oriented programming model. Thread blocks could hide all scheduling issues when optimally virtualized and provide a MIMD programming model, but at the cost of load-balancing issues and a more complex vector model.

The second restriction involves the limitations on which thread can write to a SIMD processor's local shared memory. Only a thread which is executing in a thread block on a given SIMD processor may read and write to the shared memory allocated to the thread block locally in that SIMD processor. A thread cannot write to shared memory in a thread block executing on another SIMD processor, and cannot write to staticallyallocated local shared memory of another thread block executing on the same SIMD processor (a pointer to dynamically-allocated shared memory created by the host can be shared among thread blocks on a SIMD processor, but the operations on it must be synchronized by a global barrier synchronization of all processes, since the syncthreads () command only synchronizes threads within a thread block). This forces communication to move through device global memory (optimizations for threads in the same thread block are not used because of the scarcity of local resources, described in the next section). For send and receive operations, a send may specify a source in shared memory and a receive may specify a destination in a different shared memory, but the message must move through global memory at some point. This also constrains onesided communication to targets in global memory or in the shared memory of the thread block of the invoking process.

The third restriction, the scarcity of local resources, refers to the relatively small amounts of fast, local resources in current GPUs. On the NVIDIA GPU, these resources include the registers and shared memory, as described in chapter 3.2.

There are two design decisions caused by the restriction: a single-context, flat

process name-space and a lack of optimizations for threads communicating within a thread block. MPI specifies a range of functions for subdividing the collection of all processes into subgroups and for managing unique communication contexts within groups and subgroups. Such functions require that information about the various groups and contexts be available to each process, but this implies that something must be stored for each process to identify its contexts and groups. Given the already-limited amount of local shared memory and registers, and given that the subgroups and communicators are not essential for proving the viability and conceptual cleanliness of the message-passing model, this research chooses not to implement the subgroup and communication context functionality and instead uses a single communicator: MPI COMM WORLD. The lack of local resources also limits potential optimizations for threads communicating or working within a thread block. As described in the previous section, threads communicating within a thread block could benefit from passing messages through shared memory. However, this optimization could easily consume all the shared-memory resources and leave none for user computation. As an example, if each of 256 threads in a thread block wanted to send 1 single-precision float to the next process, this would require 255\*4 =1020 bytes of shared memory (1/8 the total available if only one thread block is executing on the SIMD processor) for a single buffered send operation.

the ease with which the GPU can be accidentally live-locked, and this restriction forces

The fourth restriction is the the ease with which the GPU can be accidentally livelocked. Because MPI requires some operations to be semantically blocking, there is always the possibility of spin-locking one process while waiting on another which will not be scheduled because of the fairness issues described in chapter 4.1. Note that the choice of a process mapping does not affect this; at optimal virtualization there are still usually more blocks than SMs, and nearly always more threads than physical processors. The mapping of a process to a thread only makes it simpler to hang the hardware via SIMD enable masking used within a warp. Note that the NVIDIA GPU does not support any interrupt mechanism to recover from a lock, the only supported mechanism is a watchdog timer which terminates the kernel invocation after about 10 seconds. When the watchdog timer activates, no local state is preserved and the results of any pending memory writes are undefined. The live-lock restriction implies that not all blocking operations can be trivially implemented. This research handles this restriction by obeying the semantics of MPI blocking operations without actually blocking where possible. An example of this is MPI\_Send, which always buffers send data to a system buffer. If buffer space is unavailable, MPI\_Send returns an error (MPI\_NO\_SPACE) rather than blocking. This also relates back to the choice of a process mapping: a true blocking send and receive pair could never work at the thread granularity due to the enable masking used to implement divergence. Some MPI interfaces, such as MPI\_Recv and MPI\_Barrier, must block. As long as the user kernel is written correctly, though, these cannot actually lock the device. The restrictions for using interfaces are described in the following sections alongside the actual interfaces.

The fifth and final restriction is the orientation of hardware to 32-bit operations. Some GPUs still lack support for double-precision, including the compute-capability 1.0 GeForce 8800GTS used in this research. These devices may silently demote doubleprecision floating-point numbers and computations to single-precision equivalents[23]. Additionally, the cost for utilizing the support tends to be high compared to the native single-precision support for which GPUs became known.

Because of this restriction, this research attempts to utilize 32-bit words wherever possible. All data copy routines operate on 32-bit words, and shorter or longer data-types (including double-precision floating-point) are not supported in computation functions such as reduction. Support for double-precision floating-point could potentially be emulated using pairs of single-precision floating point numbers, as suggested by Dietz[39], but this optimization is beyond the scope of proving the viability and benefits of MPI within a GPU.

Now that the design philosophies and restrictions have been explained, the next sections will describe the important interfaces in detail. There are a total of 28 functions in the proof-of-concept implementation, but only the key ones are explained in detail in their respective sections below. There are 7 point-to-point communication interfaces implemented: MPI\_Send, MPI\_Recv, MPI\_Get\_count, MPI\_Iprobe, MPI\_Probe, MPI\_Sendrecv, and MPI\_Sendrecv\_replace. There are 8 collective communication interfaces implemented: MPI\_Sendrecv, MPI\_Bcast,

MPI\_Gather, MPI\_Scatter, MPI\_Allgather, MPI\_Alltoall, MPI\_Reduce, and MPI\_Allreduce. There are 3 data-type management interfaces implemented: MPI\_Pack, MPI\_Unpack, and MPI\_Pack\_size. There are 2 communication context management interfaces implemented: MPI\_Comm\_size and MPI\_Comm\_rank. There are 5 one-sided communication interfaces implemented: MPI\_Win\_create, MPI\_Win\_free, MPI\_Put, MPI\_Get, and MPI\_Win\_fence. Finally, there are 3 environmental management and inquiry interfaces implemented: MPI\_Get\_version, MPI\_Init, and MPI\_Finalize.

### 5.3: The Point-to-Point Communication Interfaces

Point-to-point communications are perhaps the quintessential message-passing operations. This section will focus on the send and receive implementations by describing the general point-to-point model, showing pseudo-code for the send and receive operations, and explaining each operation thoroughly. Potential performance improvements are also discussed.

The general model for point-to-point communication inside the GPU is that messages and envelopes are buffered in global memory by the process which sends the message. The buffer is a system data structure (described later in this section), and there is a static limit on the number of buffered messages and the size of each message. The receive operation searches in the buffer of the source it intends to read from, blocking until it finds a matching envelope and message. Once the receive reads the message, it marks the send buffer as read and returns. To better understand these steps, MPI\_Send and MPI Recv are each examined in detail below.

The prototype for MPI Send is shown in Figure 5.1.