University of Kentucky UKnowledge

Theses and Dissertations--Electrical and Computer Engineering

**Electrical and Computer Engineering**

2012

# Feedback Control for Electron Beam Lithography

Yugu Yang University of Kentucky, yuguyang@gmail.com

Right click to open a feedback form in a new tab to let us know how this document benefits you.

#### **Recommended Citation**

Yang, Yugu, "Feedback Control for Electron Beam Lithography" (2012). *Theses and Dissertations--Electrical and Computer Engineering*. 9. https://uknowledge.uky.edu/ece\_etds/9

This Doctoral Dissertation is brought to you for free and open access by the Electrical and Computer Engineering at UKnowledge. It has been accepted for inclusion in Theses and Dissertations--Electrical and Computer Engineering by an authorized administrator of UKnowledge. For more information, please contact UKnowledge@lsv.uky.edu.

### STUDENT AGREEMENT:

I represent that my thesis or dissertation and abstract are my original work. Proper attribution has been given to all outside sources. I understand that I am solely responsible for obtaining any needed copyright permissions. I have obtained and attached hereto needed written permission statements(s) from the owner(s) of each third-party copyrighted matter to be included in my work, allowing electronic distribution (if such use is not permitted by the fair use doctrine).

I hereby grant to The University of Kentucky and its agents the non-exclusive license to archive and make accessible my work in whole or in part in all forms of media, now or hereafter known. I agree that the document mentioned above may be made available immediately for worldwide access unless a preapproved embargo applies.

I retain all other ownership rights to the copyright of my work. I also retain the right to use in future works (such as articles or books) all or part of my work. I understand that I am free to register the copyright to my work.

### **REVIEW, APPROVAL AND ACCEPTANCE**

The document mentioned above has been reviewed and accepted by the student's advisor, on behalf of the advisory committee, and by the Director of Graduate Studies (DGS), on behalf of the program; we verify that this is the final, approved version of the student's dissertation including all changes required by the advisory committee. The undersigned agree to abide by the statements above.

Yugu Yang, Student Dr. J. Todd Hastings, Major Professor Dr. Zhi David Chen, Director of Graduate Studies

### FEEDBACK CONTROL FOR ELECTRON BEAM LITHOGRAPHY

DISSERTATION

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the College of Engineering at the University of Kentucky

> By Yugu Yang Lexington, Kentucky

Director: Dr. J. Todd Hastings, Associate professor of Electrical and Computer Engineering Lexington, Kentucky 2012

Copyright<sup>©</sup> Yugu Yang 2012

#### ABSTRACT OF DISSERTATION

#### FEEDBACK CONTROL FOR ELECTRON BEAM LITHOGRAPHY

Scanning-electron-beam lithography (SEBL) is the primary technology to generate arbitrary features at the nano-scale. However, pattern placement accuracy still remains poor compared to its resolution due to the open-loop nature of SEBL systems. Vibration, stray electromagnetic fields, deflection distortion and hysteresis, substrate charging, and other factors prevent the electron-beam from reaching its target position and one has no way to determine the actual beam position during patterning with conventional systems. To improve the pattern placement accuracy, spatial-phase-locked electron-beam lithography (SPLEBL) provides feedback control of electron-beam position by monitoring the secondary electron signal from electron-transparent fiducial grids on the substrate. While scanning the electron beam over the fiducial grids, the phase of the grid signal is analyzed to estimate the electron-beam position error; then the estimates are sent back to beam deflection system to correct the position error. In this way, closed-loop control is provided to ensure pattern placement accuracy. The implementation of spatial-phase-locking on high speed field-programmable gate array (FPGA) provides a low-cost method to create a nano-manufacturing platform with 1 nm precision and significantly improved throughput.

Shot-to-shot, or pixel-to-pixel, dose variation during EBL is a significant practical and fundamental problem. Dose variations associated with charging, electron source instability, optical system drift, and ultimately shot noise in the beam itself conspire to increase critical dimension variability and line width roughness and to limit the throughput. It would be an important improvement to e-beam patterning technology if real-time feedback control of electron-dose were provided to improve pattern quality and throughput even beyond the shot noise limit. A novel approach is proposed in this document to achieve the real-time dose control based on the measurement of electron arrival at the sample to be patterned, rather than from the source or another point in the electron-optical system. A dose control algorithm, implementation on FPGA, and initial experiment results for the real-time feedback dose control on the e-beam patterning tool is also presented.

KEYWORDS: Electron Beam Lithography, feedback control, pattern placement error, dose variation

Author's signature: Yugu Yang

Date: September 26, 2012

## FEEDBACK CONTROL FOR ELECTRON BEAM LITHOGRAPHY

By Yugu Yang

Director of Dissertation: J. Todd Hastings

Director of Graduate Studies: Zhi David Chen

Date: September 26, 2012

To my parents.

#### ACKNOWLEDGMENTS

I cannot imagine completing this thesis without the guidance and encouragement from my adviser, Professor Todd Hastings. His endless enthusiasm has always been inspirational to me, and his constructive suggestions with regard to technical issues and research methods have helped me overcome countless difficulties through this work. His willingness to give his time so generously, to either troubleshooting or to proofreading this and many other documents, has been very much appreciated. I consider myself extraordinarily lucky and privileged to be his student and to have had the opportunity to work in his lab.

It has been a great experience to work with the members of UK's Center for Nanoscale Science and Engineering. Dr. Chuck May has provided many useful insights into developing recipes for fabricating gratings. I'd also like to thank him for acquiring the PEK-130A6 photoresist for short wavelength lithography. Brian Wajdyk taught me how to use most the instruments necessary for the successful completion of this work. His diligence in maintaining the equipment has made this process a smooth one.

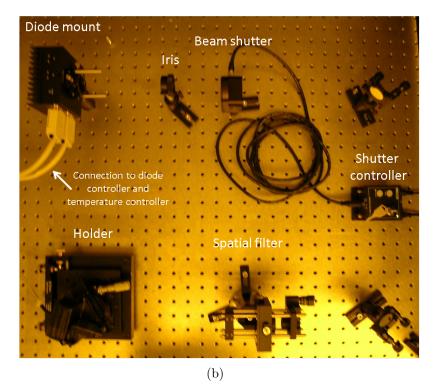

I've been fortunate to work alongside many talented people in our group. Dr. Chandan Samantaray laid the foundations of the interference lithography setup, which accelerated the process of adapting it to my project. Dr. Eugene Donev helped me develop and improve my skills at aligning optics. I also had many productive discussions with him concerning electron beam lithography. Last but not least, Neha Nehru has been a great friend, with whom I could share my experiences as a graduate student, both good and bad.

I am very grateful to my parents for their unconditional support and love. Their influence has carried me through the toughest moments in the past years. I don't

know how to thank my loving husband Donnie Keathley for being patient and understanding, and helping me maintain a positive outlook.

Finally, I'd like to thank the National Science Foundation for supporting the work presented in this dissertation.

## TABLE OF CONTENTS

| Acknow    | ledgments                                                                      | iii  |

|-----------|--------------------------------------------------------------------------------|------|

| List of 7 | Tables                                                                         | viii |

| List of I | Figures                                                                        | ix   |

| Chapter   | 1 Introduction                                                                 | 1    |

| 1.1       | Electron Beam Lithography Overview                                             | 4    |

|           | 1.1.1 Components of Electron Beam Lithogaphy System                            | 5    |

|           | 1.1.2 Exposure Strategy                                                        | 8    |

|           | 1.1.3 Electron Resist Interactions                                             | 10   |

| 1.2       | Pattern Placement Errors                                                       | 13   |

| 1.3       | Spatial Phase Locked Electron Beam Lithography                                 | 13   |

| 1.4       | Shot Noise and Dose Variation                                                  | 16   |

| 1.5       | Exposure Dose control for Electron Beam Lithography                            | 17   |

| Chapter   | 2 Fiducial Grid and Interference Lithography                                   | 19   |

| 2.1       | Fiducial Grid                                                                  | 19   |

| 2.2       | Interference Lithography Overview                                              | 21   |

| 2.3       | Implementation of interference lithography at UK                               | 25   |

| 2.4       | Lithography Experiment                                                         | 28   |

|           | 2.4.1 Patterning with 266 nm wavelength laser                                  | 28   |

|           | 2.4.2 Patterning with 405 nm wavelength laser                                  | 30   |

| Chapter   | 3 Spatial Phase Locking for Vector-scan Electron Beam Lithography              | 34   |

| 3.1       | Phase Estimation from Discrete Signal                                          | 34   |

| 3.2       | Vector-scan Spatial-phase Locking Algorithm                                    | 37   |

| 3.3       | Simulation of Spatial-phase Estimation for Vector-scan System                  | 40   |

| 3.4       | Experimental Verification of Vector-scan Spatial Phase Estimation              | 45   |

| Chapter   | 4 Implementation of Vector-scan Spatial-phase Locking on Field Pro-            |      |

| -         | grammable Gate Array                                                           | 51   |

| 4.1       | Hardware for Implementation                                                    | 52   |

| 4.2       | Digital Signal Processing (DSP) Design for Spatial-Phase Estimation            |      |

|           | Algorithm                                                                      | 54   |

|           | 4.2.1 Algorithm Translation into DSP System Using System Generator             | 54   |

|           | 4.2.2 Top-level Hardware Design Using Hardware Description Lan-                |      |

|           | $guage (HDL)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 63   |

|           | 4.2.3 Experiment Verification of DSP Design Functionality                      | 64   |

| 4.3       | FPGA Implementation of Pattern Generation                                      | 69   |

| 4.4       | Memory Configuration for Distortion Correction                                 | 75   |

|                                           | <ul><li>4.4.1 HDL Design Entity for Memory Access</li></ul>           | 77<br>81          |

|-------------------------------------------|-----------------------------------------------------------------------|-------------------|

| Chapter                                   | 5 Real-time Electron Beam Position Estimation                         | 89                |

| 5.1                                       | Analysis of Fiducial Grid                                             | 89                |

| 5.2                                       | Field Distortion Correction                                           | 92                |

| 5.3                                       | Loop Filter                                                           | 103               |

| Chapter                                   |                                                                       | 109               |

| 6.1                                       | 0                                                                     | 109               |

| 6.2                                       | Light Detection and Collection                                        | 111               |

| 6.3                                       | 1 1                                                                   | 113               |

| $\begin{array}{c} 6.4 \\ 6.5 \end{array}$ | 1 0                                                                   | $\frac{113}{118}$ |

| 0.0                                       | 1                                                                     | 118               |

|                                           | *                                                                     | 110               |

|                                           |                                                                       | 120               |

| Chapter                                   | 7 Conclusions                                                         | 129               |

| Append                                    | ix A DSP Designs in System Generator                                  | 132               |

|                                           | Figure 4.2 Low Level Schematics of Subsystem and M-function           |                   |

|                                           | 0                                                                     | 132               |

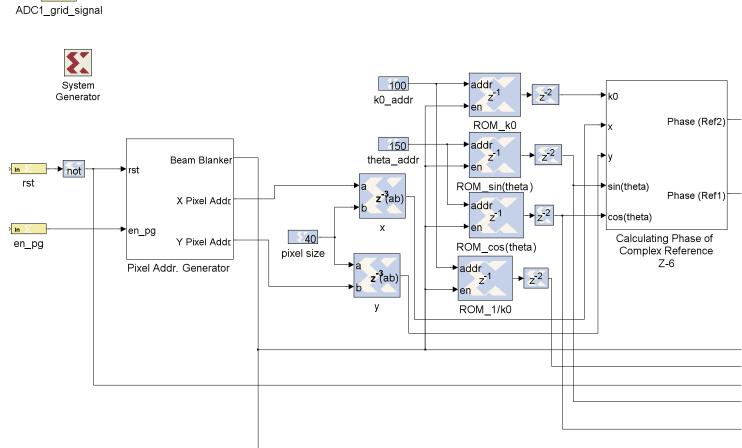

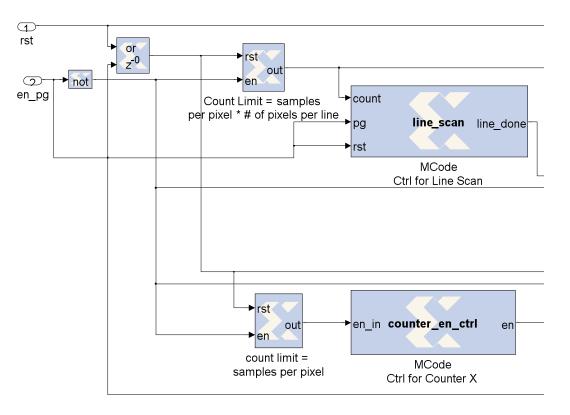

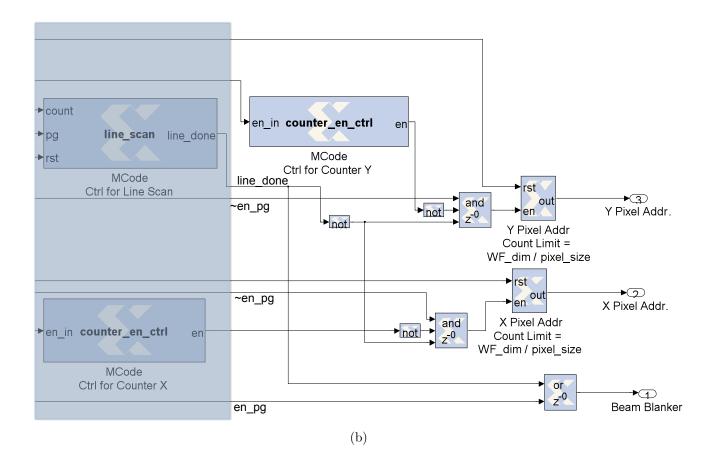

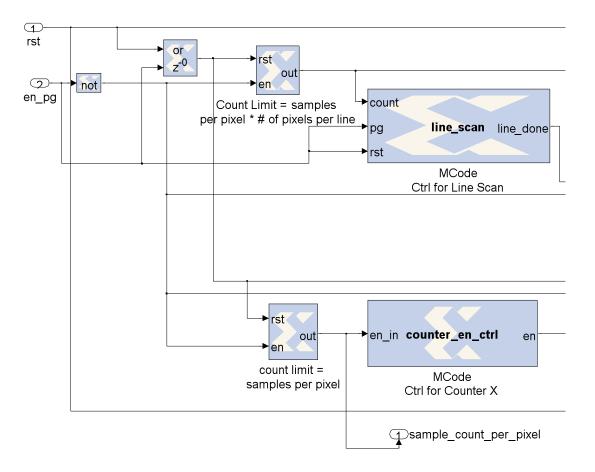

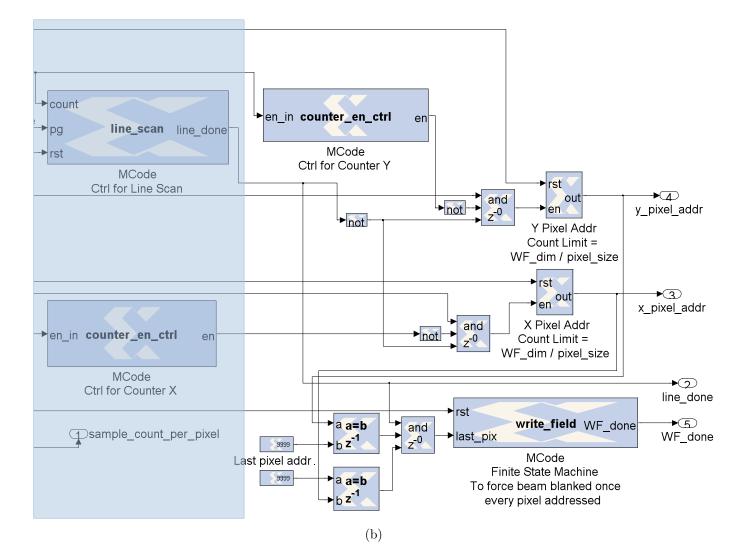

|                                           | A.1.1 Pixel Address Generator Subsystem                               | 132               |

|                                           | A.1.1.1 M-function for "counter_en_ctrl" block                        | 132               |

|                                           | A.1.1.2 M-function for "line_scan" block                              | 132               |

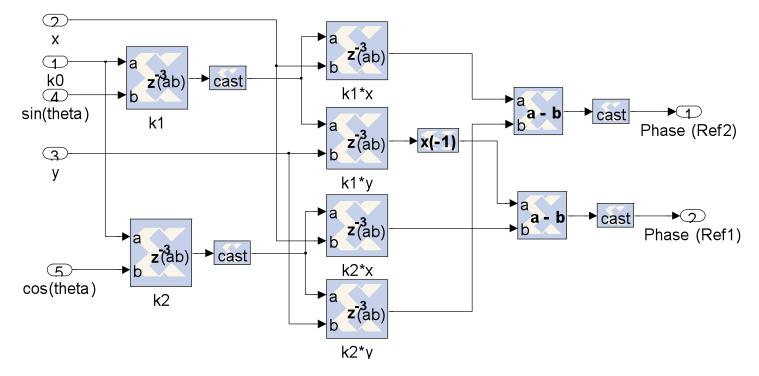

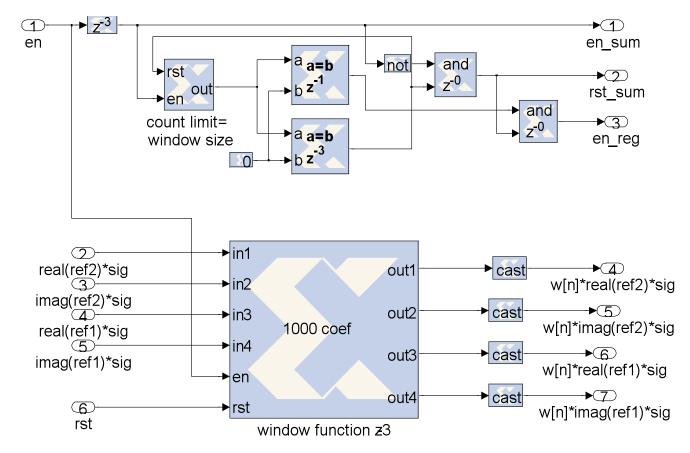

|                                           | A.1.2 Subsystem for Calculating Phase of Complex Reference            | 136               |

|                                           | A.1.3 Subsystem for Reflecting Phase to Interval $[-\pi, \pi]$        | 138               |

|                                           | A.1.4 Subsystem for Calculating Position Error                        | 141               |

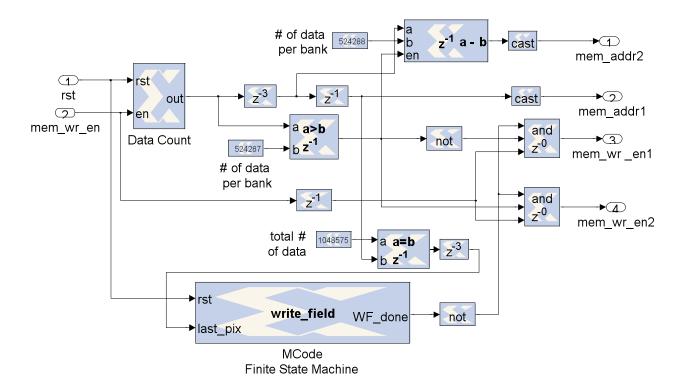

| A.2                                       | Figure 4.14 Low Level Schematics of Subsystem and M-function          |                   |

|                                           |                                                                       | 143               |

|                                           |                                                                       | 143               |

|                                           | A.2.1.1 M-function script for "accum_sample" block $\ldots$ .         | 143               |

|                                           | A.2.2 Subsystem for Generating Pixel Address with Write Field Control |                   |

|                                           | A.2.2.1 M-function script for "write_field" block                     | 146               |

|                                           |                                                                       | 149               |

| A.3                                       |                                                                       | 151               |

| A.4                                       | Figure 5.8 Subsystem of "Controlled n-tap MAC FIR Filter" and         |                   |

|                                           | - •                                                                   | 154               |

|                                           | · · ·                                                                 | 154               |

|                                           | A.4.2 M-function Script for "gen_en_f" Block                          | 156               |

| A.5                                       | Figure 6.4M-function Script for "DoseCtrl_st" Block                   | 158               |

| Append                                    | ix B HDL Design Entity                                                | 160               |

| B.1                                       |                                                                       | 160               |

| B.2                                       | HDL Design for SPL on Virtex-4 User FPGA                              | 162               |

| B.3 HDL Design for communication between Memory and Host Computer                                                                         | 183 |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Appendix C DIMEScript Code                                                                                                                | 194 |

| <ul> <li>C.1 DIMEScript Code for Loading Estimation Parameters and Distortion<br/>Correction Coefficients to Virtex-4 User FPGA</li></ul> |     |

| Bibliography                                                                                                                              | 203 |

| Vita                                                                                                                                      | 211 |

## LIST OF TABLES

| 5.1 | 10-term correction coefficients for higher-order field distortion calculated |     |

|-----|------------------------------------------------------------------------------|-----|

|     | from the estimated position errors as plotted in Figure 5.5.                 | 101 |

| 5.2 | Correction coefficients for 1st-order field distortion calculated from esti- |     |

|     | mated position errors as plotted in Figure 5.5.                              | 101 |

| 5.3 | Correction coefficients for 1st-order field distortion calculated from posi- |     |

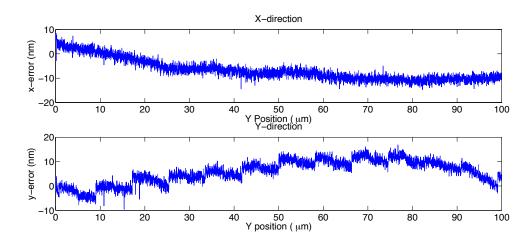

|     | tion errors as plotted in Figure 5.9.                                        | 106 |

## LIST OF FIGURES

| 1.1 | The cross section of an NMOS transistor fabricated by planar technology<br>on the surface of a thin layer of semicondct substrate.                                                                                                            | 2        |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2 | Schematic of the scanning electron-beam lithography system with major                                                                                                                                                                         |          |

| 1.3 | components                                                                                                                                                                                                                                    | 5<br>9   |

| 1.4 | In vector-scan system, the beam is only deflected to where pattern is<br>located, and the stage is fixed while the e-beam is scanning in the write                                                                                            | 10       |

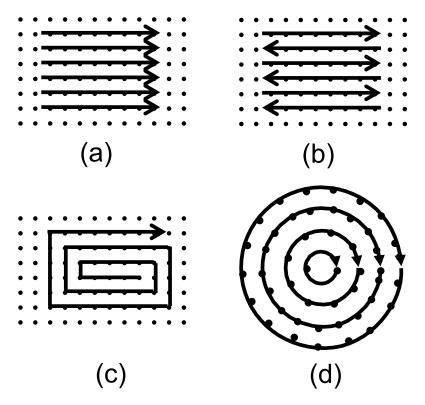

| 1.5 | filed. Only the flyback filling method is demonstrated in the schematics.<br>Filling method used in vector-scan system. (a) Flyback. (b) Meander. (c)<br>Spiral. (d) Circular.                                                                | 10<br>11 |

| 1.6 | Illustration of two types of pattern placement errors.                                                                                                                                                                                        | 14       |

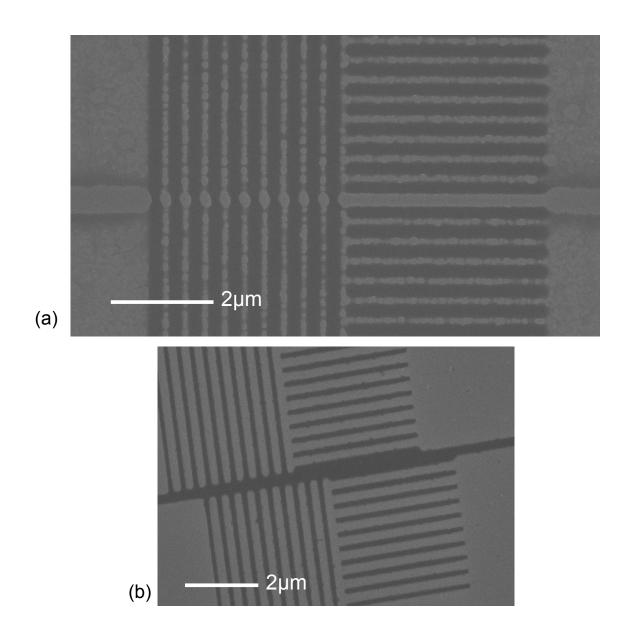

| 1.7 | Stitching errors at the write field boundary observed in the experiment.<br>(a) Bulges at the boundary due to overlapped exposure. (b) Discontinuity<br>and offset at the field boundary.                                                     | 15       |

| 1.8 | Spatial-phase-locked electron-beam lithography (SPLEBL) provides feed-<br>back control of pattern placement by estimating the beam position error<br>using detected secondary electron signal from an electron-transparent fidu-<br>cial grid | 16       |

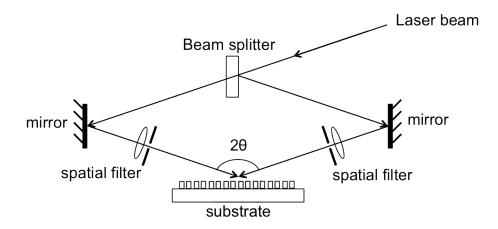

| 2.1 | Schematics of interference lithography in Mach-Zehnder style. The laser<br>beam is split into two arms which ideally should be symmetrical about an<br>axis normal to the substrate                                                           | 22       |

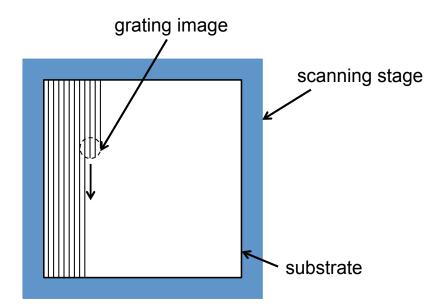

| 2.2 | Schematics of scanning beam interference lithography. The long range<br>fringes are formed by moving the stage under the interference image, and<br>the adjacent lines are overlapped by integer number of fringe periods to                  | 23       |

| 2.3 | ensure good stitching                                                                                                                                                                                                                         | 20       |

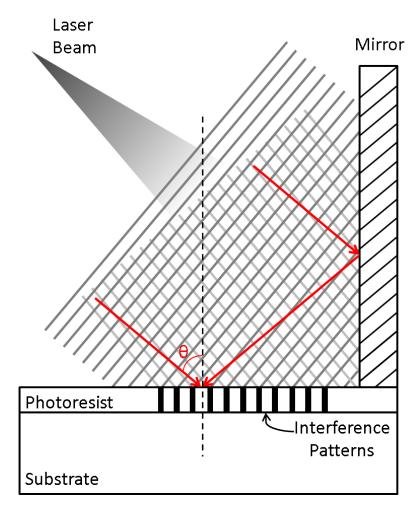

| 2.4 | interfering with the light reflected from the mirror                                                                                                                                                                                          | 24       |

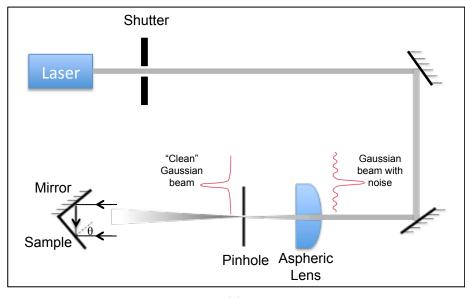

|     | 405 nm wavelength laser diode                                                                                                                                                                                                                 | 26       |

| 2.5  | Intensity profile of a perfect (blue) and a noisy (red) Gaussian beam versus the radial distance from the center of the beam. $r$ represents the radial  |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | distance from the center of the beam. $a$ is the radius at which the light                                                                               | 28 |

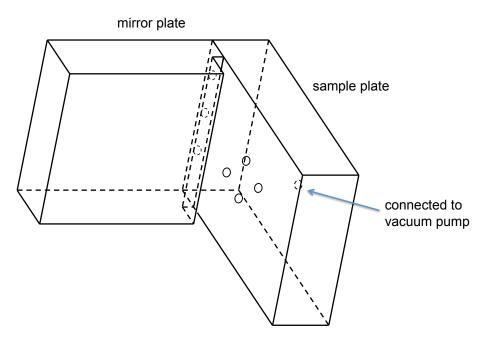

| 2.6  | Schematics of the mirror/sample holder for interference lithography. When                                                                                |    |

|      | the vacuum pump is activated, the mirror plate and the sample are held                                                                                   |    |

|      |                                                                                                                                                          | 29 |

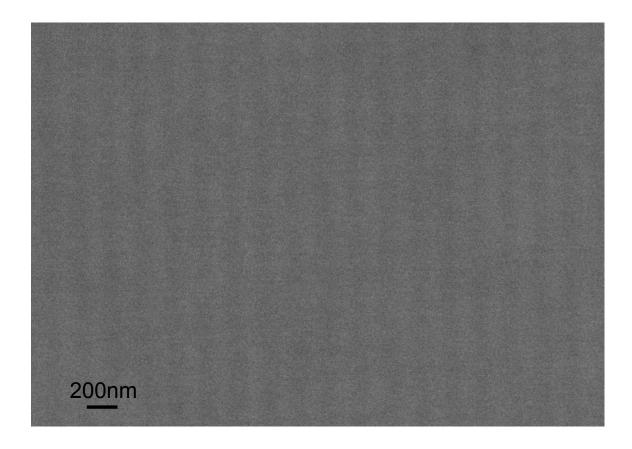

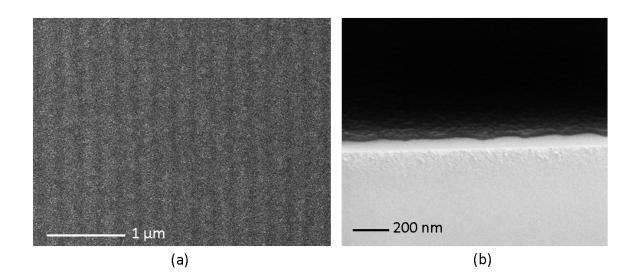

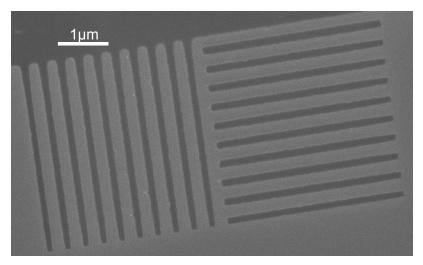

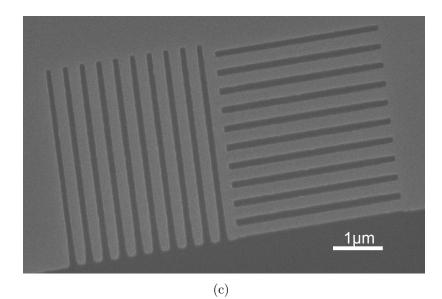

| 2.7  | SEM images of the gratings patterned on 100 nm thick Shipley 1813 resist                                                                                 |    |

| 20   | 0                                                                                                                                                        | 30 |

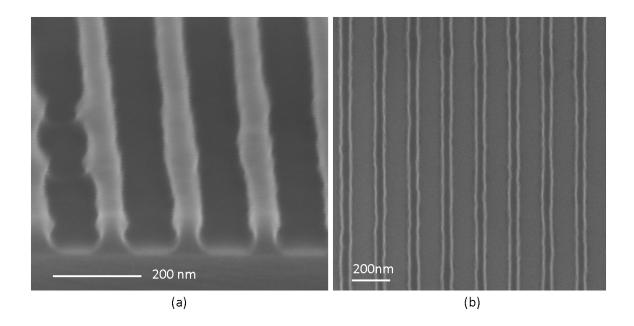

| 2.8  | SEM images of the gratings patterned on PEK-130A6 using 266 nm wave-<br>length laser. The period of the gratings is slightly less than 200 nm. This      |    |

|      | is very likely caused by the angular misalignment of the mirror due to                                                                                   |    |

|      | the curved cutting edge of the acrylic plastic sheet from heating by the                                                                                 |    |

|      | laser cutter. (a) Cross-sectional view of the gratings. (b) Top view of the                                                                              |    |

|      |                                                                                                                                                          | 31 |

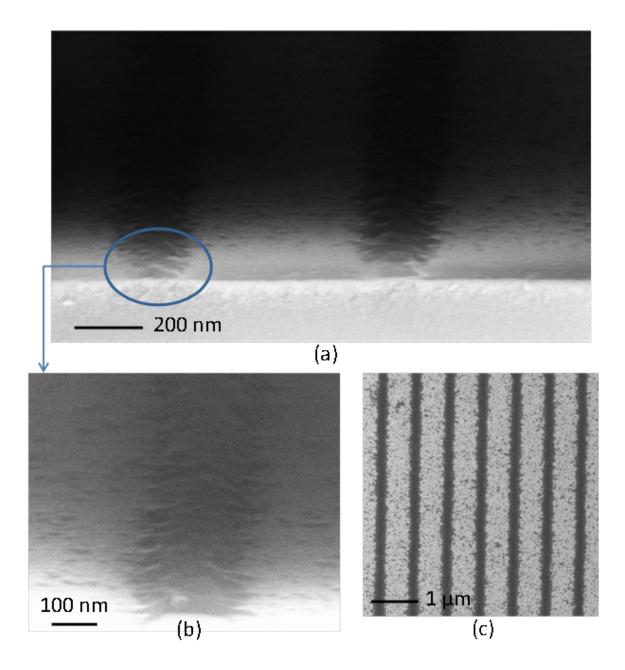

| 2.9  | SEM images of gratings patterned on 45 nm thick Shipley 1813 using                                                                                       |    |

|      | 405 nm wavelength laser. The period of the gratings is about 250 nm as                                                                                   |    |

|      | expected. (a) Top view image of the gratings. (b) Cross-sectional view of the gratgins                                                                   | กก |

| 2.10 | SEM images of 1 $\mu$ m period gratings patterned on 45 nm Shipley 1813                                                                                  | 32 |

| 2.10 | with 405 nm wavelength laser. (a) Cross-sectional view. (b) Zoomed-in                                                                                    |    |

|      |                                                                                                                                                          | 33 |

| 0.1  |                                                                                                                                                          |    |

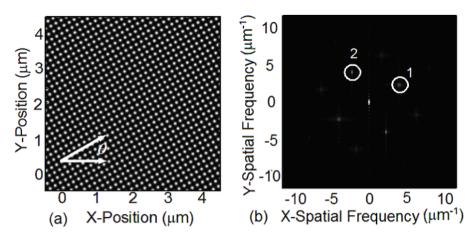

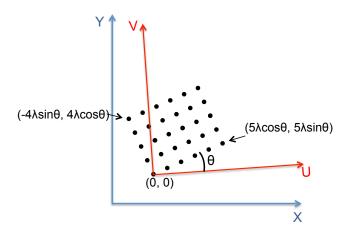

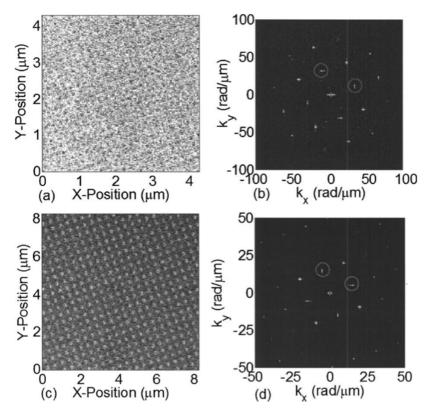

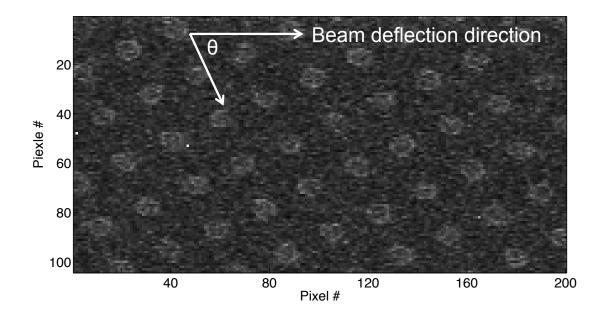

| 3.1  | (a) Simulated 2D signal from a 200 nm period fiducial grid rotated by an angle $\theta$ with respect to the scan direction. (b) 2D Fourier transforms of |    |

|      | the grid signal after sampling 5000 pixels. Circle 1 and 2 represent spatial                                                                             |    |

|      |                                                                                                                                                          | 39 |

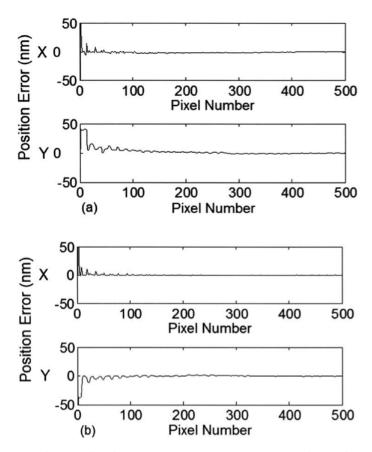

| 3.2  | Estimated x- and y-beam position errors vs. pixel number from simulation                                                                                 |    |

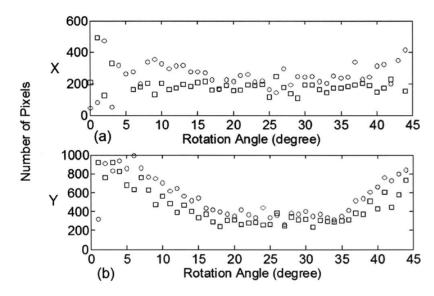

|      | (rotation angle = $20^{\circ}$ ). (a) Spiral fill. (b) Flyback fill                                                                                      | 11 |

| 3.3  | Calculated number of pixels required for 0.5 nm convergence as a function                                                                                |    |

|      | of rotation angle. ( $\bigcirc$ : spiral fill; $\Box$ : flyback fill). A large range of angles                                                           | 10 |

| 9.4  |                                                                                                                                                          | 12 |

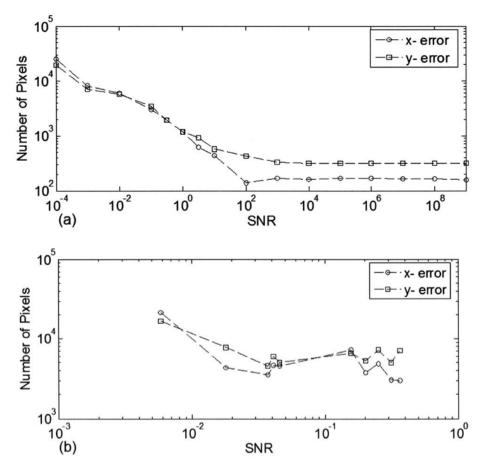

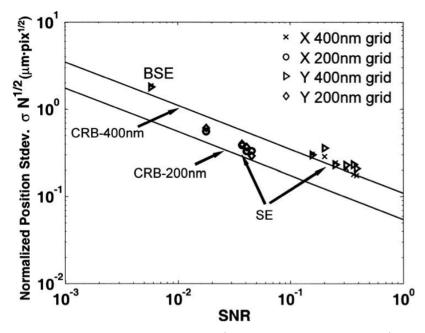

| 3.4  | Number of pixels required for 0.5 nm convergence vs. SNR for flyback fill strategy. (a) Simulation. (b) Experiment                                       | 13 |

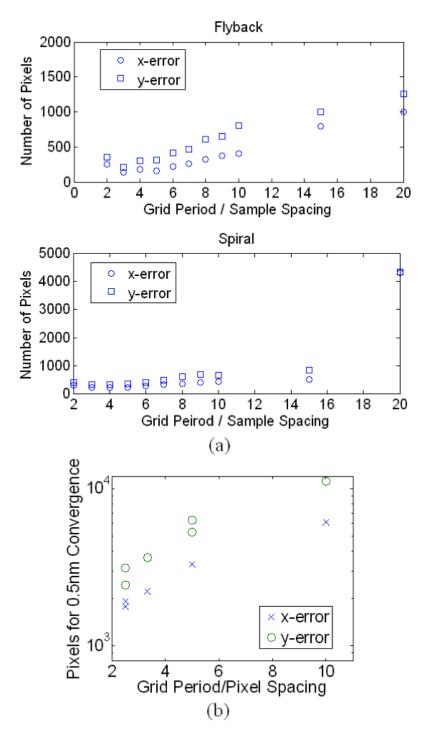

| 3.5  | Number of pixels required for 0.5 nm convergence vs. ratio of grid pe-                                                                                   | EU |

| 0.0  | riod to pixel sample spacing for flyback fill strategy. (a) Simulation with                                                                              |    |

|      | 200 nm period grid, $SNR = 10^9$ . (b) Experimental result. Measurements                                                                                 |    |

|      | were taken on a 200 nm period grid with SNR $\approx 0.4.$ Increasing pixel spac-                                                                        |    |

|      | ing beyond the minimum $(1/2 \text{ grid period})$ tends to degrade performance                                                                          |    |

|      | slightly                                                                                                                                                 | 14 |

| 3.6        | Illustration of rotated fiducial grid with respect to the EBL's stage and deflection coordinate systems after mapping the deflection axes on the grid. The angular misalignment between the two coordinate system is due to the error introduced by manually rotating the grid. The three sets of coordinates assigned to the grid only shows an example of the mapping |          |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.7        | procedure. Further apart points are usually used to minimize the error introduced by localized grid defects                                                                                                                                                                                                                                                             | 46       |

| 3.8        | 0.39                                                                                                                                                                                                                                                                                                                                                                    | 47<br>48 |

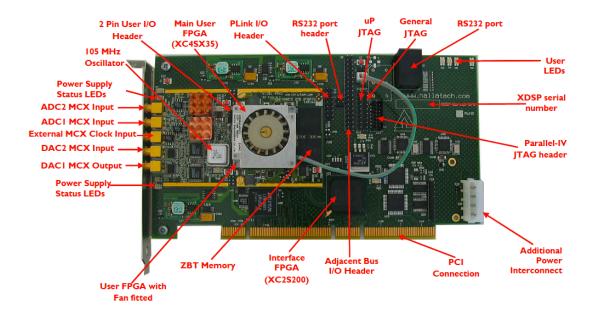

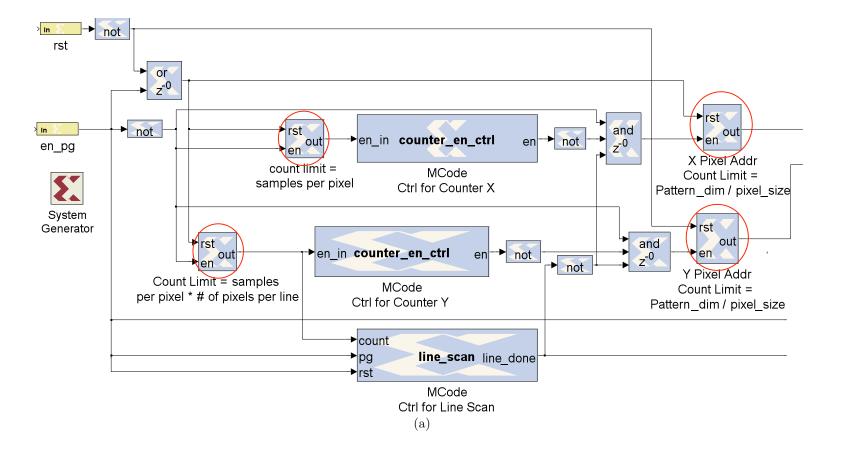

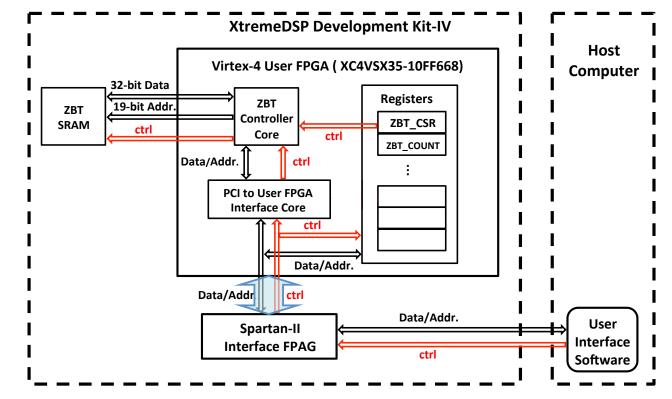

| 4.1<br>4.2 | Front view of the development board physical layout                                                                                                                                                                                                                                                                                                                     | 53       |

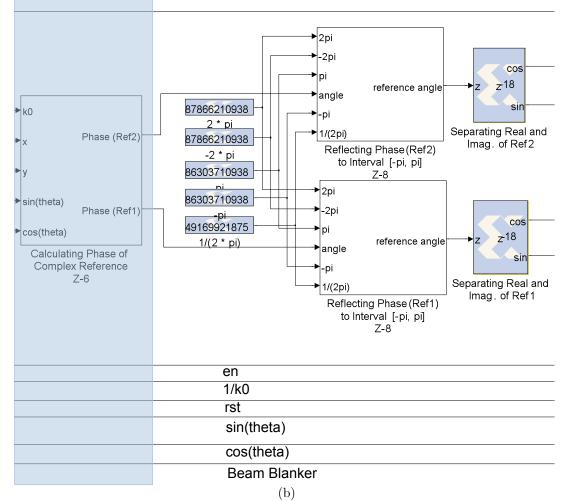

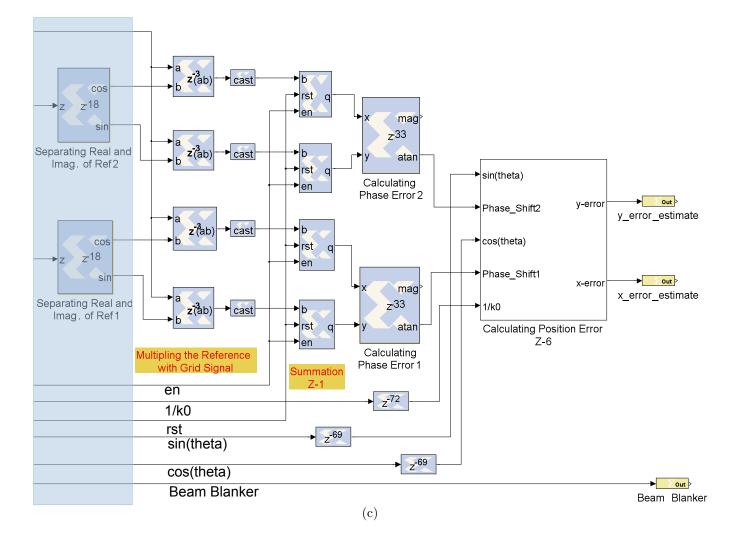

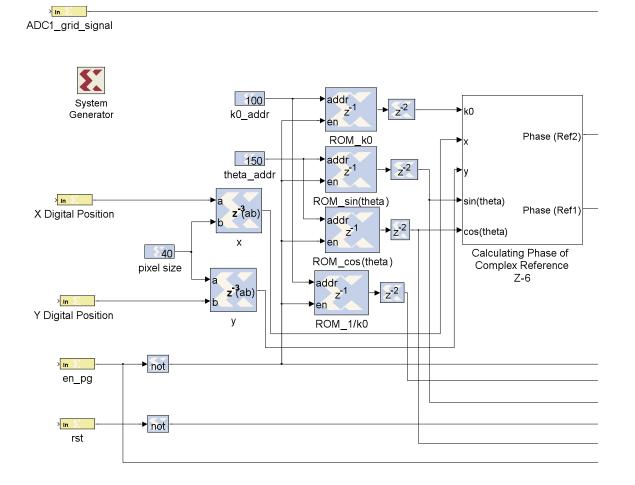

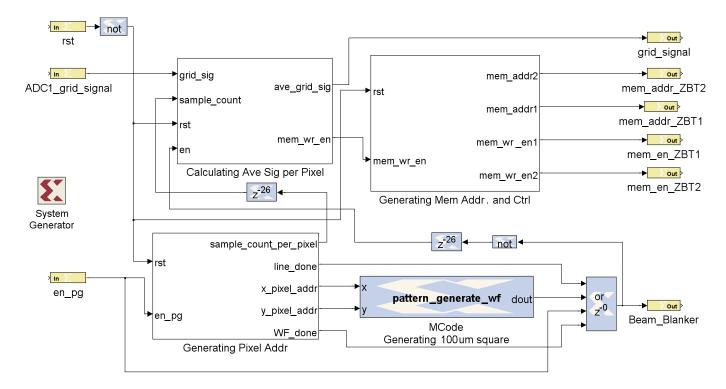

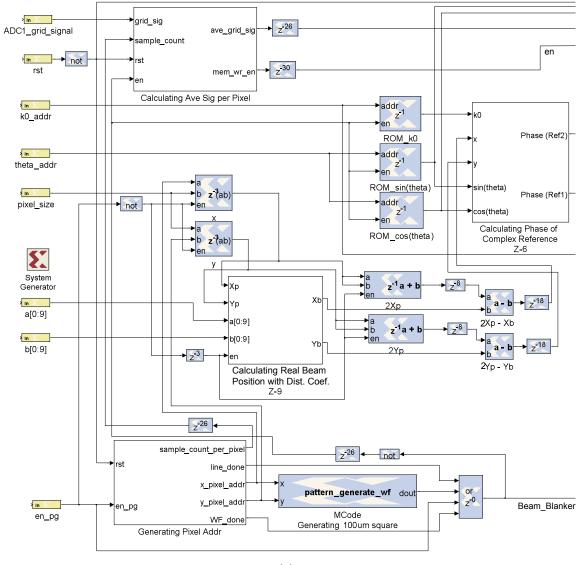

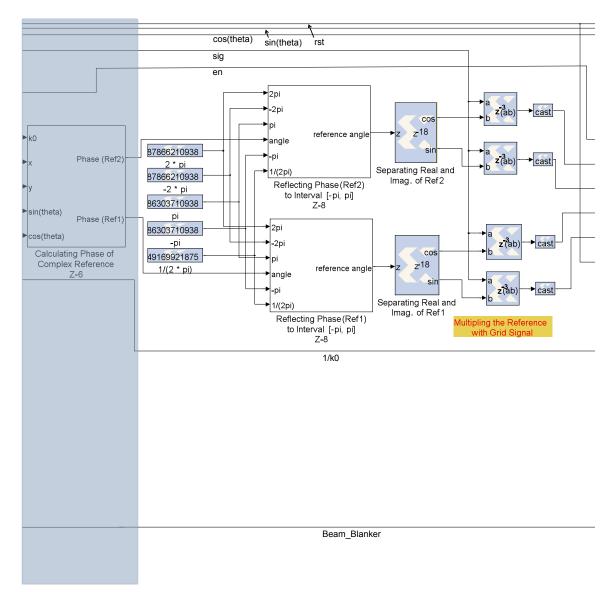

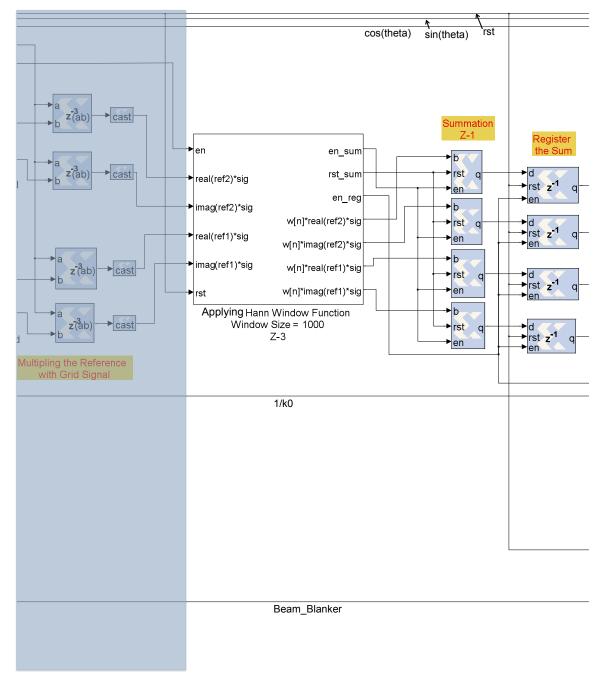

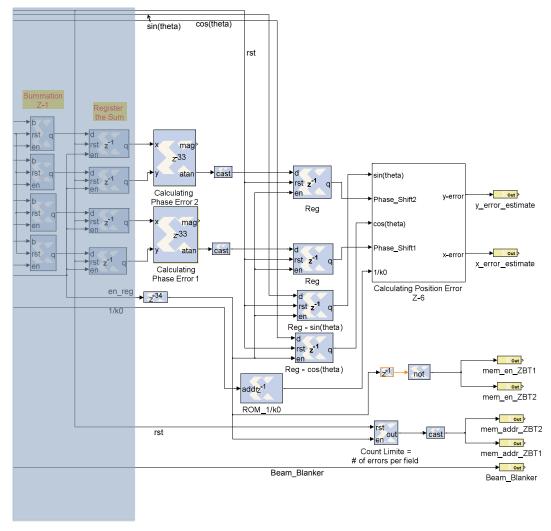

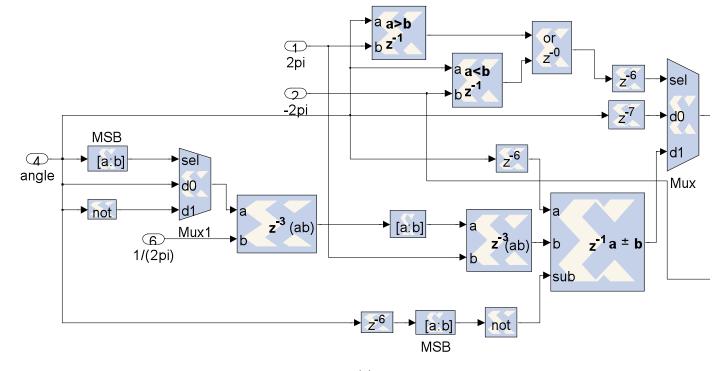

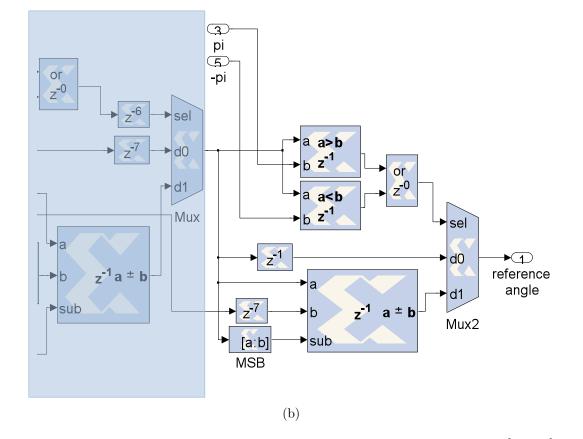

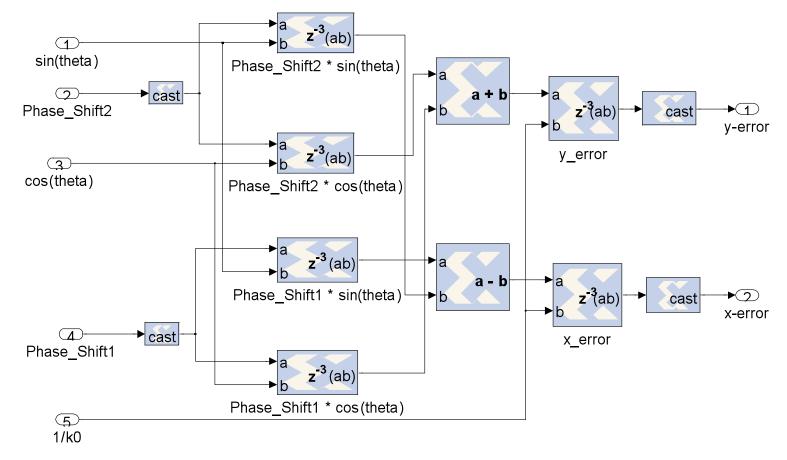

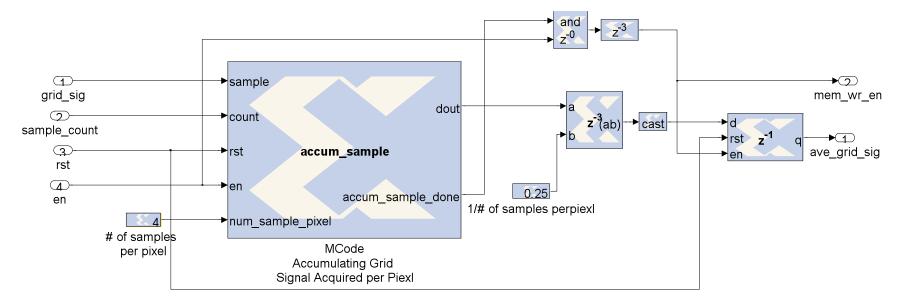

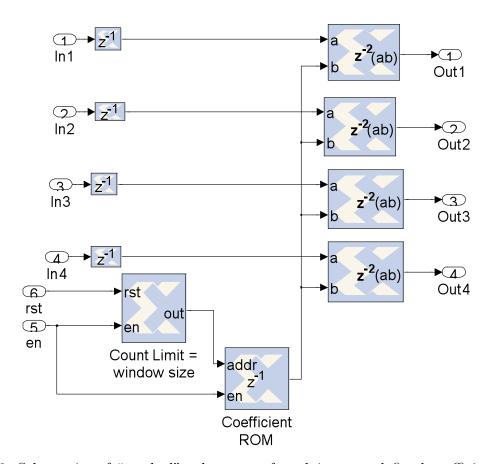

| 4.3        | subsystems can be found in Appendix A.1                                                                                                                                                                                                                                                                                                                                 | 58       |

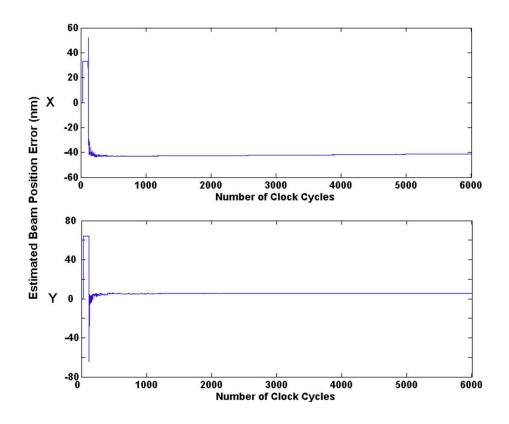

| 4.4        | and the rest is identical to that shown in Figure 4.2 Estimated x- and y-beam position errors vs. number of FPGA clock cycles from DSP design simulation in Simulink. (rotation angle: 20°; grid period:                                                                                                                                                                | 60       |

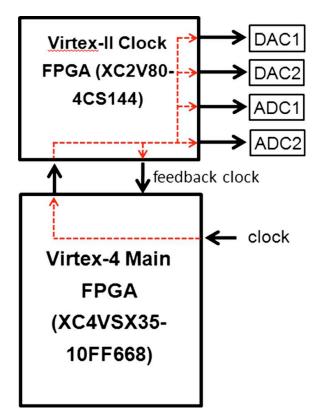

| 4.5        | 200 nm; pixel size: 40 nm; sample area: $100 \times 50$ pixel feature; SNR: $10^9$ ).<br>Schematic of clock signal routing on the FPGA. A programmable oscillator<br>controlled by FUSE system software was chosen as the system clock signal.<br>It is passed to clock FPGA to drive ADC/DACs and fed back to main                                                     | 63       |

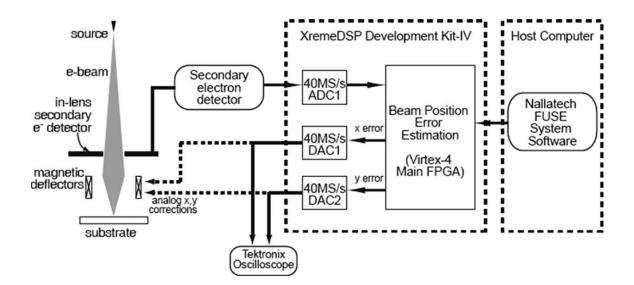

| 4.6        | FPGA to achieve synchronization                                                                                                                                                                                                                                                                                                                                         | 65       |

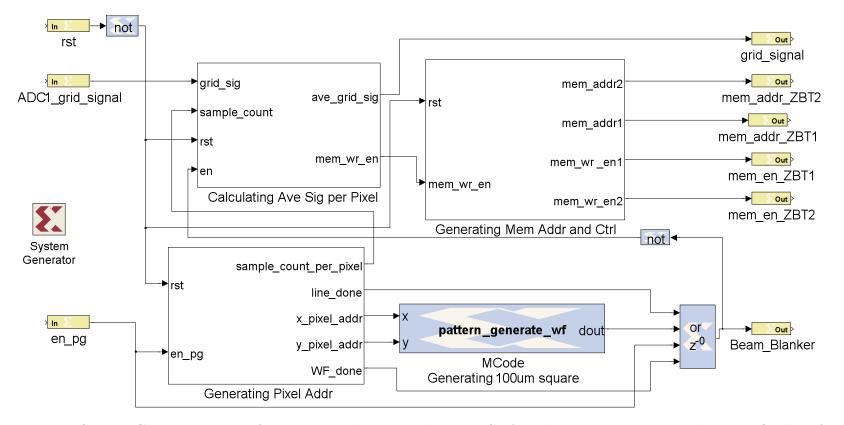

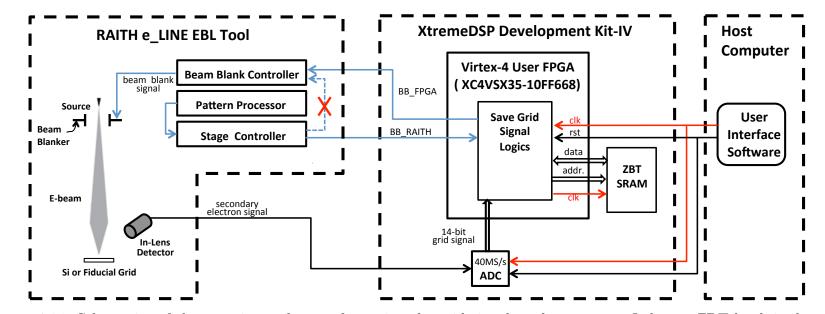

| 4.7        | is programmed and controlled through a host computer                                                                                                                                                                                                                                                                                                                    | 66       |

|            | area with area dose of 0.051 $\mu\mathrm{C/cm}^2$ at sampling speed of 40 MHz                                                                                                                                                                                                                                                                                           | 67       |

xi

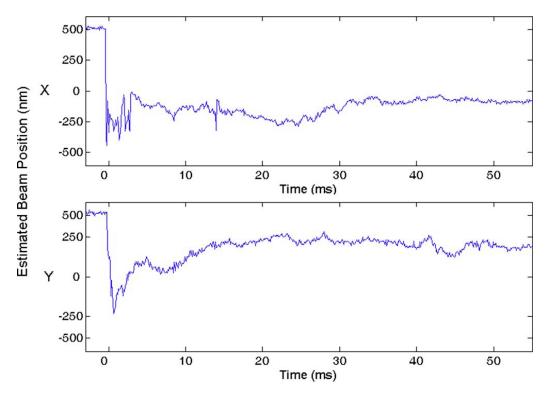

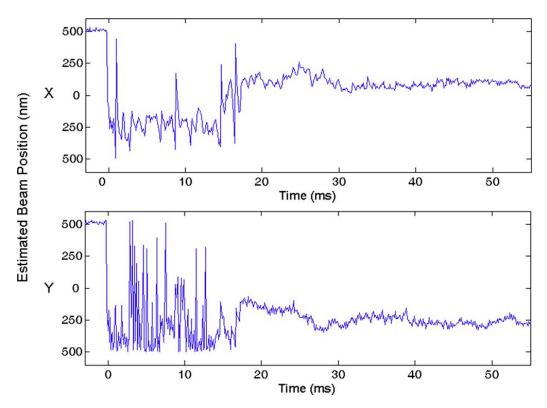

| 4.8 Experimental results of estimated x- and y-beam position errors vs. time.                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

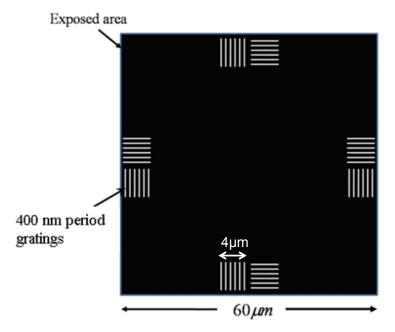

| <ul> <li>Measurements were taken on 1μm period gold grid in a 20 × 20 μm<sup>2</sup> area with area dose of 0.127μC/cm<sup>2</sup> at sampling speed of 40MHz.</li> <li>4.9 Illustration of the design pattern programmed in FPGA pattern generator. E-beam will be blanked when writing half pitch of the 400 nm period gratings with 50% duty cycle, illustrated as bright lines, and the dark</li> </ul>                                                                       | 68 |

| <ul><li>area will be exposed.</li><li>4.10 Schematics of System Generator design for generating test pattern by FPGA. Changing the count limits of the four counters (circled blocks)</li></ul>                                                                                                                                                                                                                                                                                   | 70 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 72 |

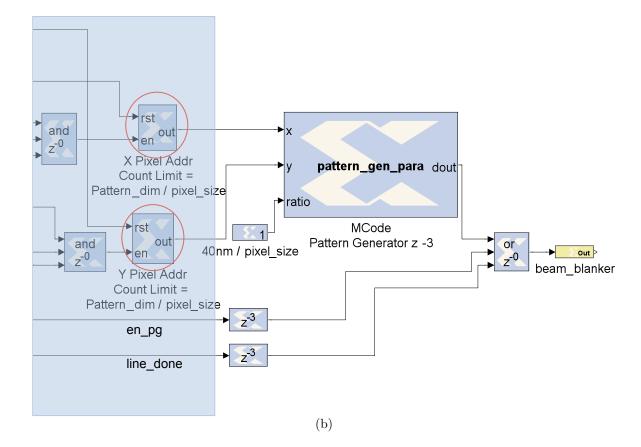

| 4.11 Schematics of experimental setup for exposing the test pattern with FPGA pattern generator                                                                                                                                                                                                                                                                                                                                                                                   | 74 |

| 4.12 (a) SEM image of the test pattern exposed on 100 nm PMMA at beam<br>energy of 10 KeV. pixel size = 20 nm; dwell time = 2 $\mu$ s; beam current =<br>198 pA; area dose = 99 $\mu$ C/cm <sup>2</sup> . (b) SEM image of gratings on the top<br>edge of the pattern exposed with pixel size of 40 nm and dwell time of<br>8 $\mu$ s. The duty cycle can be adjusted by changing the exposure dose. (c)<br>SEM image of gratings on the bottom edge of the pattern exposed under |    |

| <ul> <li>the same conditions as (b)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                     | 77 |

| controller core                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 80 |

| <ul><li>scanning over the write field. Refer to Appendix A.2 for subsystem details.</li><li>4.15 Schematics of the experimental setup for saving the grid signal to the memory. Only one ZBT bank is shown in the schematics, while both are</li></ul>                                                                                                                                                                                                                            | 82 |

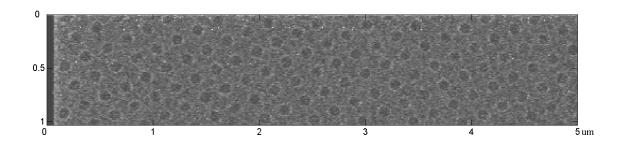

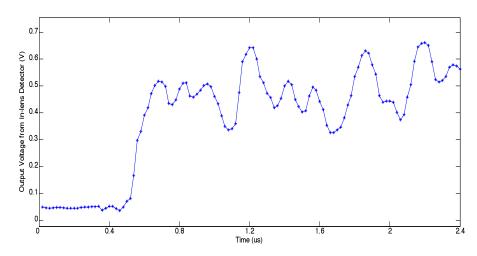

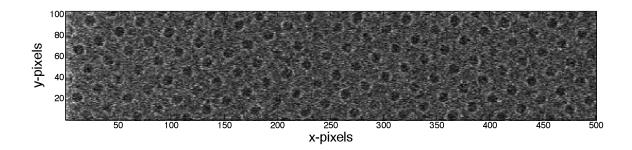

| <ul><li>4.16 Secondary electron signal captured by ADC and saved to two ZBT SRAMs while electron beam is scanning over the write field. The data are read from the memory to the host computer and plotted in MATLAB. Only</li></ul>                                                                                                                                                                                                                                              | 84 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 85 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 86 |

| scanning over the write field with compensation for delay                                                                                                                                                                                                                                                                                                                                                                                                                         | 87 |

| 4.19 Secondary electron signal captured from 200 nm period $SiO_2$ grids by ADC<br>and saved to two ZBT SRAMs while e-beam is scanning over the write<br>field with the hardware delay compensated.                                                                                                                                                                                                                                                                               | 88 |

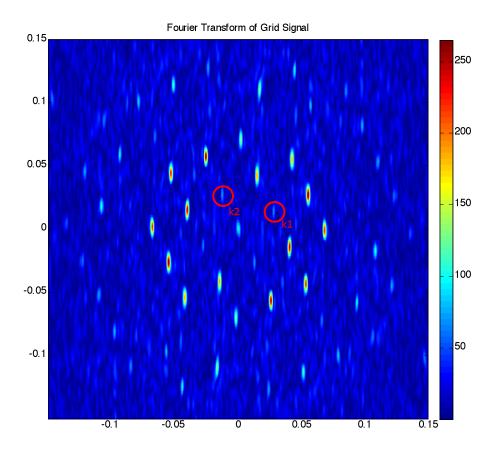

| 5.1  | 2D Fourier transform of the grid signal as in shown Figure 4.19. A 2D-<br>Hann window was applied to the signal to attenuate the interference from<br>the harmonics. The circled are the two fundamental frequency compo-<br>nents: $k_1 = (k_0 \cos \theta, k_0 \sin \theta)$ and $k_2 = (-k_0 \sin \theta, k_0 \cos \theta)$ . Strong inter- |            |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|      | ference from 2nd and higher order harmonics will significantly reduce the                                                                                                                                                                                                                                                                      |            |

| 5.2  | performance of the spatial phase estimator. $\dots \dots \dots \dots \dots \dots$<br>Secondary electron signal from 200 nm period PMMA grid. Dose of 0.016pC was used to expose an array of single pixel dots. 10000 × 104 pixels were sampled and stored in the memory, the 2D image shown here                                               | 90         |

| 5.3  | is reconstructed by a section of the samples                                                                                                                                                                                                                                                                                                   | 91         |

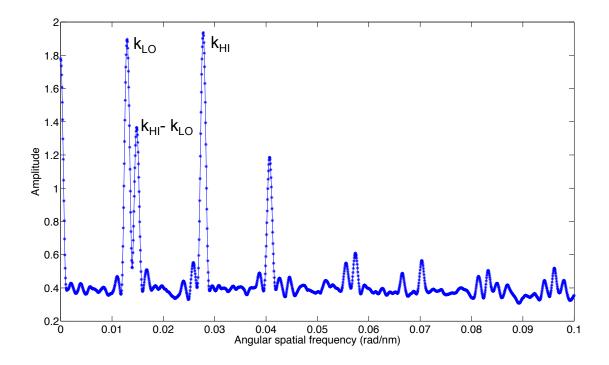

|      | form is taken over 1000 samples and the average amplitudes over 104 lines are plotted out.                                                                                                                                                                                                                                                     | 92         |

| 5.4  | Schematics of System Generator design that estimates position errors and<br>saves them to the memory. The saved position errors will be combined<br>with the intended beam position to calculate the field distortion coeffi-<br>cients off-line. Refer to Appendix A.3 for details of subsystem "Applying                                     | 0-         |

|      | Hann Window Fucntion".                                                                                                                                                                                                                                                                                                                         | 97         |

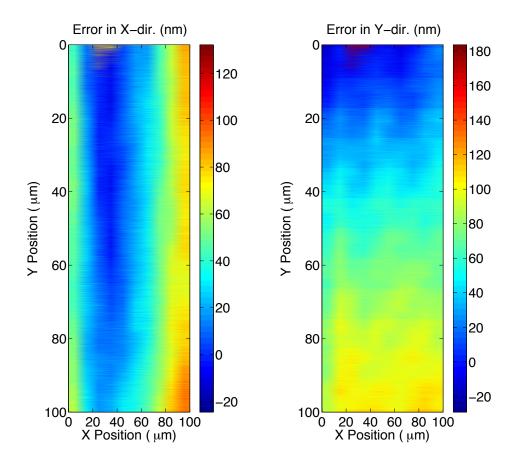

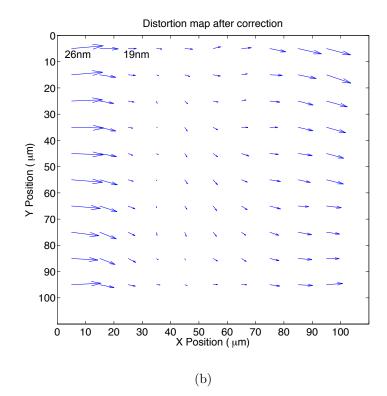

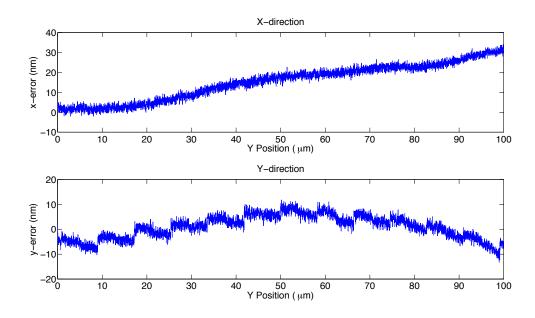

| 5.5  | The 2D estimated position errors in x- and y-direction.                                                                                                                                                                                                                                                                                        | 99         |

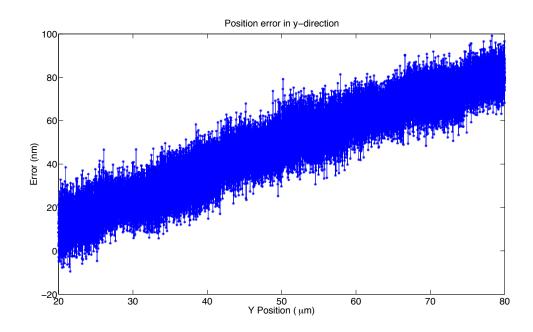

| 5.6  | Position error in y-direction vs. absolute beam position along y-axis of deflection coordinates. Only the data from a 60 $\mu$ m × 60 $\mu$ m area in the                                                                                                                                                                                      |            |

|      | center of the write filed are shown in the plot.                                                                                                                                                                                                                                                                                               | 100        |

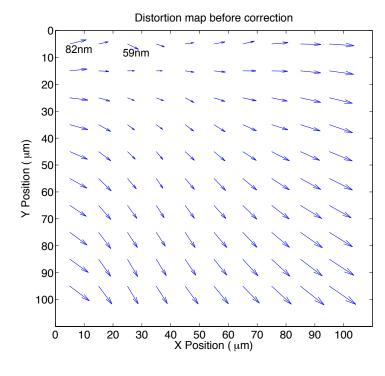

| 5.7  | Field distortion map constructed with the average position errors calculated in each 10 $\mu$ m × 10 $\mu$ m area. (a) Before 1st order correction applied.                                                                                                                                                                                    |            |

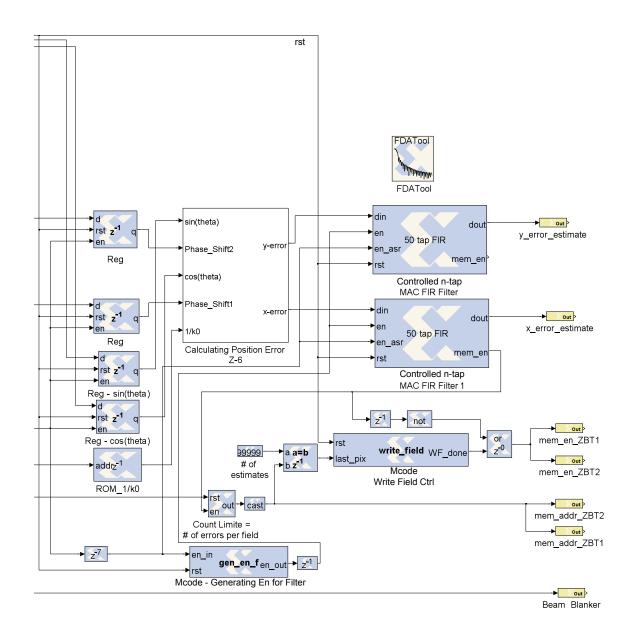

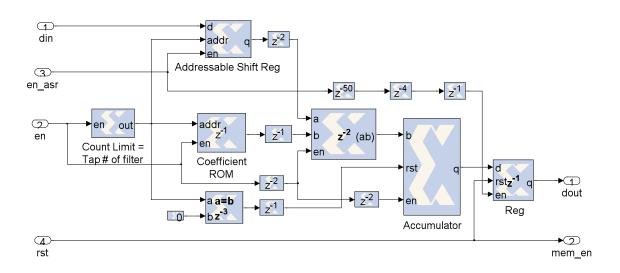

| 5.8  | (b) After 1st order correction applied<br>Schematics of the System Generator design with filter added before out-<br>putting estimated position error. Only the modified part is shown in<br>schematics. Refer to Figure 5.4(a), (b) and (c) for the rest part of the                                                                          | 102        |

| 5.9  | design                                                                                                                                                                                                                                                                                                                                         | 104        |

| 5 10 | correction applied                                                                                                                                                                                                                                                                                                                             | 105<br>106 |

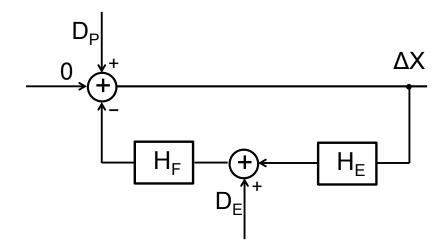

|      | Schematics of the feedback control loop.                                                                                                                                                                                                                                                                                                       | 100        |

|      | (a) System response for errors introduced by physical disturbance. 50-<br>tap low pass filter is used to achieve low-frequency cutoff of 380 Hz. (b)<br>System response for errors introduced by estimator with high-frequency                                                                                                                 |            |

|      | cutoff at 930 Hz                                                                                                                                                                                                                                                                                                                               | 108        |

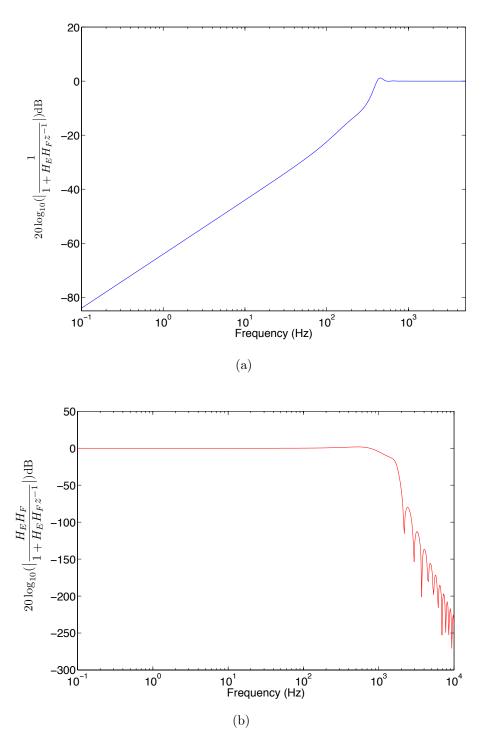

| 6.1  | Illustration of feedback system for real-time dose control. The substrate<br>to be patterned is coated with a scintillating layer that produces optical<br>signal. The signal is detected and processed to determine whether each<br>pixel has received sufficient dose so that the control electronics can stop                               |            |

|      | the exposure.                                                                                                                                                                                                                                                                                                                                  | 110        |

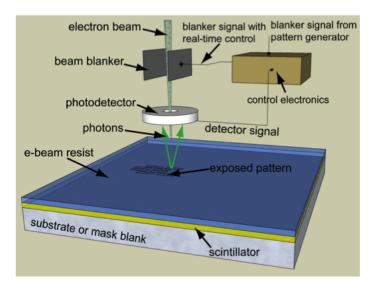

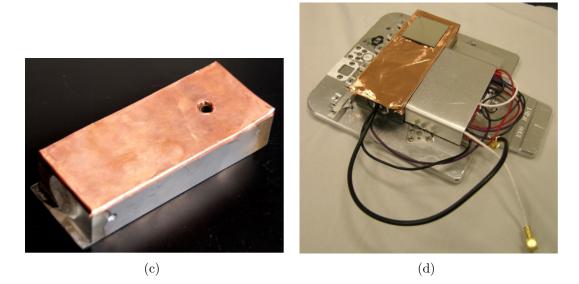

| 6.2  | (a,b) Solid model showing opposite sides of the light collection system. (a)    |       |

|------|---------------------------------------------------------------------------------|-------|

|      | shows the opening through which the e-beam passes and the mechanical            |       |

|      | support for the PMT. (b) shows the elliptical mirror and the recess in          |       |

|      | which the sample sits. (c) Side (a) of LCS is covered with copper foil, and     |       |

|      | the sample is placed underneath the small hole where the e-beam focuses.        |       |

|      | (d) Both the LCS and power supply are placed on the sample holder. The          |       |

|      | power supply is covered with a sheet of Al. In this case, side (b) of LCS       |       |

|      | faces upward, is covered with copper foil, and has the sample placed on top     | 0.112 |

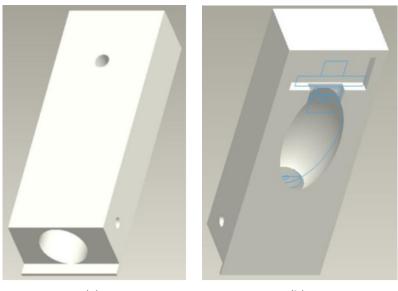

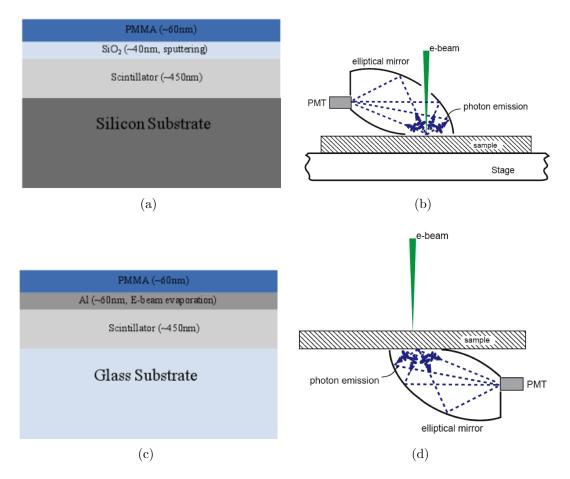

| 6.3  | (a,b) Illustration of scintillator coated Si substrate for which light is pri-  |       |

|      | marily emitted upwards. The LCS is placed on top of this type of sample.        |       |

|      | (c,d) Illustration of scintillator coated glass substrate. Light emitted from   |       |

|      | scintillator is reflected downwards by Al film. The LCS collects light from     |       |

|      | below with this type of sample                                                  | 114   |

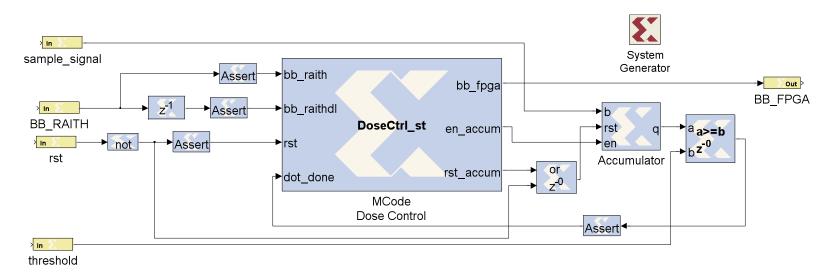

| 6.4  | Block diagram of System Generator design for dose control. The opti-            |       |

|      | cal signal is integrated and compared to a threshold value to determine         |       |

|      | whether desired dose level has reached. Refer to Appendix A.5 for MAT-          |       |

|      | LAB code of the finite state machine "DoseCtrl_st"                              | 116   |

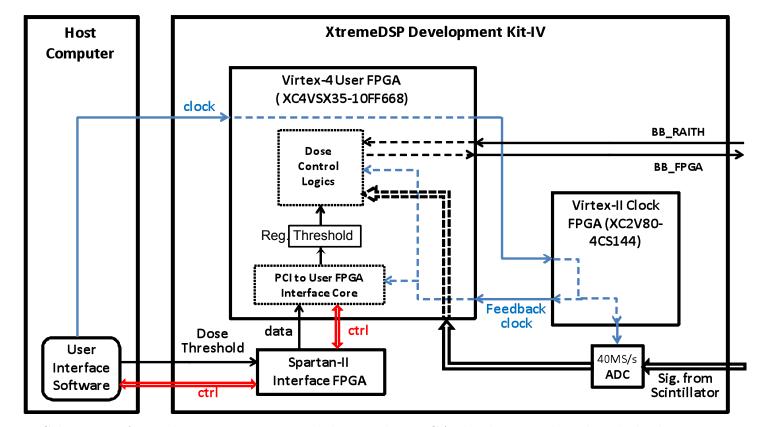

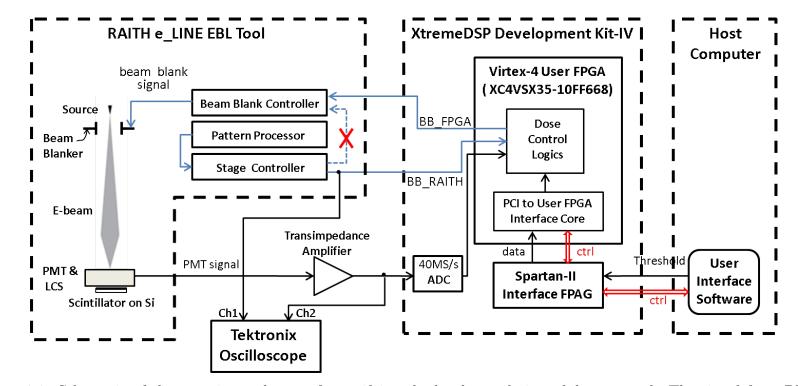

| 6.5  | Schematic of signal routing among modules on the FPGA development               |       |

|      | board and the host computer for dose control                                    | 117   |

| 6.6  | Schematic of the experimental setup for verifying the hardware design of        |       |

|      | dose control. The signal from PMT is routed through a trans-impedance           |       |

|      | amplifier and ADC, and finally processed by a Virtex-4 FPGA. The beam-          |       |

|      | blanking control signal from the EBL system (original connection shown          |       |

|      | with a red "X") now provides the control signal for the logic, and a new        |       |

|      | signal from the FPGA controls the beam blanker                                  | 119   |

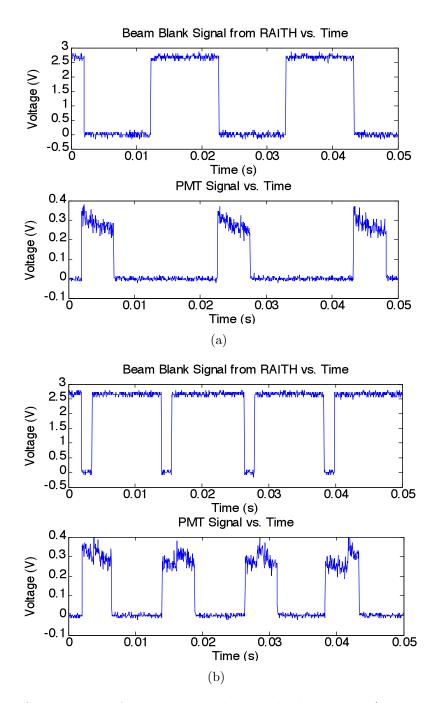

| 6.7  | Comparison of EBL system beam blanker signal (upper traces) with scin-          |       |

|      | tillator signal from the PMT (lower traces). For the upper traces, a voltage    |       |

|      | of 0 indicates that the beam would be on in the absence of feedback con-        |       |

|      | trol. (a) The dwell time was set to 10 ms (nominal dose 2095 fC) and            |       |

|      | the feedback system achieved the required dose (629 fC) by terminating          |       |

|      | the exposure early. (b) The dwell time was set to 1.5 ms (nominal dose          |       |

|      | 314 fC) and the feedback system extended the dwell times to achieve the         |       |

|      | desired dose.                                                                   | 121   |

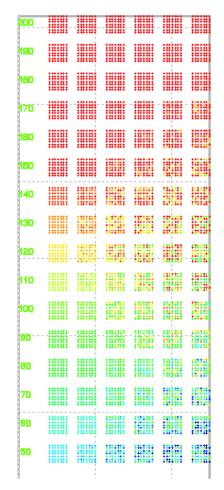

| 6.8  | Dot array in Raith software for exposure experiment                             | 122   |

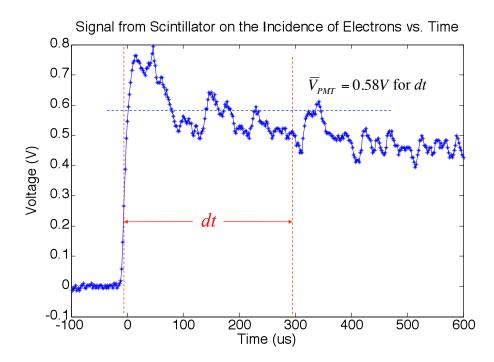

| 6.9  | Signal from PMT vs. time after turning on the beam. A slight decay in           |       |

|      | scintillator emission is present. $dt$ represents the dwell time, which is used |       |

|      | to determine the threshold value before exposure                                | 123   |

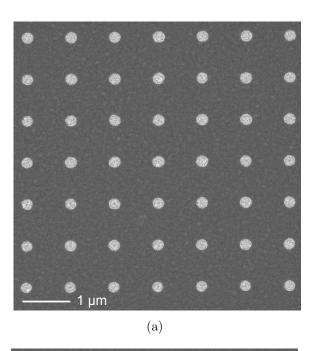

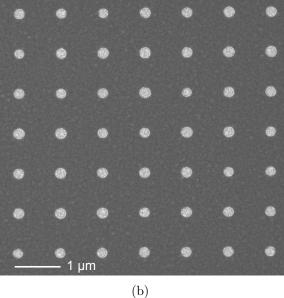

| 6.10 | SEM images of dots exposed with average dose of 0.09 pC. (a) Dose control       |       |

|      | was incorporated during exposure to achieve the desired dose level. The         |       |

|      | dwell time was set to 600 $\mu$ s (nominal dose 0.28 pC, standard deviation     |       |

|      | 0.024 pC) in the Raith lithography software to avoid the effect of e-beam       |       |

|      | motion on the pattern shape. (b) Feedback control was not used during           |       |

|      | exposure. The dose standard deviation is 0.023 pC                               | 125   |

|      |                                                                                 |       |

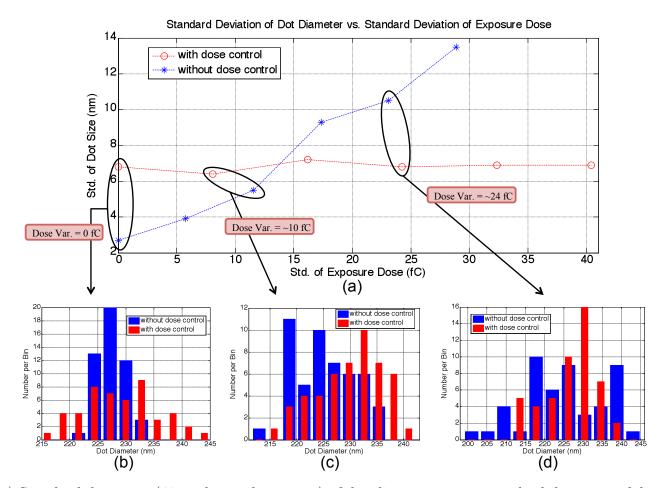

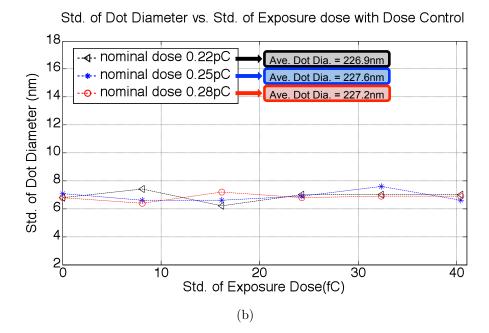

| 6.11 | (a) Standard deviation (49 trials per data point) of dot diameter versus   |     |

|------|----------------------------------------------------------------------------|-----|

|      | standard deviation of dose. Exposure was performed with average dose of    |     |

|      | 0.09 pC. For programmed standard deviations greater than 14 fC feedback    |     |

|      | control reduced the variance in dimension. (b-d) Distribution of dot sizes |     |

|      | for three example dose variations when patterned with (red bars) and       |     |

|      | without (blue bars) feedback for dose control.                             | 126 |

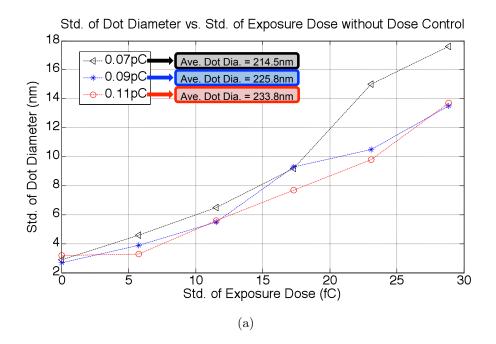

| 6.12 | (a) Standard deviation of dot diameter versus standard deviation of dose   |     |

|      | in the absence of dose control. (b) Standard deviation of dot diameter     |     |

|      | versus standard deviation of dose with feedback control                    | 128 |

# Chapter 1

# Introduction

The invention of integrated circuit (IC) in mid-20th-centuary revolutionized the industry of electronics. It can be found virtually in any electronic component today, and its absence from our modern, digital life is almost unimaginable. This is made possible because of the transition from manually assembling discrete electronic elements to mass production of highly compact circuits, leading to significantly reduced production cost per elementary function as well as increased performance to cost ratio. From the very first version of integrated circuit consisting of only a few transistors, to several billions on the surface of a thin substrate of semiconductor material today, miniaturization of circuitry by scaling down the transistor has followed the trend, known as "Moore's Law", stated by Gordon Moore in his paper published in 1965 [1]. This trend has become the principal driver for the International Technology Roadmap for Semiconductors (ITRS), and the engine of the virtuous cycle of the semiconductor industry.

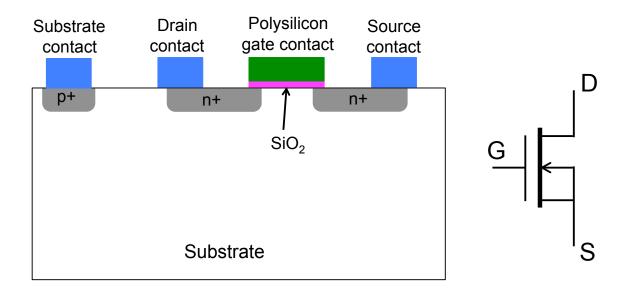

Planar fabrication technology, developed by Jean Hoerni [2, 3], has been the standard process of manufacturing the integrated circuit. By projecting a circuit on a two-dimensional plane, the concept of photographic process is adopted such that the transistors and the interconnections are built up vertically from the semiconductor substrate with layers of materials aligned with each other, as shown in Figure 1.1. Therefore, the functionality of each element and the entire circuitry is determined by the geometric patterns in each layer and the relative placement between layers, both

Figure 1.1: The cross section of an NMOS transistor fabricated by planar technology on the surface of a thin layer of semicondct substrate.

of which are defined by lithography. Lithography shares some fundamental principles with photography in that the pattern is created by transferring energy from a source to a layer of material that goes through certain chemical changes upon the absorption of energy.

For mass production of the electronic devices today, optical lithography (also called photolithography) still remains an essential step because of its extremely high throughput. However, to maintain the trend of continuously shrinking minimum half-pitch [4], it is facing the near-term challenge of transitioning from a single optical exposure to either double and multiple patterning or patterning using EUV light. Although other lithography technologies have been developed for nanostructure fabrication, such as electron beam lithography (EBL), x-ray lithography and ion beam lithography, they are not viable for cost-effective semiconductor manufacturing and mostly used for production of low-volume devices and research/development. Although EBL has not been used to pattern directly on Si substrate for IC production, it has found wide usage in writing photolithography mask, thus also faces the challenges of continuously tracking the requirements.

As the patterned feature migrates to smaller size, the accuracy of patterning in a

layer of material with respect to the existing ones has to be maintained within a certain fraction of the critical dimension (CD). The roadmap projects image placement in an optical mask with 2.7 nm error (3 sigma) in 2015, but the manufactural solution still remains unknown at the time of writing of this document [4]. However, the development of Spatial-Phase-Locked Electron Beam Lithography (SPLEBL) offers a promising solution to the problem.

The pattern placement error arises from the fundamental open-loop nature of EBL. During patterning, the electron beam is focused onto the target substrate and the feature is exposed pixel by pixel, or shot by shot. Despite the extensive effort invested in the development of individual components, one has no means of knowing the actual electron beam position. By detecting a reference signal from the substrate, processing the signal to calculate the deviation of the beam position, and feeding back the correction signal, SPLEBL monitors and controls the beam with a feedback loop, thereby improving the pattern placement accuracy. The work reported in Hastings' paper [5] using this technology has demonstrated 1 nm (1 sigma) pattern placement error, which achieved the benchmark set for year 2014.

Another aspect of the issue associated with miniaturization is poor CD control and increased line edge roughness (LER). According to ITRS's report on optical masks updated in 2011, a manufacturing solution is still not available for the CD control of transistor gate and contact till now. And the same problem for half pitch of dynamic random access memory (DRAM) also needs to be addressed soon in order to reach the benchmark in year 2014 [4]. The line edge roughness, sometimes referred to as line width roughness, is especially critical for fabricating optical waveguides as the roughness can lead to energy loss.

This lack of pattern fidelity is caused by the dosage variation of EBL, which is due to the inherent statistical nature of electrons arriving at the substrate and the system imperfection. Dosage, often referred to as dose, is defined as the electric charges delivered to the substrate per unit area, and is directly related to the total number of electrons arriving at the sample. When the exposure of each pixel is restricted to a very few electrons, so that nanometer scale features can be obtained rapidly, the uncertainty of the total number of electrons involved will become prominent, resulting in worsened variation in size and geometry. We propose to address this issue by detecting a dose related signal from the substrate and establishing a feedback control loop for the dose, which will be highlighted in Chapter 6.

## 1.1 Electron Beam Lithography Overview

Electron Beam lithography is the primary technology for writing arbitrary patterns with sub-10-nm resolution. A beam of electrons is emitted and scanned across a layer of electron sensitive resist material on the substrate in a patterned fashion. Chemical properties of the resist change upon the incidence of the electrons, which leads to the resist being hardened or removed in the process of development to achieve pattern transfer.

An EBL system can be classified according to the size and shape of the e-beam. A scanning beam system focuses the electrons to a Gaussian-shaped spot and exposes the pattern pixel by pixel. A shaped beam, either fixed [6] or variable [7], projects the electron image of an aperture onto the substrate and exposes a segment of the pattern. This method helps reduce exposure time and improve field coverage compared to the scanning concept, but the resolution is highly dependent on the geometry of the pattern. Electron projection lithography combines the optical lithography approach with an electron source. With a broad beam of electrons projected onto a physical mask, the entire pattern is defined by a single exposure. Although the limitation of low throughput encountered by the scanning and shaped EBL is overcome by using this method, the major challenge becomes the design of mask with minimized Coulomb interaction between electrons and thereby the distortion of the final pattern. Since scanning EBL is mostly suitable for implementation with spatial-phase locking, the remainder of this document will exclusively focus on the scanning-beam system.

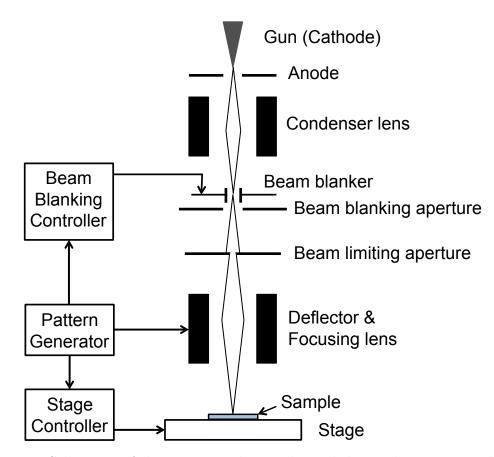

Figure 1.2: Schematic of the scanning electron-beam lithography system with major components.

#### 1.1.1 Components of Electron Beam Lithogaphy System

The major components of the scanning electron beam lithography (SEBL) system include an electron source, electron-optical column, mechanical positioning stage, and a microprocessor that generates the pattern as illustrated in Figure 1.2.

Good current stability and sufficient brightness are the two most important criteria when choosing the electron source for the lithographic tool. For a thermionic emitter, electrons gain thermal energy from a heated conducting tip and overcome the work function of the metal. This type of source is used mostly in low resolution systems due to large electron energy spread and low current density, but it offers high stability over typical writing times of several hours and is less sensitive to gases in the environment. Although increased temperature delivers more current, the emitter's lifetime will be reduced exponentially. In applications requiring higher resolution, a field electron emitter is more desirable, as the typical energy spread of a field emitter is under one electron volt (eV), and the virtual source size is on the scale of nanometers [8]. Field emission occurs when the applied electric field is sufficiently strong so that electrons can tunnel through the barrier between the the emission source and vacuum. Due to the drawback of the short term fluctuations and long term drift of emission current, cold field emission source has seen little use in EBL. However, heating up the emitter tip, know as Schottky emitter, helps reduce the current instability without compromising the resolution dramatically.

While the emission source constantly supplies electrons, an electric field at specific potential is applied to accelerate emitted electrons. The typical primary electron energy used in lithography lies in the range between 1 KeV and 100 KeV. When electrons are accelerated with extremely high energy (at least 100 KeV), they gain enough energy to penetrate deep into the substrate material. Transmission electron microscopy makes use of this phenomenon when the substrate is thin enough to let electrons pass through, while high-aspect-ratio and high resolution features are fabricated by taking the advantage of electrons' high penetration [9, 10, 11].

Intensive studies on lithography at low e-beam energy (below 5 KeV), motivated by the benefits of significantly reduced proximity effect and thereby improved resolution, began in 1990s [12, 13, 14, 15]. In addition, electron beam microcolumns for high throughput patterning require to operate at no more than few electron volts due to the miniaturized electron sources [16, 17, 18, 19, 20]. Because the penetration depth is typically well below 100 nm at low primary electron energy, a thin resist with high sensitivity is required to achieve proper exposure. The requirement on the resist's conductivity becomes especially stringent as the severe surface charging can lead to pattern distortion [21].

After the electrons have been accelerated away from the emitter, they go through a series of apertures, electron-optical lenses, and deflectors before arriving at the substrate. Electron-optical lenses focus electrons either by applying electrostatic force or magnetic force. The term "optical" is used in this context because electrons can be manipulated by the magnetic or electrostatic filed in a similar manner to a light beam through an optical lens. However, the aberration of electron lens is far worse than an optical lens, which means the electrons with different energies are focused at different points along the electron-optic axis. The electrostatic lens is usually positioned adjacent to the source as a condenser lens for its worse aberration compared to a magnetic lens. In addition, the electrostatic lens helps pull out electrons from cathode. Since the final lens determines the performance of the electron-optic column, an electron lens with the highest quality should be placed closest to the substrate.

An aperture is basically a small hole through which electron beam passes along the electron-optic axis. A beam blanking aperture works together with a high-speed electrostatic deflector to interrupt the electron flow toward the substrate without shutting off the emitter. While not writing, the electron beam is swept away from the electron optic axis by the electrostatic deflector, and intercepted by the aperture. The beam limiting aperture truncates a portion of the beam to set the convergence angle through which the electrons pass through the column, and thus the beam spot size and current.

The beam deflection system is for scanning the electron beam across the substrate during microscopy and exposure. As the beam is deflected off the optical axis, additional aberration is introduced, resulting in pattern distortion. Therefore the deflection range with acceptable aberration is highly dependent on the optical column and varies from system to system. That being said, the reliable deflection range sets the upper limit of the dimension of the deflection field, thus the throughput of the system. Deflecting the electron beam can be done either electrostatically or magnetically. The magnetic deflector allows for a longer range of deflection than the electrostatic deflector, but its frequency response is limited due to the inductance of the magnetic coils and the eddy current introduced by the magnetic field.

Since the deflection of beam is limited over a small area, precise mechanical stage positioning needs to be combined with beam deflection to pattern large features by exposing multiple deflection fields and piecing them together. This is made possible by using two laser interferometers to measure the stage position in x- and y-direction. Two split laser beams are directed to a reference mirror and a mirror attached to the stage in each direction, then the interferometers compare the position of the stage mirror to that of the reference mirror to detect and correct stage position errors.

The pattern to be exposed is first drawn out using computer aided design (CAD) program, and then the pattern data is translated into two sequences of signals by the pattern generation system for EBL. One signal contains the information of the pixel addresses in the pattern coordinate, and is converted to an analog signal by a digital-to-analog converter (DAC), and eventually sent to the beam deflection system. The other signal sequence controls the beam blanking hardware, which is synchronized with the position signal to ensure that the beam is switched on and off at the desired location according to the pattern design. The smallest pixel size is determined by the beam deflection range and the DAC's resolution. The pixel size and dwell time at each pixel are chosen to achieve a desired exposure condition. To obtain the best result, the pixel size should be kept small, usually a fraction of the beam spot size, so that smooth feature edges can be obtained by overlaying each pixel.

#### 1.1.2 Exposure Strategy

Since the beam cannot be reliably deflected more than a few millimeters due to the aberration of electron optics, while the pattern's dimension can be easily larger than that, the system must break up the patterns into segments and expose them one at a time. Depending on whether every single pixel is addressed within the segment during exposure, SEBL can be classified as vector-scan or raster-scan.

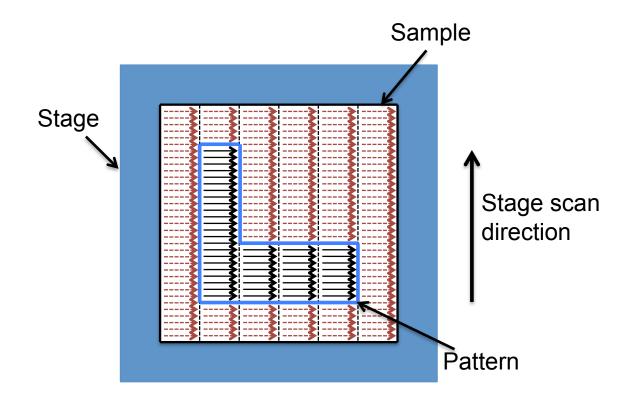

For a raster-scan system, the beam addresses every single pixel, and is switched on and off as required by the pattern design. This strategy is mostly used for highthroughput mask making when the stage is moved continuously in the direction perpendicular to beam raster scan direction. In this way, the limitation of small beam deflection range only presents itself in one direction, and is removed in the other by the stage movement. Therefore, patterns are built up with long strips as shown in Figure 1.3.

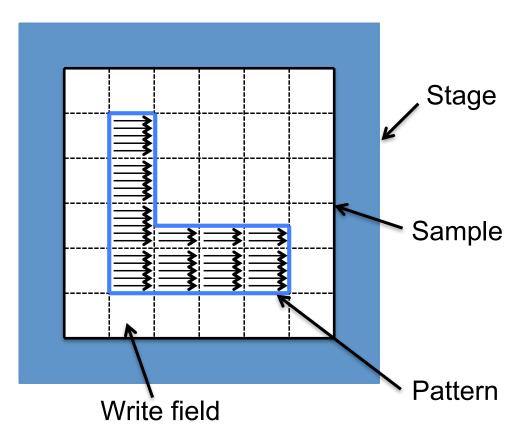

The vector-scan system only deflects the beam to where the pattern resides, and fills in the segmented shapes of the pattern as depicted in Figure 1.4. In this strategy,

Figure 1.3: In raster-scan system, the beam is deflected in one direction to address every pixel address on the sample. E-beam is only switched on at where patterns reside. If the stage scans in the direction perpendicular to the beam scanning direction, pattern is stitched with long strips as illustrated here. Red arrows show the deflection with beam switched off, while blues ones with beam switched on.

the stage is kept stationary while the beam fills in the shape, and then moved to the next location. In addition to the strategy that fills the shape line by line in one direction, referred to as flyback, as illustrated in Figure 1.4, two other methods, known as meander and spiral, are also adopted by the SEBL system as depicted in Figure 1.5(b) and (c). The benefit of using either the meander or spiral method is that the overhead time is comparably less without the effort of settling the beam between lines, and distortion introduced by the dramatic change of beam movement direction is almost eliminated. Some systems also include circular mode as shown in Figure 1.5(d) to account for round shapes.

A vector-scan system is most efficient for writing sparse patterns, and it allows to introduce dose variation from shape to shape for correcting proximity effect. However,

Figure 1.4: In vector-scan system, the beam is only deflected to where pattern is located, and the stage is fixed while the e-beam is scanning in the write filed. Only the flyback filling method is demonstrated in the schematics.

the overhead can be significant for dense patterns because of increased stage settling time before starting the exposure in each field. A vector-scan system is most suitable for research and prototyping, and sometimes for fabricating high-resolution, lowvolumn devices.

## **1.1.3** Electron Resist Interactions

Patterning in electron sensitive resist is through the process of transferring energy from incident electrons to the polymer, in which either scission or crosslinking of the polymer chain occurs. The process of development after exposure dissolves lighter molecular weight polymers, revealing the pattern defined by e-beam writings. Although the change in chemical properties of the polymer is the direct cause of imaging, the physical interaction between the incident electrons and the resist/substrate

Figure 1.5: Filling method used in vector-scan system. (a) Flyback. (b) Meander. (c) Spiral. (d) Circular.

dictates the energy distribution, thus the chemical reaction in the polymer.

As a primary electron penetrates through resist, and travels further into substrate material, it experiences both elastic and inelastic scattering from the material atoms and electrons before it completely loses its energy. The average distance traveled by the electrons before they stop is defined as range, which is a very important parameter for characterizing the electron profile in the bulk material.

Forward scattering, corresponding to many small angle scatterings, contributes to the depth of electron penetration into material as well as the beam profile broadened at the bottom of the resist compared to that on the surface. To reduce the effect of beam expansion, one can increase the accelerating voltage and spin coat thinner resist. In some instances, though, it is made use of to tailor the resist sidewall angle.

When large angle scattering occurs, also referred to as backscattering, electrons travel laterally further from the incident location, and sometimes can return back through the resist, resulting in additional exposure. This undesired exposure is the reason of what is known as proximity effect in EBL system. The mean free path of backscattered electrons is determined by the incident energy and material, and therefore, reducing accelerating voltage and choosing the material with low atomic number can effectively reduce the proximity effect.

Both events are accompanied, in a continuous manner, by both energy loss and excitation of secondary electrons (SE) with energies less than 1 KeV. The secondary electron is the largest component of free electron population in the bulk of the material, and is responsible for the actual resist exposure. Because of its low energy, the range of the secondary electrons is typically a few nanometers, which accounts for the minimum practical resolution of the final pattern after development.

Charging in the sample can cause considerable distortion due to the unexpected deflection of the e-beam away or toward the charged area, if the electrons can not quickly gain access to a path to ground. For lithography using high primary electron energy (greater than 10 KeV) on a Si substrate, virtually all electrons stop in the bulk of the substrate and are eventually grounded. However, if exposure is performed on an insulating substrate, such as photomask, the embedded electrons will take much longer time to be dissipated. The most effective solution to dissipate charges during this high energy exposure is to deposit a thin layer of metal either above or below resist. For low energy exposure (about 10 KeV or lower), positive charging of the surface due to the secondary electron emission to the vacuum has more effect. In this case, a charge dissipation layer, a type of conductive polymer, is often incorporated with the resist to minimize the scattering for high pattern fidelity [22, 23, 24].

The sensitivity of electron beam resist is determined by the dose required during exposure, measured as the amount of charges per unit area that ensures the resist film to be dissolved (positive) or retained (negative) in the process of development. It is related to the exposure parameters, i.e., beam current I, dwell time  $\tau$  and pixel size l, as given by

$$Dose = \frac{I \cdot \tau}{l^2}.$$

(1.1)

With the selected parameters, the dose can be calculated and compared to the critical value of the specific resist, and therefore necessary adjustments can be made to achieve

proper exposure.

## **1.2** Pattern Placement Errors

In either raster or vector-scan system, pattern placement is achieve by reliable beam deflection together with precise stage control. Although careful engineering of electronoptical lenses can reduce the deflection distortion caused by aberration, and the laser-controlled stage can be positioned with nanometer resolution, precise pattern placement is still impossible to retain unless other causes of error are addressed. If the sources of the error are static or quasistatic, such as an aberration of the electron-optics, imperfection of interferometer and non-linearity of deflection axes, intermittent calibration procedures can be implemented to minimize such error. As for errors introduced by dynamic sources, such as charging of sample and system, thermal expansion, vibration and stray magnetic field, if frequent calibration were to be performed, the amount of overhead added to exposure time would be prohibitive.

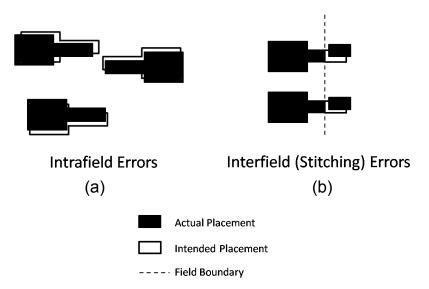

All pattern placement errors can be classified as intrafield or interfiled. The intrafield error refers to that within the write field as depicted in Figure 1.6(a), while the interfield error is what causes the mismatch between adjacent fields as in Figure 1.6(b). Figure 1.7 shows some interfield errors observed in the experiment of exposure.

# 1.3 Spatial Phase Locked Electron Beam Lithography

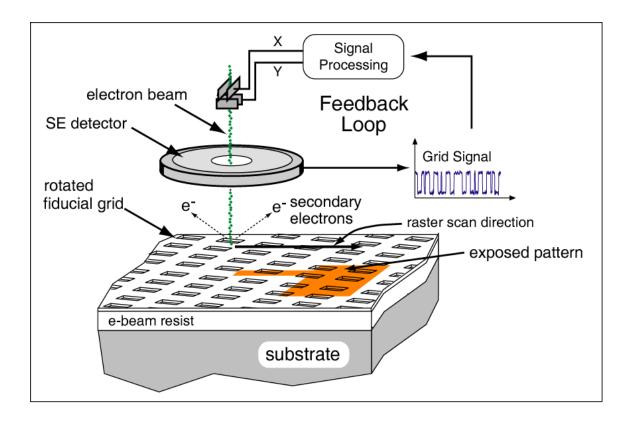

Different from the other methods of improving pattern placement precision, in which the efforts are put in directly addressing the sources that cause the error, SPLEBL seeks to "close the loop" by monitoring electron beam location and correct the deviation. As illustrated in Figure 1.8, this approach relies on detecting the secondary electron signal from a fiducial grid placed on the substrate that does not adversely affect the normal exposure. With the periodic grid signal, the e-beam position error

Figure 1.6: Illustration of two types of pattern placement errors.

referenced to the grid is estimated by external electronics, which is then sent back to the beam deflection system to be corrected.

Since the idea was first proposed [25], it has been implemented in different strategies for both raster- and vector-scan EBL. The early implementation employed discontinuous feedback mode for vector-scan system. The fiducial grids or gratings are examined before exposure, then Fourier transform is performed to extract the spatial phase and finally the correction is applied to the beam deflection system during exposure.

If segmented grid/gratings are used, referring to the reference pattern written in the unused portion of write field, highly scattering material are chosen to fabricate the reference pattern and sampling is performed with high dose level. Therefore, precise phase estimation can be achieved with high signal-to-noise ratio (SNR). Integratedoptical devices have been patterned using this technique, and the best result demonstrates the interfield error with 0.3 nm standard deviation [26, 27]. While with global fiducial grid/gratings patterned on the substrate, examining the grid/gratings is conducted at discrete locations within the write field using sub-exposure threshold dose. As a result, phase locking with lower precision is expected due to the reduced SNR. The standard deviation of 5 nm has been achieved with gratings [28], and 12 nm with

Figure 1.7: Stitching errors at the write field boundary observed in the experiment. (a) Bulges at the boundary due to overlapped exposure. (b) Discontinuity and offset at the field boundary.

Figure 1.8: Spatial-phase-locked electron-beam lithography (SPLEBL) provides feedback control of pattern placement by estimating the beam position error using detected secondary electron signal from an electron-transparent fiducial grid.

a fiducial grid [29].

The continuous feedback mode has been implemented for raster-scan system. By conducting phase locking with full dose level during exposure and reduced dose while e-beam addressing the unpatterned area, the overhead time required for examining the grid before exposure is greatly reduced, and some rapidly occurring errors are also effectively corrected during exposure. The reported exposure experiment demonstrates sub-1-nm pattern placement precision [5].

## **1.4** Shot Noise and Dose Variation