University of Kentucky UKnowledge

Theses and Dissertations--Electrical and Computer Engineering

**Electrical and Computer Engineering**

2011

# CONTROL CHARACTERISTICS OF AN ALL-DIGITAL PROPORTIONAL-INTEGRAL-DERIVATIVE (PID) COMPENSATOR

David Michael Feinauer University of Kentucky, dfeinauer@hotmail.com

Right click to open a feedback form in a new tab to let us know how this document benefits you.

#### **Recommended Citation**

Feinauer, David Michael, "CONTROL CHARACTERISTICS OF AN ALL-DIGITAL PROPORTIONAL-INTEGRAL-DERIVATIVE (PID) COMPENSATOR" (2011). *Theses and Dissertations--Electrical and Computer Engineering*. 3. https://uknowledge.uky.edu/ece\_etds/3

This Doctoral Dissertation is brought to you for free and open access by the Electrical and Computer Engineering at UKnowledge. It has been accepted for inclusion in Theses and Dissertations--Electrical and Computer Engineering by an authorized administrator of UKnowledge. For more information, please contact UKnowledge@lsv.uky.edu.

### STUDENT AGREEMENT:

I represent that my thesis or dissertation and abstract are my original work. Proper attribution has been given to all outside sources. I understand that I am solely responsible for obtaining any needed copyright permissions. I have obtained and attached hereto needed written permission statements(s) from the owner(s) of each third-party copyrighted matter to be included in my work, allowing electronic distribution (if such use is not permitted by the fair use doctrine).

I hereby grant to The University of Kentucky and its agents the non-exclusive license to archive and make accessible my work in whole or in part in all forms of media, now or hereafter known. I agree that the document mentioned above may be made available immediately for worldwide access unless a preapproved embargo applies.

I retain all other ownership rights to the copyright of my work. I also retain the right to use in future works (such as articles or books) all or part of my work. I understand that I am free to register the copyright to my work.

## **REVIEW, APPROVAL AND ACCEPTANCE**

The document mentioned above has been reviewed and accepted by the student's advisor, on behalf of the advisory committee, and by the Director of Graduate Studies (DGS), on behalf of the program; we verify that this is the final, approved version of the student's dissertation including all changes required by the advisory committee. The undersigned agree to abide by the statements above.

David Michael Feinauer, Student Dr. Bruce Walcott, Major Professor Zhi Chen, Ph.D., Director of Graduate Studies

## CONTROL CHARACTERISTICS OF AN ALL-DIGITAL PROPORTIONAL-INTEGRAL-DERIVATIVE (PID) COMPENSATOR

### DISSERTATION

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the College of Engineering at the University of Kentucky

> By David Michael Feinauer

Lexington, Kentucky

Director: Dr. Bruce Walcott, Professor of Electrical and Computer Engineering

Lexington, Kentucky

2011

Copyright © David Michael Feinauer 2011

#### ABSTRACT OF DISSERTATION

## CONTROL CHARACTERISTICS OF AN ALL-DIGITAL PROPORTIONAL-INTEGRAL-DERIVATIVE (PID) COMPENSATOR

The digitization of classical control systems presents a number of challenges and opportunities with respect to the miniaturization, distribution, reliability verification and obsolescence of both the controller and the underlying system under control. A method for the design of proportional-integral-derivative (PID) compensators realized in the form of all-digital components is presented. All-digital refers to a system implementation that is realizable with a wide range of digital logic components including discrete digital logic elements and programmable logic devices (PLDs) such as field-programmable gate arrays. The proportional, integral and derivative components of the classical PID control law were re-envisioned in terms of frequency of occurrences or counts for adaptation to combinatorial and sequential digital logic. Modification of the control scheme around this newly formed representation of system error enables the development of a PID-like FPGA-based or PLD-based controller. Details of the design of an all-digital PID-like controller including abstract, causal block diagrams and a MATLAB® and Simulink® based implementation are presented. The compensator was simulated in a velocity tracking DC motor control application and was found to perform comparably to that of a classical PID based control. Methods for assessing the resultant stability of an all-digital PID compensated system under control are discussed.

KEYWORDS: Proportional-integral-derivative (PID) control, all-digital control, FPGAbased control, PLD-based control, frequency tracking control.

David Michael Feinauer

November 30, 2011

## CONTROL CHARACTERISTICS OF AN ALL-DIGITAL PROPORTIONAL-INTEGRAL-DERIVATIVE (PID) COMPENSATOR

By

David Michael Feinauer

Bruce L. Walcott, Ph.D. Director of Dissertation

Zhi Chen, Ph.D. Director of Graduate Studies

November 30, 2011

This dissertation is dedicated to the many educators, family members and friends who have supported me throughout its development.

#### ACKNOWLEDGEMENTS

The development of this work benefited greatly from the support and guidance of many educators, friends and family members.

In terms of direct support and impact on this work, I would like to thank my committee members for the solid preparation they provided me throughout my coursework. Particularly, I thank Professors Walcott, Zhang and Holloway for the instruction they provided me in the areas of deterministic systems theory, feedback control, optimal control theory and control of manufacturing and event systems. It was instrumental in developing this work; a work I hope is reflective of the quality of the preparation I received. I would also like to express gratitude to Professor Jaromczyk for his tutelage in the area of algorithm design and complexity analysis—it has been beneficial to my reenvisioning classical control laws in the digital realm. I am grateful to Professor Eugene Bruce, although not directly reflected in this work, for inspiring my interest in biological systems through his biomedical signals courses. It was through this rigorous coursework that I honed my abilities to analyze information and think critically—skills that have proven critical in the conduct of research.

I have long felt that the true measure of any university is a metric that evaluates the impact the university—comprised of its people—has on the lives of the community it serves. The potential role that a university and its people can have as an agent of change in the local and broader community, for me, is one of the great appeals of life in academe. It is with this in mind that I wish to profoundly thank the members of my committee for reaffirming this belief and being exemplars of the many ways one can impact people through the university setting.

iii

Dr. Yuming Zhang has demonstrated to me the value of applying scholarly results to problems existent in industry and the opportunity for transferring one's endeavors into the broader community. Most impressively, he has shown that one can approach all things with an overall jolly temperament that I find inspiring.

Dr. Larry Holloway has shown me the possibility for one to evolve one's academic pursuits based on changing market trends and the broad impact one can ignite by expressing a vision for an organization and inspiring its people to take action towards a realization of that vision.

Dr. Jerzey Jaromczyk has inspired me by his embrace of the role of mentor and advisor as demonstrated by the genuine, lasting interest he takes in his students with respect to their current and future pursuits. Throughout the years I was delighted by his inquiries as to my current path and progress in life—long after that first class I followed under him.

Dr. Suzanne Smith exemplifies the direct impact one's research can have on a state and the future career opportunities for its students. I'm continually inspired by both the volume and results of the active projects supported by Dr. Smith and the effort she takes to ensure that the endeavors she supports create numerous opportunities for student involvement at all levels.

Lastly, Dr. Bruce Walcott has confirmed the many opportunities for lasting impact one can have by supporting the local community through service to its people— be it directly through outreach endeavors or indirectly by way of positive changes owing to active service on steering committees. The number of varied interests including scholarly research, teaching, community outreach, entrepreneurship and charity successfully balanced by Dr. Walcott affirms my interest in further academic pursuits.

iv

Collectively and individually, my committee members have served me well as role models and I expect they will continue to do so in my future pursuits. For this I am thankful.

I would be remiss without mentioning the encouragement, support and prodding of many family members and friends that ultimately made the completion of this work possible. I would especially like to acknowledge my parents for their continual love and support throughout this and all my endeavors. I am grateful to Jen Eli, Weston Johnson, Pat Quillen, Casey Harr, Dr. Jane Riggs and Jennifer Doerge for our many interactions during my graduate studies at UK; the experience would have been wanting in their absence.

Lastly, I am thankful to Dr. Bruce Walcott and Mrs. Katherine Walcott for their encouragement and support of my personal and professional development throughout my time at the university. Dr. Walcott, for embracing my diverse pursuits and meeting the ebbs and flows of my progress in this work with unbounded patience, I am grateful.

## TABLE OF CONTENTS

| List of Tables                                                                                                                                                                                                                                                                      | vii                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| List of Figures                                                                                                                                                                                                                                                                     | viii                 |

| <ul> <li>I. Introduction</li> <li>II. PID Control Background</li> <li>A. Proportional–Integral–Derivative (PID) Control Background</li> <li>B. PID Methods</li> <li>i. Ziegler–Nichols</li> <li>ii. Root Locus Methods</li> </ul>                                                   | 5<br>                |

| <ul> <li>iii. Frequency Domain</li> <li>III. Motivations for an All-Digital PID Compensator</li> <li>A. PID Prevalence in Industry</li> <li>B. Trends in Industrial Control Implementation</li> </ul>                                                                               |                      |

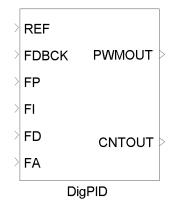

| <ul> <li>C. Proposed Problem Description</li> <li>IV. Proposed Solution</li> <li>A. All-Digital Controller / Plant / Controller Interface</li> <li>B. All–Digital PID Controller Design Framework</li> <li>i. Generation of a Proportional Error Signal</li> </ul>                  |                      |

| <ul> <li>ii. Generation of an Integral Error Signal</li> <li>iii. Generation of a Derivative Error Signal</li> <li>iv. Generation of a Combined PID Error Signal</li> <li>v. Generation of the Error and Controller Output Signals</li> </ul>                                       | 41<br>43<br>45<br>47 |

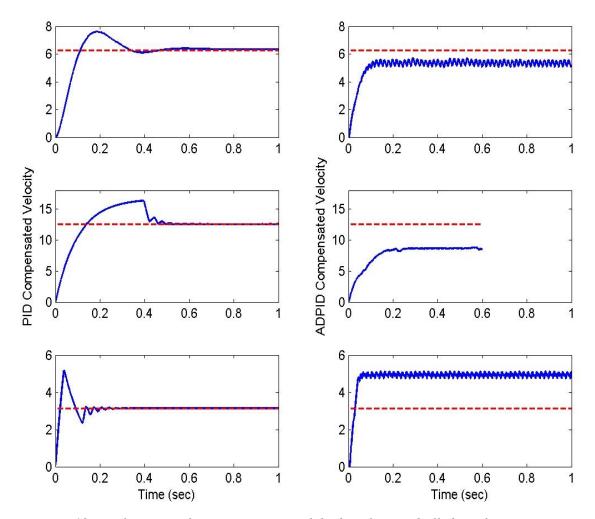

| <ul> <li>C. Procedure for Determining All-Digital PID Control Parameters</li> <li>V. Experimental Research</li> <li>A. Revisions to the All-Digital PID Compensator</li> <li>B. All-Digital PID Versus Traditional PID</li> <li>i. ADPID comparison to a Baseline System</li> </ul> | 52<br>53<br>56       |

| <ul> <li>ii. Setpoint and Parameter Sensitivity in Velocity Tracking</li> <li>iii. Baseline Comparison for an Additional DC Motor Plant</li> <li>C. Stability Discussion</li> <li>VI. Conclusions / Future Work</li> </ul>                                                          |                      |

| Appendix A<br>Appendix B<br>Appendix C<br>Appendix D<br>Appendix E<br>Appendix F                                                                                                                                                                                                    |                      |

| References                                                                                                                                                                                                                                                                          | 124                  |

| Vita                                                                                                                                                                                                                                                                                | 12/                  |

## LIST OF TABLES

| Table II-1 – Ziegler-Nichols parameters for PID controller tuning [8].                  | 10 |

|-----------------------------------------------------------------------------------------|----|

| Table II-2 – General Routh table constructed for a nth order polynomial                 | 14 |

| Table IV-1 – Truth Table of the error magnitude and sign functions                      | 47 |

| Table IV-2- Table depicting the operations required to map the error sign signal to the |    |

| appropriate scaling factors                                                             | 48 |

| Table V-1 – Parameters for DC motor mode from [10].                                     | 52 |

| Table V-2 – Performance characteristics of the PID compensated plants in Figure V-4     |    |

| and Figure V-5.                                                                         | 63 |

| Table V-3 – Armature-controlled DC motor with load specifications.                      | 73 |

| Table V-4 - Performance characteristics of the baseline and all-digital PID compensate  | d  |

| armature-controlled DC motor plant with load                                            | 79 |

## LIST OF FIGURES

| Figure II-1 – A plant under control by a negative feedback control system with input       |

|--------------------------------------------------------------------------------------------|

| U(s), output Y(s) and error E(s)                                                           |

| Figure II-2 – Block diagram of a PID compensator                                           |

| Figure II-3 – System step response depicting lag time (L) and reaction rate (R)            |

| Figure II-4 – System GH(s) with negative feedback of variable gain K 11                    |

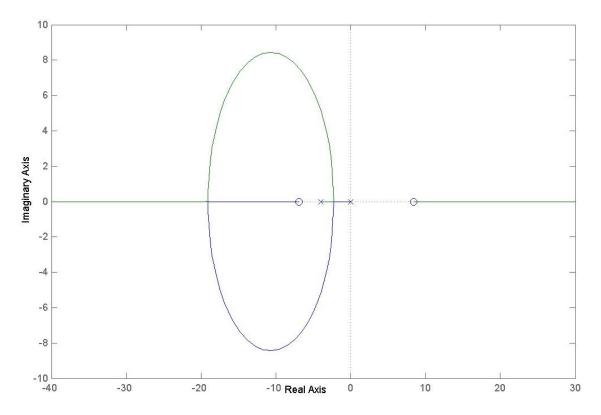

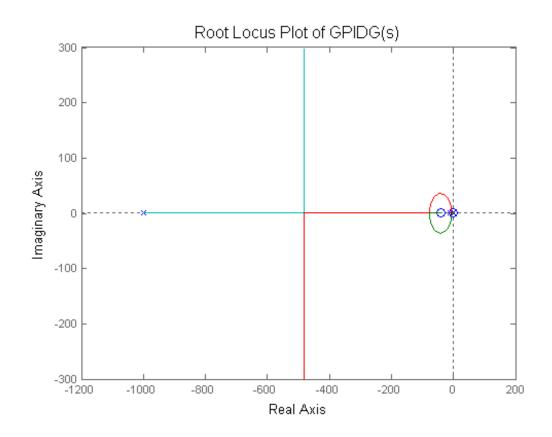

| Figure II-5 – A root locus plot of the example system with PID feedback control            |

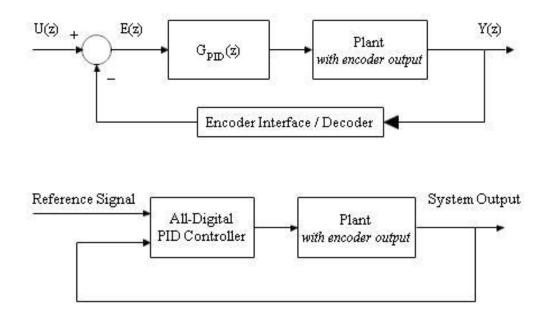

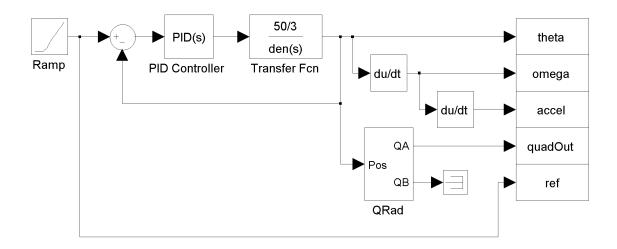

| Figure IV-1 – Block diagram of a typical plant under control by a discrete PID controller  |

| and the proposed all-digital PID controller                                                |

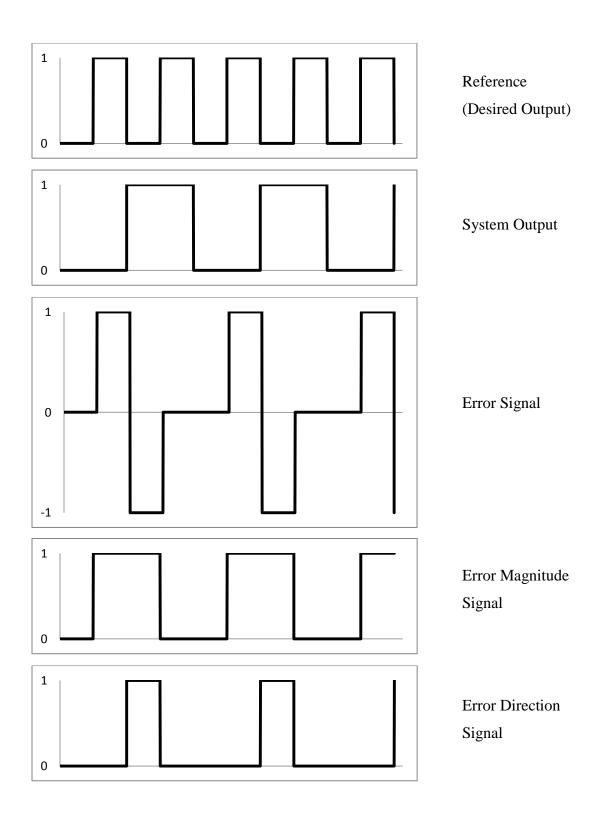

| Figure IV-2 – Diagram of five pulse trains–reference, output, error, error magnitude and   |

| error direction                                                                            |

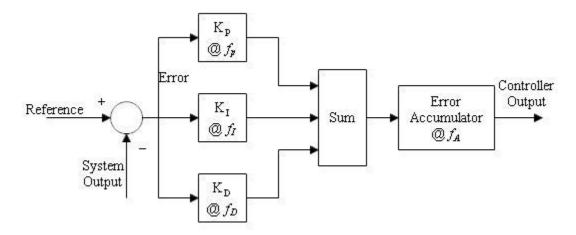

| Figure IV-3 – High-level view of the constituent components of the proposed ADPID          |

| framework                                                                                  |

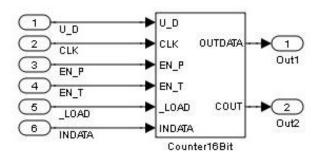

| Figure IV-4 – Block diagram of 16-bit binary up/down counter                               |

| Figure IV-5 – Detailed block diagram view of the proposed all-digital PID controller and   |

| its constituent components                                                                 |

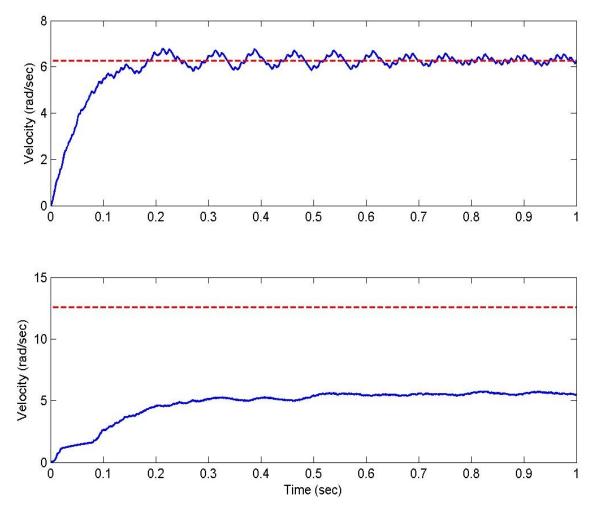

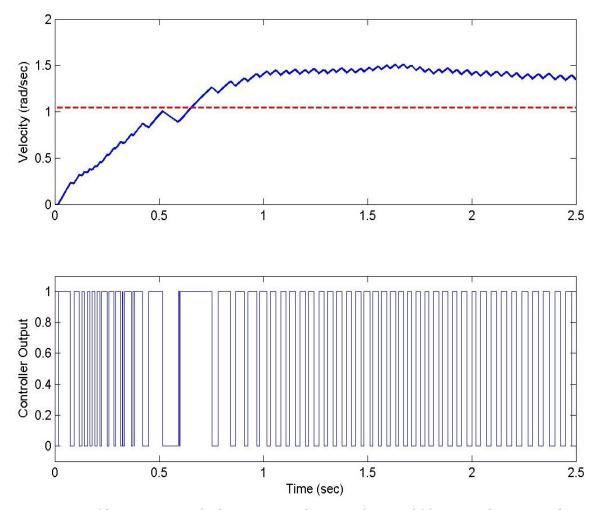

| Figure V-1 – Initial all-digital PID results for a commanded tracking velocity of 60 rpm   |

| (top) and 120 rpm (bottom)                                                                 |

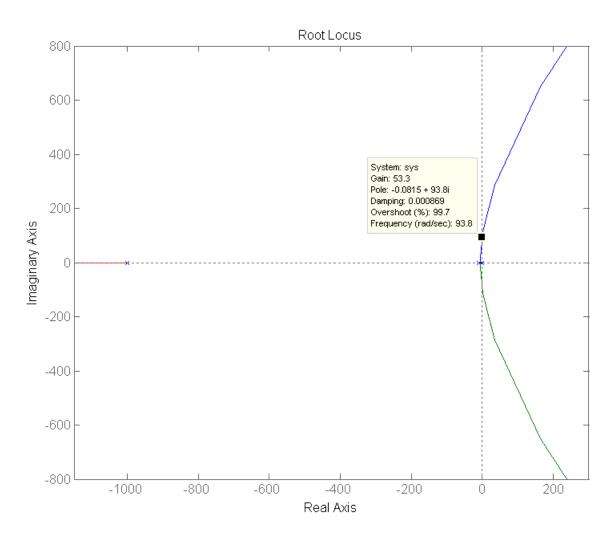

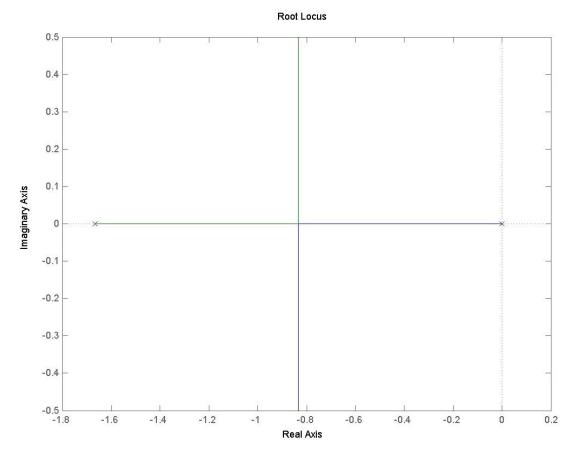

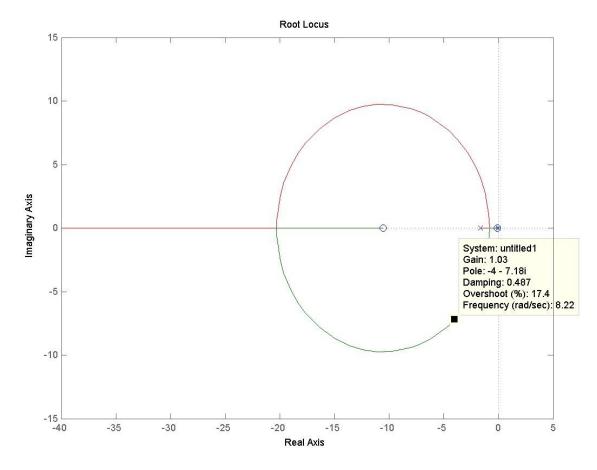

| Figure V-2 – Root locus plot of the transfer function of a DC motor plant                  |

| Figure V-3 – Root locus plot of the closed loop PID compensated DC motor system 59         |

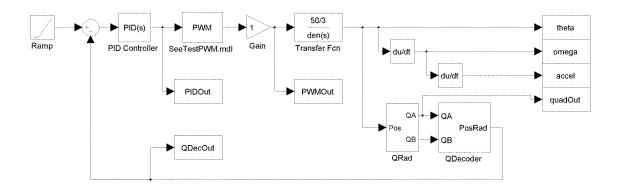

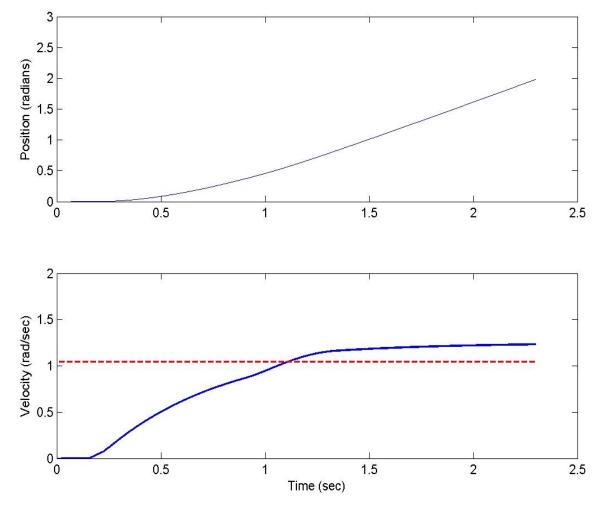

| Figure V-4 – Velocity tracking classical PID compensated DC motor                          |

| Figure V-5 – PID compensated DC motor plant model with typical controller to motor         |

| and motor to controller interfacing                                                        |

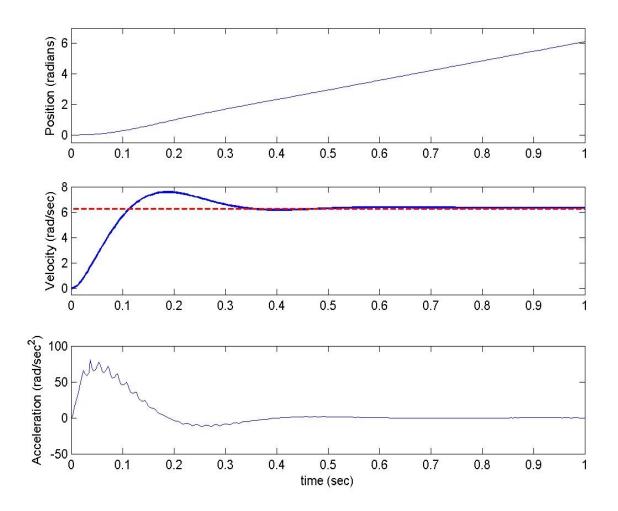

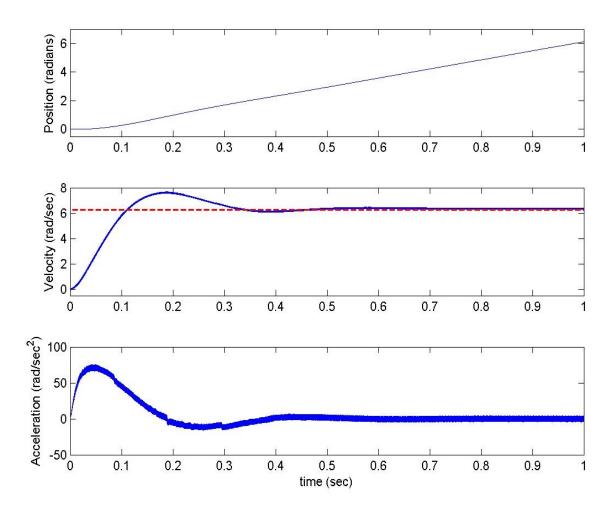

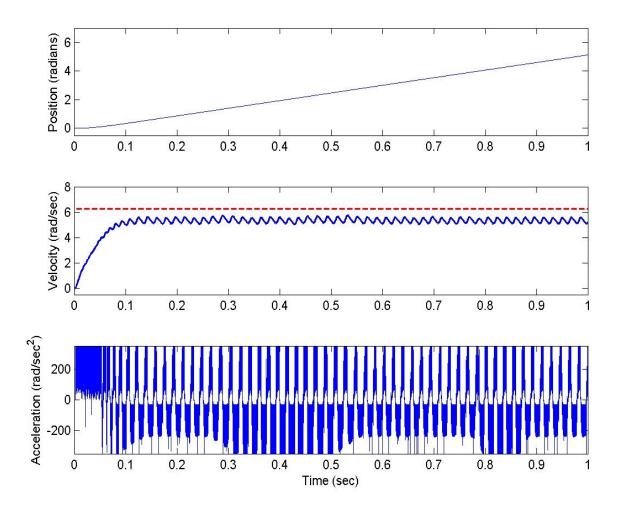

| Figure V-6 – Position, velocity and acceleration outputs from the PID compensated DC       |

| motor system                                                                               |

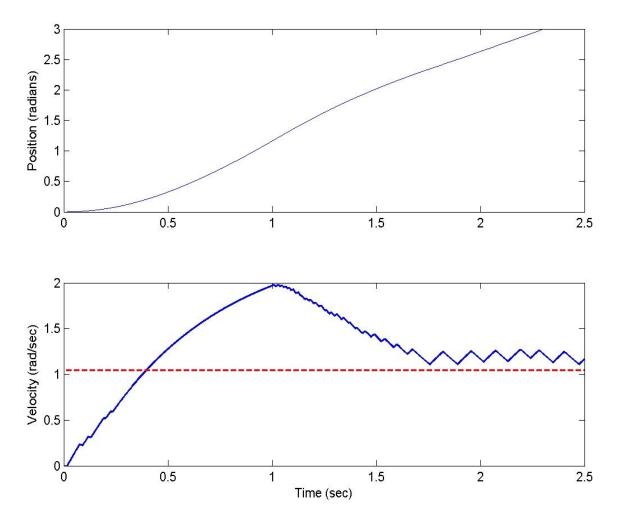

| Figure V-7 - Position, velocity and acceleration outputs from the PID compensated DC       |

| motor system with typical controller-plant interfaces                                      |

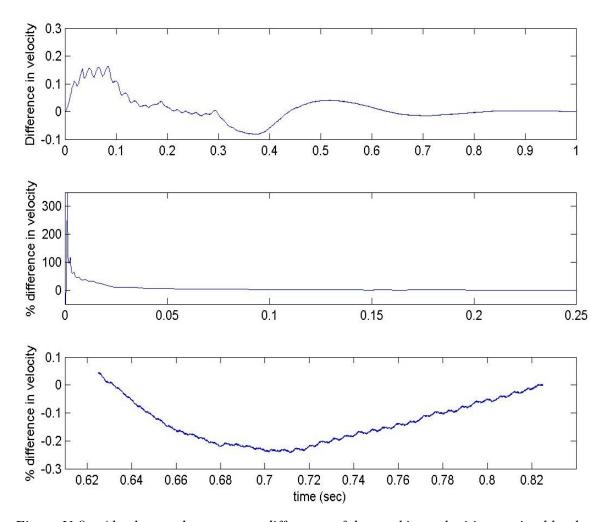

| Figure V-8 – Absolute and percentage difference of the tracking velocities attained by the |

| theoretical and modified systems                                                           |

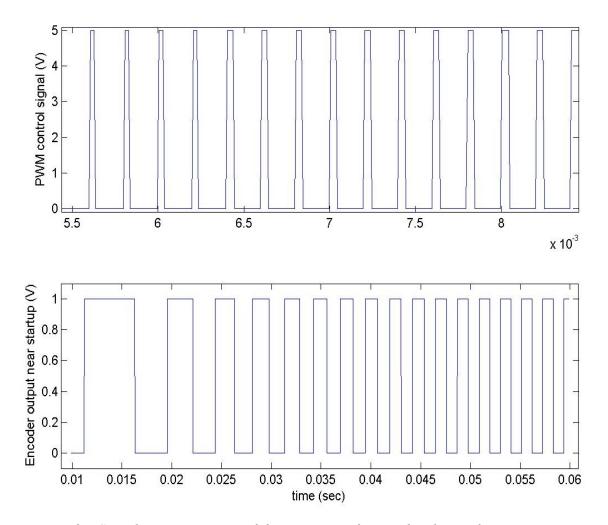

| Figure V-9 – Signals representative of the PWM interface to the classical PID              |

| compensator and one channel of the quadrature encoder output of the system plant 66        |

| Figure V-10 – Velocity tracking all-digital PID compensated DC motor                       |

| Figure V-11 – Position, velocity and acceleration outputs from the all-digital PID         |

| compensated DC motor system                                                                |

| Figure V-12 – Velocity tracking comparison of the baseline and all-digital compensators.   |

|                                                                                            |

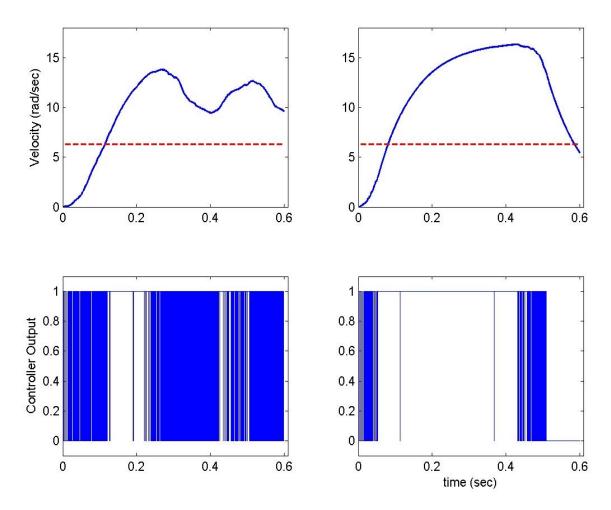

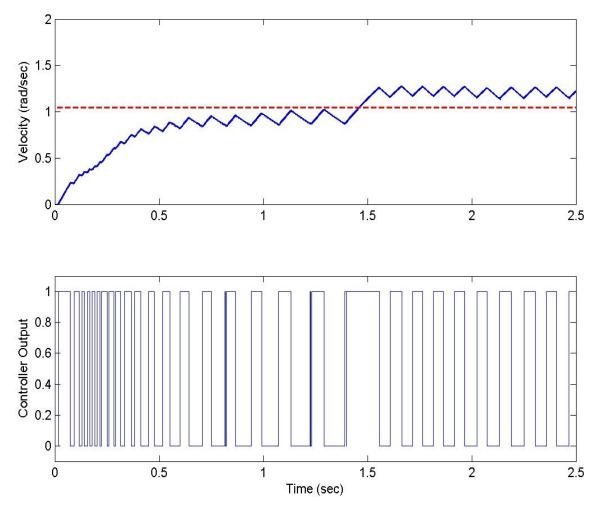

| Figure V-13 – Velocity and control outputs of a closed-loop DC motor plant with an         |

| integral gain of 0.04 (left) and 0.06 (right)                                              |

| Figure V-14 – Root locus plot of the transfer function for a DC motor plant                |

| Figure V-15 - Root locus plot of the closed loop PID compensated DC motor system 77        |

|--------------------------------------------------------------------------------------------|

| Figure V-16 – Position and velocity output of a PID compensated DC motor with load         |

| tracking a reference velocity of 10 rpm                                                    |

| Figure V-17 – Position and velocity output of the ADPID compensated DC motor with          |

| inertial load tracking a reference velocity of 10 rpm                                      |

| Figure V-18 – Proportional only control of a motor plant tracking a rotational velocity of |

| 10 rpm                                                                                     |

| Figure V-19 – PID control of a motor tracking a velocity of 10 rpm with increased          |

| derivative gain, decreased proportional gain and significantly reduced integral gain 82    |

#### I. INTRODUCTION

A common design and analysis method in engineering is the use of a "systems-based approach," where the output or operation of a plant is related to the corresponding inputs and conditions effecting the output through a description or model of the system dynamics. In bringing a concept or enterprise to fruition, design engineers are challenged with the task of optimizing a number of factors including: cost, time to market (TTM), quality and performance. The relative importance of the competing factors varies greatly from industry to industry. In the realm of commodity consumer products, for example, time to market may be considered the most critical factor to maintain competitiveness whereas in developing safety critical systems, reliability is of highest concern—one expects.

The body of knowledge known as control systems theory can aid design engineers in the development of a system, the optimization of the implementation and the resultant performance of said system with regards to the previously enumerated factors and other relevant constraints. Ideally, the available expertise and the potential for its application are considered in conjunction with other criteria when the design is in its infancy. Oftentimes it is the case that design decisions are made to minimize certain factors before considering the resources necessary for control theory to be applied to the design. Treating the various considerations individually instead of in concert, potentially limits the overall design execution with respect to reliability and other performance-related factors. Historically, the digitization of systems has afforded engineers great opportunity to achieve improved performance with respect to a diverse set of design factors.

Despite the many advances, design engineers remain challenged with balancing the aforementioned characteristics along with new or emerging concerns including energy consumption and sustainability. As systems reduce in size, become more distributed and time-to-market concerns increase the rate of component obsolescence, design engineers

and control systems engineers in particular are faced with a number of new considerations. On a different front, the trend toward "cloud" computing challenges engineers to stop distinguishing hardware devices from software methods and to think of computation as a general more unified resource.

The trends and factors discussed are not exclusive to the high-level design of the overall digital device or system; the factors propagate to the design of all constituent systems including control systems. Proportional-integral-derivative (PID) control systems are a widely used control technology with a long history. Throughout this work, the fundamental components of a classical PID compensator are re-envisioned. A method for the design of a PID compensator realized in the form of all-digital components is presented. The compound adjective "all-digital" is used herein to describe a system implementation that is realizable with a range of digital logic components. The control method and design are well-suited to an implementation with a range of programmable logic devices or discrete components. The all-digital PID (ADPID) design capitalizes on the inherently digital nature and interfaces of many modern plants to be controlled. The compensator design presented is intended for the class of digital systems that are actuated by a pulse-width modulated (PWM) input signal with a system output that can be represented by a digital pulse train when measured by a digital transducer, such as an optical encoder. The design presents a number of opportunities to address design issues related to miniaturization, distribution, performance and obsolescence.

Chapter II of this document presents a summary of classical proportional-integralderivative (PID) control theory from the theoretical-based academic domain and the practice-based industrial domain. An example of the selection or tuning of the PID control parameters based on root locus techniques is presented.

Chapter III explores the lasting dominance of PID based control in industrial applications and the trends emerging in digital, field-programmable gate array-based (FPGA-based)

control. Challenges and opportunities that remain within the well-established PID control systems domain are discussed. The obstacles that engineers face when using non-custom microcontrollers for the design of control systems are presented. Issues related to reliability and device obsolescence motivate the all-digital controller implementation proposed in this dissertation.

Details of the design of the all-digital PID-like controller are revealed in chapter IV. Classical, highly abstract, causal block diagrams of the design are presented. Implementation details of the digital design in The MathWorks *MATLAB*® and *Simulink*® *Release 2010b*, a software modeling and simulation package typical of the control systems academic domain, are described. A rule of thumb for tuning the control parameters of the proposed system is posed. The implementations for the models explained in this section are contained in the Appendices of this document and appropriately referenced throughout the discussion. The models and signal routings presented were completed with the goal of an all-digital implementation in mind. Construction of the models in this manner affords the use of the common controls simulation package for proof of concept and analysis while revealing a model that will readily map to a gate level or functional level description typical of a hardware description language (HDL) model. Such a model would be necessary for a custom digital implementation.

Chapter V introduces framework modifications to the initial design to correct the actual operation to comply with the stated functionality and for improved overall performance. The performance characteristics of the modified all-digital PID compensator design are contrasted with that of a classical PID controller when applied to models of a basic field-controlled and armature-controlled DC motor. Models for sensors required to close the loop of the control system were created. New methods for determining the error between a reference and feedback signal in terms of frequency are addressed. The ability of each controller to track a velocity (reference input frequency) is analyzed. The sensitivity of

the closed-loop system to the tuned control parameters selected under the guidance of the previously stated rule-of-thumb is analyzed. The proposed all-digital design effects a control law that is similar to a minimum time bang-off or hysteresis type controller. Methods for investigating the stability of the all-digital model are proposed.

A summary of the author's contributions is presented in chapter VI. The ability for the proposed ADPID model to the address current issues related to digital control system devices posed in chapter III is discussed. Opportunities for future work related to: further development of the all-digital model, stability analysis of the resulting model, porting of the model to an HDL-based compact ASIC design, development of an auto-tuning method for the control parameters, and implementation of the model as an FPGA-based system-on-a-chip are discussed.

#### II. PID CONTROL BACKGROUND

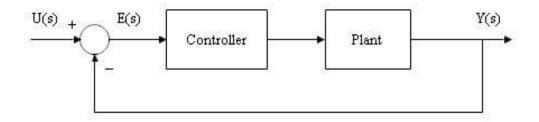

The fundamental function of automatic control is to monitor a system or process variable and to actuate a controlled response in the process or system. In a classical control system, the error between the present and desired system operating points or process control variables forms a negative feedback signal used by the controller to determine and affect the appropriate response in the system [1]. A block diagram of a negative feedback control system is shown in Figure II-1. A more advanced form of negative feedback control known as proportional-integral-derivative (PID) control utilizes negative feedback comprised of three components. Under this paradigm, the components are proportional to: the present system error, the accumulation of the error over time, and the rate of change of the error—hence the designation 'proportional-integral-derivative.' Background on the development of this control method and an in depth description of PID methods from the academic and industrial arenas are presented in sections A and B respectively.

Figure II-1 – A plant under control by a negative feedback control system with input U(s), output Y(s) and error E(s).

#### A. PROPORTIONAL-INTEGRAL-DERIVATIVE (PID) CONTROL BACKGROUND

The advent of PID control can be traced to the Taylor and Foxboro Instrument Companies in the late 1930s and the entrepreneurial culture of said companies as they assumed the roles of field-engineer and system integrator to address their customers' problems in order to sell their instrumentation and control products. Up to this time, the field of automatic control lacked a mathematical foundation and was primarily heuristic—based on observations by the instrument companies. Innovations to the PID controller led to its success and routine use as a control method by: developing methods for determining controller settings; creating techniques to assess a system's suitability for control (controllability); and improving the durability and robustness of the control system, actuators and sensors. These innovations developed out of the practice-based theory of the instrument companies and the mathematical-based foundations from the burgeoning academic field of study [2]. Today, PID control remains the most widelyused controller, pervading numerous industries, with experts roughly estimating that billions of new PID control loops are installed annually [3].

A control law with negative feedback formed by terms proportional to the system's error, the accumulation of the error over time and the rate of change of the error are known as proportional-integral-derivative control. A control law with negative feedback comprised of a subset of these three components is known simply by its constituent components (i.e. a proportional-integral (PI) control consists of a negative feedback signal proportional to the error and the accumulation of the error). A PID control law requires a control parameter (or tuning parameter) for each of the constituent control components. Classical analytical and experimental methods for determining the control parameters (or tuning the control are detailed in the following sections. The control expertise gap of the end user trying to implement the control loop contributes to the prevalence of PID because of its relative simplicity [4].

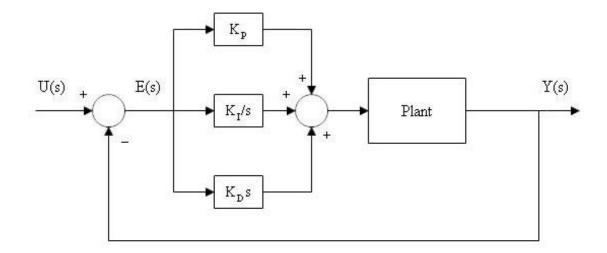

#### B. PID METHODS

A basic block diagram of a PID control system is shown in Figure II-2. A mathematical description of the system's transfer function is shown in (1). In this equation, the requisite control parameters ( $K_P$ ,  $K_I$ , and  $K_D$ ) need to be determined. The equation in (1) expresses the three parameters in "parallel" form representing the resulting effect of the compensator as the sum of the effects of the three individual components [5]. One of the early methods for determining the PID controller parameters was developed by Ziegler and Nichols in 1942 [2]. This method is demonstrated in the section below. Classical methods for determining control parameters based on root locus and frequency domain techniques are presented in the subsequent subsections.

$$GPID(s) = K_P + \frac{K_I}{s} + K_D s = \frac{K_D s^2 + K_P s + K_I}{s}$$

(1)

Figure II-2 – Block diagram of a PID compensator.

#### i. Ziegler-Nichols

The Ziegler Nichols method [6] is a technique for setting or tuning the sensitivity of a PID controller's reaction to measured error that developed out of the practice-based theory of the instrument companies and the process controls realm. The Ziegler-Nichols tuning techniques and the suitability of the method to be adapted into an auto-tuning framework contributed to the prevalence of PID control as the most widely used strategy in industrial feedback control applications [7]. The method involves a two-step process that begins with testing the response of the system to be controlled and using the resultant measurements from the test to compute the desired control parameters from a table of empirical equations [6] – [8].

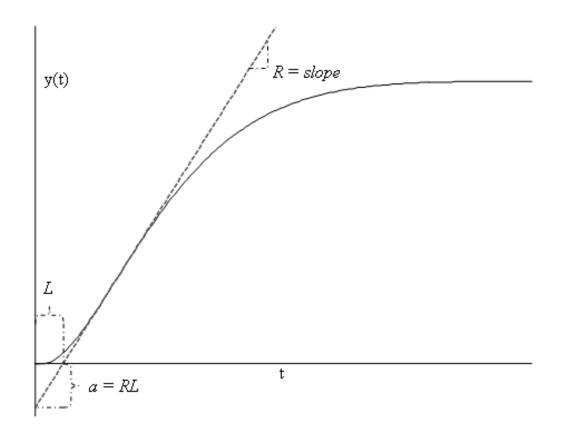

In [6], Ziegler and Nichols detailed the foundation of their two-step process by plotting the step response of the open-loop system to determine key parameters related to the "lag time" and "reaction rate" evidenced in the system output. The tunable control settings of industry standard PID process controllers were then calculated based on the experimentally determined relationship to the measured step response characteristics. The concepts of "dead time" and "rise time" that are currently pervasive in controls literature are used in some tutorials to determine the required tuning parameters; these concepts can be easily related to the lag time and reaction rate characteristics used by Ziegler and Nichols. Figure II-3 depicts the hypothetical step response of a system, and the formation of a line drawn tangent to the maximum rate of change of the system response (i.e. tangent to the inflection point). The slope of the tangent line, R, is referred to as the reaction rate. The x-intercept of the tangent line, L, is referred to as the lag time.

Figure II-3 – System step response depicting lag time (L) and reaction rate (R).

The Ziegler-Nichols tuning method can also be directly applied to the PID controller framework described above in section B. One begins by considering an equation for a PID controller, (2), that is slightly modified from the form listed in (1).

$$G_c = K_p (1 + \frac{1}{T_i s} + T_d s)$$

(2)

In this modified form, the parameters to be determined include the proportional gain,  $K_p$ , the integral time constant,  $T_i$ , and the derivative time constant,  $T_d$ . One may note that the relationship between these parameters and the parameters of the form listed in equation (1) is simply:

$$K_p = K_p, K_I = \frac{K_p}{T_i}, \text{ and } K_D = \frac{K_p}{T_d}$$

(3)

Following the four-step design process detailed in [8], one begins the process with an open-loop test of the plant excited by a step input. From the measured system response, the line tangent to the point of inflection of the system response is drawn (this will be the steepest line tangent to the curve). The y-intercept of the tangent line, *a*, and its x-intercept, *L*, are determined. Lastly, the tunable parameters  $K_p$ ,  $T_i$ , and  $T_d$ , are calculated from the heuristic relationships expressed in Table II-1. The relationship of the tunable parameters to the measured response characteristics effects a control design that may not be suitable for controlling systems where large overshoot is unacceptable due to the large control signal values and their tendency to lead to saturation typical of this tuning technique [8]. Figure II-3 displays the hypothetical step response of a system, the tangent line representing the maximum rate of change of the system, and the requisite parameters *L* and *a*, the x and y-intercepts of the tangent line, respectively. The reader may note that the parameter, *a*, is the product of the reaction rate and lag time parameters (*R* and *L*) previously discussed.

| Parameter<br>Controller Type | Kp              | T <sub>i</sub> | T <sub>d</sub> |

|------------------------------|-----------------|----------------|----------------|

| Р                            | 1<br>a          |                |                |

| PI                           | <u>0.9</u><br>a | 3L             |                |

| PID                          | <u>1.2</u><br>a | 2L             | $\frac{L}{2}$  |

#### ii. Root Locus Methods

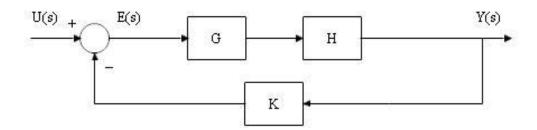

A root locus analysis of a control system evaluates how the system roots, poles and a variable closed-loop gain affect the stability of a classical system represented by a transfer function. When combined with a set of desired performance characteristics, root locus analysis can be used to determine the parameters for a feedback control system, including the three control parameters required of a PID controller. Root locus analysis results in a plot of the real and imaginary coordinates of the poles and zeros of a system's transfer function as well as a curve plotting the locus of all possible values for the system poles— assuming that the system loop was closed with negative feedback and a variable gain, *K*. By examining the locus of all possible system poles as *K* is varied from 0 to  $\infty$ , one can determine the relationship between gain and stability for the system. Values of *K* at which the root locus crosses into the right-half plane result in an unstable system.

Given a system modeled by a transfer function GH(s), a diagram of the closed loop system with negative feedback and variable gain, K, is shown in Figure II-4.

*Figure II-4 – System GH(s) with negative feedback of variable gain K.*

A root locus plot for the system in Figure II-4 begins with a graph of the poles and zeros of the open loop transfer function in the complex plane. Given any complex number,  $s = \sigma + j\omega$ , its coordinates can be graphed in the Cartesian plane with the x-axis representing all possible values for the real component,  $\sigma$ , and the y-axis representing all possible values for the complex component,  $\omega$ . An O is placed at the coordinates of all

system zeros and an X is placed at the coordinates of all system poles. A plot of the locus of all possible closed loop system poles (the roots of 1 + KGH(s) = 0) as the gain *K* is varied from 0 to  $\infty$  can be generated according to the 10 rules listed below. Construction of a root locus plot as described below relies on the Routh stability analysis discussed in the Routh-Hurwitz Stability section.

Upon completion of the root locus analysis, a PID compensator can be designed so the closed loop system will meet steady state performance criteria as described in the PID Controller Design Based on Root Locus Methods subsection. A comprehensive example of the design of a continuous-time PID control law for a simple system follows the methodology. Subsequently, a discussion of the extension of the continuous-time PID design techniques to the discrete-time domain is presented in the Discrete Time PID Controller Design subsection. This chapter concludes with a subsection on compensator design in the Frequency Domain.

#### Ten Rules For Constructing a Root Locus Plot

- I. The root locus starts at the open loop poles when K = 0.

- II. The root locus ends at the open loop zeroes when  $K = \infty$ .

- III. There are *n* root locus branches, where n represents the number of system poles.

- IV. The root locus is symmetric about the real axis,  $\sigma$ -axis. The root locus is also symmetric about any other axes of symmetry formed by the configuration of the open loop poles and zeroes.

V. As the root locus approaches the open loop zeroes at  $s = \infty$ , the angle of approach is defined by the following angle condition:

$$\angle|_{s=\infty} = \frac{180^{\circ} \times odd\#}{n-m} \tag{4}$$

where *n* and *m* denote the number of closed loop poles and zeroes, respectively, of the characteristic polynomials of the transfer function *KGH*, where  $KGH(s) = K \frac{s^m + bs^{m-1} + \dots}{s^n + as^{n-1} + \dots}$ .

VI. The asymptotes of the root locus intersect the real axis at:

$$\sigma = \frac{b-a}{n-m} \tag{5}$$

where *b*, *a*, *n* and *m* are determined from the characteristic polynomial defined in rule V.

- VII. The root locus exists on the real axis if the total number of open loop poles and zeroes to the right is odd.

- VIII. The angle of arrival / departure of the root locus at the zeroes / poles is defined as:

$$\angle zeroes - \angle poles = 180^{\circ} * odd\#$$

(6)

IX. Routh's array is used to determine for which values of the gain, *K*, the system becomes marginally stable with the root locus crossing the imaginary axis.The points at which the root loci cross the imaginary axis occur by solving

$$1 + KGH(s) = 0 \tag{7}$$

X. The break-in and break-away points are determined by setting  $\frac{\partial k}{\partial s} = 0$ , with

$$K=\frac{-1}{GH(s)}.$$

#### Routh-Hurwitz Stability

The Routh stability criterion allows for analysis of the stability of a closed loop system by classifying a system's poles instead of calculating them [9]. In order to determine stability, a Routh table is constructed using the method detailed below.

Given a system with the closed loop transfer function:  $GH(s) = \frac{N(s)}{a_n s^n + a_{n-1} s^{n-1} + \cdots}$ , the system's poles are examined and classified by forming a Routh table from the polynomial in the denominator of the transfer function. The Routh table is constructed based on the coefficients of the polynomial and a series of negative second-order determinants. Table II-2 shows a generalized Routh table for an nth order polynomial based on the equations described in [10].

| s <sup>n</sup>          | a <sub>n</sub>                                                                    | <i>a</i> <sub>n-2</sub>                                                                     | ••• | $a_0$                                                                         |  |

|-------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------|--|

| <i>s</i> <sup>n-1</sup> | <i>a</i> <sub>n-1</sub>                                                           | <i>a</i> <sub>n-3</sub>                                                                     | ••• | <i>a</i> <sub>0</sub>                                                         |  |

| s <sup>n-2</sup>        | $\frac{- a_{n-1} a_{n-3} }{a_{n-1}} = b_1$                                        | $\frac{-\begin{vmatrix} a_{n} & a_{n-4} \\ a_{n-1} & a_{n-5} \end{vmatrix}}{a_{n-1}} = b_2$ |     | $\frac{-\begin{vmatrix} a_{n} & 0 \\ a_{n-1} & 0 \end{vmatrix}}{a_{n-1}} = 0$ |  |

| s <sup>n-3</sup>        | $\frac{-\begin{vmatrix} a_{n-1} & a_{n-3} \\ b_1 & b_2 \end{vmatrix}}{b_1} = c_1$ | $\frac{-\begin{vmatrix} a_{n-1} & a_{n-5} \\ b_1 & b_3 \end{vmatrix}}{b_1} = c_2$           |     | $\frac{-\begin{vmatrix} a_{n-1} & 0\\ b_1 & 0 \end{vmatrix}}{b_1} = 0$        |  |

| :                       | :                                                                                 | :                                                                                           |     | :                                                                             |  |

| <i>s</i> <sup>0</sup>   | $\frac{-\begin{vmatrix} x_1 & x_2 \\ y_1 & y_2 \end{vmatrix}}{y_1} = z_1$         | 0                                                                                           |     | 0                                                                             |  |

*Table II-2 – General Routh table constructed for a nth order polynomial.*

The number of poles located in the right-half plane is then determined by the number of sign changes in the first column of values in the Routh table. A transfer function that produces a table without any sign changes in the first column is stable.

#### PID Controller Design Based on Root Locus Methods

The transfer function of a PID controller was defined in (1) as

$$GPID(s) = K_P + \frac{K_I}{s} + K_D s = \frac{K_D s^2 + K_P s + K_I}{s}$$

(1)

The control parameters are determined according to the following method.

- I. Develop a set of desired transient and steady state error specifications based on the application and the underlying system type (number of open loop poles located at the origin). From these specifications, determine a complex conjugate pair of closed loop dominant poles,  $s_{max}$  and  $s_{max}$ \*, that meet these specifications.

- II. Calculate *K*<sup>*I*</sup> from the steady state error specification, *ess*.

- III. Evaluate the combined system transfer function at the dominant pole and set it equal to zero to solve for the values of  $K_P$  and  $K_D$ .

$$1 + G_{PID}G(s_1) = 1 + \left(K_P + \frac{K_I}{s_1} + K_D s_1\right)G(s_1) = 0$$

$$\Rightarrow K_P + K_D s_1 = -\frac{1}{G(s_1)} - \frac{K_I}{s_1}$$

(8)

Decompose the equation above into the real and imaginary terms. Solve for  $K_D$  from the imaginary component and then solve for  $K_P$ .

An example of this design method is presented in the next section.

### Design of a Continuous-Time PID Controller

Given a system defined by the transfer function  $(s) = \frac{10}{s+4}$ , this section presents the design of a PID compensator to meet the following design criteria:

- 1. Settling time,  $t_s = 0.5$  seconds

- 2. Damping coefficient,  $\zeta = \sqrt{\frac{1}{2}} \approx 0.707$

- 3. Steady-state error,  $ess|_{ramp} = 0.1$

The method for PID compensator design outlined is applied below.

I. The desired settling time and damping coefficient for the compensated system can be used to solve for the desired dominant poles.

$$s = \zeta \omega_n \pm \omega_n \sqrt{\zeta^2 - 1} \tag{9}$$

$$t_{s} = -\frac{4}{\zeta \omega_{n}} = -\frac{4}{Re(s_{\max})}$$

(10)

$$\Rightarrow Re(s_{\max}) = -\frac{4}{0.5} = -8$$

$$\Rightarrow Im(s_{\max}) = \pm \left(\frac{8}{\sqrt{\frac{1}{2}}}\right) \sqrt{\left(\sqrt{\frac{1}{2}}\right)^{2} - 1} = \pm j8$$

$$\Rightarrow s_{max} = -8 \pm j8$$

II. The compensated system is of type 1 due to the pole at s=0 introduced by the integrator term of the PID compensator. The desired steady state error condition can then be used to solve for the integrator gain,  $K_I$ .

$$ess|_{ramp} = \lim_{s \to 0} s \frac{\frac{1}{s^2}}{\left(1 + G(s)G_{PID}(s)\right)} = \lim_{s \to 0} \frac{1}{s\left(1 + G(s)G_{PID}(s)\right)}$$

(11)

$$\Rightarrow ess|_{ramp} = \lim_{s \to 0} \frac{1}{s\left(1 + \frac{(10)}{s+4}\left(K_p + K_Ds + \frac{K_I}{s}\right)\right)} = \frac{4}{10K_I} = 0.1$$

$$\Rightarrow K_I = 4$$

III. Using the value of  $K_I$  solved for in part II, and selecting  $s_1 = -8 + j8$  as one of the dominant poles from part I, the combined system transfer function is evaluated.

$$K_{P} + K_{D}s_{1} = -\frac{1}{G(s_{1})} - \frac{K_{I}}{s_{1}}$$

(12)

$$\Rightarrow (K_{P} - 8K_{D}) + j(8K_{D}) = -\frac{1}{\frac{10}{-4 + j8}} - \frac{4}{-8 + j8}$$

$$= 0.4 - j0.8 + 0.25 + j0.25 = 0.65 - j0.55$$

$$\Rightarrow K_{D} = -\frac{0.55}{8} = -\frac{11}{160} = -0.06875$$

$$\Rightarrow K_{P} = 0.65 + 8K_{D} = 0.1$$

Thus,  $G_{PID}(s) = \frac{1}{10} - \frac{11}{160}s + \frac{4}{s} = \frac{-11s^{2} + 16s + 640}{160s}$

A root locus plot of the resultant PID compensated system is shown in Figure II-5.

GPID\*G(s) Root Locus Plot

*Figure II-5 – A root locus plot of the example system with PID feedback control.*

#### Discrete Time PID Controller Design

The previous sections detail the application of root locus based PID control design techniques in the continuous time domain, the s-domain. One technique for addressing controller design for use in the digital realm is to follow the outlined procedure for sdomain PID controller design and then convert the model into the discrete-time domain, the z-domain, using an appropriate approximation. One such approximation is known as the bilinear z-transform and is given by

$$s = \frac{2}{T} \frac{z - 1}{z + 1}$$

(13)

Depending on the application, other approximations such as a zero-order hold, ZOH, may be used when appropriate.

#### iii. Frequency Domain

The root locus design method characterizes the system response in the time-domain based on an analysis of the system poles and zeroes. Alternatively, analysis of the frequency response of both the plant and controller in terms of gain and phase can be used to design a PID controller to meet a desired set of performance specifications.

The PID design procedure in the frequency domain relies on the analysis of the frequency response of the system to be controlled. Two parameters that characterize the stability of the system in the frequency domain can be defined. The gain margin (GM) of a system is defined as the amount of gain that can be applied before a closed loop system becomes marginally stable. The phase margin (PM) of a system is defined as the amount of additional lag phase that can be added before the closed loop system becomes marginally stable.

This frequency response can be represented graphically in the form of a Bode plot. A Bode plot is a chart of the magnitude in decibels (dB) and the phase angle in degrees of the system response versus the frequency of the system input on two distinct graphs. From the Bode plot, the aforementioned stability parameters can be determined. The first parameter, the gain margin (GM), is defined as the distance of the magnitude below 0dB when the phase angle is -180°. The phase margin (PM) is defined as the distance of the phase angle above -180° when the gain is 0dB. The frequency at which the gain margin is calculated is known as the phase crossover frequency,  $\omega_{cp}$ . The frequency at which the phase margin is calculated is known as the gain crossover frequency,  $\omega_{cg}$ . These parameters are related to the classical parameters of a second-order system as defined by (14) given in [9].

$$PhaseMargin = \tan^{-1} \frac{2\zeta}{\sqrt{-2\zeta^2 + \sqrt{1 + 4\zeta^4}}}$$

(14)

Using the parameters and the relationships defined in the equation above, a PID controller can be designed by selecting a gain to meet the steady-state performance specifications and determining the other parameters from the amount of phase lag that can be added by the PID controller without making the resultant system unstable.

Copyright © David Michael Feinauer 2011

#### III. MOTIVATIONS FOR AN ALL-DIGITAL PID COMPENSATOR

In this chapter, the dominant role of PID-based control for industrial applications and the emergence of controllers based on programmable logic technology are explored. Challenges and opportunities that exist in both domains are described in section C. The limitations of a particular application of prior art are catalogued. The discussion ultimately reveals the impetus for the all-digital proportional-integral-derivative model described throughout the remainder of this work.

#### A. PID PREVALENCE IN INDUSTRY

It has been observed that PID control is one of the most prevalent control methodologies applied in industry today despite decades of advancements in modern control theory and the availability of many sophisticated, modern control technologies [11] and [12]. As previously mentioned, there are estimates that billions of new PID control loops are installed annually [3]. In the realm of process controls, it has been asserted that more than 95% of control applications still use either PI or PID control [13]. The simplicity of designing PID controller parameters is cited as a reason for PID's continued industry prevalence, given the control theory expertise gap that sometimes exists among the end users [4]. In a survey of Japanese industry [12] it was found that PID control and many advanced implementations of PID control were widely applied with high user satisfaction.

In spite of its nearly 80 year existence, PID control remains poorly understood in many applications which contributes to poor system performance. Notwithstanding the previously mentioned simplicity and rigorous development of PID control tuning techniques, complex issues such as output saturation as a result of "integrator windup" and noise induced by the differentiator combined with implementation and design complications can lead to control loop designs with undesirable performance. To address these complications, a number of auto-tuning techniques that are prevalent and simple

have resulted [3]. In a 2005 survey of controller customers, the availability of auto-tuning was specified as one of the most important features sought in a commercial controller [7]. In [13], O'Dwyer motivates the need for a more unified PID framework and notation to address the lack of understanding and the performance issues; he points out the existence of at least 408 separate sources of loop tuning rules [13]. In [5], the myriad of loop tuning rules were classified into five categories: analytical, heuristic, frequency response, optimization and adaptive tuning methods. It was also noted that nearly 80 international patents exist with specific reference to PID loop tuning methods [5]. The ability for successful application of a tuning technique can be further complicated in applications where control theory is applied for optimizing multiple objectives

#### **B.** TRENDS IN INDUSTRIAL CONTROL IMPLEMENTATION

In a survey of Scottish industry [11], Hersh found that the perceived economic factors of implementing automated control systems in an industrial setting may lead to an avoidance of them altogether—motivating a need for further development of cheap and reliable commercially available controllers. In the automotive and aerospace realms, or for any safety-critical application, industry standards require rigorous verification of control techniques, laws, implementations and tuned parameters; such verification costs often constitute more than 50% of the cost of developing the system [14]. The expensive process is very labor intensive and is often costly in terms of time-to-market as well. The ubiquitous nature of general purpose, one-size-fits-most microprocessors among many modern control implementations can also compound the problem. The reliability verification of a general purpose processor implementing numerous safety-critical control loops can be prohibitively complex and costly. Systems realizing safety or critical processes on the same processor and hardware as lower priority tasks require verification of the isolation of the subsystem in response to a fault elsewhere and the maintenance of priority for the critical system in addition to requisite overall system reliability verification. However, the development of custom digital devices for each subsystem can also be extremely expensive and time-consuming [15].

For designs using commercial-off-the-shelf processors that have invested in the requisite reliability verification, processor obsolescence creates a complex predicament for design engineers that can be costly to solve. Consumer products are often made obsolete rapidly and calculatedly to spur future sales, driving the underlying processors and general purpose digital components into obsolescence [16]. This compounds the verification hurdles present for safety-critical systems which typically have a much longer design life, in part due to the already high development costs. FPGAs utilizing "soft core" microprocessors exist as a hybrid digital implementation technology that is a general purpose, off-the-shelf component that has a microprocessor core that is "soft developed" as an intellectual property that may persist independent of a particular hardware platform or span multiple technology generations [16]. The high-level descriptions of non-processor based digital systems for implementation in programmable logic devices (PLDs) can be developed in such a way that they are also independent of specific hardware architectures, thus reducing the potential for obsolescence issues.

Recent trends reflect an increased adoption of PLDs in motion control, power electronic, communications and signal processing applications [17] and [18]. A survey of the use of PLDs for the various components of motor control (i.e. excitation circuits, feedback tachometry, torque control, etc.) is presented in [17]. Novel implementations of PLD based controllers relative to motor control including induction machine drives [19], switched reluctance machine drives [20], permanent magnet motors [21], and precision equipment such as atomic force microscopes [22] exist and are appearing more frequently in the industrial electronics and control systems literature. PLD manufactures are recognizing the role of their devices in the realm of motion control and are beginning to offer software development tools that allow for co-simulation of system designs in standard hardware description language (HDL) simulation packages along with *MATLAB* and *Simulink*, a software package frequently used by control systems engineers [17].

Technologies enabling the reduction of size (increase of component density) and the distributed implementation of systems and their components drive the development of system-on-a-chip (SoC) devices and micro-electro-mechanical systems (MEMS) which compels improvements to the cost, density and reliability of controllers for the systems and also requires improvements to precision controllers for the machines that fabricate the micro-sized devices [23]. Increased density of component integration in digital hardware combined with decreasing costs and highly developed design and simulation tools for programmable logic devices has led to their increased adoption for control engineering applications [17]. Complex programmable logic devices (CPLDs), fieldprogrammable gate arrays (FPGAs) and application specific integrated circuits (ASICs) afford varying opportunities for implementing controllers. One could consider FPGAs as generic digital logic devices that can be configured and re-configured to implement user specified digital systems. One could consider ASICs as built-to-order digital logic devices that implement engineered digital systems. The implementation of systems on an FPGA as opposed to an ASIC complements an iterative development process allowing for reprogramming, re-use and lower cost hardware design verification. Selecting an ASIC over an FPGA affords the designer a more minimal hardware implementation as the devices are built with only the required components and functionalities.

PLDs offer a number of design benefits including: privacy of proprietary architectures and components, improved performance due to the parallel nature of logic hardware resources and reduced development costs due to the ability for the design to be fully simulated and tested before being implemented with a minimal required set of hardware components [18]. In addition to these enumerated benefits, innovations in the manufacture of FPGAs have led to products that are reconfigurable in real time with integrated components beyond the programmable logic blocks. FPGAs are available with multiple integrated hard and soft core processors, RAM, signal processing and arithmetic functions as well as the integration of a small number of analog devices such as analogto-digital converters (ADCs), improving the growth of SoC devices [18].

# C. PROPOSED PROBLEM DESCRIPTION

An array of solutions for implementing digital control systems based on microprocessor and digital signal processor (DSP) technologies exist. These implementations rely on the core processor for input sampling, data storage and serial processing of the sampled and stored data for multi-component control laws as well as the actuation of a resultant controller output. The controller output is often realized in the form of a pulse-width modulated signal due to the number of low cost implementations available. The pulsewidth modulated signal is actually an analog signal realized through a number of standard circuits based on the type of modulation desired. More and more, plants or devices to be controlled are of a truly digital nature, requiring PWM input signals and providing digital output signals from a digital transducer inherent in the digital system.

Building on the apparent proclivity for digital-based controller designs, their popular use with pulse-width modulation schemes and the design of many digital plants to accept PWM inputs, one might ask if there is a way to realize the same pulse train actuation signal directly—in an all-digital manner. Additionally, recognizing the digital output resultant from a class of systems with inherent digital transducers generating output signals, one may also question whether there is a way to realize a controller whose reference input signal is driven directly by the pulse train one would expect from a digital transducer.

The prevalence and widespread recognition of proportional-integral-derivative (PID) based control technologies in industrial applications, the need for cheap, reliable and certifiable control technologies and the advantages offered by custom programmable logic devices discussed in the previous section motivate a further need for improvements in the realm of digital controller design. To address these factors, an all-digital implementation of a PID compensator is proposed. Offloading the sometimes greedy process of input sampling and serial computation of parallel, multi-objective control laws to a custom digital device presents itself as one manner of addressing the design

restrictions imposed by the current bounds of the state-of-the art. Reducing the overall real estate needed for a system by incorporating a digital formation of the pulse-width modulated signal in the custom digital device provides additional benefits. The compound adjective "all-digital" is used to designate a system design and implementation that is entirely realizable with a range of digital logic elements.

The application of phase-locked loop (PLL) techniques has been extended from the realm of communication systems to motor control techniques and they have shown to be reliable in motor speed control applications [24]. PLL devices were initially adopted for widespread use in communication systems as they allow for an output signal to track a reference signal in both frequency and phase [25]. PLLs are typically implemented as mixed systems of both digital and analog components because of the difficulty of realizing digital versions of the high frequency components [25]. In the application of PLLs loops to motor control, a novel all-digital PLL control methodology has been previously proposed and implemented [26] and [27]. It was found that although achieving steady-state tracking, the ADPLLs exhibited poor transient performance with respect to the desired specifications. It is proposed that similarly, an all-digital implementation of the widely recognized PID controller can be realized and that the multi-objective control law formed from the proportional, integral and derivative components can address transient response requirements for the closed-loop system.

Implementation of the concepts of proportional gain, integration and differentiation in the form of all-digital logic hardware requires re-envisioning a PID control law for more simplified computation and reduced complexity. The all-digital PID controller proposed would rely on the use of digital counting techniques to convert a classical PID-based compensation method from the time-domain to the frequency domain. The initial approach for an all-digital PID solution will stem from the prior graduate research described in [28]. The framework proposed in [28] is bounded by a number of factors including but not limited to its:

- restriction of the control scheme to a finite state machine-only model;

- basing the model on a 4-bit counting scheme that would rapidly reach saturation when using counting as a crude form of sampling to represent the frequency information of a signal;

- modeling of the control law around input and reference signals whose "information content" resides in the frequency domain without addressing the concept of lag among the signals;

- deviating from the core purpose and benefit of an all-digital implementation through the acknowledgement that frequency lag would need to be addressed with analog methods;

- developing a simulation model of the concept that is restricted in terms of simulating and analyzing the internal dynamics and signal routings of the proposed system;

- developing the model in a manner that it is not reusable for further investigation with respect to its application to a variety of systems to be controlled;

- and neglecting the effects of the all-digital controller on the stability of the closedloop system under control as well as neglecting to discuss the stability effects of a classical PID controller and the motivations for implementing one.

Throughout the body of this work, I will address these issues and advance the proposed concept and related design methodology by:

- capitalizing on the inherent operating states of a binary counter to map the digital controller design to a realization that can be described in a causal block diagram-like manner;

- simplifying the number of operating modes of the device as it relates to the implementation of the constituent components of a PID control law;

- improving the resolution of the counting functionality of the device;

- devising a logic based method for addressing lag between the input and reference signals;

- forming the above method in an all-digital manner;

- developing a simulation model of the concept that is far less restricted in terms of simulating and analyzing the internal dynamics and signal routings of the proposed system;

- implementing the model in a modular fashion for reuse with a number of applications;

- and discussing methods for determining the affect of the all-digital PID model on the underlying stability of the system to be controlled.

In addition to addressing the issues as described above, I will:

- compare the all-digital PID controller to the classical PID reference system as a baseline for analysis;

- develop the model with the goal of an eventual digital logic implementation of foremost concern throughout the design selection process;

- develop the model for simulation in The MathWorks *MATLAB* and *Simulink* packages to aid in suitability and stability analysis of the proposed system with respect to standards in the control systems engineering domain;

- implement additional models of hardware interface components to allow for more realistic simulation of the controller and the system under control;

- and investigate the performance of the system with respect to the presence of disturbances and the effect of higher order poles in the systems to be controlled typically unmodeled or neglected in theoretical systems.

The proposed all-digital PID (ADPID) controller framework is to be designed at a high level of abstraction—independent of a specific hardware platform, keeping the goal of an all-digital implementation in mind such that it could be realized with an FPGA, ASIC, or discrete digital logic components. A PID design framework of this nature couples the widely accepted PID controller with the advanced design and simulation frameworks of PLD-based systems for an implementation that has a minimal hardware footprint without relying on a PC or microcontroller. The parallel nature of a logical hardware implementation complements the "parallel" form of a PID-based compensator where the resulting control law is formed as the summation of the three constituent control components as opposed to a microprocessor based PID control where the control law must be implemented and applied serially. Additionally, by simplifying and offloading the PID control law computation tasks from a processor to digital hardware, one could realize a number of benefits including: simplified reliability verification due to the decoupling of the system from a multipurpose processor, reduced demand for processor bandwidth and higher sampling rates of the systems interfaced to the controller due to the dedicated hardware.

An ASIC-based implementation of the controller framework would allow for a compact, minimal controller implementation that could be available as a commercial-off-the-shelf (COTS) component or as an embedded subsystem in a larger device. A COTS implementation could further the cost effectiveness and market penetration of basic, feedback control in industrial and commercial applications. Implementing the model on an FPGA platform allows for an extension of the controller to fault recovery and self tuning techniques due to the dynamic reconfiguration and processor cores availed by the platform. Developing the model at a high level allows for an extension of the design for implementation in a MEMS or SoC device.

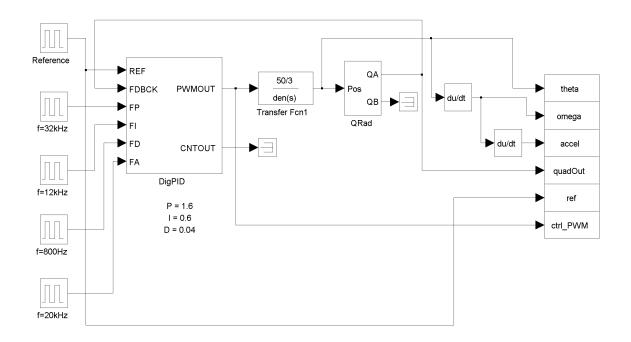

Chapter IV details the design and functionalities of the proposed controller. Initial simulations of the model proposed in chapter IV revealed a need for further design modifications. The simulation results and the revisions they motivated are discussed in the beginning of chapter V. The details of the implemented design modifications and the control characteristics of the ADPID compensator as applied to a number of example systems are presented throughout the remainder of chapter V.

Copyright © David Michael Feinauer 2011

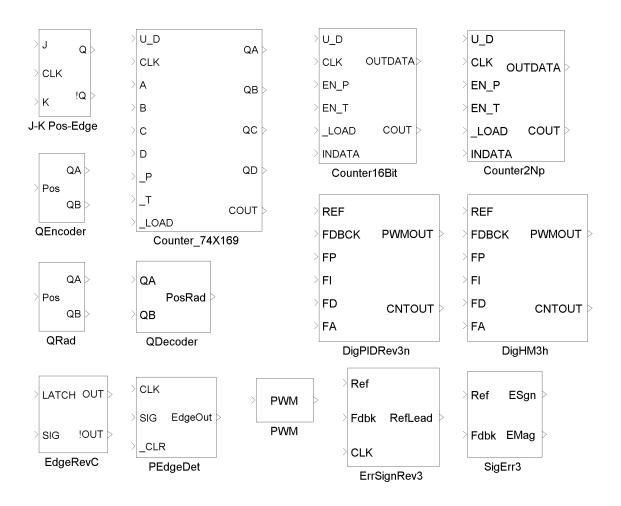

## IV. PROPOSED SOLUTION

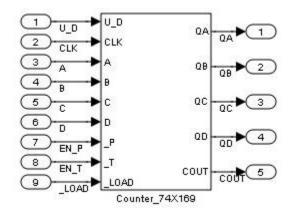

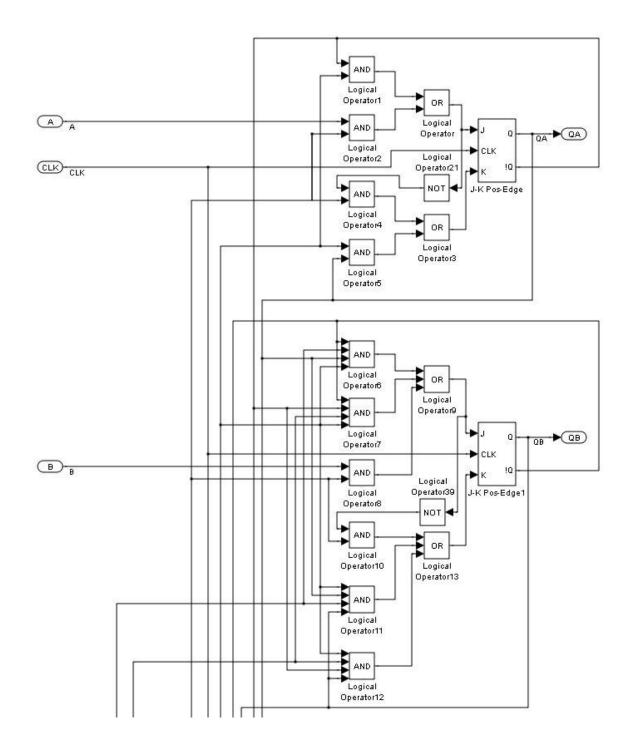

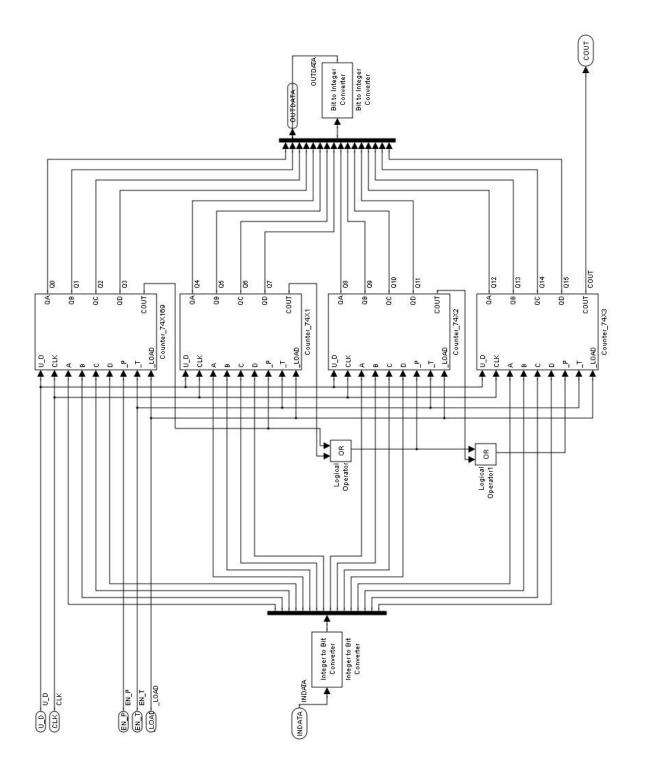

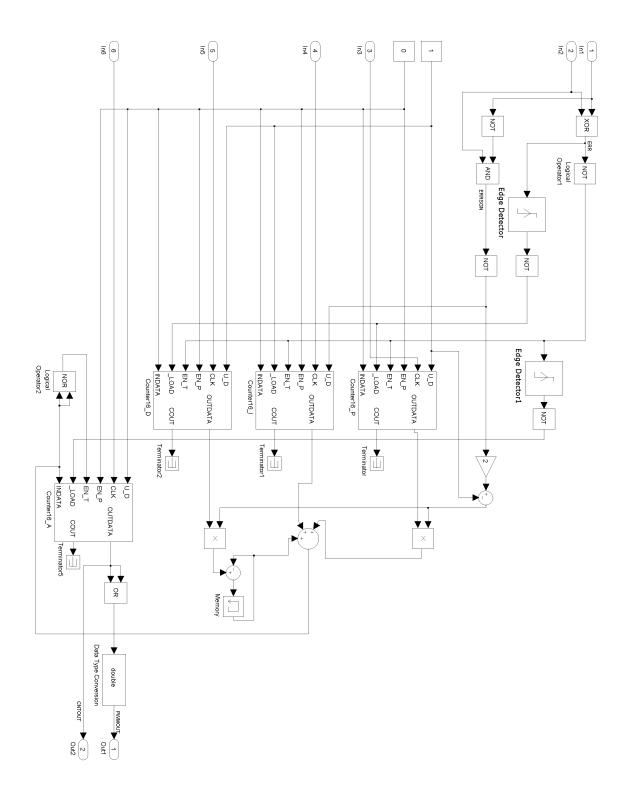

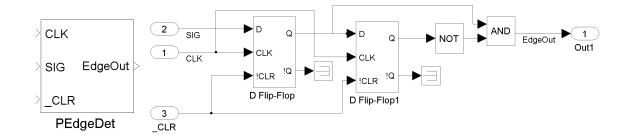

The all-digital PID controller detailed in this section uses digital counting techniques to convert a classical PID-based compensation method from the time domain to the frequency domain with an implementation based solely on digital circuit elements. The initial solution modeled is based on the foundations for the design proposed in [28]. The finite state machine model proposed in [28] was modified for simulation based on the use of edge detectors to determine transitions from the inherent states or modes of operation of the core digital component of the design, a synchronous binary up/down counter with asynchronous preset. The model was implemented to allow for the completion of an analysis of the proposed system, and for access to a richer set of analysis tools from the control theory domain. The model was also created in a modular, parameterized fashion to allow for re-use and application to additional research investigations.

The single-input, single output (SISO) model is designed to operate on the class of systems whose controller/plant interface is pulse-width modulated and whose plant/controller interface signal is a square wave—like that of an incremental encoder or other sensor. The model "converts" the signals from the time-domain to the frequency domain by characterizing the error between a reference and a feedback signal in terms of the sign of the error and the duration of the magnitude of the error. The duration (or pulse width) of the magnitude of the error between the signals is measured by an incremental binary counter. The speed at which counts occur is determined by a counting frequency parameter. In forming a proportional-integral-derivative controller, each constituent component operates on the error signal in parallel, measuring the duration of the error relative to each particular stage at a specified counting frequency. The overall control law is determined by accumulating the information from each of the stages and measuring the result of the accumulation with a counter incrementing at a distinct, base counting frequency. The ratio of the counting frequency of a given stage to the base counting frequency is related to the traditional PID control parameters or gains. In the subsequent

sections of this chapter, assumptions regarding the interface of the controller to a typical plant will be explained, the all-digital controller framework and its constituent components will be proposed, and the design procedure for determining and implementing the control parameters will be presented. Following this discussion, an abstract block diagram illustrating all of the system components and their interactions is depicted.

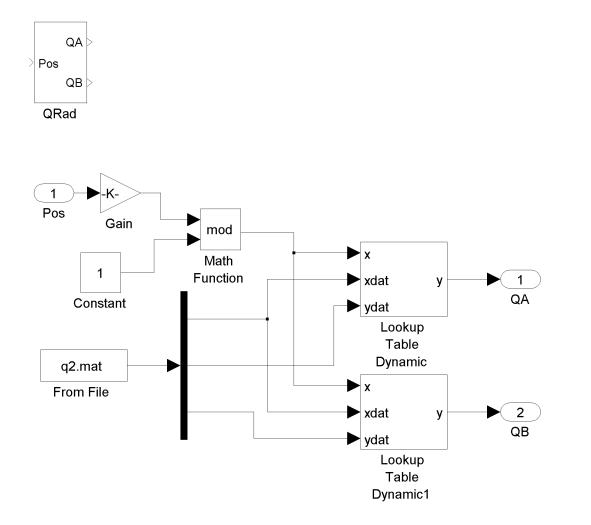

# A. ALL-DIGITAL CONTROLLER / PLANT / CONTROLLER INTERFACE

In keeping with the all-digital design objective, the controller design framework presumes that the measurable outputs from the plant to be controlled are the result of a tachometry device such as an optical encoder. Optical encoders are sensors that are widely used to detect linear and rotary positions. They utilize photoelectric elements to detect the motion of an indexed scale with respect to the photo element and produce an oscillating output signal that corresponds to the motion of the scale. For motors, a rotary optical encoder can be used to measure angular rotation or position by attaching the encoder scale to the shaft of the rotating motor or other rotating element in the drive train. In 1999, it was found that position encoders represented the third most utilized sensor in terms of number of sales [29] in the automotive industry.

In addition to the assumption of a digital encoder-based output from the system to be controlled, the proposed model similarly presumes that the input to the plant under control is implemented as a pulse-width modulated signal. The resultant pulse train from the encoder output is then fed into the proposed controller framework. The use of binary counters and other basic digital circuit components effectively converts the time domain-based output of the plant into the frequency domain. The next section will detail the digital implementation, the conversion of the system output through counting and the parameters that can be varied to affect control in the system. The formulation of the PWM output signal that actuates the plant under control will also be detailed. Figure IV-1

depicts block diagrams of a system with optical encoder output under control by both a typical discrete-time PID controller and the proposed ADPID controller.

Figure IV-1 – Block diagram of a typical plant under control by a discrete PID controller and the proposed all-digital PID controller.

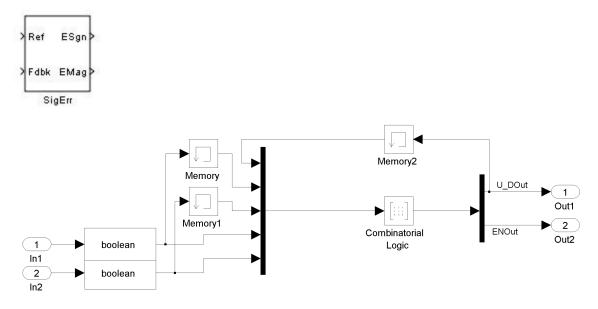

# B. ALL–DIGITAL PID CONTROLLER DESIGN FRAMEWORK

Ultimately, the implementation of any proportional-integral-derivative (PID) based controller would generate three signals: one proportional to the system error, another proportional to the accumulation of the errors over time and a third proportional to the rate of change in the error over time. The three signals are then combined to generate a control signal. The same principle components exist in the framework proposed herein. Under the proposed high level framework in Figure IV-1 above, a reference signal for the plant (or system under control) to track is compared to the actual system output. Thus, the reference signal represents the overall desired system output. The system error is defined as the difference between the two aforementioned signals. In the initial proposal of the concept [28], the error was decomposed into both a magnitude and direction signal. A digital logic formation of the magnitude of the system error was proposed and the possibility of determining the sign of the error through analog techniques was proposed and never realized. For the initial implementation of the ADPID compensator, the most basic definition of signal error based on the difference between the signal values was applied. Figure IV-2 displays two example signals and the resulting error. In addition to the three signals mentioned above, the error signal is decomposed into both a magnitude and direction signal. The result is also shown in Figure IV-2, with the value 0 representing nonnegative error, and the value 1 representing negative error. This formulation was developed to complement the proposed implementation of the model. Note that under this framework, the system output is a pulse train of variable frequency, consistent with the output of an optical digital encoder.

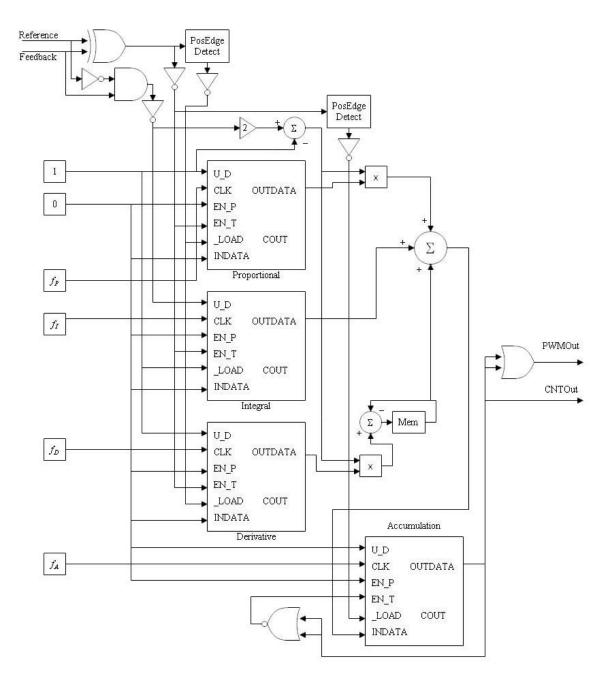

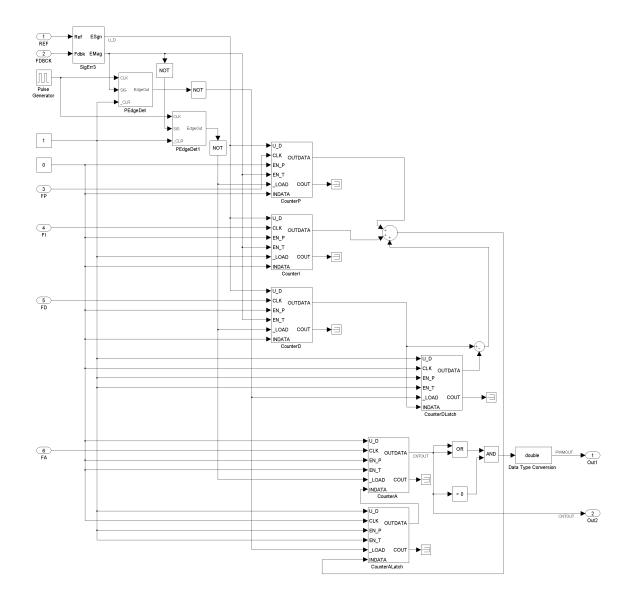

Keeping in mind the larger overall framework in Figure IV-1 above, a high-level view of the all-digital PID controller shown in Figure IV-3 depicts the "parallel" counting components that generate the proportional, integral and derivative error signals and the accumulation of the signals to create the control signal.

*Figure IV-2 – Diagram of five pulse trains–reference, output, error, error magnitude and error direction.*

*Figure IV-3 – High-level view of the constituent components of the proposed ADPID framework.*

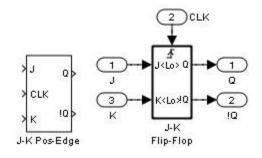

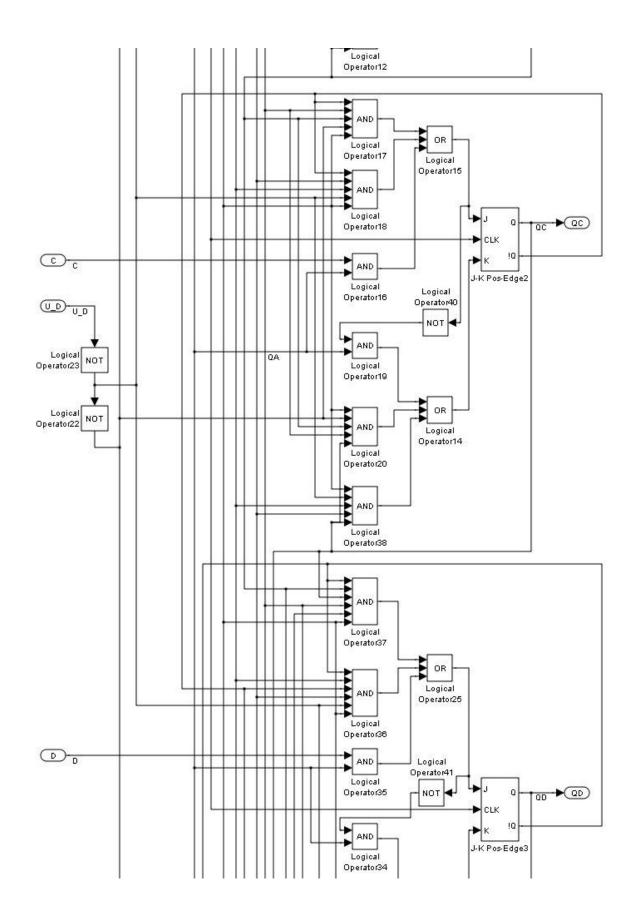

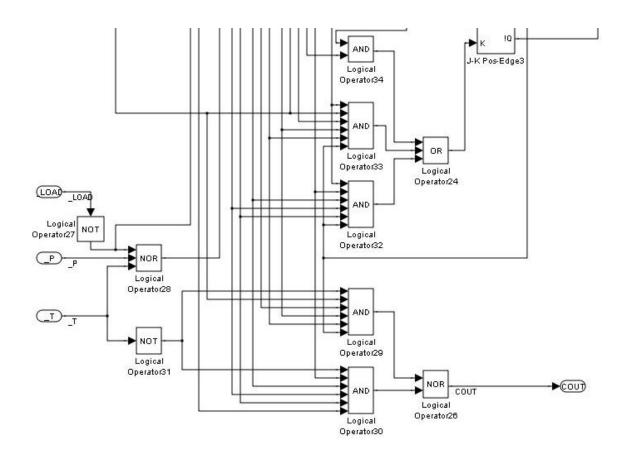

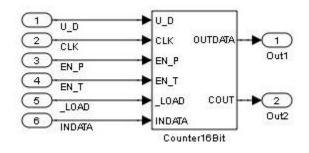

The principle component of the individual building blocks ( $K_P$ ,  $K_I$ ,  $K_D$  and the Accumulator) is a synchronous binary up/down counter. The error signal is fed into each of the constituent P, I and D components and they perform a counting operation on the error signal at speeds of  $f_P$ ,  $f_I$  and  $f_D$  respectively. The counting operations combined with variations in when and how frequently the counters reset produces results representative of the three principle components of the compensator. The results of the three subsystems are added and the combined result is counted to zero at a frequency of  $f_A$ . This resultant signal is used to generate the PWM output of the controller. Analogs to the typical control parameters  $K_P$ ,  $K_I$  and  $K_D$  can be achieved by allowing the control designer to tune the ratio of the counting frequencies  $f_P$ ,  $f_I$  and  $f_D$  to the accumulation frequency,  $f_A$ . As in the case with classic PID controller implementations, each component is generated independently which allows for a subset of the proportional, integral and derivative components to be implemented if desired. In this model, it is important to note that the accumulation stage is always required to be implemented, even in the case of a proportional only controller (P control). It is also important to note that the proposed implementation of the proportional, integral and derivative terms are parallelized and thus, grounding the control parameter for one of the constituent PID

components (implying that the corresponding control parameter in a classical PID compensator has a gain equal to zero) effects a controller instantiation with a subset of the proportional, integral and derivative control filters implemented. For example, grounding the counting frequency  $f_D$ , allows for the implementation of a PI controller, which is frequently used instead of classical PID-based control due to issues related to differentiator noise that may result in poor performance.