University of Kentucky UKnowledge

University of Kentucky Doctoral Dissertations

**Graduate School**

2007

# SIC BASED SOLID STATE POWER CONTROLLER

Xiaohu Feng University of Kentucky, xiaohuf@gmail.com

Right click to open a feedback form in a new tab to let us know how this document benefits you.

### **Recommended Citation**

Feng, Xiaohu, "SIC BASED SOLID STATE POWER CONTROLLER" (2007). University of Kentucky Doctoral Dissertations. 543.

https://uknowledge.uky.edu/gradschool\_diss/543

This Dissertation is brought to you for free and open access by the Graduate School at UKnowledge. It has been accepted for inclusion in University of Kentucky Doctoral Dissertations by an authorized administrator of UKnowledge. For more information, please contact UKnowledge@lsv.uky.edu.

# ABSTRACT OF DISSERTATION

Xiaohu Feng

The Graduate School University of Kentucky 2007

## SIC BASED SOLID STATE POWER CONTROLLER

# ABSTRACT OF DISSERTATION

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the College of Engineering at the University of Kentucky

By

Xiaohu Feng

Lexington, Kentucky

Director: Dr. Arthur V.Radun, Professor of Electrical Engineering

Lexington, Kentucky

Copyright © Xiaohu Feng 2007

### ABSTRACT OF DISSERTATION

## SiC Based Solid State Power Controller

The latest generation of fighter aircraft utilizes a 270Vdc power system [1]. Such high voltage DC power systems are difficult to protect with conventional circuit breakers because the current does not automatically go to zero twice per cycle during a fault like it does in an AC power system and thus arcing of the contacts is a problem. Solid state power controllers (SSPCs) are the solid state equivalent of a circuit breaker that do not arc and which can respond more rapidly to a fault than a mechanical breaker [2]. Present SSPCs are limited to lower voltages and currents by the available power semiconductors [8,9]. This dissertation presents design and experimental results for a SSPC that utilizes SiC power JFETs for the SSPC power switch to extend SSPC capability to higher voltages and currents in a space that is smaller than what is practically achievable with a Si power switch. The research started with the thermal analysis of the SSPC's power switch, which will guide the development of a SiC JFET multi-chip power module to be fabricated by Solid State Devices Inc. (SSDI) using JFETs from SiCED and/or Semisouth LLC. Multiple multi-chip power modules will be paralleled to make the SSPC switch. Fabricated devices were evaluated thermally both statically and dynamically and electrically both statically and dynamically. In addition to the SiC module research a detailed design of the high voltage SSPC control circuit capable of operating at 200°C was completed including detailed analysis, modeling and simulations, detailed schematic diagrams and detailed drawings. Finally breadboards of selected control circuits were fabricated and tested to verify simulation results. Methods for testing SiC JFET devices under transient thermal conditions unique to the SSPC application was also developed.

KEYWORDS: SiC, JFETs, SSPC, Thermal Analysis, Multi-Chip

Xiaohu Feng

08/24/2007

SiC Based Solid State Power Controller

By Xiaohu Feng

> Arthur V.Radun Director of Dissertation

<u>YuMing Zhang</u> Director of Graduate Studies

08/24/2007

Date

## RULES FOR THE USE OF DISSERTATIONS

Unpublished dissertations submitted for the Doctor's degree and deposited in the University of Kentucky Library are as a rule open for inspection, but are to be used only with due regard to the rights of the authors. Bibliographical references may be noted, but quotations or summaries of parts may be published only with the permission of the author, and with the usual scholarly acknowledgements.

Extensive copying or publication of the dissertation in whole or in part also requires the consent of the Dean of the Graduate School of the University of Kentucky.

A library that borrows this dissertation for use by its patrons is expected to secure the signature of each user.

| Name | Date |

|------|------|

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

DISSERTATION

Xiaohu Feng

The Graduate School

University of Kentucky

2007

SiC Based Solid State Power Controller

# DISSERTATION

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the College of Engineering at the University of Kentucky

> By Xiaohu Feng

# Lexington, Kentucky

Director: Dr. Arthur V.Radun, Professor of Electrical Engineering

Lexington, Kentucky

2007

Copyright © Xiaohu Feng 2007

### ACKNOWLEDGEMENT

My sincere thanks and heartfelt gratitude are due to my advisor, Dr. Arthur V.Radun for his professional guidance, generous support, and inspiring encouragement in the complete thesis process. I also wish to thank the dissertation committee members who are not listed here. They improved the thesis at the final stage.

I thank my parents for their support and belief in me. And, thanks are extended to my friends, both in China and in the United States, for their support. Lastly I'd like to express my great appreciation to my wife, Lei Wang, for bringing me and sharing with me so many wonderful things in my life.

| AC  | KNOWI      | LEDGEMENT                                                              | iii        |

|-----|------------|------------------------------------------------------------------------|------------|

| Lis | t of Table | es                                                                     | vi         |

| Lis | t of Figu  | res                                                                    | vii        |

| Cha | apter1 In  | troduction                                                             | 1          |

| 1.1 | Backg      | ground                                                                 | 1          |

| 1.2 | Litera     | ture Review                                                            | 3          |

| 1.3 | SiC V      | ersus Si                                                               | 3          |

| 1.4 | Conve      | entional Electromagnetic Breaker versus SSPC                           | 10         |

| 1.5 | Sumn       | nery of SSPC Requirements                                              | 11         |

| Cha | apter2 SS  | SPC Circuit Design                                                     | 12         |

| 2.1 | Introd     | luction                                                                | 12         |

| 2.2 | SSPC       | System Design and Design Results                                       | 14         |

|     | 2.2.1      | Overview of the SSPC Design                                            | 14         |

|     | 2.2.2      | Gate Drive Design                                                      | 15         |

|     | 2.2.3      | Over Current and Over Temperature Protection Circuits                  | 20         |

|     | 2.2.4      | SSPC Switch Current and Voltage Measurement Issues                     | 23         |

|     | 2.2.5      | I <sup>2</sup> T Measurement Simulation and Test Results               | 30         |

|     | 2.2.6      | Control Logic                                                          |            |

| Cha | apter3 Pc  | ower Switch Requirements                                               | 40         |

| 3.1 | Introd     | luction                                                                | 40         |

| 3.2 | Meas       | urement of the Transient Thermal Response of a Si MOSFET               | 41         |

| 3.3 | SiC J      | FET Power Switch Modeling                                              | 52         |

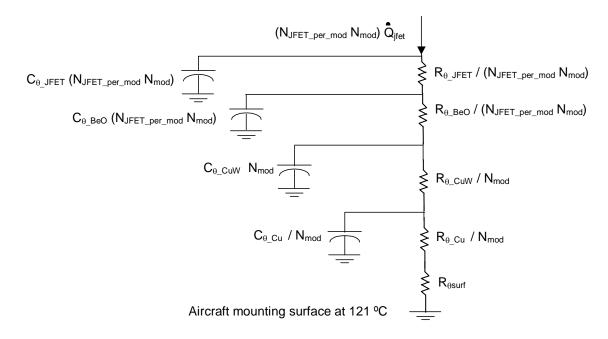

|     | 3.3.1      | Summary of SSPC Power Switch Thermal Model                             | 55         |

|     | 3.3.2      | Measurement of SiC JFET Thermal Resistance                             | 61         |

|     | 3.3.3      | Summary of SiC JFETs (9mm <sup>2</sup> active area) power switch param | neters .66 |

| Cha | apter4 Ex  | sperimental Results                                                    | 66         |

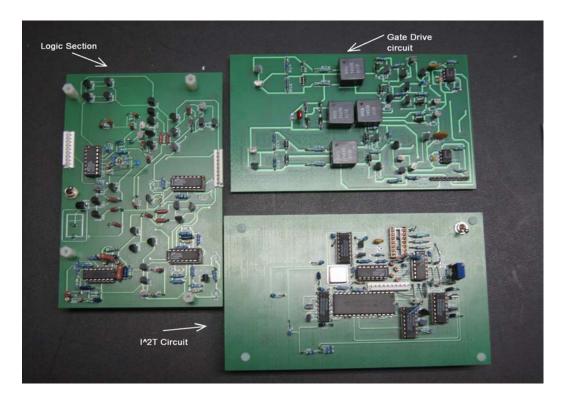

| 4.1 | Printe     | d Circuit Board Layout and Fabrication                                 | 66         |

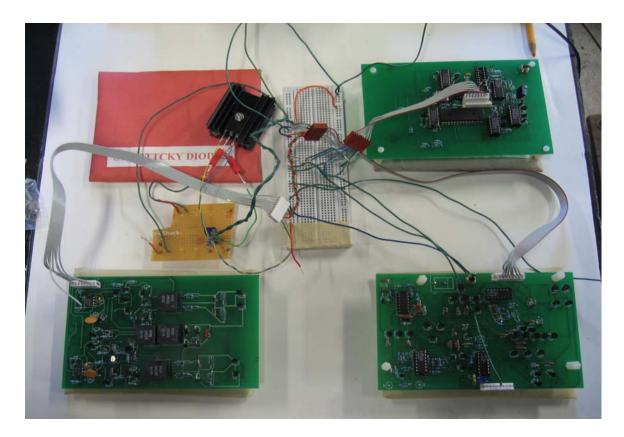

| 4.2 | Exper      | imental results                                                        | 67         |

| 4.3 | Conne      | ecting wire inductance                                                 | 75         |

# TABLE OF CONTENTS

| Chapter5 Conclusions7                                                      | 8        |

|----------------------------------------------------------------------------|----------|

| 5.1 Conclusions                                                            | 8        |

| 5.2 Future Research                                                        | 9        |

| Appendices                                                                 | 0        |

| Appendix I. Drain Current Sense Voltage Amplifier Common Mode Voltag       | ;e       |

| Calculations                                                               | 0        |

| Appendix II. VDS Sense Voltage Amplifier Common Mode Voltage Calculations8 | 2        |

| Appendix III. Specification for the 9mm2 SiC JFETSiC Chip Specification    | 4        |

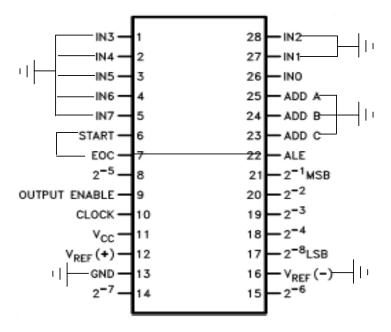

| Appendix IV. ADC0808 A/D converter                                         | 7        |

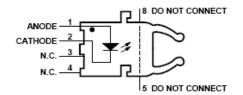

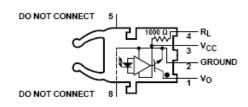

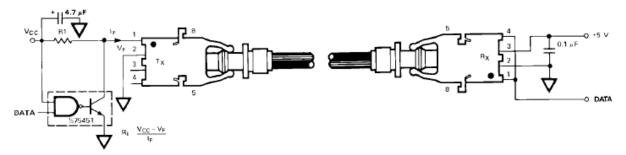

| Appendix V. The Versatile Fiber Optic Connection HFBR-0501                 | 8        |

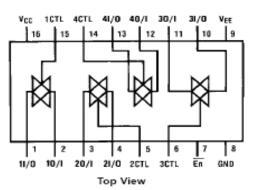

| Appendix VI MM74HC4316 Quad Analog Switch with Level Translator9           | 0        |

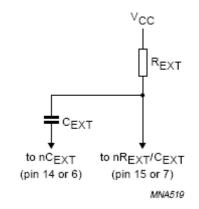

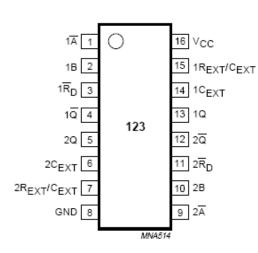

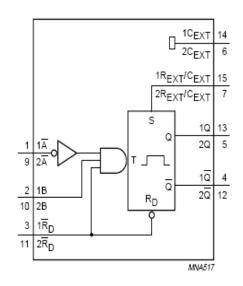

| Appendix VII. Dual retriggerable monostable multivibrator 74AHC123A9       | 1        |

| AppendixVIII. Thermal Capacitance Computation                              | <u>)</u> |

| REFERENCE                                                                  | 3        |

| VITA                                                                       | j        |

# LIST OF TABLES

| Table 1.1 Electrical and material properties of Si, and SiC at room temperatur      | e unless  |

|-------------------------------------------------------------------------------------|-----------|

| otherwise noted [19]                                                                | 4         |

| Table 2.1 Summary of the sensitivity of the current sense circuit to changes in the | he value  |

| of R1                                                                               | 25        |

| Table 2.2 Summary of the sensitivity of the current sense circuit to changes in the | he value  |

| of R2                                                                               |           |

| Table 2.3 Summary of the sensitivity of the current sense circuit to changes in the | he value  |

| of R3                                                                               |           |

| Table 2.4 Simulation and experimental results versus the input (common mode)        | voltage   |

| with rated load current (30A) when the input voltage is 270V. The voltage drop ac   | cross the |

| current sense resistor is 0.15V at this condition.                                  |           |

| Table 2.5 Simulation and experimental results versus the input voltage with 1000    | % rated   |

| load current (300A) when the input voltage is 270V.                                 | 29        |

| Table 2.6 Experimental results Vsense changes with Temperature when the input       | voltage   |

| is 270VDC                                                                           | 30        |

| Table 2.7 ADC test results and the error compared to the input value                | 35        |

| Table 2.8 DAC results and the error compared to the reference value                 | 37        |

| Table 2.9 R/S latch output and relationship to the switch status                    | 38        |

| Table 3.1 Power IRFP360LC MOSFET specification and maximum ratings                  | 50        |

| Table 3.2 Thermal Resistance of Power MOSFET IRFP360LC                              | 51        |

| Table 3.3 Comparison between Si and SiC device.                                     | 61        |

| Table 3.4 The Comparison of computed and measured time constants                    | 65        |

# LIST OF FIGURES

| Figure 1.1 Illustration of an aircraft DC electrical power system with a SSPC           |

|-----------------------------------------------------------------------------------------|

| Figure 1.2 Comparison of the Maximum Semiconductor Operating Junction Temperature       |

|                                                                                         |

| Figure 1.3 Performance Comparison for Si and SiC Technologies                           |

| Figure 1.4 SSPC Performance Comparisons for Si and SiC Technologies                     |

| Figure 1.5 Specified SSPC over current requirement                                      |

| Figure 1.6 SiC power module 270 VOLTS, 64 TO 96 AMPERES, +200°C9                        |

| Figure 1.7 Si Power module 270 VOLTS, 100 AMPERES, +125°C                               |

| Figure 1.8 Conventional thermal/magnetic circuit structures 11                          |

| Figure 1.9 Block diagram of the SSPC 12                                                 |

| Figure 2.1 SSPC Functional Block Diagram                                                |

| Figure 2.2 Basic SSPC model with showing its basic subsystems                           |

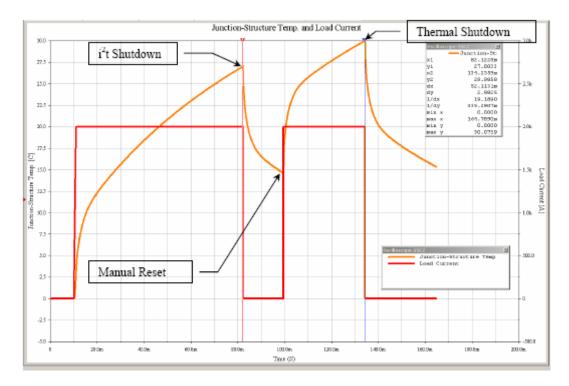

| Figure 2.3 SSPC Simulation demonstrating the $I^2t$ and thermal shutdown                |

| Figure 2.4 SSPC Gate Drive Schematic 17                                                 |

| Figure 2.5 Equivalent circuit when the upper switch is closed and lower switch in open  |

| (Vgs = 0V.)                                                                             |

| Figure 2.6 Equivalent circuit when the lower switch is closed and upper switch is open  |

| (Vgs = -40 V)                                                                           |

| Figure 2.7 The simulation results, C2=10uF and Cgs=90 nF 19                             |

| Figure 2.8 The simulations result, C1=10uF and Cgs=90nF. The upper waveform is the      |

| logic input and the lower waveform is the gate to source voltage                        |

| Figure 2.9 Temperature and Current Sensing circuit                                      |

| Figure 2.10 Figure 2.10A and 2.10B are over current sensing simulations at a rated load |

| current of 30Adc. 2.10C and 2.10D are over current sensing simulations at a rated load  |

| current of 100Adc                                                                       |

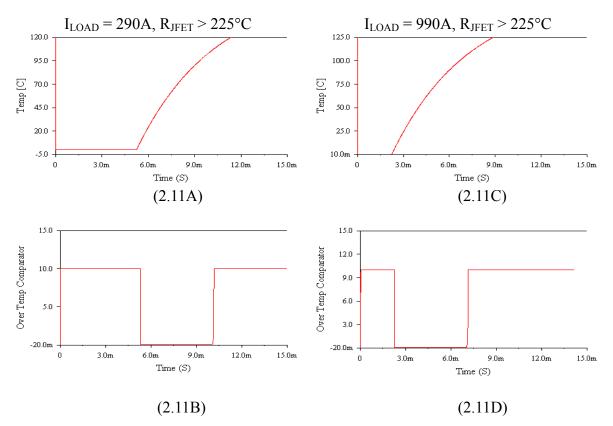

| Figure 2.11 Figure 2.11A and 2.11B are over temperature sensing simulations at a rated  |

| load current of 30Adc. 2.11C and 2.11D are over temperature sensing simulations at a    |

| rated load current of 100Adc                                                            |

| Figure 2.12 Current sense test circuit schematic                                        |

| Figure 2.13 The output voltage of the current sense circuit for different values of R125 |

|------------------------------------------------------------------------------------------|

| Figure 2.14 The output voltage of the current sense circuit for different values of R226 |

| Figure 2.15 The output voltage of the current sense circuit for different values of R327 |

| Figure 2.16 Block Diagram of the I <sup>2</sup> T circuit                                |

| Figure 2.17 Figure 2.17A and 2.17B are $I^2T$ simulation results at a 30A SSPC 100% load |

| current. Figure 2.17C and 2.17D are $I^2T$ simulation results at a 300A SSPC 1000% load  |

| current                                                                                  |

| Figure 2.18 Required SSPC trip curve                                                     |

| Figure 2.19 ADC schematic                                                                |

| Figure 2.20 Eight-bit resistive ladder DAC                                               |

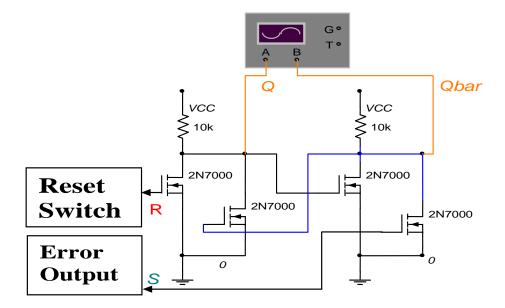

| Figure 2.21 The R/S control logic circuit                                                |

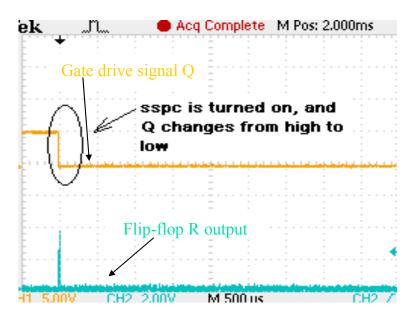

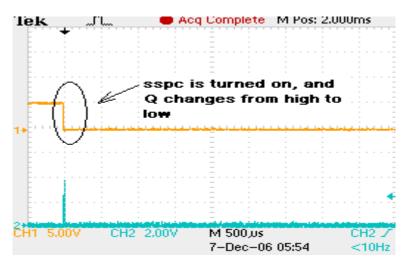

| Figure 2.22 Measured Gate drive signal Q responding to the RESET signal                  |

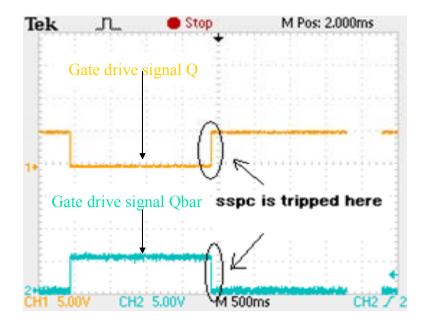

| Figure 2.23 The Q and Qbar outputs when the SSPC is turned off due to a fault condition. |

|                                                                                          |

| Figure 3.1 Schematic of the transient thermal response test circuit                      |

| Figure 3.2 Typical test circuit transient current pulses with current 31A 43             |

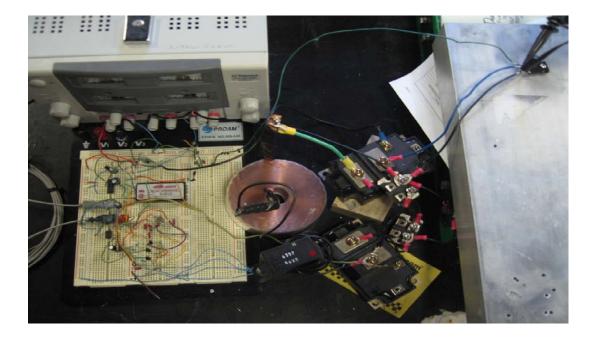

| Figure 3.3 Experimental transient thermal response test circuit used for both Si and SiC |

| devices                                                                                  |

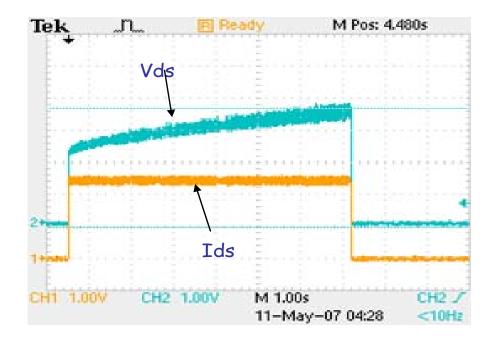

| Figure 3.4 Measured 23 A current pulse (Ids 10 A/div) and device voltage drop (Vds 1     |

| V/div) for a 6.5 s current pulse                                                         |

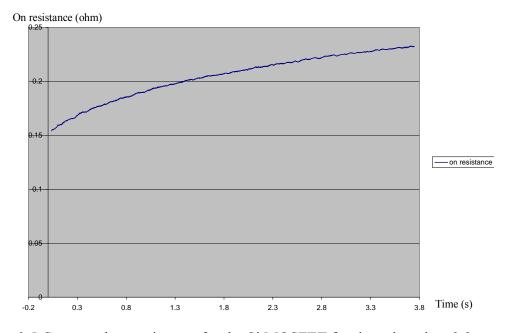

| Figure 3.5 Computed on-resistance for the Si MOSFET for times less than 3.8 second . 46  |

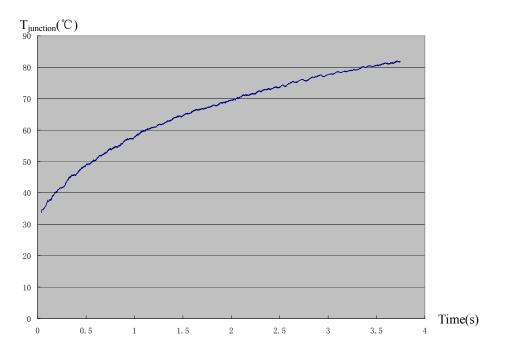

| Figure 3.6 Computed $T_j$ for the Si MOSFET data in Figure 3.5                           |

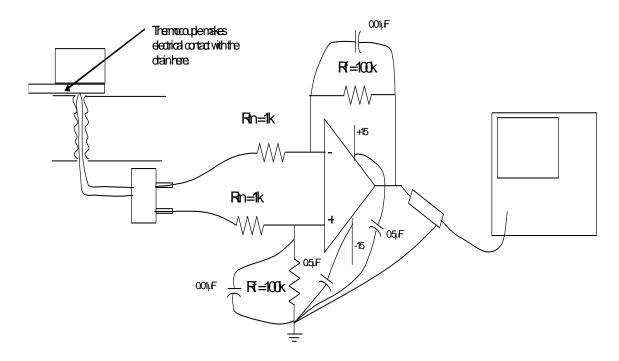

| Figure 3.7 Case Temperature Measurement Circuit                                          |

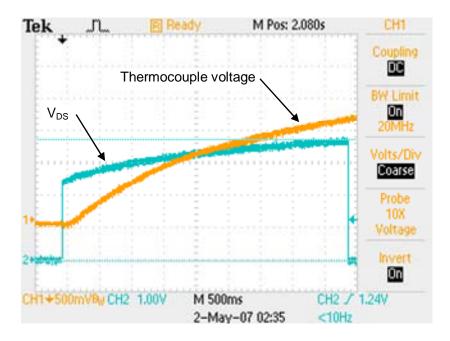

| Figure 3.8 Measured thermal couple voltage and MOSFET drain to source voltage with a     |

| constant pulse current                                                                   |

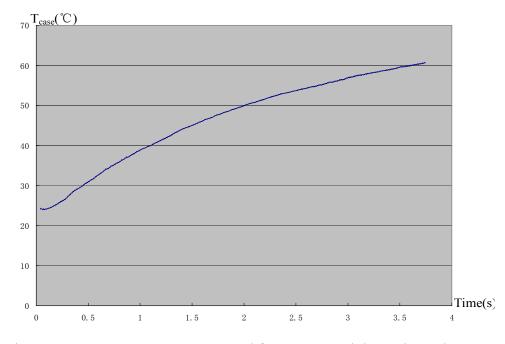

| Figure 3.9 Case temperature converted from measured thermal couple output                |

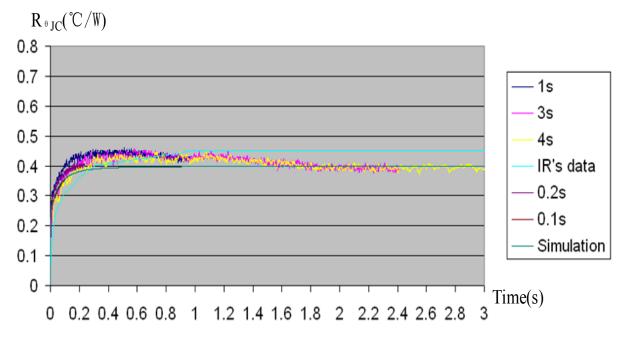

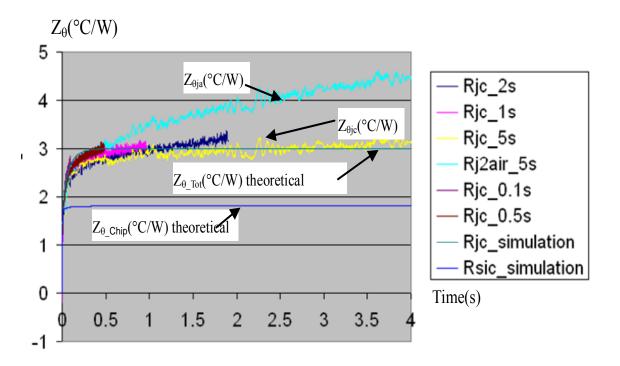

| Figure 3.10 Measured transient thermal resistance under different time scales and        |

| compared to IR's data (IR only gives maximum thermal resistance)                         |

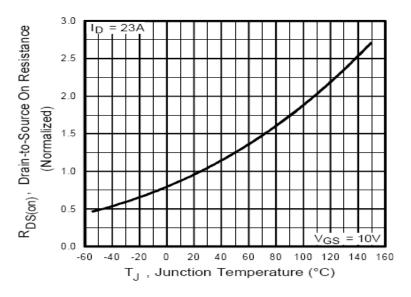

| Figure 3.11 Normalized On-ResistanceVs. Temperature                                      |

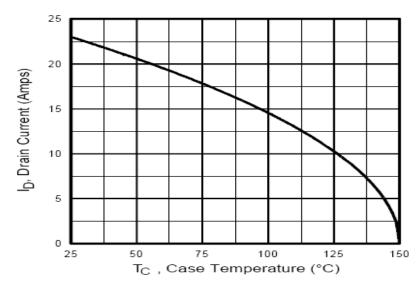

| Figure 3.12 Maximum Drain Current Vs.Case Temperature                                    |

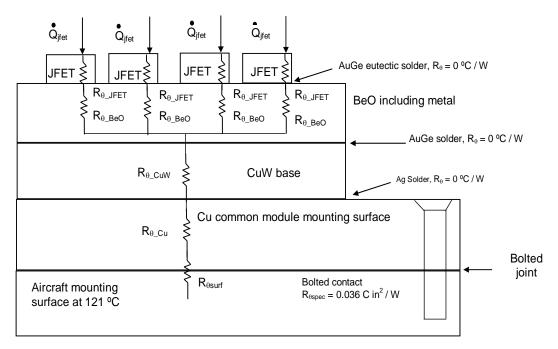

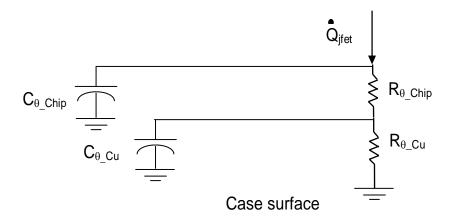

| Figure 3.13 Single Module Thermal Circuit                                                |

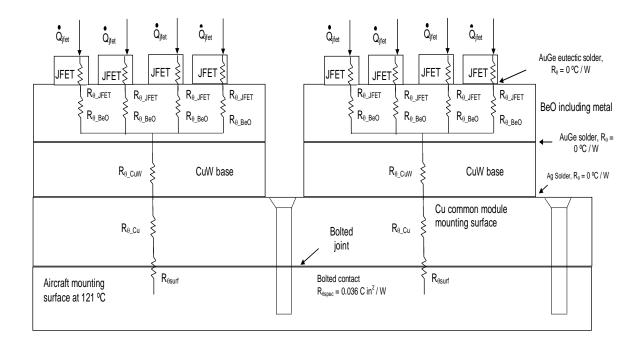

| Figure 3.14 Multi Module Thermal Circuit                                                  |

|-------------------------------------------------------------------------------------------|

| Figure 3.15 Multi Module Transient Thermal Circuit                                        |

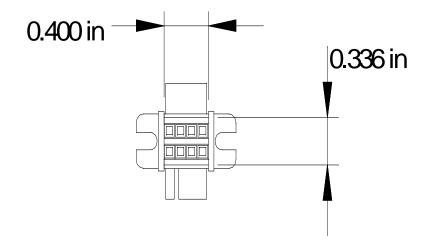

| Figure 3.16 SSPC power switch module concept                                              |

| Figure 3.17 SSPC switch concept                                                           |

| Figure 3.18 Single Module Transient Thermal Circuit                                       |

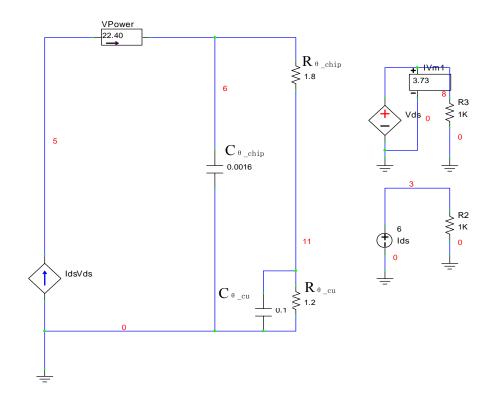

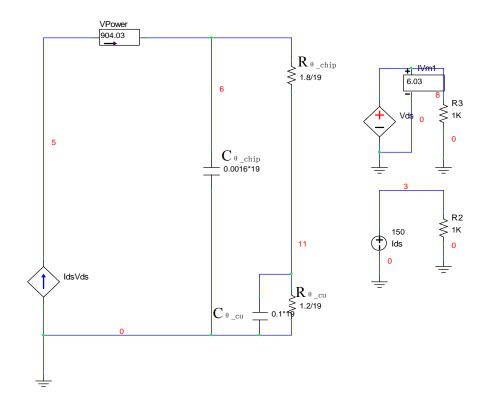

| Figure 3.19 Spice thermal model of the SiC JFET with a constant 6A drain current 58       |

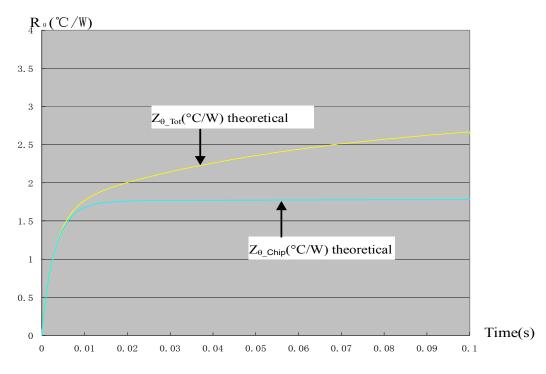

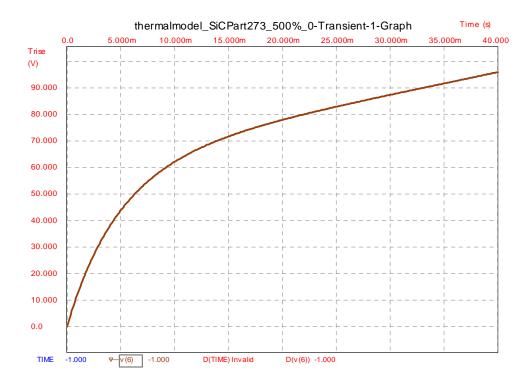

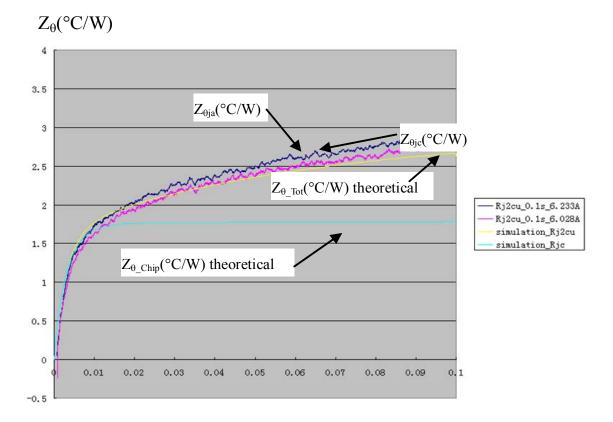

| Figure 3.20 Computed transient thermal impedances versus time with 6A drain current       |

| under 0.1 second                                                                          |

| Figure 3.21 Thermal model circuit for predicting temperature rise for 19 individually     |

| packaged SiC JFET chips in parallel                                                       |

| Figure 3.22 Temperature Rise Simulation Results For 500% rated current and 40mS 61        |

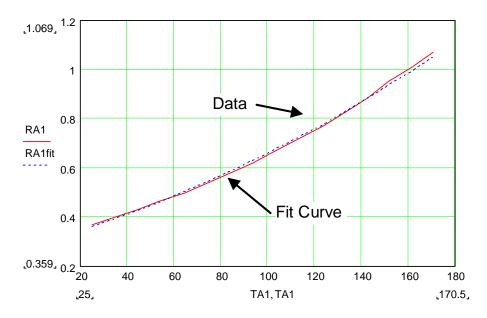

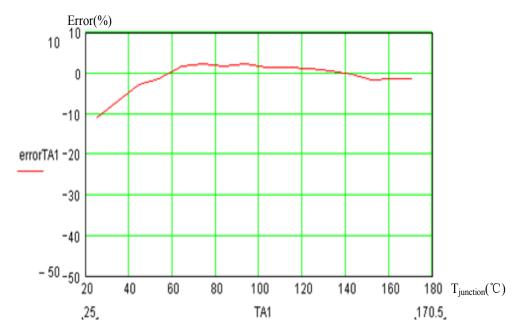

| Figure 3.23 Measured SiC JFET on-resistance and curve fit plot versus junction            |

| temeprature                                                                               |

| Figure 3.24 The error between the least square curve and the measured data                |

| Figure 3.25 Measured transient thermal resistances with different time scales and         |

| compared to simulation results                                                            |

| Figure 3.26 Measured transient thermal resistances under 0.1 second and compared to       |

| simulation results                                                                        |

| Figure 4.1 Three printed circuit boards developed for the SSPC                            |

| Figure 4.2 the Integration of the three fabricated boards with a Si MOSFET 67             |

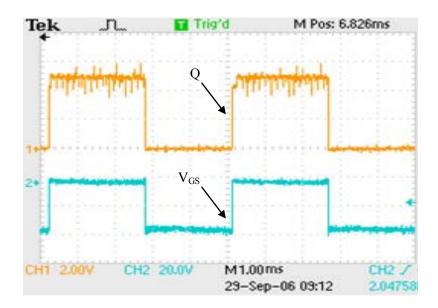

| Figure 4.3 Experimental results for the SSPC gate drive circuit with C1 in the gate drive |

| equal to10uF and $C_{GS}$ =90nF. The upper waveform is the logic input and the lower      |

| waveform is the gate to source voltage                                                    |

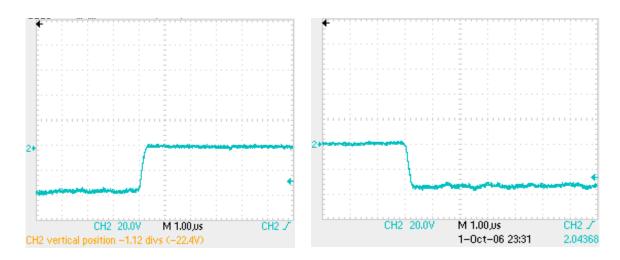

| Figure 4.4a Rise time of $V_{GS}$ , 1us/div. Figure 4.4b Fall time of $V_{GS}$ , 1us/div  |

|                                                                                           |

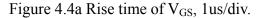

| Figure 4.5a The delay is 680ns during rise time. Figure 4.5b The delay is 920ns during    |

| fall time                                                                                 |

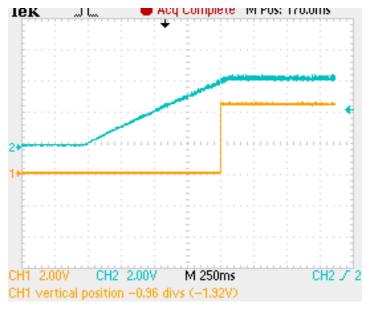

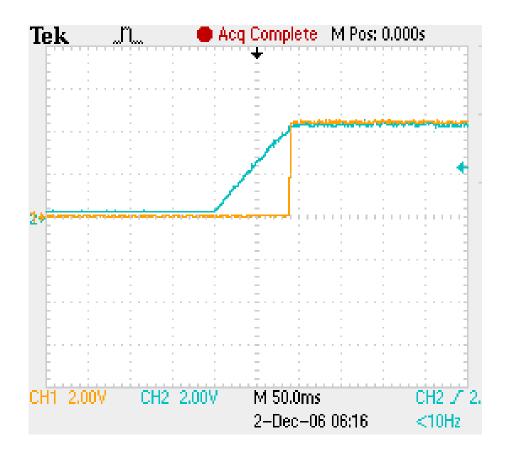

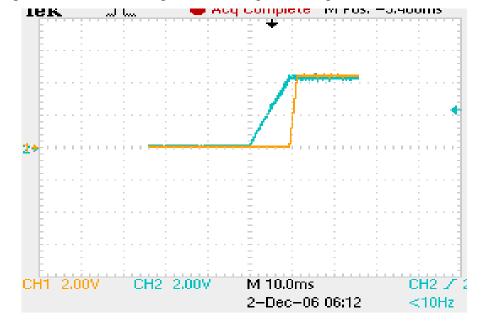

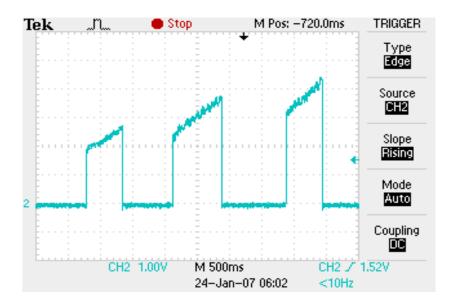

| Figure 4.6 Measured integrator and comparator output at rated current                     |

| Figure 4.7 Measured integrator and comparator output at 316% rated current                |

| Figure 4.8 Measured integrator and comparator output at 1000% rated current               |

| Figure 4.9 Specified SSPC trip curve                                                      |

| Figure 4.10 Measured $V_{DS}$ showing it doubling as the MOSFET's junction             | temperature   |

|----------------------------------------------------------------------------------------|---------------|

| goes from 25°C to 125°C because the I <sup>2</sup> t circuit shutdown is overridden by | resetting the |

| circuit 3 times                                                                        | 73            |

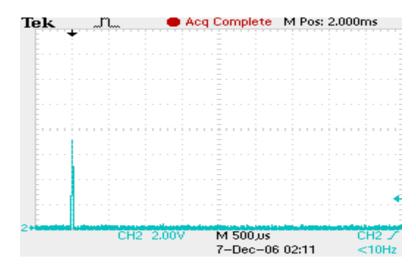

| Figure 4.11 The reset spike appears at R when the on-command is issued                 | 74            |

| Figure 4.12 The SSPC is turned on due to the change of R                               | 74            |

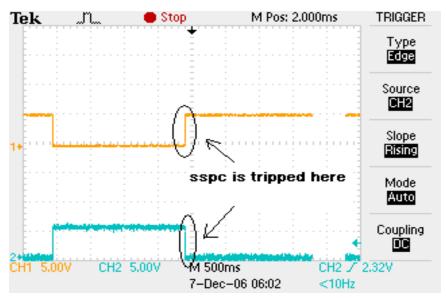

| Figure 4.13 SSPC is turned off due to fault condition                                  | 75            |

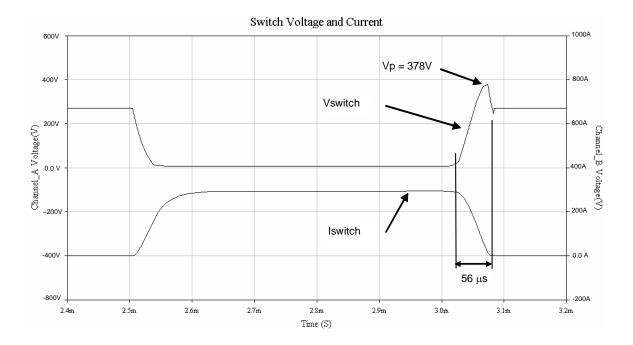

| Figure 4.14 Stray inductance spice simulation model                                    | 76            |

| Figure 4.15 Voltage drop across the SiC JFET showing the voltage spike inc             | luced by the  |

| inductance of the wire connecting the SiC JFET to the power supply and load.           | 77            |

| Figure 4.16 generated power and energy during the turn off of SSPC                     | 77            |

#### Chapter1 Introduction

#### 1.1 Background

Solid state power controllers (SSPC) were developed for power management and fault protection for aircraft power system applications [1,7]. They were first developed for the aircraft's 28Vdc power system, then for the aircraft with 115Vrms 400Hz power systems and are now under development for 270Vdc aircraft power systems. Modern aircraft have complex advanced electrical power systems that require the use of an electrical load management system [1,2]. A load management system allows the aircraft power system to make critical decisions as to which loads at any given time are mission critical, flight critical, and non-critical. The SSPC is a critical technology required to implement an electrical load management system [1,7].

In an aircraft electrical power system, the most dangerous fault is a short circuit. During a short circuit, fault the current will instantaneously increase to a value at least 10 times the rated current, a value which will cause damage to the electrical power system components. This includes overheating the power system wiring causing insulation degradation which in turn can cause arcs and arc propagation in the wiring harnesses [4]. The damage caused by such faults is minimized by turning off the fault current quickly once the fault has been detected. Faults in DC aircraft electrical power systems are especially hard to protect against since the fault current never goes to zero as it does twice per cycle in an AC system [2]. With advanced solid state device and package technology, solid state power controllers (SSPCs) can be developed for DC power systems with a turn off time that limits the energy dissipated in the wiring during a fault. This is accomplished by designing the SSPC to turn off at a chosen

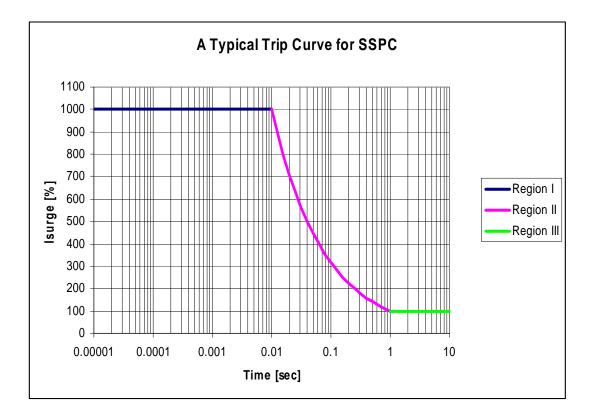

# $\int i(t)^2 dt \propto Energy$

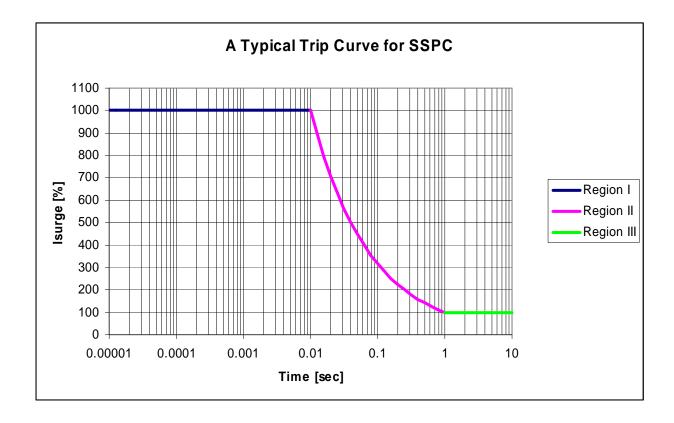

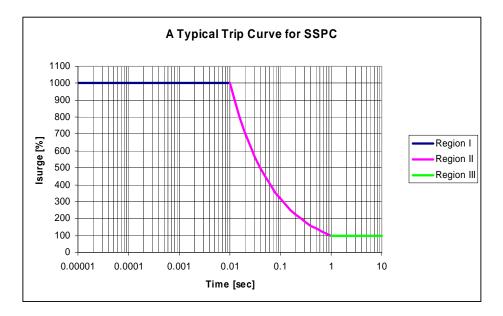

called an  $I^2T$  trip curve. A typical constant  $I^2T$  trip curve is shown in Figure 1.5.

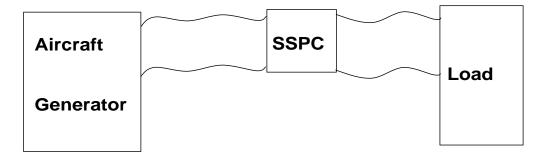

This dissertation describes research done to develop a SSPC for a 270Vdc aircraft

electrical power system. As shown in Figure1.1, the SSPC is put between the generator and the load to protect the circuitry from faults. The SSPC which is the object of this dissertation will protect against an over current that exceeds a specified maximum value, an over  $I^2T$  if the fault current is between the rated current and the specified maximum value, or an over temperature of the SSPC's main semiconductor switch by turning off the current (tripping). Thus the SSPC is essentially a smart solid-state circuit breaker which has the ability to sense current and will trip if the SSPC's current exceeds a current versus time curve. The developed SSPC can also be controlled by an external electrical signal. If the SSPC trips due to a fault it can be reset using the electrical input or a manual switch.

In the SSPC, a power semiconductor is used to turn the power being controlled on and off. The characteristics of the power semiconductor used determine the maximum current rating, power dissipation and minimum response time of the SSPC. MOSFET technology is currently used in lower current and voltage SSPCs such as DDC's SSP-21116 rated at 100V maximum with a 15 A current capability for use in 28V aircraft power systems [6,8,9]. Since available MOSFETs use Silicon (Si) they have limitations, such as high on resistance at high voltages and temperatures, high power dissipation at high temperature, a maximum 125 °C working temperature, etc.

Compared to Si, Silicon Carbide (SiC) has a number of advantages including lower on-resistance for a given chip area at high voltage and 200°C capability. A more detailed comparison between Si and SiC is given in section 1.3. In this research, the SiC JFET was chosen for the main power switching device in the SSPC to significantly improve the performance of SSPCs for use in 270Vdc aircraft power systems.

Figure 1.1 Illustration of an aircraft DC electrical power system with a SSPC

## **1.2** Literature Review

Conventional aircraft electrical power systems have used fuses, circuit breakers, and relays for circuit protection and control. The SSPC is an alternative to the conventional electromagnetic circuit breaker that uses a power semiconductor switch to protect the circuit. The solid state nature of these devices means there are no moving parts so that the SSPC's lifetime is much longer than a conventional electromagnetic circuit breaker's lifetime. Thus the SSPC improves the aircraft power system's reliability. The SSPC has the additional advantages that it has much faster response time and is less susceptible to vibrations [1,7].

Presently, SSPCs are most widely used in 28Vdc aircraft power generation and distribution applications. For example, the aerospace industry uses SSPCs built to various military specifications (Mil. Specs.) to control cabin lighting and temperature onboard aircraft [6]. SSPCs with digital interfaces are used to control 28 VDC loads, such as pumps, valves, lights, actuators, fans, to protect wiring harnesses and loads from fire due to wire shorts or insulation failures, and to monitor load operation and health [3-6].

Present research on SSPCs has focused on the stability analysis of aircraft power systems with SSPCs and how to increase the current and voltage ratings of SSPCs [1-9]. In this research the power semiconductor of choice for the main power switch has been the Si power MOSFET. As discussed before, the current and voltage capability of SSPCs using Si power MOSFETs is limited by the electrical properties of the Si.

## 1.3 SiC Versus Si

There are a number of benefits obtained by employing a SiC power semiconductor for the SSPC's main power switch. Silicon Carbide is a new semiconductor material with a much higher breakdown electric field than Si due to its higher energy gap and a material with a higher thermal conductivity than Si [18]. A comparison of the electrical properties of SiC and Si is given in Table 1.1. The performance advantages of SiC over Si in power electronics applications include lower resistance devices for the same area due to its higher breakdown electric field, higher junction temperature operation, and thus higher case temperature operation [19].

| Material property                                                                  | Si           | SiC            |

|------------------------------------------------------------------------------------|--------------|----------------|

| Electron mobility = $e (at 150 \text{ °C and } 600 \text{ V}) (cm^2/\text{V.sec})$ | 576          | 148            |

| Breakdown electric field = $E_{max}$<br>(V/cm)                                     | $3 \ge 10^5$ | $1.9 \ge 10^6$ |

| Dielectric constant = $r$                                                          | 11.7         | 9.66           |

| Built in potential (Schottky) = $V_{bs}$<br>(Volt)                                 | 0.5          | 1.1            |

| Built in potential (junction) = $V_b$<br>(Volt)                                    | 0.7          | 2.1            |

| Thermal conductivity = $K_T$ W/(cm<br>.C)                                          | 1.45         | 4.56           |

Table 1.1 Electrical and material properties of Si, and SiC at room temperature unless otherwise noted [19]

Silicon Carbide has a higher energy gap compared to Si, which gives it the advantage of significantly lower reverse leakage currents, especially important at high temperatures, compared to Si. Thus SiC can operate at higher junction temperatures. The higher energy gap of SiC compared to Si gives it the advantage of a much higher breakdown electric field compared to Si, while giving it the disadvantage that its forward p-n junction voltage drop is much greater than that for Si. Thus SiC device research to date has concentrated on devices that do not have a p-n junction, such as field effect transistors and Schottky diodes. It is junction field effect transistors that were applied in this research.

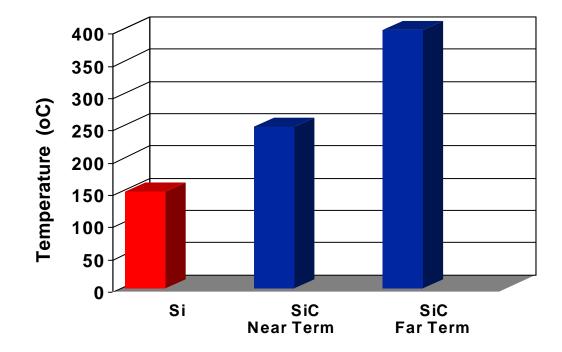

In power applications, an important consideration is the maximum junction temperature at which the device can operate. Figure 1.2 shows the maximum junction temperature of Si, SiC in the near term, and SiC in the far term. As Figure 1.2 shows, research results to date indicate that SiC has the potential to operate at temperatures as high as 400°C. In the near term, packaging considerations will limit SiC device junction temperatures to values more like 250°C. This is a significant improvement over Si's

maximum junction temperature of 150°C. In addition, a SiC device operating at a junction temperature of 250°C, which is significantly lower temperature than its theoretical maximum, should be more reliable than a corresponding Si device at operating at a junction temperature of 150°C [19]. High thermal stress is a leading cause of semiconductor failures.

Figure 1.2 Comparison of the Maximum Semiconductor Operating Junction Temperature for Si, Near Term SiC and Far Term SiC.

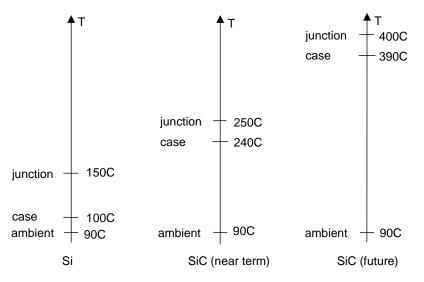

Typical thermal requirements for a system employing power semiconductors are shown in Fig 1.3. As shown, this thermal system is constrained by the maximum junction temperature of the device and the maximum ambient temperature. The difference between these two temperatures is the allowed temperature rise. This temperature rise in turn constrains the product of the system's thermal resistance and the power dissipated in the power semiconductor. The total temperature rise is made up of two main parts. The first part is the temperature drop across the device itself. The thermal conductivity of SiC is about 4.5 W / (cm  $^{\circ}$ C) compared to silicon's 1.5 W / (cm  $^{\circ}$ C). This means that a SiC

device with the same dimensions as a Si device and with the same power dissipated in it, will have 1/3 the temperature rise in the device compared to its Si counter part. Because the resistance of a SiC device for the same voltage rating is less than that of Si, the power dissipated in a SiC device whose size is equal to that of the Si device will be less than the Si device's power dissipation resulting in lower temperature rise in the SiC device. This is illustrated in Fig 1.3, where the thermal performance of a Si device is compared to that of a near term SiC device and a far term SiC device.

Figure 1.3 Performance Comparison for Si and SiC Technologies

For the work proposed here, it is the near term SiC case that is of greatest interest. In a typical application the maximum ambient temperature is around 90 °C. For a Si design, the maximum junction temperature is 150 °C and there is typically a 50 °C temperature drop from the device's junction to its case when it is operating at high power. This leaves only a 10 °C temperature rise from the ambient to the case of the device. Thus in such high power applications, the ambient is a liquid in order to keep the ambient to case temperature rise to this low value.

For a SiC design the maximum junction temperature in the near term is 250 °C. Because of the SiC device's higher thermal conductivity and its lower losses, it should be possible to design the thermal system so there is a 10 °C temperature drop from the device's junction to its case when it is operating at high power. This now leaves a 150 °C temperature rise from the ambient to the case of the device. This means that the thermal resistance from the ambient to case for the SiC device can be 15 times greater than that for the Si device. This results in the opportunity to cool the SiC device with air instead of a liquid in high power applications. This is a large system advantage since it eliminates the liquid, liquid cooling hardware, a pump, and heat exchangers. This potential advantage is an important factor for the more electric aircraft.

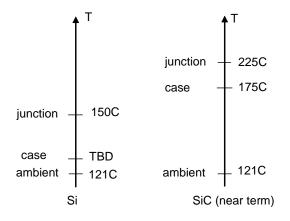

In the case of the SSPC, the maximum aircraft structure temperature is 121°C and the aircraft structure is the final ambient the heat generated by the SSPC power semiconductors must flow to. Thus the picture in Figure 1.3 must be modified as shown in Figure 1.4. Note that the maximum junction temperature of the SiC power semiconductor has been chosen to be 225°C rather than 250°C to be conservative. For this SSPC application the temperature rise of the Si device from its junction to the aircraft surface is only 29°C while the temperature rise of the SiC device from its junction to the aircraft surface is 104°C. The increased available temperature rise of the SiC device combined with its roughly 3 times greater thermal conductivity compared to Si makes a 270VDC SSPC feasible in a reasonable package size with SiC power devices while it is not feasible with Si devices.

Figure 1.4 SSPC Performance Comparisons for Si and SiC Technologies

The maximum current requirement of the SSPC is shown in Fig 1.5. This specification has three regions or boundaries. In the first, if the current exceeds 10 times the SSPC's rated current the SSPC turns off immediately. In the second region the current

is above the SSPC's rated current but less than 10 times its rated current. In this region the SSPC turns off once the integral of the current above the SSPCs rated current squared exceeds a specified value.

$$I^{2}T = \int_{i>Irate} \left(i(t) - I_{rate}\right)^{2} dt \ge I^{2}T\Big|_{\max}$$

The specified maximum value of this integral is called the I squared T ( $I^2T$ ) rating of the SSPC. In the third region, currents below the SSPC's rating, the SSPC must operate continuously. Any current above the SSPC's rated current is called a fault current.

Figure 1.5 Specified SSPC over current requirement

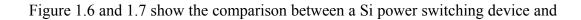

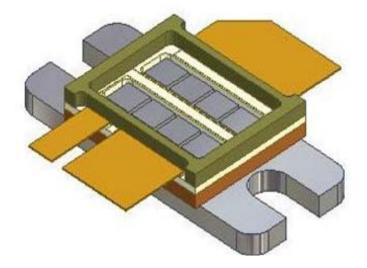

a SiC power switching device. Preliminary calculations show that a single SiC power module with 8 600V chips can work at 270V and 96A rated current with a 129C temperature rise from the aircraft structure to the SiC junction. For similar performance 8 Si power modules with a total of 64 chips with the same area as the SiC chips in parallel to work at 270 volts and 100A rated current with a 29C rise from the aircraft structure to the Si junction. Thus a silicon carbide (SiC) based solid-state power controller (SSPC) has smaller size and thus weight where high voltage and current are required.

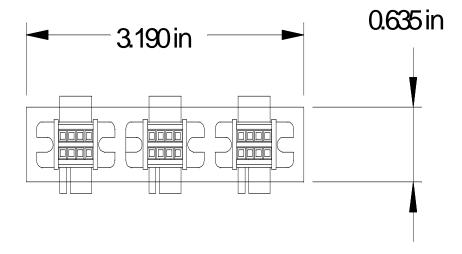

Figure 1.6 SiC power module 270 VOLTS, 64 TO 96 AMPERES, +200°C

Figure 1.7 Si Power module 270 VOLTS, 100 AMPERES, +125°C

#### 1.4 Conventional Electromagnetic Breaker versus SSPC

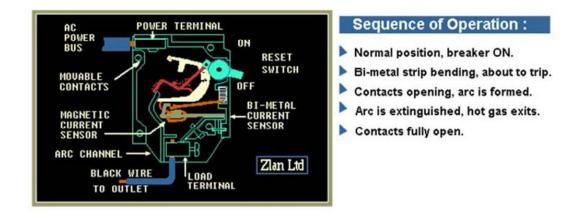

Figure 1.8 shows the structure of a conventional electromagnetic circuit breaker which uses the following principles of operation:

1 Current flowing through the circuit heats the bimetallic current sensor ( $I^2T$  calculation), causing it to bend.

2 When the amount of bending exceeds a limit, the armature is released and a spring forces the contacts to open. The load current also flows through a magnetic current sensor (coil) which creates a magnetic field that will trip the armature faster than the bimetal strip can respond when very large currents flow.

3 When the contacts open, an arc will be generated that is dissipated in the arc channel. This opening to the outside prevents pressure buildup inside the breaker's case.

The conventional circuit breaker's performance is limited by:

1 Slow response time of bimetal current sensors.

2 Mechanical tolerances that affect both the thermal and the magnetic trip limits.

3 Inability to differentiate between arcing and normal start up transients due to large motors or incandescent lamps.

4 Mechanical DC switches have arc-extinguishing capabilities built into them that are not required in solid state devices.

In contrast, the SSPC using silicon carbide FET technology allows the SSPC to respond much more quickly to true circuit overload conditions. By opening the circuit in a fraction of a second after detecting an overload, the SSPC significantly reduces the chance for damaging the circuitry being protected. Moreover, advanced aircraft power systems are using 270VDC power instead of the conventional 400 Hz aircraft power. The 270VDC power is more difficult to switch than conventional 400 Hz because of arcing associated with DC Switching. Solid state devices are desirable for this type of switching because they are able to perform arc-less switching [4].

Although the SSPC offers many advantages over conventional electromagnetic

circuit breaker, it also has some disadvantages. The major disadvantage is its cost which is much higher than its conventional counterpart, especially if a SiC power semiconductor is used.

Figure 1.8 Conventional thermal/magnetic circuit structures

#### **1.5 Summery of SSPC Requirements**

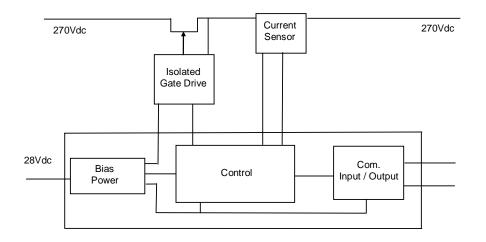

Solid State Power Controllers (solid state circuit breakers) use electronic components (semiconductor devices) to monitor and control current levels rather than simple electrical devices. These elements are much more precise, and they shut down the circuit more quickly. The SSPC consists of the main JFET switch, current sensor, gate drive, bias power supply, control section, and the communications section. In the control section, there is a detection system designed to detect over-current, exceeded I<sup>2</sup>T conditions, and over-temperature of the SSPC switch. The over-current and exceeded I<sup>2</sup>T detection protects the external circuit while the over-temperature detection protects the SSPC's power switching device.

Figure 1.9 Block diagram of the SSPC.

A thermal analysis of the SSPC's power switch has been used to specify the SiC JFET switch. The results show that multiple multi-chip power modules in parallel are required to make the SSPC switch. Representative experimental SiC JFET chips have been evaluated thermally both statically and dynamically and electrically both statically and dynamically. A detailed design of a high voltage SSPC control circuit capable of operating with a 121°C mounting surface temperature and a 225°C maximum junction temperature has been completed including detailed analysis, modeling and simulations, detailed schematic diagrams and detailed drawings. Finally breadboards of the control circuits have been fabricated and tested to verify simulation results.

### Chapter2 SSPC Circuit Design

### 2.1 Introduction

To experimentally verify the SSPC design methodology Si devices were used first to develop the test methods for characterizing the SiC JFETs thermally and to emulate the SiC JFET in the SSPC functional tests. This was done because of the limited availability of SiC devices and their high cost compared to Si devices. Also, the thermal performance of Si devices is available in their specification and this information can be used to verify the thermal models and measurement methods developed. Once the modeling and the measurement method are correct for Si devices they can be applied to SiC devices.

The functional block diagram of the SSPC is shown in Figure 2.1. The identification and sizing of the power components can be performed independently of the design and analysis of the control circuits.

Figure 2.1 SSPC Functional Block Diagram

As stated previously and shown in Fig. 2.1, the SSPC shuts down if the  $I^2T$  of the current exceeds a maximum value, the current exceeds a maximum value, or if the main semiconductor switch's temperature exceeds a maximum value. The  $I^2T$  quantity is a measure of the heat energy developed within a circuit during a fault. It can be expressed as "melting  $I^2T$ ", "arcing  $I^2T$ " or the sum of them as "clearing  $I^2T$ ". "I" stands for effective let-through current (RMS), which is squared, and "T" stands for time of opening, in seconds.

One of the research goals was to implement all of the SSPC circuit functions with components capable of operation at 200°C. This meant that a microprocessor could not be used to implement the control functions and in particular could not be used to compute the I<sup>2</sup>T of the fault current. Thus the value of I<sup>2</sup>T and all of the other control functions needed to be implemented using the available high temperature analog circuit

components.

#### 2.2 SSPC System Design and Design Results

#### 2.2.1 Overview of the SSPC Design

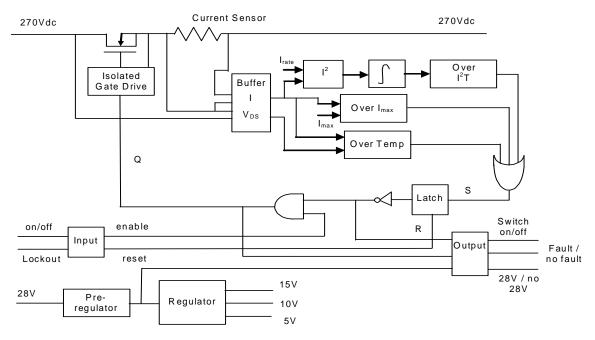

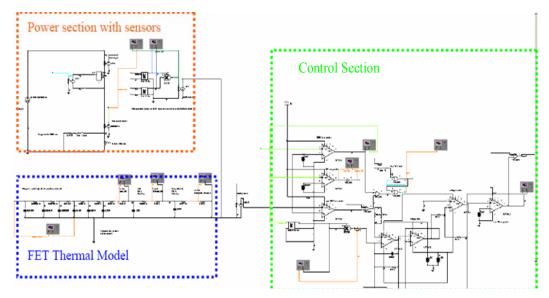

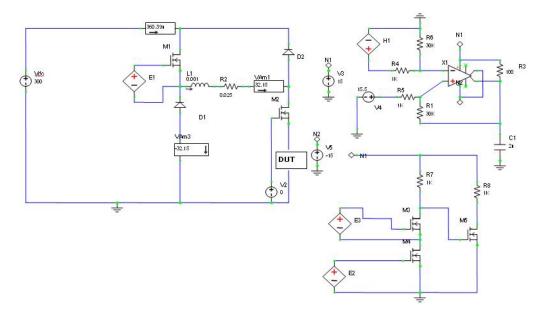

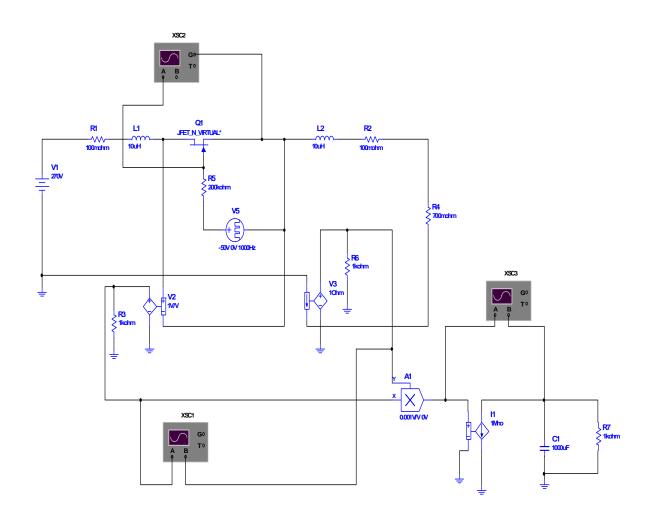

Figure 2.2 shows a Spice model of the SSPC using conventional Si MOSFETs for the power switch.

Figure 2.2 Basic SSPC model with showing its basic subsystems.

The power section (in the orange box) contains the electrical model of the power FET, continuous and surge loads, current, and temperature measurements. The control section (in the green box) contains the I<sup>2</sup>T computation, thermal shutdown, over-current shutdown, fault store, and reset logic. The thermal model of the power MOSFET (in the blue box) predicts the temperature at various locations in the power FET to insure the FET did not become too hot. The modeling and simulation focused initially on a Si power switch, and once the Si results were satisfactory, then applied to SiC FETs. The control section was designed using available 200°C electronic components though the breadboard circuit was implemented with conventional (low temperature) electronics. The model in Figure 2.2 is setup such that the load fault current is 300A. The simulation

results are shown in Figure 2.3 where the SSPC current and the power switch's junction temperature are shown. The labeled orange trace is the Si MOSFET;s junction temperature and the red (square) trace is the load current. At time = 10msec, the fault occurs and the load current is approximately 300A. After 83msec, the  $I^2T$  value exceeds its maximum allowed value and the power FET is turned off and the fault is latched keeping the FET off. At time = 100msec, the SSPC is reset manually and the fault resumes. A second shutdown occurs at 134msec with the fault being latched again due to the MOSFET's junction temperature exceeding its maximum value. The simulation results verify two of the SSPC's fault protection features.

Figure 2.3 SSPC Simulation demonstrating the I<sup>2</sup>t and thermal shutdown

## 2.2.2 Gate Drive Design

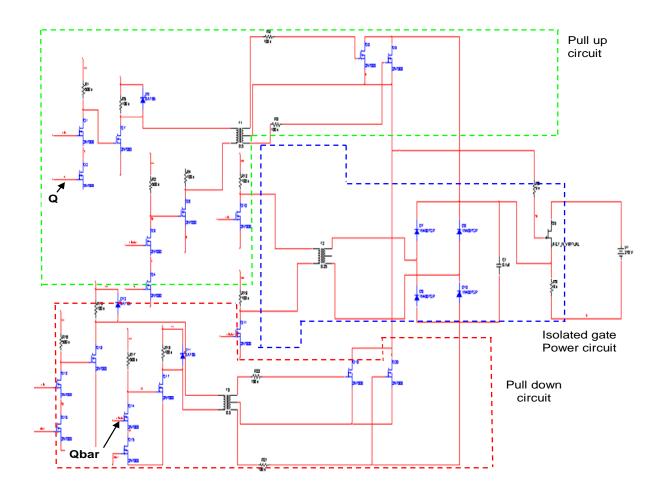

The Gate Drive circuit for the SSPC provides the required isolated interface between the ground referenced power switch on / off control command and the high side SiC JFET. The Gate Drive circuit is a high side driver that uses a push-pull topology to transmit pulse waveforms through pulse transformers to transmit signals from the control ground reference to the SiC JFET's source reference. When the SSPC control issues an Off command, the gate drive circuitry pulls the gate-to-source voltage of the JFET to - 40Vdc to turn off the JFET. When the SSPC control issues an On command, the gate drive circuitry pulls the JFET's gate to source voltage to 0Vdc to turn on the JFET. Like the rest of the SSPC control circuits the gate drive design is constrained by the goal that it be constructed out of components capable of operation at 200°C.

As shown in Fig. 2.4, the gate drive circuit consists of three parts, the pull up circuit, the isolated gate power circuit and the pull down circuit. The isolated gate power circuit produces an isolated 40 V dc voltage. Both the pull up circuit and the pull down circuit operate depending on the input command signals Q and not Q (Qbar). The Q and Qbar signals come from a R/S latch that stores the state of the main power switch and thus if a fault has occurred, If the switch is commanded Off etc. When Q is high and Qbar is low, one of the MOSFETs in the pull up circuit is on to essentially short the SiC JFET's gate and source turning the SiC JFET on. The two MOSFETs in the pull up section perform the logic OR function in that one or the other is on depending if the output of the pulse transformer driving these MOSFETs is positive or negative. Thus if the pull up pulse transformer's primary is being pulsed the JFET is turned on. If the pull up pulse transformer's primary is being pulsed both pull up MOSFETs are off. When Qbar is high and Q is low, one of the MOSFETs in the pull down circuit is on connecting the SiC JFET's gate to -40 V relative to its source. In this way, the voltage between the SiC JFET's gate and source is either zero volts or -40 V, turning it on or turn off.

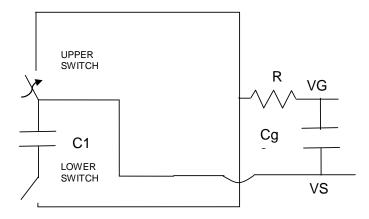

The SiC JFET switch for a 30A SSPC has about a 90 nF of gate to source capacitance which is denoted Cgs in the equivalent circuit in Figure. 2.4. There is a capacitor named C1 in Figure. 2.4 and 2.5 across the output of the isolated gate power circuit that generates the isolated 40 V DC voltage. When the initial voltage on Cgs is zero volts and the voltage on C1 is 40 V, the SiC JFET can either remain on or turn off depending on the values of Q and Qbar. If Q is high, one of the pull up MOSFETs is on as shown in Figure 2.5 and the SiC JFET remains on. If the initial voltage on Cgs is -40V it will discharge to zero through the gate resistor turning on the SiC JFET.

Figure 2.4 SSPC Gate Drive Schematic

Figure 2.5 Equivalent circuit when the upper switch is closed and lower switch in open (Vgs = 0V.)

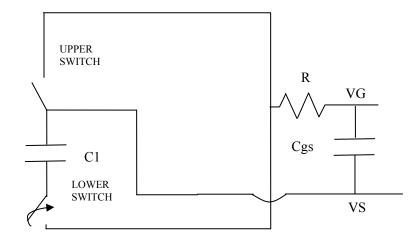

If Q is low (Qbar high), one of the pull down MOSFETs is on as shown in Figure

2.6 and the SiC JFET is turned off.

Figure 2.6 Equivalent circuit when the lower switch is closed and upper switch is open (Vgs = -40 V)

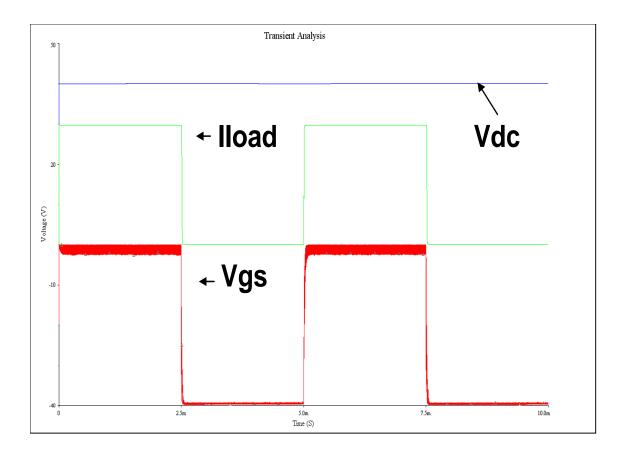

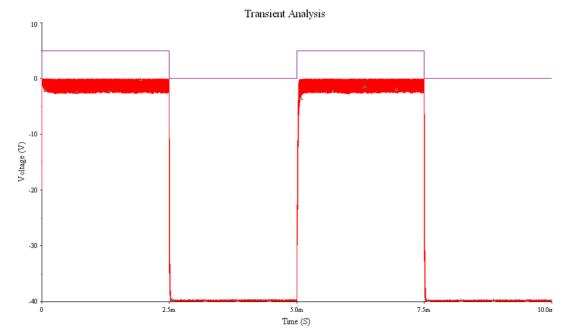

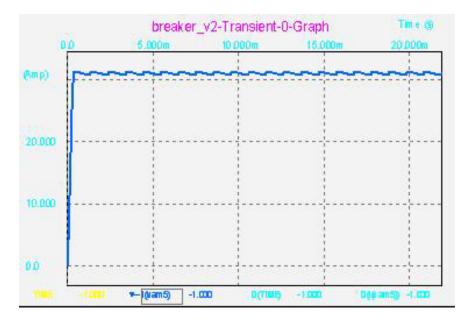

The simulation results for the circuit in Figure 2.4 are shown in Figure 2.7. The top most (blue) waveform is the isolated 40Vdc voltage, the next highest (green) waveform is the current through the SSPC and the red waveform is the gate drive signal (Vgs) to the JFET. The figure indicates that the current is 30A when the JFET is on (Vgs=0V) and is 0A when the JFET is off (Vgs=-40V). Figure 2.8 shows the same simulation results showing the relationship between the upper (purple) input command signal (Q) and the lower (blue) gate to source voltage (Vgs),

Figure 2.7 The simulation results, C2=10uF and Cgs=90 nF

Figure 2.8 The simulations result, C1=10uF and Cgs=90nF. The upper waveform is the logic input and the lower waveform is the gate to source voltage.

#### 2.2.3 Over Current and Over Temperature Protection Circuits

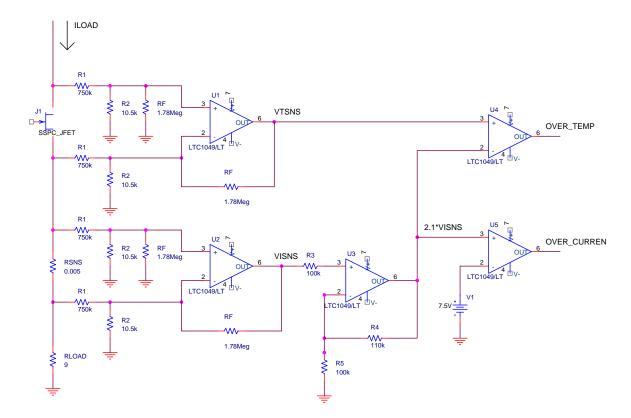

The SSPC senses temperature and current to determine when the SSPC should be on or off. To sense the main JFET switch's temperature the SSPC uses the JFET's onresistance variation with temperature by sensing the voltage drop across the JFET via a differential op-amp. As the junction temperature of the JFET increases, the on resistance of the JFET increases nearly proportional to temperature. The circuit is set to trip at a JFET junction temperature of 225°C. This occurs at the point where the on resistance of the JFET becomes greater than some value which can be expressed as a constant times the value of the current sense resistor value which does not depend on temperature. Current is sensed using the voltage across a current sense resistor because this is the simplest technique that meets the operating temperature requirement. When the JFET's drain to source voltage becomes greater than a scaled value of the voltage across the current sense resistor the JFET turns off because its junction temperature is too high.

When the load current exceeds 1000% (10 times) the rated load the SSPC shuts down immediately with the current sensing circuit sensing the over current and issuing a shutdown command to the SSPC which is latched. The current sensing circuit senses the voltage drop across the constant  $5m\Omega$  sense resistor in series with the power FET and load. The voltage across this current sense resistor is about 0.15 V at rated load current (30A) and 1.5 V at 1000% rated load current (300A). The voltage across the sense resistor is sensed with a differential amplifier (U2) as shown in Figure 2.9 since the current sense resistor is located on the high side of the circuit. The gain of this amplifier is 2.373. The voltage out of the differential amplifier is scaled up by multiplying it by a gain of 2.1 (U3) and the result is compared to a constant voltage of 7.5Vdc (U5). Therefore, when 2.1\*VISNS in Figure 2.9 becomes greater than 7.5Vdc the current sensing circuit will detect an over current condition and shutdown the SSPC. The schematic for the temperature and current sensing circuit is also shown in Figure 2.9. The voltage across the FET is sensed with a differential amplifier circuit that is identical to the one used to sense the voltage across the current sense resistor. The over current and over temperature sense circuit gain calculations are summarized below. Thus when

VTSNS becomes greater than 2.1\*VISNS or if 2.1\*VISNS becomes greater that 7.5Vdc the sensing circuits will sense a fault and issue shutdown command to the SSPC.

Figure 2.9 Temperature and Current Sensing circuit.

| Voltage across JFET (via U1):           | VTSNS -  | $\underline{ILOAD\timesRJFET\timesRF}$ |

|-----------------------------------------|----------|----------------------------------------|

| 6                                       |          | R1                                     |

| Voltage across sense resistor (via U2): | VISNS -  | ILOAD× RSNS× RF                        |

|                                         |          | R1                                     |

| Voltage at U3 output:                   | o ( ) // |                                        |

|                                         | 2.1 × VI | SNS                                    |

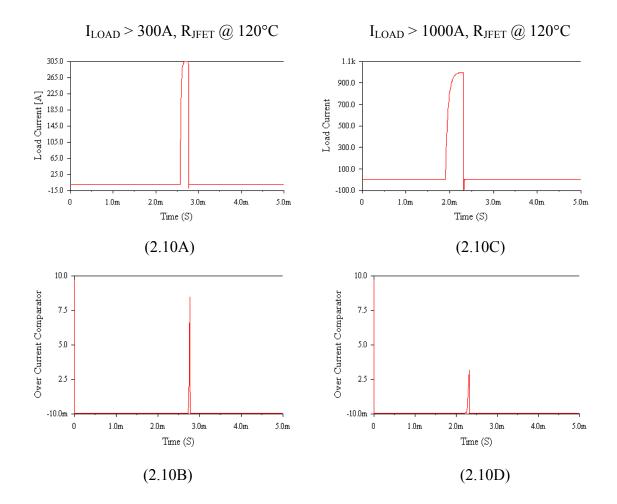

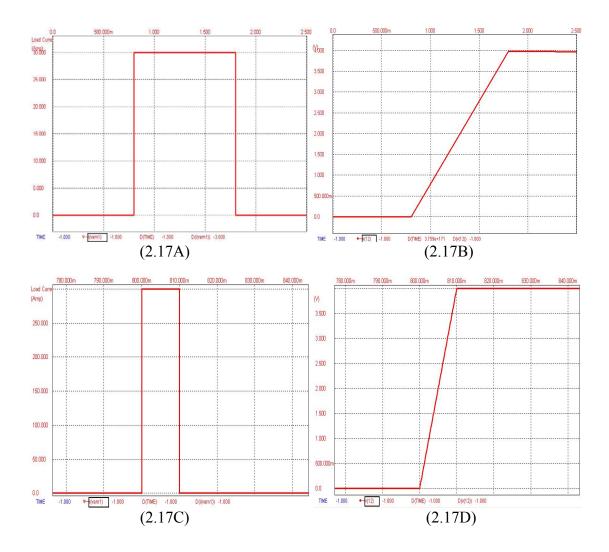

Figure 2.10 below demonstrates the over current circuit operation for an SSPC design for two different SSPC designs, one with a rated load of 30Adc and the other with a rated load of 100Adc. As shown in Figure 2.10 when the load current (Figure 2.10A and 2.10C) exceeds 1000% the rated current for each of the SSPC designs, the current sensing circuit will sense the over current (Figure 2.10B and 2.10D) and shutdown the SSPC.

Figure 2.10 Figure 2.10A and 2.10B are over current sensing simulations at a rated load current of 30Adc. 2.10C and 2.10D are over current sensing simulations at a rated load current of 100Adc.

Figure 2.11 below demonstrates the operation of the over temperature circuit for two SSPC designs with rated loads of 30Adc and 100Adc. The temperature scale used in the simulations is shifted so that 0 on the scale corresponds to 120°C, the typical operating temperature of the SSPC. A delta increase of 105°C on the temperature plot in Figure 2.11 correlates to a total junction temperature of 225°C. As can be observed from the plots in Figure 2.11, once the junction temperature reaches 105°C (i.e. 225°C) the SSPC temperature sense circuit senses an over temperature and shuts down the SSPC.

Another thing to note from the plots in Figure 2.11 is that before the SSPC JFET

is turned on the temperature sensing circuit is indicating an over temperature fault. This is due to the fact that when the SSPC JFET is off the temperature sensing circuit shown in Figure 2.9 above is sensing the 270V drain to source voltage across the off JFET. Since the SSPC JFET is off there is no load current, and the on resistance of the JFET is theoretically infinite. Therefore, the temperature sensing circuit of the SSPC senses the 270Vdc drain to source voltage that causes the circuit to indicate a fault. To accommodate this issue with the over temperature circuit, additional circuitry has been added to the final design. Since the JFET does not heat up until it has operated above the rated load for a period of time, circuitry has been added to disable the temperature sensing circuit until after the SSPC JFET is turned on.

Figure 2.11 Figure 2.11A and 2.11B are over temperature sensing simulations at a rated load current of 30Adc. 2.11C and 2.11D are over temperature sensing simulations at a rated load current of 100Adc.

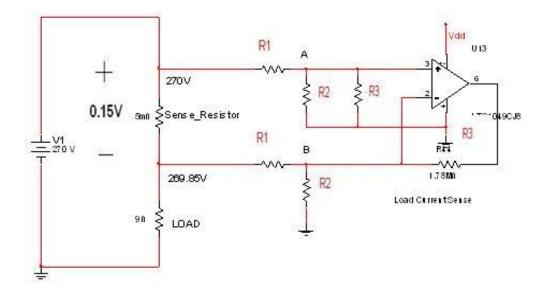

#### 2.2.4 SSPC Switch Current and Voltage Measurement Issues

Because the sense resistor is on the high voltage side, the voltage on one side of the constant sense resistor is 270V and on the other side it is 269.85V or 268.5V depending on the current. The test circuit used to evaluate the current sense circuit is shown in Figure 2.12. The 270V added to the 0.15V signal is called the signal's common mode voltage while the desired 0.15V is called the signal's differential mode voltage.

Figure 2.12 Current sense test circuit schematic

As shown in the figure 2.12, resistors R1 and R2 are used to divide the voltage on both sides of the constant sense resistor so that the voltage is small enough to be input to the differential OP-AMP. Thus the common mode part of the signal must be divided down to be within the bias voltage range of the OP-AMP. Unfortunately the small differential mode part of the signal also gets divided by the same amount. Since the voltage across the constant sense resistor is very small, it requires that the two R1 resistors must be close enough in value and the two R2 resistors must also be close enough in value so that the voltage division error between the two voltage dividers is sufficiently small compared to the small voltage drop being sensed, which is also divided by the voltage dividers.

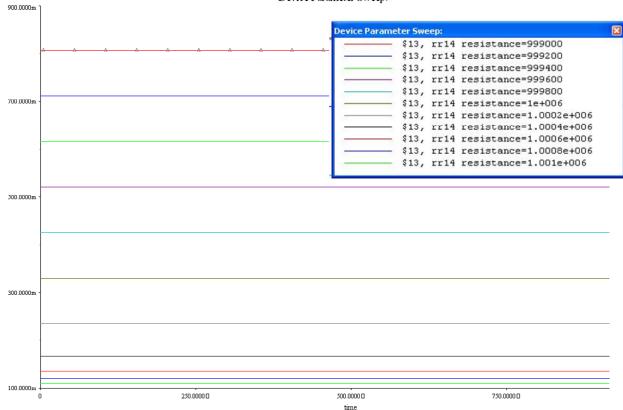

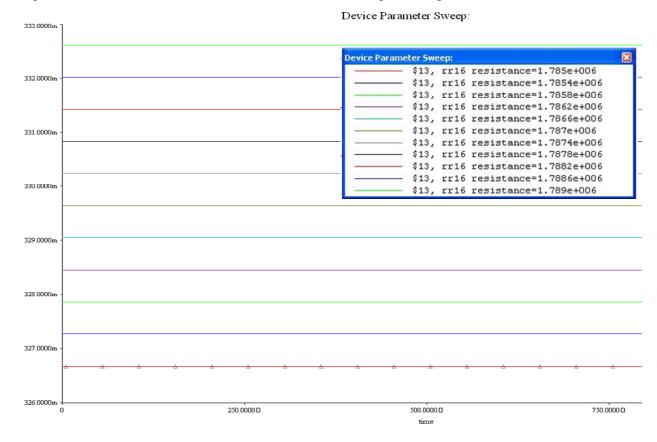

A Spice model was constructed in order to compute the error between the desired and actual output voltages due to the resistance change of the divider resistors. Figure 2.13 shows the simulation results for the output voltage response for different values of one R1 resistor and Table 2.1 summarizes the results in figure 2.13. Here the required value of R1 is 1Mohm and the resulting output voltage is 0.329 volt.

Device Parameter Sweep:

Figure 2.13 The output voltage of the current sense circuit for different values of R1. Table 2.1 Summary of the sensitivity of the current sense circuit to changes in the value

|    | of R1.    |               |                    |                  |  |  |  |  |  |

|----|-----------|---------------|--------------------|------------------|--|--|--|--|--|

|    | R1 (Mohm) | Output (Volt) | Resistor Error (%) | Output Error (%) |  |  |  |  |  |

| 1  | 0.999     | 0.807         | -0.1               | 145              |  |  |  |  |  |

| 2  | 0.9992    | 0.712         | -0.08              | 116              |  |  |  |  |  |

| 3  | 0.9994    | 0.616         | -0.06              | 87.2             |  |  |  |  |  |

| 4  | 0.9996    | 0.520         | -0.04              | 58.1             |  |  |  |  |  |

| 5  | 0.9998    | 0.425         | -0.02              | 29.1             |  |  |  |  |  |

| 6  | 1         | 0.329         | 0                  | 0                |  |  |  |  |  |

| 7  | 1.0002    | 0.236         | 0.02               | -28.2            |  |  |  |  |  |

| 8  | 1.0004    | 0.167         | 0.04               | -49.2            |  |  |  |  |  |

| 9  | 1.0006    | 0.136         | 0.06               | -58.6            |  |  |  |  |  |

| 10 | 1.0008    | 0.120         | 0.08               | -63.5            |  |  |  |  |  |

| 11 | 1.001     | 0.110         | 0.1                | -66.5            |  |  |  |  |  |

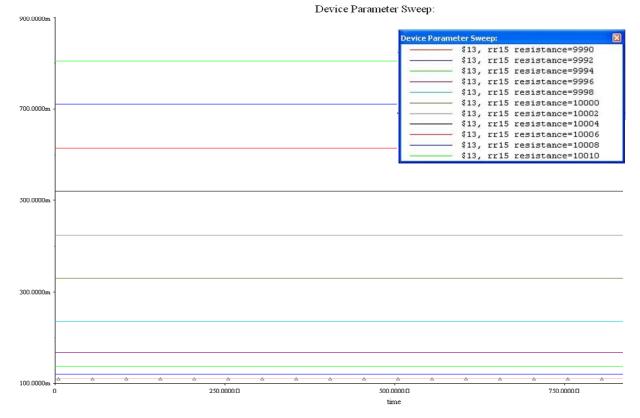

Since output error's dependence on R2 for small variations in R2's value is the same function as R1 to the simulation results are similar when the value of one of the R2 resistors is varied. The results shown in the Figure 2.14 and table 2.2 verify this. Here the required value of R2 equals 10Kohm and again the resulting output voltage is 0.329 volt.

Figure 2.14 The output voltage of the current sense circuit for different values of R2.

|   | R2 (Kohm) | Output (Volt) | Resistor Error (%) | Output Error (%) |

|---|-----------|---------------|--------------------|------------------|

| 1 | 9.99      | 0.110         | -0.1               | -66.5            |

| 2 | 9.992     | 0.120         | -0.08              | -63.5            |

| 3 | 9.994     | 0.136         | -0.06              | -58.6            |

| 4 | 9.996     | 0.167         | -0.04              | -49.2            |

| 5 | 9.998     | 0.236         | -0.02              | -28.2            |

| 6 | 10        | 0.329         | 0                  | 0                |

Table 2.2 Summary of the sensitivity of the current sense circuit to changes in the value of R2

| 7  | 10.002 | 0.424 | 0.02 | 29.1 |

|----|--------|-------|------|------|

| 8  | 10.004 | 0.519 | 0.04 | 58.1 |

| 9  | 10.006 | 0.614 | 0.06 | 87.2 |

| 10 | 10.008 | 0.709 | 0.08 | 116  |

| 11 | 10.01  | 0.804 | 0.1  | 145  |

With the help of Figures 2.13,2.14, and Tables 2.1, 2.2, it is clear that even a 0.02% error in the value of either resistor will cause about a 29% output error. This shows that the resistors R1 and R2 must be accurate enough so that the error resulting from voltage division of the common mode voltage is small enough.

Resistor R3 has different function from R1 and R2, and it is used to define the gain of the OP-AMP. Figure 2.15 plots the output voltage in response to the resistance change of R3, and Table 2.3 summarizes the results in Figure 2.15. Here the required value of R3 equals 1.787Mohms to obtain the desired 0.329 volt output voltage.

Figure 2.15 The output voltage of the current sense circuit for different values of R3.

|    | Resistor(Mohm) | Output (Volt) | Resistor Error (%) | Output Error (%) |

|----|----------------|---------------|--------------------|------------------|

| 1  | 1.785          | 0.326         | -0.1               | -0.9             |

| 2  | 1.7854         | 0.327         | -0.08              | -0.6             |

| 3  | 1.7858         | 0.327         | -0.06              | -0.6             |

| 4  | 1.7862         | 0.328         | -0.04              | -0.3             |

| 5  | 1.7866         | 0.329         | -0.02              | 0                |

| 6  | 1.787          | 0.329         | 0                  | 0                |

| 7  | 1.7874         | 0.330         | 0.02               | 0.3              |

| 8  | 1.7878         | 0.330         | 0.04               | 0.3              |

| 9  | 1.7882         | 0.331         | 0.06               | 0.6              |

| 10 | 1.7886         | 0.332         | 0.08               | 0.9              |

| 11 | 1.789          | 0.332         | 0.1                | 0.9              |

Table 2.3 Summary of the sensitivity of the current sense circuit to changes in the value of R3

Figure 4.15 and Table 2.3 demonstrate that the change in the value of the resistor R3 will not affect the output voltage much compared to changes in R1 and R2. The above results show that to obtain an accurate output voltage it is necessary to use low tolerance resistors for R1 and R2. The tolerance of R1 and R2 can be improved further by trimming their values using a small resistor in series with R1 or R2. It should be noted that if the circuit can sense the 0.15V voltage drop accurately, then it will be able to sense the 1.5V voltage drop with greater accuracy.

The circuit in Figure 2.9 was fabricated with 0.1% resistors and trimming R1 and R2 as described above. Tables 2.4 and 2.5 summarize the comparison between the simulation and experimental results for different input voltages. The simulation used the measured values of the resistors. The experimental results match the simulation results well.

Table 2.4 Simulation and experimental results versus the input (common mode) voltage with rated load current (30A) when the input voltage is 270V. The voltage drop across the

| Common       | 10 (V) | 100 (V) | 200 (V) | 270 (V) |

|--------------|--------|---------|---------|---------|

| Mode Voltage |        |         |         |         |

| Simulation   | 0.2612 | 0.283   | 0.309   | 0.328   |

| Experiment   | 0.279  | 0.3     | 0.323   | 0.343   |

| Error        | 0.0018 | 0.017   | 0.013   | 0.015   |

current sense resistor is 0.15V at this condition.

Table 2.5 Simulation and experimental results versus the input voltage with 1000% rated load current (300A) when the input voltage is 270V.

| Voltage Drop Results | 10 (V) | 270 (V) |

|----------------------|--------|---------|

| Simulation           | 2.699  | 3.359   |

| Experiment           | 2.734  | 3.369   |

| Error                | 0.035  | 0.01    |

Another issue is that the value of the resistors will change with the temperature. The change in resistance with temperature is characterized by the resistor's temperature coefficient (labeled TC, the unit is ppm/°C). From the specification, the temperature coefficient of the resistors used in the experiment is 5 ppm/°C. The resistance change can be computed using the definition of the temperature coefficient

$$TC = \frac{\Delta R * 10^6}{R_0 * \Delta T}$$

For example, R1 is 1Mohm at 25°C,  $\Delta T = 100$ °C - 25°C = 75°C,

$$\Delta R = \frac{5\,ppm/\,^{\circ}\text{C}*10^{6}\,ohm*75^{\circ}\text{C}}{10^{6}} = 375\,ohm = 0.0375\%R1$$

Thus the resistance value will be 1.000375Mohm at 100°C. This change is too large for the output of the current sense circuit to be accurate. However, if the two resistors R1 or R2 have the same TC, then the output voltage will still be accurate. Table 2.6 shows the experimental result when the circuit changes from 25°C to 200°C.

| Temp   | 25°C  | 47°C  | 60°C  | 84°C  | 113°C | 131°C  | 160°C | 200°C     |

|--------|-------|-------|-------|-------|-------|--------|-------|-----------|

| Vsense | 0.547 | 0.533 | 0.523 | 0.492 | 0.455 | 0.447  | 0.435 | 0(failed) |

| Error  | 0     | 2.56% | 4.38% | 10%   | 16.8% | 18.28% | 20.4% | N/A       |

Table 2.6 Experimental results Vsense changes with Temperature when the input voltage is 270VDC

The resistors R1 and R2 failed at 200°C, so Vsense and Von equals 0V. The reason for the resisitor failures is that the maximum specified operating temperature for the resistors is 150°C, and the resistor's Power Rating drop linearly above 85°C to zero at 150°C.

There are two solutions to eable the circuit to operate at high temperature,

- 1. Better resistors are needed than were used in the experiment, which should have low temperature coefficient and an operating temperature above 200°C.

- 2. Since the error is small, trim resistors should be trimmed precisely at different Temperature to get desired Von value.

# 2.2.5 I<sup>2</sup>T Measurement Simulation and Test Results

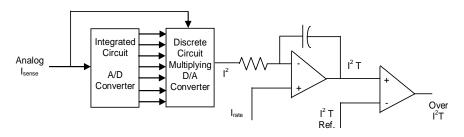

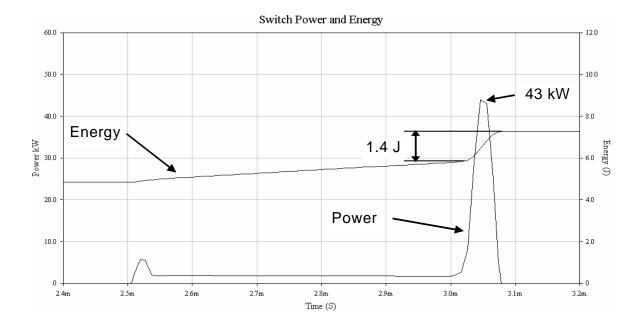

The I<sup>2</sup>T circuit turns off the SSPC main SiC JFET switch when the load current is between its rated value and 1000% of its rated load after a time duration that varies with load current so that the I<sup>2</sup>T value of the current remains constant. A block diagram of the circuit is shown in Figure 2.16. The circuit squares the current using a multiplying digital to analog converter (DAC). In the multiplying DAC the analog DAC reference is one of the signals to be multiplied and the digital signal to be converted to analog is the other signal to be multiplied. Since one of the signals being multiplied is digital, that analog signal must be first converted to digital using an analog to digital converter (ADC).

Figure 2.16 Block Diagram of the  $I^2T$  circuit. 30

The related current squaring circuit equations are shown below,

$$N_{digital} = 11111111 \times \frac{V_{in}}{V_{refA/D}}$$

(1)

$$V_{out} = \frac{N_{digital}}{11111111} \times V_{refD / A} \quad V_{refD / A} = V_{in} \quad (2)$$

$$V_{out} = \frac{V_{in}^{2}}{V_{refA} / D}$$

(3)

$$V_{sensor} = I \frac{R_{sensor} \times R_f}{R_{in}} \qquad V_{sensor} = V_{in}$$

(4)

$$V_{out} = I^2 \frac{R_{sensor}}{R_{in}^2 \times V_{refA/D}^2} = I^2 \times Gain$$

<sup>(5)</sup>

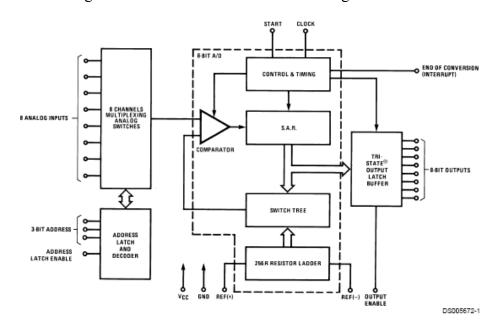

Again the design requirement that all of the components used in the circuit must be capable of operation at 200°C was imposed. A commercial ADC converter capable of operation at 200°C is available from two different venders. Thus the load current sensed by the current sensing circuit is fed into this eight-bit high temperature ADC. Unfortunately a commercial DAC capable of operation at 200°C is not available. Thus the high temperature ADC is combined with an R-2R ladder network multiplying DAC, made up of discrete components to make the I-squared circuit. This circuit was chosen because a digital circuit is inherently noise immune, fast, and 200°C ADC integrated circuits are available commercially. Also 200°C resistors and analog switches for the DAC are also available commercially. The output of the DAC is then fed into an integrator to generate the I<sup>2</sup>T function. The I<sup>2</sup>T signal is then compared to the scaled reference value equal to 4Vdc. When the I<sup>2</sup>T signal exceeds 4Vdc the SSPC will trip and shutdown. This is shown in Figure 3.12 for 30A and 100A SSPC designs. This meets the trip curve requirement in Figure 2.18.

Figure 2.17 Figure 2.17A and 2.17B are I<sup>2</sup>T simulation results at a 30A SSPC 100% load current. Figure 2.17C and 2.17D are I<sup>2</sup>T simulation results at a 300A SSPC 1000% load current.

Figure 2.18 Required SSPC trip curve

Figure 2.19 shows the ADC signal definitions. The "Equiv.Output" values in Table 2.7 were computed from measurements of the ADC's binary output in order to compare the binary output to the analog input voltage. The ADC's reference voltage was measured to be 5.17 V. An analog voltage is input to the ADC and the binary output is measured. Finally, the measured binary output is converted to the "Equiv. Output" using Eq. 6.

$$Equiv.Output = \frac{Binary.Value_{measured}}{255} \times V_{ref}$$

(6)

Table 2.7 shows the ADC test results. It can be seen that the final error between the input and output values is about 0.3%.

Figure 2.19 ADC schematic

| ADC<br>input | Bin7 | Bin6 | Bin5 | Bin4 | Bin3 | Bin2 | Bin1 | Bin0 | Dec.<br>Value | Equiv.<br>Output | %<br>Error |

|--------------|------|------|------|------|------|------|------|------|---------------|------------------|------------|

| 5.17         | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 255           | 5.16             | 0.19       |

| 4.97         | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 245           | 4.95             | 0.27       |

| 5.11         | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 252           | 5.09             | 0.47       |

| 4.99         | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 246           | 4.97             | 0.45       |

| 4.87         | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | 240           | 4.85             | 0.24       |

| 4.64         | 1    | 1    | 1    | 0    | 0    | 1    | 0    | 1    | 229           | 4.63             | 0.34       |

| 4.56         | 1    | 1    | 1    | 0    | 0    | 0    | 0    | 1    | 225           | 4.54             | 0.48       |

| 4.34         | 1    | 1    | 0    | 1    | 0    | 1    | 1    | 0    | 214           | 4.33             | 0.32       |

| 4.24         | 1    | 1    | 0    | 1    | 0    | 0    | 0    | 1    | 209           | 4.22             | 0.34       |

| 4.05         | 1    | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 200           | 4.05             | 0.24       |

| 3.97         | 1    | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 196           | 3.96             | 0.35       |

| 3.77         | 1    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 186           | 3.76             | 0.29       |

| 3.63         | 1    | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 179           | 3.63             | 0.03       |

| 3.47         | 1    | 0    | 1    | 0    | 1    | 0    | 1    | 1    | 171           | 3.46             | 0.34       |

| 3.12         | 1    | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 154           | 3.12             | 0.07       |

| 3.02         | 1    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 149           | 3.02             | 0.10       |

| 2.90         | 1    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 143           | 2.89             | 0.42       |

| 2.74         | 1    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 135           | 2.73             | 0.37       |

| 2.62         | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 129           | 2.61             | 0.36       |

| 2.37         | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 117           | 2.37             | 0.30       |

| 2.27         | 0    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | 112           | 2.26             | 0.47       |

| 2.13         | 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1    | 105           | 2.11             | 0.79       |

| 1.97         | 0    | 1    | 1    | 0    | 0    | 0    | 0    | 1    | 97            | 1.95             | 0.74       |

| 1.82         | 0    | 1    | 0    | 1    | 1    | 0    | 1    | 0    | 90            | 1.81             | 0.92       |

| 1.62         | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0    | 80            | 1.60             | 1.23       |

| 1.46         | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 72            | 1.45             | 0.67       |

| 1.36         | 0    | 1    | 0    | 0    | 0    | 0    | 1    | 1    | 67            | 1.34             | 1.13       |

| 1.16         | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1    | 57            | 1.15             | 0.75       |

| 1.07         | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1    | 53            | 1.06             | 1.63       |

| 0.95         | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 1    | 47            | 0.94             | 1.35       |

| 0.77         | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 38            | 0.76             | 0.96       |

| 0.69         | 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 34            | 0.68             | 2.08       |

| 0.61         | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 30            | 0.60             | 2.01       |

| 0.49         | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 24            | 0.48             | 2.18       |

| 0.41         | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 20            | 0.40             | 2.09       |

Table 2.7 ADC test results and the error compared to the input value

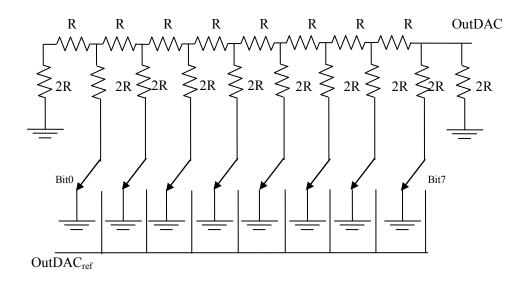

The output of ADC is fed into the multiplying DAC. Here a resistor ladder

converter was chosen. Its central component is a resistor ladder network in which horizontally drawn resistors have a value of R and vertically drawn resistors have a value of 2R. This network is sometimes called an R-2R network. An 8-bit converter is shown in Figure 2.20 [22].

Figure 2.20 Eight-bit resistive ladder DAC

The output voltage of the circuit as a function of all the switch values is shown below [22]. Here  $OutDAC_{ref}$  equals  $V_{inputADC}$  and  $Bit_j$  is zero or 1.

$$OutDAC = \frac{OutDAC_{ref}}{3} (Bit7 + \frac{Bit6}{2} + \frac{Bit5}{4} + \frac{Bit4}{8} + \frac{Bit3}{16} + \frac{Bit2}{32} + \frac{Bit1}{64} + \frac{Bit0}{128})$$

(7)

In Figure 2.20, 10K and 20K ohm resistors were used. The MM74HC4316 Quad Analog Switch was used for the switches. The details can be found in the Appendix. Table 2.8 summarizes the DAC test results. The variables are defined as shown below,

- $OutDAC_{ex}$ : The experimental results of eight-bit resistive ladder DAC. Unit is Volt.

- OutDAC<sub>th</sub>: The theoretical results of ideal eight-bit resistive ladder DAC. Unit is

Volt.

It can be seen that the DAC error between experimental and theoretical value is about 0.01%. The output of the DAC is fed into an integrator to generate the  $I^2T$  function

| OutDAC <sub>ex</sub> (V) | $OutDAC_{ref}(V)$ | OutDAC <sub>ex</sub> /OutDAC <sub>ref</sub> | OutDAC <sub>th</sub> /OutDAC <sub>ref</sub> | Error (%) |

|--------------------------|-------------------|---------------------------------------------|---------------------------------------------|-----------|

| 3.43                     | 3.43              | 1.00                                        | 1.00                                        | 0.01      |

| 3.16                     | 3.29              | 0.96                                        | 0.96                                        | 0.01      |

| 3.34                     | 3.38              | 0.99                                        | 0.98                                        | 0.01      |

| 3.18                     | 3.30              | 0.96                                        | 0.96                                        | 0.01      |

| 3.03                     | 3.22              | 0.94                                        | 0.94                                        | 0.01      |

| 2.76                     | 3.07              | 0.90                                        | 0.89                                        | 0.01      |

| 2.66                     | 3.01              | 0.88                                        | 0.88                                        | 0.01      |

| 2.41                     | 2.87              | 0.84                                        | 0.84                                        | 0.01      |

| 2.30                     | 2.80              | 0.82                                        | 0.82                                        | 0.01      |

| 2.11                     | 2.69              | 0.78                                        | 0.78                                        | 0.01      |

| 2.02                     | 2.63              | 0.77                                        | 0.77                                        | 0.01      |

| 1.82                     | 2.50              | 0.73                                        | 0.73                                        | 0.01      |

| 1.69                     | 2.41              | 0.70                                        | 0.70                                        | 0.01      |

| 1.54                     | 2.29              | 0.67                                        | 0.67                                        | 0.01      |

| 1.25                     | 2.07              | 0.60                                        | 0.60                                        | 0.01      |

| 1.17                     | 2.00              | 0.58                                        | 0.58                                        | 0.01      |

| 1.08                     | 1.92              | 0.56                                        | 0.56                                        | 0.01      |

| 0.96                     | 1.81              | 0.53                                        | 0.53                                        | 0.01      |

| 0.88                     | 1.73              | 0.51                                        | 0.50                                        | 0.01      |