University of Kentucky UKnowledge

University of Kentucky Master's Theses

Graduate School

2004

# FPGA BASED IMPLEMENTATION OF A POSITION ESTIMATOR FOR CONTROLLING A SWITCHED RELUCTANCE MOTOR

Srilaxmi Pampana University of Kentucky, spamp2@uky.edu

Right click to open a feedback form in a new tab to let us know how this document benefits you.

#### **Recommended Citation**

Pampana, Srilaxmi, "FPGA BASED IMPLEMENTATION OF A POSITION ESTIMATOR FOR CONTROLLING A SWITCHED RELUCTANCE MOTOR" (2004). *University of Kentucky Master's Theses*. 254. https://uknowledge.uky.edu/gradschool\_theses/254

This Thesis is brought to you for free and open access by the Graduate School at UKnowledge. It has been accepted for inclusion in University of Kentucky Master's Theses by an authorized administrator of UKnowledge. For more information, please contact UKnowledge@lsv.uky.edu.

## **ABSTRACT OF THESIS**

#### FPGA BASED IMPLEMENTATION OF A POSITION ESTIMATOR FOR CONTROLLING A SWITCHED RELUCTANCE MOTOR

Rotor Position information is essential in the operation of the Switched Reluctance Motor (SRM) for properly controlling its phase currents. This thesis uses Field Programmable Gate Array (FPGA) technology to implement a method to estimate the SRM's rotor position using the inverse inductance value of the SRM's phases. The estimated rotor position is given as input to the Commutator circuit, also implemented in the FPGA, to determine when torque-producing currents should be input in the SRM phase windings. The Estimator and Commutator design is coded using Verilog HDL and is simulated using Xilinx tools. This circuit is implemented on a Xilinx Virtex XCV800 FPGA system. The experimentally generated output is validated by comparing it with simulation results from a Simulink model of the Estimator. The performance of the FPGA based SRM rotor position estimator in terms of calculation time is compared to a digital signal processor (DSP) implementation of the same position estimator algorithm. It is found that the FPGA rotor position Estimator with a 5MHz clock can update its rotor position estimate every 7µs compared to an update time of 50µs for a TMS320C6701-150 DSP implementation using a commercial DSP board. This is a greater than 7 to one reduction in the update time.

KEYWORDS: Position Estimator, SRM, FPGA, Commutator, Verilog, Simulink, Xilinx.

Srilaxmi Pampana

October 26, 2004

Copyright © Srilaxmi Pampana 2004.

# FPGA BASED IMPLEMENTATION OF A POSITION ESTIMATOR FOR CONTROLLING A SWITCHED RELUCTANCE MOTOR

By

Srilaxmi Pampana

**Dr. Arthur V. Radun** (Director of Thesis)

Dr. Yu Ming Zhang

(Director of Graduate Studies)

**Octo**ber 26, 2004

# **RULES FOR THE USE OF THESES**

Unpublished theses submitted for the Master's degree and deposited in the University of Kentucky Library are as a rule open for inspection, but are to be used only with due regard to the rights of the authors. Bibliographical references may be noted, but quotations or summaries of parts may be published only with permission of the author, and with the usual scholarly acknowledgements.

Extensive copying or publication of the thesis in whole or in part also requires the consent of the Dean of the Graduate School of the University of Kentucky.

A library that borrows this thesis for use by its patrons is expected to secure the signature of each user.

| Name | Date |

|------|------|

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

|      |      |

# THESIS

Srilaxmi Pampana

The Graduate School

University of Kentucky

2004

## FPGA BASED IMPLEMENTATION OF A POSITION ESTIMATOR FOR CONTROLLING A SWITCHED RELUCTANCE MOTOR

## THESIS

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering at the University of Kentucky

By

Srilaxmi Pampana

Lexington, Kentucky

Director: Dr. Arthur Radun, Associate Professor Electrical Engineering, Lexington, Kentucky

2004

## MASTER'S THESIS RELEASE

I authorize the University of Kentucky Libraries to reproduce this thesis in whole or in part for purposes of research

Signed: \_\_\_\_\_

#### ACKNOWLEDGEMENTS

I would like to express my sincere thanks and heartfelt gratitude to Dr. Arthur V Radun for his guidance and support throughout this thesis. I am very thankful for his constant encouragement and help in providing suggestions and insights towards my thesis.

I would also like to thank Dr. J. Robert Heath and Dr. William Dieter for serving on my thesis committee and providing me with invaluable comments and suggestions for improving this thesis.

I would like to express my deepest gratitude and thanks to my parents and my brother for their support and encouragement, they provided throughout my life and in finishing my Masters. I would also like to thank all my friends for all their help and encouragement.

#### **TABLE OF CONTENTS**

| Acknowledgements | iii |

|------------------|-----|

| List of Tables   |     |

| List of figures  |     |

#### CHAPTER 1: INTRODUCTION

| 1.1 Introduction to Switched Reluctance Motor      | . 1 |

|----------------------------------------------------|-----|

| 1.2 Basic Structure and Principle of SRM Operation | . 2 |

| 1.3 Contribution of the Thesis                     |     |

| 1.4 Outline of the Thesis                          | 6   |

#### CHAPTER 2: DESIGN ANALYSIS OF ROTOR POSITION ESTIMATOR

| 2.1 Variation of inductance with rotor position                      | . 8 |

|----------------------------------------------------------------------|-----|

| 2.2 Theory behind the Rotor Position Estimator used in this thesis 1 | 12  |

| 2.3 Rotor Position State Estimator Equations                         | 16  |

#### CHAPTER 3: SIMULINK MODEL OF THE CIRCUIT TO BE DESIGNED

| 3.1 Introduction to Simulink model | 23 |

|------------------------------------|----|

| 3.2 Commutator Block               | 25 |

| 3.3 Rotor Position Estimator       | 31 |

# CHAPTER 4: IMPLEMENTATION OF THE ROTOR POSITION ESTIMATOR ON AN FPGA

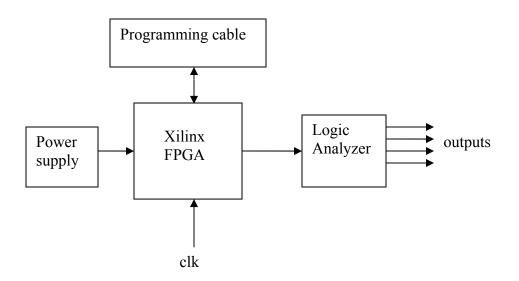

| 4.1 Block Diagram of the system          | 38 |

|------------------------------------------|----|

| 4.2 Angle wrapping                       |    |

| 4.3 Selection of the Programmable device |    |

| 4.4 Field Programmable Gate Arrays       | 44 |

| 4.5 Type of FPGA                         | 47 |

| 4.6 Xilinx Virtex XCV800                 | 49 |

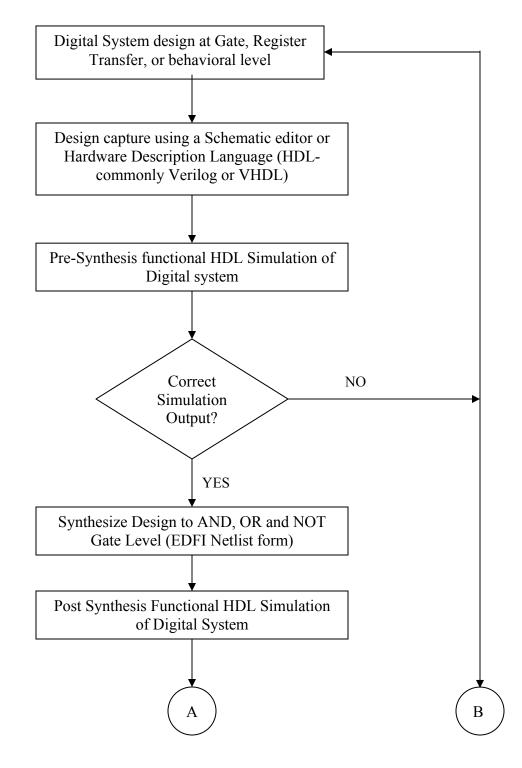

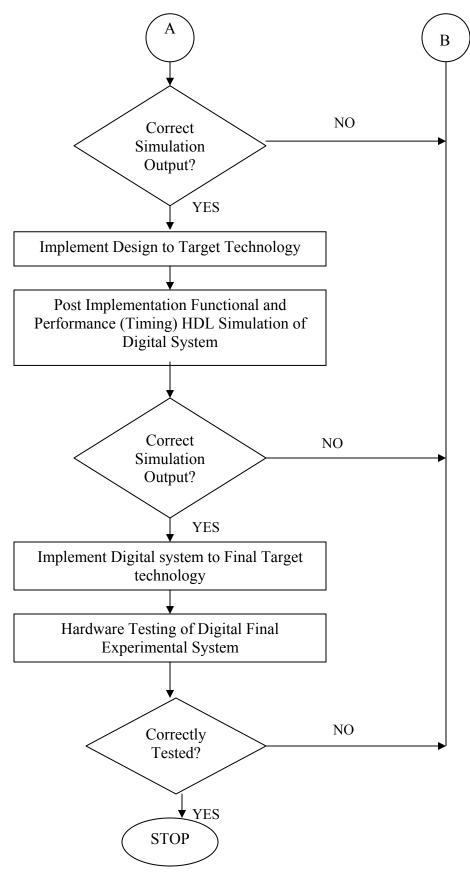

| 4.7 Digital Design Flow                  | 51 |

| 4.8 Core Generator                       | 59 |

| 4.9 Simulation Results                   | 67 |

#### CHAPTER 5: Implementation of the Estimator on an FPGA

| 5.1 Comparison of Simulink and Verilog Design Results | . 72 |

|-------------------------------------------------------|------|

| 5.2 Testing the FPGA Circuit                          | . 80 |

| 5.3 Testing the system                                | . 82 |

| 5.4 FPGA implementation results                       |      |

| 5.5 Conclusion                                        | . 92 |

|                                                       |      |

#### APPENDICES

| Appendix A: Verilog code for Position Estimator and Commutator | 93  |

|----------------------------------------------------------------|-----|

| References                                                     | 105 |

| Vita                                                           | 107 |

#### LIST OF TABLES

| Table 3.1 Truth Table for the Commutator                                          | .27 |

|-----------------------------------------------------------------------------------|-----|

| Table 4.1 The Input and Output signals of the circuit represented in the HDL code | 42  |

| Table 4.2 Comparison of Resources available in Virtex and Spartan                 | 48  |

| Table 4.3 Constants used in the block galpha of the HDL code                      | .58 |

| Table 5.1 Commutator block output for the four phases                             | 88  |

#### **LIST OF FIGURES**

| Figure 1.1, Cross-section diagram of an 8/6, four-phase SRM                                         | 2  |

|-----------------------------------------------------------------------------------------------------|----|

| Figure 1.2, The Block diagram of the entire SRM based motor system                                  | 5  |

| Figure 1.3, Block Diagram of Rotor Position Estimator and Commutator                                | 6  |

| Figure 2.1, Aligned Position                                                                        | 9  |

| Figure 2.2, Unaligned position                                                                      | 9  |

| Figure 2.3, Plot of the SRMs' phase flux versus current for different rotor positions               |    |

| showing the effect of iron saturation                                                               | 10 |

| Figure 2.4, Plot of the SRM's phase inductance versus rotor position for different                  |    |

| currents                                                                                            | 11 |

| Figure 2.5, Plot of the phase inductance at the aligned position versus current for an              |    |

| SRM                                                                                                 | 12 |

| Figure 2.6, Current Profile across an inductor                                                      | 12 |

| Figure 2.7, Ideal phase inductance profile versus rotor position                                    | 14 |

| Figure 2.8, The computed error for an experimental 4 phase SRM for $\alpha - \theta = +/-1^\circ$ , |    |

| +/-5°, and +/-10° and rotor positions from 0° to 90°                                                | 15 |

| Figure 2.9, Block diagram representation of the state estimator                                     | 19 |

| Figure 2.10, Block Diagram of the SRM control system                                                | 20 |

| Figure 2.11, Block diagram of the FPGA that is the subject of this thesis                           | 21 |

| Figure 2.12, Block diagram of Commutator                                                            | 21 |

| Figure 3.1, Block Diagram of Rotor Position Estimator and Commutator                                | 23 |

| Figure 3.2, Phase current showing the torque producing and sense phase currents                     | 24 |

| Figure 3.3, Plot of measured (from simulation) $g_1()$ and the select signal isense for             |    |

| phase one                                                                                           | 25 |

| Figure 3.4, Commutator output for forward and reverse directions under normal                       |    |

| conditions                                                                                          | 26 |

| Figure 3.5, Commutator output for forward rotation when the turn on angle is advance                | ed |

| beyond the allowed range                                                                            | 27 |

| Figure 3.6, Simulink model of the commutator block                                                  | 29 |

|                                                                                                     |    |

| Figure 3.7, Simulink model of the commutator block for one phase                                    | .30  |

|-----------------------------------------------------------------------------------------------------|------|

| Figure 3.8, Simulink model of the rotor position estimator                                          | 31   |

| Figure 3.9, Simulink model of the block galpha to calculate $g(\alpha)$                             | .32. |

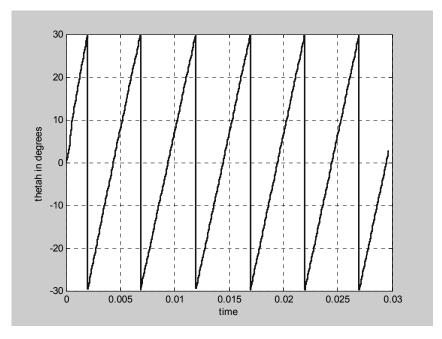

| Figure 3.10, The rotor position angle profile                                                       | .34  |

| Figure 3.11, The inverse inductance value profile                                                   | .34  |

| Figure 3.12, Error calculated for the actual and estimated inverse inductance profile               | .36  |

| Figure 3.13, Estimated rotor speed for the SRM in radian/second (for a constant speed               | lof  |

| 2000rpm)                                                                                            | 37   |

| Figure 3.14, Estimated rotor position for the SRM                                                   | 37   |

| Figure 4.1, Block diagram of the Position Estimator and Commutator                                  | .38  |

| Figure 4.2, Flux linked by phase A as a function of the rotor position                              |      |

| Figure 4.3, Block diagram of an FPGA                                                                | 45   |

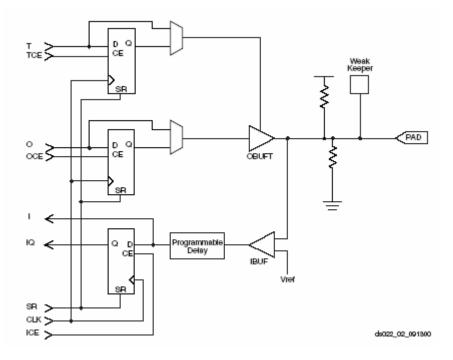

| Figure 4.4, Block diagram of a Virtex IOB                                                           | 46   |

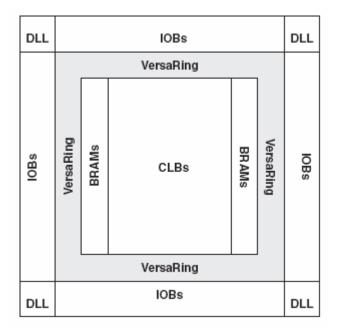

| Figure 4.5, Virtex architecture overview                                                            | 50   |

| Figure 4.6, Digital Design Flow                                                                     | .52  |

| Figure 4.7, Block diagram of the block sensetheta                                                   | 56   |

| Figure 4.8, Block diagram of the block galpha                                                       | 56   |

| Figure 4.9, Schematic diagram of the multiplier core                                                | 60   |

| Figure 4.10, Schematic diagram of the core divider                                                  | 62   |

| Figure 4.11, Block diagram of the block errorlow                                                    |      |

| Figure 4.12, Block diagram of the Integrator circuit                                                | 64   |

| Figure 4.13, Block diagram for shifting and wrapping the angles                                     | 65   |

| Figure 4.14, Block diagram of commutator circuit for one phase                                      | 66   |

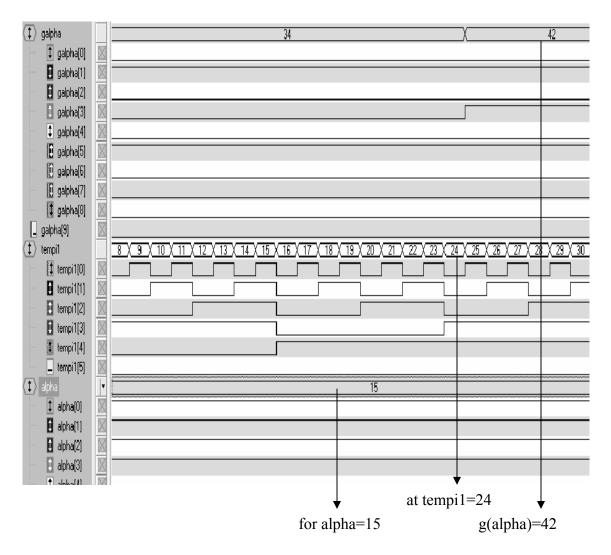

| Figure 4.15, ModelSim simulation result for calculating $g(\alpha)$ for a given $\alpha$            | 68   |

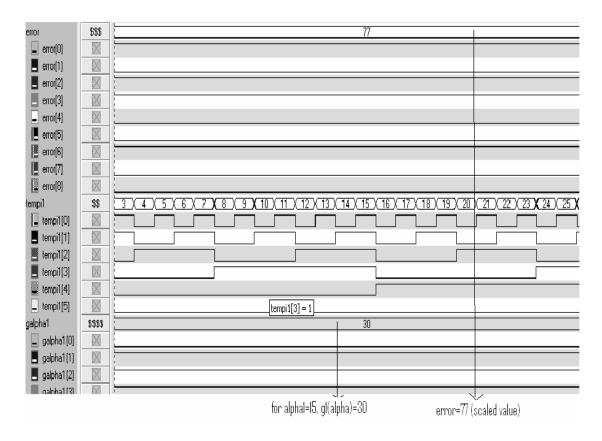

| Figure 4.16, ModelSim simulation result for calculating error                                       | 69   |

| Figure 4.17, Simulation result of the rotor position estimator                                      | .70  |

| Figure 4.18, Simulation result showing the final output when $\alpha$ becomes equal to $\theta$ and | d    |

| speed becomes zero                                                                                    | .71 |

|-------------------------------------------------------------------------------------------------------|-----|

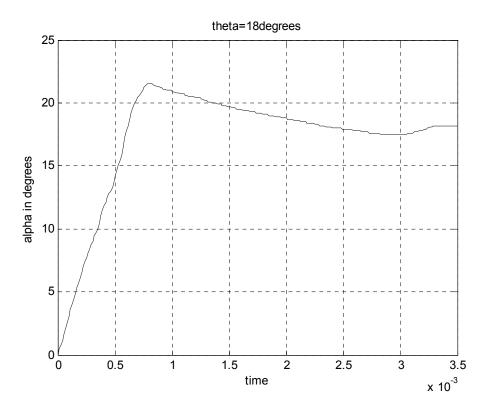

| Figure 5.1, Simulated estimated rotor position transient obtained from the Simulink                   |     |

| model for $\theta = 18^{\circ}$                                                                       | .73 |

| Figure 5.2, Simulated estimated rotor position transient obtained from the post synthes               | sis |

| Verilog model for $\theta$ =18°.                                                                      | .74 |

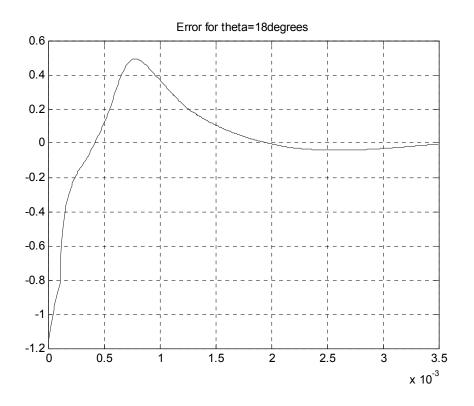

| Figure 5.3, Simulated result of the calculated error for the Simulink model for $\theta = 18^{\circ}$ | .75 |

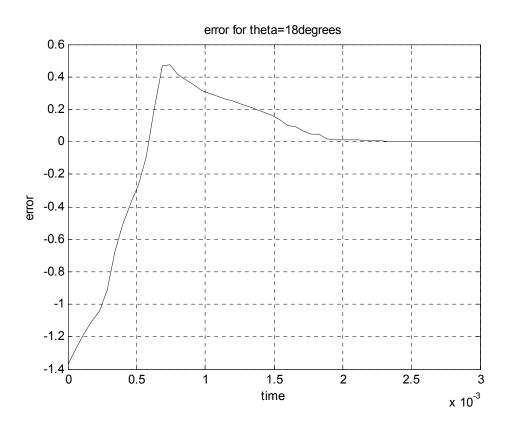

| Figure 5.4, Simulated error transient obtained from the post synthesis Verilog model for              | or  |

| $\theta = 18^{\circ}$                                                                                 | .76 |

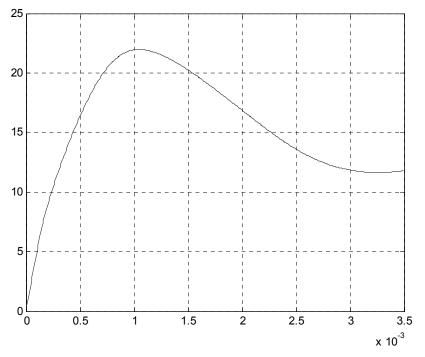

| Figure 5.5, Simulated estimated rotor position transient obtained from the Simulink                   |     |

| model for $\theta = 13^{\circ}$                                                                       | 77  |

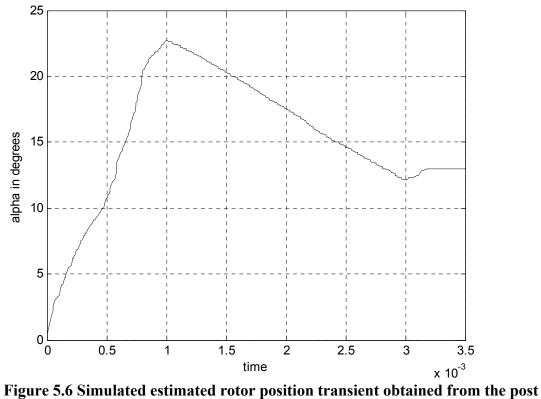

| Figure 5.6, Simulated estimated rotor position transient obtained from the post synthes               | sis |

| Verilog model for $\theta = 13^{\circ}$                                                               | 78  |

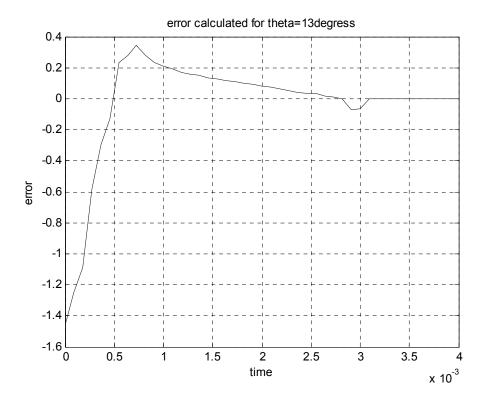

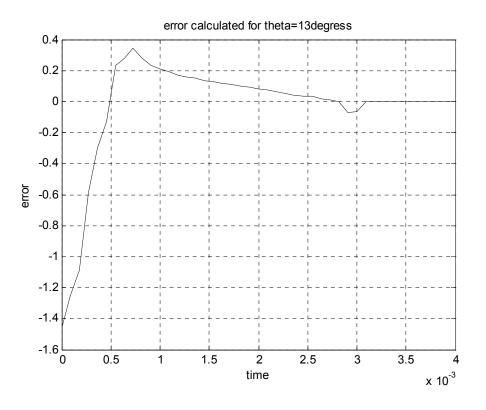

| Figure 5.7, Simulated error transient obtained from the Simulink model for $\theta = 13^{\circ}$      | 79  |

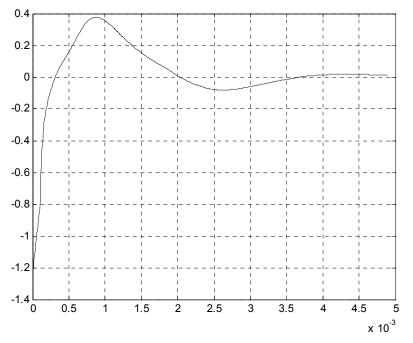

| Figure 5.8, Simulated error transient obtained from the post synthesis Verilog model for              | or  |

| θ=13°                                                                                                 | 79  |

| Figure 5.9, Block diagram of the SRM control system                                                   | .83 |

| Figure 5.10, Experimental setup for testing the design                                                | .84 |

| Figure 5.11, Experimental FPGA output for the block galpha                                            | 86  |

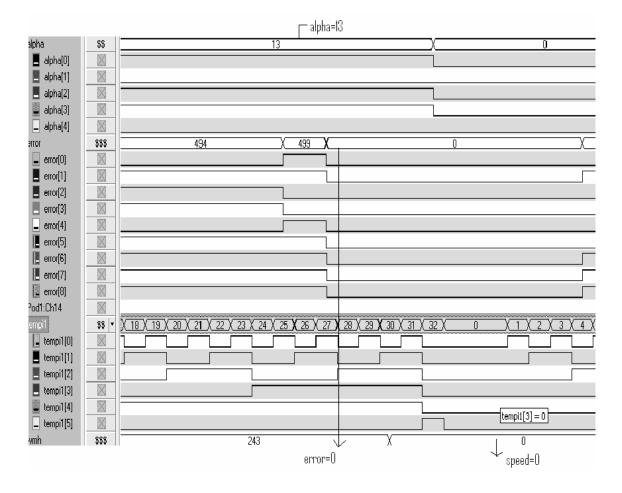

| Figure 5.12, Experimental FPGA output for the block errorlow                                          | 87  |

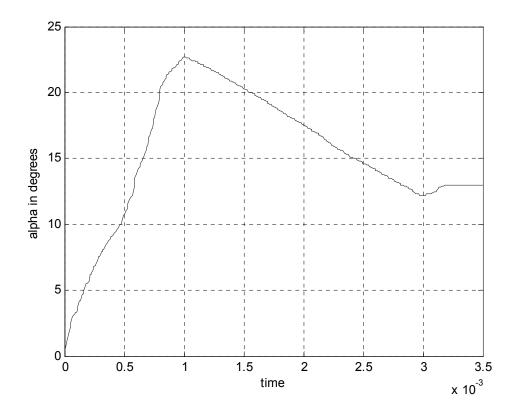

| Figure 5.13, Experimentally measured FPGA output for an actual rotor position equal                   | to  |

| θ=13°                                                                                                 | 89  |

| Figure 5.14, Experimentally measured FPGA result for the error for $\theta = 13^{\circ}$              | .90 |

| Figure 5.15, Waveform showing the FPGA output for the block sensetheta                                | 91  |

# CHAPTER 1 INTRODUCTION

#### 1.1 Introduction to Switched Reluctance Motor

The switched reluctance motor (SRM) is a doubly salient and singly excited machine with an unequal number of rotor and stator poles to avoid magnetic locking between the stator and rotor poles. The main advantages of Switched Reluctance motors are their simple construction due to the absence of magnets, rotor conductors, and brushes and high system efficiency over a wide speed range. However, the need for a direct rotor position sensor to commutate the current from phase to phase synchronously with rotor position has excluded the motor from many cost-sensitive applications.

For successful and reliable operation of the SRM, it is essential to know the rotor position accurately. For high performance SRM drives used in aircrafts, ships, and servo systems accurate rotor position is required to avoid initial starting hesitation. An encoder, resolver, or Hall sensor attached to the shaft is normally used to supply the rotor position, but the use of these sensors increases costs, decreases system reliability, and also increases the overall physical envelope of the motor drive and the number of motor wires. A variety of algorithms for sensorless control have been developed, most of which involve evaluation of the variation of magnetic circuit parameters that are dependent on the rotor position. These sensorless schemes use only terminal measurements and do not require additional hardware while maintaining reliable SRM operation over the entire speed and torque range with high resolution and accuracy.

In this thesis, a sensorless technique that has been developed to determine the SRM's rotor position is implemented using a field programmable gate array (FPGA) and the performance of the FPGA implementation is compared to a signal processor implementation.

#### 1.2 Basic Structure and Principle of SRM Operation

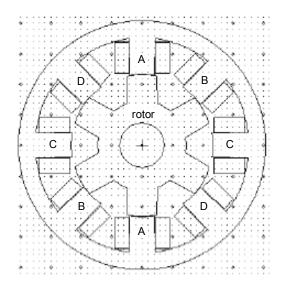

A Switched Reluctance (SR) motor is a rotating electric machine where both the stator and rotor have salient poles, with windings only on the stator. Windings of diametrically opposite stator poles are connected in series or parallel to form one phase of the machine. The cross-section diagram of a 4-phase, 8/6 (# of stator poles/# of rotor poles) SRM is shown in figure 1.1.

Figure 1.1 Cross-section diagram of an 8/6, four-phase SRM

The basic principle of a SRM operation is that when a stator phase is excited, the rotor of the SRM always rotates to the nearest position of minimum reluctance (aligned position), which corresponds to the minimum stored energy in the system.

When a stator pole pair is not aligned with a rotor pole pair, coils of the stator pole pair are excited by a sequence of current pulses applied to the phase and a magnetic flux path is created through the excited stator poles, air gap and the nearest rotor poles. Due to the tendency for the reluctance of the flux path to minimize, the rotor poles are attracted to the stator poles, producing torque. Then, when the stator pole pair becomes nearly aligned with the rotor pole pair, the excitation to the active coils is removed so that torque is not produced in the reverse direction; instead, coils of an adjacent stator pole pair are excited so that another rotor pole pair is attracted to the new stator pole pair since they are not aligned. By selectively exciting the stator pole pairs to attract rotor pole pairs, synchronous continuous motion and continuous torque are produced. The current pulses need to be applied to the respective phase at the correct rotor position relative to the excited phase. Therefore, it is evident that the rotor position plays a critical role in determining which phase of the motor must be energized in order to produce the desired torque in the desired direction.

#### 1.3 Contribution of the Thesis

The rotor position information in SRM drives is essential in determining the switching instants for proper control of speed, torque and torque pulsations. A shaft position transducer is usually employed to determine the rotor position. In inexpensive systems the rotor position sensor is comprised of a magnetized ring with Hall Effect sensors, or opto-interrupters with a slotted disk that produce discrete signals with no information between the pulses. In more expensive systems, a large number of pulses per revolution can be obtained from a resolver or optical encoder. Alternatively, a large number of pulses can be obtained by phase locking a high frequency oscillation to the pulses of discrete position sensors. Systems with such high resolution can work well down to zero speed. However, these sensors add complexity and cost to the system. Moreover, electromagnetic interference and temperature effects tend to reduce the reliability of the system. In order to avoid these difficulties some form of indirect position-sensing scheme is desirable. Several indirect position-sensing methods have been patented and published for sensorless control of SRM drives. The various indirect position-sensing techniques presented in the literature have their own advantages and disadvantages. Furthermore, the developed methods are application specific, depending on factors like, motor characteristics, converter topology, control strategy etc. The design considerations directly affect the type of indirect position scheme to be adopted for the drive.

The expected benefits of the indirect methods are: elimination of the electrical sensor connections, reduced SRM size, no maintenance, insusceptible to environmental factors and increased reliability. In addition, the expected features of desirable indirect methods

include: operating at zero speed and higher speed the same as conventional direct position sensors.

All of these indirect sensing methods use the instantaneous phase inductance variation information in some way to detect the rotor position at low speeds. This is possible with SRMs since the flux-angle-current characteristics vary significantly between the aligned and unaligned positions of the doubly salient stator and rotor poles.

In this thesis, a new method which estimates the rotor position by comparing the measured and estimated conductance values and calculating an error, which is input to a state estimator, is implemented using a FPGA. The estimated rotor position angle is used to control the electronic commutator, which controls when current is allowed in the machine's phases. The commutator is included in the FPGA with the state estimator and error calculation hardware. The rotor position estimator model is created and simulated in the Matlab/Simulink environment. The design is coded using the Verilog hardware design language and synthesized using Xilinx tools and simulated using Modelsim Simulator. The Simulated results obtained from both Simulink and Modelsim are compared. The design is then implemented on an FPGA chip and tested.

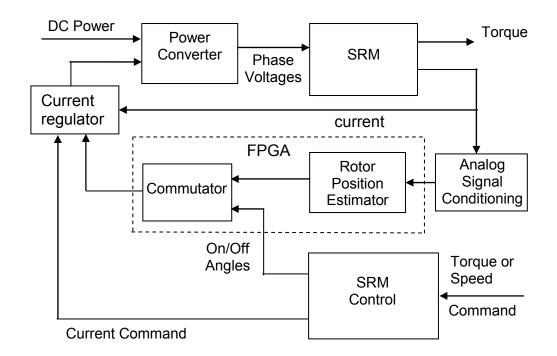

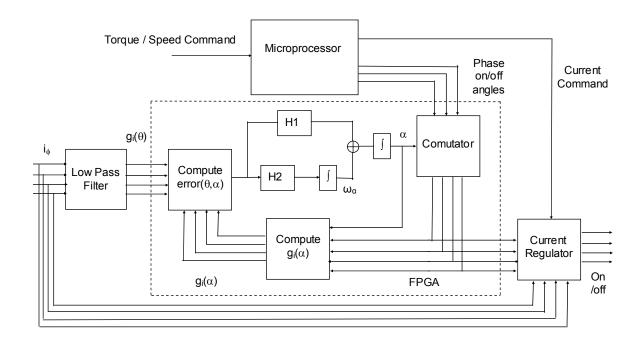

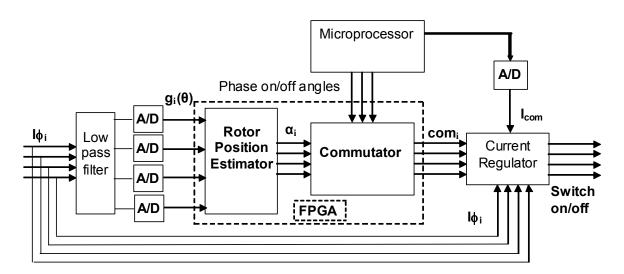

The block diagram of the entire motor drive system is as shown in figure 1.2.

Figure 1.2: The Block diagram of the entire SRM based motor system

The Power Converter typically uses Silicon MOSFETs to control the voltage to the motor. The turning on and turning off of the MOSFETs is controlled by a current regulator circuit that forces the SRMs phase currents to be equal to the current command. The current command to the current regulator is the desired current in an SRM phase. The current command depends on the desired average torque. The rotor position estimator gives the rotor position which is given as input to the commutator, which controls the current pulses, that is determines which phase has to be excited to get the desired torque.

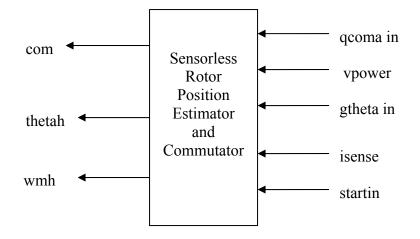

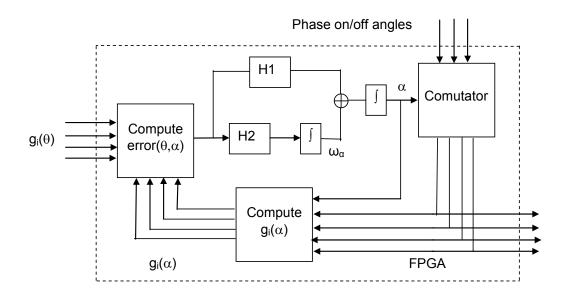

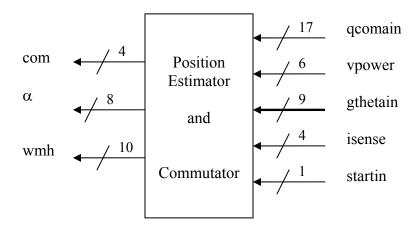

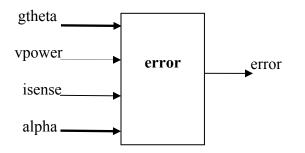

This thesis deals with the design of the blocks titled Rotor Position Estimator and Commutator in the FPGA block, in figure 1.2. The inputs and outputs of the FPGA are summarized in figure 1.3. The inputs to the estimator are used to compute the rotor position. The instantaneous position information is used as an input to the commutator to derive the instant of switching of the currents.

Figure 1.3 Block Diagram of Rotor Position Estimator and Commutator

#### 1.4 Outline of the Thesis

This thesis is organized as follows:

Chapter 1 gives a general introduction of switched reluctance motors: its basic structure and principle of operation. Then the motivation of this thesis, which is the implementation of the rotor position estimator on a Field Programmable Gate Array (FPGA) is given.

Chapter 2 discusses the basic SRM model and the background issues related to the rotor position estimator and SRM control.

Chapter 3 gives the basic SRM drive system model created in Simulink and Matlab and important simulation results for the implementation of the rotor position estimator.

Chapter 4 introduces to the design of the rotor position estimator using the Verilog Hardware design language and its synthesis and simulation results using Xilinx tools and Modelsim Simulator. It also introduces to the Field Programmable Gate Array (FPGA).

Chapter 5 gives the comparison of the simulation results obtained using both Simulink and Modelsim. It also gives the implementation of the rotor position estimator on the FPGA. Experimental results from a programmed FPGA are presented to verify the correct operation of the rotor position estimator. The performance of the FPGA based SRM rotor position estimator in terms of calculation time is compared to a signal processor implementation of the same position estimator algorithm.

#### **CHAPTER 2**

## **DESIGN ANALYSIS OF ROTOR POSITION ESTIMATOR**

#### 2.1 Variation of inductance with rotor position

An efficient operation of the Switched Reluctance Motor (SRM) can be achieved only by proper determination of the rotor position. Rotor position measurement or estimation is an integral part of SRM control because of the nature of reluctance torque production. The excitation of the SRM phases needs to be properly synchronized with the rotor position for effective control of speed, torque and torque pulsation.

All SRM's possess a unique relationship between phase inductance, phase current, and rotor position, which makes prediction of rotor position possible. Since the rate of change of phase current is dictated by the incremental inductance of the phase circuit, and the incremental inductance is in turn a function of rotor position and phase current, rotor position can be deduced from knowledge of phase current and its rate of change.

At low speeds, to estimate the rotor position of the SRM, the variation of the phase inductance with rotor position can be used. But because the SRM operates with substantial iron saturation at torque producing currents, the phase inductance is a function of both rotor position and phase current.

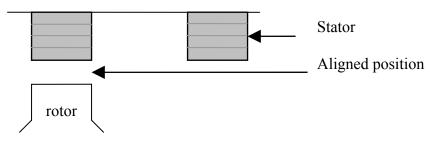

The SRM motion is produced because of the variable reluctance in the air gap between the rotor and the stator. When a stator winding is energized, producing a single magnetic field, reluctance torque is produced by the tendency of the rotor to move to its minimum reluctance position. When a rotor pole is aligned with a stator pole, as shown in figure 2.1, there is no torque because field lines are orthogonal to the surfaces (considering a small gap). In this aligned position, the unsaturated inductance is a maximum since the reluctance is minimum. If one displaces the rotor from the aligned position, there will be torque production that will tend to rotate the rotor back to the aligned position.

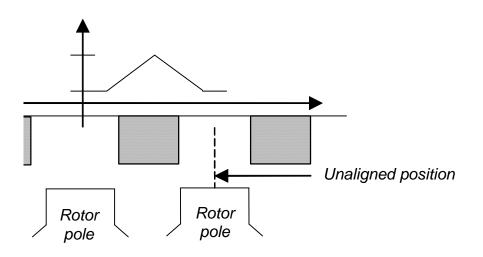

**Figure 2.1 Aligned Position**

If current is injected in the phase when the rotor is rotated to the unaligned position, as shown in figure 2.2, there will not be torque production (or very little). If one displaces the rotor from the unaligned position, then a torque is produced that tends to displace the rotor to the nearest aligned position.

**Figure 2.2 Unaligned Position**

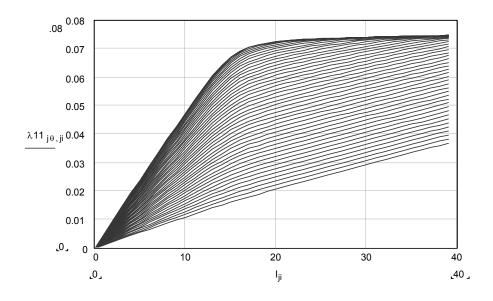

When rotor poles are aligned with the stator poles of a relevant phase the flux linkage, for a given phase current, is maximized. The flux linkage is a maximum when the unsaturated inductance is a maximum. However at this aligned position the relationship between flux linkage and phase current is extremely nonlinear in a well-designed machine, because the poles are magnetically saturated at the rated phase current. The flux linked by a phase versus phase current for different rotor positions is plotted in figure 2.3. The slope of the flux curves at a fixed rotor position is the incremental phase inductance.

Figure 2.3 Plot of the SRM's phase flux versus current for different rotor positions showing the effect of iron saturation.

Because this slope changes with current so does the phase inductance as shown in figure 2.4 where the phase inductance is plotted versus rotor position for different currents.

Figure 2.4 Plot of the SRM's phase inductance versus rotor position for different currents.

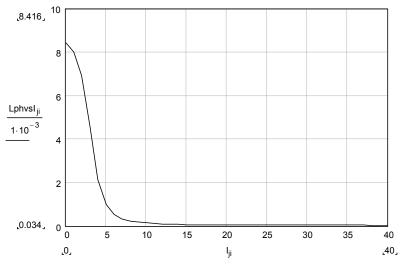

At low currents, the phase inductance has an essentially triangular shape versus rotor position while at high currents the phase inductance is far from triangular. This makes using the current in the torque-producing phase for rotor position estimation very complex. Thus, the normal practice is to stimulate the non-torque-producing phases that normally have zero current in them for some instantaneous rotor positions, with small sensing currents, that do not saturate these phases and produce little torque, to do the position estimation. Figure 2.5 shows the aligned incremental phase inductance versus current for an experimental SRM. For iron saturation to be ignored in this machine the sensing phase current must be less than about 2.0A. It has its maximum inductance when it is in an aligned position and minimum inductance when unaligned. When the voltage is applied to the stator phase the current in that phase increases and the SRM creates torque in the direction of increasing inductance.

Figure 2.5 Plot of the phase inductance at the aligned position versus current for an SRM.

## 2.2 Theory behind the Rotor Position Estimator used in this thesis

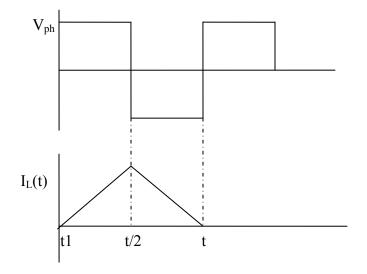

When voltage is applied across the stator winding of the SRM as shown in the figure 2.6,

Figure 2.6 Current Profile across an inductor

the current in the inductor obeys the following equations

$$Vph(t) = Lph(\theta(t))\frac{diph}{dt}, \qquad iph(t) = iph(t1) + \int_{t_1}^t \frac{Vph(\tau)}{Lph(\theta(\tau))}d\tau$$

(2.1)

$V_{ph}(t)$  is a constant from  $t_1$  to t with a value equal to the DC voltage,  $V_{DC}$ . It will be assumed that  $i_{ph}(t_1) = 0$  since t1 coincides with a zero phase current. It will also be assumed that the modulation frequency  $F_{mod}$  is high enough that the inductance does not vary over the time period of one modulation cycle. In this case

$$iph(t) = \frac{1}{Lph(\theta(t1))} \int_{t1}^{t} Vph(\tau) d\tau \equiv g(\theta(t1)) \int_{t1}^{t} Vph(\tau) d\tau \approx g(\theta(t1)) \cdot VDC \cdot t$$

(2.2)

where  $g(\theta)$  has been defined as the inverse of the phase inductance. Equation 2 gives the current during the increasing current part of the waveform in figure 2.6 and is a positive ramp as expected. The peak phase current (at  $t = t_1 + D_{mod}T_{mod}$ ) is modulated by the inverse phase inductance function  $g_{ph}(\theta)$  which does not depend on the details of the phase current or voltage during one modulation cycle. Similarly the phase current ramps down during the decreasing current part of the waveform generating a triangle of current whose peak depends on  $g_{ph}(\theta)$ . Taking the average of the phase current over one modulation cycle gives

$$\langle iph(\theta(t_1)) \rangle_{\text{Tmod}} = \frac{1}{\text{Tmod}} \int_{t_1}^{t_1 + \text{Tmod}} g_{ph}(\theta(t_1)) \int_{t_1}^t V_{ph}(\tau) d\tau dt = g_{ph}(\theta(t_1)) \frac{1}{\text{Tmod}} \int_{t_1}^{t_1 + \text{Tmod}} \int_{t_1}^t V_{ph}(\tau) d\tau dt$$

$$\langle iph(\theta(t_1)) \rangle_{\text{Tmod}} \equiv i_{sense}(\theta) = g_{ph}(\theta) \frac{V_{DcT \text{ mod}}}{4}$$

(2.3)

Thus the average of the phase current over one modulation cycle is proportional to the inverse phase inductance function  $g_{ph}(\theta)$ .

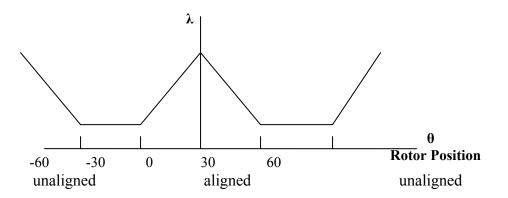

The  $g_{ph}(\theta)$  functions (one for each phase) can be used to estimate the SRM's rotor position since they are known ahead of time from the machine's characteristics and they can be measured by exciting the phases of the SRM as described above. For simplicity in what follows, it will be assumed that the known machine inductance profile has a constant value equal to the unaligned inductance for rotor positions where the rotor and stator poles do not overlap and it varies linearly from the unaligned inductance value to the aligned inductance value when the poles overlap as shown in figure 2.7.

Figure 2.7 Ideal phase inductance profile versus rotor position.

An error between the estimated and measured angle cannot be computed directly since the rotor position is not measured. However a suitable error can be defined using the  $g_{ph}(\theta)$  functions which can be measured using the average in equation 2.3. Let  $\theta$  be the actual rotor position and  $\alpha$  be the estimated rotor position, then the error for data from phases one and two is

$$error_1(\theta, \alpha) = g_2(\theta)g_1(\alpha) - g_1(\theta)g_2(\alpha)$$

(2.4)

Note that when  $\theta = \alpha$ , the error is zero. The total error is just the sum of the errors for each phase pair. The error for a four phase SRM is

$$error_{tot}(\theta,\alpha) = (g_2(\theta)g_1(\alpha) - g_1(\theta)g_2(\alpha)) + (g_3(\theta)g_2(\alpha) - g_2(\theta)g_3(\alpha)) + (g_4(\theta)g_3(\alpha) - g_3(\theta)g_4(\alpha)) + (g_1(\theta)g_4(\alpha) - g_4(\theta)g_1(\alpha))$$

(2.5)

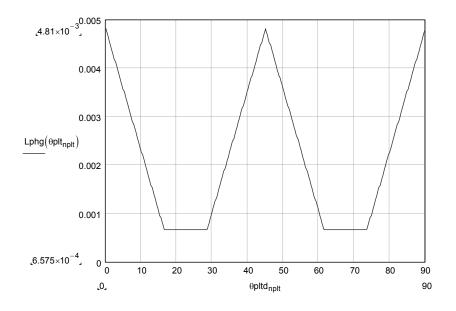

The total error is also zero when  $\theta = \alpha$ . The total error depends on both  $\theta$  and  $\alpha$  and thus on both  $\theta$  and  $\alpha - \theta$ . It can be verified that this error has one sign for  $\alpha - \theta$  positive and the opposite sign when  $\alpha - \theta$  is negative for any  $\theta$ . This is shown in figure 2.8 for an experimental 4 phase SRM for  $\alpha - \theta = +/-1^\circ$ ,  $+/-5^\circ$ , and  $+/-10^\circ$  and rotor positions from  $0^\circ$ to 90°.

Figure 2.8 The computed error for an experimental 4 phase SRM for  $\alpha - \theta = +/-1^{\circ}$ , +/-5°, and +/-10° and rotor positions from 0° to 90°.

Thus, this error can be used in a state estimator to estimate the rotor position. The gain of the estimator depends on rotor position but because the sign of the error does not vary with rotor position, it will be possible to design a stable state estimator.

#### 2.3 Rotor Position State Estimator Equations

Consider the physical system of a motor. The state equations for the physical system are of the form

$$X_p = A x_p + B u_p \tag{2.6}$$

$$Y_p = C x_p \tag{2.7}$$

Where the subscript p indicates the variables are for the physical system. The motor's acceleration is given by

$$\frac{Jdwm}{dt} = Te - Tload$$

(2.8)

where, J= Moment of Inertia

$$\frac{dwm}{dt} = \text{acceleration}$$

$$T_e = \text{electrical Torque}$$

$$T_{load} = \text{mechanical Torque}$$

When the motor runs at steady speed, the acceleration is zero because the load and electrical torques balance. Therefore

$$\frac{\mathrm{dwm}}{\mathrm{dt}} = 0 \tag{2.9}$$

The rate of change of rotor position is the rotor speed,  $\boldsymbol{w}_m$  given by

$$\frac{d\theta}{dt} = \omega_m \tag{2.10}$$

where  $\theta$  is the angular position of the rotor of the motor.

The equation (2.6) can be deduced from equations (2.9) and (2.10)  $\frac{d}{dt} \begin{bmatrix} \theta \\ \omega_m \end{bmatrix} = \begin{bmatrix} 0 & 1 \\ 0 & 0 \end{bmatrix} \begin{bmatrix} \theta \\ \omega_m \end{bmatrix}$ (2.11) Since time rate of change of the rotor position is nothing but  $\omega_m$  (the rate of change of position is speed), the first row of the matrix is  $\begin{bmatrix} 0 & 1 \end{bmatrix}$  and since the acceleration is zero, the rotor speed  $\omega_m$  is zero, hence the second row of matrix is  $\begin{bmatrix} 0 & 0 \end{bmatrix}$ .

The state equations for the state estimator in the linear case are

$$X_e = A x_e + B u_e + H (Y_e - Y_p)$$

(2.11)

$Y_e = C x_e$  (2.12)

Since the model system used to estimate the unmeasurable state is not exactly the same as the real physical system, an error between what is measured and the estimator's prediction of what is measured (Y) is input to the model estimator equations. In equation 2.11 this error input is given by H (Y<sub>e</sub> – Y<sub>p</sub>), where H is a constant gain matrix to be determined by the designer such that the error between the estimated state and the actual state values decays to zero (thus H (Y<sub>e</sub> – Y<sub>p</sub>) decays to zero) and thus the estimated state is the correct value. The gain matrix H is adjusted to see how fast and with what dynamics the state error decays to zero

The error is the difference between the actual and the estimated values and can be computed by

$$d \operatorname{Error} / dt = d (X_{p} - X_{e}) / dt$$

= A X<sub>p</sub> + B U<sub>p</sub> - A X<sub>e</sub> + B U<sub>e</sub> + H (Y<sub>e</sub> - Y<sub>p</sub>)

= A (X<sub>p</sub>- X<sub>e</sub>) - H(C X<sub>e</sub> - C X<sub>p</sub>)

= (A+HC) (X<sub>p</sub>- X<sub>e</sub>)

= (A+HC) ε (2.13)

$\varepsilon = \varepsilon_0 e^{(A+HC)t}$

For the error to decay to zero the real parts of the eigen values of the matrix (A+HC) must be negative. The matrix H is chosen so that the error decays with the desired dynamics.

For the SRM rotor position estimator the state vector and state vector error vectors are

$$X = \begin{bmatrix} \theta \\ \omega_m \end{bmatrix}$$

(2.14)

$$\varepsilon = \begin{bmatrix} \theta - \alpha \\ \omega_m - \omega_\alpha \end{bmatrix}$$

(2.15)

where  $\alpha$  is the estimated rotor position angle and  $\omega_{\alpha}$  is the estimated speed of the rotor. Differentiating equation (2.14),

$$\frac{dX}{dt} = \frac{d}{dt} \begin{bmatrix} \theta \\ \omega_m \end{bmatrix}$$

$$= \begin{bmatrix} 0 & 1 \\ 0 & 0 \end{bmatrix} \begin{bmatrix} \theta \\ \omega_m \end{bmatrix} + \begin{bmatrix} 0 \\ 1 \end{bmatrix} (Te - T_{load}) \quad \dots \text{ (from equation (2.8))}$$

But because of equation (2.9), ( $T_e$ -  $T_{load}$ ) is equal to zero.

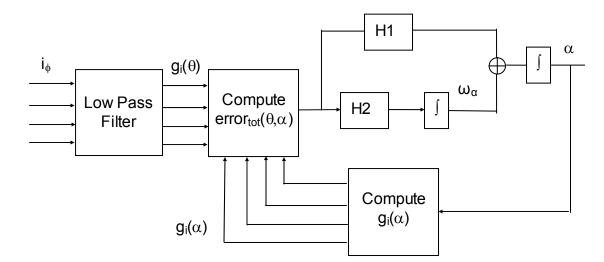

The equation for the state estimator is defined as

$$\frac{d}{dt}\begin{bmatrix}\alpha\\\omega\alpha\end{bmatrix} = \begin{bmatrix}0 & 1\\0 & 0\end{bmatrix}\begin{bmatrix}\alpha\\\omega\alpha\end{bmatrix} + \begin{bmatrix}H_1\\H_2\end{bmatrix}(g_2(\theta)g_1(\alpha) - g_1(\theta)g_2(\alpha)) + (g_3(\theta)g_2(\alpha) - g_2(\theta)g_3(\alpha)) + (g_4(\theta)g_3(\alpha) - g_3(\theta)g_4(\alpha)) + (g_1(\theta)g_4(\alpha) - g_4(\theta)g_1(\alpha)))$$

$$= \begin{bmatrix} 0 & 1 \\ 0 & 0 \end{bmatrix} \begin{bmatrix} \alpha \\ \omega_{\alpha} \end{bmatrix} + \begin{bmatrix} H_1 \\ H_2 \end{bmatrix} error_{tot}(\theta, \alpha)$$

(2.16)

$$\frac{d\alpha}{dt} = \omega_{\alpha} + H_{1.error_{tot}}(\theta, \alpha)$$

(2.17)

where  $\operatorname{error}_{tot}(\theta, \alpha)$  was defined previously in equation 2.5. To compute the stability of the state error e the nonlinear error function must be linearized.

$$error_{tot}(\theta, \alpha) = error_{tot}(\theta, \theta - \alpha) = error_{tot}(\theta, \varepsilon_{\theta}) \approx \left(\frac{\partial}{\partial \theta e} \left(error_{tot}(\theta, \varepsilon_{\theta})\right)_{\theta, 0}\right) \cdot \varepsilon_{\theta}$$

(2.18)

The partial derivative in equation 2.18 can be estimated from the results in figure 2.8. With the linearization of the error function the error dynamics are governed by

$$\frac{d}{dt}\begin{bmatrix}\varepsilon_{\theta}\\\varepsilon_{\omega}\end{bmatrix} = \begin{bmatrix}H_{1}\frac{\partial}{\partial\varepsilon_{\theta}}(error_{tot}(\theta,\varepsilon_{\theta})_{\theta,0} & 1\\H_{1}\frac{\partial}{\partial\varepsilon_{\theta}}(error_{tot}(\theta,\varepsilon_{\theta})_{\theta,0} & 0\end{bmatrix}\begin{bmatrix}\varepsilon_{\theta}\\\varepsilon_{\omega}\end{bmatrix}$$

(2.19)

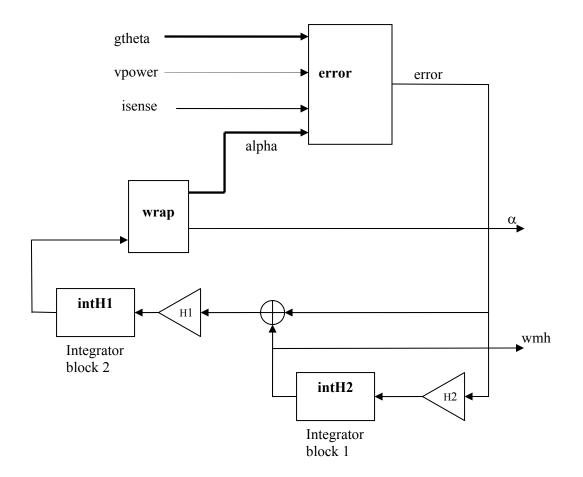

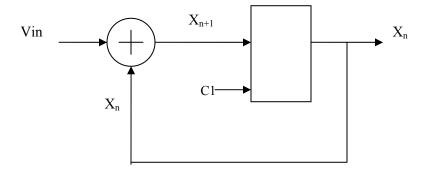

The equations (2.16) and (2.17) can be represented by the block diagram shown in figure 2.9.

Figure 2.9. Block diagram representation of the state estimator

This system is used to estimate the values of rotor position and rotor speed. In this thesis, this system is coded using the Verilog hardware design language and then is implemented

on an FPGA chip. The programmed FPGA chip would be suitable for use as part of the SRM motor control.

The block diagram of the control system of the Switched Reluctance Motor is as shown in figure 2.10.

Figure 2.10 Block Diagram of the SRM control system

The block diagram of the block FPGA, which is actually the basis of this thesis, is as shown in the figure 2.11.

Figure 2.11 Block diagram of the FPGA that is the subject of this thesis

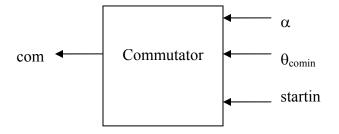

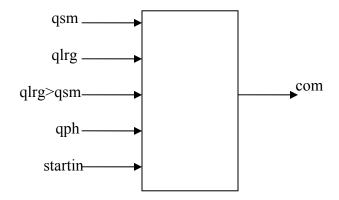

The estimated value of rotor position,  $\alpha$  is given as input to the commutator circuit. The basic block diagram of the commutator is as shown in the figure 2.12.

Figure 2.12 Block diagram of Commutator

The commutator gets the estimated rotor position angle as input, which it compares with the desired angle range and determines which of the four phases is to be excited and then accordingly turns on the phase that is to be excited. Thus, the current is given as input to that phase, which will in turn produce the desired torque. The commutator compares the instantaneous estimated rotor position  $\alpha$  with the values ( $\theta_{sm}$ ,  $\theta_{lrg}$ ) which are given as input through ' $\theta_{comin}$ ' and commutates the current in the corresponding phase. The

commutator insures that the currents in the stator circuits are switched on and off in accordance with the rotor position. The torque can be controlled to give a resultant which is positive (i.e. motor action) or is negative (i.e. generator action) simply by switching the current in the coil on and off at appropriate instants.

A model of the circuitry in the FPGA and which is the subject of this thesis has been created in Simulink prior to this thesis research and was available to facilitate this research. This model will be discussed in detail in Chapter 3.

## CHAPTER 3

# SIMULINK MODEL OF THE CIRCUIT TO BE DESIGNED

#### 3.1 Introduction to Simulink model

The simulation of a system is important in view of its design and experimental realization. Simulation using Matlab/Simulink allows a high flexible modeling environment to model power electronic systems containing electrical machinery, electronic controls, and power circuits. This thesis implements part of the control design for a power electronics controller for a SRM. During this thesis a complete Matlab/Simulink model of this power electronics system was available. It included a model of the part of the control being implemented here. All Simulink simulations are documented by their block diagrams, their corresponding special Matlab functions and their input parameters. A strong aspect of the SRM simulation using Simulink is the use of conventional blocks allowing easier understanding of the program's structure.

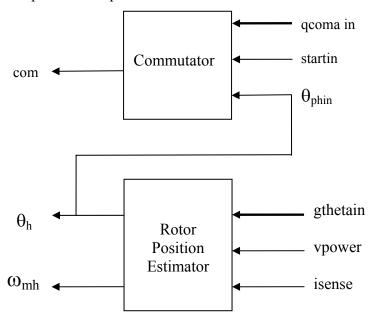

Figure 3.1 shows the block diagram of the Rotor Position Estimator and Commutator with all the inputs and outputs.

Figure 3.1 Block Diagram of Rotor Position Estimator and Commutator

Consider the block diagram of the Sensorless Rotor position estimator. The input gthetain represents the inverse inductance value of the actual rotor position  $g(\theta)$ . The input vpower is the voltage applied to the motor. The input isense is the select signal given as input to the estimator to choose between  $g(\theta)$  and  $g(\alpha)$ . Recall that the error is defined as

$$error_{tot}(\theta,\alpha) = (g_2(\theta)g_1(\alpha) - g_1(\theta)g_2(\alpha)) + (g_3(\theta)g_2(\alpha) - g_2(\theta)g_3(\alpha)) + (g_4(\theta)g_3(\alpha) - g_3(\theta)g_4(\alpha)) + (g_1(\theta)g_4(\alpha) - g_4(\theta)g_1(\alpha))$$

If the measured  $g(\theta)$  from a particular phase is not available because the rotor is in a position where that phase is producing torque (as seen in figure 3.2), the calculated  $g(\alpha)$  for that phase is used instead. The signal isense is high when the rotor is in a position where the given phase is not producing torque and thus is being energized with sense pulses to produce  $g(\theta)$  and is low when the rotor is in a position where the given phase is producing torque as shown in figure 3.3. When the select signal isense is high,  $g(\theta)$  is selected and thus used in the error calculation used to estimate the rotor position. When isense is low,  $g(\alpha)$  for the given phase is selected because the  $g(\theta)$  for that phase is not available, and thus error is computed without the  $g(\theta)$  information from the given phase. The error is computed using only the  $g(\theta)$ s from the other phases.

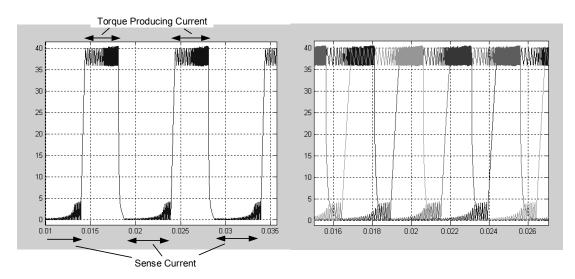

Fig. 3.2 Phase current showing the torque producing and sense phase currents

Figure 3.3 Plot of measured (from simulation)  $g_1(\theta)$  and the select signal isense for phase one.

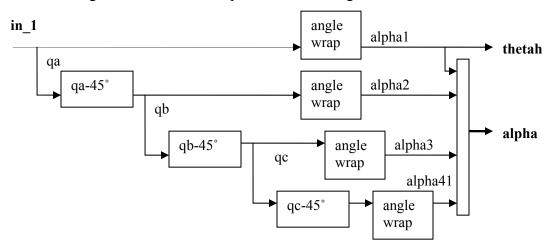

The output  $\omega_{mh}$  represents the speed of the motor. The output  $\theta_h$  represents the estimated rotor position,  $\alpha$ . This rotor position angle,  $\alpha$  is the input to the commutator as  $\theta_{phin}$ . The rotor position angle is shifted to produce 3 additional angles. These shifted angles are input to the same commutator hardware to produce the commutator output for the other 3 phases.

#### 3.2 Commutator Block

Now, consider the commutator block. The input startin is the select signal given to the commutator, which tells the commutator whether the user wants the SRM to operate normally and produce torque or to go into startup mode. If the startin select signal is high, the control and position estimator go into start up mode. In this mode the control continuously applies sense pulses to all four phases of the SRM so that the SRM's rotor position can be estimated without a net torque being produced and without the rotor rotating. When the user wants the SRM to produce torque, the input startin is made low taking the control and position estimator out of the startup mode. Now the control commutates the SRM so that it produces the commanded torque.

The input qcomin is a concatenation of the angles  $\theta_{sm}$ ,  $\theta_{lrg}$  and a one bit signal  $\theta_{lrg} > \theta_{sm}$ , given as a single digital word.

The angle  $\theta_{sm}$  is the smaller of  $\theta_{sm}$  and  $\theta_{lrg}$ . If the motor is rotating in the forward direction  $\theta_{sm}$  is the turn-on angle and  $\theta_{lrg}$  is the turn off angle and the reverse is true if the motor is rotating in the reverse direction. These angles are the rotor's position defined relative to a given stator. This rotor position is near the rotor's unaligned position with respect to the stator pole.

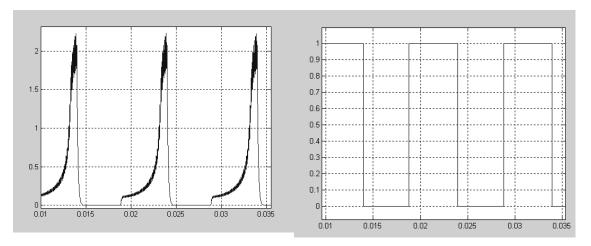

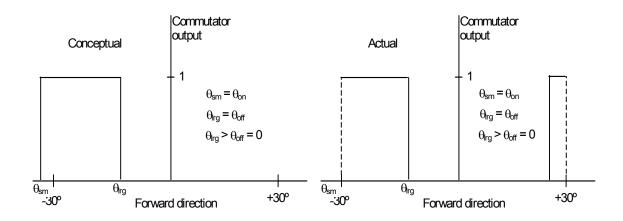

The commutator checks if the estimated rotor position angle  $\alpha$  falls in between  $\theta_{sm}$  and  $\theta_{lrg}$ . If the estimated rotor position is between these two angles the commutator outputs a one, otherwise it outputs a zero as shown in figure 3.4. This is done for all the four phases of the stator and accordingly each phase of the stator is commutated enabling the SRM to produce torque.

The signal  $\theta_{lrg} > \theta_{sm}$  is high when  $\theta_{lrg}$  is greater than  $\theta_{sm}$ , i.e. the normal case and low when  $\theta_{lrg}$  is smaller than  $\theta_{sm}$ , i.e. when the angles are outside the range of  $-30^{\circ}$  to  $+30^{\circ}$  and they must be wrapped to stay within this range as illustrated in figure 3.5 for forward rotor rotation.

Figure 3.4 Commutator output for forward and reverse directions under normal conditions.

Figure 3.5 Commutator output for forward rotation when the turn on angle is advanced beyond the allowed range.

The output com is the four-bit output from the commutator corresponding to the four phases, each bit being high or low according to whether that phase is to produce torque or not.

The commutation for all possible combinations of  $\alpha$  with respect to  $\theta_{sm}$ ,  $\theta_{lrg}$  and  $\theta_{lrg} > \theta_{sm}$  is discussed below.

| $\theta_{ph} > \theta_{sm}$ | $\theta_{ph} < \theta_{lrg}$ | $\theta_{lrg} \!\!>\!\! \theta_{sm}$ | com |

|-----------------------------|------------------------------|--------------------------------------|-----|

| 0                           | 0                            | 0                                    | 0   |

| 0                           | 0                            | 1                                    | 0   |

| 0                           | 1                            | 0                                    | 1   |

| 0                           | 1                            | 1                                    | 0   |

| 1                           | 0                            | 0                                    | 1   |

| 1                           | 0                            | 1                                    | 0   |

| 1                           | 1                            | 0                                    | 0   |

| 1                           | 1                            | 1                                    | 1   |

Table 3.1 Truth Table for the Commutator

As seen from the table 1.1, the commutator turns on for only three cases.

1) When the estimated rotor position  $\theta_{ph}$  falls in between  $\theta_{sm}$  and  $\theta_{lrg}$ , i.e.,  $\theta_{ph}$  is greater than  $\theta_{sm}$  and smaller than  $\theta_{lrg}$  and  $\theta_{lrg}$  is greater than  $\theta_{sm}$ .

2) When qph is larger than both  $\theta_{sm}$  and  $\theta_{lrg}$  and  $\theta_{lrg}$  is smaller than  $\theta_{sm}$ .

3) When qph is smaller than both  $\theta_{sm}$  and  $\theta_{lrg}$  and  $\theta_{lrg}$  is smaller than  $\theta_{sm}$ .

This truth table is obtained from figures 3.4 and 3.5.

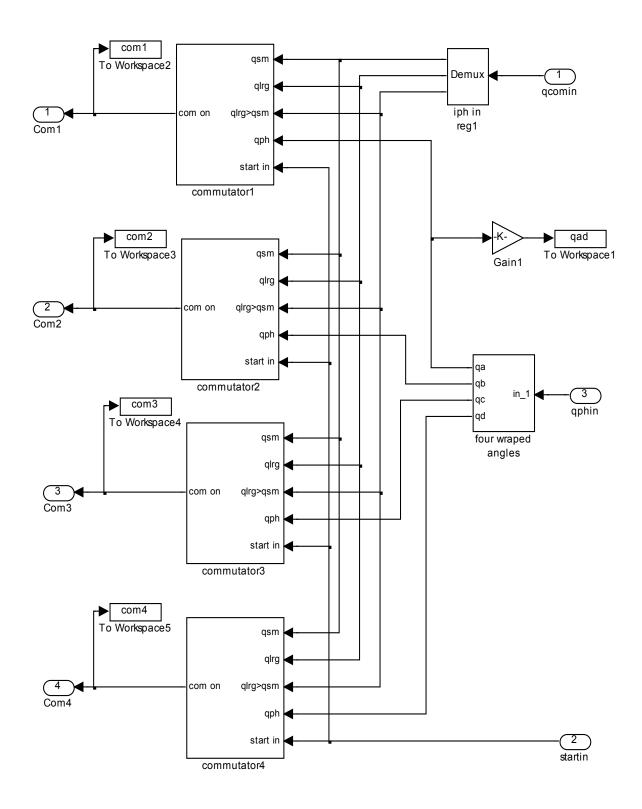

A Simulink model developed for the commutator block and available for this thesis showing all the four phases is as shown in figure 3.6. Note that in the Simulink model the letter q is used for  $\theta$  and no subscripts are used. The figure shows the block named four wrapped angles in which the shifting of the rotor position angle by 45° takes place for each phase, and then wrapping also takes place such that the rotor position angle for each phase lies in between -30° and +30°. The blocks named commutator1, commutator2 etc. represents the commutator for each phase.

Figure 3.6 Simulink model of the commutator block.

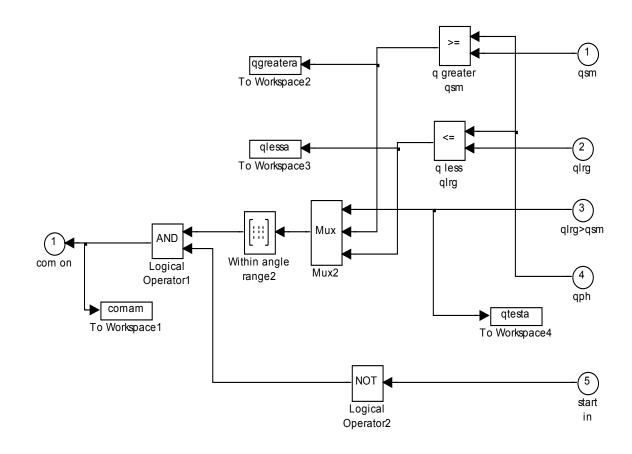

Figure 3.7 shows the Simulink model of the block commutator1, which is a sub-block of the commutator model. As seen in the figure, the angle  $\theta_{sm}$  (qsm), the angle  $\theta_{lrg}$  (qlrg), the signal corresponding to  $\theta_{lrg} > \theta_{sm}$  (qlrg>qsm), the startin signal and the estimated rotor position angle are the inputs. The model checks if the rotor angle is greater than  $\theta_{sm}$  and also if it is less than  $\theta_{lrg}$  and accordingly gives the 3-bit input to the look-up table which contains the corresponding truth-table shown in table 3.1. The model also checks the status of the startin signal. The output of the AND gate is the output of the commutator for that phase. If it is one, the phase is energized to produce torque and if it is zero, the phase is energized with sense pulses.

Figure 3.7 Simulink model of the commutator block for one phase

#### 3.3 Rotor Position Estimator

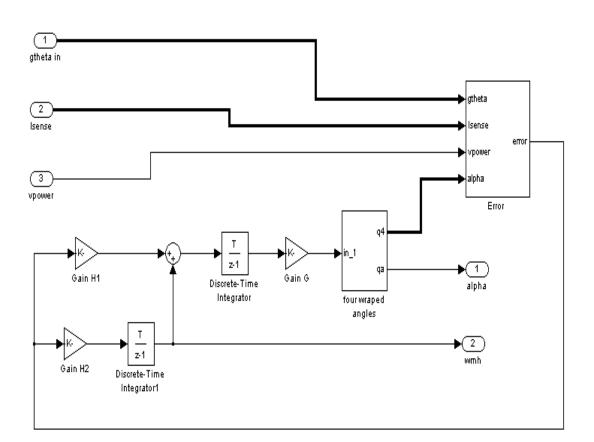

Now consider the block diagram of the Sensorless rotor position estimator in figure 3.1 shown in figure 3.8. The signals  $g(\theta)$  (gthetain),  $V_{DC}$  (vpower) and  $i_{sense}$  (isense) are inputs to the error computing block. Based on these inputs and also the shifted and wrapped estimated rotor position  $\alpha$  (alpha), the error is calculated.

Rotor postion Estimator

Figure 3.8 Simulink model of the rotor position estimator.

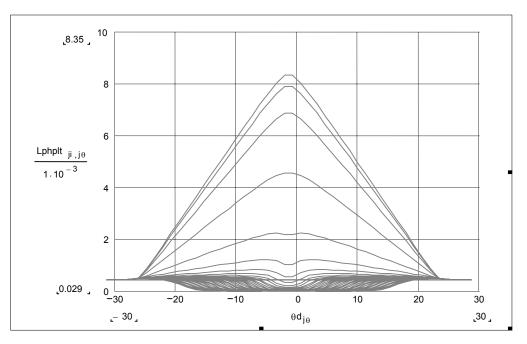

As discussed in chapter 2, the error is calculated using the measured inverse inductance values  $g(\theta)$  and the computed inverse inductance values  $g(\alpha)$  using equation 2.5. To compute the error, the values of  $g(\alpha)$  for all four phases must be computed.

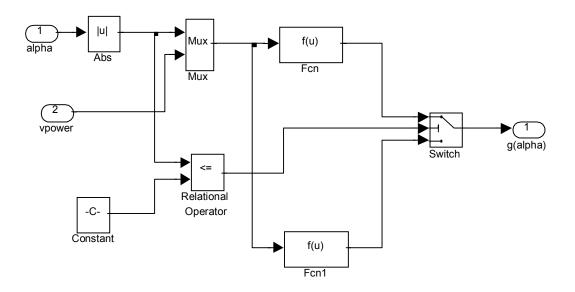

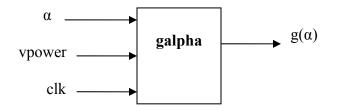

Figure 3.9 Simulink model of the block galpha to calculate  $g(\alpha)$

While calculating  $g(\alpha)$ , the absolute value of  $\alpha$  is used since the function is an even function of  $\alpha$ . The inverse inductance function  $g(\alpha)$  is a function of  $\alpha$  and should be equal to the measured  $g(\theta)$  function obtained by demodulating (low pass filtering) the sense pulse currents. The sense pulse currents are triangular in shape with a peak value determined by the SRM's phase inductance. Thus  $g(\alpha)$  is calculated by using the following equation.

$$g(\alpha) = \frac{\text{vpower} * (D \mod)^2}{100^2 * F \mod^* (\text{Laideal} - \text{mideal} * \text{alpha})}$$

(3.1)

where, vpower is the input power.

$D_{mod}$  is the modulation duty cycle in % = 40

$F_{mod}$  is the modulation frequency =1000Hz

Laideal is the inductance value in the aligned position= 0.0084

mideal= (Laideal-Lpideal )/thetaTm

Lpideal is the phase inductance at a rotor position of +/- 24°

thetaTm is the torque producing angle range, and 100 is to convert the % duty cycle to its decimal value.

In the Simulink model, equation 3.1 is computed by the block labeled Fcn, if alpha <thetaTm ( $\alpha$ <24°), otherwise equation 3.2 computed by Fcn1 is used.

$$g(\alpha) = \frac{\text{vpower}^* (D \text{ mod})^2}{100^2 * F \text{ mod}^* (\text{Lpideal} - \text{mpideal}^* (\text{alpha} - \text{thetaTm})}$$

(3.2)

mpideal= (Lpideal-Luideal)/ (thetaum-thetaTm);

thetaum is the unaligned rotor position angle in radians

It is known that the maximum inductance occurs at the position of minimum reluctance when the rotor pole aligns with the stator poles, and the minimum inductance occurs when the rotor and stator poles are completely unaligned. Therefore the inverse inductance  $g(\alpha)$  is maximum when the rotor and stator align with each other and is minimum when unaligned.

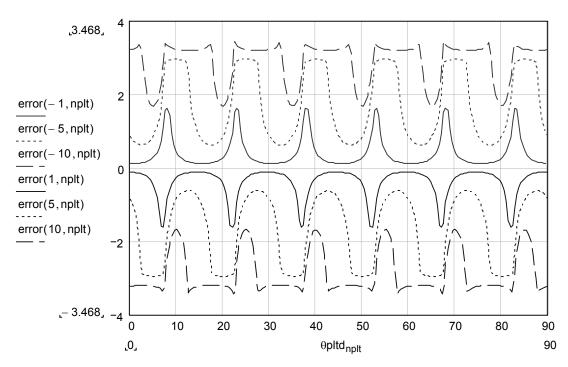

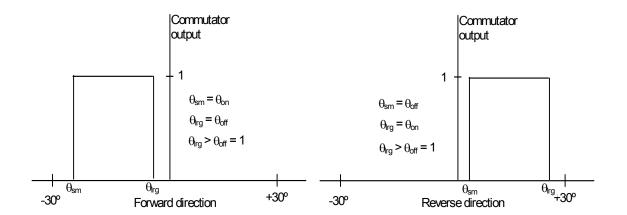

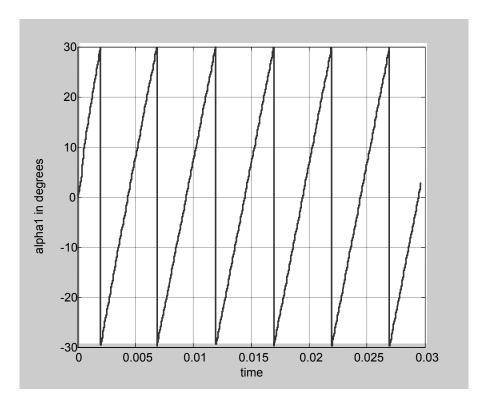

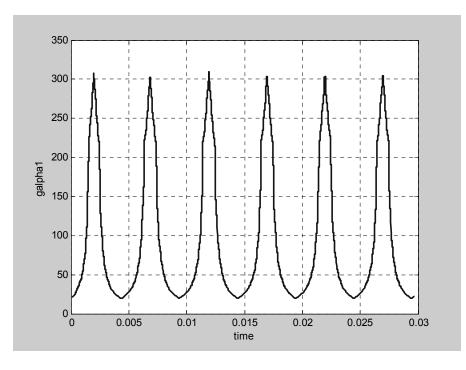

Figure 3.10 shows the alpha profile varying between  $-30^{\circ}$  to  $+30^{\circ}$  and figure 3.11 shows the corresponding g( $\alpha$ ) profile obtained by simulating the block galpha.

Figure 3.10 The rotor position angle profile.

Figure 3.11 The inverse inductance value profile.

Therefore, as seen in these figures, when a rotor pole is in complete alignment with a stator pole i.e.,  $\alpha$  is 0°, the inductance is at its maximum, and therefore the inverse of inductance, g( $\alpha$ ) is minimum. As  $\alpha$  increases from 0° to 30°, inductance decreases thus increasing the value of g( $\alpha$ ) to the maximum value and as  $\alpha$  decreases from 30° to -30°, g( $\alpha$ ) also decreases to the minimum value.

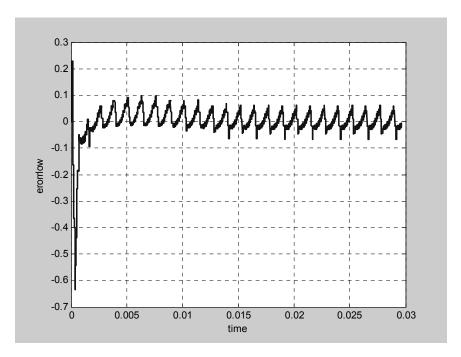

Now, consider the Simulink model of the block for computing the error. Four of the galpha blocks shown in figure 3.9, one for each phase, are instantiated in the error block. The values of  $\alpha$  for each phase are the input to each of these blocks and they compute outputs  $g(\alpha)$  for all four phases. The definition of the error requires all four values of the computed  $g(\alpha)$ s and all four values of the measured  $g(\theta)$ s, one for each phase. If a phase is producing torque there is no measured  $g(\theta)$  from that phase. In this case  $g(\alpha)$  is substituted for  $g(\theta)$ . Depending on the input signal isense, a switch is used to select if  $g(\alpha)$  should be substituted for  $g(\theta)$ . Four switches are used, one for each of the four phases. Then the values of  $g(\alpha)$  and  $g(\theta)$  of all the four phases are connected through multiplier blocks and then are added or subtracted accordingly to calculate the error. The simulation result from the error block for values of  $\alpha$  and  $\theta$  varying as shown in figure 3.10 is given in figure 3.12. As seen in the result, the average error goes to zero as the estimated value of the rotor position ( $\alpha$ ) becomes equal to the actual value of the rotor position ( $\theta$ ). The average value is zero though there are fluctuations.

Figure 3.12 The error calculated for the actual and estimated inverse inductance profile.

Now consider the Simulink model of the rotor position estimator shown in figure 3.8. The sub-block galpha and the error block are instantiated in this main block.

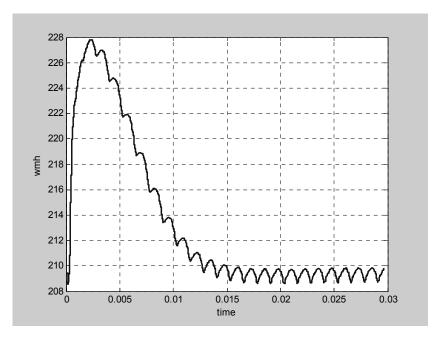

The error calculated by the error block is used as the input to a state estimator to estimate the rotor position. This is done using the equations in chapter 2. The gains in the state estimator are chosen such that the state estimator is stable and its output converges to the correct values rapidly. The error multiplied with a gain factor is given as an input to an integrator whose output is the angular speed of the motor. Figure 3.13 shows the predicted estimated SRM speed using the Simulink model when the actual speed is constant and there is an initial error is the estimated rotor position. From the figure, we observe that the speed reaches its required constant value as the error between the actual and estimated rotor position tends to zero. Figure 3.14 shows the estimated rotor position for the SRM. The estimated angle has been wrapped such that it falls in between  $-30^{\circ}$  and  $+30^{\circ}$ .

Figure 3.13 Estimated rotor speed for the SRM in radian/second (for a constant speed of 2000rpm).

Figure 3.14 Estimated rotor position for the SRM

The next chapter describes the design and implementation of the commutator and position estimator design described in this chapter using an FPGA.

### **CHAPTER 4**

# IMPLEMENTATION OF THE ROTOR POSITION ESTIMATOR ON AN FPGA

### 4.1 Block Diagram of the system

The block diagram of the rotor position estimator and commutator system summarizing the inputs and outputs is as shown in the figure 4.1.

Figure 4.1: Block diagram of the Position Estimator and Commutator

The number of bits required to represent the inputs and outputs are selected to obtain the required accuracy. The width of the inputs and outputs must be determined in order to implement the position estimator and commutator. Each of the inputs and the outputs and their bit representation are discussed in this section.

The input 'qcomain' is a concatenation of the angles  $\theta_{sm}$ ,  $\theta_{lrg}$  and the signal  $\theta_{lrg} > \theta_{sm}$ , which are given as a single input. As discussed earlier  $\theta_{sm}$  and  $\theta_{lrg}$  establish the range of rotor positions within which an SRM phase is to produce torque. Since there are six rotor poles, the angle between the rotor poles is 60°. Thus the values for  $\theta_{sm}$  and  $\theta_{lrg}$  can be anywhere between -30° to +30°. So, a 6-bit number can be used to represent these angles to within approximately 1° since  $2^6 - 1 = 63$ . However, the allowable error is 0.5°, so that it is necessary to choose a 7-bit number to represent the angle. One more bit is required to

represent the sign. Thus, an 8-bit word is used to represent each of  $\theta_{sm}$  and  $\theta_{lrg}$ . Since  $\theta_{lrg}>\theta_{sm}$  is a select signal as described in chapter 3, it is a 1-bit number. Thus, a 17-bit number is required to represent 'qcomain'.

The value of the DC input voltage 'vpower', which is the voltage applied to the motor, is typically 42 volts for the SRM drive system under consideration. The number of bits chosen to represent the value of the voltage is 6 bits since

$2^6 - 1 = 63$ .

Thus assuming the input voltage is always less than 63V, the voltage can be represented to within 1V. The actual rotor position angle is unknown and what is measured is  $g(\theta)$ (gtheta). This signal is measured from the demodulated (low pas filtered) current sense pulses. The analog version of this signal will be scaled to be between 0 and 12V. This analog signal will be converted to digital form before being input to the FPGA. The input 'gthetain' represents the four different  $g(\theta)$  signals, one for each of the four phases. As seen in the Simulink block diagram in Fig. 4.1, 'gthetain is represented by a dark line indicating that it is a bus, consisting of input from all the four phases. The measured  $g(\theta)$ s will be used to compute an error with the calculated  $g(\alpha)$ s. To insure the accuracy of this error calculation which includes multiple multiplies and adds, the number of bits used to represent  $g(\theta)$  in digital form is 9 bits, one bit more than used for the angles.

The input 'isense' is the select signal given as input to the estimator to choose between using  $g(\theta)$  and  $g(\alpha)$  in the error calculation depending on whether the given phase is producing torque. There is one 'isense' select line for each of the four phases. Thus 'isense' is a 4-bit number, with each bit coming from one of the four phases.

The input 'startin' is the select signal given to the commutator and is used to turn the commutator on or off. Thus, it is a 1-bit number.

The output 'wmh' is the estimated angular speed of the motor. For the SRM this position estimator is being designed for the machine inductance and the smallest current values that can be measured while still measuring the largest current values that are required limits the maximum speed the position estimator can operate at 2,500rpm which gives the maximum value of speed to be 262 radian/second. Therefore, the number of bits required

to represent wmh is 10 bits including the sign bit which is required because the speed is negative if the SRM is turning backwards.

Consider the number of bits to represent the estimated rotor position,  $\alpha$ . The rotor position can vary from 0 to 360°. Since there are 6 rotor poles, the angle between each of the poles is 60°. Now considering the position of the rotor pole with respect to the stator pole was defined to vary from -30° to +30°, the number of bits chosen for representing the rotor position should be able to represent 60 values including the sign. Choosing the allowable error for the estimated rotor position to be 0.5°, a 7-bit number is chosen. Since a sign bit is also required, a total of 8 bits is required to represent the estimated rotor position.

## 4.2 Angle wrapping

The fundamental principle of operation of a SRM is the variation in flux linkage with the change in the angular position of the rotor. When a rotor pole pair aligns with the stator pole pair, the flux linked by that stator phase is at a maximum. When the rotor pole pair moves away from the stator pole pair, it becomes unaligned with the stator phase, then the flux linked by the stator phase is at a minimum. Thus, the stator flux goes from maximum to its minimum as each of the six rotor poles pass through the stator poles. The flux profile versus rotor position is as shown in figure 4.2. Since the SRM for which the position estimator is being implemented has four phases and its rotor has six poles, the flux will repeat six times in  $360^{\circ}$  so the angular period is  $360^{\circ}/6 = 60^{\circ}$ .

Figure 4.2: Flux linked by phase A as a function of the rotor position

As seen in the flux profile, the flux changes from unaligned to aligned position when the rotor position changes from  $-30^{\circ}$  to  $0^{\circ}$  and then goes back to unaligned position from  $0^{\circ}$  to  $30^{\circ}$ . Since it repeats after every  $60^{\circ}$ , it is sufficient to consider only the angles from  $-30^{\circ}$  to  $+30^{\circ}$  of rotor rotation.

Since there are four stator phases, angle between them is  $360^{\circ}/4 = 90^{\circ}$ . Hence, the angle between each of the eight stator poles is 45°. Therefore, once the rotor position for one phase has been determined, by shifting the rotor position by multiples of 45°, the rotor position for all the other phases is determined relative to their own stator poles.

The rotor position has the periodicity of the phase flux so that it will repeat every 60° just as the phase flux does. Thus, the rotor position only needs to be estimated for the interval from -30° to +30°. Thus when the rotor position reaches 30° it goes back to -30°. This is known as wrapping the angle at 30°. Assume that  $\theta$  represents the actual angle and  $\alpha$ represents the wrapped angle confined between -30° and +30° Then if  $\theta = 45^{\circ}$ , then  $\alpha = \theta$ -60°=-15°.Similarly, if  $\theta = 150^{\circ}$ , then  $\alpha = \theta$ -120°=30° and so on.

The type of the input and output signals and the number of bits assigned for each of them is summarized in the table 4.1.

|                |              |                            | # of bits used |  |

|----------------|--------------|----------------------------|----------------|--|

| I/O signal     | Туре         | I/O, the signal            | to represent   |  |

| 1/O signai     |              | represents                 | the signal     |  |

|                |              | Turn-on and turn-          |                |  |

|                |              | off angles input to        |                |  |

| qcomain        | input        | all four phases of         | 17             |  |

|                |              | commutator                 |                |  |

| vnower         | Input        | Voltage to the             | 6              |  |

| vpower         | vpower Input |                            | U              |  |

| gthetain Input |              | $g(\theta)$ input from all | 9*4=36         |  |

| guietam        | mput         | four phases                | 7 4-30         |  |

| isense         | Input        | sense select signal        | 1*4=4          |  |

| isclise        | mput         | to estimator               |                |  |

|                |              | Start signal to all        |                |  |

| startin        | Input        | four phases of             | 1              |  |

|                |              | commutator                 |                |  |

|                |              | Output from all            |                |  |

| com            | Output       | four phases of             | 1*4=4          |  |

|                |              | commutator                 |                |  |

| α              | Output       | Estimated rotor            | 8              |  |

| ~~~~           | Output       | position                   | 0              |  |

| wmh            | Output       | Rotor speed                | 10             |  |

|                |              |                            |                |  |

Table 4. 1: The Input and Output signals of the circuit represented in the HDL code

### 4.3 Selection of the programmable device

The different programmable devices that can be used to implement the position estimator are

- 1. Microcontroller

- 2. Digital Signal Processor (DSP)

- 3. Field Programmable Gate Array(FPGA)

While microprocessors have been the dominant devices in use for general-purpose computing for the last decade, there is still a large gap between the computational efficiency of microprocessors and custom silicon. Reconfigurable devices, such as FPGAs, have come closer to closing that gap, offering a 10 times benefit in computational density over microprocessors, and often offering another potential 10 times improvement in yielded functional density on low granularity operations. On highly regular computations, reconfigurable architectures have a clear superiority to traditional processor architectures. On tasks with high functional diversity, microprocessors use silicon more efficiently than reconfigurable devices. Microprocessors are not specifically designed to do calculations in real time.

FPGAs have proven extremely efficient for certain processing tasks. The key to their cost/performance advantage is that conventional processors are often limited by instruction bandwidth and execution restrictions or by an insufficient number or type of functional units. FPGAs exploit more program parallelism. By dedicating significantly less instruction memory per active computing element, they achieve a 10 times improvement in functional density over microprocessors. At the same time this lower memory ratio allows reconfigurable devices to deploy active capacity at a finer grained level, allowing them to realize a higher yield of their raw capacity, sometimes as much as 10 times than conventional processors.

Based on all the factors, the FPGA is expected to be able to perform the position estimation function with a shorter sampling/update time. The position estimator and commutator functions described above have already been implemented by engineers at Mechatronic Systems using a TMS320C6701-150 DSP based commercial DSP board. This implementation resulted in a sampling and position estimate update time that just met the SRM drive-system requirements. Simulink simulations showed that an analog (zero sampling and up date time) implementation of the position estimator resulted in smaller errors compared to the DSP implementation. Thus, the system performance will be improved if the sample and position estimate update time is reduced from what was achieved with the DSP. Thus, the research presented here was undertaken to verify that a FPGA based implementation of the position estimator and commutator would result in a design with a reduced sample and update time compared to the DSP implementation and to quantify the improvement.

### 4.4 Field Programmable Gate Arrays

A Field Programmable Gate Array (FPGA) is a microchip made with millions of programmable logic gates. FPGAs are readily programmable and can be programmed and reprogrammed repeatedly. They must be programmed by users to connect the chip's resources in the appropriate manner to implement the desired functionality.

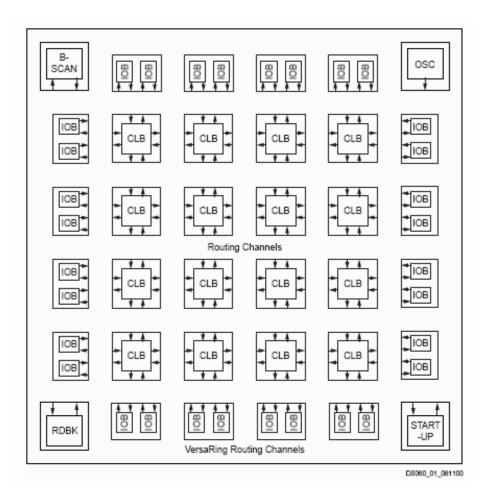

A FPGA contains a regular, extendable, flexible and programmable architecture of logic blocks surrounded by input/output blocks on the perimeter. These functional blocks are linked together by a hierarchy of highly versatile programmable interconnects. The basic block diagram of an FPGA is as shown in the figure 4.3.

Figure 4.3 Block diagram of an FPGA

The basic components of an FPGA are:

- 1. CLBs (Configurable Logic Blocks)

- 2. IOBs (Input/Output Blocks)

- 3. Switch matrix (resources for interconnection)

An FPGA consists of thousands of CLBs. Each CLB consists of a small number of inputs and outputs, a look-up table (LUT), flip-flops and a few basic gates. Multiplexers are used to configure the interconnections between CLB components and the inputs and outputs of the CLB. LUTs are used to implement combinational logic by implementing the truth tables corresponding to the logic circuit. The flip-flops are used as sequential components and can be configured to operate on either edge of the clock or as latches. Thus, a CLB can be configured to implement the combinational and sequential components that have been assigned to it. Loading these configuration bits for each CLB within the FPGA is referred to as the process of programming the FPGA.

The perimeter of configurable Input/Output Blocks (IOBs) provides a programmable interface between the internal logic array and the external device package pins. Each IOB contains a few logic gates and flip-flops. The input and output signals can directly pass to the pin or can be stored in a flip-flop as shown in figure 4.4.

Figure 4.4 Block diagram of a Virtex IOB

Programmable-interconnection resources within the FPGA provide routing paths to connect inputs and outputs of the IOBs and CLBs into logic networks.

The interconnection wires in the FPGA are organized as horizontal and vertical routing channels between rows and columns of logic blocks. At the intersection of the horizontal and vertical wires are switches, which collectively form a switch matrix.

The FPGA user logic functions and interconnections are determined by the configuration program data stored in internal static memory cells.

The factors affecting the selection of the programming device are:

- 1. Number of available IOBs

- 2. Total number of system gates.

#### Number of IOBs

The Input/Output Block (IOB) provides a programmable, bidirectional interface between I/O pin and the FPGA's internal logic.

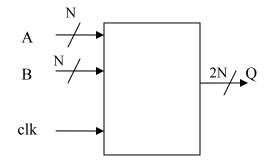

Since the total number of bits required to represent all of the inputs and outputs is 81and each of the bits is assigned to a separate I/O port, the number of independent I/O ports required is 81. This method of transmitting data, where each bit of information is assigned to an individual port is called parallel data transmission.

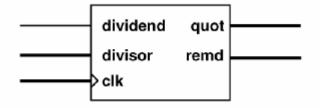

#### Number of system gates

There are many intermediate signals generated, like the signal to represent the error calculated between  $g(\theta)$  and  $g(\alpha)$ , the signals given as input and taken as output from the two integrators. There are many calculations including multiplications and divisions to be done, which require many logic gates.

### 4.5 Type of FPGA

Based on the availability of the required number of IOBs and the number of system gates and multipliers, either of the following devices can be used.

- 1. Virtex XCV800

- 2. Spartan XC3S1000

The datasheets for each of these devices are found in the Xilinx website, the link to which is given in the reference 5 and 6.

The number of available resources in each of the FPGA chips, as given in the data sheets is summarized in the table 4.2.

| Device                | Virtex XCV800 | Spartan XC3S1000 |

|-----------------------|---------------|------------------|

| System gates          | 888,439       | 1M               |

| Total CLBs            | 4704          | 1920             |

| Maximum user I/O      | 240           | 391              |

| Dedicated multipliers | N/A           | 24               |

#### Table 4.2 Comparison of Resources available in Virtex and Spartan

The design is implemented on both these devices to determine which would be a better choice. The implementation results are as shown below.

Implementation results using Virtex XCV800

Release 6.1.03i Par G.26

Copyright (c) 1995-2003 Xilinx, Inc. All rights reserved.

Selected Device: v800hq240-4

| Number of Slices:           | 7844 out of 9408 83%   |

|-----------------------------|------------------------|

| Number of Slice Flip Flops: | 10787 out of 18816 57% |

| Number of 4 input LUTs:     | 7178 out of 18816 38%  |

| Number of bonded IOBs:      | 129 out of 170 75%     |

Number of GCLKs: 1 out of 4 25%

Implementation results using Spartan XC3S1000 Selected Device: 3s1000ft256-4

| Number of Slices:           | 7705 out of 7680 100% (*) |  |  |

|-----------------------------|---------------------------|--|--|

| Number of Slice Flip Flops: | 10769 out of 15360 70%    |  |  |

| Number of 4 input LUTs:     | 7103 out of 15360 46%     |  |  |

| Number of bonded IOBs:      | 92 out of 173 53%         |  |  |

| Number of MULT18X18s:       | 28 out of 24 116% (*)     |  |  |

| Number of GCLKs:            | 3 out of 8 37%            |  |  |

WARNING:Xst:1336 - (\*) More than 100% of Device resources are used

As one can observe the number of slices (logic blocks) used by the Spartan chip is more than what is available and hence the design wouldn't fit onto the Spartan XC3S1000. The number of multipliers available in the Spartan chip is also less than required. Though using the Core generator would reduce the number of multipliers required it would increase the number of logic gates required. Thus, the Spartan XC3S1000 is not a feasible choice. As seen in the implementation result of the Virtex chip, the design will fit onto it while not having excessive resources unused. Hence, the Xilinx Virtex XCV800 is chosen to implement the circuit and test it.

#### 4.6 Xilinx Virtex XCV800

The general characteristics of a FPGA have been discussed in the previous section. The main characteristics of the chosen FPGA, the Xilinx Virtex XCV800 are discussed here.