University of Kentucky UKnowledge

University of Kentucky Master's Theses

**Graduate School**

2004

# FUNCTIONAL ENHANCEMENT AND APPLICATIONS DEVELOPMENT FOR A HYBRID, HETEROGENEOUS SINGLE-CHIP MULTIPROCESSOR ARCHITECTURE

Sridhar Hegde University of Kentucky, hedge@uky.edu

Right click to open a feedback form in a new tab to let us know how this document benefits you.

#### **Recommended Citation**

Hegde, Sridhar, "FUNCTIONAL ENHANCEMENT AND APPLICATIONS DEVELOPMENT FOR A HYBRID, HETEROGENEOUS SINGLE-CHIP MULTIPROCESSOR ARCHITECTURE" (2004). University of Kentucky Master's Theses. 252.

https://uknowledge.uky.edu/gradschool\_theses/252

This Thesis is brought to you for free and open access by the Graduate School at UKnowledge. It has been accepted for inclusion in University of Kentucky Master's Theses by an authorized administrator of UKnowledge. For more information, please contact UKnowledge@lsv.uky.edu.

#### ABSTRACT OF THESIS

#### FUNCTIONAL ENHANCEMENT AND APPLICATIONS DEVELOPMENT FOR A HYBRID, HETEROGENEOUS SINGLE-CHIP MULTIPROCESSOR ARCHITECTURE

Reconfigurable and dynamic computer architecture is an exciting area of research that is rapidly expanding to meet the requirements of compute intense real and non-real time applications in key areas such as cryptography, signal/radar processing and other areas. To meet the demands of such applications, a parallel single-chip heterogeneous Hybrid Data/Command Architecture (HDCA) has been proposed. This single-chip multiprocessor architecture system is reconfigurable at three levels: application, node and processor level. It is currently being developed and experimentally verified via a three phase prototyping process. A first phase prototype with very limited functionality has been developed. This initial prototype was used as a base to make further enhancements to improve functionality and performance resulting in a second phase virtual prototype, which is the subject of this thesis. In the work reported here, major contributions are in further enhancing the functionality of the system by adding additional processors, by making the system reconfigurable at the node level, by enhancing the ability of the system to fork to more than two processes and by designing some more complex real/non-real time applications which make use of and can be used to test and evaluate enhanced and new functionality added to the architecture. A working proof of concept of the architecture is achieved by Hardware Description Language (HDL) based development and use of a Virtual Prototype of the architecture. The Virtual Prototype was used to evaluate the architecture functionality and performance in executing several newly developed example applications. Recommendations are made to further improve the system functionality.

KEYWORDS: Reconfigurable Computing, System on a Chip, Embedded Systems, Multi-Processor System

Sridhar Hegde 12/15/2004

# FUNCTIONAL ENHANCEMENT AND APPLICATIONS DEVELOPMENT FOR A HYBRID HETEROGENEOUS SINGLE-CHIP MULTIPROCESSOR ARCHITECTURE

By

Sridhar Hegde

Dr. J. Robert Heath (Director of Thesis)

Dr. YuMing Zhang (Director of Graduate Studies)

12/15/2004

#### RULES FOR THE USE OF THESES

Unpublished theses submitted for the Master's degree and deposited in the University of Kentucky Library are as a rule open for inspection, but are to be used only with due regard to the rights of the authors. Bibliographical references may be noted, but quotations or summaries of parts may be published only with the permission of the author, and with the usual scholarly acknowledgments.

Extensive copying or publication of the theses in whole or in part also requires the consent of the Dean of the Graduate School of the University of Kentucky.

A library that borrows this thesis for use by its patrons is expected to secure the signature or each user.

Name

Date

THESIS

Sridhar Hegde

The Graduate School University of Kentucky 2004

# DESIGN ENHANCEMENT AND APPLICATIONS DEVELOPMENT FOR A HYBRID, HETEROGENEOUS, SINGLE-CHIP MULTIPROCESSOR ARCHITECTURE

THESIS

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering in the College of Engineering at the University of Kentucky

By

Sridhar Hegde

Lexington, Kentucky

Director: Dr. J. Robert Heath, Associate Professor of Electrical and Computer

Engineering

Lexington, Kentucky

2004

### MASTER'S THESIS RELEASE

I authorize the University of Kentucky Libraries to reproduce this thesis in whole or in part for purposes of research

Signed: \_\_\_\_\_

Date: 12/15/2004

#### ACKNOWLEDGEMENTS

The following thesis, while an individual work, benefited from the insights and direction of several people. First, my Thesis Chair, Dr. J Robert Heath, exemplifies the high quality scholarship to which I aspire. Next, I wish to thank the complete Thesis Committee: Dr. J Robert Heath, Dr. Hank Dietz, and Dr. Bill Dieter. Each individual provided insights that guided and challenged my thinking, substantially improving the finished product. In addition to the technical and instrumental assistance above, I received equally important assistance from family and friends. Finally, I wish to thank the respondents of my study (who remain anonymous for confidentiality purposes). Their comments and insights created an informative and interesting project with opportunities for future work.

| Acknowledgements                                                                | iii   |

|---------------------------------------------------------------------------------|-------|

| List of Tables                                                                  | vi    |

| List of Figures                                                                 | . vii |

| Chapter One : Introduction                                                      |       |

| 1.1 Background                                                                  | 1     |

| 1.2 HDCA Concepts                                                               | 4     |

| 1.3 Goals and Objectives of the Thesis                                          | 6     |

| 1.4 Thesis Summary                                                              | 7     |

| Chapter Two : Background and System Details                                     |       |

| 2.1 HDCA and Related Background Work                                            |       |

| 2.2 PRT Mapper                                                                  |       |

| 2.3 Multi-Function Queue                                                        |       |

| 2.3.1 FIFO Block                                                                |       |

| 2.3.2 Rate Block                                                                |       |

| 2.4 The Computing Elements                                                      |       |

| 2.5 The CE Controller                                                           | . 21  |

| 2.6 Interface Controller                                                        | . 23  |

| 2.7 The Multiplier and the Divider CEs                                          | . 28  |

| Chapter Three : Design Methodology and Modifications                            |       |

| 3.1 Design Methodology                                                          | . 32  |

| 3.1.1 Problem Definition                                                        |       |

| 3.1.2 Requirements definition                                                   |       |

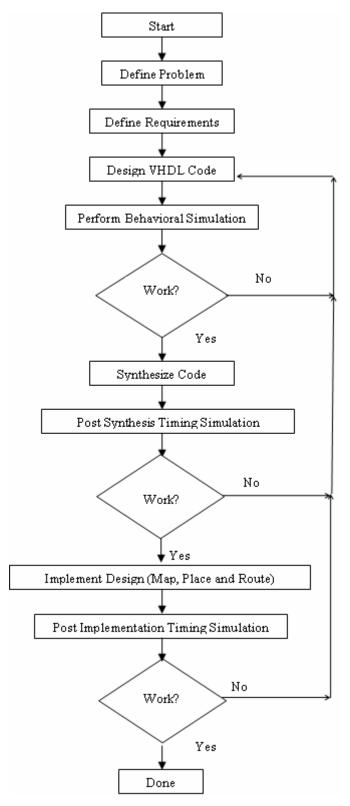

| 3.2 Design Flow Approach                                                        |       |

| 3.3 Modifications to the First Phase Prototype                                  |       |

| 3.3.1 PE Controller                                                             |       |

| 3.3.2 Interface Controller                                                      |       |

| 3.3.3 Crossbar Interconnect Network                                             |       |

| 3.3.4 Input Rom for the Data                                                    |       |

| 3.3.5 Multiplier CE                                                             |       |

| 3.3.6 Dynamic Load Balancing Circuit                                            |       |

| 3.3.7 Memory-Register Computer Architecture CEs                                 |       |

| 3.4 Second Version (Phase) HDCA System                                          | . 46  |

| Chapter Four : Virtual Prototype Development                                    |       |

| 4.1 The Virtual Prototype                                                       |       |

| 4.3 FPGA Based Chip Resource Utilization Reports                                |       |

| 4.3.1 Device Utilization report for the Multiple Forking Application            |       |

| 4.3.2 The Delay and Timing Summary Report – Application One                     |       |

| 4.3.3 Device Utilization Report for Un-pipelined Integer Manipulation Algorithm |       |

| 4.3.4 Delay and Timing Summary Report – Application Two                         |       |

| 4.4 Timing Constraints Definition for Post Implementation Simulation            | . 53  |

| <b>Chapter Five : Functional Enhancements to the HDCA</b>                       |       |

| 5.1 Dynamic Node Level Reconfigurability                                        |       |

| 5.1.1 Introduction and Concept                                                  | . 54  |

### TABLE OF CONTENTS

| 5.1.2 Assignment Policy and Implementation                                     |

|--------------------------------------------------------------------------------|

| 5.2 Multiple Forking                                                           |

| 5.2.1 Introduction and Concept                                                 |

| 5.2.2 Implementation                                                           |

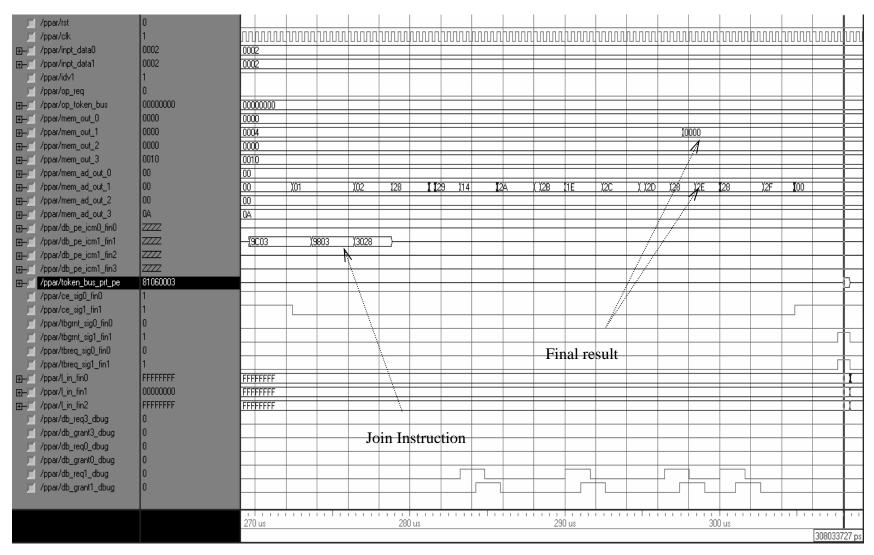

| 5.2.3 Post Place n Route Simulation Validation of an Application with Multiple |

| Forking                                                                        |

| Chapter Six : Example Applications Development, Testing and Evaluation for     |

| Enhanced Fully Functional HDCA                                                 |

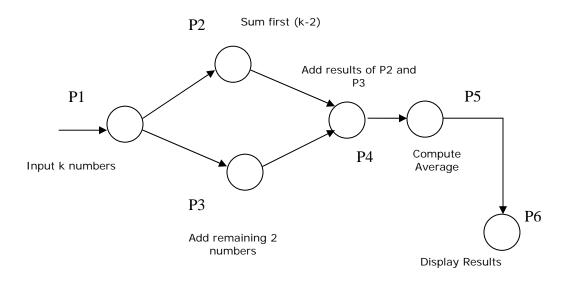

| 6.1 Application One: Acyclic Integer Averaging Algorithm77                     |

| 6.2 Acyclic Application Two – 2x 2 Matrix Multiplication Algorithm             |

| 6.3 Acyclic Application 3 – 3x3 by 3x2 matrix multiplication algorithm with    |

| performance evaluation and gate count comparisons 104                          |

| 6.4 Application Four – Acyclic Pipelined integer manipulation algorithm 129    |

| 6.5 Complex Non-Deterministic Cyclic Value Swap Application                    |

| Chapter Seven : Conclusions and Recommendations                                |

| 7.0 Conclusion                                                                 |

| 7.1 Recommendations                                                            |

| <b>Appendix A</b>                                                              |

| <b>Appendix B</b>                                                              |

| References                                                                     |

| Vita                                                                           |

### LIST OF TABLES

| Table 2.1, Instruction Set of the Memory-Register CEs         | 19 |

|---------------------------------------------------------------|----|

| Table 2.2, Token Formats Available for the HDCA System        |    |

| Table 2.3, Physical Addresses of the Modules in the Prototype |    |

| Table 3.1, New Token Format for the Command Token of the HDCA |    |

| Table 4.1, Device Utilization Summary for Application One     |    |

| Table 4.2, Device Utilization Summary for Application Two     |    |

### LIST OF FIGURES

| Figure 1.1 : High Level Architecture of the DPCA                                          | 3 |

|-------------------------------------------------------------------------------------------|---|

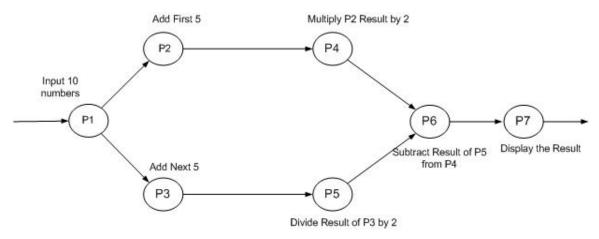

| Figure 1.2 : Process Flow Graph for a Typical Application                                 | 7 |

| Figure 2.1a : A High Level Diagram of the original HDCA 10                                | 0 |

| Figure 2.1b : Basic Process Flow Graph Structures                                         | 1 |

| Figure 2.2 : Example Process Flow Graph 12                                                | 2 |

| Figure 2.3 : Token Format for the HDCA 12                                                 | 2 |

| Figure 2.4 : Process Request Token mapper Circuit Diagram                                 | 4 |

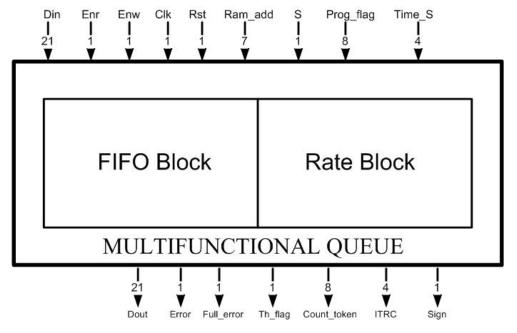

| Figure 2.5 : Multifunctional Queue                                                        |   |

| Figure 2.6 : FIFO Block Functional Diagram                                                | 6 |

| Figure 2.7 : Rate Block Functional Diagram                                                | 7 |

| Figure 2.8 : Memory Register Computer Architecture - CE0 and CE1 20                       | 0 |

| Figure 2.9 : CE controller for 16-bit unpipelined Memory Register CEs 21                  |   |

| Figure 2.10 : Explanation of Hold and Join Concept                                        | 2 |

| Figure 2.11 : Interface Controller State Machine for the CE                               | 3 |

| Figure 2.12 : Divider CE. To be CE2 in the Latest Version HDCA                            | 8 |

| Figure 2.14 : Multiplier CE used in the HDCA                                              |   |

| Figure 3.1 : Design Methodology for the HDCA System                                       |   |

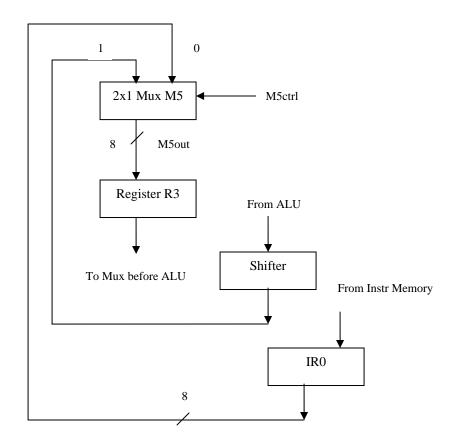

| Figure 3.3 : Changes to the PE Controller Showing the Additional Multiplexer M5 39        |   |

| Figure 3.4 : Control Logic for the Interface Controller Module                            |   |

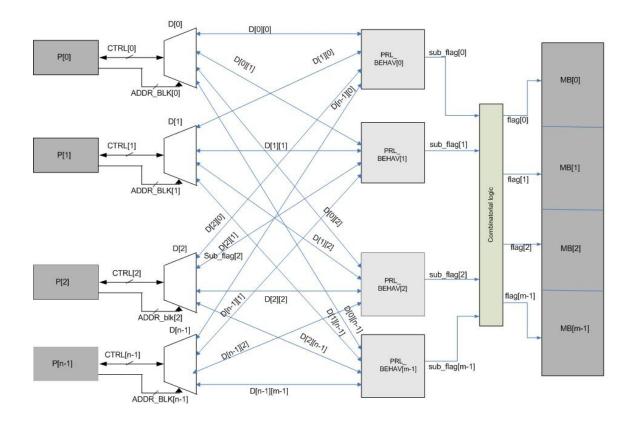

| Figure 3.5 : Crossbar Interconnect Network for the Revised HDCA                           |   |

| Figure 3.6 : Simple Application 1 for the HDCA system                                     |   |

| Figure 3.7 : Modified Memory Register Computer Architecture as it exists now              |   |

| Figure 3.8 : An Enlarged Figure of the CE Controller Showing all its Functional Units. 46 |   |

| Figure 3.9 : Block Diagram of the Second Phase HDCA System                                |   |

| Figure 4.1 : Timing constraints for Post Implementation Simulation                        |   |

| Figure 5.1a : Dynamic Node Level Re-configurability                                       |   |

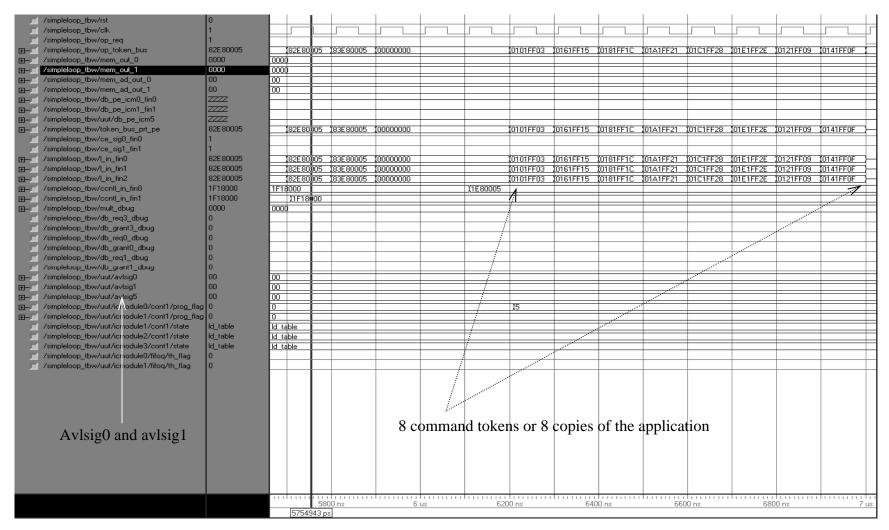

| Figure 5.1 : Two Threshold Tokens and Eight Command Tokens being input into the           |   |

| System                                                                                    | 7 |

| Figure 5.2 : Process 1 Executed for the 4 Command Tokens and "Prog_Flag" being set 60     | 0 |

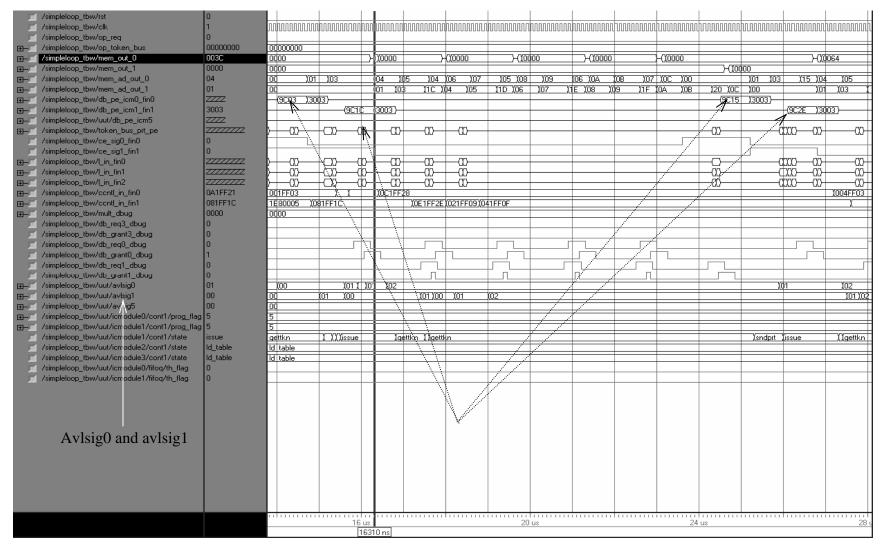

| Figure 5.3 : Threshold Flag Set for CE1 and Queue Depth Increasing for CE1                | 1 |

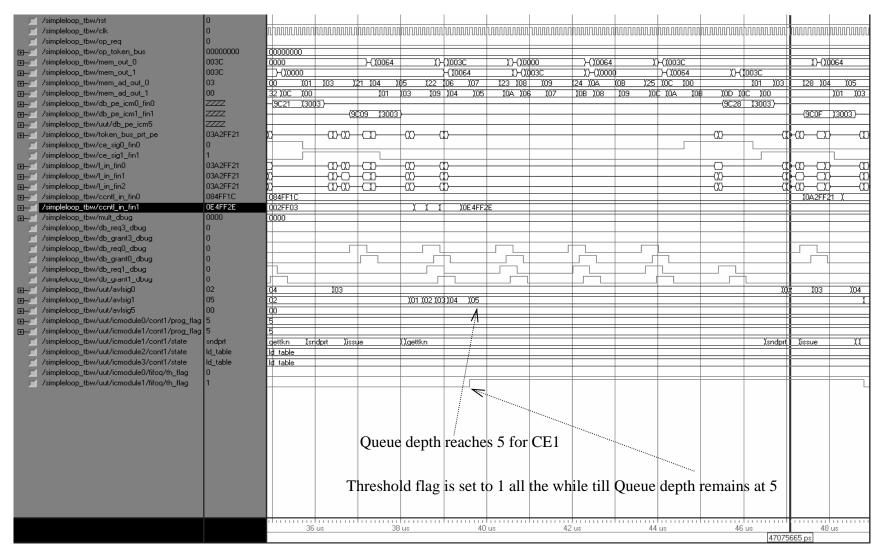

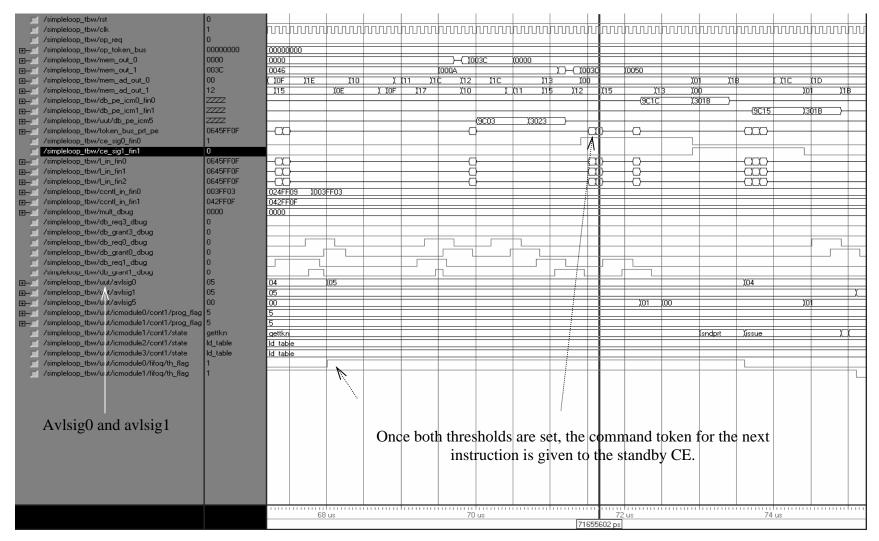

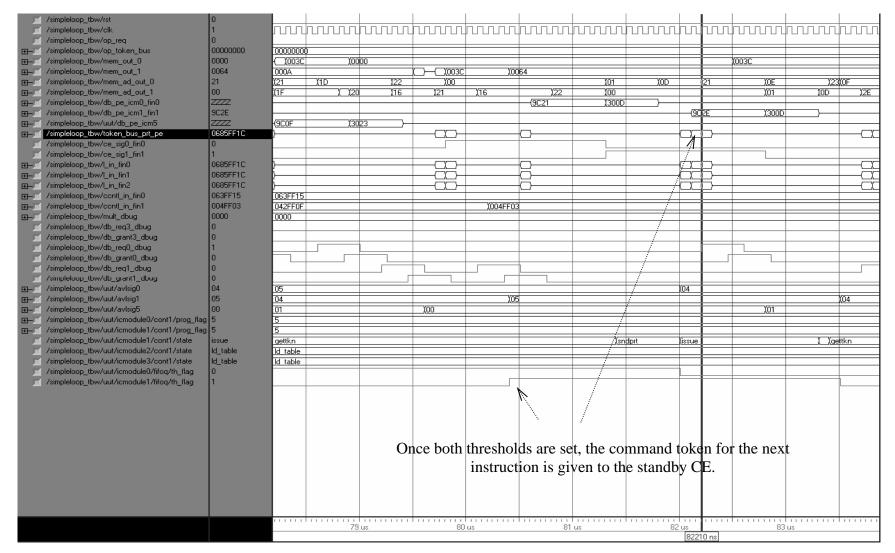

| Figure 5.4 : Both Thresholds set and Standby CE Reconfiguring                             |   |

| Figure 5.5 : Standby CE Kicking in to take in the Additional Load on the System 64        | 4 |

| Figure 5.6 (a), (b) and (c) : Different Flow Graph Topologies                             |   |

| Figure 5.7 : Application Flow Graph for Multiple Forking                                  |   |

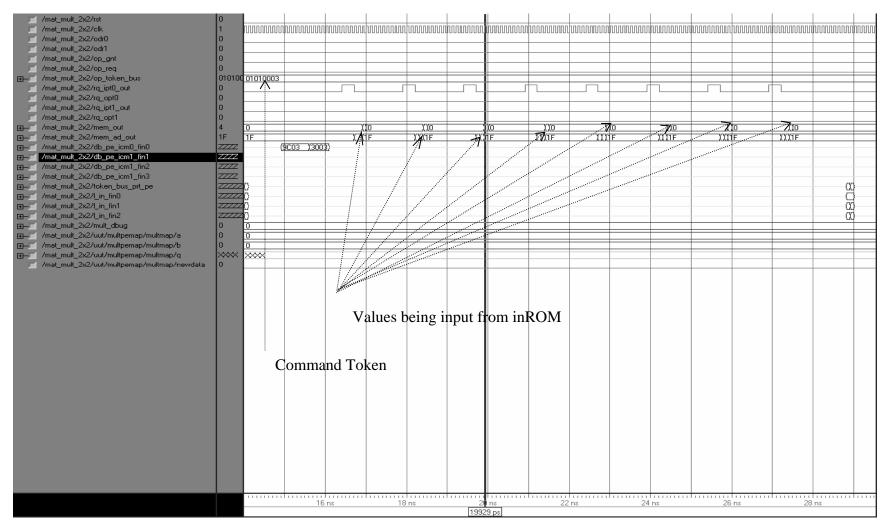

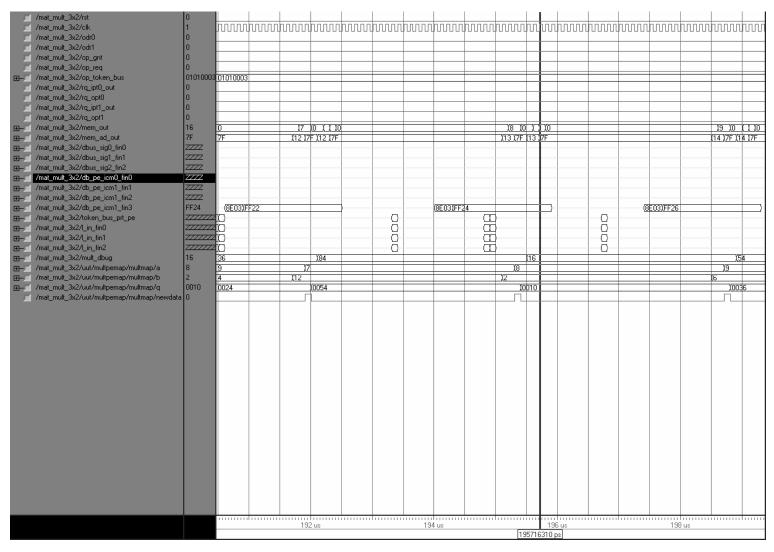

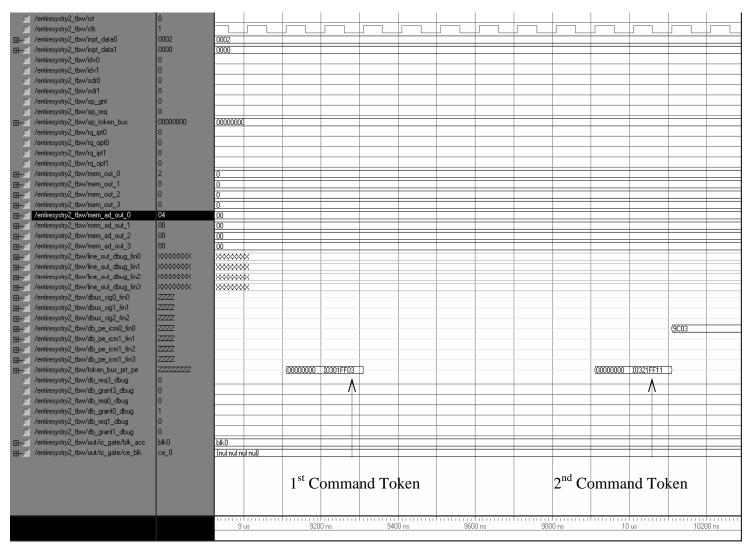

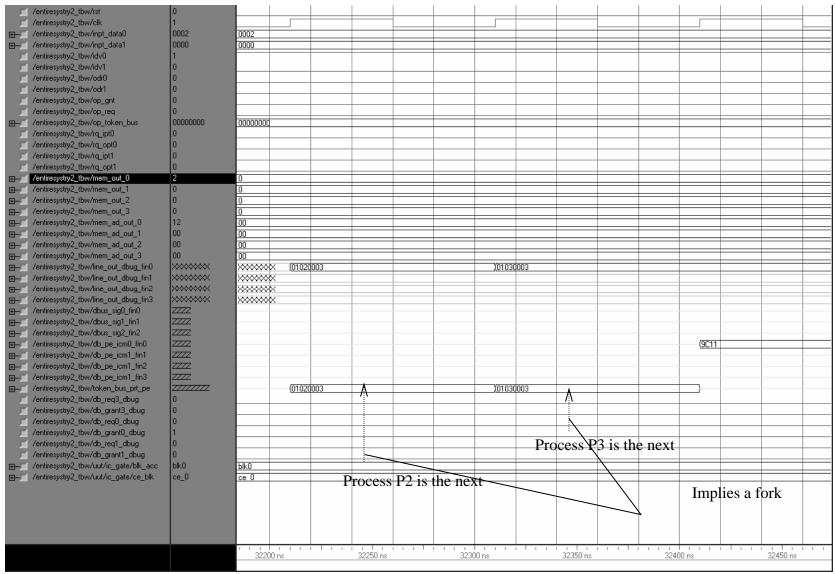

| Figure 5.8 : One Command Token of x"01010003" for the Multiple Fork Application 69        |   |

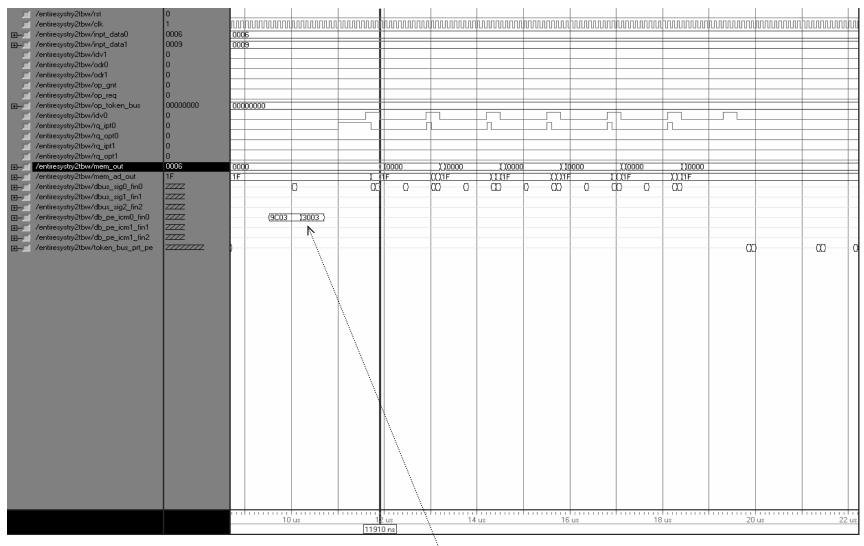

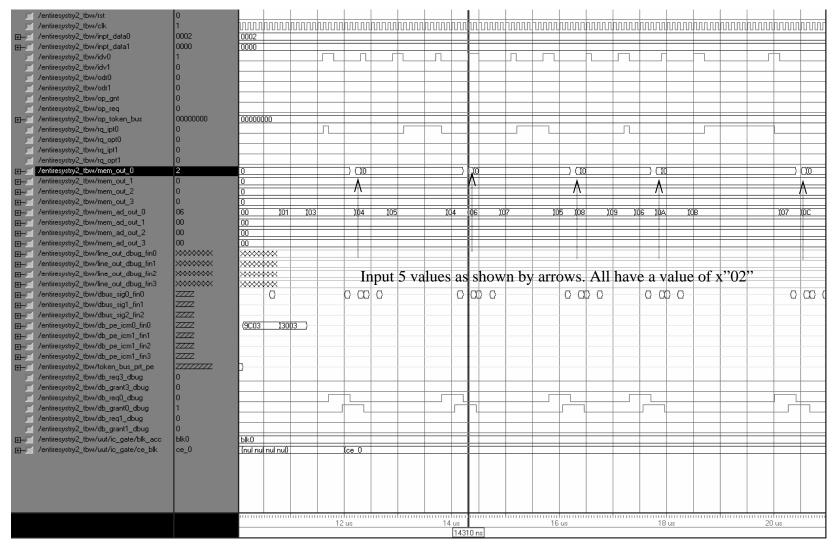

| Figure 5.9 : Values of x"02" being Input into the System                                  |   |

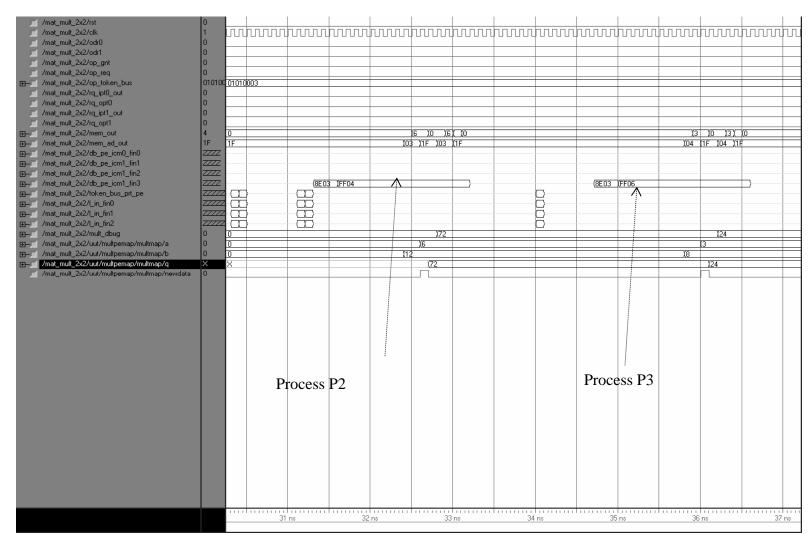

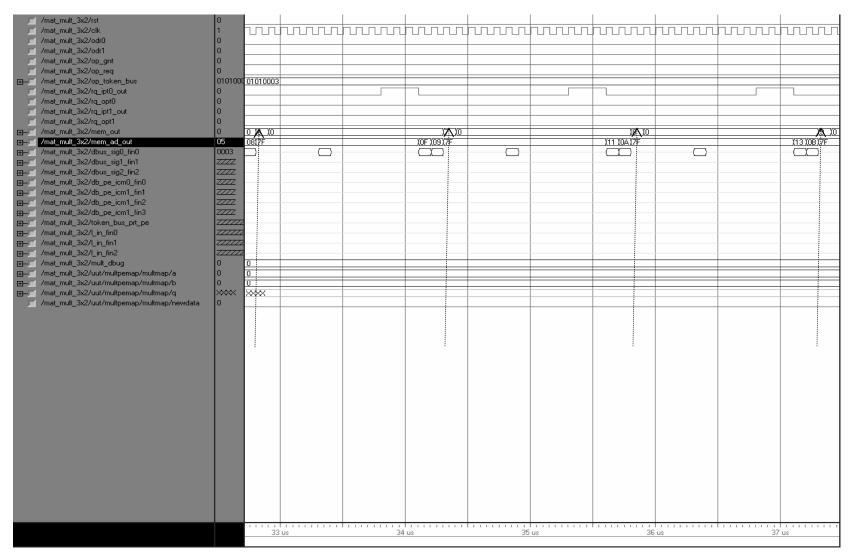

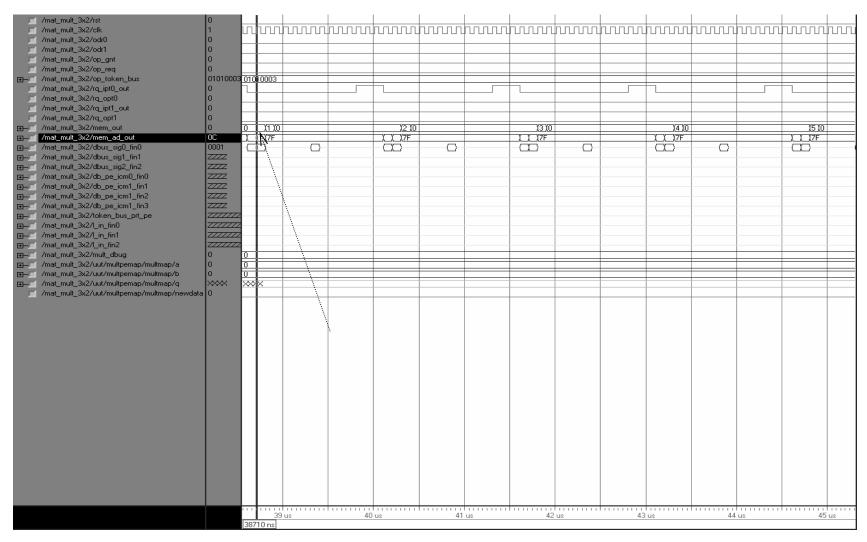

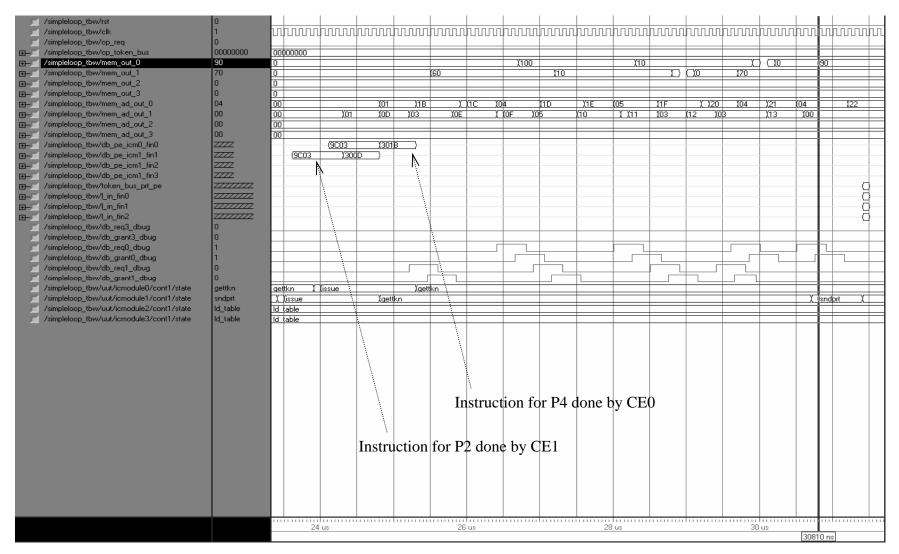

| Figure 5.10 : Token for P3 Issued and P2 Completes Execution                              |   |

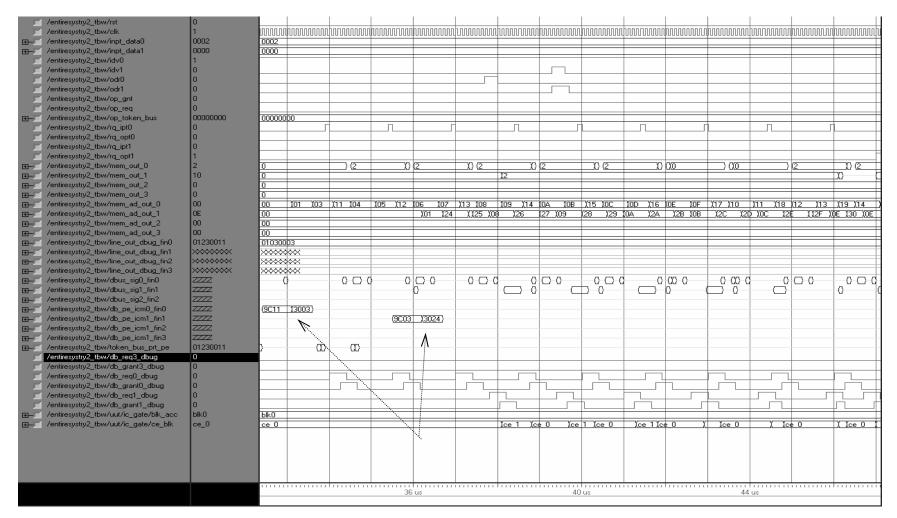

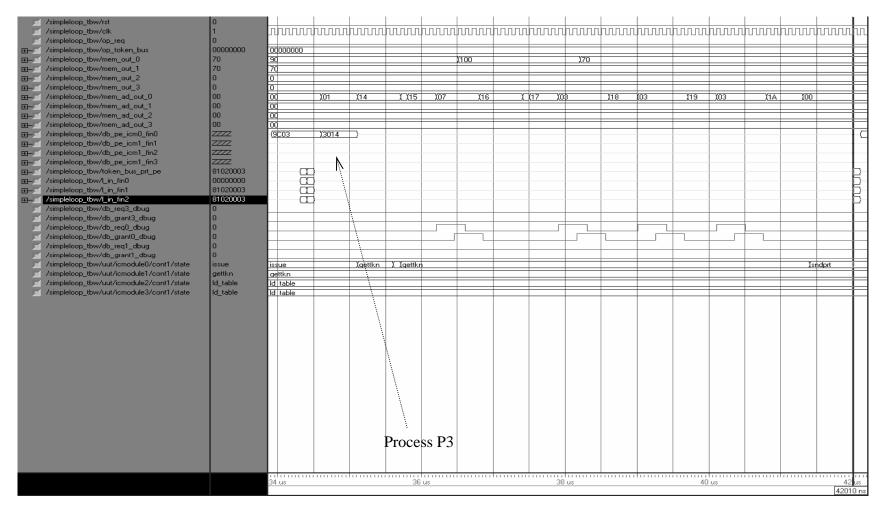

| Figure 5.11 : The Dummy Process P3 and the Instruction for Multiplication                 |   |

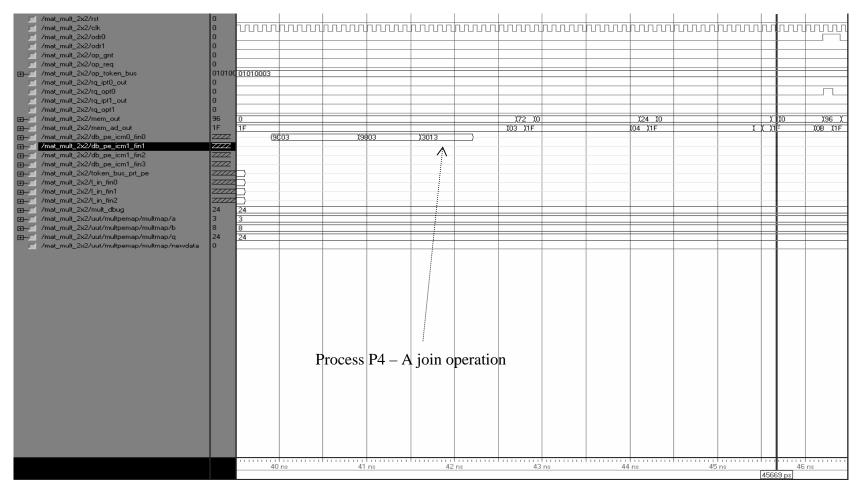

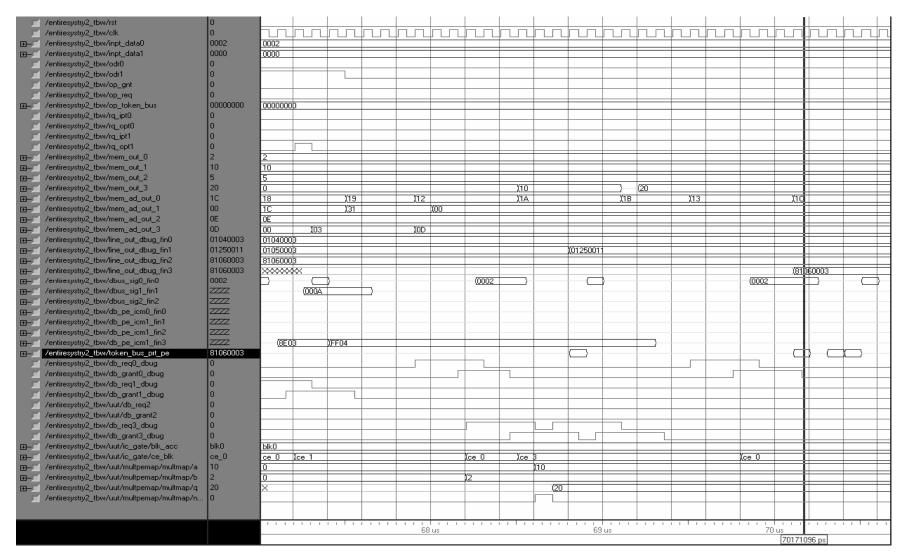

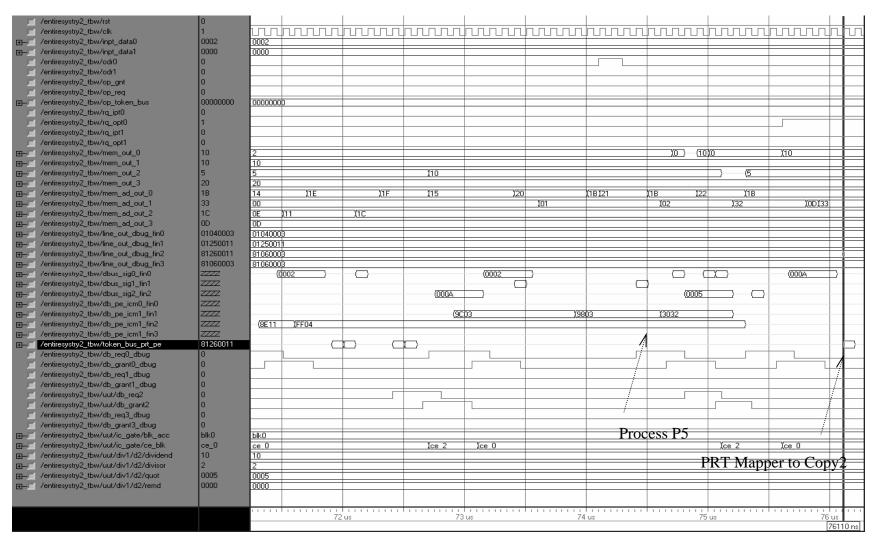

| Figure 5.12 : Process P4 and P5 Successfully Executing                                    | 3 |

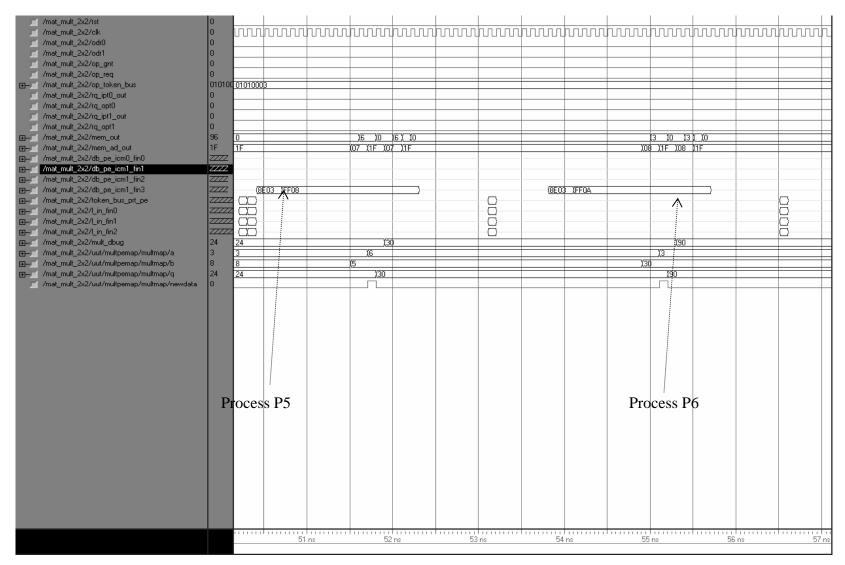

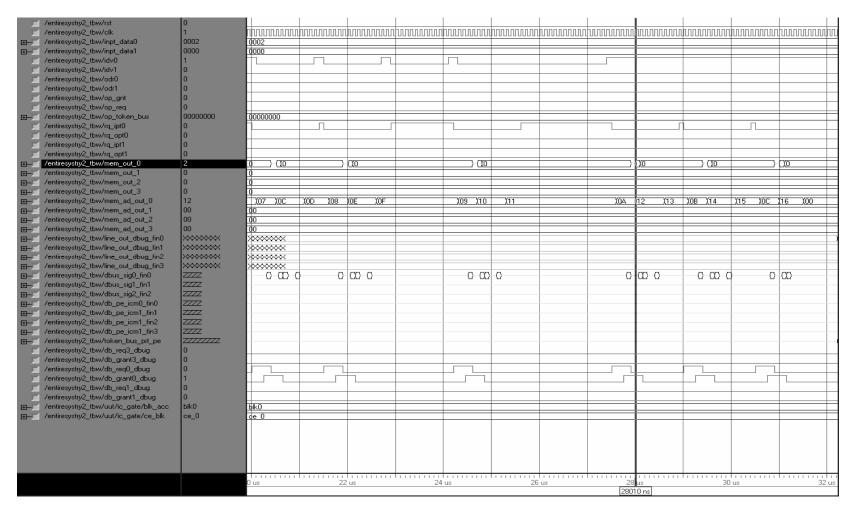

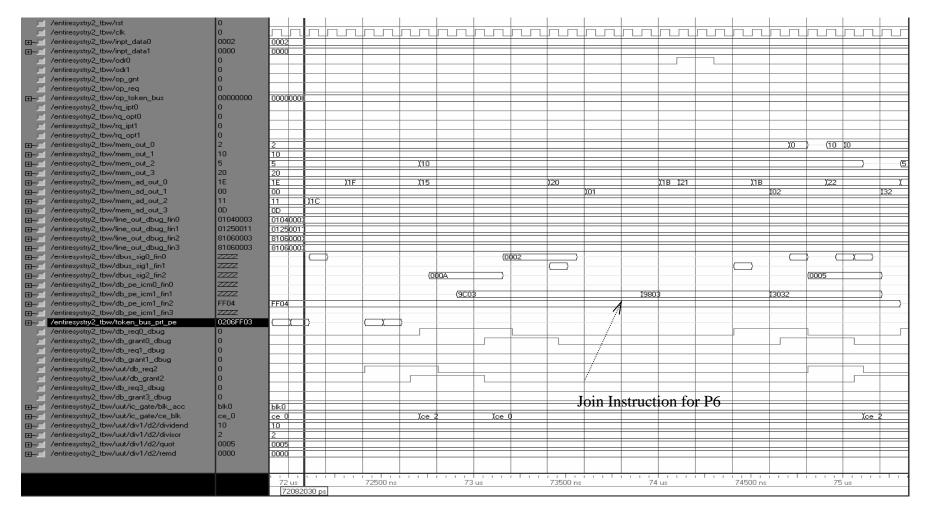

| Figure 5.13 : Join Operation - Subtraction is Performed Leading to x"0000" at x"2E" 74    | 4 |

| Figure 5.14 : Final Result is Displayed at the Proper Location                            |   |

| Figure 6.1 : Integer Averaging Algorithm                                                  |   |

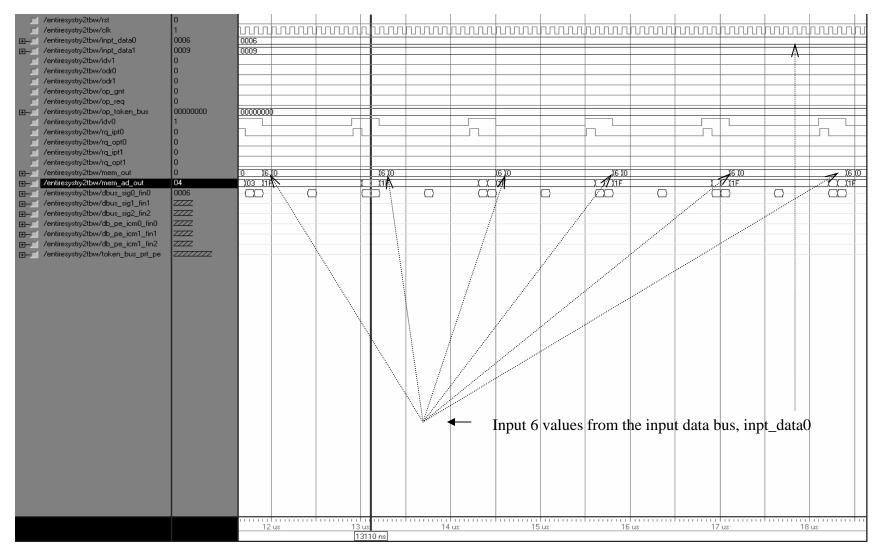

| Figure 6.2 : Process P1 being done by CE0                                                 |   |

| Figure 6.3 : Input Values Stored at Consecutive Locations                                 | 1 |

| Figure 6.4 : P2 and P3 being Done Simultaneously by CE0 and CE1                            | 82    |

|--------------------------------------------------------------------------------------------|-------|

| Figure 6.5 : Join Operation of P2 and P3 to P4 being done by CE0                           | 83    |

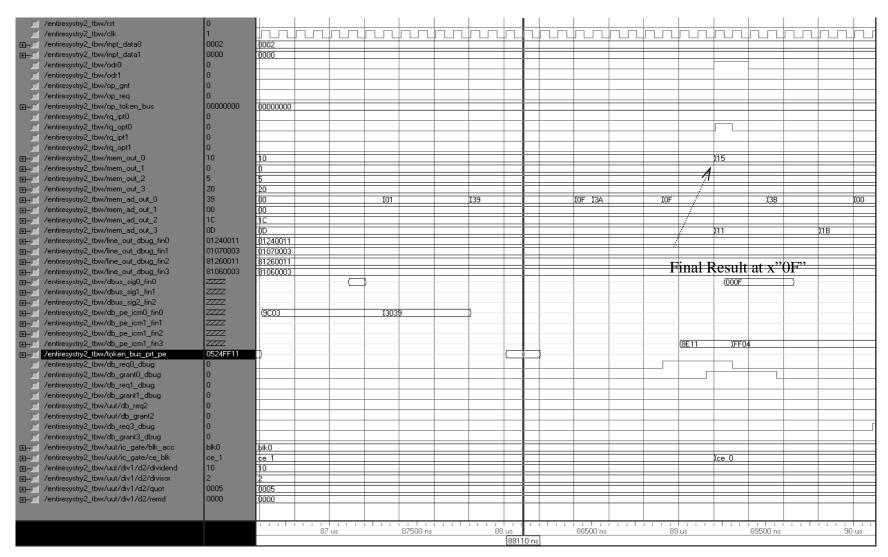

| Figure 6.6 : Average of the k Numbers being Computed by the Divider CE                     | 84    |

| Figure 6.7 : Final Result of Algorithm being Displayed in Process P6 by CE0                |       |

| Figure 6.8 : Matrix Multiplication Operation for Application two                           |       |

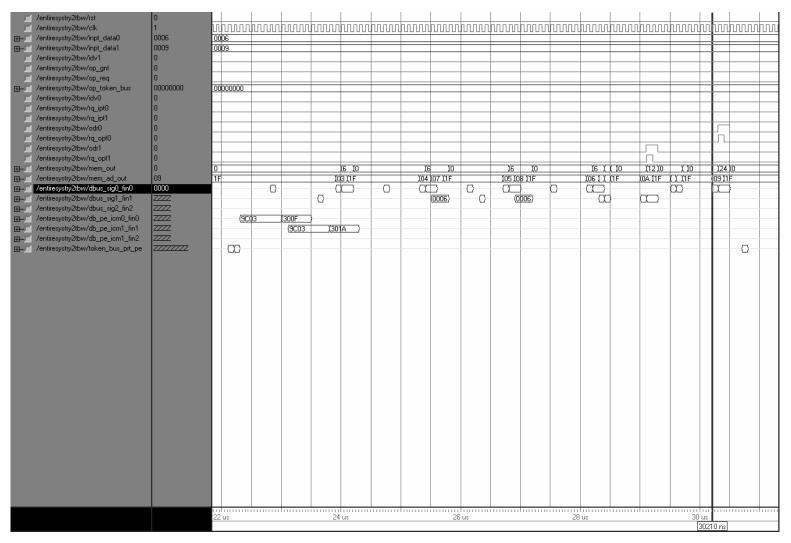

| Figure 6.10 : 2 sets of the First Four Values in Matrix A are Inputs into the System.      |       |

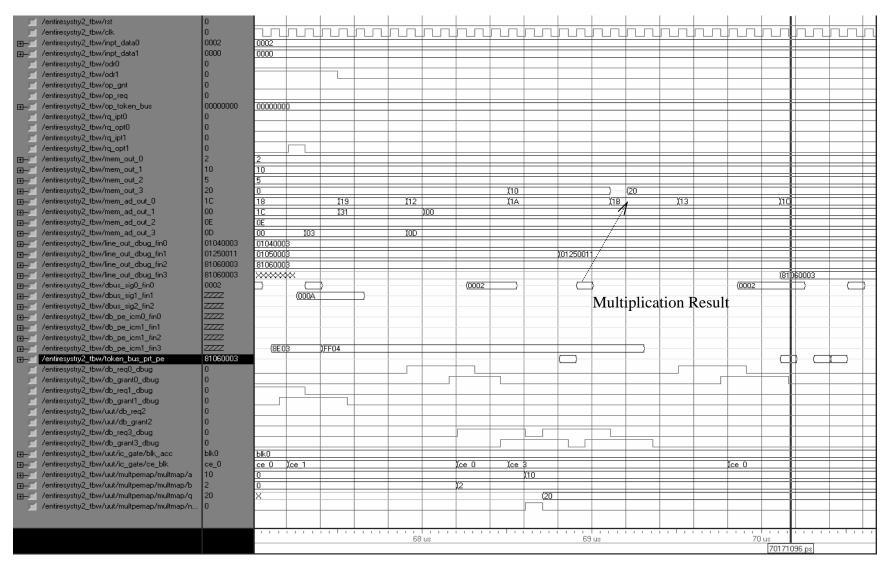

| Figure 6.11 : Process P2 and P3 being done by CE0 and their Results being Stored           |       |

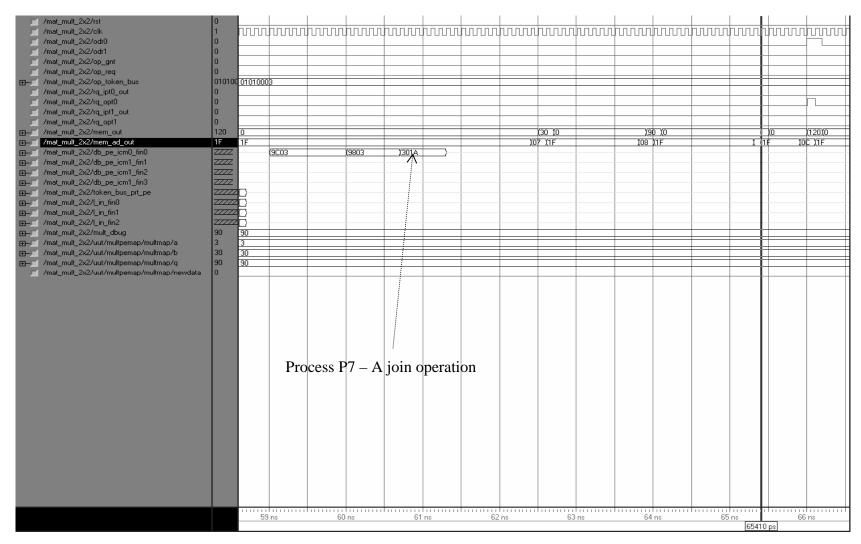

| Figure 6.12 – Process P4 executed by CE0                                                   |       |

| Figure 6.13 : Processes P5 and P6 executed by CE0 and their Results                        |       |

| Figure 6.14 – Process P7 being executed by CE0 and the Results Being Displayed             |       |

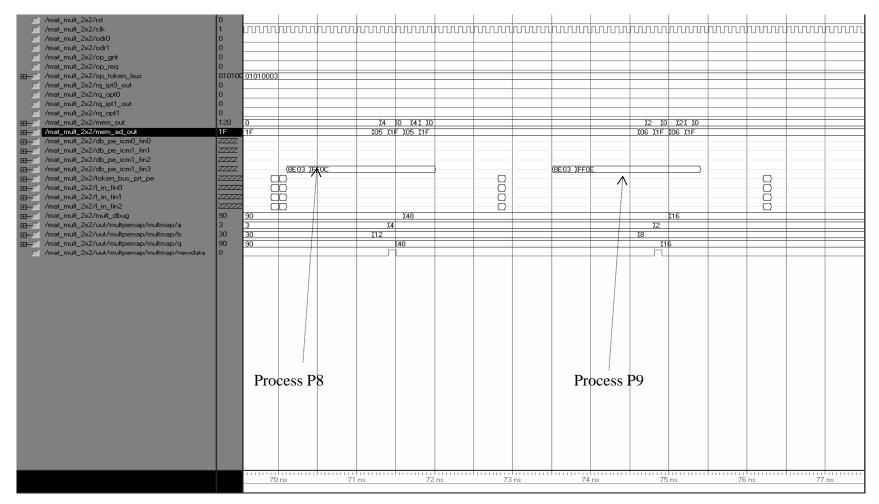

| Figure 6.15 : Processes P8 and P9 being Executed by CE0                                    |       |

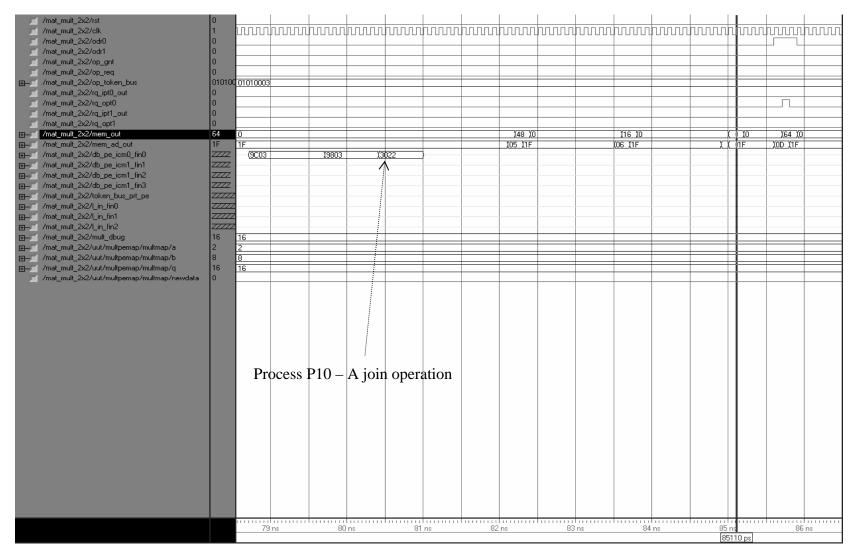

| Figure 6.16 : Process P10 being Done by CE0. It Computes Component $C_{21}$                |       |

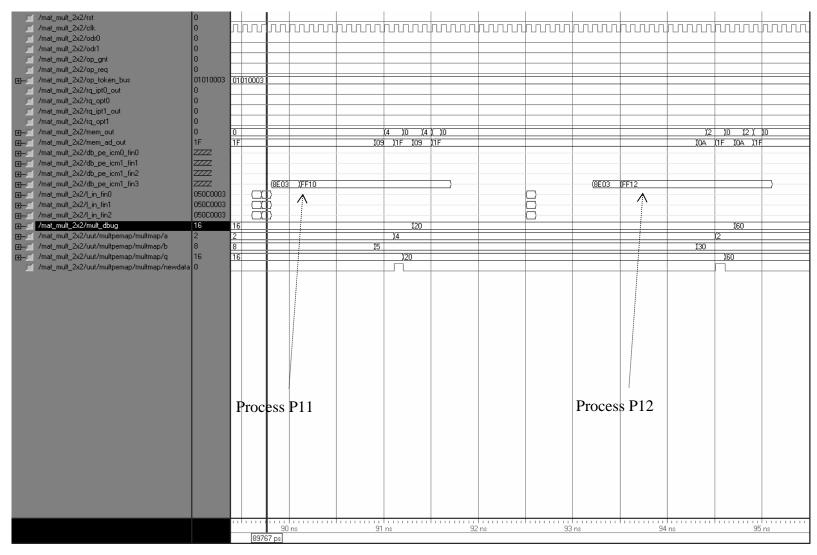

| Figure 6.17 : Processes P11 and P12 done by CE0                                            |       |

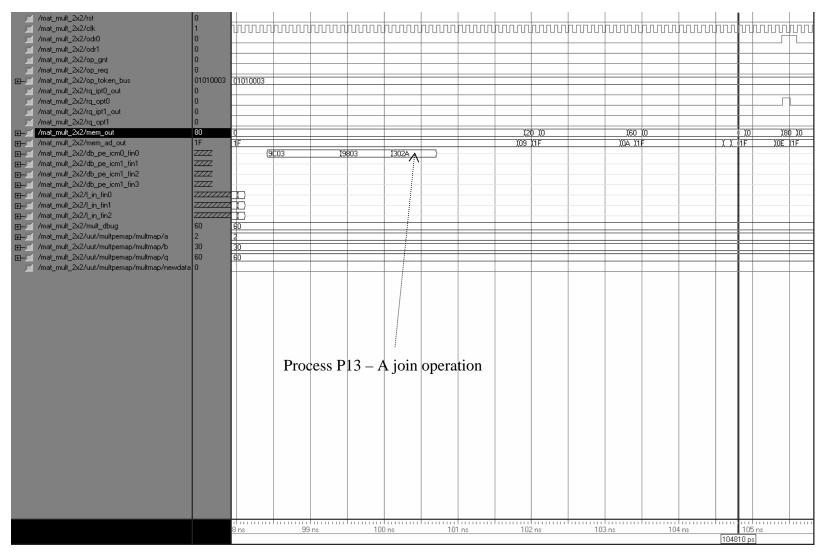

| Figure 6.18 : Process P13 Computing the Last Component C <sub>22</sub>                     |       |

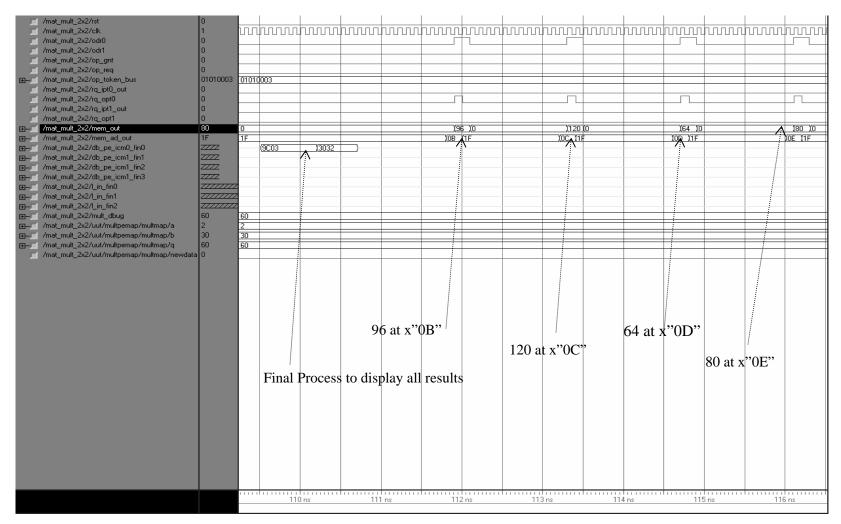

| Figure 6.19 : All Results with their Data Locations in the Shared Data Memory              |       |

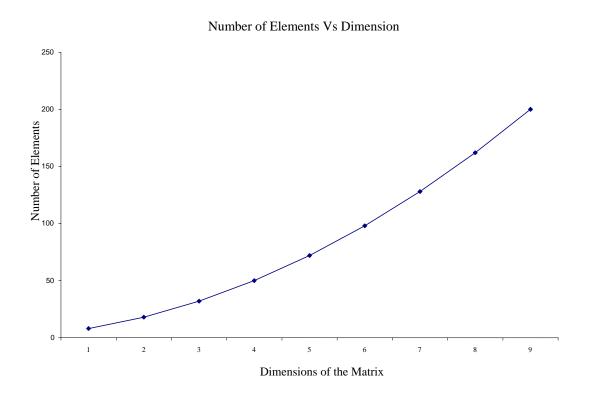

| Figure 6.20 : Number of Elements in the Data Rom vs. Dimensions of Input matrix            |       |

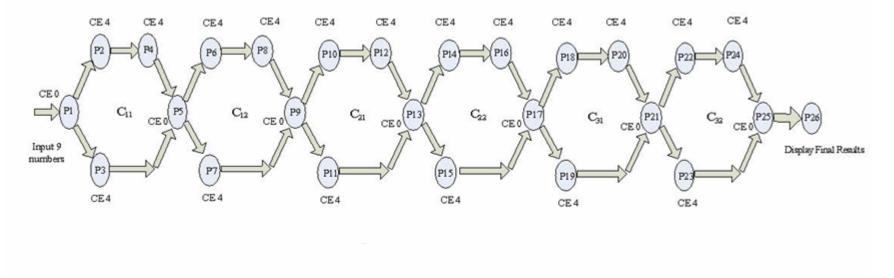

| Figure 6.21 : Process Flow Graph for Asymmetric Matrix Multiplication of Applica           |       |

|                                                                                            |       |

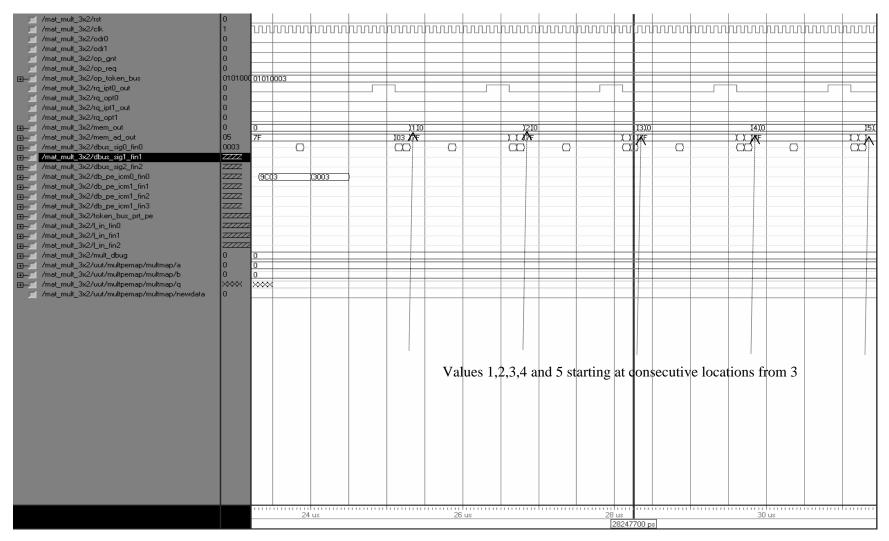

| Figure 6.22 : First 5 Values of the Matrix A being Input Through the Data ROM              |       |

| Figure 6.23 : Last Four Values of the First Set of Data Stored at Locations Ending a       |       |

| "09"hex                                                                                    |       |

| Figure 6.24 – Second set of Data for Matrix A, Starting at "OC" hex                        | 111   |

| Figure 6.25 : Last 4 Data Values for Second Set of Matrix A, Ending at "14" hex            |       |

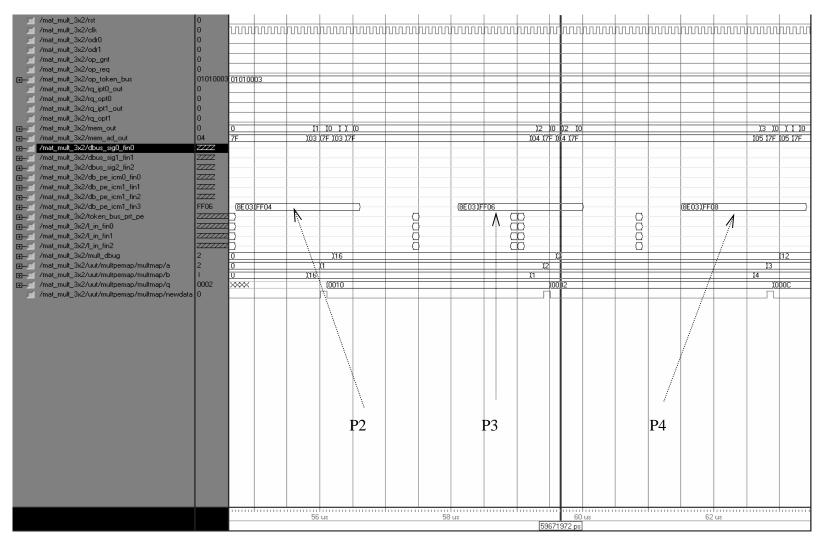

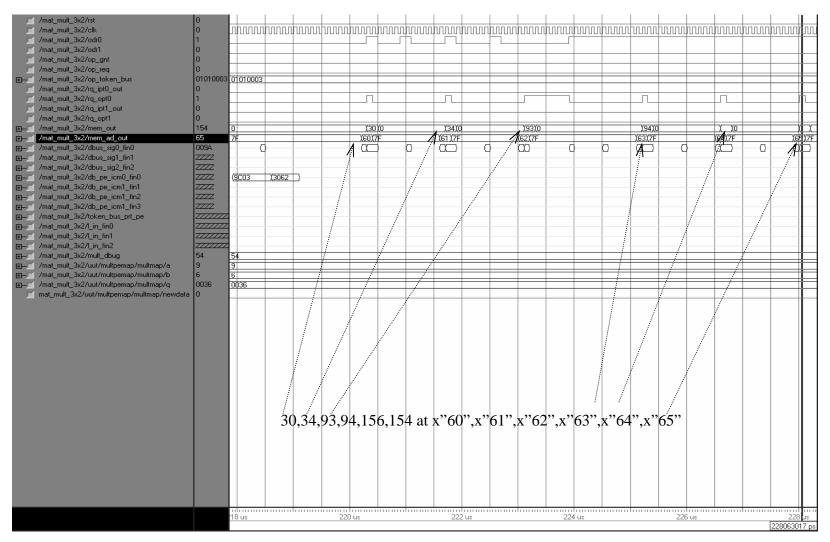

| Figure 6.26 : P2, P3 and P4 with Results, "16", "2" and "12" Unsigned on "mult_db          |       |

|                                                                                            |       |

| Figure 6.27: P5 Being Done to Calculate C <sub>11</sub>                                    | 114   |

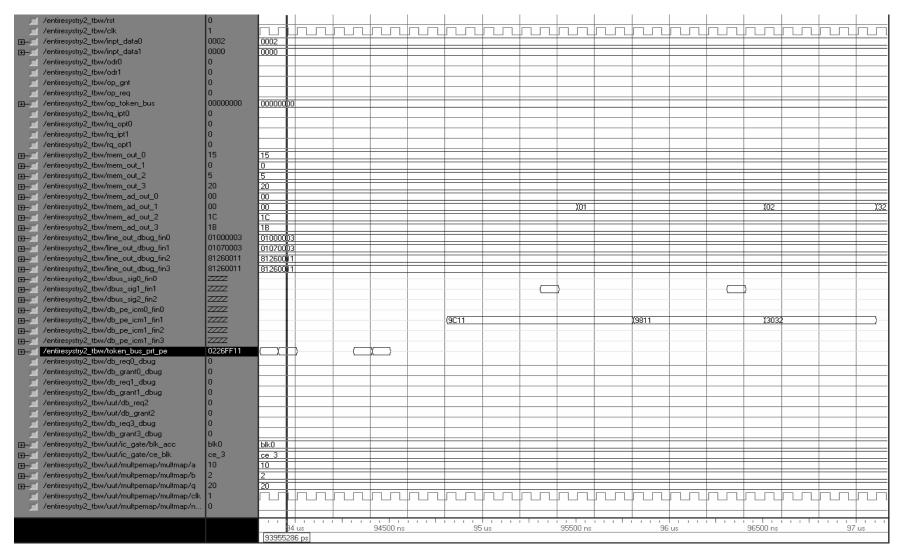

| Figure 6.28 : Processes P6, P7 and P8 being executed by CE 0                               |       |

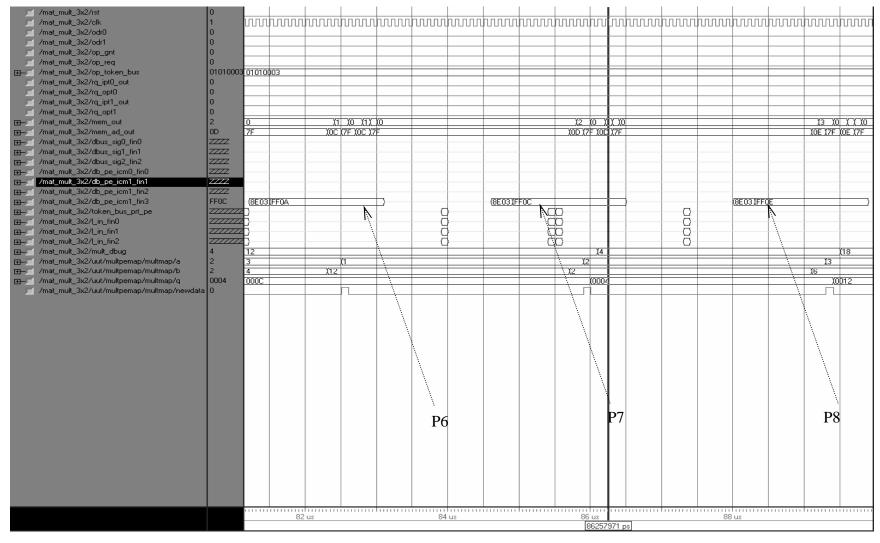

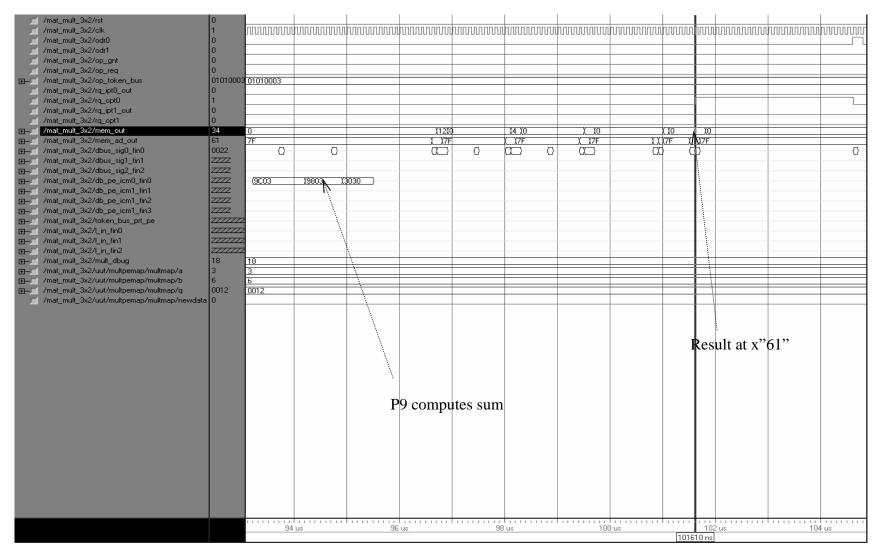

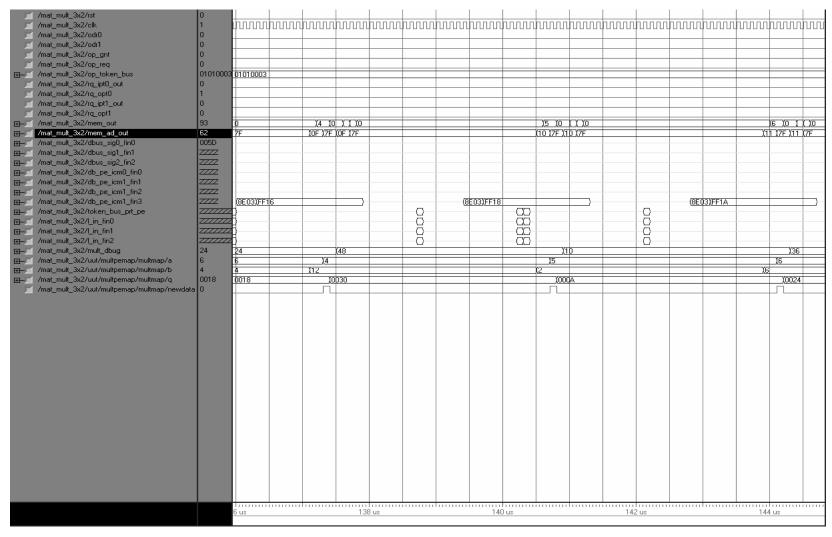

| Figure 6.29 : P9 Computes Sum of Products C12 stored at "61" hex in Data Memory            | 117   |

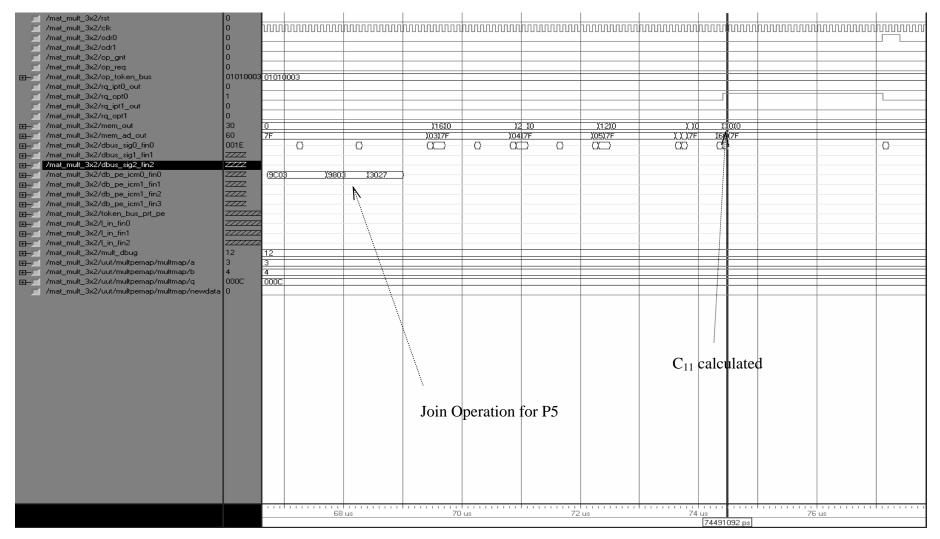

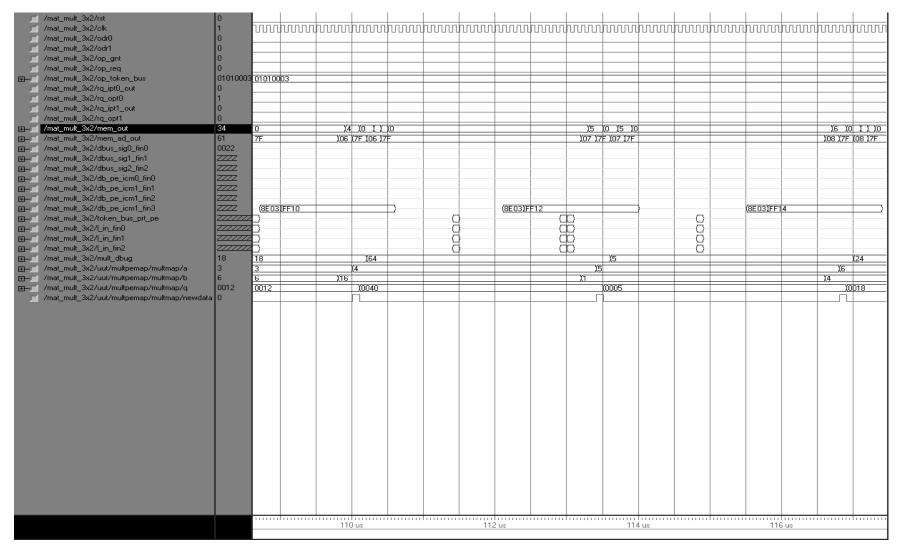

| Figure 6.30 : Process P10, P11 and P12 – Multiplications being Done                        | 118   |

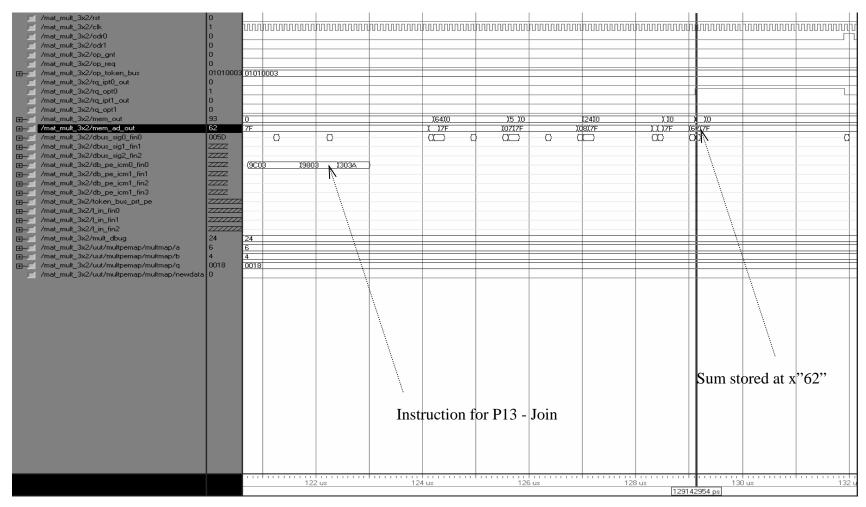

| Figure 6.31 –Process P13 Computes C <sub>21</sub> Stored at "62"hex finally in Shared Data |       |

| Memory                                                                                     | 119   |

| Figure 6.32 – Processes P14, P15 and P16 Computing Products                                | 120   |

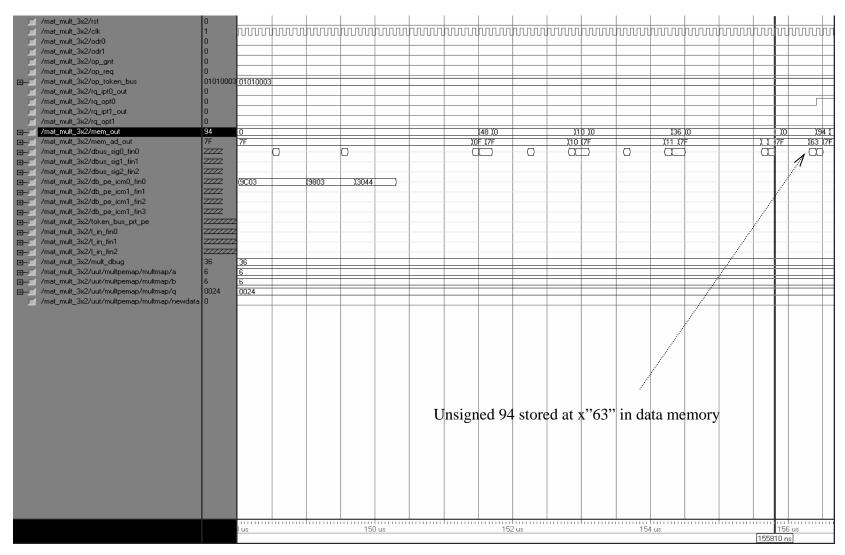

| Figure 6.33 : Process P17 Calculates $C_{22}$ Stored at "63" hex Finally in Shared Data    |       |

| Memory                                                                                     |       |

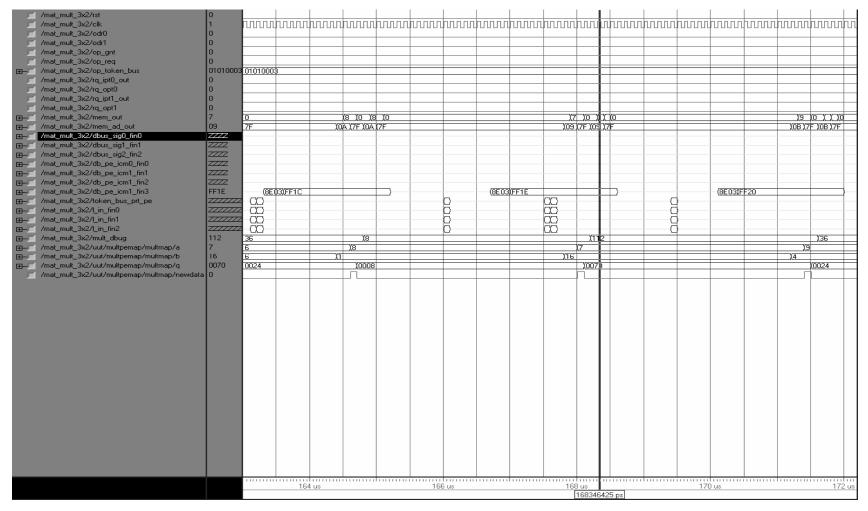

| Figure 6.34 : Processes P18, P19 and P20 are Done by the Multiplier CE 4                   | 122   |

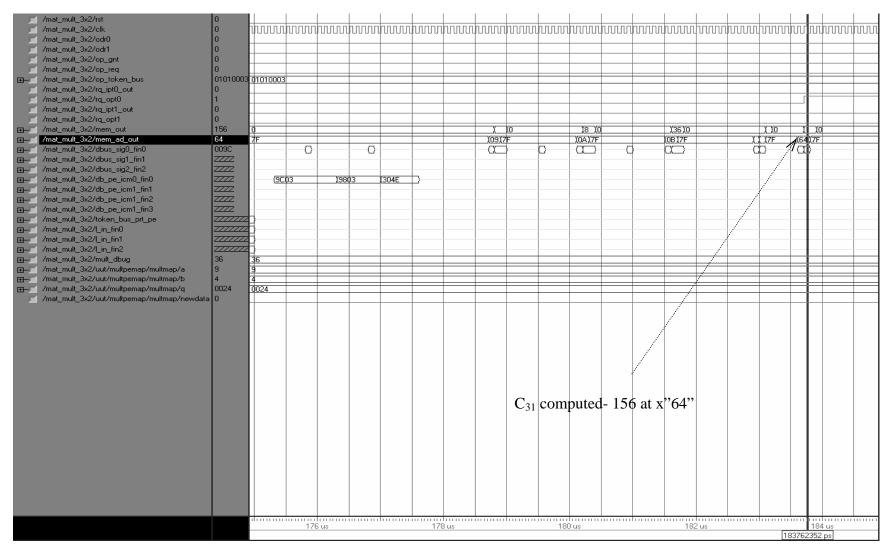

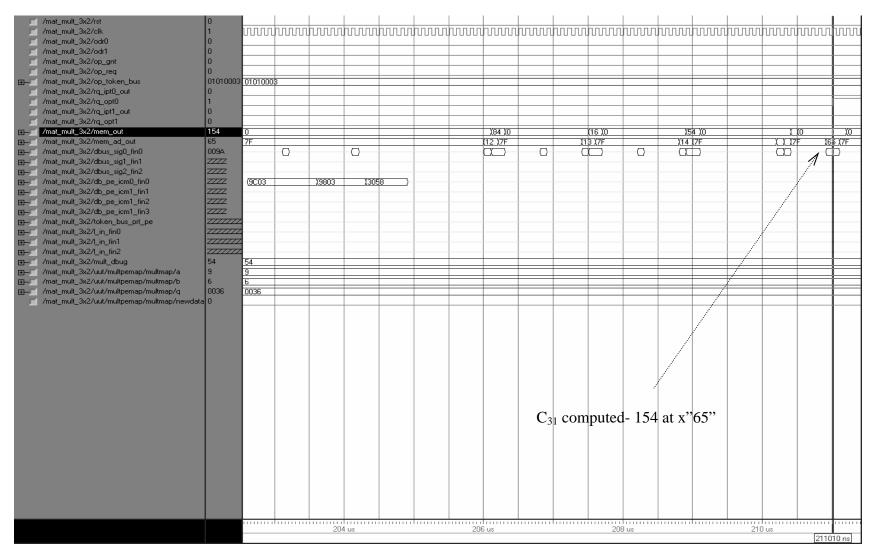

| Figure 6.35 : Join Operation0Ccomputes C31 Storing it at "64" hex in Shared Data           |       |

| Memory                                                                                     | 123   |

| Figure 6.36 : P22, P23 and P24 being Performed by CE4                                      | 124   |

| Figure 6.37 : Last Component of Result being Calculated and Stored as part of P25.         | 125   |

| Figure 6.38 : Final Results Being Displayed by Process P26                                 | 126   |

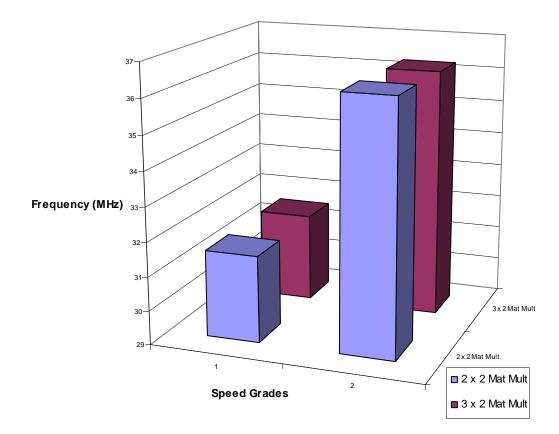

| Figure 6.39 : Plot of Maximum Frequency vs. Speed Grades for Applications 2 and            | 3 127 |

| Figure 6.40 : Process Flow Graph for Application Four                                      |       |

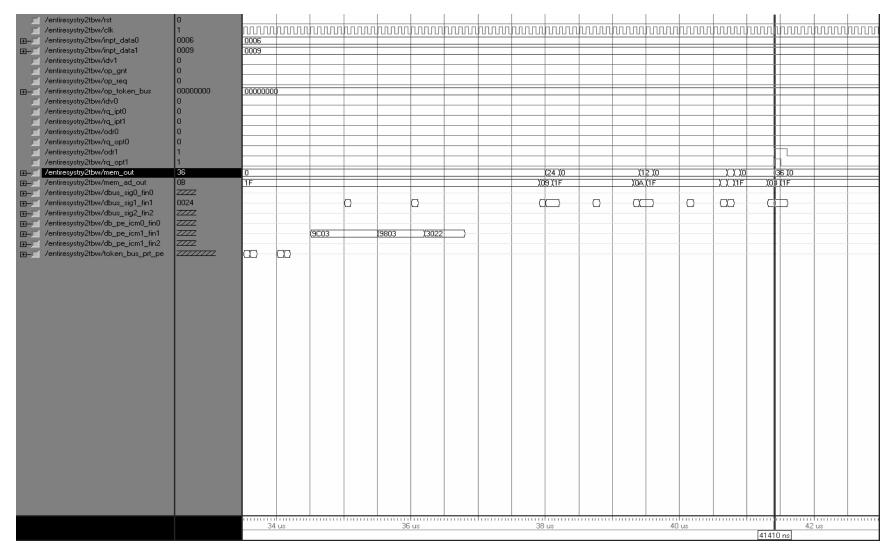

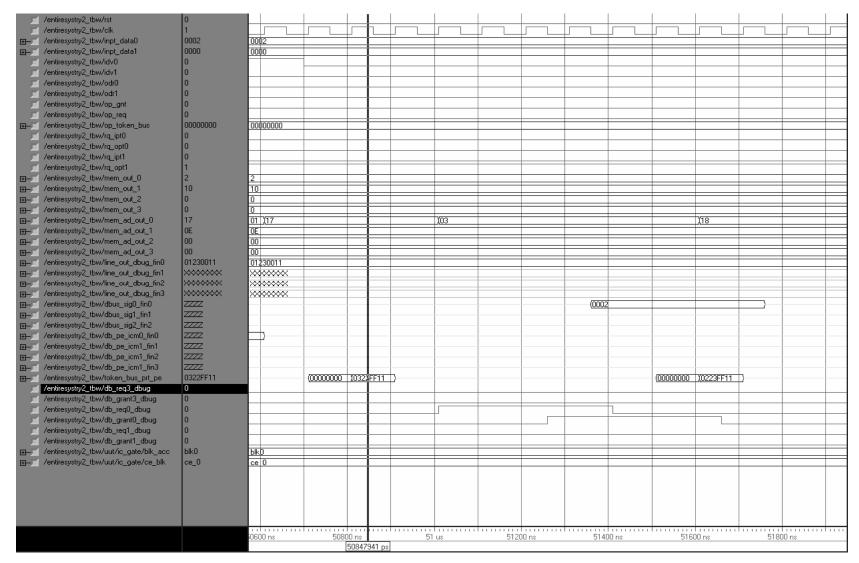

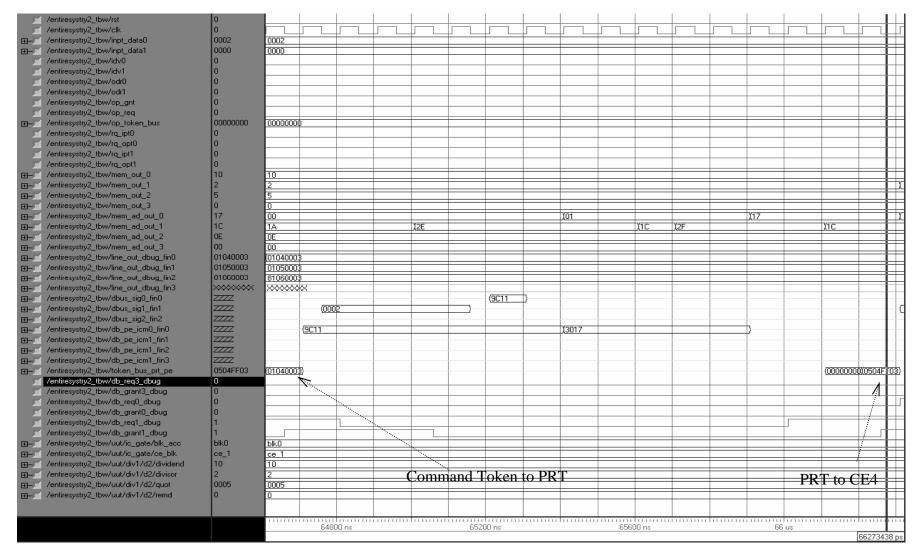

| Figure 6.41 : Command Tokens for both Copies of Process P1 to CE0 Issued by PR'            |       |

| Mapper                                                                                     |       |

| Figure 6.42 : P1 – First 5 Values of Copy1 being sent to Shared Data Memory                | 133   |

| Figure 6.43 - Input of Last 5 Values for Process P1 of Copy 1                              | 134   |

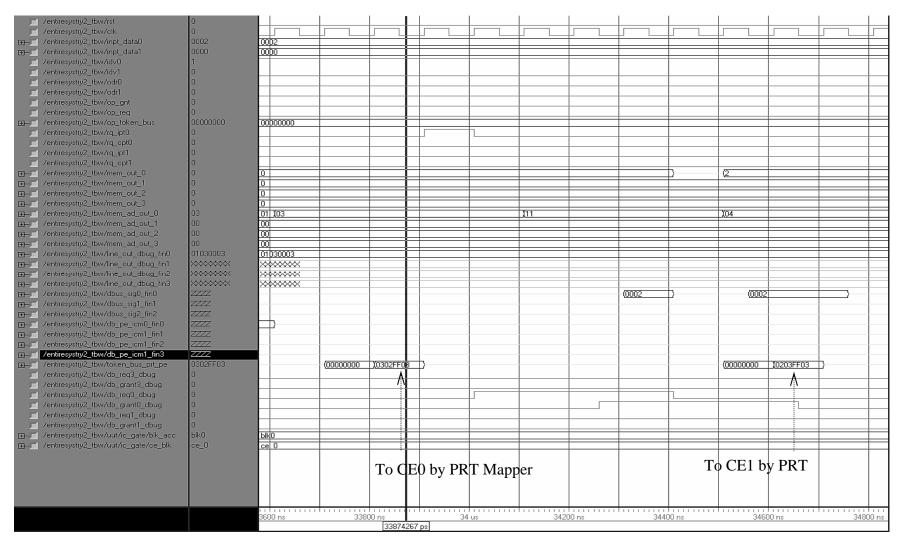

| Figure 6.44 : Two Command Tokens being Issued to PRT Mapper for Copy 1 135                         |

|----------------------------------------------------------------------------------------------------|

| Figure 6.45 : Command Tokens Issued to CE0 and CE1 by PRT Mapper for Copy1 136                     |

| Figure 6.46 : Instructions for Process P1 of Copy 2 and for Process P3 of Copy 1 137               |

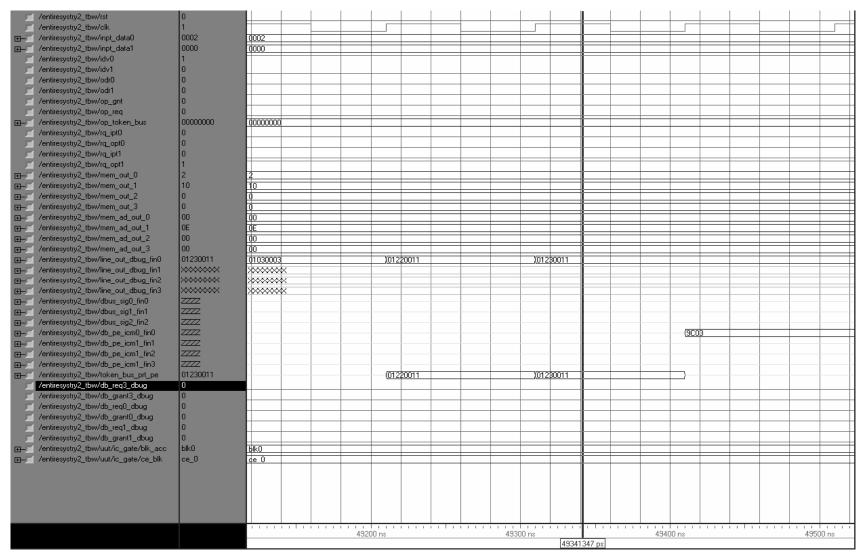

| Figure 6.47 : Two Command Tokens Issued to PRT Mapper for Copy 2 139                               |

| Figure 6.48 : Two Command Tokens Issued to CEs by PRT Mapper for Copy 2 - P2 and                   |

| P3                                                                                                 |

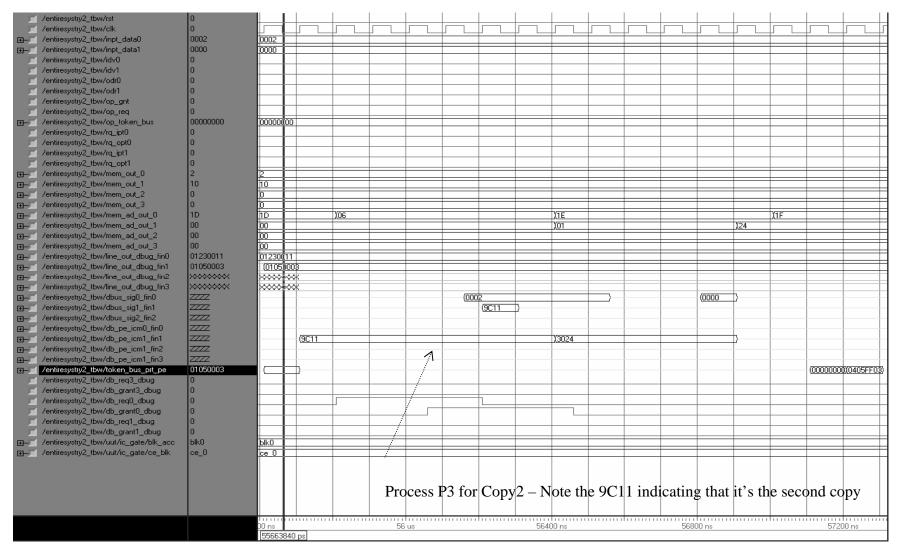

| Figure 6.49 : Process P3 for Copy2 of the Application 141                                          |

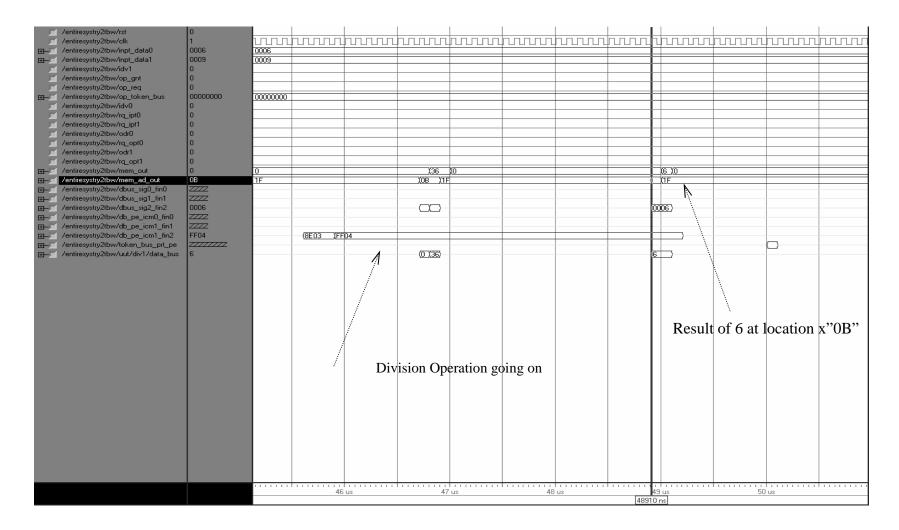

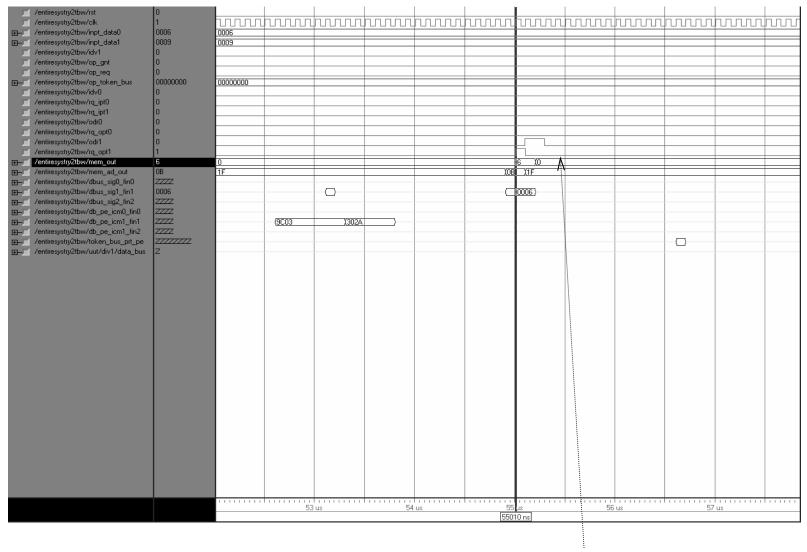

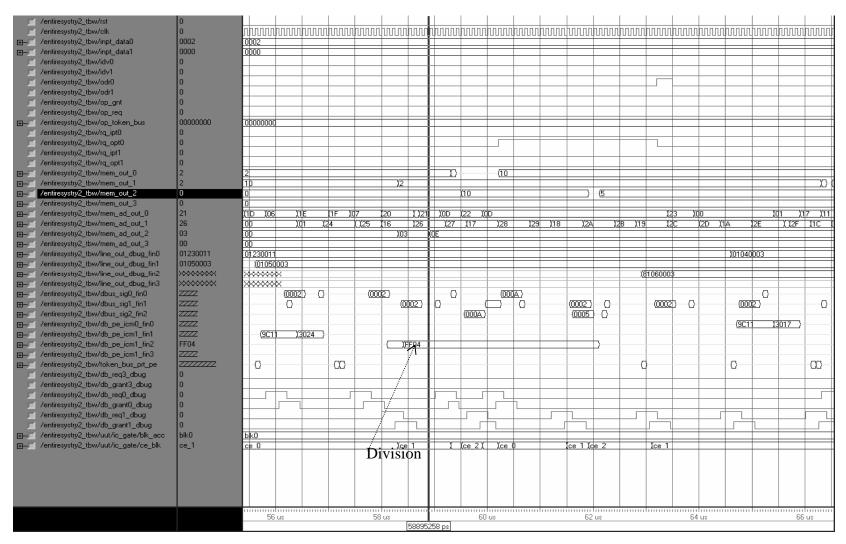

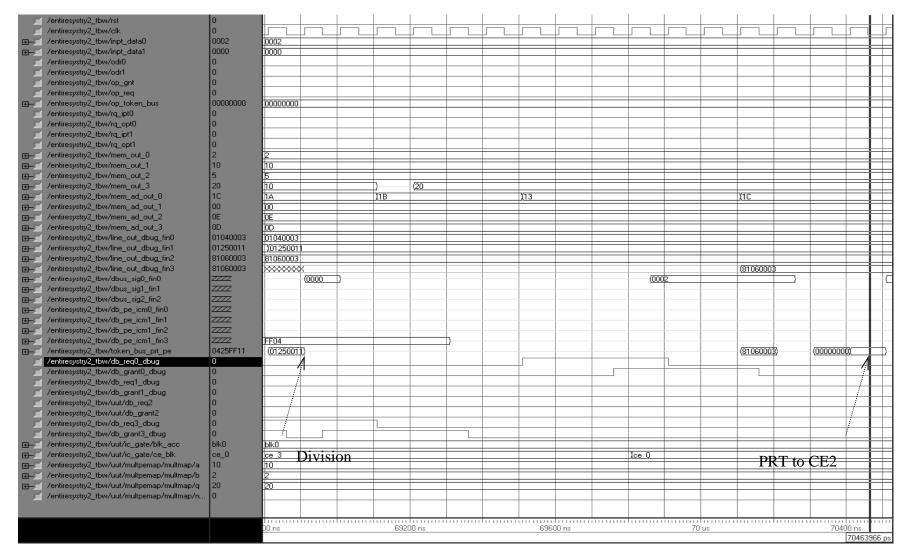

| Figure 6.50 : Division Operation in the Process of Execution                                       |

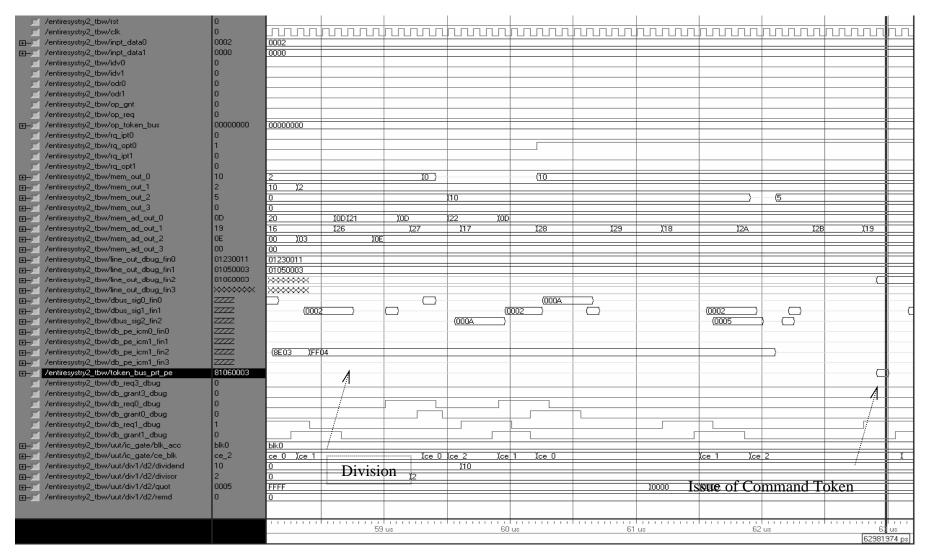

| Figure 6.51 : Division Operation for Process P5 with Results and Issue of Command                  |

| Token to PRT Mapper for Copy 1 144                                                                 |

| Figure 6.52 : Command Token for Process P4 Issued to PRT Mapper and from PRT to                    |

| CE4 for Copy 1                                                                                     |

| Figure 6.53 : Multiplication Operation by CE4 and Command Token Issued to PRT                      |

| Mapper for Copy 1                                                                                  |

| Fig: 6.54 : Command Token for P5 Issued to PRT mapper and from PRT to CE2 for                      |

| Copy 1                                                                                             |

| Figure 6.55 : Process P5 and Command Token to PRT Mapper for Copy 2 149                            |

| Figure 6.56 : Join Instruction for Process P6 of Copy 1                                            |

| Figure 6.57: Instruction for P7 and Final Results for Copy1 of Application Displayed 152           |

| Figure 6.58 : Result of Multiplication and Command Token Issued to PRT Mapper 154                  |

| Figure 6.59 : Join Process P6 - Instructions for Copy 2 155                                        |

| Figure 6.60 : Process P7 with Final Value of the Result Displayed for Copy 2 156                   |

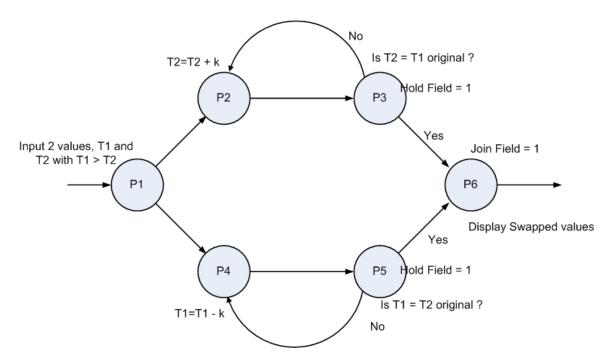

| Figure 6.61 : Process Flow Graph for the Application Swapping Two Sets of Values 158               |

| Figure 6.62 – First 2 Values being Input from Input ROM into the Shared Data Memory                |

|                                                                                                    |

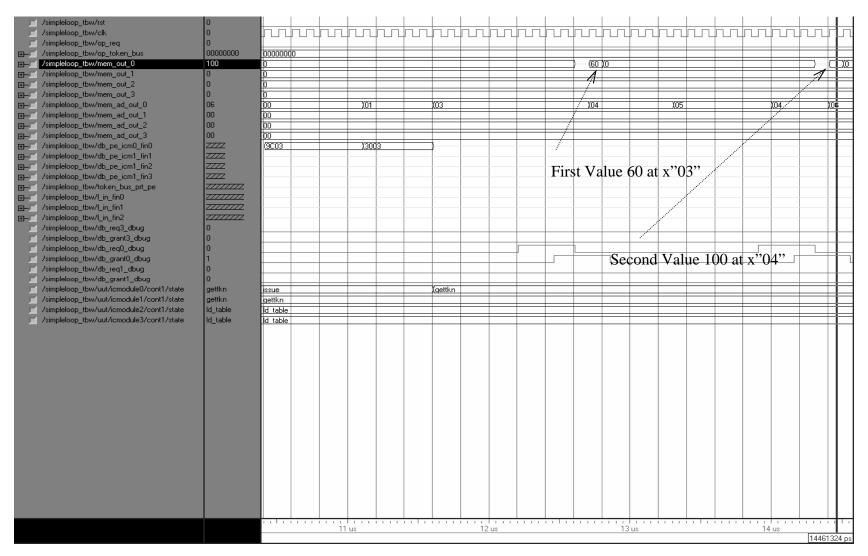

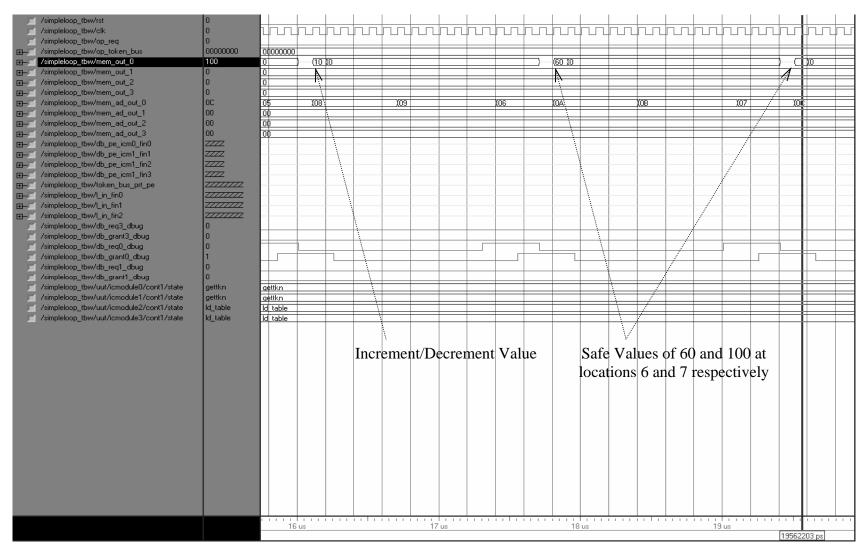

| Figure 6.63 : Values of k and Safe Values of T1 and T2 being Input into the System 162             |

| Figure 6.64 : Instructions for Processes P2 and P4164                                              |

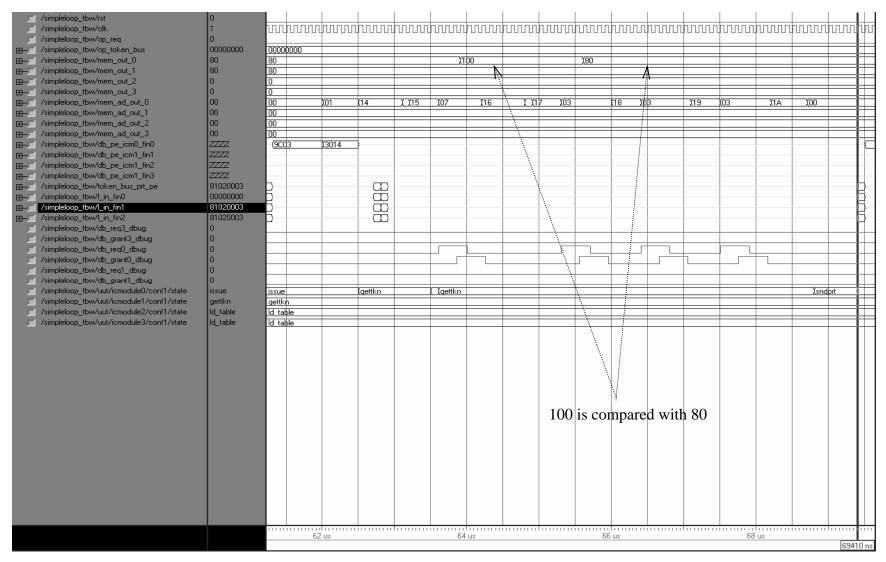

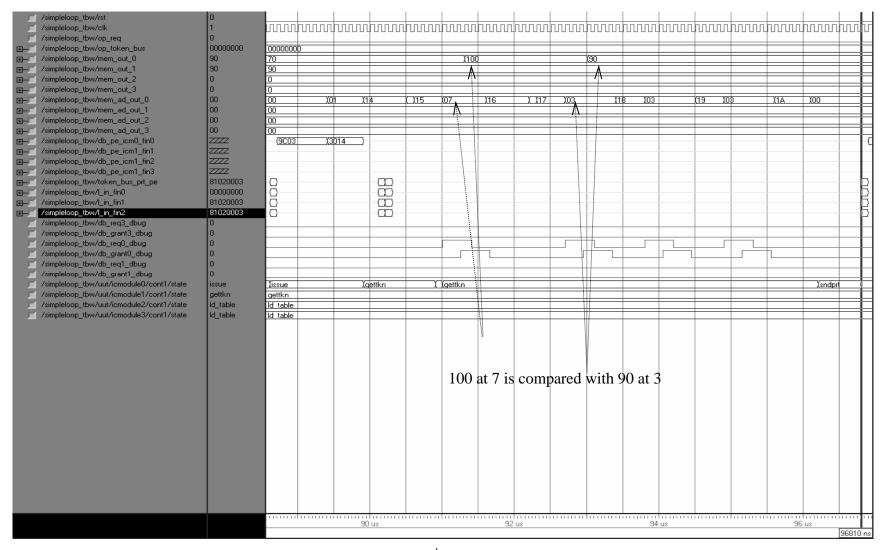

| Figure 6.65 : Process P3 being done. First Comparison Will be Performed 165                        |

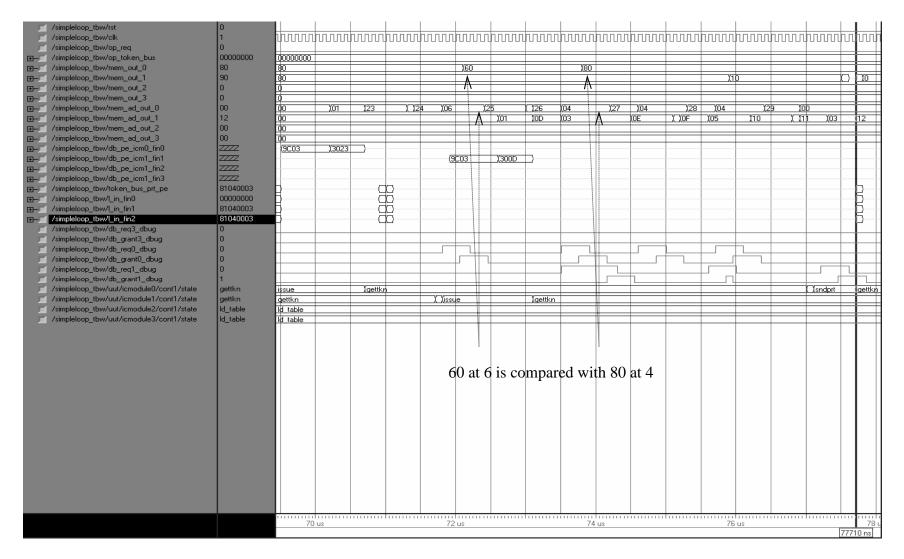

| Figure 6.66 : Process P5 is done comparing 60 with 90 166                                          |

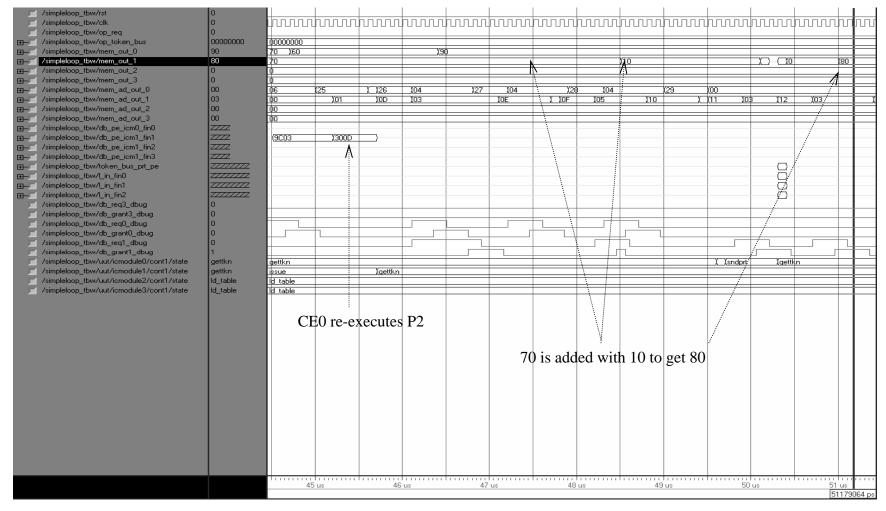

| Figure 6.67 : P2 being Re-Executed as Part of First Feedback Loop 168                              |

| Figure 6.68 : First Feedback for P4 done by CE0 169                                                |

| Figure 6.69 : Process P3 being Executed For the Second Time 170                                    |

| Figure 6.70 : Process P5 being Executed Second Time and the Follow on Process P4. 172              |

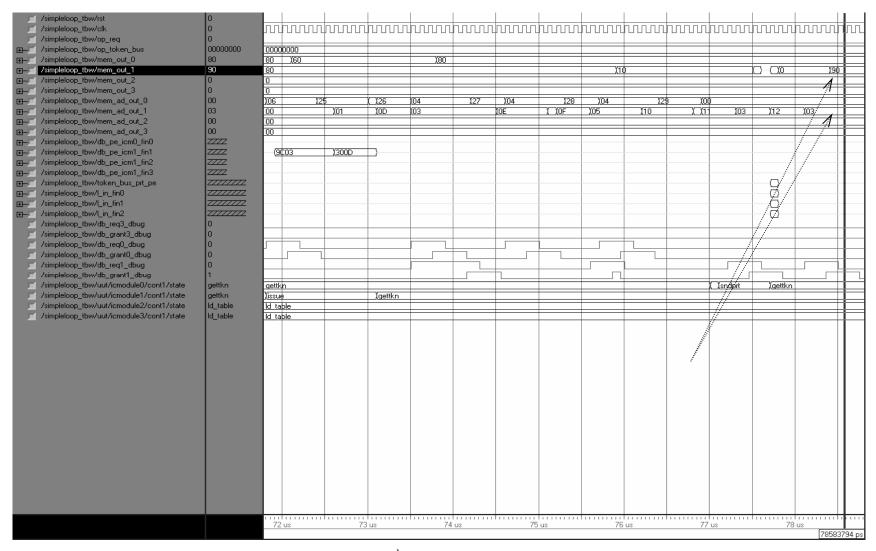

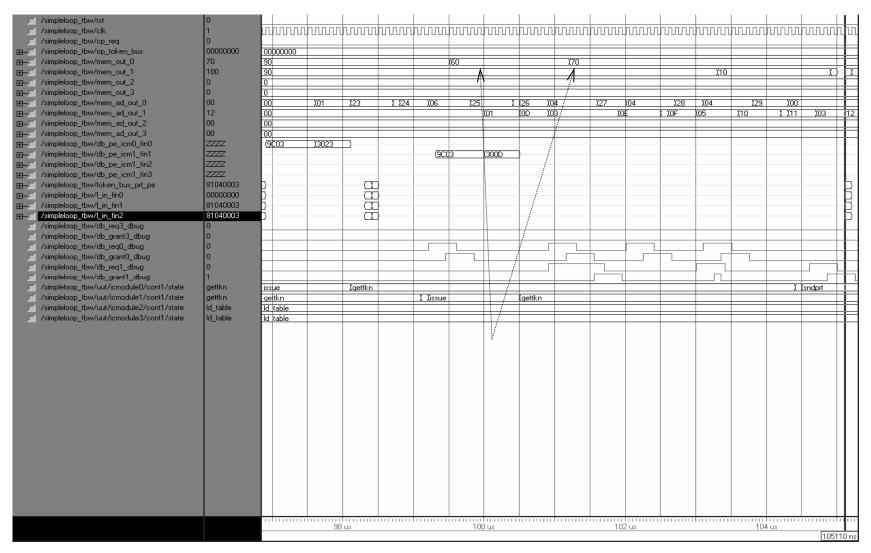

| Figure 6.71 : Process P2 Executed 3 <sup>rd</sup> Time and a Value of 90 Stored at Location x"03"  |

|                                                                                                    |

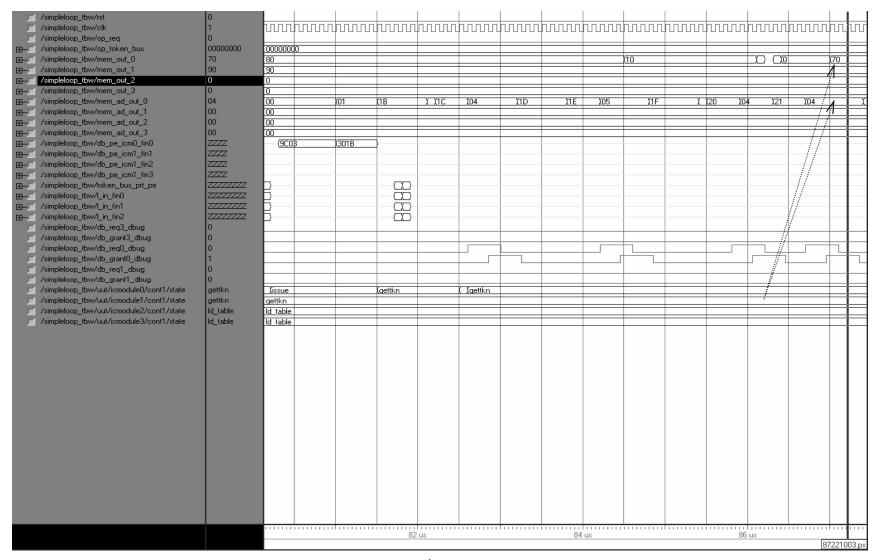

| Figure 6.72 : Process P4 Executed 3 <sup>rd</sup> Time With 70 Stored at Location x"04" 175        |

| Figure 6.73 : Process P3 Executed 3 <sup>rd</sup> Time Where 90 is Compared with 100 176           |

| Figure 6.74 : Process P5 done by CE0 where 70 is compared with 60 177                              |

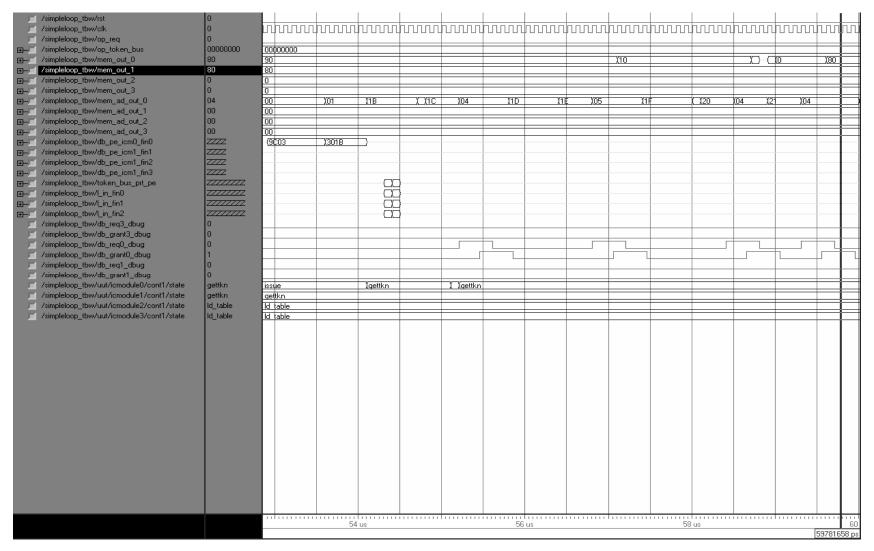

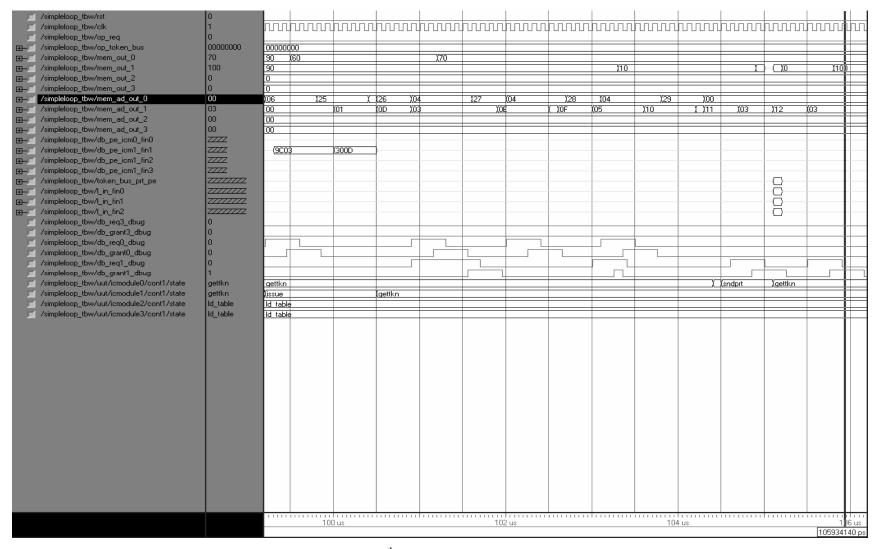

| Figure 6.75 : Process P2 Executed 4 <sup>th</sup> time by CE1 to Obtain a Result of Unsigned "100" |

|                                                                                                    |

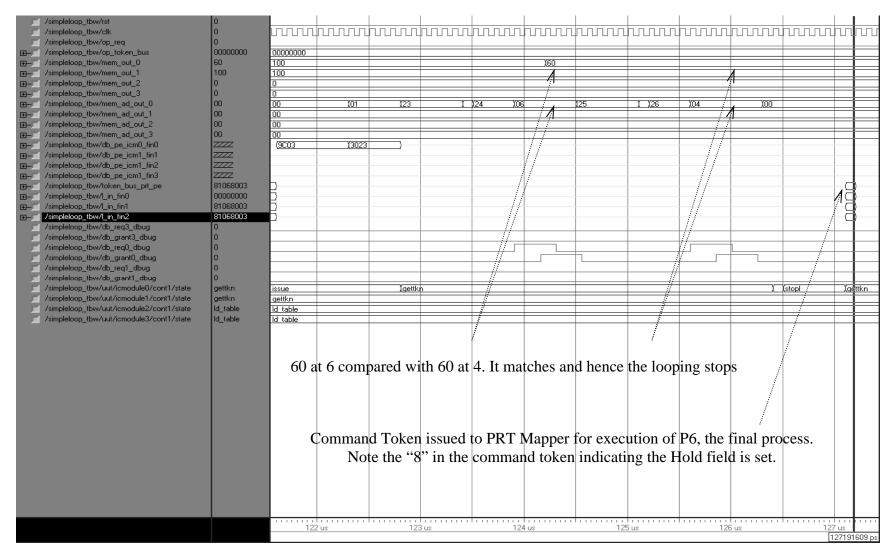

| Figure 6.76 : P4 is done by CE1 - 4th Iteration. A Value of Unsigned "60" at x"04" 179             |

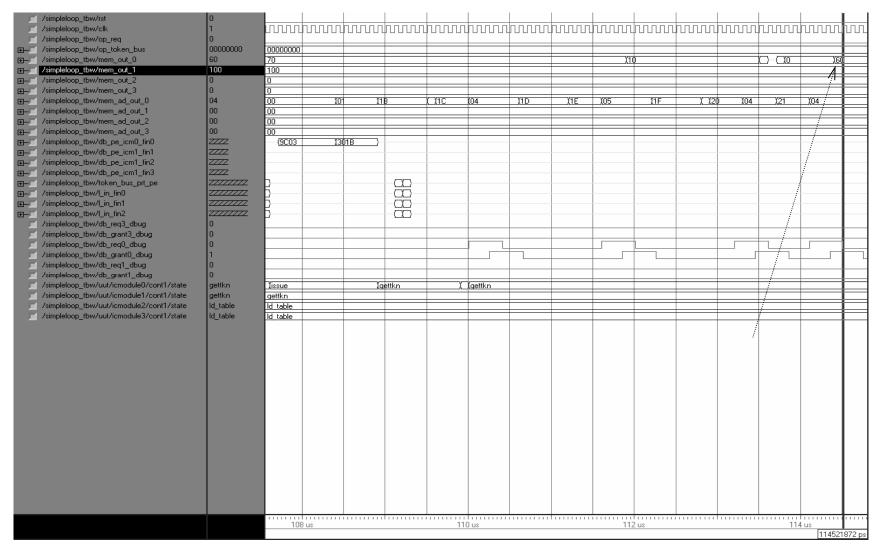

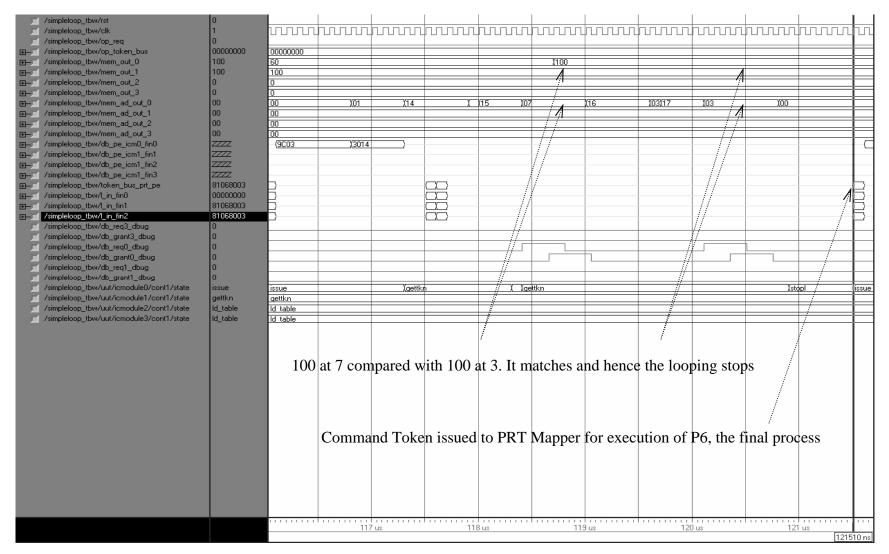

| Figure 6.77 – Process P3 Final Execution and Token for P6 Issued to PRT Mapper 180                 |

| Figure 6.78 – Process P5 Executed for Last Time and Command Token for P6 182                       |

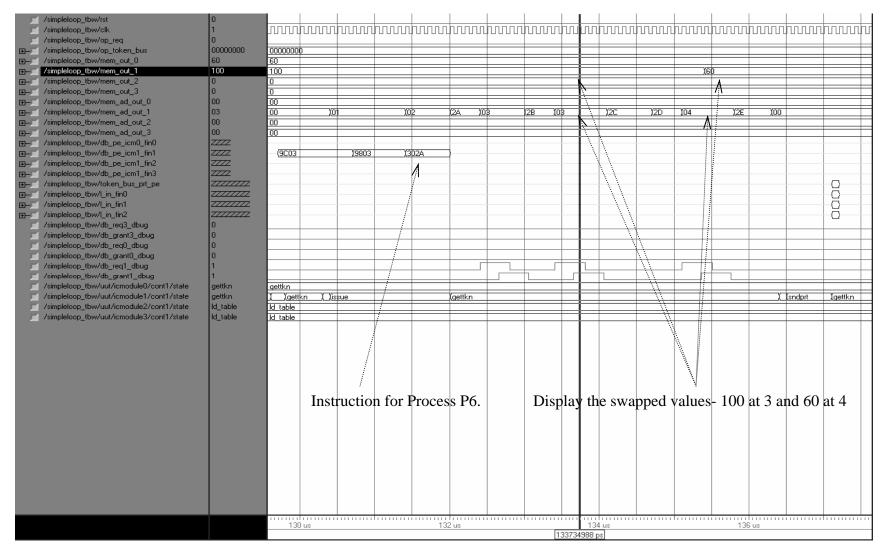

| Figure 6.79 – Join Operation P6 with Final Results and Addresses Displayed 183                     |

## Chapter One Introduction

#### 1.1 Background

Despite the increase in computing power and performance of uni-processor systems, there have been advancements in technology causing the evolution of complex real and non real time algorithms which demand the increased performance of multiprocessor systems. Along with such requirements, is the need for a fault tolerant, reconfigurable system, which can dynamically reconfigure to match the needs of compute intense applications. Such systems often use Field Programmable Gate Array (FPGA) technology as the basis for their use and design. The ability to configure these chips for a particular application and then quickly modify a configuration to meet the demands of new applications is highly desirable. Not only does it allow for application specificity, but it can also add a certain degree of fault tolerance and re-configurability that applications may demand. If a particular section of the chip has a fault then the existing logic can still be modified to execute the applications on the chip.

An early inception of these concepts originally led to introduction of a tightly coupled Dynamic Pipeline Computer Architecture (DPCA) [1,2,3,4,5,6,7,8,9] in the early 1980s. The DPCA as originally envisioned was reconfigurable at the application and the node level. It was reconfigurable at the application level in the sense that it could execute any application described by a process flow graph. At the node level, the architecture could dynamically allocate additional processors, on the fly, to a processor node when it became overloaded and continue execution of the application, as described in [3]. As indicated in [3], The DPCA architecture was originally developed as a real time processing system for phased array radar. In addition, the system was designed to execute any medium to coarse grained application which could be modeled as a single or multiple input/output, cyclic or acyclic process flow graph of any topology. The architecture varied from most others at the time because of utilization of hybrid data-flow concepts and von Neumann type processors. It was a hybrid data flow machine since it used data flow concepts to migrate data from one process on processors. Additionally,

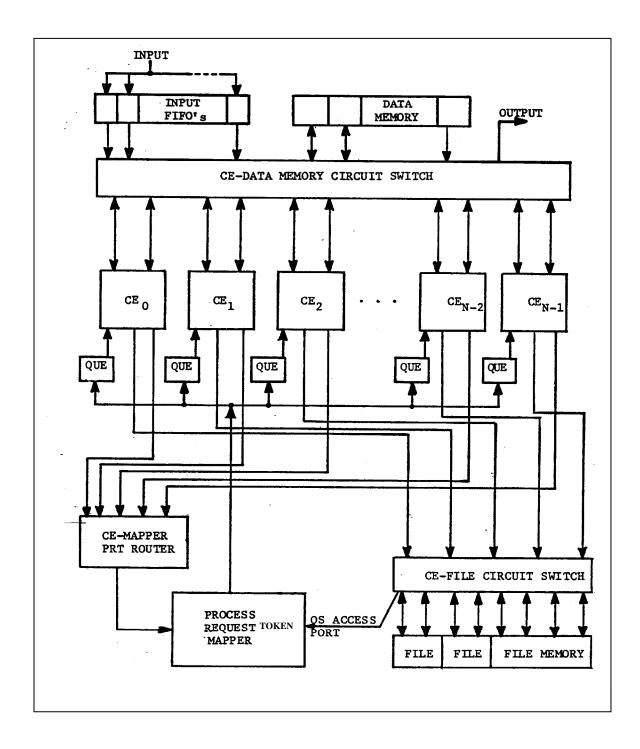

within the architecture, it is not the arrival of data at a node which causes the processes to execute but instead the arrival of a control token. The idea was to implement a medium to coarse grained multi-processor system with no inter-communication between individual processors. This system would consist of multiple processors that would communicate only through the exchange of command tokens and shared data memory. These tokens, upon their arrival into a queue fronting a processor would activate an appropriate process in the instruction memory of a given processor, commonly referred to in the architecture as a Computing Element (CE). A functional level diagram of the original DPCA is shown in Figure 1-1. Each CE in the figure was to be an early 1980s era mini computer.

The DPCA architecture functioned by receiving any process flow graph as an input. The Operating System would analyze this flow graph and allocate processes to CE's that would optimize the flow graph's execution [3,4,10,11]. The system would then be initialized and the application execution would start. Throughout an application's execution, control tokens circulate in the system. As a processor executing in a CE completes, it writes data needed by successor processes of a flow graph to the shared data memory of Figure 1.1. It lastly generates a control token which is routed to the CE-Mapper Process Request Token (PRT) Router and then the Process Request Mapper functional unit of Figure 1.1. The Process Request Mapper, using hardware; dynamically balances the load of the system. The CE-Mapper PRT Router and Process Request Mapper analyze the current load condition of each CE and issue a control token to a CE holding a copy of the process where wait time for execution of the process is minimal [3,7,12]. A CE receiving a control token executes the desired process and then, upon its completion, issues a control token to the CE-Mapper that indicates the next process (es) to execute. In this system, CE's do not directly communicate but are able to share data through the CE-Data Memory Circuit Switch [2,3,8,9,27,28]. Applications are thus executed by executing the process flow graphs that represent them.

For a more intricate explanation of the DPCA system and its operation, see [3].

Figure 1.1 : High Level Architecture of the DPCA

The DPCA system, over time and as Integrated Circuit (IC) technology changed, has evolved into the single-chip based HDCA or the Hybrid Data/Command Driven Architecture.

#### **1.2 HDCA Concepts**

As one can see upon review of [1-12], high level simulation and design for several of the functional units of the DPCA system were developed but no hardware prototypes were ever developed for experimental testing. Also, no attemps were made to prototype and test the entire DPCA system. More recently, due to rapid enhancement in IC technology and heightened interest in high performance single-chip multiprocessor architectures for embedded and other applications, it was realized that the DPCA was functionally amenable; with some functional changes and enhancements to being implemented as a hybrid single-chip heterogeneous multiprocessor system. Consequently, the DPCA system has evolved into the current HDCA system. The start was in the 1997 time-frame [13,14]. A number of changes were incorporated while moving from the DPCA to the HDCA system. Amongst the most significant were, moving from a distributed system to a single chip architecture or a System On a Chip (SoC) and making the system reconfigurable at a third, processor architecture level, which basically implied that the processor used in a Computing Element (henceforth referred to as a CE), could be dynamically configured from a reference "library" of processors to optimize execution of portions of the process flow graph. The entire HDCA concept was envisaged to be implemented in a three stage process. As part of the first stage, system simulation work [13,14], it was demonstrated that the system could be reconfigured at the system and node levels. A hardware prototype was not built at that time due to constraints related to costs and changes in architecture that were to come. Recent changes in IC technology have spawned reconfigurable logic such as FPGAs with as many as 5 to 6M gates on a single chip and have also scaled down the costs associated with manufacturing such chips. An approach was undertaken of first imeplementing and experimentally testing and validating an FPGA based hardware prototype of key functional units of the HDCA [15,16]. A first hardware prototype of a very basic and scaled down entire system HDCA was developed, experimentally tested and it further

validated that the architecture could execute simple and elementary applications described by acyclic process flow graphs [17].

As a background to which the research and development of this thesis can be compared, an examination of various journals and papers reveals different interesting areas to which reconfigurable and dynamic computing has expanded. One of these areas is in developing custom architectures. In [18], the researchers show that a custom FPGA solution outperforms an ASIC based design due to the fact that the logic in an FPGA can be reconfigured to meet the needs of applications running on the architecture.

Another area of research is in replacing software modules by the equivalent hardware circuitry. It is here that the reconfigurable nature of an FPGA is most important as shown in [19], where one can use the available hardware resources in the FPGA to accelerate the bottleneck in the software code, thereby gaining some extra performance benefits. Since the logic elements in the FPGA are programmable, one can customize the hardware for any application without having the need to make board revisions. Also, the work done in [19,20,21] show that often implementing an algorithm in hardware instead of software provides performance improvements.

Recently, combining ASICs with reconfigurable logic has been increasing as shown in the GARP system of [22,23]. Here the researchers allow the system to implement certain functions of an application in the reconfigurable logic in order to obtain enhanced performance. The close integration of ASICs and reconfigurable logic allows designers to take advantage of fast, general purpose ASICs while maintaining the flexibility and specificity of reconfigurable logic.

Yet another area where reconfigurable computing is expanding is in space applications where the focus is on fault tolerant, low power, radiation tolerant design. In the work done in [24], the researchers have been designing a Reconfigurable Data Path processor for Space applications where execution agility is maintained by conditional switching of the data path instead of conditional branching.

Another venture is in the work done at Clemson University [25] where scientific algorithms are mapped to FPGAs through the use of a 'toolbox' of designs. The Reconfigurable Computing Application Development Environment (RCADE) system combines several designs from its library to execute an application in a data flow manner.

Through the use of these techniques, the researchers are able to utilize FPGAs for scientific applications while maintaining the desired speed of the application.

The work done in [26] is notable, where the researchers present a coarse-grained dynamically reconfigurable array architectures promising performance and flexibility for different challenging applications in the area of broadband mobile communication systems.

Based on the above developments, the HDCA can be classified under the same category as the work reported in [21, 25 and 26]. Reconfigurable Architectures have thus touched every aspect of life from Communication, Signal Processing to Space applications in the recent years. Unlike systems in the work of [21,25], the HDCA system can analyze an input application's needs at run time and then configure the system for the most efficient execution. Additionally, the HDCA is designed to be fault tolerant. It is capable of recognizing failed nodes and reconfiguring itself to continue operations. Overall, the main contributions to this field are the integration of compiler-type run time system configuration, with dynamic hardware implementations of software algorithms and the incorporation of fault tolerance. Typical applications of the HDCA architecture would thus be in real and non-real time systems, such as in embedded systems for use in space, phased array radars, and sonar signal processing and different areas of Digital Signal Processing such as image processing where multiple filtering operations may be needed to be performed on the same set of input pixels. As an example, one set of the input data pixels in an image may need to be Sobel edge enhanced and the other may need to be smoothened.

#### **1.3 Goals and Objectives of the Thesis**

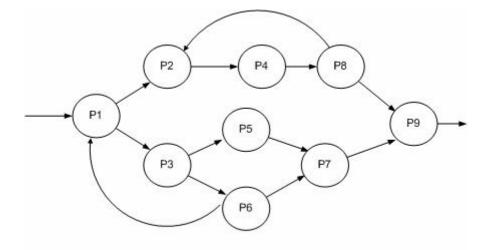

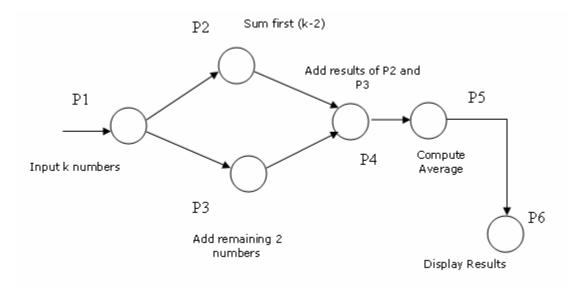

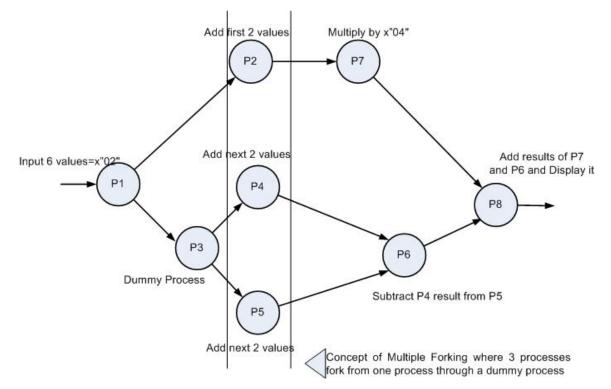

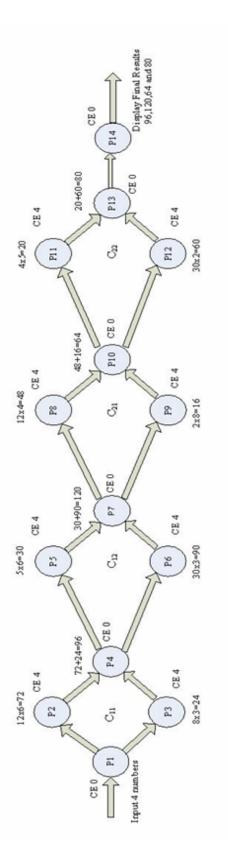

The main goal of the research and development done here is to design, implement and test a second phase functionally working latest model of the HDCA computer architecture[3,12,13,14,15,16,29] with non complex and complex applications and take it through a "virtual prototyping" process where a working single-chip post place and route VHDL simulation model is demonstrated. In order to achieve this goal, several previously developed system functional units will be used. Some will be significantly modified and newly designed.A VHDL model of the latest version of the HDCA will be developed.The system should have multiple Computing Elements (each with a Multifunction Queue [16]), the Process Request Token Mapper [15], a shared memory that is accessible by all processing elements [29], and a common Token Bus. An additional goal is to demonstrate the ability of the system to function with heterogeneous processing elements and to reconfigure dynamically at the node level at run-time to meet the additional processor work load requirements and maintain a fault tolerant model of the system (as mentioned in [3]). Thus the work done here, should demonstrate that the architecture can process an application dynamically reconfigurable at the node level. The second phase virtual prototype of the HDCA will not have the restriction of the first phase system prototype [17] which was that one process could, fork into, atmost two processes. Removing this restriction will allow the HDCA to execute interesting process flow graphs, such as the acyclic graph shown in Figure 1.2 below.

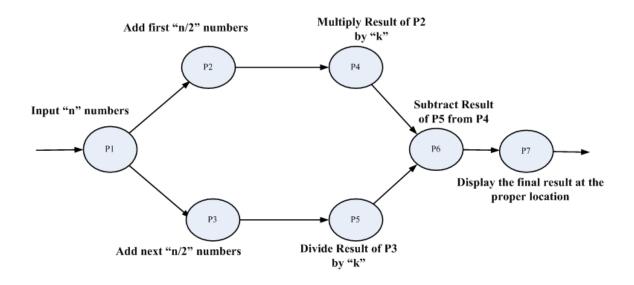

Figure 1.2 : Process Flow Graph for a Typical Application

Finally, the work of this thesis demonstrates that the heterogeneous shared memory HDCA multiprocessor system can be implemented to a single-chip.

#### **1.4 Thesis Summary**

The remainder of the thesis provides the detailed information on the HDCA system architecture and the steps taken to functionally enhance and upgrade the existing model to one which can implement process flow graph of any topology and implement node level dynamic reconfigurability. Chapter Two adresses previous work done on the HDCA and provides more detail on the system concepts utilized for the same and

explains in great detail, all the core components of the system including the additional components added while moving to the second phase model of the HDCA. Chapter Three provides information on the systematic design methodology utilized and the changes made to the first phase prototype [17] to get it from a partially-functional condition to a fully functional, synthesizable and implementable second phase "virtual prototype" using the latest version of the Xilinx ISE 6.2.3i software [30] and Mentor Graphics Modelsim 5.7g SE [31] tool sets in the new foundation ISE environment. Chapter Four addresses the "Virtual Prototype" development process and provides information on hardware usage and timing statistics. Chapter Five introduces the functional enhancements into the HDCA and provides a detailed insight into the concepts of dynamic node level reconfigurability and multiple forking. Next, Chapter Six discusses complex real/non-real time applications developed for the architecture and the simulation results obtained. It also showcases talks about system scalability at the application level and performance results. It also justifies the policy decisions taken in the process of demonstrating the concepts. Chapter Seven concludes by discussing the overall achievements and suggests directions for the continued advancement of the architecture in the form of recommendations.

# Chapter Two Background and System Details

#### 2.1 HDCA and Related Background Work

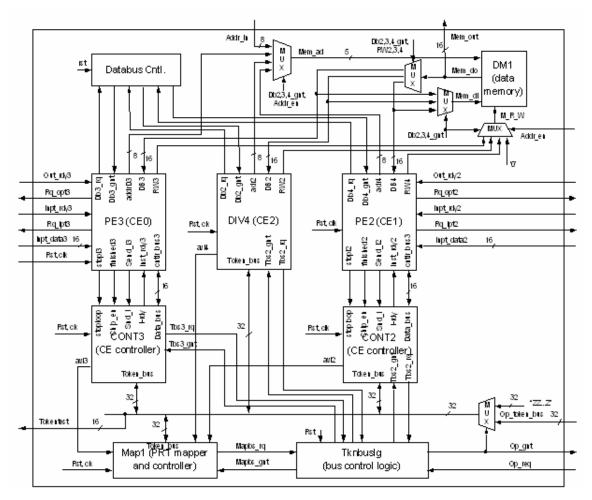

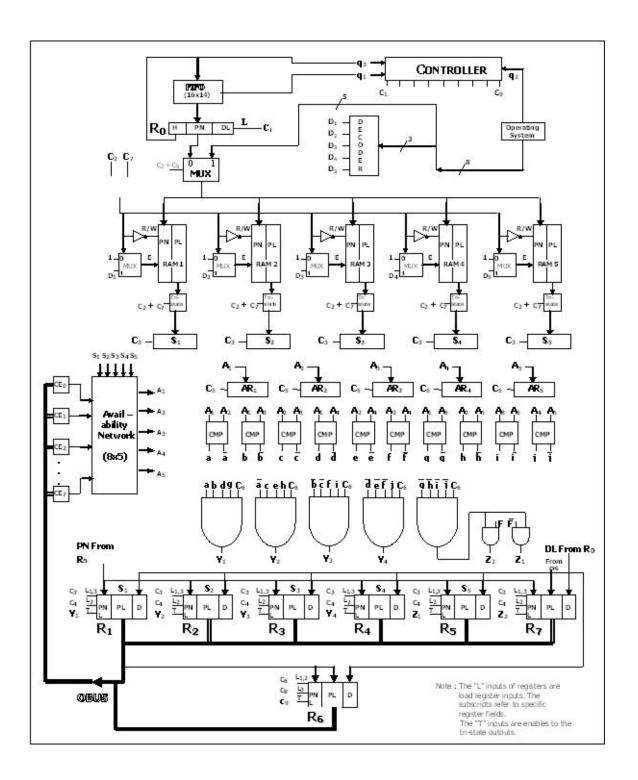

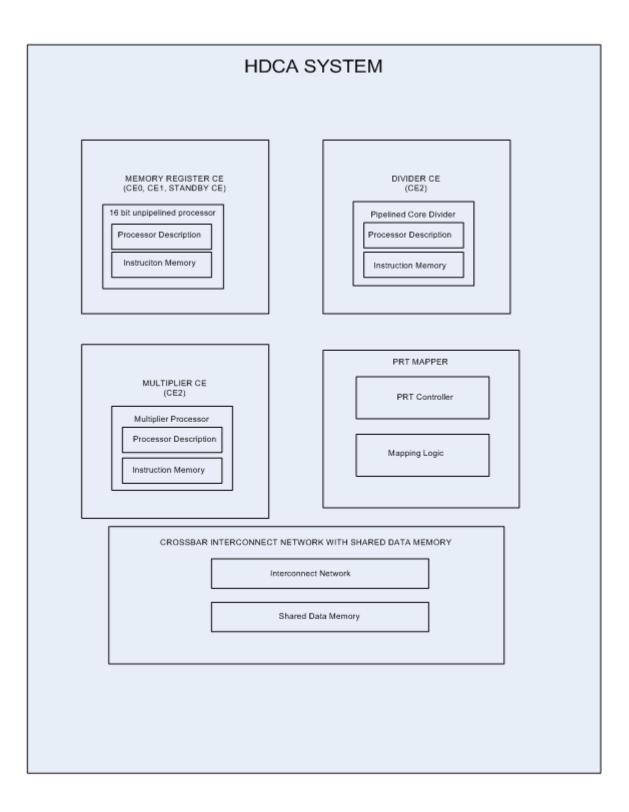

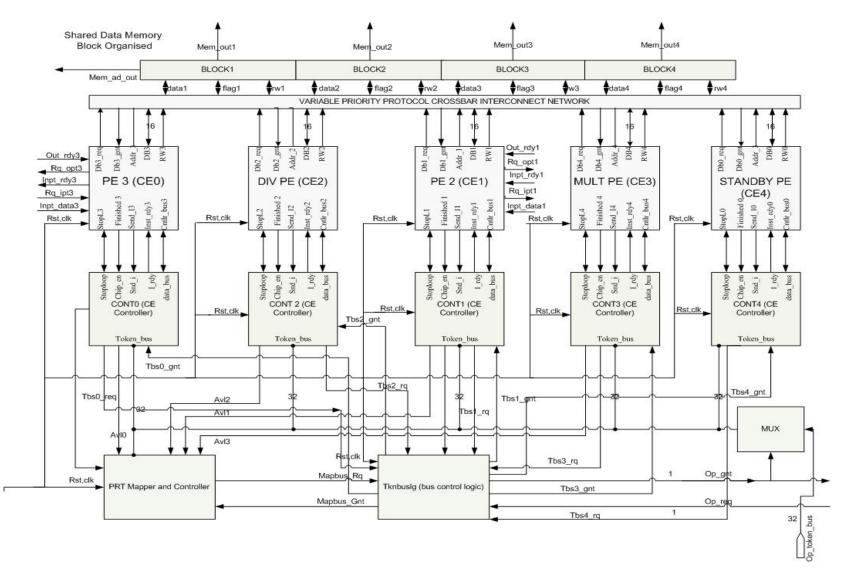

The HDCA architecture as developed and demonstrated in [17] consisted of three CE's (each with an instruction memory and CE controller), a Token bus, a Process Request Token (PRT) mapper with controller and a data bus with shared data memory as shown in Figure 2.1a. In theory, the CEs used in the system could be any CEs but in order to demonstrate the heterogeneous nature of the system, two of the CEs used were 16 bit un-pipelined memory register type computer architectures developed as part of coursework. The third CE was a special purpose Divider CE.It was different in the sense that it did not have a program counter like the other CE instead it used a controller along with a special purpose pipelined divider to execute processes that needed to use the divide operation.

One of the core concepts of the HDCA architecture is its ability to execute any application that can be described by a process flow graph model. As mentioned in [17], in this model, data arrival does not trigger process execution as would a pure data flow graph model. Instead, the arrival of Control Tokens triggers process execution. These Control Tokens are shorter and thus more efficiently and quickly transmitted between computing elements than blocks of data. In the process flow model, data is propagated from one process to another through the use of a shared memory structure. Actions are performed on that data when processes access the data memory. The HDCA architecture operates on the principle that applications can be modeled using process flow graphs and then implemented in a system.

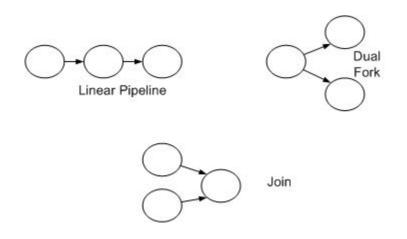

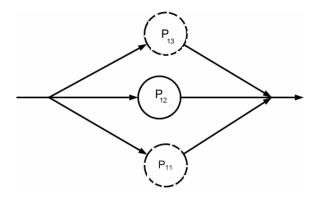

Figure 2.1a : A High Level Diagram of the original HDCA

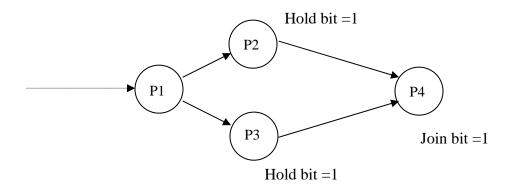

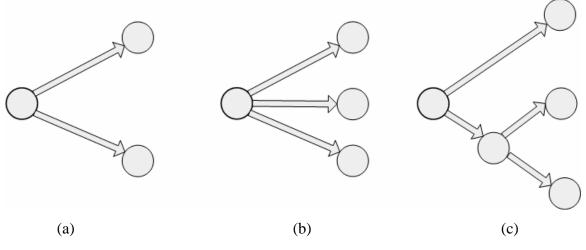

The fundamentals of process flow graphs start with their three basic structures as shown in Figure 2.1b from [3]. A process flow graph can basically consist of linear pipelines, forks, and joins. In a linear pipeline Control Tokens simply move from one process to the next in a uniform manner. Data needed by the processes are resident in a shared memory. Within a fork Control Tokens are distributed to multiple follow-on or successor processes. Forking may be to two or more processes and may be selective or non-selective. To potentially increase the amount of parallelism in an application, a scheme for multiple forking has been introduced to the HDCA. The join is the complimentary function to the fork where Control Tokens from two or more sources are selectively or non-selectively combined for execution in one process. The non-selective fork represents a total broadcast of data along all output arcs, whereas the selective fork represents a broadcast of data along a single output arc or a subset of output arcs.Similarly, during the execution of a selective join, only a selected subset of input arcs to a process is active. A non-selective join is triggered when all the inputs to a process are active. When these basic structures are combined, any application composed of multiple processes can be modeled. Figure 2-2 shows a simple process flow graph of an algorithm operating on integers. In this graph execution begins at "Process P1" with the input of a set of integers. "Process P1" then forks a subset of this information to processes P2 and P3 where some integers are summed. Simultaneously, in pipeline fashion, Process P1 inputs a second set of integers. Processes P4 and P5 then perform multiplication and division operations on their results to obtain new results which they transmit to process P6 where an absolute difference is taken. Process P7 finally outputs the result of this computation to the user. The simulation results and virtual prototype output waveforms for this application can be found in later chapters of this thesis. The idea behind the HDCA is to have multiple processors

Figure 2.1b : Basic Process Flow Graph Structures.

Processes on individual Computing Elements (CE's) do not start execution until an initializing token has arrived. Once a token is received, indicating the location and availability of data needed by the process, the CE parses it in order to determine the proper process to execute. This is due to the fact that each CE can hold several processes in its Instruction memory or only one process. The CE then executes the appropriate process and upon completion issues the follow-on token(s) for the successor process (es).

These tokens are the sole communication between CE's. An example Control Token format is shown in Figure 2.3.

Figure 2.2 : Example Process Flow Graph.

In this token the Hold Field is used to indicate a requested process that is a member of a join operation. It is also used by the system in a manner such that the processor token queue depth represents true wait time for the initiation of a requested process. The Physical address denotes the destination CE or functional unit for the token. For example the five different CEs used in the HDCA system presented later have addresses of two, three, four, five and six The Process Number indicates which process to execute and the Data Location provides the address of the data in shared memory which is accessed through the Crossbar interconnect switch as described in [29,32].

| Hold Field &     | Process Number | Data Location |

|------------------|----------------|---------------|

| Physical Address |                | Data Location |

Figure 2.3 : Token Format for the HDCA

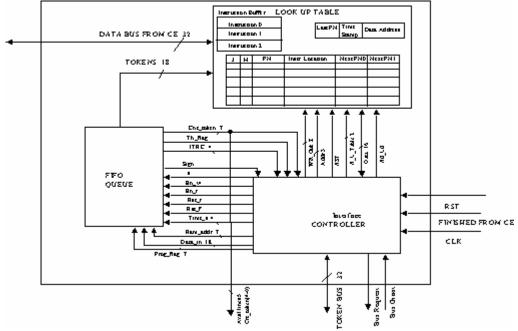

#### 2.2 PRT Mapper

An important function of the PRT Mapper (see Figure 1.1 for this dunctional unit in the DPCA and Figure 2.4 for a more detailed view of its design as enhanced to operate in the

HDCA) is to maintain the dynamic system workload balance. In order to achieve this goal, it constantly monitors the input control token queue lengths/depths of each CE in order to determine the most available CE. Control tokens are sent first to the PRT mapper where it is cross-referenced in a RAM table to determine which CE's are able to run the desired process. Not all CEs can run all the processes. The workloads of the eligible CEs are then compared, resulting in a control token being issued to the least loaded CE i.e the one with the lowest amount of work to be done. In order to determine which CE has the least amount of work, the concept of shortest wait time is used. The CE that has the shortest wait time indication in its input control token queue is the most available since it will service the token before its corresponding CE. Once the eligible CE's are known, it compares the workloads of those CE's to determine which is the least utilized. A new control token is then created using the physical address of the selected CE and the location of the associated data. The newly formed token is then output on the Token Bus via the OBUS to the appropriate CE. This new control token contains the Process Number to be executed, the physical location of the destination CE, and the address of the required data in the shared data memory. The original design capture was done in Verilog, therefore it was necessary to interpret the code and translate it to VHDL for the HDCA VHDL model. This was done in the work described in [17].

In addition to the load balancing function of the PRT mapper, the state of the system is continuously monitored in order to detect faults and system failures. If a CE node fails, the system has the ability to shift the work of a failed node to another location. Additionally, the system is designed with the intent to allow it to reconfigure its processing elements in the event of a failure or to create additional copies of a resource that is heavily used. This happens when the tokens have been queued sufficient enough, that the queue depth reaches a pre-defined "threshold" determined by the user/operating system. At this stage, an additional processor is dynamically initiated and configured, on the fly, to "help-out" this overloaded CE and help it reduce the queue depth by executing some of the follow on processes. This allows the system to dynamically maintain the desired application system input to output rate and functionality of the system even if elements fail or workloads are higher than initially and statically predicted from the application process flow graph.

Figure 2.4 : Process Request Token mapper Circuit Diagram.

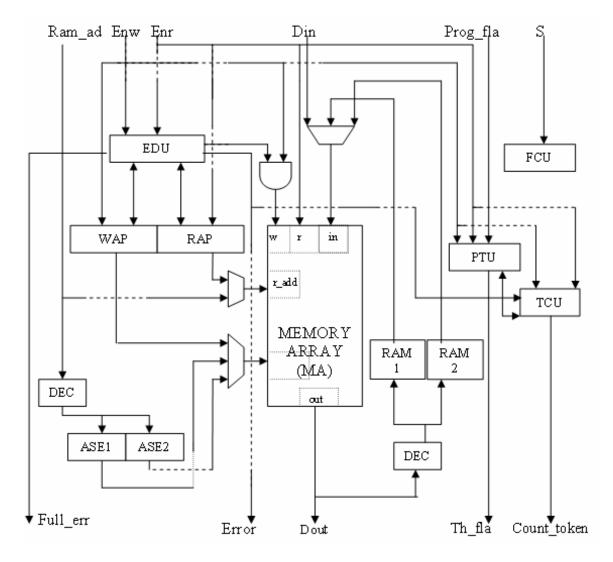

#### 2.3 Multi-Function Queue

When the original architecture (DPCA) was designed as represented in Figure 1-1, it was a known fact that the CE's would each require a FIFO queue to hold control tokens that were yet to be parsed and executed. This was so because as tokens are parsed by the CEs and a particular CE gets busy executing the process, the incoming tokens have to wait for their turn in the queue. If there was no queue provided, these tokens would be lost and hence the system would not behave as expected. Gradually, as work progressed on the development of the HDCA, it was determined that this queue needed some more additional features. These new features allow the HDCA to operate in both a real time and non-real time environment, and they support its dynamic node-level reconfigurability. The functionality of the FIFO queue was expanded to implement six different functions [16]. It can read and write simultaneously, maintain a count of elements in the queue, and signal when a programmable queue depth threshold is met. It can also switch the order of any two tokens in the queue and report the net rate at which tokens are entering or leaving the queue over a programmable time period. A high-level block diagram of the Multi-Function Queue is found in Figure 2-5. Figures 2-6 and 2-7 show a functional level diagram of the FIFO and Rate blocks respectively.

Figure 2.5 : Multifunctional Queue

#### 2.3.1 FIFO Block

Figure 2.6 : FIFO Block Functional Diagram.

The Queue's ability to switch the order of tokens can allow the system to give priority to a given token. If the system sees that a process is waiting for an input token that is stuck in an unusually long queue, it can re-organize the queue such that the token of interest is swapped with the token at the top of the queue which is about to be serviced. This helps to reduce execution time by allowing processes to be executed faster. The queue achieves this by placing the tokens in a temporary buffer and then swapping them. The swapping is implemented by an address interchange between the two tokens using the RAM1 and RAM2

#### 2.3.2 Rate Block

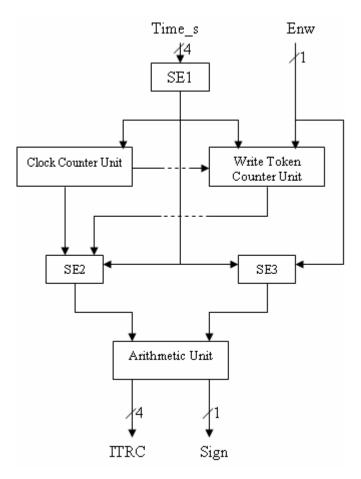

Figure 2.7 : Rate Block Functional Diagram.

Another important feature of the Queue is the "rate" feature as represented by the Rate Block of Figure 2.7. It measures the Input Token Rate Change (ITRC) over a programmable time interval (Time\_S). This time period indicates the time period over which to base the calculations. The Queue then determines whether there was a net increase or decrease in the number of tokens passing through the Queue over the given time period. The outputs of this function are a sign bit (Sign) and a magnitude (ITRC). Thus the Operating System can determine the workload of a CE by the number of tokens arriving or departing a given queue. The original queue VHDL code had to be modified as reported in the work done in [17,33] to suit the HDCA system.

#### **2.4 The Computing Elements**

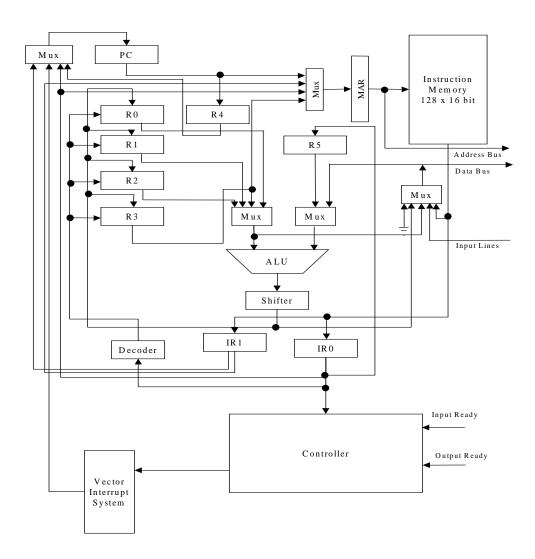

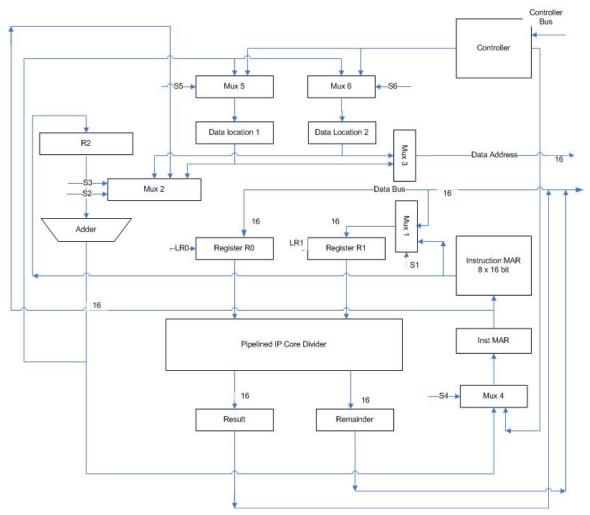

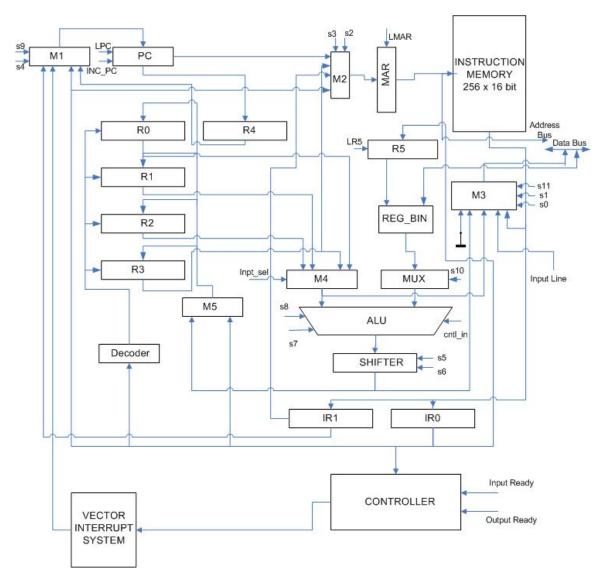

The first phase prototype of the HDCA consisted of 3 Computing Elements [17, 33]. Two of the CEs - CE0 and CE1, were 16-bit unpipelined memory-register computer architectures, developed as part of the graduate program coursework and as shown in Figure 2.8. In order to show the heterogeneous nature of the system, a special purpose simple pipelined divider CE was also included in the system. The instruction set for CE0 and CE1 is shown in Table 2.1. Both processors have full functionality: a register set in the data path available to the assembly language programmer, a Hardware Vectored Priority Interrupt System (HVPIS) in addition to other functional units such as Arithmetic and Logical Unit (ALU), a Program Counter (PC) and simple Input/Output (I/O) structure. The instruction set listed in table 2.1 was felt to be sufficient to test the functionality of the second phase model of the HDCA. The processor used for CE2 is a simple pipelined divider circuit. This divider can be considered as a special purpose circuit for a system that needs additional computational power and it allows the singlechip multiprocessor prototype system to be heterogeneous. Each CE, as shown in Figure 2.8, has its controller, which includes a multifunctional queue [16,17,33], a Lookup Table (LUT) and an Interface Controller (see Figure 2.9 for the CE controller). Additionally, as part of work done to build the second phase model, two additional Computing Elements were added to the HDCA system. In order to execute complex and non-complex applications, the need for a special purpose multiplier CE was felt. Often, in DSP and Image Processing applications, multiplication is an important aspect of any operation and hence a new special purpose multiplier was added to the HDCA system. A fifth CE will be added to this HDCA system as part of this work and it will be architecturally the same as the Memory-Register CEs of Figure 2.8., but it is unique in the sense that it does not come into picture under normal conditions. Under normal operating conditions, when the Queues of the existing CEs have not built up to their threshold, this CE acts as a stand-by CE monitoring the queue depth of either of the two CEs. Once the queue depth of both of the operational CEs exceeds the pre-programmed threshold, this additional CE is dynamically configured, on the fly, to initiate and start accepting the tokens from that point on and executing them. This concept has been explained in detail in Chapter 5 along with the design decisions that have been made. Implentation of this concept results

in node-level dynamic capability of the architecture. Once the queue depth goes reduces below the pre-programmed threshold, the CE goes back to its sensing state where it silently monitors the queue depth of either CEs.

| No. | Instruction            | Action                                           |

|-----|------------------------|--------------------------------------------------|

| 0   | Mem [Ri] <= input      | Input data to Mem [Ri], $i = 0,3$                |

| 1   | Add RD, Mem [Ri]       | $RD \le Mem [Ri] + RD, i = 0,3, D = 0,3,$        |

|     |                        | D≠i                                              |

| 2   | Store Mem [Ri], RD     | Mem [Ri] $\leq$ RD, i = 0,3, D = 0,3, D $\neq$ i |

| 3   | Jump address immediate | PC <= Address immediate                          |

| 4   | Branch RD, Mem [Ri],   | If RD >= Mem [Ri], then PC <= Address, i =       |

|     | Address                | 0,3, D = 0,3, D≠i                                |

| 5   | Sub Mem [Ri], RD       | Mem [Ri] <= Mem [Ri] – RD, i = 0,3, D =          |

|     |                        | 0,3, D≠i                                         |

| 6   | Output <= Mem [Ri]     | Output data Mem [Ri], $i = 0,3$                  |

| 7   | Load RD, Mem [Ri]      | $RD \le Mem [Ri], i = 0,3, D = 0,3, D \neq i$    |

| 8   | Branch out loop        | If RD = Mem [Ri], then branch out Process flow   |

|     |                        | loop, $i = 0,3$ , $D = 0,3$ , $D \neq i$         |

| 9   | Load Ri, immediate     | Ri <= Immediate                                  |

| А   | Increment Ri           | $Ri \le Ri + 1, i = 0,3$                         |

| В   | Add Ri, immediate      | $Ri \le Ri + immediate, i = 0,3$                 |

| С   | Sub Ri, immediate      | $Ri \le Ri - immediate, i = 0,3$                 |

Table 2.1, Instruction Set of the Memory-Register CEs

Additionally, this new CE can also be configured with proper programming to act as a back-up CE in case any node fails due to unforeseen circumstances. This would help in producing a fault tolerant model of the system, consistent with the idea presented in [3]. Most of the instructions represented by Table 2.1 are self explanatory. The special instruction "Branch out Loop" is used to exit from applications that involve looping and it is necessary to exit from the loop when a predefined condition has been met. This is further explained in the CE controller module.

Figure 2.8 : Memory Register Computer Architecture - CE0 and CE1

The HVPIS and IR1 are not used in the cirtual prototype testing of the HDCA reported in this thesis. These units are though included in the design and VHDL description of the CE and can be used whenever desired.

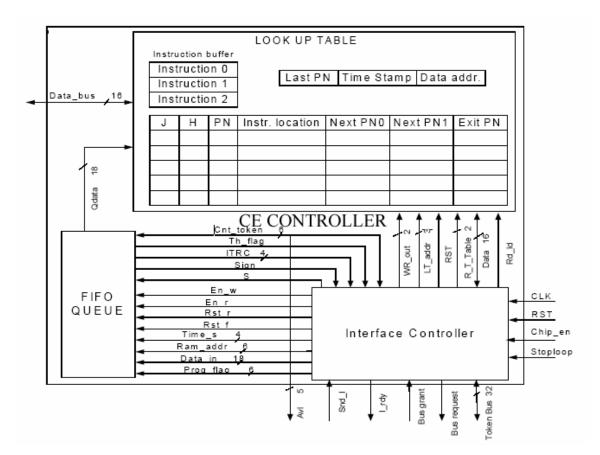

#### 2.5 The CE Controller

Figure 2.9 : CE controller for 16-bit unpipelined Memory Register CEs

Each Memory register CE architecture has a controller associated with the CE as shown in Figure 2.9. It basically consists of an Interface Controller, the FIFO queue and a Look up Table (LUT). Some of these components have been described earlier in this chapter. The LUT contains all the information necessary to communicate with a CE. During system initialization, the LUT is loaded with information about all of the processes that a given CE can execute. It consists of process number identifier (PN), the address of the Process Number's first instruction in memory (Instruction Location), follow-on process numbers (PN0, PN1), a hold bit (H) and a join bit (J). Since the only communication between CE's is tokens, any CE must know what the next processes are in order to issue the correct follow-on token. This explains the reason for having the follow on process numbers in the LUT. The functionality of Hold and Join bits come into picture when the process flow graph is non-linear, or in other words, has forks and joins as explained earlier. The Hold bit is set to logic one if the follow-on process to be executed is a member of a Join operation. The Join bit when set to logic one indicates that the Process to be run is a join process and thus will have more than one token associated with it in the Queue. To further explain, let's take a simple example. Say process P1 forks

into two follow on processes, P2 and P3 and let's say these processes finally join at P4 as illustrated in Fig.2.10.

Figure 2.10 : Explanation of Hold and Join Concept

The initial HDCA design [17,33] was limited to two follow on processes but in the work done here it will been shown that the design can be modified to incorporate a multiple fork where a single process has more than two successors. Also the number of processes that could be held in the LUT is limited to 18 processes. This is, however, a figure that can be changed and is a function of the underlying technology to which the design is being synthesized and the complexity of the application. Once the LUT is loaded, it works by receiving a token from the Queue. It compares this token's Process Number with the LUT entries. In the event of a match, its instruction buffers are then filled with the Instruction address and the data address. This helps the CE decide what is to be done. An example of these instructions is as follows. Instruction '0' tells the CE to load the data address into a register. If this is a join operation, then Instruction Two loads data address two into a register. Instruction one tells the CE to jump to the address of its first instruction. The LUT sends these instructions when the CE indicates over the 'Finished' input that it is done executing the current process and is ready to receive information about the next process that is to be executed. This is explained more vividly in Chapter 6, when applications are discussed. When the CE finishes a previously running Process, it signals 'Finished' and thus the LUT prepares to send the follow-on token to the PRT mapper, it places the finished Process' information in a buffer (Last PN, Time Stamp, Data Address). Then it compares the Process Number with the entries in its table. Once a match is found, it sends the data location along with the Hold Field bit, and the follow-on Process Number(s) to the Interface Controller, which sends the token(s) out on the Token Bus.

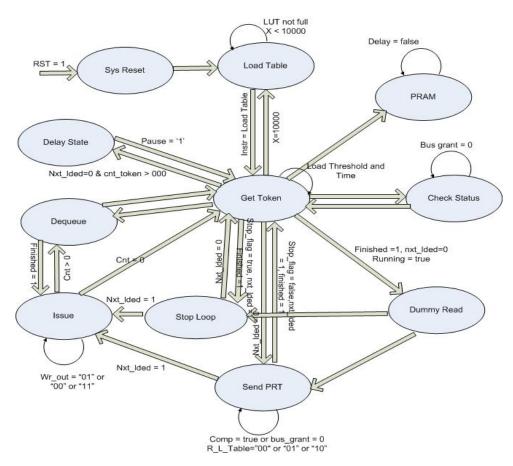

## 2.6 Interface Controller

The Interface Controller of Figure 2.11 provides the logic to integrate the LUT, the Queue, and the CE. One of the functions of the Interface Controller is to receive Tokens from the Token Bus and transmit output Tokens. On the receive side, it has the previously described FIFO buffer to temporarily hold fifteen inbound tokens. Besides this simple task, the Interface Controller is a State Machine for the control of the LUT and Queue. The State Diagram for the Interface Controller is found in Figure 2.11

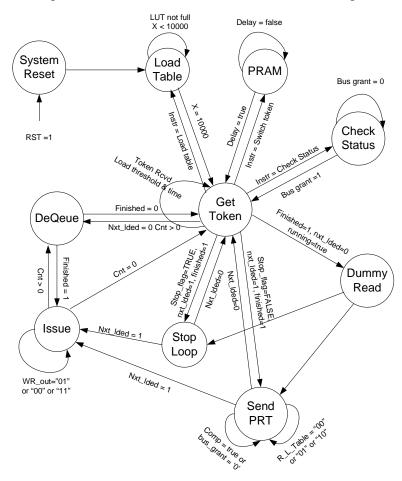

Figure 2.11 : Interface Controller State Machine for the CE

The controller starts functioning, as soon as the reset signal goes active low. The first state, after "System Reset" is the "Load Table" state. It remains in this state until the

Look up Table described above has all its entries populated. How many entries are needed to fill up the Look up Table - depends on the topology of the process flow graph. This concept is thoroughly explained in Chapter 6 where applications are described. Once the Look up Table is full, the controller moves to the "Get Token" state. Here the controller waits for properly addressed tokens to arrive from the Token Bus. The first thing the controller checks is if a process previously sent to the CE has completed executing. If it has, and another token is available in the instruction buffers for execution (Next\_Loaded is true), then the state switches to Send PRT. If no token is ready for executing a process and a token is in the queue, the controller moves to the "De-Queue" state. If none of those conditions are met, then the inbound token is parsed to determine what type of command it contains. The state will then move to "Check Status", "Load Table", "PRAM", or it will loop back to Get Token. The Get Token State is the Default State when the system is waiting for a token arrival or Process completion.

The "De-Queue" state simply removes a token from the Queue and passes it to the LUT. The state then moves to "Get Token" if the CE is busy (not Finished) or to Issue if the CE is ready for another Process (Finished). In the Issue state, the LUT records the last Process executed, if any, and issues a new process to the CE. After issuing the Process, if another token is in the Queue, it will go to the "De-Queue" State to keep the LUTs instruction buffer full. Otherwise, it will go back to the Default State.

The "Dummy Read" state is only used in the case where a Process completes and there is no token available in the instruction buffer to send to the CE. The state allows the LUT to record the finished Process' information without issuing another Process. This state always transitions to the Send PRT State. In the applications described here, the CEs are fairly efficient and hence the system never goes into this state.

The "Send PRT" state transmits the follow-on tokens of a completed process from the LUT to the Interface Controller. The Interface Controller then negotiates for the Token Bus and submits the tokens to the PRT mapper. Upon completion of the send, if another token is loaded in the LUT's instruction buffer, the state moves to Issue. If a token is not loaded the state returns to the "Get Token" state. The "Check Status" and "PRAM" states are for the Multifunctional Queue. The PRAM is used to aid in the swap function. The instructions place the Queue in the swap mode and then provide the swap address locations from where tokens are to be swapped. Finally the Queue is removed from the swap mode when this is accomplished.

The HDCA can not start functioning until it has received all the information it needs to start system operation. This information is in essence a set of Tokens. There are different set of Token formats for the HDCA, each performing a unique function. The token names were chosen sensibly to give a good idea of what the function of the token was. Table 2.2 represents the tokens that could be used in the HDCA system. Though not all Token formats are used in the work reported here, some of the Token formats are needed for special functionalities incorporated in the core components that were designed earlier.

Table 2.2, Token Formats Available for the HDCA System

# a. Table Load Token

| 1    | Physical<br>Location | 11111 | XXXXXXXXX | Join Field | Hold Field | Instruction<br>Address |

|------|----------------------|-------|-----------|------------|------------|------------------------|

| 31 3 | 30 24                | 23 19 | 18 1      | 0 9        | 8 7        | 0                      |

b. Table Input Token

| 1  | Physical | 11   | 110 | Process Num | ber | Next P | N0 | Nex | kt PN1 | XXX | X |

|----|----------|------|-----|-------------|-----|--------|----|-----|--------|-----|---|

|    | Location |      |     | (PN)        |     |        |    |     |        |     |   |

| 31 | 30 2-    | 1 23 | 19  | 18          | 14  | 13     | 9  | 8   | 43     | (   | 0 |

c. Load Threshold Token

| 1  | Physical Location | 11101   | XXXXXXXXX | Time_S | Threshold |

|----|-------------------|---------|-----------|--------|-----------|

| 31 | 30 24 2           | 23 19 1 | 18 10 9   | 65     | 0         |

| d. | Switch | Tokens | Token |

|----|--------|--------|-------|

|    |        |        |       |

| 1  | Physical Location | 11011 | XXXXXXX | Address 2 | Address 1 |

|----|-------------------|-------|---------|-----------|-----------|

| 31 | 30 24 2           | 19 1  | 18 12   | 6         | 5 0       |

|    | 31 30      |        | 24 2  | 23 19  | 18               |             | 0        |

|----|------------|--------|-------|--------|------------------|-------------|----------|

|    | 51 50      |        | 212   | 25 17  | 10               |             | 0        |

|    |            |        | f.    | Send   | l Status Tok     | en          |          |

| 0  | Physical   | 0      | Sign  | ITRC   | Threshold        | XXXXXXXXXXX | XXXXXXXX |

|    | Location   |        |       |        |                  |             |          |

| 31 | 30 24      | 23     | 22    | 21 18  | 17               | 16          | 0        |

|    |            |        |       |        |                  |             |          |

|    |            |        | g.    | Load_P | <b>RT Mapper</b> | Token       |          |

| 1  | PRT Locati | on 110 | 010 X | XXX    | Physical         | Process     | RAM      |

|    |            |        |       |        | Location         | Number      | Address  |

| 31 | 30         | 24 23  | 19 18 | 15 14  | 8                | 7 3 2       | 2 0      |

|    |            |        |       |        |                  |             |          |

### e. Read Status Token

11100

Physical Location

1

### h. Command Token

| Hold Field | Physical<br>Location | Time<br>Stamp | Process<br>Number | XXXXXXXX | Data<br>Address |

|------------|----------------------|---------------|-------------------|----------|-----------------|

| 31         | 30 24                | 23 21         | 20 16             | 15 8     | 7 0             |

Out of these possible token formats, Token formats a, b, g and h were used for all applications. The "Load Threshold" token was used in the application for demonstrating dynamic node level reconfigurability. The tokens that are used to initialize the Look up Table are the "Table Load" and "Table Input" tokens. These tokens, in essence, contain information about the processes different CEs could possibly execute. They provide information on the current process number, the following process numbers for the successor nodes, the address of the process's first instruction in local memory, a Hold and a Join field. The remaining four tokens are used to access the advanced functionality of the multifunctional queue if required. The "Load Threshold Token" identifies the queue for a CE by the "physical location" of the CE and programs the threshold for the queue and the time period (Time\_s) desired for sampling the input and output rate. The "Switch Tokens" token is utilized to swap tokens in the queue by address as previously mentioned in this chapter. The "Read Status Token" and "Send Status Token" are designed to obtain status information of a queue. The "Read Status Token" is sent by the operating system to a CE directing it to provide status information. The "Send Status Token" is like an "ack" containing the Input Token Rate Change (ITRC) over the specified time, its sign (positive and negative) and a flag to indicate whether or not the threshold has been crossed for the

queue. "Load PRT" token is used to initialize the RAM in the PRT mapper upon system startup. It contains information about the physical location (address) of the CE, the process number that CE holds, and the RAM address within PRT to load this information. This token is primarily responsible for starting application execution.

Each CE has a unique address which distinguishes it from the other CEs. Table 2.3 represents the physical addresses of the CEs as used in the current HDCA. These addresses are essential for proper functionality of the token bus with the set of tokens described above. The work done in [17] had 4 unique locations. However additional CEs were added as part of the second phase modeling explained in the next chapter which now leads to 6 unique locations.

| Element      | Physical Location |

|--------------|-------------------|

| PRT mapper   | 0000001           |

| CE0(MR16)    | 0000011           |

| CE1(MR16)    | 0000010           |

| CE2(DIV)     | 0000100           |

| CE3(MULT)    | 0000101           |

| CE4(STANDBY) | 0000110           |

Table 2.3, Physical Addresses of the Modules in the Prototype

Beside each CE, in parenthesis, is a brief description of its features. CEs 0, 1 and 4 are the 16-bit unpipelined memory register computer architectures. CE2 and CE3 are the special purpose multiplier and divider CEs. CE4 is a STANDBY CE (see Figure 2.8); it is the CE that will be used to show the dynamic nature of the system by automatically being configured and re-configured as needed when the queue depth increases beyond a particular threshold as determined by the Operating System.

### 2.7 The Multiplier and the Divider CEs

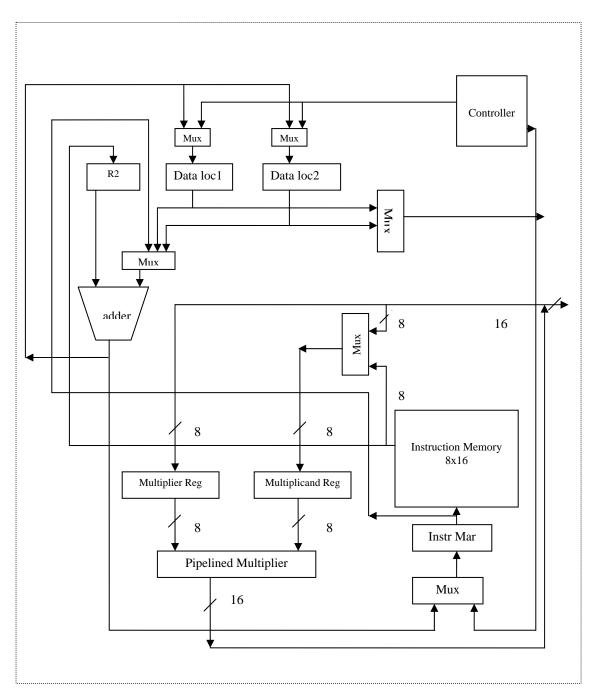

The Multiplier and divider CEs are special purpose CEs. The Divider is a simple core-generated pipelined divider. It uses unsigned arithmetic. Figure 2.12 shows the divider CE used in the HDCA system.

DIVIDER CE

Figure 2.12 : Divider CE. To be CE2 in the Latest Version HDCA

This processor is capable of receiving the data locations from the CE Controller and then fetching its operands. The processor first loads one or two data location addresses into registers (Data Loc 1 and Data Loc 2). Then, the start instruction is received from the CE Controller. This provides it the first address in Instruction Memory to access. The first Instruction provides an offset for the Data Locations if necessary. The system then fetches the divisor and places it in a register (R1). If there is a valid address in the Data Loc 2 Register, the divisor comes from the shared HDCA Data Memory; otherwise it is

loaded from the Instruction Memory. Next, the dividend is fetched from Data Memory and placed in a register (R0). When both operands are loaded the division operation begins. Twenty clock cycles later, the result is output and placed in output registers (Result and Remainder). The results are then output to the shared HDCA Data Memory. Lastly, the processor reverts to address zero and awaits the next process.

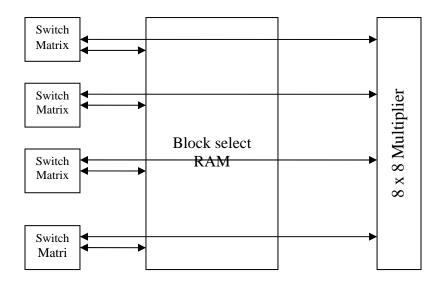

The multiplier CE of Figure 2.14 is similar to the Divider CE but is much faster. When a choice was to be made between the different types of algorithms that could be used to implement the multiplier, careful analysis was needed to determine which approach was the best out of the various methods of implementation available such as the well known Booth's algorithm. The Xilinx Virtex 2 FPGA multiplier contains hardware multipliers. In order to limit the usage of LUT and based on power considerations, the style of coding used was such that the inferred multipliers used the coregen Intellectual Property (IP) multipliers from the Virtex 2 chip. Besides, they are ideally suited for performing operations like Digital Down Converting (DDC) and Convolutions which falls under some typical applications that would be run on this architecture. These multipliers are associated with a block RAM as shown in Figure 2.13. A few important rules need to be kept in mind. When multiplying, the width of the result would be the sum of the widths of the two inputs. Also signed data representations often use the top bit (MSB) to represent the information about the sign. For example, for a positive number the MSB is always 0 and for a negative number its always 1. When working with signed data, it is important to maintain sign information. The multiplier used here infers a pipelined multiplier that is faster that the unpipelined version. Also, since the data bus width is 16 bits for the entire system, the inputs to the multiplier cannot be greater than 8 bits each. The coregen multipliers have been found to produce the same results in terms of resource usage as instantiated multipliers. However instantiated versions were used in this code so that additional ports and signals could be added to the multiplier if needed and the design could be scaled in the future.

Figure 2.13: Core Multipliers associated with Block RAMs

A performance of up to 200 MHz + can be inferred using this core multiplier as mentioned in [34]. Figure 2.14 shows a block diagram of a typical multiplier CE in the system. Since the multiplier is pipelined and the inferred multiplier is implemented on the basis of Look up Tables in the chip, the result is obtained in one clock cycle. Using the current design, the programmer is forced to utilize relative addressing for accessing data items. Since the original data address provided by the Operating System is passed along with each token, there is no way to use a different addressing scheme to access data items. This certainly is a system limitation but works well for small systems.

Figure 2.14 : Multiplier CE used in the HDCA

All these components as described above, when put together along with the associated I/O structure will form the latest version of the HDCA system addressed and will be shown in the next chapter.

# **Chapter Three Design Methodology and Modifications**

### **3.1 Design Methodology**

While designing the second and latest phase model of the HDCA, a "Top Down" design system was utilized. In this approach, the problem is first defined and then split into smaller manageable components. These smaller components are then developed, tested and integrated into the main system. This approach allows the designer to develop the components in a simple, modular fashion while maintaining focus on the system's requirements.

### **3.1.1 Problem Definition**

The first step in accomplishing the previously presented goals was to analyze the background information and then define the problem statement. In this case, the initial problem was to modify an initial version limited functionality prototype into a model that could be behaviorally simulated. Next, the scope of the project was to design and develop additional processors with their respective controllers, develop complex applications for the system and demonstrate node level reconfigurability for the added standby processors. Next, an additional feature was to be added wherein, the HDCA could fork to more than two processes. An additional goal was to integrate the crossbar Interconnect network switch developed in [32], into the system and the existing devices re-configured to counter the latency introduced by the switch. The Operating System, processor level re-configurability and replacing the addressing system would be left for a future third phase model where an actual working hardware prototype would be built.

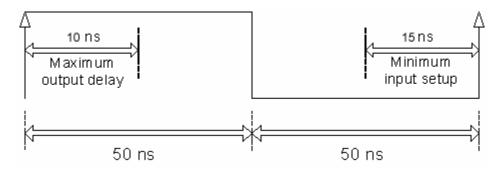

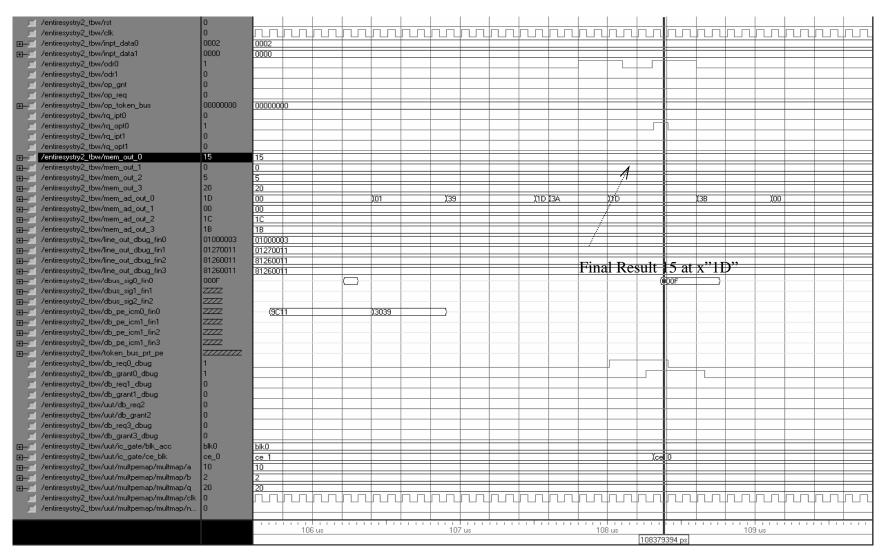

#### **3.1.2 Requirements definition**