University of Kentucky UKnowledge

University of Kentucky Master's Theses

Graduate School

2004

# AUTOMATED SYNTHESIS OF VIRTUALBLOCKS FOR INTERFACING SYSTEM UNDER TEST

Andrew Hai Liang She University of Kentucky, ahshe0@uky.edu

Right click to open a feedback form in a new tab to let us know how this document benefits you.

#### **Recommended Citation**

She, Andrew Hai Liang, "AUTOMATED SYNTHESIS OF VIRTUALBLOCKS FOR INTERFACING SYSTEM UNDER TEST" (2004). *University of Kentucky Master's Theses*. 251. https://uknowledge.uky.edu/gradschool\_theses/251

This Thesis is brought to you for free and open access by the Graduate School at UKnowledge. It has been accepted for inclusion in University of Kentucky Master's Theses by an authorized administrator of UKnowledge. For more information, please contact UKnowledge@lsv.uky.edu.

#### ABSTRACT OF THESIS

### AUTOMATED SYNTHESIS OF VIRTUALBLOCKS FOR INTERFACING SYSTEM UNDER TEST

In this thesis, I/O signal recognizers, called VIRTUALBLOCKS, are synthesized to interface with a SYSTEM UNDER TEST (SUT). Methods for automated synthesis of virtualblocks allow us to simulate environment interfaces with SUT and also perform fault detection on SUT. Such methods must be able to recognize incoming sequences of signals from SUT, and upon the signal recognition determine the proper outgoing sequences of signals to SUT. We characterize our systems into four distinctive systems: system under test, AUXILIARY SYSTEM, controller and external environment. The auxiliary system is represented as a form of condition system Petri net (virtualblocks) and interacts with SUT along with the interaction among the controller and the external environment. Fault detection is performed by subsystems called DETECTBLOCKS synthesized from the virtualblocks. We present construction procedures for virtualblocks & detectblocks and discuss the notion of LEGALITY and DETECTABILITY. Finally, we illustrate our approach using a model of a scanner control unit.

KEYWORDS: Auxiliary System, Petri Nets, Fault Detection, Condition Systems, System Under Test

Andrew Hai Liang She

12/01/04

### AUTOMATED SYNTHESIS OF VIRTUALBLOCKS FOR INTERFACING SYSTEM UNDER TEST

By Andrew Hai Liang She

> Dr. Larry E. Holloway Director of Thesis.

Dr. Yu-Ming Zhang Director of Graduate Studies.

12/01/04

#### RULES FOR THE USE OF THESES

Unpublished dissertations submitted for the Master's degree and deposited in the University of Kentucky Library are as a rule open for inspection, but are to be used only with due regard to the rights of the authors. Bibliographical references may be noted, but quotations or summaries of parts may be published only with the permission of the author, and with the usual scholarly acknowledgments.

Extensive copying or publication of the thesis in whole or in part also requires the consent of the Dean of the Graduate School of the University of Kentucky.

A library that borrows this thesis for use by its patrons is expected to secure the signature of each user.

Name

<u>Date</u>

THESIS

Andrew Hai Liang She

The Graduate School University of Kentucky 2004

#### AUTOMATED SYNTHESIS OF VIRTUALBLOCKS FOR INTERFACING SYSTEM UNDER TEST

THESIS

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in the College of Engineering at the University of Kentucky

> By Andrew Hai Liang She Lexington, Kentucky

Director: Dr. Lawrence E. Holloway, Professor of Electrical & Computer Engineering, University of Kentucky, Lexington, Kentucky 2004

Copyright © Andrew Hai Liang She 2004

## ACKNOWLEDGMENTS

I thank the Graduate School and the Center for Robotics and Manufacturing Systems at the University of Kentucky for giving me a Kentucky Graduate Scholarship, a research assistantship and unlimited usage of computing, printing, and office facilities all through the process of my master degree studies.

My parents have been given me a lot of love and support throughout my studies in the USA. They have had to live with many years of separation from me while I have been involved in my academic pursuits in the USA.

Finally, I would like to express my sincerest thankfulness to my thesis advisor, Dr. Larry Holloway for giving me this opportunity to work with him. His extraordinary knowledge of the control world has inspired me to do this thesis. Because of his guidance and open mind, I have been able to make my dream come true of completing this master's thesis program.

## TABLE OF CONTENTS

| Acknow    | vledgments                                               | iii  |

|-----------|----------------------------------------------------------|------|

| List of I | Figures                                                  | viii |

| List of I | Files                                                    | ix   |

| Chapter   | r 1 Introduction                                         | 1    |

| 1.1       | Background                                               | 1    |

| 1.2       | Approach                                                 | 5    |

| Chapter   | r 2 Condition Systems                                    | 8    |

| 2.1       | Condition System Languages                               | 9    |

|           | 2.1.1 Descriptive Ordering                               | 11   |

|           | 2.1.2 Observability                                      | 13   |

| 2.2       | Condition System Model                                   | 14   |

| 2.3       | Composition of Condition System Models                   | 19   |

| 2.4       | Condition System Models Modularity                       | 21   |

|           | 2.4.1 Specification Block                                | 21   |

|           | 2.4.2 Achievable Specification Block                     | 23   |

|           | 2.4.3 Composition of Specification Block                 | 24   |

| Chapter   | r 3 Modeling For Interfacing                             | 27   |

| 3.1       | Real and Expected Systems                                | 29   |

| 3.2       | Systems under Modeling for Interfacing Framework         | 30   |

| 3.3       | Fault Detection under Modeling for Interfacing Framework | 34   |

| Chapte    | r 4 Virtualblocks                                        | 36   |

| 4.1       | Legality                                                 | 37   |

| 4.2       | Inputblock                                               | 37   |

| 4.3       | Outputblock                                              | 38   |

| 4.4       | Composition of Inputblocks and Outputblocks              | 40   |

|                                           | 4.4.1  | Sequential Composition of Inputblocks                       | 41   |  |  |  |  |

|-------------------------------------------|--------|-------------------------------------------------------------|------|--|--|--|--|

| 4.5                                       | Algori | ithms                                                       | 43   |  |  |  |  |

|                                           | 4.5.1  | Construction Procedures for Inputblocks                     | 43   |  |  |  |  |

|                                           | 4.5.2  | Construction Procedures for Outputblocks                    | 50   |  |  |  |  |

|                                           | 4.5.3  | Construction Procedures for Virtualblocks                   | 55   |  |  |  |  |

| Chapter 5 Fault Detection of Virtualblock |        |                                                             |      |  |  |  |  |

| 5.1                                       | Fault  |                                                             | 60   |  |  |  |  |

| 5.2                                       | Detec  | tability                                                    | 61   |  |  |  |  |

| 5.3                                       | Detec  | tblock                                                      | 62   |  |  |  |  |

| 5.4                                       | Algori | ithm                                                        | 63   |  |  |  |  |

|                                           | 5.4.1  | Construction Procedures for Detectblocks                    | 63   |  |  |  |  |

|                                           | 5.4.2  | Construction Procedures for Composing Multiple Detectblocks | 69   |  |  |  |  |

|                                           | 5.4.3  | Construction Procedures for Resetting Virtualblock and Dete | ect- |  |  |  |  |

|                                           |        | block                                                       | 72   |  |  |  |  |

| Chapte                                    | r6 Ap  | pplication to Scanner Control Unit                          | 75   |  |  |  |  |

| 6.1                                       | Binary | y Signal                                                    | 77   |  |  |  |  |

| 6.2                                       | Serial | Signal                                                      | 80   |  |  |  |  |

| 6.3                                       | Softw  | are Overview                                                | 83   |  |  |  |  |

| Chapte                                    | r7Co   | onclusion                                                   | 86   |  |  |  |  |

| Bibliog                                   | raphy  |                                                             | 89   |  |  |  |  |

| Vita                                      |        |                                                             | 92   |  |  |  |  |

## LIST OF FIGURES

| 1.1        | Systems within the Methodology                                                                                      | 6             |

|------------|---------------------------------------------------------------------------------------------------------------------|---------------|

| 2.1        | Examples of voltage signal time lines corresponding to the C-sequence $s = (\{a\} \{\neg c\} \{bd\} \{\emptyset\})$ |               |

| 2.2        | $S = ((u_1, v_1, v_2, v_3))$                                                                                        |               |

| 2.2        | unit                                                                                                                |               |

| 2.3        | A simple chart showing some of the structural configurations which are                                              |               |

| 2.3        | allowed and not allowed for condition systems satisfying property deter-                                            |               |

|            | ministic                                                                                                            |               |

| <b>∩</b> ⁄ |                                                                                                                     |               |

| 2.4        | Condition subsystems model for the scanner power, lamp & motor control                                              |               |

| о г        | unit                                                                                                                |               |

| 2.5        |                                                                                                                     |               |

| 26         | of Figure 2.2                                                                                                       |               |

| 2.6        | An example SpecBlock $\mathcal{G}^{SB2}$ for scanner power motor control unit ( $\mathcal{G}^{Sys}$ )               |               |

| 07         | of Figure 2.2                                                                                                       |               |

| 2.7        | An example of Composed SpecBlock SB1 SB2 for scanner power motor                                                    |               |

|            | control unit ( $\mathcal{G}^{Sys}$ ) of Figure 2.2                                                                  | 5             |

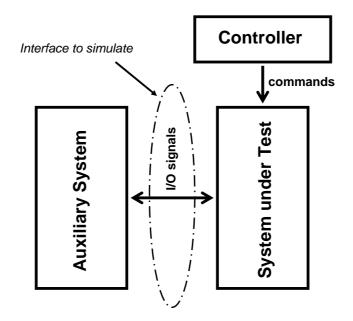

| 3.1        | System interactions among system under test, auxiliary system and con-                                              |               |

|            | troller                                                                                                             | 8             |

| 3.2        | Scheme for Real and Expected System Fault Detection                                                                 | 0             |

| 3.3        | Scheme for General System within the Framework of Modeling for Inter-                                               |               |

|            | facing                                                                                                              | 51            |

| 3.4        | SUT and Auxiliary System Interfacing under Modeling for Interfacing                                                 | г<br><b>Э</b> |

|            | Framework                                                                                                           | 3             |

| 3.5        | Fault Detection on SUT under Modeling for Interfacing Framework . 3                                                 | 85            |

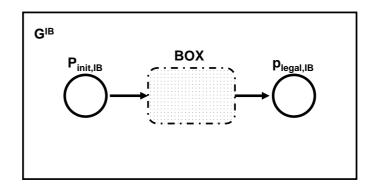

| 4.1        | General Structure of Inputblock                                                                                     | 88            |

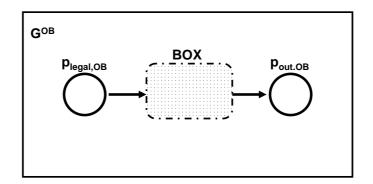

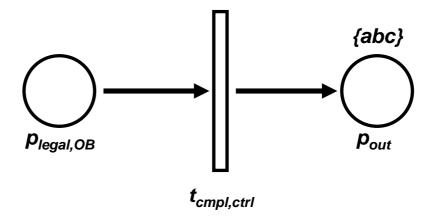

| 4.2        | General Structure of outputblock                                                                                    | 9             |

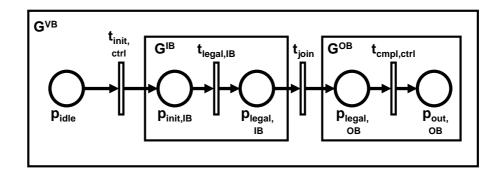

| 4.3        | Example of Virtualblock                                                                                             | 0             |

| 4.4  | Example of Sequential Composition for Two Inputblocks in Virtualbloc              | k  |

|------|-----------------------------------------------------------------------------------|----|

|      | interacts Specblocks with SUT and the Controller                                  | 41 |

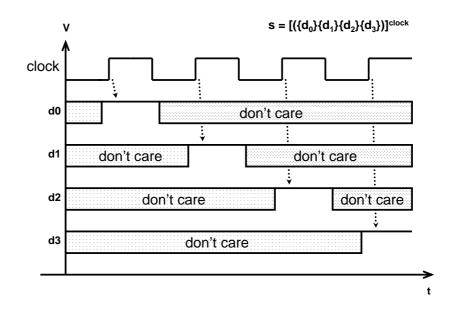

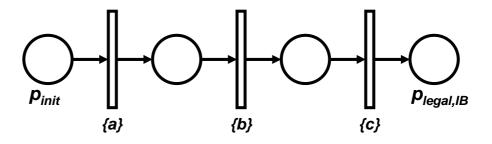

| 4.5  | Example of voltage time line corresponding to C-sequence s                        | _  |

|      | $[(\{d_0\}\{d_1\}\{d_2\}\{d_3\})]^{clock} \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | 44 |

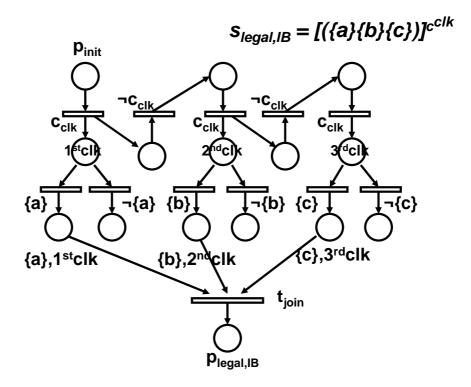

| 4.6  | Condition system model of inputblock for clocked signal                           | 46 |

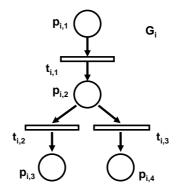

| 4.7  | Figure for net $G_i$                                                              | 46 |

| 4.8  | Algorithm 4.1 An algorithm for construction of inputblock for clocke              | d  |

|      | signal                                                                            | 47 |

| 4.9  | Condition system model of inputblock for non-clocked signal                       | 48 |

| 4.10 | Algorithm 4.2 An algorithm for construction of inputblock for nor                 | 1- |

|      | clocked signal.                                                                   | 49 |

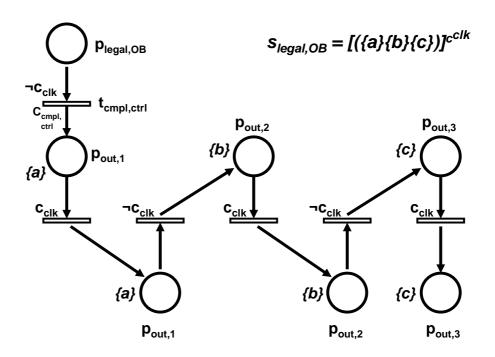

| 4.11 | Condition system model of outputblock for clocked signals                         | 51 |

| 4.12 | Algorithm 4.3 An algorithm for construction of outputblock for clocke             | d  |

|      | signals                                                                           | 52 |

| 4.13 | Condition system model of outputblock for non-clocked signals                     | 53 |

| 4.14 | Algorithm 4.4 An algorithm for construction of outputblock for nor                | 1- |

|      | clocked signals.                                                                  | 54 |

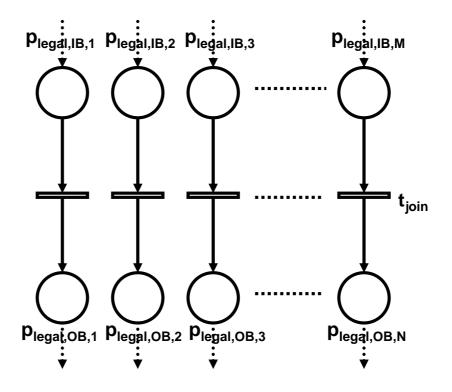

| 4.15 | Condition system model of multiple inputblocks and outputblocks com               | 1- |

|      | position                                                                          | 56 |

| 4.16 | Algorithm 4.5 An algorithm for construction of multiple inputblocks and           | d  |

|      | outputblocks composition.                                                         | 57 |

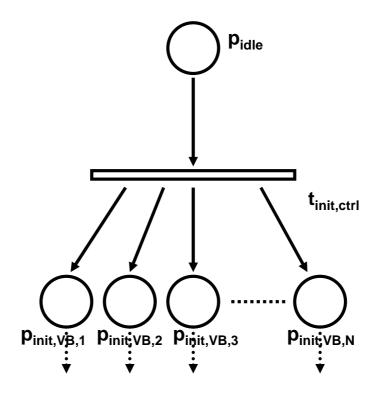

| 4.17 | Condition system model of multiple virtualblocks initiation                       | 58 |

| 4.18 | Algorithm 4.6 An algorithm for construction of multiple virtualblock              | S  |

|      | initiation                                                                        | 59 |

| 5.1  | Scheme for Fault Detection of System Under Test and Auxiliary System              | 61 |

| 5.2  | General Structure of Detectblock                                                  | 63 |

| 5.3  | Condition system model for non-clocked inputblock fault detection .               | 65 |

| 5.4  | <b>Algorithm 5.1</b> An algorithm for non-clocked inputblock fault detection.     | 66 |

| 5.5  | Condition system model for clocked inputblock fault detection                     | 67 |

| 5.6  | Algorithm 5.2 An algorithm for clocked inputblock fault detection.                | 68 |

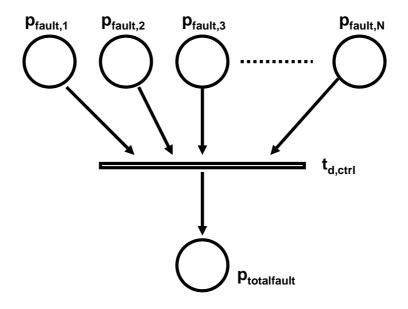

| 5.7  | Condition system model for multiple detectblocks fault detection                  | 70 |

| 5.8  | <b>Algorithm 5.3</b> An algorithm for multiple virtualblock fault detection.      | 71 |

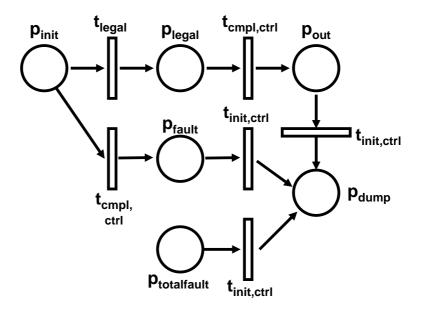

| 5.9  | Condition system model of VirtualBlock with Reset Operation                       | 73 |

| 5.10 | Algorithm 4.7 An algorithm for resetting virtualblock.                            | 74 |

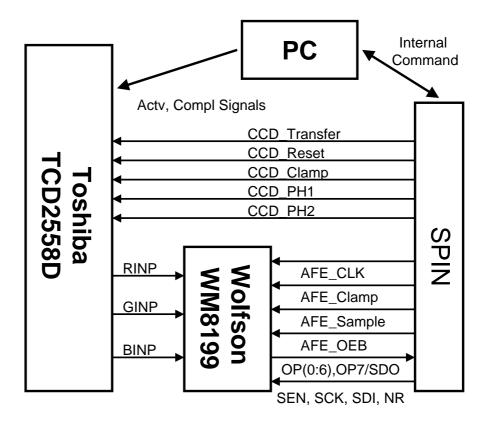

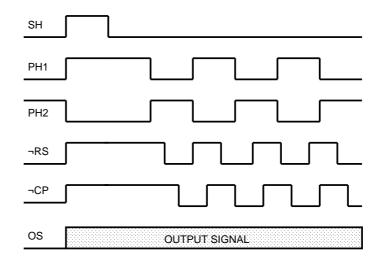

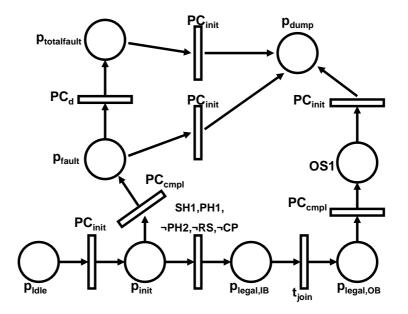

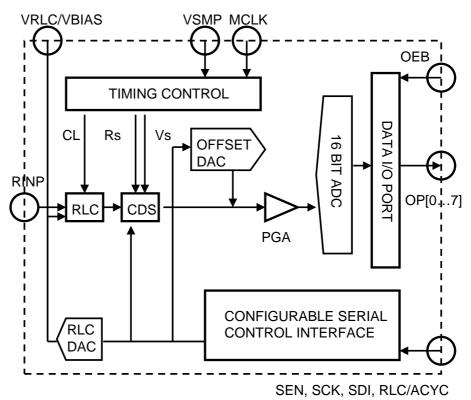

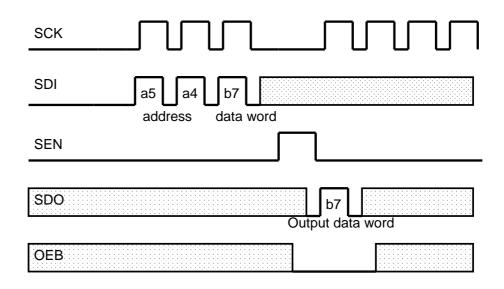

| 6.1 | Figure for Scanner Control Unit Connections                            | 76 |

|-----|------------------------------------------------------------------------|----|

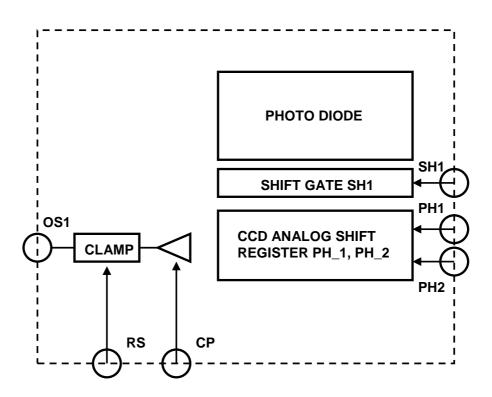

| 6.2 | Figure for Part of TCD2558D                                            | 77 |

| 6.3 | Timing Chart for TCD2558D in Bit Clamp Mode                            | 78 |

| 6.4 | Condition Models for Binary Signal of TCD2558D in Bit Clamp Mode       | 79 |

| 6.5 | Figure for Part of WM8199                                              | 80 |

| 6.6 | Timing Chart for WM8199 in Register Write Back Mode                    | 81 |

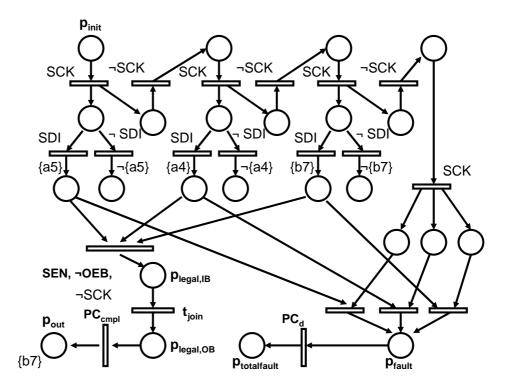

| 6.7 | Condition Models for Serial Signal of Serial Interface: a5,a4          | 82 |

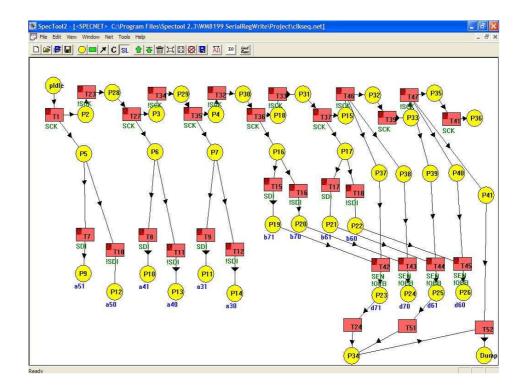

| 6.8 | An example Specnet of scanner control unit in register write back mode | 84 |

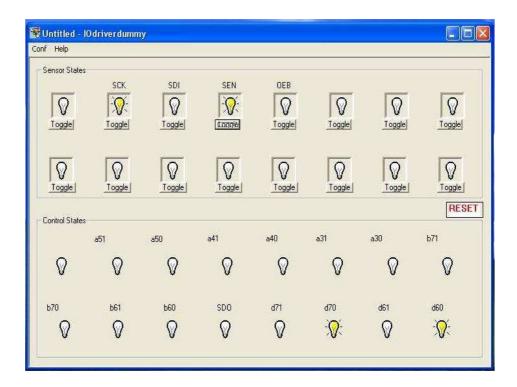

| 6.9 | An example simulator of scanner control unit in register write ba      | ck |

|     | mode                                                                   | 85 |

## LIST OF FILES

AHLSthes.pdf

671 KB

## Chapter 1

## Introduction

In this thesis, we address issues on modeling and fault detection for a class of modeling systems called condition systems Petri nets. We first present the theoretical basis for condition systems. We then establish a concept of modeling for interfacing and define the notion of legality and detectability. The construction procedures for virtualblocks and detectblocks will also be presented in the thesis. We conclude this thesis by illustrating how we apply our modeling and fault detection methodologies into a scanner control unit application.

In the next section, we will present the background information and current issues on modeling and fault detection in the literature of system engineers, control system researchers, computer scientists and reliability engineers. We end this chapter with a discussion of our approach for the methodologies and an overview of the rest of the thesis.

### 1.1 Background

According to system and control theory, there are two prominent features in the very definition of SYSTEM. First, a system consist of interacting components/subsystems, and second a system is associated with a functionality. As system engineers, we are interested in the quantitative analysis of systems and therefore we seek a mathematical model of an actual physical system. There are two distinct physical phenomena to be modeled: physical systems which are modeled by mathematical equations, and physical signals which are modeled by mathematical functions [PP99].

Systems are further categorized into different classes based on their own unique characteristics. In system classifications, systems can generally be classified into static systems and dynamic systems. A static system is a system where output is in-

dependent of past values of input, and whereas a dynamic system is a system where output determination generally requires "memory" of input history. From dynamic systems, systems can be further classified depending on their stationarity (timevarying, time-invariant), linearity (linear, nonlinear), state space (continuous, discrete), state transition mechanism (time-driven, event-driven), predictability (deterministic, stochastic) and time sample path (continuous, discrete). A detailed description of those system classifications can be found in [G85].

Historically, scientists and engineers have concentrated on studying natural phenomena which are well modeled by laws of physics, chemistry, astronomy and other physical sciences. So we typically encounter with quantities such as velocity and acceleration of a solid particle, temperature rates of fluids and gases, gravity force of a planet and etc. All of these quantities are considered "continuous variables" because the state space of these variables are both continuous and comprised of real number. Based on these system characteristics, mathematical techniques such as calculus had been developed to perform system modeling. To use these mathematical models, there are two key properties that systems must satisfy: state space is a continuum and the state transition mechanism is time-driven. This class of systems is also referred as CONTINUOUS-VARIABLE DYNAMIC SYSTEMS (CVDS).

But nowadays, we encounter systems that are inefficient to be modeled mathematically by continuous variables. First of all, state space for such systems are "discrete", typically involving integer numbers. And second, their state transition mechanism depends on instantaneous "events". Such systems include computer systems, communication systems and manufacturing systems. Based on this fact, a class of dynamic systems: Discrete Event Dynamic Systems, or just DISCRETE EVENT SYSTEMS (DES) is being introduced. Discrete event systems are systems whose state space are discrete and state changes can only occur as a result of asynchronously occurring instantaneous events over time. There are basically three levels of abstraction in DES: Logical (untimed), Timed and Timed Stochastic. The choice of the appropriate level of abstraction depends on the objective of the analysis.

As for modeling formalism in discrete event systems, two major formalisms are AUTOMATA and PETRI NET [KG95],[MA98],[ZV99],[ZD93],[E03]. Each of these formalisms have their own unique properties and advantageous over the issues of concurrency, modularity, state explosion and decidability. A detailed comparison of Petri nets and automata can be found in [CL99].

Detection of system failure plays a crucial role in protecting human life and improving the overall performance of industrial processes through reducing the risk of product failure and time to market pressure. Fault Diagnosis has been the subject of extensive research among various research communities due to the fact that the swift evolution of computing, communication and industrial technologies in the era of information revolution has brought the proliferation of new dynamic systems which is often highly complex and gigantic. Thus the increasing complexity in technological systems have necessitated the development of systematic methods for accurate and reliable fault detection system.

First of all, we will review the concept of "FAULT". By reading through the literature in the field of fault diagnosis, one can easily discover that the terminology of fault in this field is not consistent. In [HA02], fault is the inconsistency of system observation with the expected modeled behaviors. Fault on the other hand is considered to be an unobservable event in [SSL96]. Fault in [HCJK03] represents a normal occurrence or an inherent characteristic of system which is inevitable in the existing industrial environment. According to SAFEPROCESS Technical committee of control engineering society, there are distinctions among the very definition of fault, failure, malfunction, error, disturbance and etc. For example, fault is defined as an unpermitted deviation of at least one characteristic property or parameter of the system from the acceptable, usual or standard condition. Failure, "a permanent interruption of a system's ability to perform a required function under specified operating conditions". Error, "a deviation between measured or computed value of an output variable and its true or theoretically correct one". Symptom, "a change of an observable quantity from normal behavior". More definitions and terminologies can be found in nomenclature section of [SFP03].

Despite the deviation in the terminology of fault among different researchers, the term "FAULT DIAGNOSIS" is also being treated differently. While in [SSL95] the authors define failure diagnosis as the detection of failure events and identification of the type of failure events through the record of observable events, in [J04] the author distinguishes the definition of fault diagnosis with different meanings by defining fault detection as the determination that the system behavior is different from allowed behavior and fault diagnosis as localizing or identifying the fault.

The issues of fault diagnosis are well explored problems in reliability engineering, computer science and control system research, in particularly discrete event system. Fault diagnosis using fault tree analysis has been studied in detail by reliability engineers. The analysis starts by considering an overall failure event and working down the tree to identify the roots/parts of failure [O'C81]. Expert systems and model based reasoning schemes for diagnosis have been proposed by computer scientists. Expert systems are generally being applied in the case when it is difficult to design and obtain a model for a particular system.

In addition to MODEL-FREE methods of expert systems from computer scientists, quantitative-analytical model based methods have been extensively used by control system researchers. In MODEL-BASED fault detection, a traditional approach to fault detection is based on hardware or physical redundancy methods which require the use of multiple sensors and actuators to measure and control a particular variable. A typical voting technique is then applied to the hardware redundant system to decide whether a system fault has occurred. One of the main problems of the traditional hardware redundancy methods is the extra cost incurred from the use of multiple redundant hardware in the system. Due to the conflict between adding extra cost and reliability, the analytical or functional redundancy methods have gradually replaced this traditional approach.

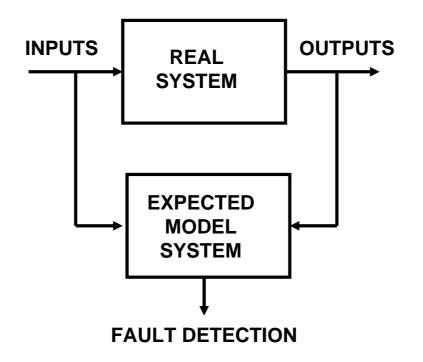

In the analytical redundancy scheme, a mathematical model system will be obtained from an actual physical system/plant. Input variables will then be applied into the system models and actual system. The output variables from these systems will be gathered and compared. Ideally the system behavior of model system should mimic the actual system. The difference generated from the comparison of variables will be called a symptom or residual signal. If the system is operating normally then the residual signal should be zero. Thus the residual signal is used to determine whether a fault has occurred or not. These model-based diagnosis schemes rely on continuous-variable models such as differential and difference equations. Examples of the methodologies include observer-based approaches, parameter estimation and parity vector methods. The observer-based methods work by generating residuals for output variables with fixed parametric models. Fixed parametric or non parametric models are used under parity equations method and adaptive nonparametric or parametric models are used under parity equations method and methodology [SFP03].

In [ZKW03], the authors state that for the purpose of only detecting and diagnosing some particular unique failure, detailed continuous-variable models as in analytical redundancy schemes are often unnecessary. Under these conditions, discrete event system models are usually sufficient as system models in terms of information integrity and usually provide a more convenient way to model due to the nature of discrete systems comparing to continuous systems. DES techniques in fault detection generally require the use of models to model faulty behaviors and then use a form of detector system to determine a proper detection from a given set of observed events.

### 1.2 Approach

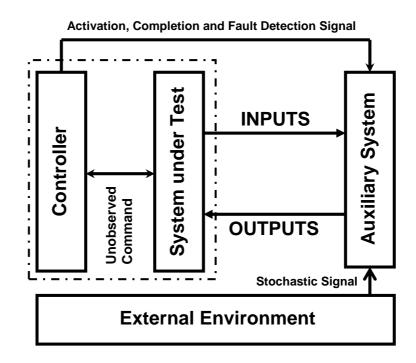

In this thesis, there are two salient issues to be tackled: modeling & fault detection of system. On the modeling issue, the goal of our system modeling is to simulate the auxiliary system which interfaces with SUT. We begin our modeling approach by first analyzing the details and properties of our given systems which mainly consist of system under test, auxiliary system and the controller. Next from our analysis, we will then determine the appropriate modeling formalism and methodology for our given systems. In terms of modeling formalism, we will use condition system Petri net models as our systems modeling formalism. Condition systems are a form of Petri net where systems are composed of subsystems which interact through condition signals. The advantages of using condition system Petri net will be discussed in the following chapter. The auxiliary system modeling methodologies are relied on the automated synthesis of virtualblocks which capable of recognizing input signals from SUT and providing appropriate output signals to SUT. Virtualblocks under our modeling methodology are designed to recognize and output two different type of signals from SUT which are either clocked signals or non-clocked signals.

As for fault detection, we will specifically focus on model-based OFFLINE PAS-SIVE fault detection only. This means that our methodologies involve modeling of systems and fault detection systems that are derived from auxiliary system before the given systems are on the line of work. Our methodologies also do not use any test inputs to detect system failure. In our approach, a fault, failure or any other faulty terms will be treated the same and the term is defined as an inconsistency between observed system behavior from system under test with the expected system behavior of auxiliary system. Fault detection will be defined as the determination that the system under test is not behaving as expected according to the model of

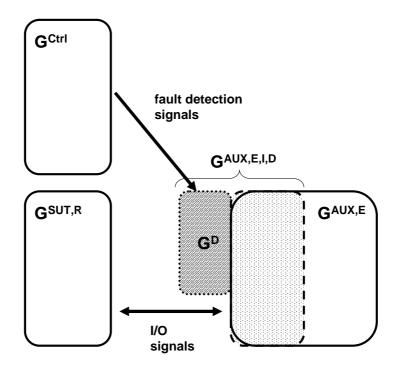

Fault detection signals

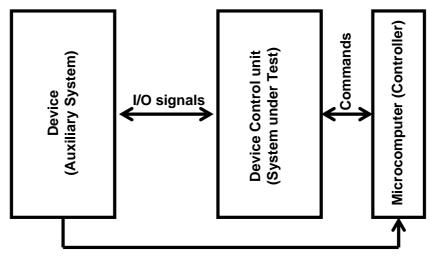

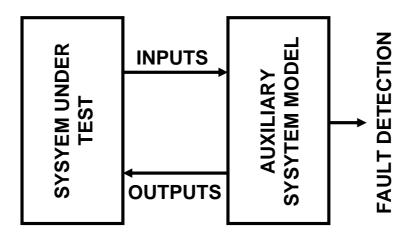

Figure 1.1: Systems within the Methodology

the auxiliary system. In addition, our approaches vary in the respect that we do not require the modeling of fault and thus drastically simplify the modeling process. Our fault detection methodologies rely on detectblocks which are synthesized from virtualblocks. Detectblocks are responsible for detecting whether a given sequences of signals are recognizable by virtualblocks. If virtualblocks are unable to recognize the signals then detectblocks will issue a fault detection signal.

In general, systems considered within the thesis consist of a physical device, device's control unit and a microcomputer. The physical device interacts with its control unit through a common signal interface. The task of the microcomputer is to control both the device and device's control unit and determine their correct system operations. Such physical system design testing has several disadvantages in term of flexibility and observability. It is impractical to use a real system in design testing due to the time, cost and future design constraint impose on it. From these disadvantages, we are motivated to develop a systematic methodology which utilizes software model in system design testing. The main goal of the methodology is to create a system model out of the physical device. The system model of the device will not only provide a virtual system to the device's control unit but also perform fault detection on the control unit. Initially we intend to design a complete model from the physical device. During the modeling process, we encounter several

modeling issues such as insufficient system information and the existence of CVDS environment within the system components where we are unable to obtain a complete model from the device. Due to these issues, we decided to create a model to simulate the interface between device's control unit and physical device instead of a complete model. To achieve these goals, there are two main tasks for the device model: 1. Responds to control unit's excitations with appropriate responses and 2. Detects fault among control unit's excitations. The device model will be modeled and simulated in a modular approach. Such modular approach allows the system to be modeled within the Spectool (a type of control synthesis software tool) framework which will implement automated synthesis of software code for the device model. In addition, it will also permit the performance of formal model analysis in future research. Under our methodology framework, device's control unit will be denoted as system under test (SUT) and the device will be denoted as auxiliary system. Microcomputer will be considered as a controller.

The thesis is organized as follows. In chapter 2, we present the background information of condition system languages & model and condition subsystem models composition & modularity. We will define the concept of modeling for interfacing in chapter 3, and in chapter 4 we present the notion of legality, virtualblocks and also construction procedures for virtualblocks. In chapter 5 the notion of detectability, detectblocks and construction procedures for detectblocks are illustrated. Applications for our modeling and fault detection methodologies will be illustrated in chapter 6. Finally, chapter 7 will be our thesis conclusion.

## Chapter 2

## **Condition Systems**

We present our approaches for modeling & fault detection method which rely on a form of modeling formalism namely, CONDITION SYSTEM. Condition system is a form of Petri net modeling formalism with explicit inputs and outputs called CONDITION SIGNALS. These explicit I/O features of the system allow us to represent a system as a collection of subsystems which interact through condition signals. The condition system framework is a subset of the condition/event models developed by Sreenivas and Krogh where there are two classes of input output signals for a C/E system: condition signals and event signals [SK91].

One of the main advantages of using condition system Petri nets is the ability to avoid state space problem in modeling of large and complex systems. With event communication(automata), the traditional DES approach, modeling of a huge sophisticated system requires synchronous composition of subsystem models which will lead to state explosion. Modeling formalisms emphasizing state communication such as condition systems can easily overcome this issue. The well defined notions of input and output in condition system framework consequently allow the system model to exhibit clear cause & effect relationships. The dynamics within the subsystems can be defined independent of each others due to these well defined interfaces, and this would simplify the system model construction by allowing the reuse of subsystem models.

This chapter is presented for the purpose of providing background knowledge on condition systems which is required for the understanding of later chapters. The chapter is organized into four sections. In the first section of the chapter, we will define the condition system languages. We then present the model of condition system in section 2.2. In section 2.3, we discuss about the composition of condition system models. In the last section, we present the modularity of condition system models by introducing a special kind of condition system, Specification Block.

### 2.1 Condition System Languages

In this section, we introduce notions and notations of the languages generated by condition systems found in [HA98a], [HA98b], [HGSA00] & [HA02]. The systems that we consider interact with each other and their external environment through conditions. A condition is a signal that either has value "TRUE", or "FALSE". A condition with a "true" value would mean that the particular condition is valid and vice versa for the condition with "false" value. Let *AllC* be the universe of all conditions, such that for each condition c in *AllC*, there also exists a negated condition denoted  $\neg c$ , where  $\neg(\neg c) = c$ . Such notation of negation will contribute to a form of condition signal property: CONTRADICT; where a condition signal c is said to be contradict to condition signal  $\neg c$ . We will define TrueC as set of conditions (C) where their condition values are "true". Therefore  $\neg$ TrueC is defined as set of conditions (C) at a given time where their condition values are "false". Also note that condition  $\emptyset$  will be defined as condition set that does not have any conditions.

Next we will introduce another condition signal property that first appeared in [GH00]. A condition signal c is said to be EXCLUSIVE to another condition signal c', if at most one of c, c' can be true at any time. Note that c' is not necessarily the same as  $\neg$ c. Two condition sets are exclusive if each set contains at least one condition signal exclusive to another condition signal in the other condition set. We assume that there exists a designation of exclusive condition signals over *AllC*. Such condition signal property is essential for avoiding system conflict among condition system model which will be illustrated in the following section. Note that any contradicting signals are necessarily exclusive.

System behavior of a particular condition system can be described by sequence of condition sets. A condition set sequence, called a C-SEQUENCE, is a finite length sequence of condition sets. A C-sequence from a typical condition system will indicate a string of ordered condition sets which is valid over certain period of time and thus describing the system behavior of condition system during that time frame. Each condition set sequence is of the form  $(C_0C_1...C_n)$  for some integer n and sets  $C_i \subseteq AllC$  for all  $0 \le i \le n$ . From the concept of condition signal property: Contradict, a C-sequence is said to be CONTRADICTION FREE if for each  $C_i$  for any  $c \in C_i$ , then  $\neg c \notin C_i$ . Given two C-sequences  $s_1$  and  $s_2$ , the expression  $s_1s_2$  will indicate the concatenation of  $s_2$  on the end of  $s_1$ , and this will allow the formation of Csequences set. A set of C-sequences is called a language, and the set consisting of

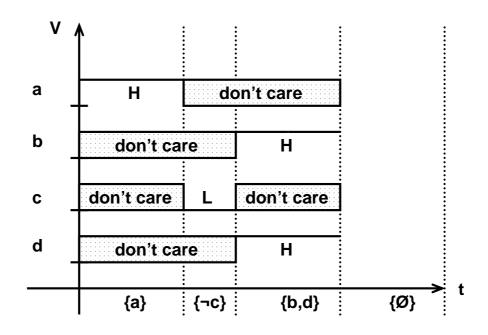

Figure 2.1: Examples of voltage signal time lines corresponding to the C-sequence  $s = (\{a\}\{\neg c\}\{bd\}\{\emptyset\})$

all C-sequences is denoted  $\mathcal{L}$ .

A C-sequence can be viewed as a sequence of conditions that must be true over certain specified though ordered time periods. Given a C-sequence  $s = (C_0C_1...C_n)$  and some  $0 \le i \le n$ ,  $C_i$  represents a subset of conditions (or negated conditions) that are true for some (possibly non-unique) period of time.  $C_i$  does not have to include all true conditions over the time period. However, the time period that  $C_i$  represents must follow immediately after the time period represented by  $C_{i-1}$ , and must be followed immediately by the time period represented by  $C_{i+1}$ . This is further illustrated in the high level voltage signal modeling of Figure 2.1. Note that the condition a might be true throughout the time line, but does not have to be listed in all condition sets in the sequence. This is analogous to a "do not care" condition on its value when it is not specified.

#### 2.1.1 Descriptive Ordering

Next, we will introduce the notion of DESCRIPTIVE ORDERING from [HA98b] which will allow us to compare elements of condition languages (sequences of condition sets). Elements of these languages are sequences of condition sets that are responsible for representing the evolution of a condition system. These condition sequences can also be used to specify the desired system behavior of a typical condition system. Each elements of the language will contain condition information of a particular condition system, and the ordering will be used to compare the richness of such information among each elements.

For the goal of simplicity in condition language analysis, we need to describe important characteristics of condition sequence without listing all the details of all condition activity within the C-sequence. A convenient way to characterize a C-sequence is through a partial ordering "≤" which we had previously referred to as the descriptive ordering. Such ordering can be used to analyze and compare features of different C-sequences.

Definition 2.1 will formally define the notion.

**Definition 2.1** Define the DESCRIPTIVE ORDERING  $\leq$  over condition sequences such that:

- 1.  $(C_1C'_1) \leq (C_2)$  if  $C_1 \subseteq C_2$  and  $C'_1 \subseteq C_2$ .

- 2.  $(C_1) \leq (C_2C'_2)$  if  $C_1 \subseteq C_2$  and  $C_1 \subseteq C'_2$ .

- 3. Given C-sequences  $s_1$ ,  $s_1'$ ,  $s_2$ , and  $s_2'$  such that  $s_1 \leq s_1'$  and  $s_2 \leq s_2'$ , then  $s_1s_2 \leq s_1's_2'$ .

- 4. If  $s_1 \leq s_2$  and  $s_2 \leq s_3$ , then  $s_1 \leq s_3$ .

From the definition above, we see that given sequences  $s_1$  and  $s_2$ , if  $s_1 \le s_2$ , then  $s_1$  contains no more condition information in it than  $s_2$ , and  $s_2$  can be said to be AT LEAST AS DESCRIPTIVE as  $s_1$ . If  $s_1 \le s_2$  and  $s_2 \le s_1$ , then the sequences are said to be EQUIVALENT under the ordering, written as  $s_1 \equiv s_2$ . Statement 1 and 2 in the definition above establish the ordering based on subsets of condition sets. Statement 3 considers the concatenation of smaller ordered C-sequences, and statement 4 defines the ordering to be transitive. Conditions that are not listed are considered "don't care" conditions. The descriptive ordering lets us omit consideration of specific conditions during periods when they are not of interest, while still allowing comparison of some basic sequencing characteristics.

**Example 2.1** To illustrate the descriptive ordering, consider a power control unit for a document scanning system with condition signals SCANNER ON, MOTOR ON and signals MU and MD to indicate that the scanner motor is moving in upward or downward position. Example C-sequences are as follows.

$$\begin{split} s_1 &= (\{\emptyset\}\{\text{motor on}, MD\})\\ s_2 &= (\{\text{motor on}\}\{MD\}\{\text{motor on}, MD\})\\ s_3 &= (\{\text{motor on}\}\{\text{motor on}, MD\}\{\text{motor on}, MD\})\\ s_4 &= (\{\text{motor on}, MU\}\{\text{motor on}, MD\})\\ s_5 &= (\{\text{motor on}, MD\})\\ s_6 &= (\{\text{motor on}, MU, \text{scanner on}\}\{\text{motor on}, MD, \text{scanner on}\}\\ \{\text{motor on}, MU, \neg \text{scanner on}\}) \end{split}$$

The following relationships are true.

$s_1 \le s_2 \equiv s_3 \le s_4 \le s_6$  $s_1 \le s_2 \equiv s_3 \le s_5$

Note that  $s_5$  and  $s_6$  are not comparable under the descriptive ordering since {motor on, MD}  $\not\subseteq$  {motor on, MU, scanner on} and vice versa.

Let (*AllC*) be the C-sequence of length one that consists of all conditions (including negations). Note that it is inherently contradictory. Let ( $\{\emptyset\}$ ) be the C-sequence of length one that consists of no conditions. The following results can be shown.

Lemma 2.1 (HA98b) The following statements are true:

- 1.  $s \leq (AllC)$  for any C-sequence s.

- 2.  $(\{\emptyset\}) \leq s$  for any C-sequence s.

- 3.  $(C) \equiv (CC) \equiv (CCC) \equiv (C^n)$  for any condition set C and any n > 0.

- 4. Given C-sequences  $s_1$  and  $s_2$  and condition set C,  $s_1Cs_2 \equiv s_1CCs_2$ .

- 5. Given C-sequences  $s_1$  and  $s_2$  and condition set C, C', if  $C \subseteq C'$ , then  $s_1Cs_2 \leq s_1C's_2$ .

Note that statement 1 of lemma 2.1 says that the condition sequence consisting of the set of all conditions (and their negations) being true is the most descriptive of all C-sequences (but it is contradictory). Statement 2 says that the C-sequence consisting of just an empty set of conditions is the least descriptive C-sequence, since it says nothing about the truth value of any condition at any time. Statement 3 says that any finite nonzero length sequence is equivalent to any other finite nonzero length sequence of the same condition set. Statement 4 says that duplication of a condition set within a sequence results in an equivalent sequence. Statement 5 considers two sequences that differ only in a single condition set, where the set in the first sequence is a subset of the set in the second sequence. The statement then says that the second sequence is at least as descriptive.

#### 2.1.2 Observability

Finally we conclude this section with a brief definition of OBSERVABILITY over conditions which was initially introduced in [HA98a]. Let  $C_{obs} \subseteq AllC$  be a set of conditions which can be observed, where it is implied that if  $c \in C_{obs}$  then  $\neg c \in C_{obs}$ . For any  $c \in C_{obs}(\mathcal{G})$ , this will implied that the condition signal c is observable with respect to  $\mathcal{G}$ . These observed conditions can either be the inputs to  $\mathcal{G}$  or outputs of  $\mathcal{G}$ . Note that the internal state of  $\mathcal{G}$  is not always observable, and their observability will depend on the synthesis of state observer within the system [GH00],[GH01].

Next we will associate observed condition set,  $C_{obs}$  with C-sequence, *s* in the following definition.

**Definition 2.2 OBSERVABILITY :** Given a C-sequence  $s = (C_0C_1...C_n)$  for some integer n and some condition set  $C_{obs} \subseteq AllC$ , define the projection of s onto C, denoted  $s \mid_C as s \mid_{C_{obs}} = ((C_0 \cap C_{obs})(C_1 \cap C_{obs})...(C_n \cap C_{obs})).$

Therefore s  $|_{C_{obs}}$  is also known as the observed system behavior of a particular condition system.

From the definition 2.2 we get the following basic result presented in lemma 2.2:

**Lemma 2.2 (HA02)** For any  $s \in \mathcal{L}$  and any  $C \subseteq AllC$ ,

$s \mid_{C_{obs}} \leq s.$

C-sequence s is said to be at least as descriptive to observed C-sequence s  $|_{C_{obs}}$ . Note that, if s  $|_{C_{obs}} \equiv$  s, these would imply that all the condition sets in C-sequence s are observable.

### 2.2 Condition System Model

Condition system  $\mathcal{G}$  is defined as a form of Petri net that requires conditions for enabling of transitions,  $\mathcal{T}_{\mathcal{G}}$  and outputs condition signals through places,  $\mathcal{P}_{\mathcal{G}}$  according to its markings m. Definition 2.1 from [HGSA00] formally defines condition systems that we consider for this thesis.

**Definition 2.3** A condition system  $\mathcal{G}$  is characterized by a set of states  $M_{\mathcal{G}}$ , a next state mapping  $f_{\mathcal{G}} : M_{\mathcal{G}} \times 2^{AllC} \longrightarrow 2^{M_{\mathcal{G}}}$ , and a condition output mapping  $g_{\mathcal{G}} : M_{\mathcal{G}} \longrightarrow 2^{AllC}$ . In this paper, we assume that  $M_{\mathcal{G}}$ ,  $f_{\mathcal{G}}$ , and  $g_{\mathcal{G}}$  are defined through a form of Petri net consisting of a set of places  $P_{\mathcal{G}}$ , a set of transitions  $T_{\mathcal{G}}$ , a set of directed arcs  $A_{\mathcal{G}}$  between places and transitions, and a condition mapping function  $\Phi_{\mathcal{G}}(\cdot)$ , where  $(\forall p)\Phi_{\mathcal{G}}(p) \subseteq AllC$  maps output conditions to each place, and  $(\forall t)\Phi_{\mathcal{G}}(t) \subseteq AllC$  maps ENABLING CONDITIONS to each transition. The net is related to  $M_{\mathcal{G}}$ ,  $f_{\mathcal{G}}$  and  $g_{\mathcal{G}}$  in the following manner:

- 1. The states are the markings of the Petri Net: each state  $m \in M_{\mathcal{G}}$  is a function over  $\mathcal{P}_{\mathcal{G}}$  that represents a mapping of nonnegative integers to places.

- 2. The output conditions result from Marked places: for any  $m \in M_{\mathcal{G}}$ ,  $g_{\mathcal{G}}(m) = \{c \mid \exists p \text{ s.t. } c \in \Phi_{\mathcal{G}}(p) \text{ and } m(p) \ge 1\}$

- 3. NEXT-STATE DYNAMICS DEPEND ON STATE ENABLING AND CONDITION ENABLING: for any  $m \in M_{\mathcal{G}}$  and any set of conditions TrueC  $\subseteq$  AllC,  $m' \in f_{\mathcal{G}}(m, TrueC)$ if and only if there exists some transition set T such that

- (a) T is STATE-ENABLED, meaning  $(\forall p \in P_{\mathcal{G}}) m(p) \ge |\{t \in T | p \text{ is input to } t\}|$

- (b) T is CONDITION-ENABLED, meaning  $(\forall t \in T) \ \Phi_{\mathcal{G}}(t) \subseteq TrueC$

- (c) the next marking m' satisfies  $\forall p \in P_{\mathcal{G}}$ ,  $m'(p) = m(p) - |\{t \in T | p \text{ is input to } t\}| + |\{t \in T | p \text{ is output of } t\}|$

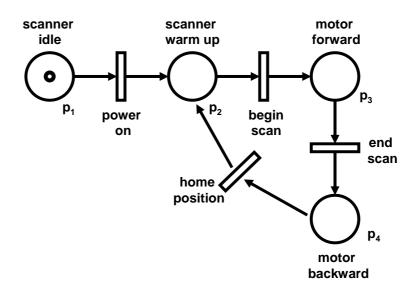

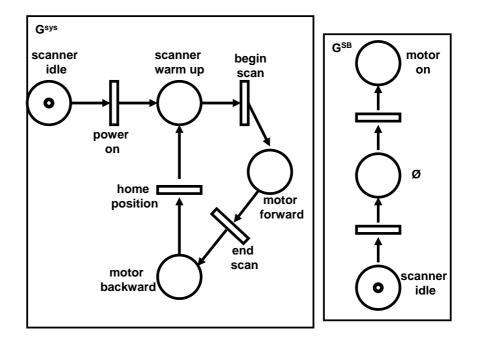

Figure 2.2: Example of condition system model for a scanner motor power control unit.

4.  $M_{\mathcal{G}}$  IS CLOSED UNDER  $f_{\mathcal{G}}(\cdot)$ : if  $m \in M_{\mathcal{G}}$  and  $m' \in f_{\mathcal{G}}(m, TrueC)$  for some TrueC  $\subseteq$  AllC, then  $m' \in M_{\mathcal{G}}$ .

In statement 2, we assume all conditions that are output from G will have value defined by the marking of  $\mathcal{G}$ . Thus, if a condition c is forced true on one marking, then it will also be forced to either true or false for all other markings either through the function g or defaulting to a known value. We note that items in 3a and 3c above correspond to standard Petri net state enabling and firing of a transition set, respectively. Item 3b adds an additional transition set enabling constraint that the input conditions to each transition must also be within the considered set TrueC of true conditions.

We will define enabling conditions of transitions as the input condition set for a condition system  $\mathcal{G}$ ,  $C_{in}(\mathcal{G}) = \{c \in \Phi_{\mathcal{G}}(t) \mid t \in T_{\mathcal{G}}\}$ . Similarly we define the conditions of a place as the output condition set for the condition system  $\mathcal{G}$ ,  $C_{out}(\mathcal{G}) = \{c \in \Phi_{\mathcal{G}}(p) \mid p \in \mathcal{P}_{\mathcal{G}}\}$ .

**Example 2.2** Consider the condition system model shown in Figure 2.2. The net shown represents a simple scanner mechanism under its motor control unit. There are three basic operational buttons on the scanner: "power on", "begin scan" & "end

scan" and they are controlled by the user. The scanner motor control unit can either be in the state of "scanner idle", "scanner warm up", "motor forward" or "motor backward". The conditions associated with the transitions represent input conditions to the system. The conditions on the places are output conditions from the system. If a place is marked then its associated output condition is "true". According to Definition 2.3, the marking shown in the figure is  $m_0 = [1 \ 0 \ 0 \ 0]$  and  $g_G(m_0) = \{$  scanner idle  $\}$ . Under the input condition set  $C_{in}(\mathcal{G}) = \{$  power on  $\}$ , the transition from  $p_1$  to  $p_2$  is both state enabled and condition enabled, so  $f_{\mathcal{G}}(m_0, C) = \{$  [0 0 0 1], [0 0 1 0]  $\}$ . Note that when the scanner is in the state of "motor backward", an internal command "home position" will be issued within the scanner control unit to bring the scanner back to the "scanner warm up" state.

The next lemma follows directly from the Definition 2.3.

**Lemma 2.3 (HGSA00)** Consider a condition system G, with marking m and next state mapping  $f_G$ . The following statements are true:

- 1. Given condition sets C and C', if  $C \subseteq C'$ , then  $f_{\mathcal{G}}(\mathfrak{m}, C) \subseteq f_{G}(\mathfrak{m}, C')$ ;

- 2. Given condition sets C and C', if  $C \cap C_{in}(\mathcal{G}) = C' \cap C_{in}(\mathcal{G})$ , then  $f_{\mathcal{G}}(\mathfrak{m}, C) = f_{\mathcal{G}}(\mathfrak{m}, C')$ ;

- 3. For any true condition set TrueC,  $m \in f_{\mathcal{G}}(m, TrueC)$ .

The first statement relates the next state marking with subsets of condition sets and the second statement explores on relationship of input condition sets with the next state marking. The third statement of the lemma 2.3 is true because the set of transitions T in Definition 2.3 can be an empty set which means that the next state dynamics is independent of state enabling and condition enabling of the corresponding set of transitions, T due to the issue of timing delay in real world modeling.

**Definition 2.4** Given a condition system  $\mathcal{G}$  and a marking  $m_0$ , define the language  $L(\mathcal{G}, m_0) \subseteq \mathcal{L}$  to be the set of condition set sequences such that  $(C_0C_1C_2...C_n) \in L(\mathcal{G}, m_0)$  if there exists some marking sequence  $(m_0m_1...m_k)$  and index mapping function j(i) with j(0) = 0, j(k) = n such that:

1. MARKINGS EVOLVE ACCORDING TO CONDITIONS:

$\mathfrak{m}_{i+1} \in f_{\mathcal{G}}(\mathfrak{m}_i, C_{\mathfrak{j}(\mathfrak{i})})$  for  $0 \leq \mathfrak{i} \leq k-1$ .

- 2. OUTPUT CONDITIONS RESULT ONLY FROM THE MARKING:  $g_{\mathcal{G}}(\mathfrak{m}_i) = C_{\mathfrak{j}(i)} \bigcap C_{\mathrm{out}}(\mathcal{G}).$

- 3. SEQUENCING IS MAINTAINED:

A marking  $m_{i+1}$  either maps to condition sequence element  $C_{j(i)}$  corresponding to prior marking  $m_i$  in the marking sequence, or it maps to the next condition sequence element. More formally, for any  $0 \le i < k$ , j(i+1) = j(i) or j(i+1) = j(i) + 1.

The above definition deserves some explanation. The notation  $C_{j(i)}$  indicates the condition set associated with the ith marking. From statement 1, marking  $m_i$  will evolve to marking  $m_{i+1}$  only if it is enabled under condition set  $C_{j(i)}$ . Statement 2 states that the output conditions in set  $C_{j(i)}$  correspond to the marking  $m_i$ . For statement 3, there are only two possibilities for condition set associates with marking  $m_{i+1}$ :it can either be the condition set that was associated with the previous marking  $m_i$  or the next condition set following immediately from the condition set of previous marking. In this way, the condition sequencing is maintained.

The marking sequence and condition set sequences have different indices because the mapping between the sequence is not necessarily one-to-one. A marking could change from  $m_i$  to  $m_{i+1}$ , but  $g(m_i)$  and  $g(m_{i+1})$  could be the same. Thus, it is possible that both markings could correspond to the same condition sets in the C-sequence. This then implies that there could be fewer condition sets in the C-sequence than distinct markings in the corresponding marking sequence.

On the other hand, note that for any m and any C,  $m \in f_{\mathcal{G}}(m, C)$ , which implies that there is no transition firing. From statement 3, then it is possible that  $m_{i+1} = m_i$ . Under these circumstances, there will be more condition sets in the C-sequence than distinct markings in the corresponding marking sequence, Finally, we point out that  $L(\mathcal{G}, m_0)$  is obviously prefix-closed (excluding the empty prefix).

From the definition 2.4 we get the following basic result:

**Lemma 2.4 (HA98a)** For any  $\mathcal{G}$  with any marking m and for any two C-sequences  $s_1, s_2$  such that  $s_1 \in L(\mathcal{G}, m)$ , the following are true:

1. if  $s_2$  is a prefix of  $s_1$ , then  $s_2 \in L(\mathcal{G}, \mathfrak{m})$

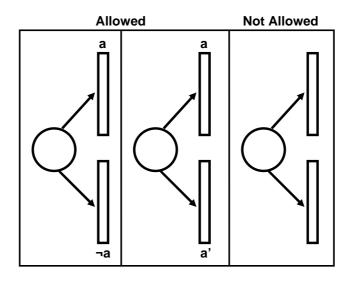

Figure 2.3: A simple chart showing some of the structural configurations which are allowed and not allowed for condition systems satisfying property deterministic

- 2. if  $s_1 \leq s_2$  and  $s_1 \mid_{C_{out,\mathcal{G}}} \equiv s_2 \mid_{C_{out,\mathcal{G}}}$ , then  $s_2 \in L(\mathcal{G}, m)$ .

- 3. if  $s_2 \equiv s_1$ , then  $s_2 \in L(\mathcal{G}, m)$ .

Note from the lemma 2.4, statement 1 states that the set  $L(\mathcal{G}, m)$  is prefix closed. Statement 2 says a string that is more descriptive with the equivalent output conditions is also in the language,  $L(\mathcal{G}, m)$ .

In this thesis, our condition system model is subjected to the limitation related to one of the subclasses of Petri Net, Free-Choice Petri Nets [P81]. The class of systems we consider is best illustrated with the condition system property DETERMINISTIC.

The system property DETERMINISTIC will be formally defined in Definition 2.5:

**Definition 2.5 Property DETERMINISTIC:** A condition system satisfies Property DETERMINISTIC if the following is true:

1. Given a place p and the set  $p^{(t)} = \{t \in T \mid t \text{ is output of } p\}$ , if the set  $p^{(t)}$  has more than one element, then for each  $t, t' \in p^{(t)}$ , there exist  $c \in \Phi_G(t)$  and  $c' \in \Phi_G(t')$  with c and c' exclusive with each other.

According to this limitation, a place cannot be an input to several transitions with one exception that when enabling condition of each transitions are exclusive

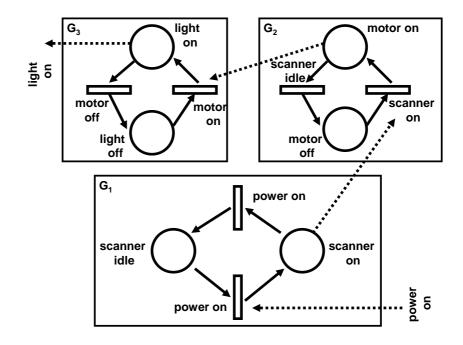

Figure 2.4: Condition subsystems model for the scanner power, lamp & motor control unit

or contradict among each other. But we do allow more than one place to be an input to a single transition. A place is also allowed to be an output from several transitions.

### 2.3 Composition of Condition System Models

A condition system can be subdivided into subsystems, where each subsystem is a condition system over a set of connected places and transitions which are disconnected from all other places and transitions. For the remainder of this thesis, we use the notation  $\mathcal{G}$  to indicate the complete system, and the notation  $\{G_1, ..., G_n\}$  to indicate the set of subsystems in  $\mathcal{G}$ . Given an initial marking  $m_0$  of  $\mathcal{G}$ , we let  $m_{0,i}$  denote the marking over just the places in  $G_i \in \mathcal{G}$ .

Condition systems can also be composed to create other condition systems. Concurrent composition of condition systems is formally defined in the following definition:

Definition 2.6 CONCURRENT COMPOSITION: Given two distinct systems G1 and

$G_2$  with markings  $m_1$  and  $m_2$ , let  $\mathcal{G} = G_1 \cup G_2$  the concurrent composition of  $G_1$  and  $G_2$  correspond to the simple unions of the systems, such that:

1.  $\mathcal{G}$ :  $\mathcal{P}_{\mathcal{G}} = \mathcal{P}_{G_1} \cup \mathcal{P}_{G_2}, \mathcal{T}_{\mathcal{G}} = \mathcal{T}_{G_1} \cup \mathcal{T}_{G_2}, \mathcal{A}_{\mathcal{G}} = \mathcal{A}_{G_1} \cup \mathcal{A}_{G_2}.$

2.

$$G_1$$

:  $\Phi_{\mathcal{G}}(x) = \Phi_{G_1}(x)$  for  $x \in \mathcal{P}_{G_1} \cup \mathcal{T}_{G_1}$

3. G<sub>2</sub>:  $\Phi_{\mathcal{G}}(x) = \Phi_{G_2}(x)$  for  $x \in \mathcal{P}_{G_2} \cup \mathcal{T}_{G_2}$

We assume x cannot be in both  $G_1$  and  $G_2$ . We will define the expression  $m = m_1 \cup m_2$  such that  $m(p) = m_1(p)$  for  $p \in \mathcal{P}_{G_1}$  and  $m(p) = m_2(p)$  for  $p \in \mathcal{P}_{G_2}$ .

The properties in the following lemma then result.

**Lemma 2.5 (HGSA00)** Given systems  $G_1$  and  $G_2$  with markings  $m_1$  and  $m_2$ , the following properties are true:

- 1. Given some condition set C, some  $m_1, m'_1 \in M_{G_1}$ , and some  $m_2, m'_2 \in M_{G_2}$ ,  $m'_1 \cup m'_2 \in f_{G_1 \cup G_2}(m_1 \cup m_2, \text{TrueC})$  if and only if  $m'_1 \in f_{G_1}(m_1, \text{TrueC})$  and  $m'_2 \in f_{G_2}(m_2, \text{TrueC})$

- 2.  $g_{G_1 \cup G_2}(\mathfrak{m}_1 \cup \mathfrak{m}_2) = g_{G_1}(\mathfrak{m}_1) \cup g_{G_2}(\mathfrak{m}_2).$

- 3. For each  $s \in L(G_1 \cup G_2, m_1 \cup m_2)$ , there exist  $s_1 \in L(G_1, m_1)$  and  $s_2 \in L(G_2, m_2)$ such that  $s_1 \leq s$  and  $s_2 \leq s$

- 4. If  $C_{out}(G_1) \cap C_{out}(G_2) = \emptyset$ , then  $L(G_1 \cup G_2, m_1 \cup m_2) = L(G_1, m_1) \cap L(G_2, m_2)$ .

Statement 1 in the lemma 2.5 states that if a condition set is sufficient to enable transitions in system  $G_1$  to fire to marking  $m_1$ , and to enable transitions in system  $G_2$  to fire to marking  $m_2$ , then it is sufficient to enable transitions in system  $G_1 \cup G_2$  to fire to marking  $m_1 \cup m_2$  in the composed system. The converse is also true. Statement 2 in the lemma states that the output of the composed system is just the union of the output of the individual systems. Statement 3 states that for any C-sequence s in the language of the composed system, for each of the subsystems there is some C-sequence in the subsystem language that is comparable to s and no more descriptive than s.

The condition in statement 4 about the composed systems having nonintersecting output condition sets is often true. The lemma statement 4 states that when the output conditions of these individual subsystems are nonintersecting, then the resulting language of the composed system is just the simple intersection of the individual languages. Figure 2.4 shows an example of a set of subsystems model for a scanner control unit. Dashed arcs in the figure indicate the flow of conditions between subsystems.

### 2.4 Condition System Models Modularity

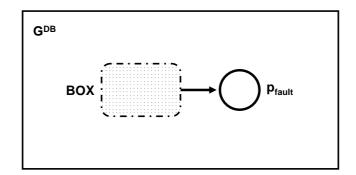

In this section we will present a special class of condition system models, SPECI-FICATION BLOCK (SpecBlock) introduced in [HA98A] & [HGSA00] to demonstrate the modularity of condition models which allow us to standardize, group and reuse system models. The specification block is a condition system used to specify the language that a system model (i.e. an auxiliary system model) should follow. In other words, SpecBlocks specify the desired states of a system model. Following the introduction of the specification block, we will define the properties of SpecBlock by presenting the notion of an achievable SpecBlock and the composition of SpecBlock.

#### 2.4.1 Specification Block

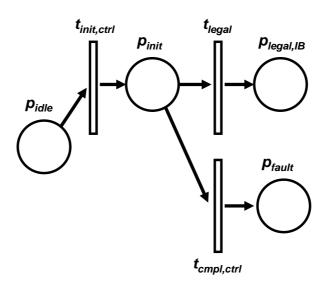

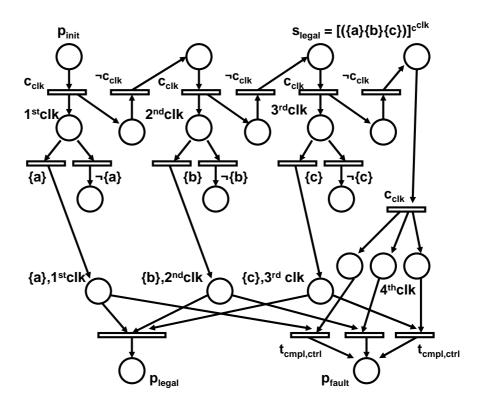

We represent our specification of desired system model in terms of a specification block (SpecBlock), defined as a triple ( $\mathcal{G}^{SB}$ ,  $m_{init,SB}$ ,  $m_{cmpl,SB}$ ), where  $\mathcal{G}^{SB}$  is a condition system,  $m_{init,SB} \in M_{\mathcal{G}^{SB}}$  is an INITIATION STATE and  $m_{compl,SB} \in M_{\mathcal{G}^{SB}}$  is a COMPLETION STATE. The set of states  $M_{\mathcal{G}^{SB}}$  is limited to the set of states reachable from the initiation state.

Next we will characterize the specification block by two condition sets, defined as:

$$\begin{split} C_{\text{init,SB}} &= \{ c \in \Phi_{\mathcal{G}^{SB}}(p) \mid p \text{ is marked under } m_{\text{init,SB}} \} \\ C_{\text{cmpl,SB}} &= \{ c \in \Phi_{\mathcal{G}^{SB}}(p) \mid p \text{ is marked under } m_{\text{cmpl,SB}} \} \end{split}$$

The condition set,  $C_{init,SB}$ , represents a set of conditions that are true whenever a specification is initiated. Likewise,  $C_{cmpl,SB}$  is the set of conditions generated by the final marking within the specification block. We will also defined condition system for system model as  $\mathcal{G}^{Sys}$ .

In the following definition, we will formally define the completion language of SpecBlock:

Figure 2.5: An example SpecBlock  $\mathcal{G}^{SB}$  for scanner power motor control unit ( $\mathcal{G}^{Sys}$ ) of Figure 2.2

**Definition 2.7** Given a SpecBlock ( $\mathcal{G}^{SB}$ ,  $m_{init,SB}$ ,  $m_{cmpl,SB}$ ), the completion language  $L_{cmpl}(\mathcal{G}^{SB}) \subseteq L(\mathcal{G}^{SB}, m_{init,SB})$  is defined such that:  $s \in L_{cmpl}(\mathcal{G}^{SB})$  if there exists some marking sequence ( $m_0...m_k$ ) consistent with s where  $m_0 = m_{init,SB}$  and  $m_k = m_{cmpl,SB}$ .

We note that the completion language for condition systems is analogous to the marked language in traditional event-based languages. It is not necessary prefix closed.

**Example 2.3** Suppose that the scanner power control unit model shown in Figure 2.2 is the system model,  $\mathcal{G}^{Sys}$  and specification block associates with switching the scanner off/on and turning the motor on is shown in  $\mathcal{G}^{SB}$  of Figure 2.5. The SpecBlock is represented as ( $\mathcal{G}^{SB}$ , (100), (001)) where the marking vector correspond to the places from down to up in the figure. One of the C-sequence, s within the completion language is ({Scanner Idle} { $\emptyset$ } {Motor On}). The { $\emptyset$ } in the C-sequence effectively allows any intermediate activity between the Scanner Idle and Motor On conditions under the descriptive ordering. Note that the C-sequence

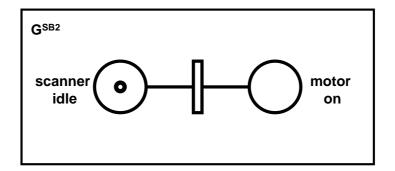

Figure 2.6: An example SpecBlock  $\mathcal{G}^{SB2}$  for scanner power motor control unit ( $\mathcal{G}^{Sys}$ ) of Figure 2.2

is ambiguous in the sense that it describes selected output conditions of  $\mathcal{G}^{Sys}$ , but does not describe details of how to achieve those conditions.

#### 2.4.2 Achievable Specification Block

In this subsection, we will now formally define an achievable specification block.

**Definition 2.8** A SpecBlock  $(\mathcal{G}^{SB}, \mathfrak{m}_{init,SB}, \mathfrak{m}_{cmpl,SB})$  is achievable with respect to a system model  $\mathcal{G}^{Sys}$  if for any  $\mathfrak{m} \in M_{\mathcal{G}^{Sys}}$  such that  $g_{\mathcal{G}^{Sys}}(\mathfrak{m}) = g_{\mathcal{G}^{SB}}(\mathfrak{m}_{init,SB}) \bigcap C_{out}(\mathcal{G}^{Sys})$ , then there exists a  $s \in L_{cmpl}(\mathcal{G}^{SB})$  and a  $s' \in L(\mathcal{G}^{Sys}, \mathfrak{m})$  such that  $s \leq s'$ .

Thus, if a specification  $\mathcal{G}^{SB}$  is achievable, then for any state of the system model that matches the output of the initial state of the specblock, there will exist a C-sequence from that state such that the sequence is at least as descriptive as some C-sequence of the completion language of the specblock. Note that ACHIEVABIL-ITY does not imply that the system model could be restricted to just the specified behavior, it simply says that the system model is capable of satisfying the behavior.

**Example 2.4** From example 2.3, the C-sequence within the completion language of  $\mathcal{G}^{SB}$ , ({Scanner Idle} { $\emptyset$ } {Motor On}) is achievable with respect to  $\mathcal{G}^{Sys}$  since the system model can produce a C-sequence as descriptive as this. Now suppose we omitted the middle state in the  $\mathcal{G}^{SB}$  of Figure 2.5 as shown in Figure 2.6 ( $\mathcal{G}^{SB2}$ ), so that we now had ({Scanner Idle} {Motor On}) as the C-sequence within our com-

pletion language of  $\mathcal{G}^{SB2}$ , this then would not be achievable with respect to  $\mathcal{G}^{Sys}$ , since the system model cannot go from scanner idle to motor on without traveling through some intermediate state. C-sequences within the completion language from both  $\mathcal{G}^{Sys}$  and  $\mathcal{G}^{SB2}$  are said to be incomparable with each other.

#### 2.4.3 Composition of Specification Block

Next, we will present results on sequentially composing SpecBlocks into larger SpecBlocks. If each individual SpecBlock is achievable and certain relationships between the SpecBlocks used are satisfied, then the resulting composed block will also be achievable.

We define the SEQUENTIAL COMPOSITION of specification blocks formally in the following definition:

**Definition 2.9 SEQUENTIAL COMPOSITION** FOR **SPECBLOCK:** Given two SpecBlocks  $SB_1 = (\mathcal{G}^{SB_1}, m_{init,SB_1}, m_{cmpl,SB_1})$  and  $SB_2 = (\mathcal{G}^{SB_2}, m_{init,SB_2}, m_{cmpl,SB_2})$ , define the sequential composition, denoted  $SB_1|SB_2 = (\mathcal{G}^{SB_1}|\mathcal{G}^{SB_2}, m_{init,SB_1}|SB_2, m_{cmpl,SB_1}|SB_2)$  such that:

- 1.  $\mathcal{G}^{SB_1}|\mathcal{G}^{SB_2}$  is the union of the nets  $\mathcal{G}^{SB_1}$  and  $\mathcal{G}^{SB_2}$  with the addition of an additional transition  $t_{join}$  and arcs such that, arcs lead to  $t_{join}$  from each place  $p \in \mathcal{P}_{SB_1}$  marked under  $m_{cmpl,SB_1}$ , and lead from  $t_{join}$  to each place  $p \in \mathcal{P}_{SB_2}$ , marked under  $m_{init,SB_2}$ .

- 2.  $\mathfrak{m}_{\text{init},SB_1|SB_2}(p)$  equals  $\mathfrak{m}_{\text{init},SB_1}(p)$  if  $p \in \mathcal{P}_{SB_1}$  and equals 0 if  $p \in \mathcal{P}_{SB_2}$ .

- 3.  $\mathfrak{m}_{cmpl,SB_1|SB_2}(p)$  equals 0 if  $p \in \mathcal{P}_{SB_1}$  and equals  $\mathfrak{m}_{cmpl,SB_2}(p)$  if  $p \in \mathcal{P}_{SB_2}$ .

Note that the initiation  $SB_1|SB_2$  ( $\mathcal{G}^{SB,seq}$ ) is the same as initiating just  $SB_1$ . When  $SB_1$  in the composition reaches completion, then  $SB_2$  initiates. The composed block then completes upon the completion of  $SB_2$ .

The following properties follow from the definition:

**Lemma 2.6 (HA98A)** Consider SpecBlocks  $SB_1$  and  $SB_2$  is the same as just initiating just  $SB_1$ . When  $SB_1$  in the composition reaches completion, then  $SB_2$  initiates. The composed block then completes upon the completion of  $SB_2$ . The following properties are true:

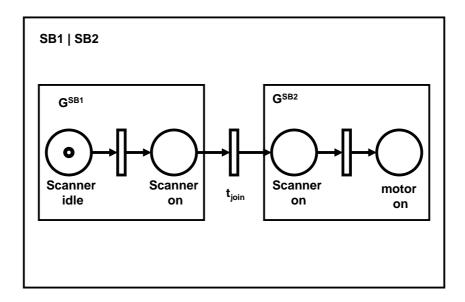

Figure 2.7: An example of Composed SpecBlock SB1|SB2 for scanner power motor control unit ( $\mathcal{G}^{Sys}$ ) of Figure 2.2

- 1.  $C_{\text{init},\mathcal{G}_{SB,seq}} = C_{\text{init},SB_1}$ .

- 2.  $C_{cmpl,\mathcal{G}_{SB,seq}} = C_{cmpl,SB_2}$ .

- 3.  $L_{cmpl}(\mathcal{G}^{SB,seq}) = \{ss' | s \in L_{cmpl}(\mathcal{G}^{SB_1}), s' \in L_{cmpl}(\mathcal{G}^{SB_2})\}.$

To show the last statement of the lemma, note that for any  $s \in L_{cmpl}(G^{SB_1})$ , there exists a marking sequence from  $m_{init,SB_1}$  to  $m_{cmpl,SB_1}$ . By the composition,  $m_{cmpl,SB_1}$  enables the transition  $t_{join}$  between the SpecBlocks. Firing  $t_{join}$  empties  $G^{SB_1}$  and gives  $m_{init,SB_2}$ , from which any marking sequence leading to  $m_{cmpl,SB_2}$ gives string  $s' \in L_{cmpl}(G^{SB_2})$ . Since neither SpecBlock has transition condition inputs from the other SpecBlock, then linking of the two blocks does not cause one to restrict the transition firings of the other. By definition 2.8, if follows then that  $ss' \in L(\mathcal{G}^{seq,SB}, m_{init,SB_{seq}})$ , and  $ss' \in L_{cmpl}(SB_{seq})$ . We have thus shown that  $L_{cmpl}(\mathcal{G}^{SB_{seq}}) \subseteq \{ss' \mid s \in L_{cmpl}(\mathcal{G}^{SB_1}), s' \in L_{cmpl}(\mathcal{G}^{SB_2})\}$  Containment in the other direction is shown by noting that  $m_{cmpl,SB_{seq}}$  is  $m_{cmpl,SB_2}$  by its definition, and since  $\mathcal{G}^{SB_2}$  is initially unmarked in the composition, no marking sequence can reach  $m_{cmpl,SB_{seq}}$  without first reaching  $m_{cmpl,SB_1}$  to enable the firing of  $t_{join}$ .

**Example 2.5** Consider the composed Specblock SB1|SB2 shown in Figure 2.7, SB1 =  $(\mathcal{G}^{SB1}, (10), (01))$  is achievable with respect to system model of Figure 2.2

$G_{Sys}$  and  $SB2 = (\mathcal{G}^{SB2}, (10), (01))$  is also achievable with respect to  $\mathcal{G}^{Sys}$ . SB1|SB2will be achievable too w.r.t  $\mathcal{G}^{Sys}$  since  $C_{init,\mathcal{G}^{SB_2}} = \{Scanner \text{ on}\}, C_{cmpl,\mathcal{G}^{SB_1}} = \{Scanner \text{ On}\}$  and therefore  $C_{init,\mathcal{G}^{SB_2}} \subseteq C_{cmpl,\mathcal{G}^{SB_1}}$ . But SB2|SB1 will not be achievable w.r.t.  $\mathcal{G}^{Sys}$  since  $C_{init,\mathcal{G}^{SB_2}} \not\subseteq C_{cmpl,\mathcal{G}^{SB_2}}$ .

Finally we will present the main result of achievable sequential composition as presented in lemma 2.7:

**Lemma 2.7 (HA98A)** Given SpecBlocks SB<sub>1</sub> and SB<sub>2</sub> which are achievable w.r.t.  $\mathcal{G}^{Sys}$ , the sequential SpecBlock composition, SB<sub>1</sub>|SB<sub>2</sub>, is achievable w.r.t.  $\mathcal{G}^{Sys}$  if  $C_{init,\mathcal{G}^{SB_2}} \subseteq C_{cmpl,\mathcal{G}^{SB_1}}$ .

# Chapter 3

# Modeling For Interfacing

Modeling for interfacing focuses on issues in simulating environment interfaces with a particular target system. The environment subjected to simulation communicates with target system through a common interface and the objective of modeling for interfacing is to build a system model,  $\mathcal{G}^{sys}$  out of the environment solely for the objective of imitating its interaction with the target system. In other words, the system model created is only responsible for providing an accurate system interaction with its target system. A successful modeling process will lead target system into "believing" that it is interacting with the actual system even though the system it interacted with is merely a virtual system and it is not the actual and original system. Under the modeling for interfacing framework, a subsystem model will then be synthesized from  $\mathcal{G}^{sys}$  to perform fault detection on signal interactions between target system and  $\mathcal{G}^{sys}$ . The concept of modeling for interfacing will serve as a fundamental foundation for the introduction of two special classes of condition system model, virtualblock and detectblock.

In our cases, we are given a system under test (SUT) which interacts primarily with an auxiliary system and a controller. The SUT will be our target system and the auxiliary system will be the system model. Controller's function is to determine whether SUT is in working condition and the auxiliary system will act as a supplement to SUT through their signals interface interaction. In addition, the specification of SUT is only partially known or understood, and therefore a complete system model of SUT is unavailable. However, we will have the necessary specification of the auxiliary system which will allow us to develop the corresponding system model. Under our modeling methodologies, auxiliary system, the system interfacing with system under test, is subjected to modeling process and is represented as a form of condition system Petri net. The auxiliary system model will not only provide signal interactions with SUT, but also detect faults on SUT.

Figure 3.1: System interactions among system under test, auxiliary system and controller

One of the goals of this thesis is to develop a system model out of the real and actual auxiliary system for the purpose of interfacing with system under test. Motivations for developing such system model originate from the disadvantages of using a real system in terms of design time, manufacturing cost and also the potential danger involved in actual system testing. By using a system model (such as a software model), the corresponding system behavior can either be operated as a STANDARD BEHAVIOR where both "normal" and "rare" behavior can be simulated or CUSTOMIZED BEHAVIOR where forced behavior such as peripheral failures and errors can be modeled. In comparison to hard coding specific responses, a model based approach is more suitable in light of flexibility on future testing and design. Coding can be synthesized from the model and device modeling can be done with multiple behaviors instead of just a single response. Thus in order to test certain functionality of the SUT, we will utilize the model-based approach to model the auxiliary system.

The goal of the auxiliary system modeling is to eventually confirm the SUT correct signals interaction with the auxiliary system. To achieve this goal, there are mainly two tasks to be completed: 1. Given an excitation of auxiliary system by SUT, determine the possible responses of auxiliary system. 2. Given the possible responses of the auxiliary system, confirm that the SUT responds appropriately (fault detection). The first task will be accomplished by virtualblock which will be addressed in the following chapter, chapter 4. Another class of condition system model, detectblock is introduced to tackle the second task. Detectblock will be addressed in chapter 5.

This chapter is presented as follow: we will first briefly define the notion of real and expected behavior on a system. From such notions, we will then formally define our definition of fault. Next, we will present and define the system architecture under our modeling for interfacing framework which mainly consist of: System Under Test, Auxiliary System, Controller and External Environment. Finally, fault detection under modeling for interfacing framework will be defined and described in the last section of the chapter.

### 3.1 Real and Expected Systems

In this section, we will define the notion of real and expected behavior of a system presented in [A04]. For a given system, we use superscripts (R,E) to distinguish between the real and actual behavior of a system,  $\mathcal{G}^{R}$  and expected behavior of a system model,  $\mathcal{G}^{E}$ . The REAL SYSTEM distinguishes itself from the EXPECTED SYSTEM through the definition of fault which we will briefly define in Definition 3.1:

**Definition 3.1** Under the notion of real and expected behavior, a system is said to have a FAULT if the language of the real system ( $\mathcal{G}^R$ ) is not contained within the language of its corresponding model system ( $\mathcal{G}^E$ ) of the expected behavior, i.e. For all  $s \in L(\mathcal{G}^R, m_0^R)$ , if  $s \notin L(\mathcal{G}^E, m_0^E)$  then s represents a fault.

Ideally, an expected system completely captures the necessary system behavior of a real system and therefore it is fault free. The expected behavior of a system model is considered as a subset of the real system,  $\mathcal{G}^{E} \subseteq \mathcal{G}^{R}$ .

Figure 3.2: Scheme for Real and Expected System Fault Detection

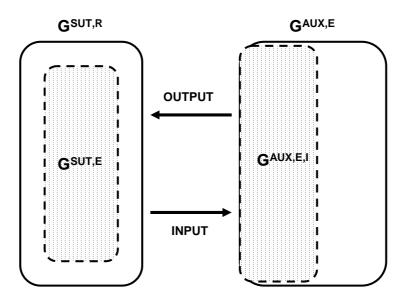

### 3.2 Systems under Modeling for Interfacing Framework

In general, there are four systems we consider: SYSTEM UNDER TEST, AUXILIARY SYSTEM, CONTROLLER and EXTERNAL ENVIRONMENT. For any given system, we use superscripts (SUT, Aux) to distinguish between System under Test,  $\mathcal{G}^{SUT}$  and Auxiliary System,  $\mathcal{G}^{Aux}$ . Superscripts (Ctrl, Env) will be used to define the Controller,  $\mathcal{G}^{Ctrl}$  and the External Environment,  $\mathcal{G}^{Env}$ . We will also use superscript (I) to denote system which is responsible for interfacing any target systems,  $\mathcal{G}^{I}$  and superscript (D) to denote system which is capable of performing fault detection,  $\mathcal{G}^{D}$ .