University of Kentucky UKnowledge

University of Kentucky Master's Theses

Graduate School

2010

## DESIGN AND IMPLEMENTATION OF THE INSTRUCTION SET ARCHITECTURE FOR DATA LARS

Kalyan Ponnala University of Kentucky, ponnala.kalyan@gmail.com

Right click to open a feedback form in a new tab to let us know how this document benefits you.

#### **Recommended Citation**

Ponnala, Kalyan, "DESIGN AND IMPLEMENTATION OF THE INSTRUCTION SET ARCHITECTURE FOR DATA LARS" (2010). *University of Kentucky Master's Theses*. 58. https://uknowledge.uky.edu/gradschool\_theses/58

This Thesis is brought to you for free and open access by the Graduate School at UKnowledge. It has been accepted for inclusion in University of Kentucky Master's Theses by an authorized administrator of UKnowledge. For more information, please contact UKnowledge@lsv.uky.edu.

#### ABSTRACT OF THE THESIS

#### DESIGN AND IMPLEMENTATION OF THE INSTRUCTION SET ARCHITECTURE FOR DATA LARS

The ideal memory system assumed by most programmers is one which has high capacity, yet allows any word to be accessed instantaneously. To make the hardware approximate this performance, an increasingly complex memory hierarchy, using caches and techniques like automatic prefetch, has evolved. However, as the gap between processor and memory speeds continues to widen, these programmer-visible mechanisms are becoming inadequate.

Part of the recent increase in processor performance has been due to the introduction of programmer/compiler-visible SWAR (SIMD Within A Register) parallel processing on increasingly wide DATA LARs (Line Associative Registers) as a way to both improve data access speed and increase efficiency of SWAR processing. Although the base concept of DATA LARs predates this thesis, this thesis presents the first instruction set architecture specification complete enough to allow construction of a detailed prototype hardware design. This design was implemented and tested using a hardware simulator.

KEYWORDS: Line Associative Registers, DATA LARs, SIMD Within a Register (SWAR), Cache Registers (CRegs), Associativity.

KALYAN PONNALA

(03/09/10)

# DESIGN AND IMPLEMENTATION OF THE INSTRUCTION SET ARCHITECTURE FOR DATA LARS

By

Kalyan Ponnala

Dr. Hank Dietz Director of Thesis Dr. Stephen D. Gedney Director of Graduate Studies

(03/09/2010)

#### RULES FOR THE USE OF THESES

Unpublished theses submitted for the Master's degree and deposited in the University of Kentucky Library are as a rule open for inspection, but are to be used only with due regard to the rights of the authors. Bibliographical references may be noted, but quotations or summaries of parts may be published only with the usual scholarly acknowledgements.

Extensive copying or publication of the thesis in whole or in part also requires the consent of the Dean of the Graduate School of the University of Kentucky.

A library that borrows this thesis work for use by its patrons is expected to secure the signature of each user.

#### <u>Name</u>

Date

THESIS

Kalyan Ponnala

The Graduate School

University of Kentucky

2010

### DESIGN AND IMPLEMENTATION OF THE INSTRUCTION SET ARCHITECTURE FOR DATA LARS

THESIS

A thesis submitted in the partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering in the College of Engineering at the University of Kentucky

By

Kalyan Ponnala

Lexington, Kentucky

Director: Dr. Hank Dietz, Professor of Electrical Engineering

Lexington, Kentucky

2010

Copyright<sup>©</sup> Kalyan Ponnala 2010

## DEDICATION

To my extraordinary parents

And

All my friends at the University of Kentucky

#### ACKNOWLEDGEMENTS

I sincerely thank my academic advisor and thesis Director, Dr. Hank Dietz from the bottom of my heart for his guidance and support throughout my thesis. I am very thankful to Dr. Robert Heath for allowing me to work in his lab and helping me with my thesis. I would also like to acknowledge Dr. Meikang Qiu for his willingness to serve on my thesis committee.

I would like to thank my mom, dad and brother for their emotional support and belief in me. Finally, I would like to thank all my friends at the University of Kentucky who have encouraged me during my work at this university.

## TABLE OF CONTENTS

| ACKNOWLEDGEMENTS iii                        |

|---------------------------------------------|

| LIST OF TABLES                              |

| LIST OF FIGURES                             |

| CHAPTER 1 1                                 |

| 1. INTRODUCTION                             |

| 1.1 MOTIVATION                              |

| 1.2 BACKGROUNG                              |

| 1.2.1 SWAR                                  |

| 1.2.2 CREGS                                 |

| 1.2.3 CACHE                                 |

| CHAPTER 2                                   |

| 2. LARS                                     |

| 2.1 DATA TYPES                              |

| 2.1.1 Fundamental Data Types                |

| 2.1.2 PACKED SIMD DATA TYPES                |

| 2.2 SIGNED AND UNSIGNED INTEGERS 10         |

| 2.3 Memory Alignment                        |

| 2.4 DATA LARS REGISTER SET11                |

| CHAPTER 3                                   |

| 3. INSTRUCTION SET ARCHITECTURE             |

| 3.1 DATA TRANSFER INSTRUCTIONS              |

| 3.2 TYPE CASTING INSTRUCTIONS               |

| 3.3 ARITHMETIC AND LOGICAL INSTURCTIONS     |

| 3.3.1 TYPE CONVERSIONS                      |

| 3.3.2 SCALAR ALU OPERATIONS                 |

| 3.4 NO-OP                                   |

| 3.5 LOADDUMMY                               |

| 3.5 SUMMARY OF INSTRUCTION SET ARCHITECTURE |

| CHAPTER 4                                   |

| 4. DATA LARS ARCHITECTURE                   |

| 4.1 Interrupts                                         | 33 |

|--------------------------------------------------------|----|

| 4.2 TRADE OFFs OF DATA LARs                            | 33 |

| 4.2.1 DATA HAZARDS                                     | 34 |

| 4.2.2 STRUCTURAL HAZARD                                | 36 |

| 4.2.3 ASSOCIATIVE SEARCH OF LOAD INSTRUCTIONS          | 39 |

| CHAPTER 5                                              | 40 |

| 5. RESULTS                                             | 40 |

| 5.1 TRIVIAL EXAMPLE                                    | 40 |

| 5.1.1 EXECUTION OF ALIAS ANALISIS EXAMPLE ON DATA LARs |    |

| SIMULATOR                                              | 42 |

| 5.1.2 EXECUTION OF LAZY STORE EXAMPLE ON DATA LARs     |    |

| SIMULATOR                                              | 46 |

| 5.2 DEVICE UTILIZATION SUMMARY                         | 48 |

| CHAPTER 6                                              | 49 |

| 6. CONCLUSION AND FUTURE WORK                          | 49 |

| REFERENCES                                             | 51 |

| Vita                                                   | 53 |

## LIST OF TABLES

| Table 1: Bit field variations of WDSZ                                                     |

|-------------------------------------------------------------------------------------------|

| Table 2: Bit Field variation of TYP    13                                                 |

| Table 3: Variations of LOAD instruction                                                   |

| Table 4: Variations of the STORE instruction                                              |

| Table 5: Arithmetic instructions and their variations    21                               |

| Table 6: Summary of Instruction Set Architecture    28                                    |

| Table 7: Assembly language code of the C program "nasty" for DATA LARs and MIPs           |

|                                                                                           |

| Table 8: Static Comparison of DATA LARs and MIPs    41                                    |

| Table 9: the assembly language instructions modified for DATA LARs to test the alias      |

| analysis program of listing 2 42                                                          |

| Table 10: Register assignment in case of ambiguous alias of j and k in above example . 43 |

| Table 11: program to show lazy store mechanism of DATA LARs                               |

| Table 12: Summary of the device utilization of the straw man's model of DATA LARs         |

| architecture                                                                              |

## LIST OF FIGURES

| Figure 1: The hardware structure of CRegs                                                |

|------------------------------------------------------------------------------------------|

| Figure 2: The hardware structure of cache                                                |

| Figure 3: Fundamental Data Types                                                         |

| Figure 4: Bytes, Half words, Words and Double Words in memory9                           |

| Figure 5: Packed SIMD data types                                                         |

| Figure 6: The hardware structure of DATA LARs                                            |

| Figure 7: Format of LOAD instruction                                                     |

| Figure 8: DATA LARs before the LOAD instruction                                          |

| Figure 9: DATA LARs after the LOAD instruction                                           |

| Figure 10: DATA LARs d1 in the case of cancel LOAD 16                                    |

| Figure 11: Format of STORE instruction                                                   |

| Figure 12: DATA LARs before the STORE instruction                                        |

| Figure 13: DATA LARs after the STORE instruction 19                                      |

| Figure 14: Format of Arithmetic instructions                                             |

| Figure 15: modular arithmetic followed by the ALU                                        |

| Figure 16: Type conversion- Rules for sign extension in the DATA LARs architecture. 23   |

| Figure 17: Type conversion- saturation arithmetic rules for packing data                 |

| Figure 18: DATA LARs before the ADDs Instruction                                         |

| Figure 19: DATA LARs after the ADDs instruction. d1's value pointed by the word offset   |

| is changed from 1h to 4h                                                                 |

| Figure 20: Block diagram of DATA LARs architecture design                                |

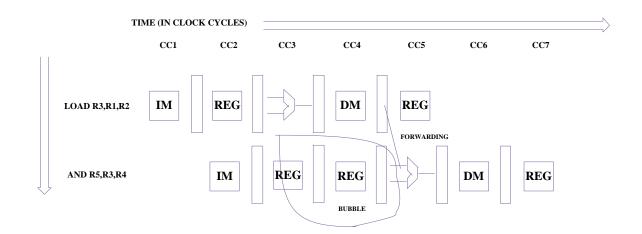

| Figure 21: Forwarding the pipeline saves the cost of a stall cycle                       |

| Figure 22: This shows what really happens in the MIPs hardware when the data             |

| dependency goes backward in time                                                         |

| Figure 23: For same problem the hazard forces the AND instruction to repeat in the       |

| clock cycles 4 and 5 what it did in clock cycle 3                                        |

| Figure 24: Clock cycle 4 repeats the operations done during clock cycle 3 to introduce a |

| pipeline bubble                                                                          |

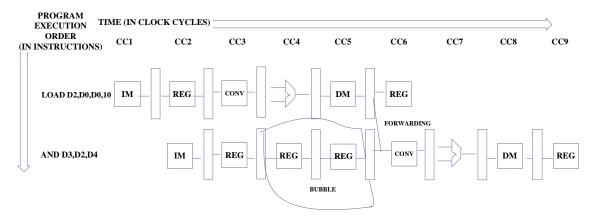

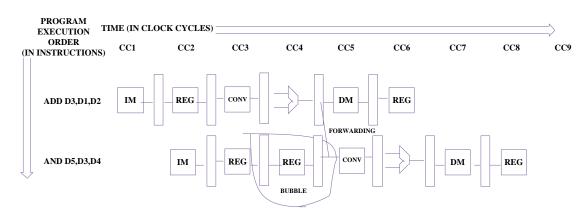

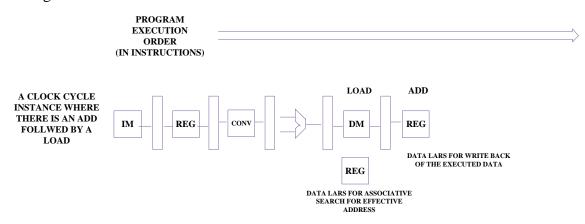

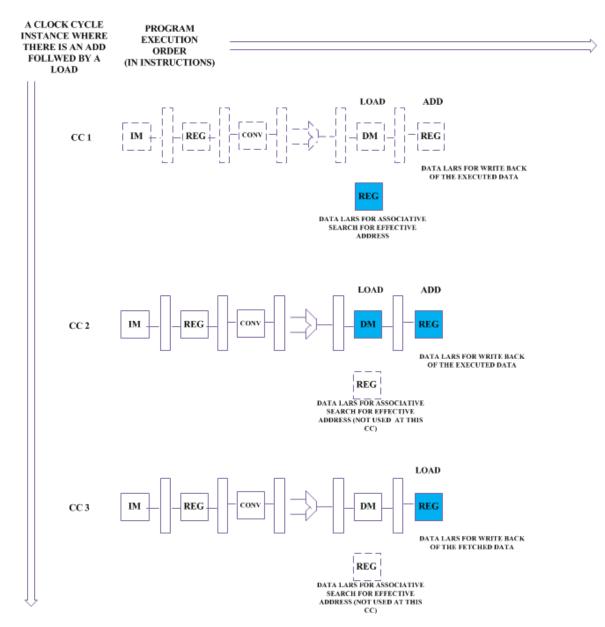

| Figure 25: The structural hazard problem with DATA LARs design for LOADs                 |

| Figure 26: The flow of instructions through the pipeline when there is a load instruction. |

|--------------------------------------------------------------------------------------------|

|                                                                                            |

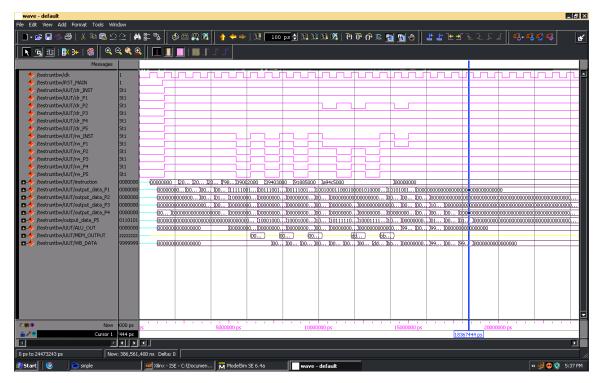

| Figure 27: the snapshot of alias analysis program run on the DATA LARs simulator with      |

| j != k                                                                                     |

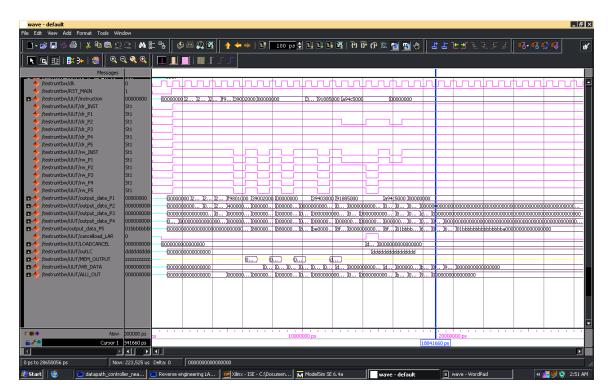

| Figure 28: the snapshot of alias analysis program run on the DATA LARs simulator with      |

| j == k                                                                                     |

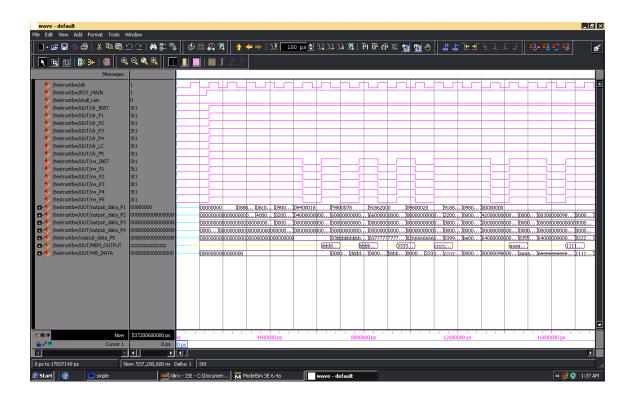

| Figure 29: screen shot of DATA LARs simulator output for the program given above 47        |

## LIST OF FILES

| 1. Thesis | _Kalyan_ | _Ponnala62 | 22KB |

|-----------|----------|------------|------|

|-----------|----------|------------|------|

#### **CHAPTER 1**

#### **1. INTRODUCTION**

The volume of data processed by the processors these days is increasing exponentially whereas the methods to suppress the high memory latency through programmer invisible mechanisms like caches or multithreading are falling short to keep up with these huge complexities. Even the speed of the conventional Von Neumann organization is highly dependent on the technology. This chapter provides a background the problem of the inefficiency of present memory hierarchies in bridging the gap between the high performance processors and the main memory and the motivation to opt for the Line Associative Registers (LARs) design.

#### **1.1 MOTIVATION**

The usual memory hierarchy goes from Registers (smaller) to RAMs (bigger). The reason for using different levels of memory from the cost issues of fabricating these memory units; registers being expensive because of the fabrication technology they use and the number of flip-flops they employ for storing a single bit of data. Layers of Cache are introduced to compensate for this gap in a less expensive way at the cost of relatively low bandwidth and high memory latency. The increase of the processor speeds these days has left a larger memory footprint on the whole processor-memory performance system.

As one of the solutions to this problem, parallel processing is considered where similar processing elements work simultaneously on a single big problem. SWAR (Single Instruction Multiple Data (SIMD) Within A Register) introduces a good programming model for data level parallelism by adding the ability to perform SIMD-like operations on fields within a register or datapath. SWAR operations replace a series of memory accesses and field extraction/insertion operations with a single access for a word's worth of fields. CRegs (Cache Registers) provide a hybrid hardware structure for registers with both the properties of caches and registers and have the advantages of both. The idea of extending the concepts of CRegs to support data level parallelism leads to the motivation of this thesis. Line Associative Registers (LARs) are evolved with the properties of

CRegs and SWAR. These registers along with type tagging lead to a whole lot of advantages. The next section gives the background of LARs.

#### **1.2 BACKGROUNG**

#### 1.2.1 SWAR

SIMD parallel processing over multiple data fields within each processor registers was intended to speed-up multimedia algorithms by supporting high-level parallel programming models. SWAR is such a hardware model which was implemented using only minor modifications to existing datapaths and function units. The PA-RISC [16][17] and the IA32 MMX [18][19] extensions both operate on the SWAR concept of having wide registers with the ability to operate on short integer operands on fields within 64-bits datapaths, although these mechanisms are add-ons to the existing architecture designs.

AltiVec and SSE have 128-bit data paths. One problem with AltiVec is that data cannot be moved directly between the vector and general-purpose integer registers. Thus, array indices generated in the vector registers must be moved via memory to the integer registers for use in a load or store instruction. 3DNow! [20] is a good first step toward adding floating-point SWAR capabilities to MMX and improving its coverage. There is still room for improvement which is addressed by the Athlon extensions to 3DNow!

The most salient aspect of these architectures is their vector SIMD nature. This has several implications for the design of a programming model including the expression of data parallelism and the execution of multiple control paths. In order to ease adoption of SWAR, many of the implementations provide both parallel and scalar instructions. The oxymoronic scalar SWAR instructions simply act on a single field, generally the one in the lowest bit field [21].

#### **1.2.2 CREGS**

The CRegs (C-Reg, Cache Registers) [9][10] are designed to reduce the number of memory accesses required by spotting and updating the ambiguous aliasing automatically and thereby letting these values stay in registers much longer. This idea would be really

important for SWAR-like processing where a single fetch cycle would mean fetching a whole line of data.

A CReg is a memory module which replaces the registers in a computer architecture design. It combines the structures of cache and registers as shown in the figure below. These special registers allow the variable values to stay in registers a while longer by controlling the way ambiguously aliased values are detected as well as updated.

| Name Datum Object Address status | Name | Datum | Object Address | status |

|----------------------------------|------|-------|----------------|--------|

|----------------------------------|------|-------|----------------|--------|

Figure 1: The hardware structure of CRegs

Ambiguous aliasing is a concept that occurs when the processor is dealing with arrays or pointers. Considering an array "a" with "n" elements,

Listing 1: compile-time Unresolvable Aliasing problem

In the above C program, the compiler does not know if "i" and "j' have the same values till runtime, so the compiler takes these values to be ambiguously aliased and assigns two separate registers to a[i] and a a[j]. The compiler can't tell if a change of the value in the register holding a[i] should also change the value in the register holding a[j]. Thus, the compiler is forced to generate code that flushes the new value of a[i] to memory and then re-loads the value of a[j] from memory. The compiler is forced not only to allocate a separate register for each, but also to flush and reload *all potentially aliased* registers each time the value in *any one* of those registers is modified. This problem is common in code working on arrays and/or pointers.

CRegs handle this problem efficiently with less memory access traffic. Before writing any values to these registers the processor checks for any register with same address field. In case it finds one, the hardware associatively updates both, the current register which is going to be written with this new value and the register with same address field. By doing so the hardware maintains coherence of these entries in a way similar to the implementing the Associativity of a cache. The difference between the CReg hardware and the Cache is that, unlike a cache, CRegs avoid making memory references on an aliased Load operation by using duplicating entries in the CReg array.

The important point to note here is that a cache can handle the ambiguously aliased values since it has the address field of the variables on it, but the problem with it is that it cannot be controlled by a compiler.

Despite the idea being twenty years old, the strangeness of requiring a new instruction set design has prevented CRegs from being widely applied. The only commercial implementation to date is the IA64 Advanced Load mechanism [11], which does not achieve the full benefit because it uses its CReg-like mechanism as a filter for memory references rather than as a replacement for conventional registers and cache. The idea of STM (Short Term Memory cell) [12] and Rack [13] is similar to CRegs but without the Associativity of CRegs. Trace cache and loop recognition systems employed by Intel in their P4 and i7 [14] [15] also use the CReg mechanisms but they just use it as a storage buffer rather than replacing the register and cache with these cache-registers in which case they could have improved the efficiency of the system by the help of the compiler.

#### **1.2.3 CACHE**

The several levels of Cache that were mentioned before are introduced to bridge the semantic gap between the processor and main memory speeds and act like a buffer which maintain quickly accessible copies of the data and instructions which are most likely to be needed by the processor. As long as the cache holds right data the processor effectively sees the cache access time with the large memory address. The Hardware cell of a cache is given below:

Index (Line Address)

Data

Tag (Line Address)

Status

Figure 2: The hardware structure of cache

Since 1969 when the first cache based computer was developed by IBM as IBM 360/85 [1], having a cache in the processor-memory system design is proving to be inefficient. The following points would make this clear.

- Having a cache only helps when there is a cache hit. It's the only case where the processor sees the actual intended speed called the cache access time rather that the memory access time. Misses are more costly here when compared to a cache-less memory hierarchy.

- A majority of data elements which are reference in a program are referenced so infrequently that other cache traffic is certain to evict these elements from cache before they are referenced again. In such cases, there is no benefit in placing the item in cache, but there is the excess overhead involved in evicting some other item out of cache to make room for this useless cache entry. This would prove more inappropriate in cases where a cache line is larger than a processor word in which case it has an additional penalty of loading an entire line from memory into cache. [2] [25]

- Since processors these days use SIMD registers, it is not wise to have same data in both cache and the long register lines. [Intel's MMX, SSE, Itanium, GPUs etc].

- Caches nowadays take up a lot of space on chip which could be used for better purposes [3].

Re-evaluation of many computer design concepts like compiler methods for optimization and parallelization [4][5], architecture concepts of RISC and CISC [6][7][8], should be opted and inspired since the traditional memory hierarchy which includes the cache designs is falling short of the required expectations of bridging the semantic gap between the processor and main memory.

#### **1.3 THESIS ORGANIZATION**

The thesis documentation is divided into 6 chapters. The first chapter presented the introduction along with motivation and background of LARs. The second chapter describes the idea of LARs along with its hardware structure. The third chapter describes the instruction set architecture of DATA LARs. The fourth chapter gives a detailed description of the DATA LARs hardware simulator of the straw-man model along with

the discussions about its tradeoffs. The fifth chapter gives the results where comparison of DATA LARs design with other architectures is explained along with some simple program examples run on the simulator. The sixth chapter concludes and gives the future work for this topic.

#### **CHAPTER 2**

#### 2. LARS

Line Associative Registers (LARs) concept is derived mainly from Associativity of CREGs and SWAR operations on wide lines of data. Compared to a normal CPU register, LAR can also hold the address of the starting object similar to a CREG and are wide SIMD registers similar to SWAR. LARs are assigned to both instructions and data when the processor's architecture design is considered. An Instruction LAR has the address of the starting object and is wide as discussed above whereas the DATA LARs are type tagged in addition to having the address field and the width. The address field could be used as a typed pointer to point to any object within the given LAR line. This makes it much easier for scalar operations on objects within a LAR to have great flexibility to access any field, not just the one in the lowest bits. Registers like MMX and SSE extensions [18][19] which utilize the SWAR concepts, are just wide registers which are not that convenient to be used for scalar operations as LARs could be used as discussed above.

Since the CPU registers are compiler friendly, LARs could be handled efficiently when compared to a Cache (because compiler doesn't know the address of the cache line). Moreover, the ambiguous aliasing flush/reload problem is handled by updating aliased objects in registers as in CREGs with the difference that this updating is extended to work with wider lines rather than single objects in registers.

This helps improve the memory bandwidth. Type tagging Line Associative Register Lines also bring a lot of advantages to the design. Since data LARs are type tagged at the load time this would decrease the instruction set considerably by removing the type conversion instructions thereby increasing the code density and increasing architectural regularity and simplifying the instruction set. Type conversions occur automatically in this design in the hardware itself according the conditions depending on the data types and signs that would be discussed later. The stores are lazy in this design. This would reduce the memory cycles at hand and above that this makes store instructions to be used for different purpose which in our case would be to do changes to the type information of

the LAR under use. Intel's iAPx432 [22] had type-tagged main memory when compared to LARs which has type-tagged registers. Type-tagging objects in memory worsened the dependence on memory performance.

Research on the concept of LARs began with the thesis of Krishna Melarkode [23] However, the initial ideas have proven to have many more complex implications than were originally realized. The prototype designed for this thesis is a straw man implementation with the parameters such as line width of the LAR scaled down to fit the standard FPGA. The main aim of the design is to present sufficient details so as to allow the reader to fully appreciate the complexity and logic involved in the LARs concept compared to a conventional processor.

The design implemented here is a 32-bit microprocessor with 6-stage pipeline to achieve higher throughput and shorter clock. There are 8 data LARs 64-bits wide (CPU registers which handle data), although this number could be varied anytime and the number of instruction LARs (CPU registers which handle code) is not fixed either. The actual design was intended to contain 32-data LARs 256-bits.

#### **2.1 DATA TYPES**

This chapter introduces data types defined for Line Associative Registers (LARs) architecture.

#### 2.1.1 FUNDAMENTAL DATA TYPES

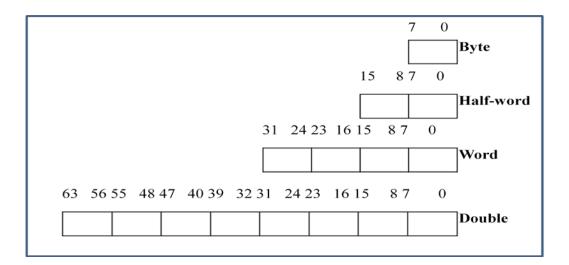

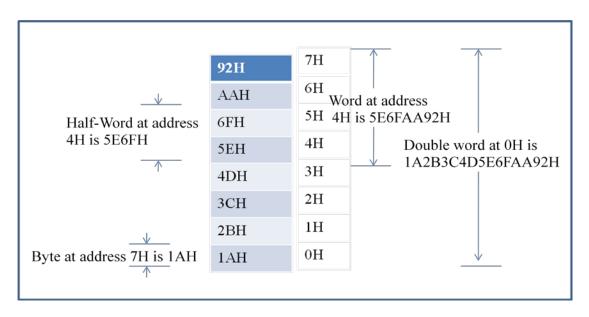

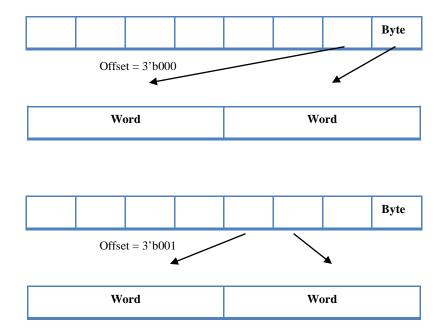

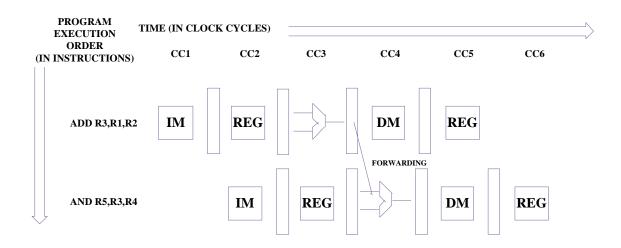

The fundamental data types are bytes, half-words, words and double-words. A byte is of 8-bits, a half-word is of 2 bytes (16-bits), a word is of 4 bytes (32-bits), and a double-word is of 8 bytes (64-bits) as shown in figure 3. Byte order of each of these data types when referenced as operands in memory is shown in the figure 4. The low byte (bits 0 through 7) of each data type occupies the lowest address in memory and that address is also the address of the operand. This is a "little endian" machine which means that bytes of a word are numbered starting from the least significant byte.

Figure 3: Fundamental Data Types

Figure 4: Bytes, Half words, Words and Double Words in memory

#### 2.1.2 PACKED SIMD DATA TYPES

The designed LARs architecture operates on 64-bits of packed SIMD data. The fundamental packed SIMD data types are defined as packed bytes, packed half-words, packed words and packed double-words. At the time of processing, the numeric SIMD operations on the CPU registers interpret these packed data types to contain packed or scalar byte, half-word, word, or double-word integer values.

| Packed Bytes       | 63 |  | 0 |

|--------------------|----|--|---|

| Packed Half Words  | 63 |  | 0 |

| Packed Words       | 63 |  | 0 |

| Packed Double Word | 63 |  | 0 |

Figure 5: Packed SIMD data types

#### 2.2 SIGNED AND UNSIGNED INTEGERS

Unsigned integers are ordinary binary values ranging from 0 to the maximum positive number that can be encoded in the selected operand size. Signed integers are two's complement binary values that can be used to represent both positive and negative integer values.

Unsigned integers are unsigned binary numbers contained in a byte, half-word, word, and double-word. Their values range from 0 to 255 for an unsigned byte integer, from 0 to 65,535 for an unsigned half-word integer, from 0 to  $2^{32}$ -1 for an unsigned word integer and from 0 to  $2^{64}$ -1 for an unsigned double word integer.

Signed integers are represented in two's complement form throughout this design. The sign bit is located in bit 7 in a byte integer, bit 15 in a half-word integer, bit 31 in a word integer, and bit 63 in a double word integer. Saturation arithmetic uses the following representations to fix the overflow or underflow values to some boundary. For an unsigned, 8-bit byte, the largest and the smallest represent-able values are FFh and 0x00; for a signed byte the largest and the smallest represent-able values are 7Fh and 0x80. This is important for pixel calculations where this would prevent a wrap-around add from

causing a black pixel to suddenly turn white while, for example, doing a 3D graphics Gouraud shading loop.

#### 2.3 MEMORY ALIGNMENT

Data structures are always aligned in this design. So words, double words, and quad words are all aligned in memory on natural boundaries. The natural boundaries for words, double words, and quad words are even-numbered addresses, addresses evenly divisible by four, and addresses evenly divisible by eight, respectively. The main advantage with this limitation is that it will improve the performance of programs. This is because the processor would require only one memory cycle to fetch an aligned data compared to two memory cycles required for an unaligned data.

#### 2.4 DATA LARS REGISTER SET

Data LARs are the CPU registers which handle data part of the processor. All the data LARs are assigned the address field, the type field and the dirty field as shown in the figure 6.

|      |   |      |   |    |      |     |        |         | Add    | lress  |        |       |       |

|------|---|------|---|----|------|-----|--------|---------|--------|--------|--------|-------|-------|

| Data |   | Data |   |    |      |     |        | 64-     | bits   | WDSZ   | ТҮР    | Dirty |       |

| LAR  |   |      |   | 64 | -bit |     |        |         | Tag    | Word   | 2-bits | 1-bit | 1-bit |

|      |   |      |   |    |      |     |        | 61-bits | offset |        |        |       |       |

|      |   |      |   |    |      |     |        |         |        | 3-bits |        |       |       |

| d0   | 7 | 6    | 5 | 4  | 3    | 2   | 1      | 0       |        | Bytes  | 2'b00  | 1'b0  | 1'b0  |

| d1   | - | 3    | ź | 2  |      | 1 0 |        | Half    | Word   | 2'b01  | 1'b0   | 1'b0  |       |

| d2   |   |      |   |    |      |     |        |         |        |        |        |       |       |

| d3   | 1 |      |   |    | 0    |     |        |         | Word   | 2'b10  | 1'b0   | 1'b0  |       |

| d4   |   |      |   |    |      |     |        |         |        |        |        |       |       |

| d5   |   |      |   | 0  |      |     | Double | Word    | 2'b11  | 1'b0   | 1'b0   |       |       |

| d6   |   |      |   |    |      |     |        |         |        |        |        |       |       |

| d7   |   |      |   |    |      |     |        |         |        |        |        |       |       |

Figure 6: The hardware structure of DATA LARs

There are 8 data LARs represented as "d" followed by "0 - 7" (0,1,2..7) 64-bits wide each which can hold one of the packed SIMD data types (8 packed bytes or 4 packed

half-words or 2 packed words or 1 packed double word). Each of these data LARs from d0 to d7 has an Address field, WDSZ field, TYP field and a Dirty field. The address field (64-bits in our case) is further classified into a TAG (61-bits) and a Word-Offset (3-bits). The whole address field acts as a typed pointer where TAG field points to the starting location of the LAR line and Word-Offset field is used to pick one of the objects within this line of data. So address operations can be scaled by object size much as the C programming language does for pointer arithmetic and moreover, scalar operations on objects within a LAR have full flexibility to access any field, not just the one in the lowest bits.

The WDSZ and TYP field are used to represent the type tagging information of the data that gets loaded from the main memory. When compared architectures with type tagging or object in main memory, LARs type tags the objects or say lines after they get loaded from the main memory. Type tagging the memory makes it expensive since it increases the memory bandwidth and space requirement. Overriding these tags would also be difficult.

WDSZ field is 2-bits wide this specifies if the data loaded into the data LARs is one of the packed data types. The table 1 below shows the different bit field settings for different data types.

TYP field is 1-bit wide and this specifies if the data loaded is Signed or Unsigned. The table 2 below shows the bit field variations for signed and unsigned data.

| WDSZ   | PACKED              |

|--------|---------------------|

| 2-bits | SIMD                |

|        | DATA TYPE           |

| 2'b00  | Packed Bytes        |

| 2'b01  | Packed Half Words   |

| 2'b10  | Packed Words        |

| 2'b11  | Packed Double Words |

| Table 1: Bit field | l variations | of WDSZ |

|--------------------|--------------|---------|

|--------------------|--------------|---------|

#### Table 2: Bit Field variation of TYP

| ТҮР   | SIGN          |

|-------|---------------|

| 1-bit |               |

| 1'b0  | Unsigned Data |

| 1'b1  | Signed Data   |

LARs architecture tries to reduce memory cycles as far as possible. It uses Lazy Store mechanism to store back the data from CPU registers to main memory. It has a Write-Buffer, whose size could be varied as necessary, which stores the dirty information spilled to the main memory. Dirty field (1-bit field) is used to know if the data in a certain data LAR has been changed due to some operation. If the processor tries to load some data into a dirty location, the dirty data is spilled to the Write-Buffer. For the current design, this data is sent to the main memory is a case where the buffer itself is full. In that situation, the whole pipeline is stalled and the buffer spills the excess data to main memory.

There would not be any need for store instructions in this case. So the store instructions are used for type castings, or say, to change the address, WDSZ and TYP fields of the current data LAR so that it could be used for a different purpose without actually loading the data again since the processor already knows if the required address is present in one of the data LARs or not. This would be further explained with an example in the third chapter.

#### **CHAPTER 3**

#### **3. INSTRUCTION SET ARCHITECTURE**

#### **3.1 DATA TRANSFER INSTRUCTIONS**

There are eight different LOAD instructions in this architecture whose opcodes are used for type tagging the DATA LARs. These instructions transfer data from the main memory to the LARs and type tag the registers by filling in the required information about the type and size of the data that is loaded. The difference between these instructions and the other architectures instructions like MIPS is the way they get executed; there would be an associative search of DATA LARs internally to check if the data at the calculated effective address has been already loaded by previous load instructions. This would save the cost of fetching the data (line of data) all the way from the main memory in case of a hit at the data LARs.

| Opcode  | DST     | SRC1    | SRC2    | IMMEDIATE |

|---------|---------|---------|---------|-----------|

| [31:27] | [26:22] | [21:17] | [16:12] | [11:0]    |

Figure 7: Format of LOAD instruction

The DEST LAR (destination DATA LAR), SRC1 (Source DATA LAR 1), and SRC2 (Source DATA LAR 2) are all five bit fields since these fields are aimed to address 32 DATA LARs instead of 8. Hence the architecture utilizes only 3 bits out of 5 to encode the register set and the two most significant bits are left in place and ignored in this prototype. And there is a 12-bit immediate field as shown.

The calculation of the effective address and the whole procedure of a load instruction could be better understood by an example. Let the instruction be

The instruction says that the data to be loaded from memory is an unsigned byte. The opcode for LOADUB is 5 'b00001, this opcode is sent to the DATA LARs along with the

data from main memory so that the TYP and WDSZ fields of the destination LAR can be filled simultaneously to 1'b0 for unsigned and 2'b0 for byte data respectively.

The TAG and WORDOFFSET fields together constitute the effective address calculated by ALU. The way the effective address is calculated is:

Effective addr = SRC1.Addr + SRC2.Data + immediate (Destination LAR)

Let us assume that the data stored at DATA LARs d2 and d3 are as shown below:

| Data |                   |   |   |   | Data  | l |        |              | Add     | ress   | WDSZ   | ТҮР   | Dirty |

|------|-------------------|---|---|---|-------|---|--------|--------------|---------|--------|--------|-------|-------|

| LAR  |                   |   |   |   | 64-bi | t |        |              | 64-     | bits   | 2-bits | 1-bit | 1-bit |

|      |                   |   |   |   |       |   |        |              | Tag     | Word   |        |       |       |

|      |                   |   |   |   |       |   |        |              | 61-bits | offset |        |       |       |

|      |                   |   |   |   |       |   |        |              |         | 3-bits |        |       |       |

| d1   | 7                 | 6 | 5 | 4 | 3     | 2 | 1      | 0            |         | Bytes  | 2'b00  | 1'b0  | 1'b0  |

| d2   |                   |   |   |   |       |   |        | 61'b0 3'b000 |         | 3'b000 | 2'b10  | 1'b0  | 1'b0  |

| d3   | 16'b0 16'b0 16'b0 |   |   |   |       |   | {10'b0 | ),6'b1}      | {61'b0, | 3'b111 | 2'b01  | 1'b0  | 1'b0  |

|      |                   |   |   |   |       |   |        |              | 1'b1}   |        |        |       |       |

Figure 8: DATA LARs before the LOAD instruction

| Destination DATA LAR   | = | d2.address + d3.data + 5;                   |

|------------------------|---|---------------------------------------------|

| dl's effective address |   |                                             |

|                        | = | 0 + {58'b0, 6'b1} + 5;                      |

|                        | = | 000000 + 111111 + 000101;                   |

| Effective Address      | = | 1000100;                                    |

| =>Tag                  | = | 61'b {57'b0, 4'b1000} = (8) <sub>10</sub> ; |

| =>Word Offset          | = | $3'b100 = (4)_{10};$                        |

The 64 bit address (TAG+WORDOFFSET) of d2 (source 1) added with 64 bit data of d3 (source 2) and 5 (the 12 bit immediate field) would be the effective address. The obtained 64 bit data from the main memory using this effective address, along with the opcode, will be sent to the DATA LAR in the last stage. Even the effective address would be

utilized here in the form of TAG and WORDOFFSET for the destination DATA LAR. The word offset is 3 bits wide since the DATA LAR is 64 bits wide and is byte accessible (eight bytes accessed by three offset bits).

| Data |       |              | Data       |              | Addı     | ess    | WDSZ   | ТҮР   | Dirty |

|------|-------|--------------|------------|--------------|----------|--------|--------|-------|-------|

| LAR  |       |              | 64-bit     |              | 64-b     | oits   | 2-bits | 1-bit | 1-bit |

|      |       |              |            |              | Tag      | Word   |        |       |       |

|      |       |              |            |              | 61-bits  | offset |        |       |       |

|      |       |              |            |              |          | 3-bits |        |       |       |

| d1   | Data  | a from dat   | ta memory  | y from the   | 61'b1000 | 3'b100 | 2'b00  | 1'b0  | 1'b0  |

|      | calcu | lated effect | ctive addr | ess location |          |        |        |       |       |

| d2   |       |              |            |              | 61'b0    | 3'b000 | 2'b10  | 1'b0  | 1'b0  |

| d3   | 16'b0 | 16'b0        | 16'b0      | {10'b0,6'b1} | {61'b0,  | 3'b111 | 2'b01  | 1'b0  | 1'b0  |

|      |       |              |            |              | 1'b1}    |        |        |       |       |

After the Load the data LARs will look like this

Figure 9: DATA LARs after the LOAD instruction

As explained before, the LARs architecture would not go to the main memory blindly. It would stall the whole pipeline for one clock cycle and perform an associative search for every LOAD instruction to check if the calculated effective address is already present in one of the DATA LARs. In the above case, if 64 'b1000100 address is already present in one of the LARs then the fetch cycle is canceled and a copy of the already present data would be placed at the DATA LAR d1.

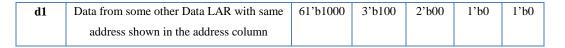

Figure 10: DATA LARs d1 in the case of cancel LOAD

Therefore, in order to save the cost of fetching the data all the way from the data memory this architecture uses one clock cycle to associatively search for the calculated address in the DATA LARs. This cost would be more visible when we are dealing with SIMD data (multiple data elements in one line). This approach is advantageous because caches are not employed to store vector data elements [2] [3] [25] as it would be a waste of space to have long lines of data in both the registers and the cache.

| Opcod    | le  | Instruction | Description                                                                                                                                 |

|----------|-----|-------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Binary   | Hex |             |                                                                                                                                             |

| 5'b00001 | 01  | LOADUB      | Check for the required effective address in the data LARs and then Load unsigned byte from memory in case you can't find that address.      |

| 5'b00010 | 02  | LOADUHW     | Check for the required effective address in the data LARs and then Load unsigned half-word from memory in case you can't find that address. |

| 5'b00011 | 03  | LOADUW      | Check for the required effective address in the data LARs and then Load unsigned word from memory in case you can't find that address.      |

| 5'b00100 | 04  | LOADUDW     | Check for the required effective address in the data LARs and then Load unsigned double from memory in case you can't find that address.    |

| 5'b00101 | 05  | LOADSB      | Check for the required effective address in the data LARs and then Load signed byte from memory in case you can't find that address.        |

| 5'b00110 | 06  | LOADSHW     | Check for the required effective address in the data LARs and then Load signed half-word from memory in case you can't find that address.   |

| 5'b00111 | 07  | LOADSW      | Check for the required effective address in the data LARs and then Load signed word from memory in case you can't find that address.        |

| 5'b01000 | 08  | LOADSDW     | Check for the required effective address in the data LARs and then Load signed double from memory in case you can't find that address.      |

Table 3: Variations of LOAD instruction

#### **3.2 TYPE CASTING INSTRUCTIONS**

Stores are unnecessary for this architecture as it supports lazy store mechanism through which it updates the memory with the changes made to the DATA LARs. Hence STORE instructions are used for type casting in this architecture. As explained above, DATA LARs are all type tagged and therefore the type tags are updated on the new destination LAR. Whenever there is overwrite of data into one of the DATA LARs, the current data is sent into the write buffer from where it will be sent to data memory when the processor finds a free bus cycle. The format of the store instruction is:

| Opcode  | DST     | SRC1    | SRC2    | IMMEDIATE |

|---------|---------|---------|---------|-----------|

| [31:27] | [26:22] | [21:17] | [16:12] | [11:0]    |

Figure 11: Format of STORE instruction

All the fields remain the same for store instructions as they were for load instructions. The way the type castings happen when a store instruction is encountered is better explained with an example. Consider that these two instructions occur in the order shown.

LOADUB d1, d2, d3, 5

#### STORESHW d1, d4, d5, 10

| DATA LAR |        |       |       |   | ata                |   |   |        | Add           | lress          | WDSZ  | ТҮР   | D     |

|----------|--------|-------|-------|---|--------------------|---|---|--------|---------------|----------------|-------|-------|-------|

|          | 64 bit |       |       |   |                    |   |   |        | TAG<br>61 bit | OFFSET<br>3bit | 2 bit | 1 bit | 1 bit |

| d1       | 0      | 5     | 0     | 1 | 0                  | 3 | 0 | 4      | 8             | 4              | 2'b00 | 1'b0  | 1'b0  |

| d2       |        | 32'b( | )     |   | {28'b0,4'b1}       |   |   | }      | 61'b0         | 3'b000         | 2'b10 | 1'b0  | 1'b0  |

| d3       | 16     | 'b0   | 16'b( | 0 | 16'b0 {10'b0,6'b1} |   |   | ,6'b1} | 1             | 7              | 2'b01 | 1'b0  | 1'b0  |

| d4       | 0      | 0     | 0     | 0 | 0                  | 0 | 0 | 4      | 0             | 2              | 2'b00 | 0     | 0     |

| d5       |        | 0     |       |   | 16                 |   |   |        | 3             | 4              | 2'b10 | 0     | 0     |

Figure 12: DATA LARs before the STORE instruction

The effective address of the STORE instruction will be calculated in the same way as for the LOAD instructions. So the calculated value will be:

The content of the DATA LAR d1 will not be changed after the store instruction. Their type fields will be changed. So the data values will look as if they are words now instead of bytes as they were before the store.

| DATA LAR |         |       |       | D | ata                |   |   |        | Add                  | ress           | WDSZ  | ТҮР   | D     |

|----------|---------|-------|-------|---|--------------------|---|---|--------|----------------------|----------------|-------|-------|-------|

|          | 64 bit  |       |       |   |                    |   |   |        | <b>TAG</b><br>61 bit | OFFSET<br>3bit | 2 bit | 1 bit | 1 bit |

| d1       | 5 1     |       |       |   | 3 4                |   | 5 | 4      | 2'b01                | 1'b1           | 1'b0  |       |       |

| d2       |         | 32'b( | )     |   | {28'b0,4'b1}       |   |   | }      | 61'b0                | 3'b000         | 2'b10 | 1'b0  | 1'b0  |

| d3       | 16      | 'b0   | 16'b0 | ) | 16'b0 {10'b0,6'b1} |   |   | ,6'b1} | 1                    | 7              | 2'b01 | 1'b0  | 1'b0  |

| d4       | 0 0 0 0 |       |       | 0 | 0                  | 0 | 0 | 4      | 0                    | 2              | 2'b00 | 0     | 0     |

| d5       |         | 0     |       |   | 16                 |   |   | -      | 3                    | 4              | 2'b10 | 0     | 0     |

Figure 13: DATA LARs after the STORE instruction

The first LOAD instruction loads d1 with some TAG and WORDOFFSET fields by calculating the effective address as shown above and fills the WDSZ and TYP fields with 2'b00 (byte) and 1'b0 (unsigned) bits. When the STORE instruction gets executed, it will replace all the fields of d1 leaving the 64-bit data associated with it unchanged. WDSZ field will change to 2'b10 (word) and TYP field will change to 1'b1 (signed). So, we can see that STORE instruction does not store the data from d1 to the effective address calculated as we might expect from conventional architectures. It simply changes the address, type and word size fields of d1.

| Table 4: Variations of the STORE instruction | Table 4: | Variations | of the ST | FORE | instruction |

|----------------------------------------------|----------|------------|-----------|------|-------------|

|----------------------------------------------|----------|------------|-----------|------|-------------|

| Opcod    | le  | Instruction | Description                                               |

|----------|-----|-------------|-----------------------------------------------------------|

| Binary   | Hex |             |                                                           |

| 5'b01001 | 09  | STOREUB     | Change destination LAR's data type to unsigned byte.      |

| 5'b01010 | 0A  | STOREUHW    | Change destination LAR's data type to unsigned half-word. |

| 5'b01011 | 0B  | STOREUW     | Change destination LAR's data type to unsigned word.      |

| 5'b01100 | 0C  | STOREUDW    | Change destination LAR's data type to unsigned double.    |

| 5'b01101 | 0D  | STORESB     | Change destination LAR's data type to signed byte.        |

| 5'b01110 | 0E  | STORESHW    | Change destination LAR's data type to signed half-word.   |

| 5'b01111 | 0F  | STORESW     | Change destination LAR's data type to signed word.        |

| 5'b10000 | 10  | STORESDW    | Change destination LAR's data type to signed double.      |

#### **3.3 ARITHMETIC AND LOGICAL INSTURCTIONS**

The arithmetic and logical instructions are designed to support the different packed and unpacked SIMD data types. The DATA LARs architecture supports ADD, SUB, AND, OR, and EXOR operations. Unlike MMX [18][19] or SSE designs, where the architecture has 57 or more opcodes to actually distinguish the type conversion operations, LARs design has only five different opcodes for these five instructions and the rest of the bits of the 32-bit instruction are used as control bits to help resolve the boundaries of the type conversions.

Therefore, all these type conversions take place during the flow of data from one pipeline stage to another and not as separate instructions in which case we would have to wait for this converted data to be placed back in the registers. Hence this design would reduce the instruction fetch bandwidth and would be faster compared to the present architectures which employ separate registers for SIMD operations.

The basic arithmetic instruction format would be

| Opcode  | Dest    | SRC1    | SRC2    | SV   | Offset1 | Offset2 | Dest offset | NO    |

|---------|---------|---------|---------|------|---------|---------|-------------|-------|

| [31:27] | [26:22] | [21:17] | [16:12] | [11] | [10:8]  | [7:5]   | [4:2]       | USE   |

|         |         |         |         |      |         |         |             | [1:0] |

#### Figure 14: Format of Arithmetic instructions

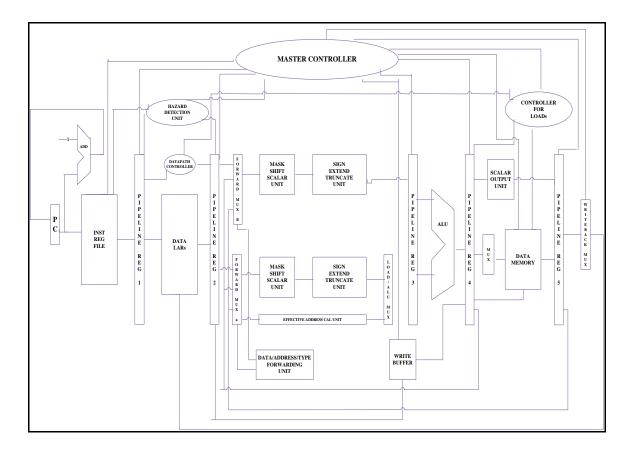

The ADD and SUB instructions have 4 variations in them. The 11<sup>th</sup> bit of the 32-bit instruction is used to specify if it is a vector or a scalar instruction. The offsets from bit 1 to bit 10 are all used for the type conversions for packing and unpacking the data to required ALU boundaries. Vector operations are made on the whole array of data inside a DATA LAR, and scalar operations are made on the data pointed to by the WORDOFFSET of that particular data LAR. All calculations are made by taking WDSZ and TYP bits into consideration which are filled by the instructions executed earlier in that pipeline process. In case of data hazards, forwarding of these required bits (WDSZ and TYP) would be done and for cases where this is not possible, pipeline bubbles would be introduced to stall until the required data is ready to be forwarded.

| Opcod    | le  | Instruction | Description                                                                                                                                                                                                                                |

|----------|-----|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Binary   | Hex |             |                                                                                                                                                                                                                                            |

| 5'b10010 | 12  | ADD         | This is classified into ADDV and ADDS namely vector or scalar addition depending on the 12 <sup>th</sup> bit of the instruction. And at the end of this instruction, associatively update the data LARs with same address field.           |

| 5'b10011 | 13  | SUB         | This is classified into SUBV and SUBS, vector or scalar subtraction respectively depending on the 12 <sup>th</sup> bit of the instruction. And at the end of this instruction, associatively update the data LARs with same address field. |

| 5'b10100 | 14  | MUL         | (Reserved) for multiplication.                                                                                                                                                                                                             |

| 5'b10101 | 15  | AND         | Perform AND operation on the two source LAR lines. And at the end of this instruction, associatively update the data LARs with same address field. Classified into ANDS and ANDV.                                                          |

| 5'b10110 | 16  | OR          | Perform OR operation on the two source LAR lines. And at the end of this instruction, associatively update the data LARs with same address field. Classified into ORS and ORV.                                                             |

| 5'b10111 | 17  | EXOR        | Perform EXOR operation on the two source LAR lines. And at the end of this instruction, associatively update the data LARs with same address field. Classified into EXORS and EXORV.                                                       |

Table 5: Arithmetic instructions and their variations

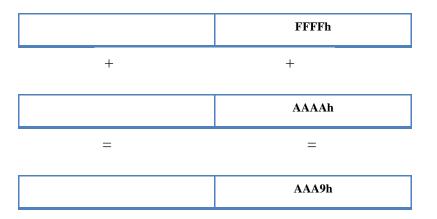

All the ALU operations follow modular arithmetic, also known as wrap-around arithmetic. It is the normal computer arithmetic in which the stored result is the low n bits of the actual result, where n is the size of the space in which the result is to be stored. This is equivalent to taking the actual result modulo the maximum value storable in the available space. Most existing instruction sets include some form of modular addition except for MVI, which does not, and the extensions to MMX, which use the MMX instructions for this purpose. When the source operand's word size is bigger than the destination operand's word size, the bits that are in excess when compared to the destination operand's bits will be discarded. Figure 15 will explain this procedure.

Figure 15: modular arithmetic followed by the ALU

In this case, the right-most result exceeds the maximum value representable in 16-bits thus it wraps around. This is the way regular computer arithmetic behaves. FFFFh + AAAAh would be a 17 bit result. The 17th bit is lost because of wrap around, so the result is AAA9h.

#### **3.3.1 TYPE CONVERSIONS**

Since LARs design is type tagged, the data type information is used by the hardware to process the SIMD data by keeping track of the data type fields. There will not be any explicit data conversions generated by the compiler as in the Intel's iAPX432 [22], so considerable compiler overhead is saved.

The third pipeline stage is used for these type conversions. The two operands are sent to the Sign Extension-Truncation Unit and in a case where the operand is of different word size when compared to the destination register's word size field, depending on the sign bit of the operand, sign extension or truncation of the operand's data to the destination operand's word size takes place. If the operand is unsigned, sign extension would be appending zeros and if the operand is signed, sign extension takes place by appending ones. In case of truncation, the conversion follows saturation arithmetic rules. It is best explained by considering what happens in computing an assignment like:

C=A+B

#### **3.3.1.1 SATURATION ARITHMETIC**

Saturation arithmetic is a form of computer conversion in which the result is set to the maximum storable value of the same sign when an overflow occurs. This form of addition is used primarily for multimedia applications in which the data value represents some physical parameter whose value should not wrap with incremental changes. For example, adjusting the volume level of a sound signal can result in overflow, and saturation causes significantly less distortion to the sound than wrap-around (wrap around may result in a sudden drop from high to 0). LARs architecture follows saturation

arithmetic rules to truncate the operand's data in case it does not fit in the destination LAR.

Consider a case where A is byte (8 bits), B is a half word (16-bits) and C is word (32-bits). Now the boundaries of the ALU will be set according to the destination register's word size which is a word (32-bits). A will be converted from 64-bit data with bytes in it to 64-bit data with words in it. We take a temporary register D which acts as a pipeline register for the later stage and do the following operation.

Figure 16: Type conversion- Rules for sign extension in the DATA LARs architecture

The two cases with offset as 3'b000 and 3'b001 are derived from the offset field of the 32-bit instruction. If the offset of the source register A is given to be 3'b000 then the type conversion will be applied on the first two eight bits of the DATA LAR A. If the offset is 3'b001 then the next two 8-bits of A[23:16] and A[31:24] will be considered and so on. There are 3-bits for offset because the maximum possibility of selecting a pair of data elements occurs in case if A is a byte and c is a double where there are 8 possibilities.

D[7:0] = A[7:0]; D[31:8] = 24 zero's D[39:32] = A[15:8]; D[63:40] = 24 zero's. If A is signed, then sign extension is performed:

```

D[7:0] = A[7:0];

If (A[7] == 1'b1) C[31:8] = 24 1's

else C[31:8] = 24 0's;

D[39:32] = A[15:8];

If (A[15] == 1'b1) C[63:40] = 24 1's

else C[63:40] = 24 0's;

```

Now consider a case where we have to truncate the operand A to fit in the destination register. Let A be a word (32-bits), B be a half word (16-bits) and C be a byte. The ALU boundaries will be set to byte. If A is an unsigned word data type we compare the magnitudes of A[31:0] and A[7:0] and if A[31:0] is greater than or equal to A[7:0] we place 8 1's in D[7:0] which is greatest possible number for unsigned numbers or else we place A[7:0] in D[7:0]. We do the same to the next 32 bits of A and place the truncated result in D[15:8]. The rest of D[63:16] is filled with zeros.

Figure 17: Type conversion- saturation arithmetic rules for packing data

In case of signed data type we see if the most significant bit of A is 1 or not. If it is a 1 then we replace the C[7:0] with 8'b10000000 which is the least negative number. If it is not we check for the magnitudes again and replace D[7:0] with 8'b0111111 which is greatest positive number for signed numbers in the case A[31:0] > A[7:0]. If it is not greater then we just copy the value A[7:0] into D[7:0]. The rest is again filled with zeros.

#### **3.3.2 SCALAR ALU OPERATIONS**

Unlike SSE-1 or SSE-2 extensions, LARs can perform flexible scalar operations [24]. When the SV bit (11<sup>th</sup> bit of the instruction) is high the processor considers the instruction to be a scalar instruction. In this case we allow only the data pointed to by the word offset to pass through to the pipeline register which supplies the operands to the ALU. This isolated data is sign extended or truncated according to the destination LAR's WDSZ and TYP fields. Finally, after the data is processed at the ALU, we place the data at the position pointed to by the destination LAR's word offset field. The following example explains the way in by which a scalar ADD instruction is executed:

| ADDS | D1, | D4, | D5; |

|------|-----|-----|-----|

|------|-----|-----|-----|

| DATA |      |                           |     | Data | Ļ |           |     |   | Add            | ress  | WDSZ  | ТҮР   | D    |

|------|------|---------------------------|-----|------|---|-----------|-----|---|----------------|-------|-------|-------|------|

| LAR  |      | 64 bitTAGOFFSET61 bit3bit |     |      |   | 64 bit    |     |   | OFFSET<br>3bit | 2 bit | 1 bit | 1 bit |      |

| d1   | 0    | 5h                        | 0   | 1h   | 0 | 0 3h 0 4h |     |   | 8              | 4     | 2'b00 | 1'b0  | 1'b0 |

| d2   |      | 0                         |     |      |   | FFh       |     |   | 0              | 0     | 2'b10 | 1'b0  | 1'b0 |

| d3   | d3 0 |                           | 0 0 |      | 0 |           | 3Fh |   | 1              | 6     | 2'b01 | 1'b0  | 1'b0 |

| d4   | 0    | 0                         | 0   | 0    | 0 | 5h 0 4h   |     | 2 | 2              | 2'b00 | 0     | 0     |      |

| d5   |      | FFFI                      | Fh  |      |   | Fh        |     | 3 | 4              | 2'b10 | 0     | 0     |      |

Figure 18: DATA LARs before the ADDs Instruction

The address of d4 points to the third location (byte) from the right. That particular byte is taken out and sent to the conversion unit where it will be aligned with the boundaries of the ALU as discussed before. Here the boundaries of ALU are set to byte since the destination LAR's WDSZ is byte, so there will be no need to convert the contents of d4. Since d5 has words in it, its contents will be truncated to bytes as explained before. Only the second word which is FFFFh is sent out to get converted since the word offset is pointing to it.

After masking and shifting the data pointed to by the offset is extracted out and truncated. Only after these operations does the processor add the two operands. The destination LAR d1's contents will be brought along through the pipeline registers, and at the end of the ALU operation the result will be shifted to the position pointed to by the destination LAR's word offset and placed at the required position in that pipeline register. After the whole scalar arithmetic operation, the shifted sum replaces the data pointed to by the word offset of the d1 DATA LAR. So, 1h is replaced by 4h. The following figure gives us the end result.

| DATA |       |    |   | Data  |         |           |  |   | Add                  | lress                 | WDSZ  | ТҮР   | D     |

|------|-------|----|---|-------|---------|-----------|--|---|----------------------|-----------------------|-------|-------|-------|

| LAR  |       |    |   | 64 bi | t       |           |  |   | <b>TAG</b><br>61 bit | <b>OFFSET</b><br>3bit | 2 bit | 1 bit | 1 bit |

| d1   | 0     | 5h | 0 | 4h    | 0       | 0 3h 0 4h |  |   | 8                    | 4                     | 2'b00 | 1'b0  | 1'b0  |

| d2   |       | 0  |   |       |         | FFh       |  |   | 0                    | 0                     | 2'b10 | 1'b0  | 1'b0  |

| d3   | 0 0   |    | 0 |       | 0 0 3Fh |           |  | 1 | 6                    | 2'b01                 | 1'b0  | 1'b0  |       |

| d4   | 0     | 0  | 0 | 0     | 0       | 5h 0 4h   |  | 2 | 2                    | 2'b00                 | 0     | 0     |       |

| d5   | FFFFh |    |   |       | Fh      |           |  | 3 | 4                    | 2'b10                 | 0     | 0     |       |

Figure 19: DATA LARs after the ADDs instruction. d1's value pointed by the word offset is changed from 1h to 4h

#### **3.4 NO-OP**

This is used by the hardware internally to introduce pipeline bubbles in case the forwarding unit does not meet the data hazards requirements. This is recognized by its opcode field which is all zeroes- 5'b00000. When this opcode is seen at the second stage (Instruction Decode Stage), the hardware makes all the control signals required by the pipeline hardware for particular ID stage to point to do harmless work, thereby acting like a pipeline bubble.

#### **3.5 LOADDUMMY**

This instruction is used before an ALU instruction when the destination DATA LAR's address and type fields are not set by a previous instruction. This is necessary because of the way this architecture is designed. The type tags are placed on the DATA LARs along with the fetched data from main memory by the LOAD instructions. So for cases where the DATA LAR has to used before a LOAD or STORE instruction has filled its contents, this instruction is sent through the pipe just before the main instruction. The hardware recognizes this instruction and lets it pass through the pipe like a STORE instruction. So this instruction has the same format as the STORE or a LOAD with same effective address calculation procedure. Its opcode is 5'b11111.

# 3.5 SUMMARY OF INSTRUCTION SET ARCHITECTURE

# Table 6: Summary of Instruction Set Architecture

| Opcode Inst |     | Instruction | Description                                                                                               |

|-------------|-----|-------------|-----------------------------------------------------------------------------------------------------------|

| Binary      | Hex |             |                                                                                                           |

| 5'b00000    | 00  | NO-OP       | This is no operation instruction which is used by the hardware to introduce a pipeline                    |

|             |     |             | bubble in case of data hazards.                                                                           |

| 5'b00001    | 01  | LOADUB      | Check for the required effective address in the data LARs and then Load unsigned byte                     |

|             |     |             | from memory in case you can't find that address.                                                          |

| 5'b00010    | 02  | LOADUHW     | Check for the required effective address in the data LARs and then Load unsigned half-                    |

|             |     |             | word from memory in case you can't find that address.                                                     |

| 5'b00011    | 03  | LOADUW      | Check for the required effective address in the data LARs and then Load unsigned word                     |

|             |     |             | from memory in case you can't find that address.                                                          |

| 5'b00100    | 04  | LOADUDW     | Check for the required effective address in the data LARs and then Load unsigned double                   |

|             |     |             | from memory in case you can't find that address.                                                          |

| 5'b00101    | 05  | LOADSB      | Check for the required effective address in the data LARs and then Load signed byte                       |

|             |     |             | from memory in case you can't find that address.                                                          |

| 5'b00110    | 06  | LOADSHW     | Check for the required effective address in the data LARs and then Load signed half-                      |

|             |     |             | word from memory in case you can't find that address.                                                     |

| 5'b00111    | 07  | LOADSW      | Check for the required effective address in the data LARs and then Load signed word                       |

|             |     |             | from memory in case you can't find that address.                                                          |

| 5'b01000    | 08  | LOADSDW     | Check for the required effective address in the data LARs and then Load signed double                     |

|             |     |             | from memory in case you can't find that address.                                                          |

| 5'b01001    | 09  | STOREUB     | Change destination LAR's data type to unsigned byte.                                                      |

| 5'b01010    | 0A  | STOREUHW    | Change destination LAR's data type to unsigned half-word.                                                 |

| 5'b01011    | 0B  | STOREUW     | Change destination LAR's data type to unsigned word.                                                      |

| 5'b01100    | 0C  | STOREUDW    | Change destination LAR's data type to unsigned double.                                                    |

| 5'b01101    | 0D  | STORESB     | Change destination LAR's data type to signed byte.                                                        |

| 5'b01110    | 0E  | STORESHW    | Change destination LAR's data type to signed half-word.                                                   |

| 5'b01111    | 0F  | STORESW     | Change destination LAR's data type to signed word.                                                        |

| 5'b10000    | 10  | STORESDW    | Change destination LAR's data type to signed double.                                                      |

| 5'b10010    | 12  | ADD         | This is classified into ADDV and ADDS namely vector or scalar addition depending on                       |

|             |     |             | the 12 <sup>th</sup> bit of the instruction. And at the end of this instruction, associatively update the |

|             |     |             | data LARs with same address field.                                                                        |

| 5'b10011    | 13  | SUB         | This is classified into SUBV and SUBS, vector or scalar subtraction respectively                          |

|             |     |             | depending on the 12 <sup>th</sup> bit of the instruction. And at the end of this instruction,             |

|             |     |             | associatively update the data LARs with same address field.                                               |

|             |     |             | 1                                                                                                         |

| 5'b10100 | 14 | MUL       | (Reserved) for multiplication.                                                      |

|----------|----|-----------|-------------------------------------------------------------------------------------|

| 5'b10101 | 15 | AND       | This is classified into ANDS and ANDV namely scalar or vector And operation         |

|          |    |           | depending on the 12th bit of the instruction. And at the end of this instruction,   |

|          |    |           | associatively update the data LARs with same address field.                         |

| 5'b10110 | 16 | OR        | Perform ORS or ORV operation on the two source LAR lines. And at the end of this    |

|          |    |           | instruction, associatively update the data LARs with same address field.            |

| 5'b10111 | 17 | EXOR      | Perform EXORS or EXORV operation on the two source LAR lines. And at the end of     |

|          |    |           | this instruction, associatively update the data LARs with same address field.       |

| 5'b11111 | 1f | LOADDUMMY | This is just a dummy instruction sent before an ALU instruction in a case where the |

|          |    |           | destination DATA LAR does not have any of the fields set.                           |

|          |    |           |                                                                                     |

Table 7: Summary of Instruction Set Architecture (contd...)

#### **CHAPTER 4**

## 4. DATA LARS ARCHITECTURE

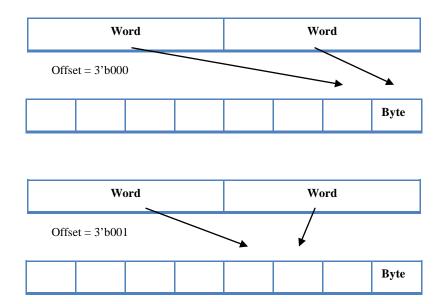

Figure 20: Block diagram of DATA LARs architecture design

The DATA LARs Architecture design is a six-stage pipelined architecture. The stages are named as follow:

- Stage 1: Instruction Fetch

- Stage 2: Instruction Decode

- Stage 3: Conversion

- Stage 4: Execution

- Stage 5: Memory

- Stage 6: Write Back

The Hardware units designed and used for this architecture are as follow:

- Instruction Register File with 32 32-bit registers to give instructions every cycle to the data path. Since this design being a simulator for testing the DATA LARs unit in an ordinary architecture (replacing the normal CPU registers), there is no instruction memory that is actually being used to fetch code from. This register file just acts as a continuous supplier of instructions to test the actual concept of DATA LARs.

- The DATA MEMORY is designed to supply the 64-bit data required by the 64-bit wide DATA LARs. So it's designed to contain 16 64-bit wide registers. This design is this small because of the chip constraints that it is being design on. The main aim of this design is to fit as many registers as possible to actually test the validity of the concepts that it is based on and in this process add some more ideas to make it work and be efficient.

- The DATA LARs unit which is the replacement of the normal CPU registers when compared to a normal architecture. These registers are 132-bits wide each as they were described in the section 2. The actual data is of 64-bits wide SIMD data and the rest of the bits are used to store the address and type information of the same. There are about 8 of these registers employed in the current design.

- Five pipeline registers named as IF/ID, ID/CONV, CONV/EX, EX/MEM, MEM/WB.

- Write Buffer with two 125-bit registers to lazy-store the evicted data and address from the DATA LARs to main memory.

- There are 3 ALUs in this design. The first ALU is fixed to add only and it is for incrementing the program counter to point to the next instruction in the Instruction Fetch stage. The second ALU is also fixed to add only in the conversion stage where it is used as an initial adder for calculating the main effective address for LOAD and STORE instructions. And the third ALU is a carry select adder which is used for calculating ADD, SUB, AND, OR and EXOR instructions and also for the final effective address calculation in case of LOAD and STORE instructions.

- The MASK SHIFT SCALAR UNIT is activated only for scalar operations. This unit allows only the required data pointed by the WORD OFFSET field of the particular DATA LAR in question. It masks the rest of the data and shifts it to the least significant bit position.

- The SIGN EXTEND/TRUNCATE UNIT is the main hardware block where all the sign extensions and compressions required by the operand's data to level according to the ALU's boundaries are made. The ALU's boundaries are set according to the type of the destination DATA LAR.

- The EFFECTIVE ADDRESS CALULATION UNIT is used to add the initial two operands: The 64-bit address and the sign extended 12-bit immediate field.

- The SCALAR OUTPUT UNIT shifts the ALU output back to its original position to which the destination DATA LAR's WORD OFFSET field was pointing to. And this shifted output is placed back in the old destination DATA LAR so that only the pointed data is changed.

- Since the DATA LARs architecture is type tagged and also lets the registers contain the address of the data, forwarding information to prevent data hazards has to be done for all the three fields of the DATA LAR. Therefore, the DATA/ADDRESS/TYPE FORWARDING UNIT does all the three forwards.

- The ALU at the Execution stage comprises of a 64-bit carry select adder with a provision to add byte sized 64-bit packed SIMD data. It could be viewed as a collection of eight 8-bit adders. The carries from these adders are monitored and managed by the hardware block called the ANDING UNIT.

- The HAZARD DETECTION UNIT detects the data hazards which cannot be cured by the forwarding unit. It sends the main controller signals to stall the pipeline process by introducing a no-op instruction.

- There are three controllers in this design. The first is DATAPATH CONTROLLER. This generates signals to hardware in the later stages which solely depend on the opcode. The second controller is the CONTROLLER FOR LOADs. This is really important as it is responsible to send the interrupt signal to main controller to stall the whole pipeline process for one clock cycle in case of a LOAD instruction. This controller actually incorporates the main concept of

LARs which is to check for a possible match of effective address in the DATA LARs itself due to the previous LOAD instructions. In case of a match of the calculated effective address in the DATA LARs, the actual fetch cycle for data from main memory is cancelled and a copy of the found data at this address location inside the DATA LAR is sent to the MEM/WB pipeline register, after which this data would be copied into the destination DATA LAR. This is a structural hazard and this controller deals with the same issue.