University of Kentucky UKnowledge

University of Kentucky Master's Theses

**Graduate School**

2010

# A NOVEL MESSAGE ROUTING LAYER FOR THE COMMUNICATION MANAGEMENT OF DISTRIBUTED EMBEDDED SYSTEMS

Darren Jacob Brown University of Kentucky, darrenjacobbrown@gmail.com

Right click to open a feedback form in a new tab to let us know how this document benefits you.

#### **Recommended Citation**

Brown, Darren Jacob, "A NOVEL MESSAGE ROUTING LAYER FOR THE COMMUNICATION MANAGEMENT OF DISTRIBUTED EMBEDDED SYSTEMS" (2010). *University of Kentucky Master's Theses*. 41. https://uknowledge.uky.edu/gradschool\_theses/41

This Thesis is brought to you for free and open access by the Graduate School at UKnowledge. It has been accepted for inclusion in University of Kentucky Master's Theses by an authorized administrator of UKnowledge. For more information, please contact UKnowledge@lsv.uky.edu.

#### ABSTRACT OF THESIS

### A NOVEL MESSAGE ROUTING LAYER FOR THE COMMUNICATION MANAGEMENT OF DISTRIBUTED EMBEDDED SYSTEMS

Fault tolerant and distributed embedded systems are research areas that have the interest of such entities as NASA, the Department of Defense, and various other government agencies, corporations, and universities. Taking a system and designing it to work in the presence of faults is appealing to these entities as it inherently increases the reliability of the deployed system. There are a few different fault tolerant techniques that can be implemented in a system design to handle faults as they occur. One such technique is the reconfiguration of a portion of the system to a redundant resource. This is a difficult task to manage within a distributed embedded system because of the distributed, directly addressed data producer and consumer dependencies that exist in common network infrastructures. It is the goal of this thesis work to develop a novel message routing layer for the communication management of distributed embedded systems that reduces the complexity of this problem. The resulting product of this thesis provides a robust approach to the design, implementation, integration, and deployment of a distributed embedded system.

KEYWORDS: Message Routing, Broadcast Network, Distributed Embedded Systems, Communication Management Mechanism, Fault Tolerance

> Darren Jacob Brown December 3, 2010

## A NOVEL MESSAGE ROUTING LAYER FOR THE COMMUNICATION MANAGEMENT OF DISTRIBUTED EMBEDDED SYSTEMS

By

Darren Jacob Brown

James E. Lumpp, Jr., Ph.D. Director of Thesis

Stephen D. Gedney, Ph.D.

Director of Graduate Studies

December 3, 2010

### RULES FOR THE USE OF THESES

Unpublished theses submitted for the Master's degree and deposited in the University of Kentucky Library are as a rule open for inspection, but are to be used only with due regard to the rights of the author. Bibliographical references may be noted, but quotations or summaries of parts may be published only with permission of the author, and with the usual scholarly acknowledgments.

Extensive copying or publication of the thesis in whole or in part also requires the consent of the Dean of the Graduate School of the University of Kentucky.

A library that borrows this thesis for use by its patrons is expected to secure the signature of each user.

Thesis

Darren Jacob Brown

Graduate School University of Kentucky 2010

### A NOVEL MESSAGE ROUTING LAYER FOR THE COMMUNICATION MANAGEMENT OF DISTRIBUTED EMBEDDED SYSTEMS

THESIS

A Thesis submitted in partial fulfillment of the requirements for the degree of Masters of Science in Electrical Engineering in the College of Engineering at the University of Kentucky

By

Darren Jacob Brown

Lexington, Kentucky

Director: Dr. James. E. Lumpp, Jr., Associate Professor of Electrical and Computer Engineering

Lexington, Kentucky

2010

Copyright <sup>©</sup> Darren Jacob Brown 2010

To my loving wife and family ...

# ACKNOWLEDGEMENTS

The following thesis, while an individual work, benefited from the insight, patience, experiences, and guidance from several people. I would like to thank my Thesis Chair, Dr. James Lumpp, for giving me the opportunity to pursue my masters degree, and for providing me with the tools and opportunity to start a career in the aerospace industry. If it had not been for the experiences provided, lessons learned, and mentorship given by Dr. Lumpp during my time in the IDEA lab, I would not be the engineer and leader that I am. Next, I would like to thank the other members of my thesis committee, Dr. William Smith and Dr. Bruce Walcott. Dr. Smith as both an advisor on the BIG BLUE project and professor impacted my undergraduate and graduate education. Dr. Walcott as a very involved mentor during my undergraduate experience through programs like FESC, B3 tutoring, KNEED, and Tau Beta Pi, indirectly guided me through my EE undergraduate experience. It was those experiences that lead me to continue my Masters education at the University of Kentucky. For all these reasons, I am forever thankful for all the contributions each member made toward my career, education, and thesis.

Beyond the mentorship and guidance mentioned above, the support of my entire family helped me through my masters and my complete collegiate career. However, this thesis would not have been possible if it had not been for my wife, Anne-Walker Brown. The love, patience, sacrifices, and support she has given me during this process is beyond belief. I truly owe the success of this thesis to her.

# TABLE OF CONTENTS

|                                                                                                                                  | LEDGEMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                 |  |

|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|

| LIST OF TABLES                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                 |  |

| LIST OF FIGURES                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                 |  |

| 1 INTRODUCTION<br>1.1 Background                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                 |  |

| 1.1.1                                                                                                                            | Fault Tolerant Embedded Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2                                                                                                                               |  |

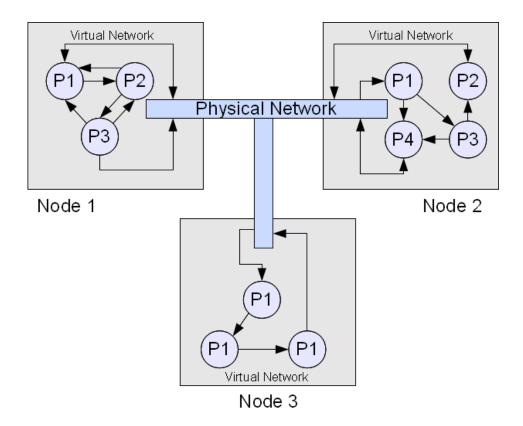

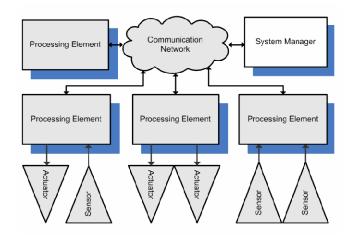

| 1.1.2                                                                                                                            | Distributed Embedded Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3                                                                                                                               |  |

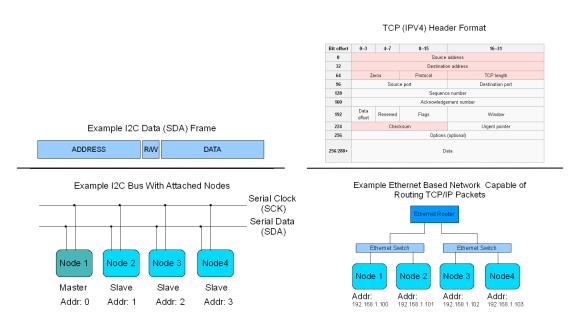

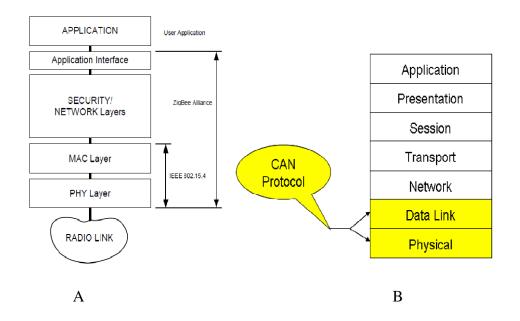

| 1.1.3                                                                                                                            | Embedded Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                                                                                               |  |

| 1.1.4                                                                                                                            | Embedded Operating Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7                                                                                                                               |  |

| 1.2                                                                                                                              | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                 |  |

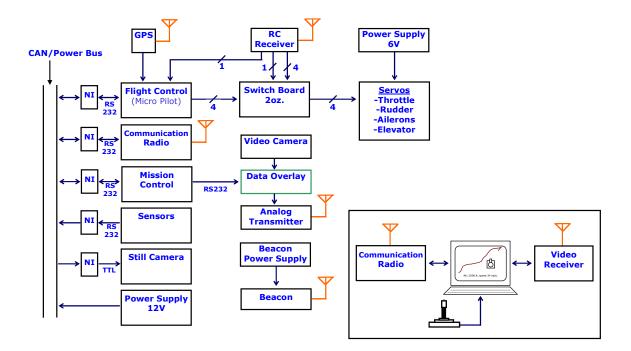

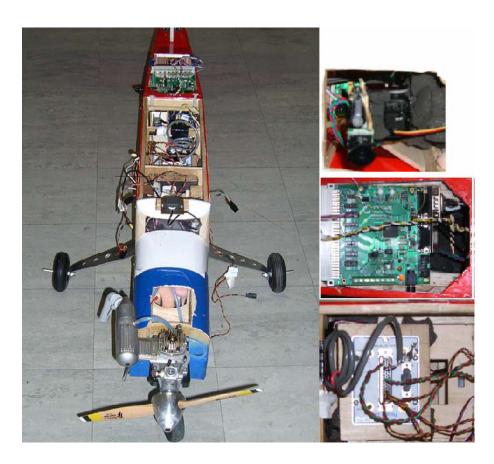

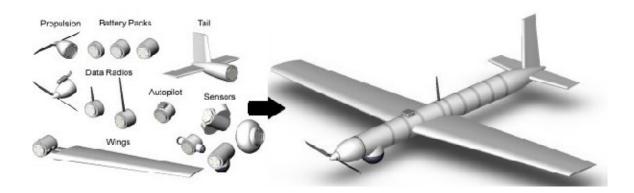

| 1.2.1                                                                                                                            | BIG BLUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11                                                                                                                              |  |

| 1.2.2                                                                                                                            | AUVSI UAV Student Competitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                 |  |

| 1.2.3                                                                                                                            | ARDEA Framework and Run-Time Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                 |  |

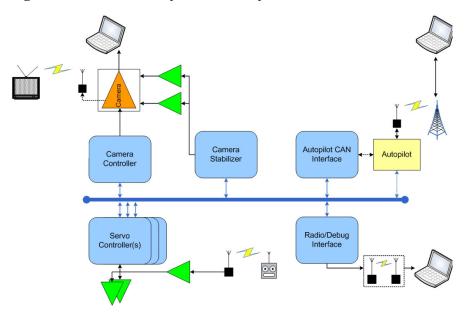

| 1.2.4                                                                                                                            | Ready UAV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                 |  |

| 1.3                                                                                                                              | Problem Statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                 |  |

| 1.3.1                                                                                                                            | Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                 |  |

| 1.4                                                                                                                              | Thesis Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                 |  |

|                                                                                                                                  | T TOLERANT EMBEDDED SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                 |  |

| 2.1                                                                                                                              | Embedded System Faults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                 |  |

| 2.1<br>2.2                                                                                                                       | Embedded System Faults<br>Fault Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                 |  |

|                                                                                                                                  | Fault Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                 |  |

| 2.2                                                                                                                              | Fault Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                 |  |

| 2.2<br>2.2.1                                                                                                                     | Fault Handling<br>Fault Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25<br>25<br>27                                                                                                                  |  |

| 2.2<br>2.2.1<br>2.2.2<br>2.3                                                                                                     | Fault Handling<br>Fault Detection<br>Fault Correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25<br>25<br>27<br>27<br>29<br>32                                                                                                |  |

| 2.2<br>2.2.1<br>2.2.2<br>2.3<br>3 THE 1                                                                                          | Fault Handling<br>Fault Detection<br>Fault Correction<br>Fault Tolerant System Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25<br>25<br>27<br>29<br>29<br>32<br>33                                                                                          |  |

| 2.2<br>2.2.1<br>2.2.2<br>2.3<br>3 THE 1<br>3.1                                                                                   | Fault Handling<br>Fault Detection<br>Fault Correction<br>Fault Tolerant System Models<br>NETWORK<br>Broadcast/Multicast Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25<br>25<br>27<br>27<br>29<br>29<br>23<br>33<br>33<br>33                                                                        |  |

| 2.2<br>2.2.1<br>2.2.2<br>2.3<br>3 THE 1<br>3.1<br>3.2                                                                            | Fault Handling<br>Fault Detection<br>Fault Correction<br>Fault Tolerant System Models<br>NETWORK<br>Broadcast/Multicast Networks<br>Communication Protocol Classification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25<br>25<br>27<br>29<br>32<br>33<br>33<br>34                                                                                    |  |

| 2.2<br>2.2.1<br>2.2.2<br>2.3<br>3 THE 1<br>3.1<br>3.2<br>3.2.1                                                                   | Fault Handling<br>Fault Detection<br>Fault Correction<br>Fault Tolerant System Models<br>NETWORK<br>Broadcast/Multicast Networks<br>Communication Protocol Classification<br>Node Oriented Protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25<br>25<br>27<br>29<br>29<br>32<br>33<br>33<br>33<br>34<br>35                                                                  |  |

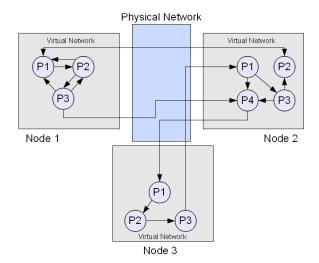

| 2.2<br>2.2.1<br>2.2.2<br>2.3<br>3 THE 1<br>3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.3                                                   | Fault Handling<br>Fault Detection<br>Fault Correction<br>Fault Correction<br>Fault Tolerant System Models<br>Fault Correction<br>Fault Correct | 25<br>25<br>27<br>29<br>32<br>33<br>33<br>33<br>33<br>34<br>35<br>35<br>39                                                      |  |

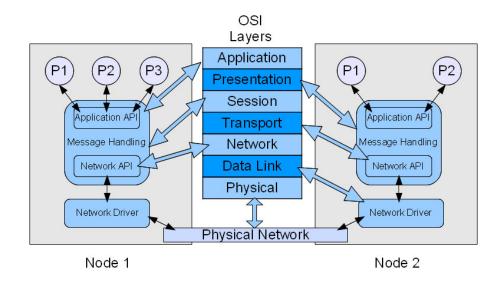

| 2.2<br>2.2.1<br>2.2.2<br>2.3<br>3 THE 1<br>3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.3<br>4 THE 1                                        | Fault Handling<br>Fault Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25<br>25<br>27<br>29<br>32<br>33<br>33<br>33<br>34<br>34<br>35<br>35<br>35<br>39<br>40                                          |  |

| 2.2<br>2.2.1<br>2.2.2<br>2.3<br>3 THE 1<br>3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.3<br>4 THE 1<br>4.1                                 | Fault Handling<br>Fault Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25<br>25<br>27<br>29<br>32<br>33<br>33<br>33<br>33<br>33<br>35<br>35<br>35<br>39<br>40<br>42                                    |  |

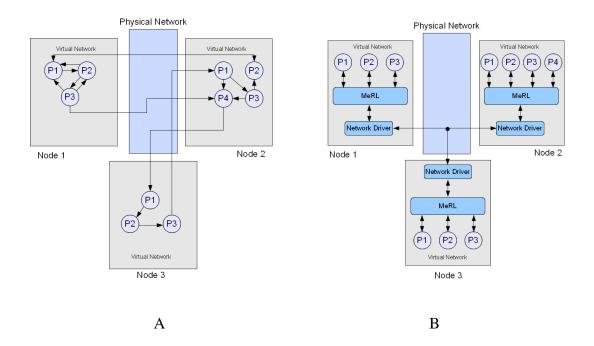

| 2.2<br>2.2.1<br>2.2.2<br>2.3<br>3 THE 1<br>3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.3<br>4 THE 1<br>4.1<br>4.2                          | Fault Handling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25<br>25<br>27<br>29<br>32<br>33<br>33<br>33<br>33<br>34<br>35<br>35<br>35<br>39<br>40<br>40<br>42<br>44                        |  |

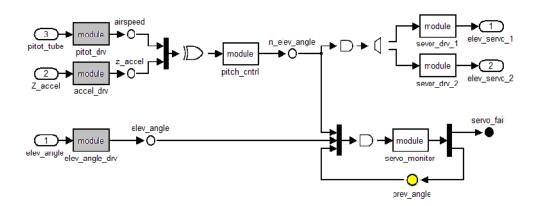

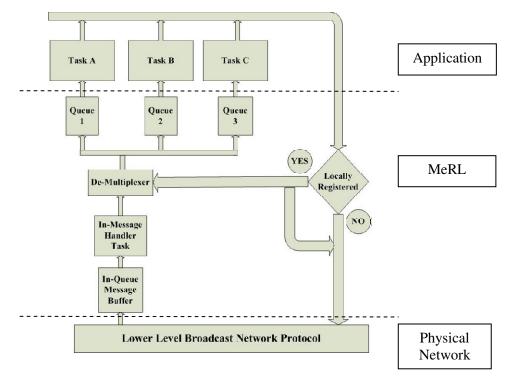

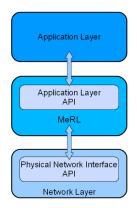

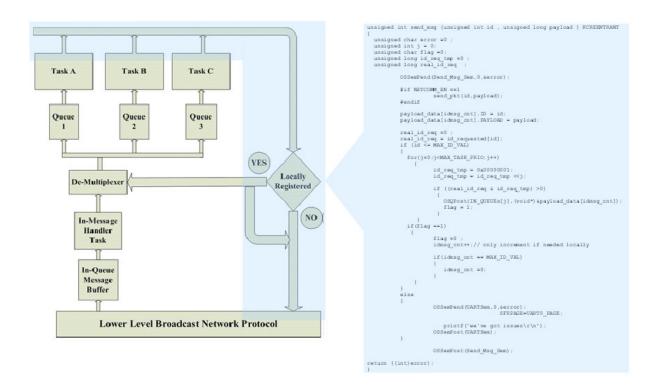

| 2.2<br>2.2.1<br>2.2.2<br>2.3<br>3 THE 1<br>3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.3<br>4 THE 1<br>4.1<br>4.2<br>4.3                   | Fault Handling<br>Fault Detection<br>Fault Correction<br>Fault Correction<br>Fault Tolerant System Models<br>NETWORK<br>Broadcast/Multicast Networks<br>Communication Protocol Classification<br>Node Oriented Protocols<br>Message Oriented Protocols<br>Network Protocol Selection for Fault Tolerant Applications<br>DESIGN OF A MESSAGE ROUTING LAYER<br>MeRL's Design Requirements.<br>The Design of MeRL<br>MeRL Integration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 25<br>25<br>27<br>29<br>32<br>33<br>33<br>33<br>33<br>33<br>33<br>34<br>35<br>35<br>35<br>39<br>40<br>40<br>42<br>44<br>44<br>5 |  |

| 2.2<br>2.2.1<br>2.2.2<br>2.3<br>3 THE 1<br>3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.3<br>4 THE 1<br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2 | Fault Handling<br>Fault Detection<br>Fault Correction<br>Fault Tolerant System Models<br>Fault Tolerant System Models<br>NetWORK<br>Broadcast/Multicast Networks<br>Communication Protocol Classification<br>Node Oriented Protocols<br>Message Oriented Protocols<br>Network Protocol Selection for Fault Tolerant Applications<br>DESIGN OF A MESSAGE ROUTING LAYER<br>MeRL's Design Requirements<br>The Design of MeRL<br>MeRL Integration<br>MeRL Application Layer API                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25<br>25<br>27<br>29<br>                                                                                                        |  |

|    | 5.2         | The Development of IDEAnix                       | 51  |

|----|-------------|--------------------------------------------------|-----|

|    | 5.3         | IDEAnix Driver Support of Silicon Labs c8051f04x | 53  |

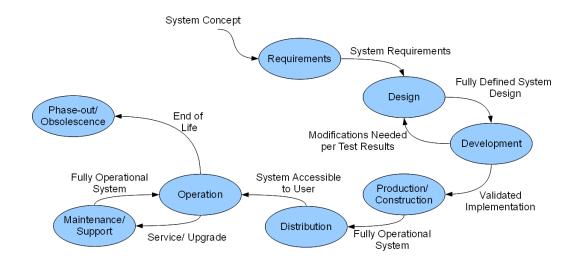

| 6  |             | IQUE EMBEDDED SYSTEM DESIGN PROCESS              |     |

|    | 6.1         | Systems Engineering - System Lifecycle           |     |

|    | 6.2         | A Systems Approach with MeRL                     |     |

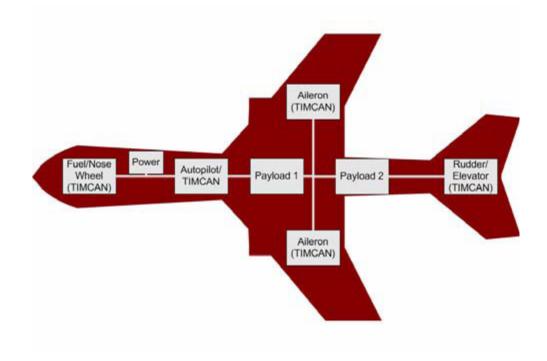

| 7  | IMPL<br>7.1 | EMENTATION AND TESTING<br>IDEAnix Implementation |     |

|    | 7.1         | MeRL Implementation                              |     |

|    | 7.2         | Modular UAV Design                               |     |

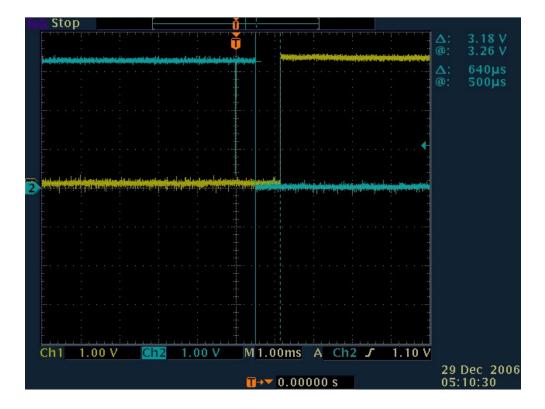

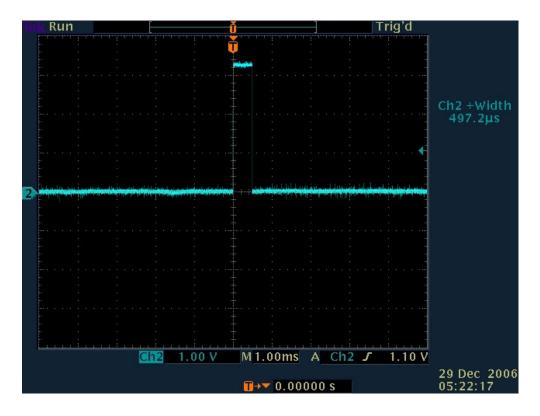

|    | 7.4         | Timing                                           |     |

|    | 7.5         | Experimental Results                             |     |

| 8  |             | CLUSIONS                                         |     |

| 0  | con         |                                                  |     |

| Δ  | PPENDI      | X: Demonstration UAV Source Code                 | 78  |

| 11 |             | I Source Code:                                   |     |

|    | uC/OS-I     | I Port Files:                                    | 78  |

|    | OS_C        | PU.H:                                            | 78  |

|    | OS_C        | PU_A.ASM                                         |     |

|    | OS_C        | PU_C.C:                                          | 85  |

|    | OS_K        | CDEF.H                                           |     |

|    | uC/OS-II    | I Configuration Files:                           | 93  |

|    | INCLU       | UDES.h                                           | 93  |

|    | OS_C        | FG.h                                             | 94  |

|    | ENDUR       | A (CAN Network) Files:                           | 97  |

|    | CAN_        | HEADER.h                                         | 97  |

|    | CAN_        | HEADER_INTERNAL.h                                |     |

|    | CAN_        | LIB.c                                            |     |

|    | Ideanix/    | MeRL Files:                                      | 111 |

|    | IDEAI       | NIX_INIT.h                                       | 111 |

|    | IDEAI       | NIX_INIT.c                                       | 112 |

|    | IDEAI       | NIX_ISR.h                                        | 117 |

|    | IDEAI       | NIX_ISR.c                                        | 118 |

|    | IDEAI       | NIX_MSG_HANDLER.h                                |     |

|    | IDEA        | NIX_MSG_HANDLER.c                                |     |

|    | IDEA        | NIX_TASK_MSG.h                                   |     |

|    | IDEA        | NIX_TASK_MSG.c                                   |     |

|    | IDEAI       | NIX_CONFIG.h                                     | 134 |

| IDEANIX_CONFIG.c    |  |

|---------------------|--|