# University of Kentucky UKnowledge

University of Kentucky Master's Theses

**Graduate School**

2010

# COMMERCIALIZATION AND OPTIMIZATION OF THE PIXEL ROUTER

Steven James Dominick *University of Kentucky*, steve.dominick@gmail.com

Right click to open a feedback form in a new tab to let us know how this document benefits you.

### **Recommended Citation**

Dominick, Steven James, "COMMERCIALIZATION AND OPTIMIZATION OF THE PIXEL ROUTER" (2010). *University of Kentucky Master's Theses*. 39. https://uknowledge.uky.edu/gradschool\_theses/39

This Thesis is brought to you for free and open access by the Graduate School at UKnowledge. It has been accepted for inclusion in University of Kentucky Master's Theses by an authorized administrator of UKnowledge. For more information, please contact UKnowledge@lsv.uky.edu.

#### ABSTRACT OF THESIS

#### COMMERCIALIZATION AND OPTIMIZATION OF THE PIXEL ROUTER

The Pixel Router was developed at the University of Kentucky with the intent of supporting multi-projector displays by combining the scalability of commercial software solutions with the flexibility of commercial hardware solutions. This custom hardware solution uses a Look Up Table for an arbitrary input to output pixel mapping, but suffers from high memory latencies due to random SDRAM accesses. In order for this device to achieve marketability, the image interpolation method needed improvement as well. The previous design used the nearest neighbor interpolation method, which produces poor looking results but requires the least amount of memory accesses. A cache was implemented to support bilinear interpolation to simultaneously increase the output frame rate and image quality. A number of software simulations were conducted to test and refine the cache design, and these results were verified by testing the implementation on hardware. The frame rate was improved by a factor of 6 versus bilinear interpolation on the previous design, and by as much as 50% versus nearest neighbor on the previous design. The Pixel Router was also certified for FCC conducted and radiated emissions compliance, and potential commercial market areas were explored.

Keywords: Pixel Router, Cache, Bilinear Interpolation, LUT, Commercialization

| Steven James Dominick |  |

|-----------------------|--|

|                       |  |

| <u>12/15/2010</u>     |  |

# COMMERCIALIZATION AND OPTIMIZATION OF THE PIXEL ROUTER

Ву

Steven James Dominick

Dr. Bruce Walcott

Co-Director of Thesis

Dr. Ruigang Yang

Co-Director of Thesis

Dr. Stephen Gedney

Director of Graduate Studies

12/15/2010

### RULES FOR THE USE OF THESES

Unpublished theses submitted for the Master's degree and deposited in the University of Kentucky Library are as a rule open for inspection, but are to be used only with due regard to the rights of the authors. Bibliographical references may be noted, but quotations or summaries of parts may be published only with the permission of the author, and with the usual scholarly acknowledgements.

Extensive copying or publication of the thesis in whole or in part also requires the consent of the Dean of the Graduate School of the University of Kentucky.

A library that borrows this thesis for use by its patrons is expected to secure the signature of each user.

| <u>Name</u> | <u>Date</u> |

|-------------|-------------|

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

|             |             |

# THESIS

Steven James Dominick

The Graduate School

University of Kentucky

2010

### COMMERCIALIZATION AND OPTIMIZATION OF THE PIXEL ROUTER

THESIS

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering in the College of Engineering at the University of Kentucky

Ву

**Steven James Dominick**

Lexington, Kentucky

Co-Directors: Dr. Bruce Walcott, Professor of Electrical Engineering and Dr. Ruigang Yang, Professor of Computer Science

Lexington, KY

2010

Copyright <sup>©</sup> Steven James Dominick 2010

# TABLE OF CONTENTS

| TABLE OF CONTENTS                                        | ii     |

|----------------------------------------------------------|--------|

| LIST OF TABLES                                           | iv     |

| LIST OF FIGURES                                          | ۰۰۰۰۰۰ |

| LIST OF FILES                                            | V      |

| Section 1: Introduction                                  | 1      |

| Multi-Projector Displays                                 | 1      |

| Software Blended Displays                                | 1      |

| Hardware Blended Displays                                | 3      |

| The Pixel Router                                         | 3      |

| Section 2: Previous Work                                 | 5      |

| Pixel Router Design                                      | 5      |

| Cache with Blocks                                        | б      |

| Section 3: Bilinear Interpolation and Memory Performance | 8      |

| Memory Performance                                       | 11     |

| Section 4: Prefetch Cache Design and Simulation          | 14     |

| Basic Cache System                                       | 14     |

| Prefetch Cache System                                    | 20     |

| Dynamically Loaded Cache System                          | 25     |

| Cache Definitions                                        | 27     |

| Additional Cache Lines                                   | 27     |

| Cache Operation Example                                  | 28     |

| Measured Results                                         | 30     |

| Section 5: LUT Description and Generation                | 32     |

| LUT Description                                          | 32     |

| LUT Generation                                           | 33     |

| Section 6: Packaging                                     | 35     |

| Case and Power Supply                                    | 35     |

| FCC Certification                                        | 37     |

| Section 7: Business Strategy                             | 45     |

| Potential Markets                                        | 45     |

| Cost of Materials                                        | 46     |

| Section 8: Conclusion and Future Work                    | 48     |

| Appendix A: LUT Generation Code                          | 49     |

| Appendix B: Cache Simulation Code                        | 84     |

| REFERENCES                                               | 93     |

| \/ITA                                                    | 05     |

# LIST OF TABLES

| Table 1 - 16 Pixel Cache Simulation                             | 16 |

|-----------------------------------------------------------------|----|

| Table 2 - 32 Pixel Cache Simulation                             | 17 |

| Table 3 - 64 Pixel Cache Simulation                             | 17 |

| Table 4 - 128 Pixel Cache Simulation                            | 18 |

| Table 5 - Optimized Cache Sizes for Rotation                    | 20 |

| Table 6 - 16 Pixel Cache Simulation with Prefetching            | 22 |

| Table 7 - 32 Pixel Cache Simulation with Prefetching            | 22 |

| Table 8 - 64 Pixel Cache Simulation with Prefetching            | 23 |

| Table 9 - 128 Pixel Cache Simulation with Prefetching           | 23 |

| Table 10 - Prefetching Cache Improvement                        | 24 |

| Table 11 - Dynamically Loaded Cache Simulation                  | 26 |

| Table 12 - Cache with 8 Lines                                   | 28 |

| Table 13 - Prefetch LUT Data                                    | 29 |

| Table 14 - Measured versus Simulated Frame Rates                | 31 |

| Table 15 - Prefetch LUT Description [3]                         | 32 |

| Table 16 - Per Pixel LUT Description [3]                        | 33 |

| Table 17 - ATX Power Supply Minimum Current Requirements        | 36 |

| Table 18 - Heat Characteristics of Power Dissipation Resistors  | 37 |

| Table 19 - FCC Part 15 B Class A Radiated Emissions Limits [9]  | 38 |

| Table 20 - FCC Part 15 B Class A Conducted Emissions Limits [9] | 38 |

| Table 21 – Pixel Router Cost of Materials and Production [14]   | 46 |

# LIST OF FIGURES

| Figure 1 – Alpha blending mask example [1]                  | 2  |

|-------------------------------------------------------------|----|

| Figure 2 - Inverse Mapping                                  | 5  |

| Figure 3 - Cache with Blocks Simulation [3]                 | 6  |

| Figure 4 – Video Output Data Path [3]                       | 7  |

| Figure 5 - Rotation with Nearest Neighbor Interpolation [3] | 9  |

| Figure 6 - Bilinear Interpolation Diagram                   | 10 |

| Figure 7 - Rotated Image with Bilinear Interpolation [3]    | 11 |

| Figure 8 - SDRAM Read Timing Diagram [6]                    | 12 |

| Figure 9 - Cache Simulation Comparing Cache Width           | 19 |

| Figure 10 - Cache Refill Example                            | 21 |

| Figure 11 - Cache Simulation with Prefetching               | 24 |

| Figure 12 - Dynamically Loaded Cache Simulation             | 26 |

| Figure 13 – Cache Field Definitions Definitions             | 27 |

| Figure 14 - Cache Operation Example Timing Diagram          | 30 |

| Figure 15 - LUT Generation Flowchart                        | 34 |

| Figure 16 - Pixel Router Packaging                          | 35 |

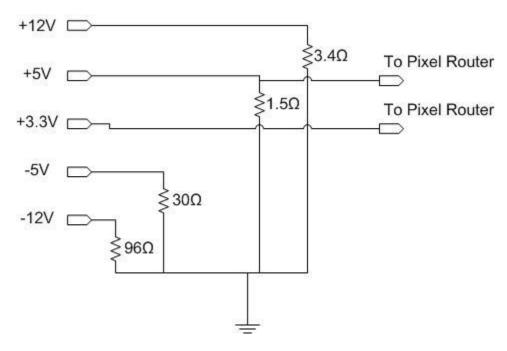

| Figure 17 - ATX Power Supply Power Dissipation Schematic    | 36 |

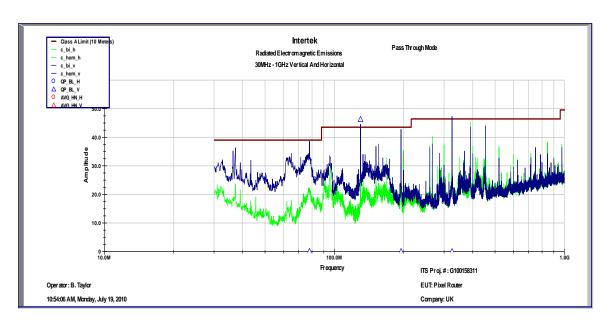

| Figure 18 - Initial Radiated Emissions Scan                 | 39 |

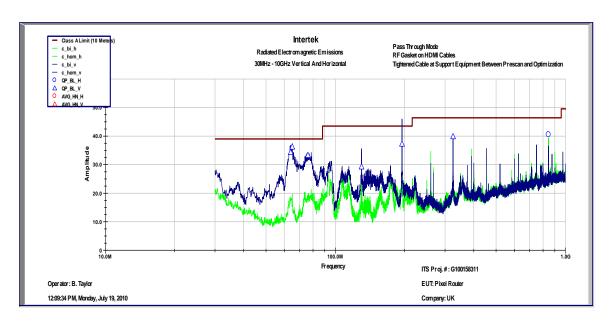

| Figure 19 - Support for HDMI Cables                         | 40 |

| Figure 20 - Compliant Radiated Emissions Scan               | 41 |

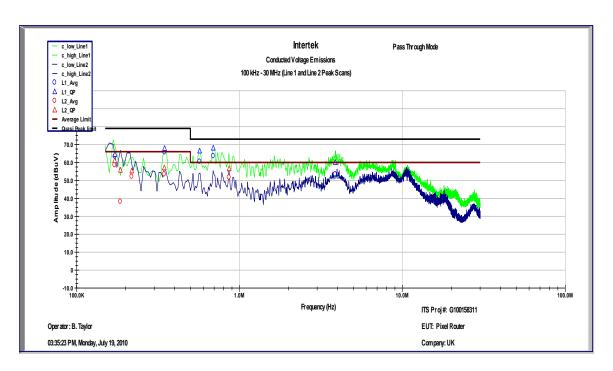

| Figure 21 - Initial Conducted Emissions Scan                | 42 |

| Figure 22 - In-line Power Filter                            | 43 |

| Figure 23 - In-line Power Filter Schematic [11]             | 43 |

| Figure 24 - Compliant Conducted Emissions Scan              | 44 |

# LIST OF FILES

| Thesis Document                      | <u>Dominick Thesis.pd</u>     |

|--------------------------------------|-------------------------------|

| Pixel Router FCC Part 15 Test Report | FCC Part 15 Report.pdf        |

| Pixel Router FPGA Specification      | Pixel Router Specification.pd |

| Pixel Router Production Quote        | Q0805-006-FA-01.pd            |

#### Section 1: Introduction

# Multi-Projector Displays

The utilization of multiple projectors to create a single seamless, uniform display is quickly becoming a mature technology. Television newscast sets, command and control centers, large conference halls, houses of worship, and many other markets take advantage of this technology to enhance the presentation of visual information. By overlapping and "edge-blending" two or more video projectors, one can create a resulting image with higher resolution and brightness and less throw distance between the projection and the projector lens.

# Software Blended Displays

There are two primary approaches to creating edge blended displays that are currently available in the market. The first approach is a software-based process that runs on commodity hardware. Typically, this process involves camera feedback to automatically align and blend the projectors to create blending and warping masks that result in a perfectly aligned and blended seamless display. This process is the same for any number of projectors in any configuration, thus making it an extremely scalable method. The calibration procedure in software can be performed in a few minutes or seconds, even for large arrays of projectors. In 2005, Brown et al presented a survey of available techniques for camera-based projector calibration, comparing capabilities and computational requirements for each method [1]. In this survey, the two primary metrics used to compare calibration techniques consisted of geometric registration and photometric correction. Calibration techniques can compute the geometric registration on either planar surfaces or arbitrary surfaces, using one or several cameras. On an arbitrary (non-planar) surface, the geometric warping can be computed for either a stationary viewer with a single ideal head position or for a moving viewer where the head position is tracked. This second method, known as 3D global registration, allows for the creation of immersive displays capable of displaying 3D rendered content that correctly accounts for a user's viewpoint. The other important component to software blended displays is the photometric correction of the display. In the paper, Brown discusses variables to which photometric correction can be applied: intra-projector variance, inter-projector variance, and overlap variance. Intra-projector variance is a result of non-uniformities within the display of a single projector which can result from properties of the projector lamp or the display surface itself. Inter-projector variance is the difference in luminance between separate projectors. Even projectors of the same make and model can have differences in color and intensity due to manufacturing tolerances and uneven aging of projector lamps and other components in the device. Both intra-projector and inter-projector variance are small, however, compared to variance in the overlap regions between projectors. In the software blending methods discussed, overlap blending is the primary focus for the photometric correction. These methods use a linear or cosine ramp function in the overlap regions of the projectors to produce smooth transitions between the display area of one projector to another. Brown gives an example of linear ramping by considering two overlapping projectors,  $P_1$  and  $P_2$ , whose contributions at a location x on the screen on the display surface are  $P_1(x)$  and  $P_2(x)$ , respectively. The blended intensity at x is calculated by the equation below, where  $\alpha_1 + \alpha_2 = 1$ .

$$I(x) = \alpha_1(x)P_1(x) + \alpha_2(x)P_2(x)$$

The alpha weights  $\alpha_1$  and  $\alpha_2$  are calculated based on the distance of x from the boundaries of the overlap region. For a linear ramp function,  $\alpha_1$  and  $\alpha_2$  are calculated as follows, where d1 and d2 are the distances to the edges of the overlap region.

$$\alpha_1(x) = \frac{d1}{d1 + d2}; \ \alpha_2(x) = \frac{d2}{d1 + d2}$$

Brown et al also give an example of the resulting blending masks from 4 overlapping projectors using this linear ramp function blending technique. In that image, shown below in Figure 1 [1], the left most images are the alpha blending masks for these projectors, the middle image is the unblended but geometrically corrected image, and the right image is the geometrically and photometrically corrected image using these alpha masks.

Figure 1 – Alpha blending mask example [1]

Software blended displays are not without their disadvantages, however. The output images to the projectors in the display are warped and blended through commodity graphics hardware in a PC. However this hardware does not natively support blending and warping functions in the low-level drivers, thus an application must be written at the Operating System level which applies the geometric and photometric correction to any content that is desired to be displayed. Generally, applications written for an OS are not designed to support blended multi-projector output, and thus source code modifications are required to enable this feature. Most applications use proprietary source code that is not possible to modify as an end user, thus content is difficult to generate for software blended displays. This limitation reduces the number of applications that software blended displays can be useful for to scenarios where the

content source code can be accessed either through open source modification or active cooperation with the company that produces the software. Thus, software blended displays tend to only be used in high-end simulation and visualization applications that use specialized image generation software that can be easily modified.

## Hardware Blended Displays

Another approach to creating multi-projector displays is to use customized hardware that acts as an image processing "pass-through" device. These devices have one or more video inputs and at least two video outputs, and apply basic warping and blending techniques to achieve geometric and photometric uniformity on a display. Unlike software blended displays which use camera feedback to automatically compute the warping and blending masks, these devices rely on a manual calibration process for image alignment and correction. To compute this correction, projector is connected to each of the device's video outputs and some alignment tool, such as a displayed grid pattern, is used to assist the user in manual overlap correction. Once the display has been properly aligned and blended, the inputs on the device allow the user to treat the entire display as a single monitor. Any compatible video input plugged in to the blending device will be shown across all projectors in a seamless, uniform manner. The major disadvantage of systems such as these is setup time. Consider a projector array with M projectors in the horizontal direction and N projectors in the vertical direction. Aligning a 1xN or Mx1 array is not a terribly complex task using these systems, but alignment difficulty grows dramatically with an MxN system, where M and N are both greater than 1. In a 1xN or Mx1 array, no projector overlaps with more than 2 other projectors. However in an MxN array, a projector may overlap with many other projectors, creating more variables and adjustment parameters than can be accounted for in a short period of time. As the number of projectors is increased, the complexity of setup increases exponentially. This presents a significant disadvantage as compared to software blended displays, whose calibration time is a linear function to the number of projectors in the display. Thus, hardware-based blended displays typically are more useful in long term, stationary environments than in situations where there is need for frequent realignments.

The Pixel Router

The Pixel Router is a custom hardware device developed at the University of Kentucky with the intention of bridging the gap between software and hardware edge blending. The device, which has 4 HDMI inputs and 4 HDMI outputs, uses look-up tables (LUTs) generated by a software calibration process to warp and blend up to 4 input images across the outputs. These LUTs represent alpha masks such as the one shown in **Error! Reference source not found.** Figure 1, and apply photometric alpha blending to correct for overlap variations. Additionally, the LUTs can map any given input pixel to any given output pixel, allowing for the implementation of the geometric correction calculated by the calibration software [2]. This device takes advantage of the scalability and flexibility of the software calibration procedure while maintaining the content agnostic properties

of hardware based solutions. This thesis will focus on efforts to improve the performance of the Pixel Router and potential opportunities for commercialization. The primary area of performance improvement will be to improve the appearance of rotated, warped, and scaled images while maintaining an acceptable frame rate. This will be achieved through the implementation of bilinear interpolation and the design of an efficient cache that improves the performance of this memory-intensive operation. Additionally, packaging the device and securing proper FCC certification will be explored.

### Section 2: Previous Work

## Pixel Router Design

The Pixel Router is the result of a number of years of work and research at the University of Kentucky (and the University of North Carolina Chapel Hill?), and has undergone several design iterations. The current version is implemented on a Xilinx Virtex-4 FPGA, part number XC4VLX40-FF1148. Four 32Meg x 32-bit DDR SDRAM memory banks are used to store LUT data as well as input and output video frame buffer data. These memory banks are each made up of two Micron MT4632M16P-5B devices and operate at 133MHz for a data rate of 266MHz. The HDMI interface uses 4 Analog Devices AD9398 receivers on the input side and 4 Analog Devices AD9889B transceivers for video transmission [PR Spec]. This allows the Pixel Router to receive and transmit 4 independent HDMI channels each capable of handling video at up to 1080p resolution (1920x1080 pixels).

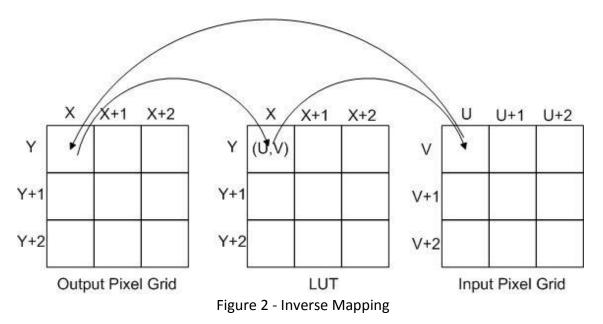

The Pixel Router is designed with a Look Up Table architecture that allows any input pixel to be mapped to any output pixel, with the pixel color value multiplied by an alpha to allow for image intensity blending. The Look Up Table uses an inverse mapping function where the input pixel address required is determined by the output pixel location. This is because an input pixel can be assigned to multiple output pixel locations, but not vice versa. A diagram showing this inverse mapping concept is shown below. In this diagram, the [X, Y] coordinate system represents the output pixel space and the [U,V] coordinate system represents the input pixel space.

These features make the Pixel Router a flexible device capable of performing arbitrary image warping in a variety of applications. The intent of the device is act as a stand-

alone hardware platform to perform the image blending and warping required for multiprojector displays, keeping a computer out of the loop.

#### Cache with Blocks

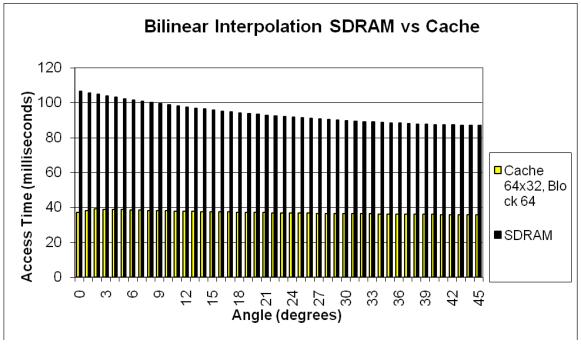

Previous work has been done by Vijai Raghunathan [3] to design a cache for the Pixel Router that improves performance and allows for bilinear interpolation to be implemented. In this project, an optimal cache was designed that allowed the Pixel Router to operate at reasonable frame rates independent of the amount of image rotation. This cache system used the concept of "Memory Blocks", which divides the memory space into blocks and effectively rearranges the access pattern to minimize memory latency. In this design, it was determined that the optimal block size was 64x64 pixels, and the optimal cache size was 64x32 pixels. Below is an image comparing the performance of this cache system to direct SDRAM access [3].

Figure 3 - Cache with Blocks Simulation [3]

This simulation measured the SDRAM access time for one 1024x768 pixel image frame across different amounts of image rotation, with bilinear interpolation applied to improve the image quality. The simulations suggest that this cache design provides a significant performance improvement over direct SDRAM access. Additionally, this cache design is independent of the amount of image rotation, as the access time remains nearly flat at just under 40 milliseconds.

Another way of describing the performance of cache design that is perhaps more intuitive is in terms of output frame rate rather than access time. For these simulations,

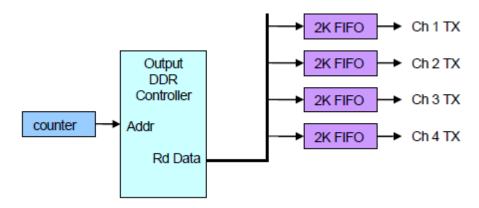

the access time for one output frame was measured. In the Pixel Router, however, there are 4 output ports, and each one is processed sequentially rather than in parallel. The block diagram below is taken from the Pixel Router Specification [3] and shows the data path of the video output signals.

Figure 4 – Video Output Data Path [3]

The transmit FIFOs in the diagram above are written sequentially in 256 word bursts, and therefore the number of pixel values output from the Rd Data port on the Output DDR Controller is equal to 4 times the output resolution on each channel. This creates a bottleneck in processing the data, and that same bottleneck is present on the interface between the FPGA and the Input DDR Controller. Thus when considering the real frame rate on the Pixel Router, the access time presented in Raghunathan's thesis should be multiplied by 4. Parallelizing these memory interfaces could help improve bandwidth and therefore frame rate, but such work is outside of the scope of this project as the goal is to optimize the performance for the current hardware revision. The conversion for the access time in the simulations above to Pixel Router frame rate is shown below.

$$Frame\ Rate = \frac{1}{4*Access\ Time}$$

The access time in these simulations was approximately 35 milliseconds, which corresponds to a frame rate on the Pixel Router of just over 7 frames per second. While this marks an improvement over implementing bilinear interpolation on previous design with no cache architecture, it is below the design target of 60 frames per second, and also below the nearest neighbor operation of 20 frames per second. Additionally, it was determined that implementation of this cache system would be complex and costly. One of the primary goals of this project is to design a cache that is simple and effective at improving the frame rate of the Pixel Router employing bilinear interpolation.

# Section 3: Bilinear Interpolation and Memory Performance

Previously, the Pixel Router calculated the input pixel value to be mapped to the output pixel through a process called nearest neighbor interpolation. When computing the mapping between input and output pixels after warping an image, floating point numbers with a non-zero value after the radix for the input pixel locations are produced. However, pixels by their nature are quantized color values in integer grids. In nearest neighbor interpolation, the floating point x and y locations in the pixel grid are rounded to the nearest whole number to produce exact pixel locations. When implemented using pre-defined look-up tables, as in the Pixel Router, this process eliminates the need for any calculation to be performed by the graphics hardware and minimizes the required memory bandwidth. However, this method of interpolation is the least visually appealing, especially for content such as text and lines with rotation relative to the pixel grid. Below is an image used by Vijai Raghunathan that has been rotated and interpolated using the nearest neighbor method [3]. The text in this image, while readable, appears jagged and rough and below users' expectations for current graphics hardware.

Figure 5 - Rotation with Nearest Neighbor Interpolation [3]

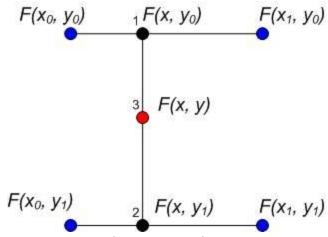

Bilinear interpolation is an image processing technique for improving the appearance of scaled, rotated, or warped images. Instead of rounding the floating point x and y coordinates of pixel values, the bilinear interpolation method computes a pixel value based on the weighted values of each of the 4 neighboring pixels [5]. This concept is illustrated in the image below.

Figure 6 - Bilinear Interpolation Diagram

In the above image, the blue dots represent input pixels, where  $X_0$ ,  $X_1$ ,  $Y_0$ , and  $Y_1$  are integer values representing pixel locations in the image. The function  $F(X_a, Y_b)$  represents the color values of these pixels. The location (X,Y) is the interpolated input pixel location that maps to an output pixel location after an image warping operation, where X and Y are floating point, non-integer values. The two black dots represent values that are linearly interpolated along the X-direction. The equations below describe the calculations to compute the value of F(X, Y) by first linearly interpolating in the X-direction, and using the interpolated values to linearly interpolate in the Y-direction. In the context of an image, the distance between  $X_0$  and  $X_1$  is one pixel, and the same is true in the Y direction. That assumption is made in these equations.

$$f(x, y_0) = (x_1 - x) * f(x_0, y_0) + (x - x_0) * f(x_1, y_0)$$

$$f(x, y_1) = (x_1 - x) * f(x_0, y_1) + (x - x_0) * f(x_1, y_1)$$

$$f(x, y) = (y_1 - y) * f(x, y_0) + (y - y_0) * f(x, y_1)$$

This three step equation can be simplified in to one by substituting the equations for  $F(X, Y_0)$  and  $F(X, Y_1)$  into the final equation.

In order to perform the bilinear interpolation calculation, the FPGA must be provided with a base input pixel address (u, v) and a value for both the x and y directions that represent that percentage of pixels (u+1, v), (u, v+1), and (u+1, v+1) to use. It was determined by Vijai Raghunathan that providing 3 bits after the radix point for both the x and y floating point values yielded sufficient resolution to produce visually appealing results. The bits after the radix point correspond to the values of (x1 - x), (x - x0), (y1 - y), and (y - y0), and determine the precision of the bilinear interpolation calculation. Figure 7 below is an image produced by Vijai Raghunathan rotated with bilinear

interpolation calculated using only 3 binary digits after the radix [3]. Vijai found that increasing the number of bits after the radix beyond 3 provided limited benefit to the resulting image quality. Thus, to conserve bit space in the Look Up Table, 3 bits will be used for bilinear interpolation.

Figure 7 - Rotated Image with Bilinear Interpolation [3]

### Memory Performance

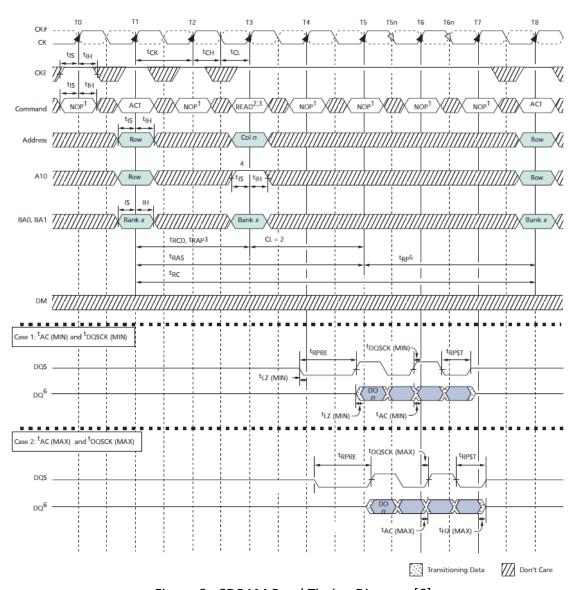

Though bilinear interpolation provides great benefit to the appearance of rotated, warped, and scaled images, it is not without its cost. The first penalty is the calculation time required to compute the resulting output pixel from the 4 input pixels. The bilinear interpolation formula requires 4 multiplications and 4 additions to calculate the value of each output pixel. However, this performance penalty can be treated as negligible because this process can be pipelined through hardware design. The major performance penalty comes from having to read pixel values from 4 locations in Random Access Memory in order to compute the value of 1 output pixel. This effectively multiplies the required memory bandwidth by 4. Additionally, when accessing Random Access Memory, there is a latency penalty for opening a new memory row. Bilinearly interpolated pixels always require pixel data from 2 different rows, exposing this latency penalty on every pixel calculation. The Pixel Router is using

Micron MT4632M16P-5B devices for the memory banks. These devices are set to operate at 133MHz, and are programmed to use 2.5 cycle CAS latency with a burst length of 2 [3]. Based on the datasheet, the row opening penalty is due to latency values, the Auto Refresh command (<sup>t</sup>RFC) and the Precharge command (<sup>t</sup>RP). <sup>t</sup>RFC is specified at approximately 10 clock cycles and <sup>t</sup>RP at 2 clock cycles for a penalty of 12 clock cycles each time a new row is accessed [6]. The image below, which is taken from the data sheet, shows the low-level signals required to access a memory location and the latency associated with such access.

Figure 8 - SDRAM Read Timing Diagram [6]

If no action is taken to mitigate this latency when bilinear interpolation is implemented on the Pixel Router, the result is a dramatic decrease in performance (measured in output frame rate). The current hardware operates at 20 frames per second using nearest neighbor interpolation. The simulation by Vijai Raghunathan in the previous chapter suggests that the implementation of bilinear interpolation with no memory caching will cause the access time for one 1024x768 frame to drop to approximately 100ms. This equates to a frame rate on four 1024x768 output channels of 2.5 frames per second. Such a low frame rate would render the Pixel Router useless for virtually all applications besides the display of still images. The goal of the Pixel Router project is to produce a commercially viable product, and thus there cannot be a tradeoff between acceptable image quality and acceptable frame rate; both goals must be met. Therefore a cache system must be designed to allow the Pixel Router to process image transformations using bilinear interpolation at a frame rate that meets users' expectations.

# Section 4: Prefetch Cache Design and Simulation

## Basic Cache System

A common method of mitigating performance drops due to memory latency is to introduce a cache in the system. A cache serves as a small block of memory that contains a subset of the data stored in a larger memory block, and can be accessed much more quickly. Because the cache only contains a small amount of available memory, it should be loaded with data that is likely to be used on the next read attempt. Of course, the memory address location that is requested cannot always be guaranteed to be available in the cache because it is likely that all or most of the memory address locations in the larger memory block will be accessed at some point. Thus, a cache design is often evaluated by its efficiency or hit rate, which is defined as the percentage of memory access requests where the data is available in the cache versus the total number of memory access requests.

The design of the Pixel Router lends itself well to a cache system because the data in the input memory is always accessed in the same order. The access pattern is described by Look Up Tables (LUTs) which are calculated offline and loaded into the Pixel Router's memory at runtime. Because there is a much larger clock cycle penalty for accessing new memory rows than for new memory columns, the goal of a cache design for the Pixel Router should be to minimize the number of rows that need to be opened in order to read one video frame from memory. The previous work by Vijai Raghunathan described earlier focused on improving the performance of the pixel router under the worst-case scenario, which is a 45 degree rotation image transformation. Under that scenario, each memory access attempt would request pixel data from a new row and column in memory. His design proved effective at enhancing the performance of the Pixel Router under that condition, however the memory block system would have been costly and difficult to implement. Additionally, a 45 degree image rotation is not a typical scenario for a multi projector display. While projectors that are to be blended via software calibration can be placed arbitrarily, often they are at least "casually aligned" and placed in a generally normal, horizontal configuration. Often, the average rotation amount for each projector is quite small. The cache design for the Pixel Router will remove the constraint of rotation independence and instead focus on optimization for cases of image rotation of 5 degrees or less. Thus, a simpler cache system can be designed that is highly efficient for small amounts of rotation, which covers a majority of applications. Simulations will be conducted with up to 45 degrees of rotation, however, to fully evaluate any cache design.

The primary goal of the cache for the Pixel Router is to improve the frame rate for performing bilinear interpolation. Because bilinear interpolation requires two rows of input pixel data, the cache should contain at least two rows of data to avoid row opening penalties on every pixel read. Below are tables showing simulations of the Pixel Router using bilinear interpolation with simple two row caches of various widths with different amounts of rotation on the input image. Hennessy and Patterson [7] describe

several areas in which to optimize a cache. These include reducing the hit time, increasing the cache bandwidth, reducing the penalty for a cache miss, reducing the cache miss rate, and adding parallelism to the cache architecture. In these simulations, the effectiveness of the cache is evaluated by three metrics: frame rate, hit rate, and input memory efficiency. The ultimate goal is to increase the frame rate on the device, and the effectivenss of the cache is determined by the hit rate and input memory efficiency. The Frame Rate calculation uses the Pixel Router's clock speed of 133MHz. The assumptions in this calculation are that the cache cannot be written to and read from at the same time, and that it takes one clock cycle to read one interpolated pixel from the cache (4 data locations due to bilinear interpolation). The Pseudocode below describes the process for determining the total number of clock cycles to render one frame of data.

```

for each (CacheLine_Refill) {

if(currentRow = lastRowOpened)

loadCycles = CACHE_WIDTH * T_READ_PIXEL

else

loadCycles = T_OPEN_ROW + CACHE_WIDTH *

T_READ_PIXEL

Total_Cycles = Total_Cycles + loadCycles +

pixelsProcessed

}

```

This code reflects the behavior of the SDRAM by including the clock cycle penalty for opening a new row of data. This calculation also assumes that the cache cannot be written to and read from at the same time by adding the pixelsProcessed value to the number of cycles calculated. The number of clock cycles calculated by this (Total\_Cycles) refers to the cycles required for one frame of data on one video output. The Pixel Router uses 4 video outputs that are written to in round-robin fashion, so to estimate the real frame rate this number must be multiplied by 4 (assuming all video outputs have the same image transformation/rotation). The clock cycle value listed in the tables below is calculated before this multiplication. The frame rate is calculated as

$$Frame\ Rate = \frac{1}{4*Clock\ Cycles}*Clock\ Speed$$

Input memory efficiency is related to the frame rate and describes how effectively the SDRAM for the input frame buffer is being utilized. It can be calculated using the ratio of pixels read versus the total number of pixels possible to be read, and an efficiency of 100% would mean that a pixel is read from the SDRAM at every available instance. For DDR SDRAM operating at 133MHz, that corresponds to 266 million pixels read per second. Row opening wait times, during which no input pixels can be read, reduces the memory efficiency. The memory efficiency can be calculated based on the output frame

rate for cases of regular image transformation. As discussed previously, when applying bilinear interpolation to the image 4 input pixels are required to calculate each output pixel. However, for a regular image rotation there are 2 unique pixels used per output pixel, as there is overlap between the input pixels required to calculate each output pixel. Therefore, input memory efficiency on DDR SDRAM for the Pixel Router can be calculated as

Input Memory Efficiency =

$$\frac{Pixels \ per \ Frame * 4 * 2 * Frame \ Rate * 100\%}{Clock \ Speed * 2}$$

The cache hit rate describes how effectively the data within the cache is utilized by showing the number of times the cache is accessed where the desired data is in the cache versus the number of times where that data is not in the cache. It is calculated as

$$Hit\ Rate = \frac{Cache\ Hits*100\%}{Cache\ Hits+Cache\ Misses}$$

The tables below show the results of the simulations of the initial cache design, evaluated using the metrics described above.

Table 1 - 16 Pixel Cache Simulation

| Rotation (Degrees) | Clock Cycles | Frame Rate (fps) | Hit Rate (%) | Memory Eff. (%) |

|--------------------|--------------|------------------|--------------|-----------------|

| 0                  | 3171612      | 10.48            | 92.77        | 24.80           |

| 1                  | 3358048      | 9.90             | 92.05        | 23.42           |

| 2                  | 3172687      | 10.48            | 92.14        | 24.79           |

| 3                  | 3953832      | 8.41             | 90.05        | 19.89           |

| 4                  | 2793343      | 11.90            | 92.39        | 28.15           |

| 5                  | 2859129      | 11.63            | 91.95        | 27.51           |

| 10                 | 5166938      | 6.44             | 85.46        | 15.22           |

| 15                 | 6999775      | 4.75             | 80.34        | 11.24           |

| 20                 | 8390303      | 3.96             | 76.48        | 9.37            |

| 25                 | 9368092      | 3.55             | 73.80        | 8.39            |

| 30                 | 9960016      | 3.34             | 72.23        | 7.90            |

| 35                 | 10190250     | 3.26             | 71.71        | 7.72            |

| 40                 | 10080609     | 3.30             | 72.16        | 7.80            |

| 45                 | 9651829      | 3.44             | 73.53        | 8.15            |

Table 2 - 32 Pixel Cache Simulation

| Rotation (Degrees) | Clock Cycles | Frame Rate (fps) | Hit Rate (%) | Memory Eff. (%) |

|--------------------|--------------|------------------|--------------|-----------------|

| 0                  | 2355396      | 14.12            | 96.58        | 33.39           |

| 1                  | 2268204      | 14.66            | 96.52        | 34.67           |

| 2                  | 2091471      | 15.90            | 96.56        | 37.60           |

| 3                  | 3067752      | 10.84            | 94.95        | 25.64           |

| 4                  | 3993127      | 8.33             | 93.42        | 19.69           |

| 5                  | 4883897      | 6.81             | 91.95        | 16.10           |

| 10                 | 8824890      | 3.77             | 85.46        | 8.91            |

| 15                 | 11948447     | 2.78             | 80.34        | 6.58            |

| 20                 | 14310431     | 2.32             | 76.48        | 5.50            |

| 25                 | 15961532     | 2.08             | 73.80        | 4.93            |

| 30                 | 16947728     | 1.96             | 72.23        | 4.64            |

| 35                 | 17310474     | 1.92             | 71.71        | 4.54            |

| 40                 | 17087169     | 1.95             | 72.16        | 4.60            |

| 45                 | 16313397     | 2.04             | 73.53        | 4.82            |

Table 3 - 64 Pixel Cache Simulation

| Rotation (Degrees) | <b>Clock Cycles</b> | Frame Rate (fps) | Hit Rate (%) | Memory Eff. (%) |

|--------------------|---------------------|------------------|--------------|-----------------|

| 0                  | 1974900             | 16.84            | 98.34        | 39.82           |

| 1                  | 1944180             | 17.10            | 98.25        | 40.45           |

| 2                  | 3822415             | 8.70             | 96.56        | 20.57           |

| 3                  | 5609832             | 5.93             | 94.95        | 14.02           |

| 4                  | 7303463             | 4.55             | 93.42        | 10.77           |

| 5                  | 8933433             | 3.72             | 91.95        | 8.80            |

| 10                 | 16140794            | 2.06             | 85.46        | 4.87            |

| 15                 | 21845791            | 1.52             | 80.34        | 3.60            |

| 20                 | 26150687            | 1.27             | 76.48        | 3.01            |

| 25                 | 29148412            | 1.14             | 73.80        | 2.70            |

| 30                 | 30923152            | 1.08             | 72.23        | 2.54            |

| 35                 | 31550922            | 1.05             | 71.71        | 2.49            |

| 40                 | 31100289            | 1.07             | 72.16        | 2.53            |

| 45                 | 29636533            | 1.12             | 73.53        | 2.65            |

Table 4 - 128 Pixel Cache Simulation

| Rotation (Degrees) | Clock Cycles | Frame Rate (fps) | Hit Rate (%) | Memory Eff. (%) |

|--------------------|--------------|------------------|--------------|-----------------|

| 0                  | 1483583      | 22.41            | 99.12        | 53.01           |

| 1                  | 2822772      | 11.78            | 98.25        | 27.86           |

| 2                  | 5553359      | 5.99             | 96.56        | 14.16           |

| 3                  | 8151912      | 4.08             | 94.95        | 9.65            |

| 4                  | 10613799     | 3.13             | 93.42        | 7.41            |

| 5                  | 12982969     | 2.56             | 91.95        | 6.06            |

| 10                 | 23456698     | 1.42             | 85.46        | 3.35            |

| 15                 | 31743135     | 1.05             | 80.34        | 2.48            |

| 20                 | 37990943     | 0.88             | 76.48        | 2.07            |

| 25                 | 42335292     | 0.79             | 73.80        | 1.86            |

| 30                 | 44898576     | 0.74             | 72.23        | 1.75            |

| 35                 | 45791370     | 0.73             | 71.71        | 1.72            |

| 40                 | 45113409     | 0.74             | 72.16        | 1.74            |

| 45                 | 42959669     | 0.77             | 73.53        | 1.83            |

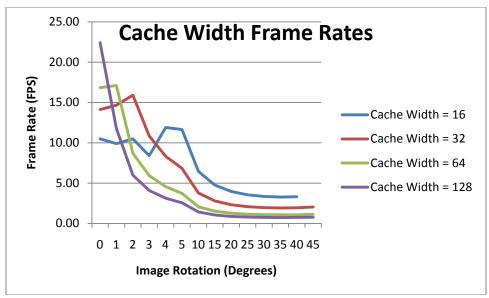

Several conclusions can be drawn from this data. The first is that, in terms of frame rate, none of these is an acceptable cache design. While the cache is providing some benefit, the frame rate for all but one case is less than 20 fps. This is despite the fact that the hit rate for each cache is very high. All 4 cache widths have hit rates of over 90% for image rotations of between 0 and 5 degrees. Another conclusion is that generally smaller cache widths perform better for higher amounts of image rotation and larger cache widths perform better for lower amounts of image rotation. A graph showing the frame rates of all 4 cache design is shown below.

Figure 9 - Cache Simulation Comparing Cache Width

Another interesting aspect of this cache design that can be drawn from the data is that, for smaller cache widths especially, the frame rate is lower for no rotation than it is for small amounts of rotation (1-4 degrees generally). Two factors contribute to this effect. The first is that there is an advantage when the row desired to be loaded in to the cache is the same as the previous row opened, and thus the row opening penalty does not apply as the row is already precharged. Two separate rows are used on each cache load, but for small amounts of positive (counter-clockwise) rotation, as was simulated, the first line loaded in the current cache reload is the same row as the second line loaded in the previous cache load. For instance, the cache might contain data from rows 0 and 1, and when it is refreshed contain data from rows 1 and 2. In these simulations, images with no rotation did not enjoy this advantage because rows would always be loaded in alternating order (e.g. 0, 1, 0, 1, 0, 1, etc.). With some effort, the same data rows could be loaded in the cache in the order 0, 1, 1, 0, 0, 1, etc., maximizing the efficiency of the memory in this case. Because this was not simulated in this matter, 0 degree image rotation had in some cases significantly lower frame rate than small amounts of image rotation.

As an aside, something similar to a "resonant frequency" of the cache can be determined by describing image rotation (a continuous function) using the number of pixels (discrete values) in the horizontal direction before a change in row value occurs. For a given image rotation amount,  $\theta$ , this can be calculated using

$$\tan\theta = \frac{\Delta r}{\Delta c}$$

where  $\Delta r$  is the change in pixel row value, and  $\Delta c$  is the change in pixel column value. For angles less than 45 degrees,  $\Delta r$  can be assumed to be 1. The caches described earlier will operate most efficiently at the amount of image rotation with a

corresponding  $\Delta c$  close to but below their cache width. This means that few pixels at the end of the cache will go unused because they belong to the wrong row, resulting in fewer wasted clock cycles loading unnecessary pixels. Below in Table 5 is a list of the frequencies that were simulated, along with their corresponding  $\Delta c$ . A rotation of 0 degrees would of course have an infinite  $\Delta c$ .

Table 5 - Optimized Cache Sizes for Rotation

| Rotation (degrees) | Δc |

|--------------------|----|

| 1                  | 57 |

| 2                  | 29 |

| 3                  | 19 |

| 4                  | 14 |

| 5                  | 11 |

| 10                 | 6  |

| 15                 | 4  |

| 20                 | 3  |

| 25                 | 2  |

| 30                 | 2  |

| 35                 | 1  |

| 40                 | 1  |

| 45                 | 1  |

This means that a cache of width 64 will operate most efficiently for images rotated approximately 1 degree and a cache of width 32 will operate most efficiently for images rotated approximately 2 degrees. A cache width of 16 presents an interesting scenario for images rotated 3 degrees. Because  $\Delta c$  is 19, if 16 usable pixels are loaded in to the cache in one cache refill, only 3 usable pixels will be loaded in to the cache on the next cache refill because the image row changes on the  $20^{th}$  pixel. Thirteen pixels loaded into the cache1 go unused in this cache refill. Only 59% of the pixels loaded in the two cache refills are useful, and this perhaps more accurately describes this cache's effectiveness than hit rate percentage.

## Prefetch Cache System

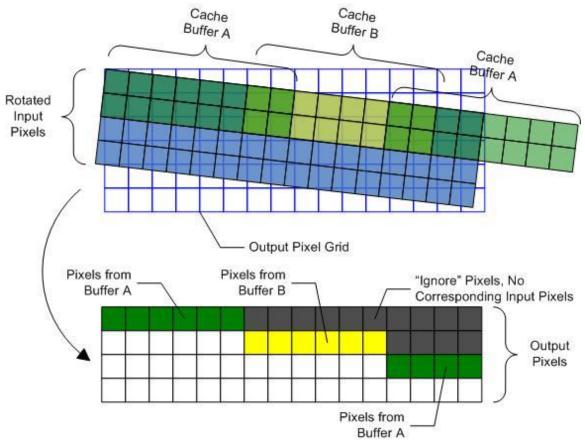

Clearly, there exists room for improvement in the design of this cache system. A major area of inefficiency lies in the fact that the cache cannot be written to and read from at the same time. This can be addressed by exploring the concept of "prefetching". The pre-calculated LUT architecture of the Pixel Router allows for knowledge of the exact input pixel locations where the cache will need to be refilled. This gives rise to the ability to create a "ping-pong" cache system, where one cache buffer is being read from while another cache buffer is being loaded with the next set of pixels to be used. The net effect of this is a two stage cache pipeline system that eliminates the inefficiency of

being unable to read from and write to the cache at the same time. The image below illustrates this concept with an example cache width of 8 pixels.

Figure 10 - Cache Refill Example

In the above image, the blue outlined squares represent the output pixel space, and the rotated blue shaded squares represent input pixels in memory that get rotated in the image transformation. The input image in this case is 16x4 pixels, and each cache buffer contains 8x2 pixels. The image represents a simulation of 3 separate cache fills, first to Buffer A, then to Buffer B, then back to Buffer A. The lower half of the image shows the input pixels applied to the output image space after bilinear interpolation. The green pixels in the lower half of the image were interpolated from the input pixels in Buffer A, and the yellow pixels were interpolated from the input pixels in Buffer B. The dark grey pixels are output pixels which have no corresponding input pixels due to the rotation and thus are ignored for processing and show up as black pixels on the output.

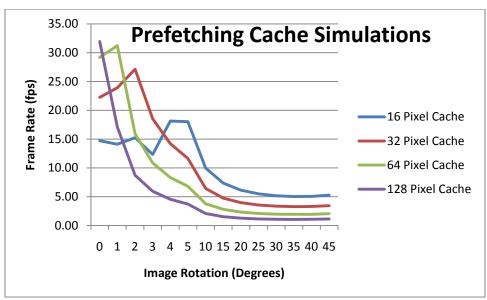

This prefetching cache system was simulated in the same method as the non-prefetch cache system. Again, in these simulations only each cache buffer contains only 2 rows of pixels. The results of the simulation are shown in the tables and graph below.

Table 6 - 16 Pixel Cache Simulation with Prefetching

| Rotation (Degrees) | Clock Cycles | Frame Rate (fps) | Hit Rate (%) | Memory Eff. (%) |

|--------------------|--------------|------------------|--------------|-----------------|

| 0                  | 2262312      | 14.70            | 92.77        | 34.76           |

| 1                  | 2357228      | 14.11            | 92.05        | 33.36           |

| 2                  | 2183259      | 15.23            | 92.14        | 36.02           |

| 3                  | 2701524      | 12.31            | 90.05        | 29.11           |

| 4                  | 1835531      | 18.11            | 92.39        | 42.84           |

| 5                  | 1846757      | 18.00            | 91.95        | 42.58           |

| 10                 | 3337974      | 9.96             | 85.46        | 23.56           |

| 15                 | 4525451      | 7.35             | 80.34        | 17.38           |

| 20                 | 5430239      | 6.12             | 76.48        | 14.48           |

| 25                 | 6071372      | 5.48             | 73.80        | 12.95           |

| 30                 | 6466160      | 5.14             | 72.23        | 12.16           |

| 35                 | 6630138      | 5.01             | 71.71        | 11.86           |

| 40                 | 6577329      | 5.06             | 72.16        | 11.96           |

| 45                 | 6321045      | 5.26             | 73.53        | 12.44           |

Table 7 - 32 Pixel Cache Simulation with Prefetching

| Rotation (Degrees) | <b>Clock Cycles</b> | Frame Rate (fps) | Hit Rate (%) | Memory Eff. (%) |

|--------------------|---------------------|------------------|--------------|-----------------|

| 0                  | 1495236             | 22.24            | 96.58        | 52.60           |

| 1                  | 1391436             | 23.90            | 96.52        | 56.52           |

| 2                  | 1225999             | 27.12            | 96.56        | 64.15           |

| 3                  | 1796712             | 18.51            | 94.95        | 43.77           |

| 4                  | 2337959             | 14.22            | 93.42        | 33.64           |

| 5                  | 2859129             | 11.63            | 91.95        | 27.51           |

| 10                 | 5166938             | 6.44             | 85.46        | 15.22           |

| 15                 | 6999775             | 4.75             | 80.34        | 11.24           |

| 20                 | 8390303             | 3.96             | 76.48        | 9.37            |

| 25                 | 9368092             | 3.55             | 73.80        | 8.39            |

| 30                 | 9960016             | 3.34             | 72.23        | 7.90            |

| 35                 | 10190250            | 3.26             | 71.71        | 7.72            |

| 40                 | 10080609            | 3.30             | 72.16        | 7.80            |

| 45                 | 9651829             | 3.44             | 73.53        | 8.15            |

Table 8 - 64 Pixel Cache Simulation with Prefetching

| Rotation (Degrees) | Clock Cycles | Frame Rate (fps) | Hit Rate (%) | Memory Eff. (%) |

|--------------------|--------------|------------------|--------------|-----------------|

| 0                  | 1139316      | 29.18            | 98.34        | 69.03           |

| 1                  | 1065588      | 31.20            | 98.25        | 73.80           |

| 2                  | 2091471      | 15.90            | 96.56        | 37.60           |

| 3                  | 3067752      | 10.84            | 94.95        | 25.64           |

| 4                  | 3993127      | 8.33             | 93.42        | 19.69           |

| 5                  | 4883897      | 6.81             | 91.95        | 16.10           |

| 10                 | 8824890      | 3.77             | 85.46        | 8.91            |

| 15                 | 11948447     | 2.78             | 80.34        | 6.58            |

| 20                 | 14310431     | 2.32             | 76.48        | 5.50            |

| 25                 | 15961532     | 2.08             | 73.80        | 4.93            |

| 30                 | 16947728     | 1.96             | 72.23        | 4.64            |

| 35                 | 17310474     | 1.92             | 71.71        | 4.54            |

| 40                 | 17087169     | 1.95             | 72.16        | 4.60            |

| 45                 | 16313397     | 2.04             | 73.53        | 4.82            |

Table 9 - 128 Pixel Cache Simulation with Prefetching

| Rotation (Degrees) | <b>Clock Cycles</b> | Frame Rate (fps) | Hit Rate (%) | Memory Eff. (%) |

|--------------------|---------------------|------------------|--------------|-----------------|

| 0                  | 1041215             | 31.93            | 99.12        | 75.53           |

| 1                  | 1944180             | 17.10            | 98.25        | 40.45           |

| 2                  | 3822415             | 8.70             | 96.56        | 20.57           |

| 3                  | 5609832             | 5.93             | 94.95        | 14.02           |

| 4                  | 7303463             | 4.55             | 93.42        | 10.77           |

| 5                  | 8933433             | 3.72             | 91.95        | 8.80            |

| 10                 | 16140794            | 2.06             | 85.46        | 4.87            |

| 15                 | 21845791            | 1.52             | 80.34        | 3.60            |

| 20                 | 26150687            | 1.27             | 76.48        | 3.01            |

| 25                 | 29148412            | 1.14             | 73.80        | 2.70            |

| 30                 | 30923152            | 1.08             | 72.23        | 2.54            |

| 35                 | 31550922            | 1.05             | 71.71        | 2.49            |

| 40                 | 31100289            | 1.07             | 72.16        | 2.53            |

| 45                 | 29636533            | 1.12             | 73.53        | 2.65            |

Figure 11 - Cache Simulation with Prefetching

Based on these simulations, the frame rate using a prefetching cache system is greatly improved over using a non-prefetching cache. One item to note, however, is that the cache hit rate is unchanged between the two cache designs. This is because cache hit rate is defined as

Cache Hit Rate =

$$\frac{Cache\ Misses}{Cache\ Hits+Cache\ Misses} * 100\%$$

.

The number of cache hits and cache misses is unaffected by adding a second cache buffer. The only operational difference is that when a cache miss occurs, the buffers are switched if the second buffer is done loading. The table below shows the percentage improvement of the prefetching cache over the non-prefetching cache for the four cache widths examined.

Table 10 - Prefetching Cache Improvement

| Cache Width (Pixels) | Average Improvement (%) |  |  |

|----------------------|-------------------------|--|--|

| 16                   | 50.95                   |  |  |

| 32                   | 68.89                   |  |  |

| 64                   | 81.91                   |  |  |

| 128                  | 45.03                   |  |  |

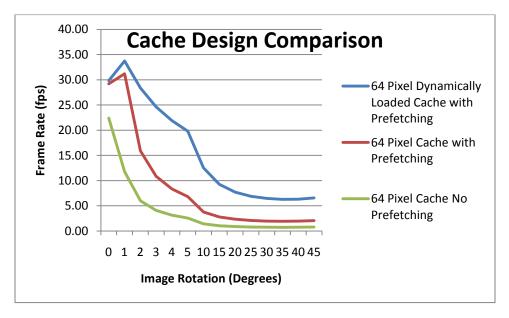

# Dynamically Loaded Cache System

This cache design brings the Pixel Router operation with bilinear interpolation closer in line to the previous performance standard using nearest neighbor interpolation of 20 frames per second. In fact, several cache widths exceed this mark for small amounts of rotation. However, it is clear that the performance of this cache is very dependent on the image transformation to be performed. While the goal of this project was to design a cache that is optimized for small amounts of rotation, a robust design should make every effort to maximize performance in as many cases as possible while still maintaining its optimization target. The prefetching cache design reduced or eliminated the clock cycle penalty of reading data from the cache. However as the amount of image rotation is increased, more of the pixels that are loaded in to the cache remain unused. Once again, the fixed nature of the LUT architecture of the Pixel Router lends itself to a solution to this issue. Just as it is possible to know which memory address in the input buffer to begin loading the second cache buffer with, it is also possible to know which pixels in the cache will cause a cache miss. Thus, an additional field can be added to the look up table that tells the Pixel Router how many pixels to load in the cache on a given cache refill. This "Pixels to Load" field allows the cache to be dynamically loaded with only pixels that are guaranteed to be used rather than with an entire set of pixels equal to the cache width.

To determine the impact of a dynamically loaded cache system, a 64 pixel wide cache was examined. The table below shows the simulation results of the cache simulated under the same conditions as the previous cache designs. The following graph compares the frame rates of the dynamically loaded cache with the 64 pixel statically loaded cache with and without prefetching.

Table 11 - Dynamically Loaded Cache Simulation

|                    |              |                  |              | Memory   |

|--------------------|--------------|------------------|--------------|----------|

| Rotation (Degrees) | Clock Cycles | Frame Rate (fps) | Hit Rate (%) | Eff. (%) |

| 0                  | 1114740      | 29.83            | 98.34        | 70.55    |

| 1                  | 986036       | 33.72            | 98.25        | 79.76    |

| 2                  | 1171737      | 28.38            | 96.56        | 67.12    |

| 3                  | 1350784      | 24.62            | 94.95        | 58.22    |

| 4                  | 1518483      | 21.90            | 93.42        | 51.79    |

| 5                  | 1679797      | 19.79            | 91.95        | 46.82    |

| 10                 | 2652096      | 12.54            | 85.46        | 29.65    |

| 15                 | 3597563      | 9.24             | 80.34        | 21.86    |

| 20                 | 4320215      | 7.70             | 76.48        | 18.20    |

| 25                 | 4835102      | 6.88             | 73.80        | 16.27    |

| 30                 | 5155964      | 6.45             | 72.23        | 15.25    |

| 35                 | 5295096      | 6.28             | 71.71        | 14.85    |

| 40                 | 5263599      | 6.32             | 72.16        | 14.94    |

| 45                 | 5072001      | 6.56             | 73.53        | 15.51    |

Figure 12 - Dynamically Loaded Cache Simulation

Dynamically loading this cache with only pixels that are guaranteed to be useful provides an enormous performance increase, especially for cases with image rotation. This makes sense as image rotation causes fewer pixels in a given input row to be valid for a given output row. Dynamically loading the cache brings any given cache width in line with the values in Table 5, where the effective cache width is roughly equal to  $\Delta c$  for a given image rotation value. Based on these simulations, the Pixel Router should

operate at or above 20 frames per second for up to 5 degrees of rotation for a 1024x768 pixel image.

## Cache Definitions

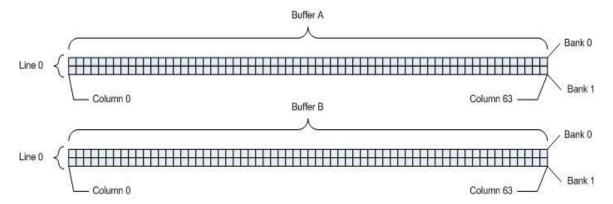

The cache design implemented in the Pixel Router to support bilinear interpolation was a 64 pixel wide dynamically loaded cache with prefetching. The image below presents this cache and the definitions of its fields.

Figure 13 – Cache Field Definitions Definitions

The cache is comprised of two buffers, Buffer A and Buffer B, which act as the prefetch pipeline. One buffer is being read from while another buffer is being written to. Each cache buffer consists of one cache line (Line 0). A cache line contains data from two rows of input pixels, however this data is only valid for one output pixel line due to bilinear interpolation, thus one line represents two rows. The input pixel rows in each cache line are referred to as banks, and each cache line contains two of them (Bank 0 and Bank 1). There are 64 columns in each bank which represent the 64 pixel locations available.

### Additional Cache Lines

Cache simulations to this point have included one cache line per buffer. The natural extension of this is to consider whether additional cache lines would provide performance benefits. To determine this, an 8 line cache was examined. In this case, Buffer A and Buffer B would each contain 8 cache lines, and each cache line would be filled starting with the address of the next predicted cache miss. The simulation showing the percentage improvement in frame rate of an 8 line cache over a 1 line cache are shown below.

Table 12 - Cache with 8 Lines

| Rotation (Deg) | Frame Rate, 8 Lines (fps) | Frame Rate, 1 Line (fps) | Improvement (%) |

|----------------|---------------------------|--------------------------|-----------------|

| 0              | 38.81                     | 29.83                    | 30.13           |

| 1              | 33.50                     | 33.72                    | -0.66           |

| 2              | 28.69                     | 28.38                    | 1.09            |

| 3              | 25.08                     | 24.62                    | 1.90            |

| 4              | 22.48                     | 21.90                    | 2.64            |

| 5              | 20.43                     | 19.79                    | 3.21            |

| 10             | 13.11                     | 12.54                    | 4.55            |

| 15             | 9.72                      | 9.24                     | 5.13            |

| 20             | 8.13                      | 7.70                     | 5.66            |

| 25             | 7.31                      | 6.88                     | 6.27            |

| 30             | 6.90                      | 6.45                     | 6.98            |

| 35             | 6.77                      | 6.28                     | 7.87            |

| 40             | 6.88                      | 6.32                     | 8.98            |

| 45             | 7.24                      | 6.56                     | 10.47           |

While the 8 line cache offers improvement for the case of 0 degree rotation, there is little difference in performance for images with rotation. The improvement in the 0 degree rotation case can be attributed to the fact that this cache is organized and written in such a way as to minimize row opening penalties. To achieve this, all entries of a particular row within a cache refill are opened consecutively, regardless of the order they will be accessed in. This has the greatest impact on images with no rotation because most of the entries in a particular cache refill are in the same video row, thus eliminating a greater number of row opening penalties. For rotated images, however, roughly the same number of row opening penalties occur in an 8 line cache as in a 1 line cache, which is why there is little if any improvement gained by using an 8 line cache in this case. Because the overall benefit of additional cache lines is minimal, it was decided that a 1 line cache would suffice in the final implementation of the Pixel Router to reduce hardware complexity and conserve memory space on the FPGA.

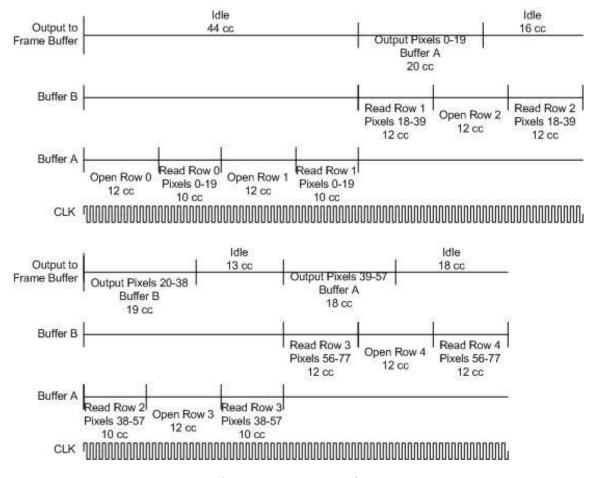

#### Cache Operation Example

To better understand the process of writing to and reading from a cache, here a clock cycle simulation is presented as an example. This simulation uses data from a look up table that describes a 3 degree image rotation. Below is the data from that look up table.

Table 13 - Prefetch LUT Data

| Pixels to Load | Input Column | Input Row | Cache Line | Bank |

|----------------|--------------|-----------|------------|------|

| 20             | 0            | 0         | 0          | 0    |

| 20             | 0            | 1         | 0          | 1    |

| 22             | 18           | 1         | 0          | 0    |

| 22             | 18           | 2         | 0          | 1    |

| 20             | 38           | 2         | 0          | 0    |

| 20             | 38           | 3         | 0          | 1    |

| 22             | 56           | 3         | 0          | 0    |

| 22             | 56           | 4         | 0          | 1    |

There are a few points to note about this data. The Pixels to Load field in this data, as in all cases, is an even value. This is due to the fact that the DDR SDRAM data bus to the FPGA is effectively 64 bits per clock cycle, which is enough data for two 24-bit pixels. Thus, it does not make sense to load an odd number of pixels because two pixels are loaded per clock cycle no matter what. In addition, the Input Column field is also even. This will be addressed in a later section, but to save space in the Look Up Table, the input address field was reduced by one bit, forcing the column of the address to be an even number. The image below shows the timing diagram of the memory reads and writes for this simulation.

Figure 14 - Cache Operation Example Timing Diagram

This conceptual timing diagram illustrates the impact of the memory overhead and the effect of the "ping-pong" cache. The first line represents pixels output to the frame buffer, where they are stored before being output on the HDMI port. The next two lines tell what activity is taking place on either Buffer A or Buffer B, and how many clock cycles it takes. The last line is the Clock signal for reference. Note that after the first time Buffer A is written to, the amount of time the output to the frame buffer is idle drops significantly. Starting on the 45<sup>th</sup> clock cycle, the output frame buffer is written to for 57 clock cycles and idle for 47 clock cycles, giving it an active percentage of 54.8%. The first 44 clock cycles can be considered a one-time penalty at the beginning of the frame to load the first pixels into the first cache buffer, as after that output pixels will always be processed concurrently with cache refills.

#### Measured Results

This cache design has been implemented on the Pixel Router by Verien Design, Inc., an outside consulting firm, and is operational. The frame rate for LUTs of different rotation

amounts was measured to validate the results from simulation. The results are shown in the table below, along with the simulated values.

Table 14 - Measured versus Simulated Frame Rates

| Rotation (Deg) | Real Frame Rate (FPS) | Simulated Frame Rate (FPS) |

|----------------|-----------------------|----------------------------|

| 0              | 20                    | 29.83                      |

| 1              | 30                    | 33.72                      |

| 2              | 20                    | 28.38                      |

| 3              | 20                    | 24.62                      |

| 4              | 20                    | 21.90                      |

| 5              | 15                    | 19.79                      |

| 10             | 12                    | 12.54                      |

This frame rate data was taken from the Pixel Router control interface, which provides frame rate information for each input channel. The frame rate on Channel 1 was measured. The Pixel Router calculates frame rate in hardware and can only provide values that are divisors of 60, without rounding up. This explains the difference between the simulated and measured values. For instance, at 0 degrees rotation, the simulated value was 29.83 degrees, but the measured value in hardware rounded down to 20 degrees. Based on this measurement restriction, however, the measured frame rate correlates directly with the simulated frame rate. Unfortunately, measurements for images rotated more than 10 degrees were not able to be obtained due to a flaw in the hardware.

# **Section 5: LUT Description and Generation**

### LUT Description

The image transformation performed by the Pixel Router is calculated offline and described by Look Up Tables (LUTs) that tell the hardware what order to process the pixels in and the attenuation factor for specific pixels. To accommodate the prefetching cache system, a dual LUT architecture was developed. In this architecture, one LUT contains 2 entries for each cache refill (one for each row of input memory to be read) that describe which input pixels to load in the cache, how many to load, and which cache location they should be stored in. This LUT is known as the "Prefetch LUT". The other LUT, known as the "Per-Pixel LUT", has one entry per output pixel and contains information about where in the cache the input pixels are located, the attenuation factor of this output pixel, and the X and Y pixel weights for bilinear interpolation. Both the Prefetch LUT and Per-Pixel LUT are made up of 32-bit entries, with headers at the top that describe which type of LUT it is and how many entries are present. The Per-Pixel LUT contains as many entries as there are pixels in the output space. The number of entries in the Prefetch LUT is dependent on the number of cache refreshes required for a particular image transformation. The tables below are described in the Pixel Router Specification [3] and contain a detailed description of each LUT field.

Table 15 - Prefetch LUT Description [3]

| Bits  | Field          | Description                                                                                                                            |

|-------|----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 31    | Reserved       | Reserved                                                                                                                               |

| 30:26 | Pixels_To_Load | Pixels to be loaded in to the cache, mod 2. The number of pixels loaded in to the cache is 2*(Pixels_To_Load+1).                       |

| 25:24 | Channel_ID     | Input channel ID                                                                                                                       |

| 23:4  | Offset         | Address of the first pixel to be loaded in to the cache line, mod 2. Address space allows for an image with 1920x1080 pixels           |

| 3     | CD_Bank        | Bank within Buffer A or B to which data will be written.                                                                               |

| 2:0   | CD_ID          | Cache line where the data will be written. Note that the Pixel Router currently only supports 1 cache line, so this value is always 0. |

Table 16 - Per Pixel LUT Description [3]

| Bits  | Field    | Description                                                                                                                     |  |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------|--|

| 31:30 | Command  | Command bits: 00: User bilinear interpolation, normal operation. 01: Switch cache buffers (A to B or B to A) due to cache miss. |  |

| 29:28 | Reserved | Reserved                                                                                                                        |  |

| 27    | CD_ID1   | Cache Destination ID 1. Cache line in bank 1 containing pixel 3 and 4 for bilinear interpolation.                               |  |

| 26    | CD_ID0   | Cache Destination ID 0. Cache line in bank 0 containing pixel 1 and 2 for bilinear interpolation.                               |  |

| 25:20 | ADDR1    | Address of pixel 3 within cache line CD_ID1. Pixel 4 is located at ADDR1+1.                                                     |  |

| 19:14 | ADDR0    | Address of pixel 1 within cache line CD_ID0. Pixel 2 is located at ADDR0+1.                                                     |  |

| 13:6  | Alpha    | Alpha blending attenuation factor.                                                                                              |  |

| 5:3   | SubY     | The Y coordinate of the output pixel relative to the input pixels for bilinear interpolation.                                   |  |

| 2:0   | SubX     | The X coordinate of the output pixel relative to the input pixels for bilinear interpolation.                                   |  |

The LUT entry fields were designed to maximize flexibility for any future upgrades by enabling control of multiple cache lines (only one is used currently) and leaving bits available for future use. For instance, the cache could be expanded to 128 pixels wide by using increasing the field size of ADDR1, ADDR0, and Pixels\_To\_Load by one bit using the bits that are currently labeled "Reserved" in the LUT description. Alternatively, additional cache lines could be added, causing the field size of CD\_ID1 and CD\_ID0 to increase. Through continued use of the Pixel Router and evaluation of future requirements, it will be determined which, if any, of these changes would provide maximum benefit or usefulness.

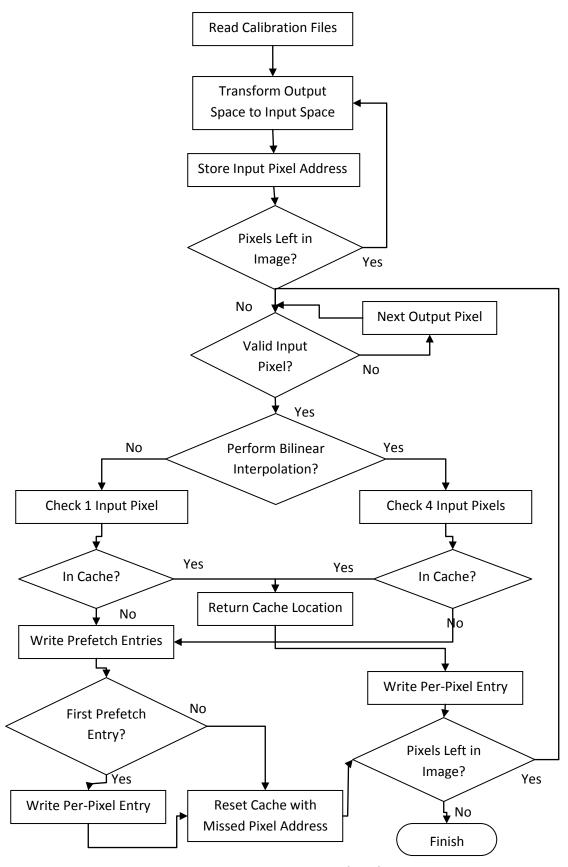

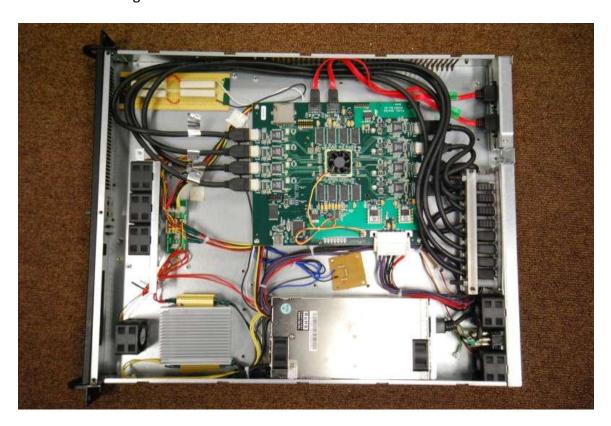

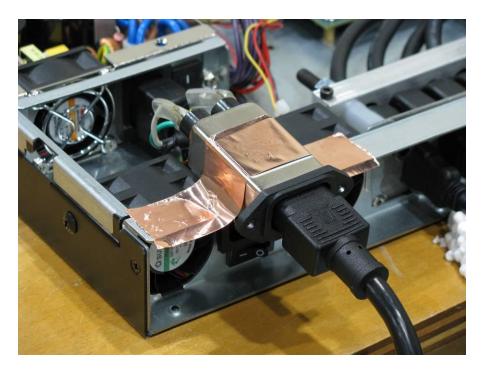

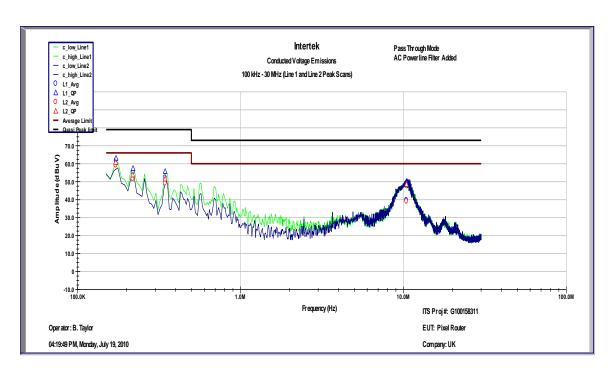

#### LUT Generation