# University of South Florida Scholar Commons

Graduate Theses and Dissertations

Graduate School

May 2018

# Emerging Non-Volatile Memory Technologies for Computing and Security

Rekha Govindaraj University of South Florida, rekhag@mail.usf.edu

Follow this and additional works at: https://scholarcommons.usf.edu/etd Part of the <u>Computer Engineering Commons</u>, and the <u>Computer Sciences Commons</u>

Scholar Commons Citation

Govindaraj, Rekha, "Emerging Non-Volatile Memory Technologies for Computing and Security" (2018). *Graduate Theses and Dissertations.* https://scholarcommons.usf.edu/etd/7674

This Dissertation is brought to you for free and open access by the Graduate School at Scholar Commons. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact scholarcommons@usf.edu.

Emerging Non-Volatile Memory Technologies for Computing and Security

by

Rekha Govindaraj

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy Department of Computer Science and Engineering College of Engineering University of South Florida

Co-Major Professor: Swaroop Ghosh, Ph.D. Co-Major Professor: Srinivas Katkoori, Ph.D. Charles Augustine, Ph.D. Xinming (Simon) Ou, Ph.D. Srikant Srinivasan, Ph.D.

> Date of Approval: May 31, 2018

Keywords: Content Addressable Memory, Hardware Security, Spintronic Memory, Magnetic Tunnel Junction, Resistive Random Access Memory, Random Telegraph Noise

Copyright © 2018, Rekha Govindaraj

# DEDICATION

Dedicated to my parents. "Nothing in life is to be feared, it is only to be understood. Now is the time to understand more, so that we may fear less" - Marie Curie (1867-1934)

#### ACKNOWLEDGMENTS

I would like to express my deep gratitude to Dr. Swaroop Ghosh for his indispensable support and patience in training me during my PhD journey. Advices from Dr. Ghosh have helped me tackle complex problems effortlessly by always keeping the broader picture of my research. Constant support from Dr. Ghosh through out has helped me not only be successful in my current academic research but in preparing me for future endeavors.

My special thanks to Dr. Srinivas Katkoori for accepting me as his student and supporting my research interests. I thank my co-advisors Dr. Swaroop Ghosh and Dr. Srinivas Katkoori for spending countless hours in research problem discussions, meticulously reviewing the paper drafts and this dissertation. Constructive and critical comments from Dr. Ghosh and Dr. Katkoori were crucial in having successful publications.

I acknowledge and deeply appreciate the presence and contribution of other students at Dr. Ghosh's and Dr. Katkoori's lab in this success. I like to thank University of South Florida faculty, staff and student members at the Department of Computer Science and Engineering for all the support and assistance in successfully completing my research. I also thank my cohorts at American Association of University Women (AAUW-USF) for their camaraderie at graduate school.

I sincerely thank my loving parents, amazing siblings Nagaraj and Roopa, wonderful husband Shantharaju for all their love and support for my success. I thank all my friends for their help and presence to make this journey the most cherish-able.

# TABLE OF CONTENTS

| LIST OF TABLES                                                   | iv   |

|------------------------------------------------------------------|------|

| LIST OF FIGURES                                                  | v    |

| ABSTRACT                                                         | viii |

| CHAPTER 1 : INTRODUCTION                                         | 1    |

| 1.1 Conventional CMOS and Design Challenges                      | 1    |

| 1.2 Emerging Technologies - Beyond CMOS for Memory and Computing | 3    |

| 1.3 Hardware Security                                            | 5    |

| 1.4 Organization of Thesis                                       | 8    |

| CHAPTER 2 : MAGNETIC TUNNEL JUNCTION DEVICE                      | 9    |

| 2.1 Introduction                                                 | 9    |

| 2.2 Magnetic Tunnel Junction                                     | 10   |

| 2.3 MTJ for Memory and Computing                                 | 14   |

| 2.4 Summary                                                      | 16   |

| CHAPTER 3 : RESISTIVE RANDOM ACCESS MEMORY                       | 17   |

| 3.1 Introduction                                                 | 17   |

| 3.2 Types of RRAM                                                | 18   |

| 3.3 RRAM for Hardware Security                                   | 20   |

| 3.4 Summary                                                      | 24   |

| CHAPTER 4 : 6T-2MTJ TERNARY CAM                                  | 25   |

| 4.1 Introduction                                                 | 25   |

| 4.2 Content Addressable Memory                                   | 27   |

| 4.3 Proposed TCAM Cell                                           | 28   |

| 4.3.1 NOR TCAM Cell Circuit                                      | 28   |

| 4.3.2 Qualitative Analysis of the Cell Design                    | 29   |

| 4.3.3 Write Operation                                            | 32   |

| 4.3.4 Search Operation                                           | 34   |

| 4.4 Proposed NAND Type TCAM Cell                                 | 37   |

| 4.5 NOR TCAM Cell Design Analysis                                | 40   |

| 4.5.1 Selection of $R_L$ and NMOS Device                         | 41   |

|         | 4.5.2 Impact of TMR on Sense Margin                            | 42 |

|---------|----------------------------------------------------------------|----|

| 4.6     | Simulation Results of NOR TCAM Cell                            | 44 |

|         | 4.6.1 Setup                                                    | 44 |

|         | 4.6.2 Temperature Variation Analysis                           | 44 |

|         | 4.6.3 Voltage Scaling                                          | 46 |

|         | 4.6.4 Process Variation Analysis                               | 47 |

| 4.7     | $V_{TH}$ and SE Modulation for Sense Margin Improvement        | 48 |

| 4.8     | NAND Type TCAM Cell Simulation Results                         | 49 |

| 4.9     | Comparative Analysis                                           | 52 |

|         | 4.9.1 Comparison with CMOS TCAM                                | 52 |

|         | 4.9.2 Comparison with Spintronic CAMs                          | 53 |

| 4.10    | Summary                                                        | 55 |

| CHAPTER | 5 : CSRO BASED TRUE RANDOM NUMBER GENERATOR                    | 56 |

| 5.1     | Introduction                                                   | 56 |

| 5.2     | Background and Related Work                                    | 57 |

| 5.3     | Proposed RRAM TRNG                                             | 60 |

|         | 5.3.1 Details of the Proposed TRNG                             | 60 |

|         | 5.3.2 Sampling Frequency                                       | 62 |

|         | 5.3.3 Configurability                                          | 63 |

|         | Simulation Results                                             | 66 |

| 5.5     | Adversary Attacks on TRNGs                                     | 69 |

|         | 5.5.1 Background of Attacks and Prevention                     | 70 |

|         | 5.5.2 Vulnerabilities of RRAM-based Design                     | 70 |

|         | 5.5.3 Attack Model: Colling and Model Building                 | 71 |

|         | 5.5.4 Countermeasures: Temperature Sensing and Configurability | 71 |

| 5.6     | Summary                                                        | 72 |

|         | 6 : RRAM ARBITER PUF WITHIN 1T-1R MEMORY ARCHITECTURE          | 73 |

|         | Introduction                                                   | 73 |

| 6.2     | Background                                                     | 75 |

|         | 6.2.1 Background of PUFs                                       | 75 |

|         | 6.2.2 Background of RRAM PUFs                                  | 75 |

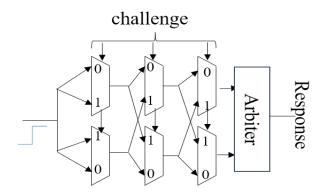

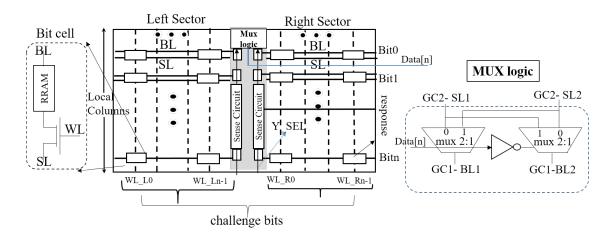

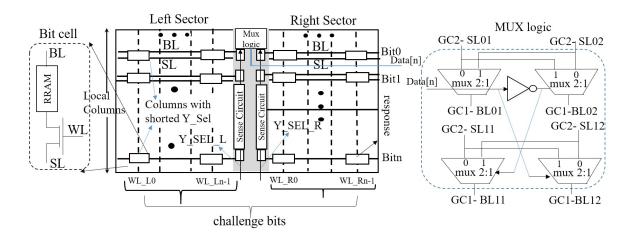

| 6.3     | Proposed PUF Architecture                                      | 76 |

|         | 6.3.1 Summary of Proposed PUF Architecture                     | 77 |

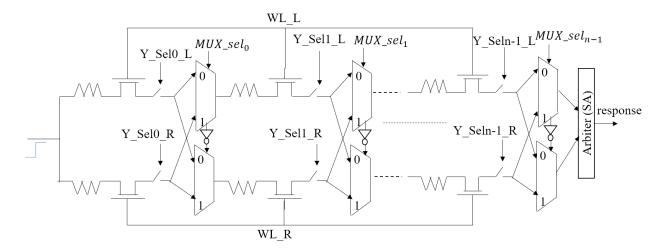

|         | 6.3.2 Implementation of APUF                                   | 78 |

|         | 6.3.3 Implementation of Challenges                             | 79 |

|         | 6.3.4 Implementation of Arbiter                                | 79 |

|         | 6.3.5 Number of CRPs                                           | 80 |

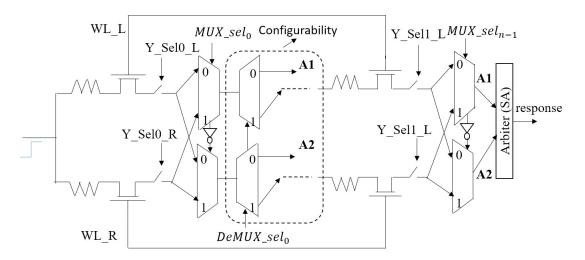

|         | 6.3.6 Configurability                                          | 80 |

|         | 6.3.7 CRPs with Configurability                                | 81 |

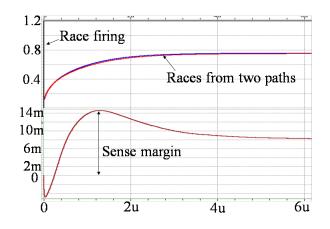

| 6.4     | Simulation Results                                             | 82 |

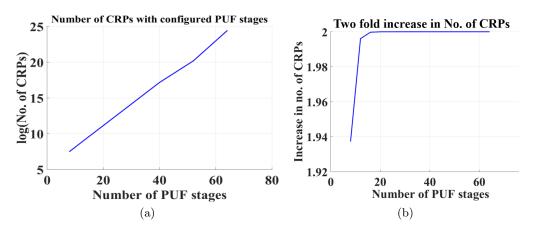

| 6.5 Attacks on Proposed APUF                                 | 86       |

|--------------------------------------------------------------|----------|

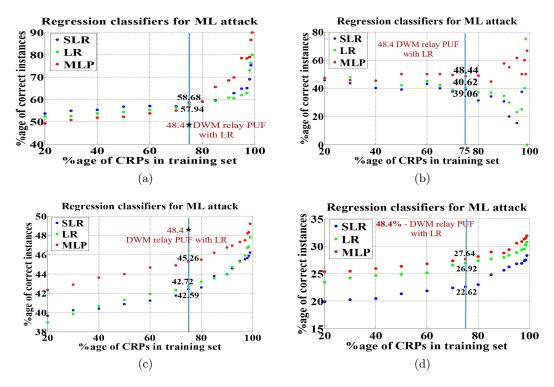

| 6.5.1 ML Based Model Building Attacks                        | 87       |

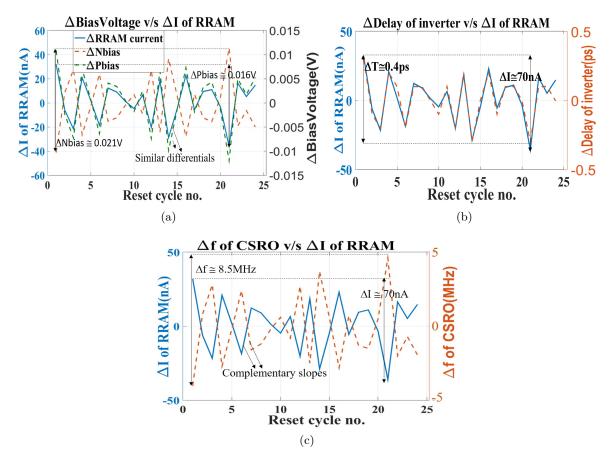

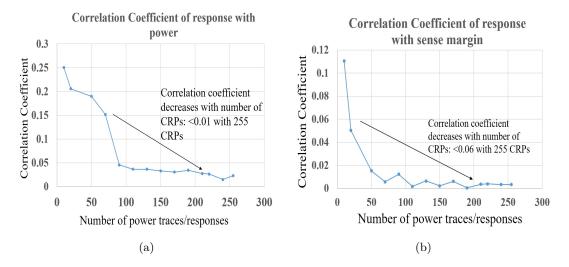

| 6.5.2 Analysis of Side Channel Attacks                       | 89       |

| 6.6 Proposed Architecture for Resiliency to ML Attacks       | 91       |

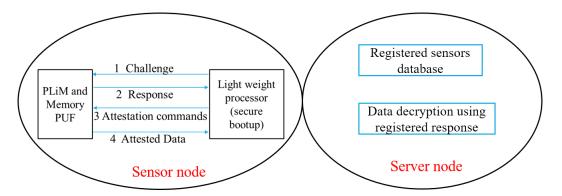

| 6.7 Application in Hardware Attestation                      | 93       |

| 6.7.1 Basics of Hardware Attestation                         | 93       |

| 6.7.2 Implementation of Encryption Hardware                  | 95       |

| 6.7.3 Data Attestation Sensor Node                           | 96       |

| 6.7.4 Performance Analysis of Proposed Attestation Technique | 96       |

| 6.8 Summary                                                  | 97       |

| CHAPTER 7 : SUMMARY                                          | 98       |

| REFERENCES                                                   | 100      |

| APPENDIX A: COPYRIGHT CLEARANCE FORMS                        | 112      |

| ABOUT THE AUTHOR                                             | END PAGE |

# LIST OF TABLES

| Table 1.1 | Properties offered by emerging NVM technologies $[1, 2]$      | 6  |

|-----------|---------------------------------------------------------------|----|

| Table 2.1 | Parameters of MTJ used                                        | 14 |

| Table 4.1 | States of control signals NOR TCAM memory write operations.   | 33 |

| Table 4.2 | States of control signals NOR TCAM memory search operations.  | 35 |

| Table 4.3 | States of control signals NAND TCAM memory write operations.  | 39 |

| Table 4.4 | States of control signals NAND TCAM memory search operations. | 39 |

| Table 4.5 | Power (in $\mu W)$ comparison of CMOS and proposed TCAMs      | 53 |

| Table 4.6 | Comparison with other spintronic CAMs                         | 54 |

| Table 5.1 | Comparative analysis of TRNG                                  | 64 |

| Table 6.1 | Number of CRPs with and without configurability.              | 82 |

| Table 6.2 | Comparison of RRAM based PUFs                                 | 93 |

# LIST OF FIGURES

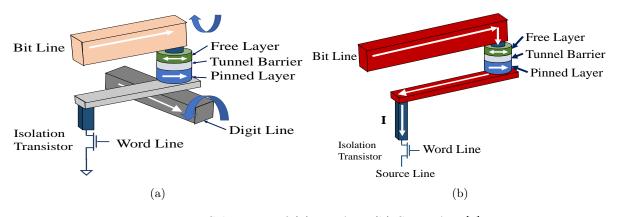

| Figure 2.1  | Schematic of (a) MRAM; (b) STTRAM [1].                                                  | 11 |

|-------------|-----------------------------------------------------------------------------------------|----|

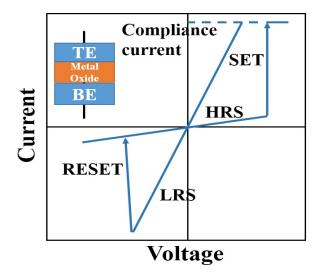

| Figure 3.1  | RRAM memory device and resistance transfer characteristics.                             | 18 |

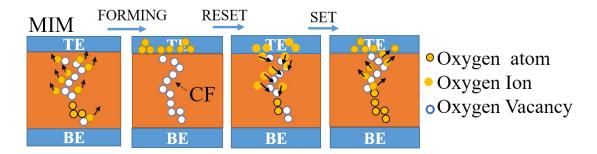

| Figure 3.2  | Forming, SET and RESET switching mechanism in RRAM.                                     | 19 |

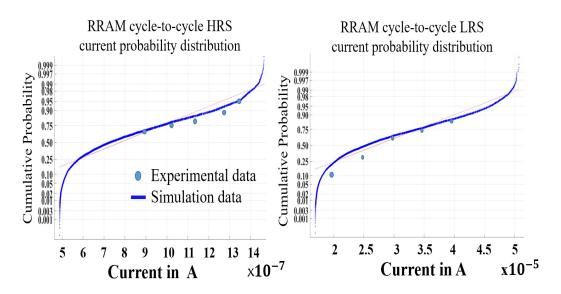

| Figure 3.3  | LRS and HRS distribution of RRAM.                                                       | 22 |

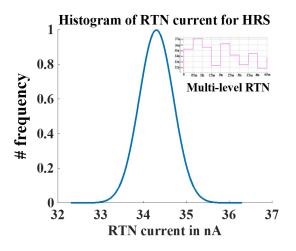

| Figure 3.4  | RTN current distribution in HRS state of RRAM based on measurement data [3].            | 24 |

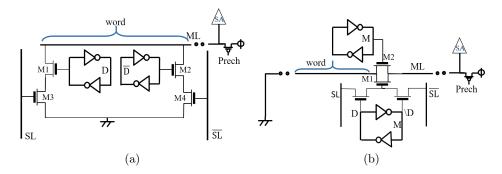

| Figure 4.1  | Conventional CMOS TCAM types                                                            | 28 |

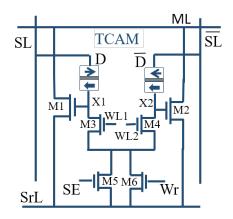

| Figure 4.2  | Proposed NOR type TCAM cell.                                                            | 29 |

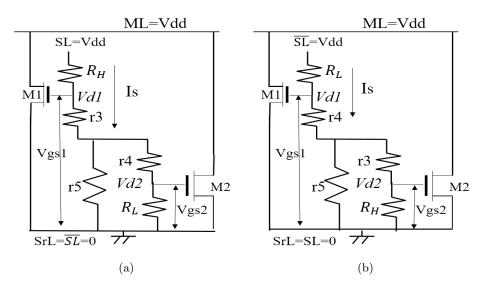

| Figure 4.3  | Equivalent circuit during match and mismatch.                                           | 30 |

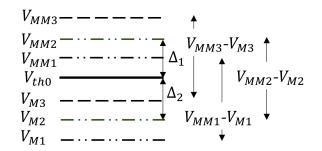

| Figure 4.4  | $V_{gs}$ margin diagram illustrating best and worst $V_M$ and $V_{MM}$ with $V_{th0}$ . | 32 |

| Figure 4.5  | Equivalent circuit during write and search operation.                                   | 33 |

| Figure 4.6  | Waveform showing the search operation.                                                  | 36 |

| Figure 4.7  | Proposed NAND configuration TCAM cell (Bit 0 stored).                                   | 38 |

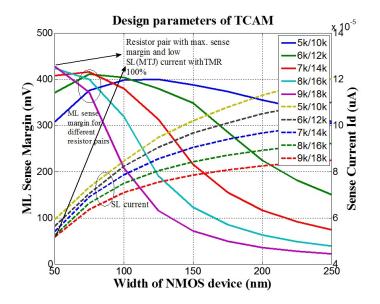

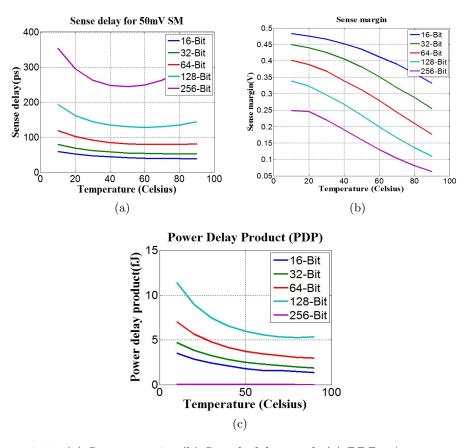

| Figure 4.8  | Width of M5 v/s SM and STTRAM current from SL for various $R_L$ .                       | 42 |

| Figure 4.9  | Width of M3/M4 v/s sense margin and search current for various $R_L$ .                  | 43 |

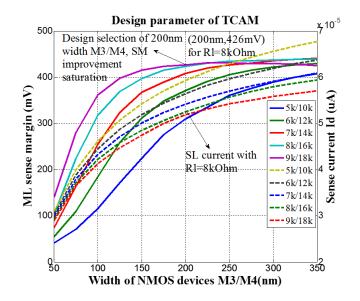

| Figure 4.10 | ML sense margin and search current with width of NMOS M5 and TMR.                       | 44 |

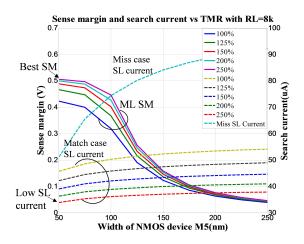

| Figure 4.11 | (a) Sense margin; (b) Search delay; and, (c) PDP v/s temperature.                       | 45 |

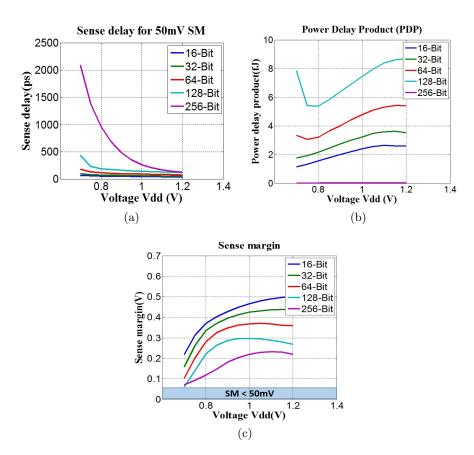

| Figure 4.12 | Voltage scaling from 0.7V to 1.2V.                                                      | 46 |

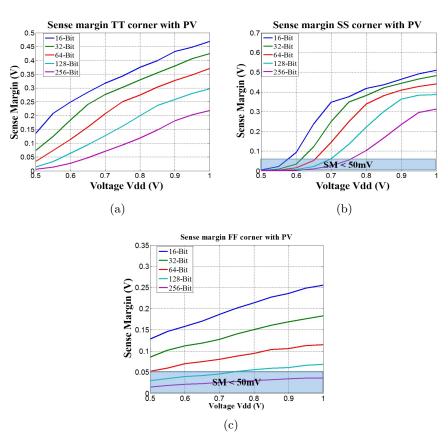

| Figure 4.13 | Distribution of sense margin in (a) TT; (b) SS; and, (c) FF corners.                    | 48 |

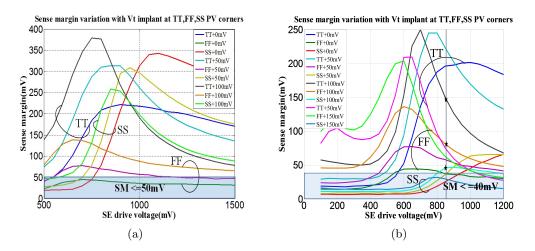

| Figure 4.14 | Maximum SM variation with $V_{TH}$ implant.                                             | 50 |

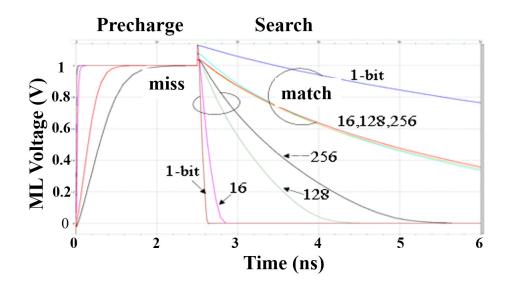

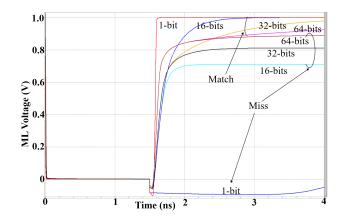

| Figure 4.15 Match and miss case match line voltages.                              | 51 |

|-----------------------------------------------------------------------------------|----|

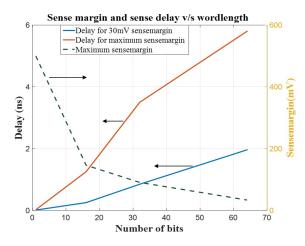

| Figure 4.16 Search delay and maximum SM of NAND type TCAM v/s word length.        | 51 |

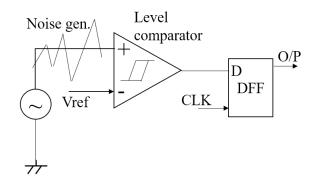

| Figure 5.1 Noise based RNG.                                                       | 58 |

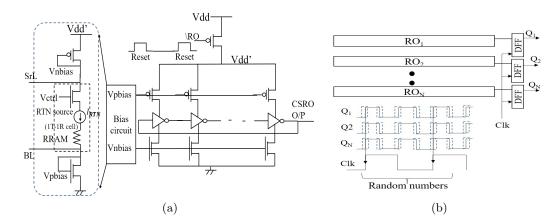

| Figure 5.2 (a) Proposed TRNG based on CSRO; and, (b) Illustration of N-bit TRNG.  | 61 |

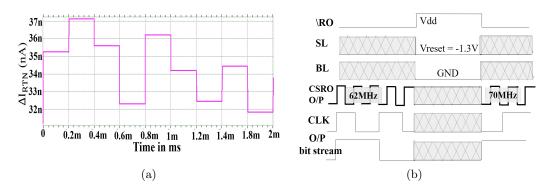

| Figure 5.3 RTN current $\Delta I$ and reconfiguration of TRNG.                    | 63 |

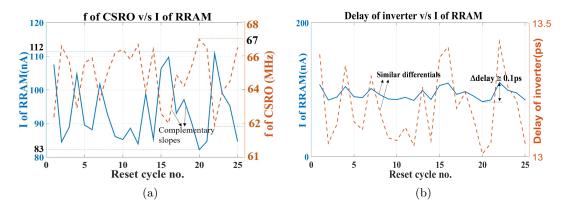

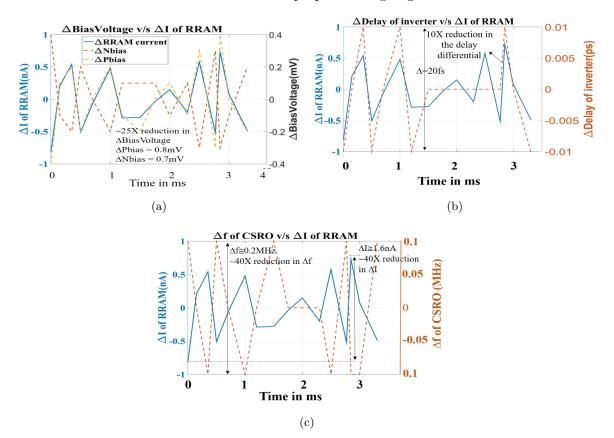

| Figure 5.4 Variations of CSRO parameters (configurability) with RRAM current.     | 65 |

| Figure 5.5 Variations of voltage across NMOS and PMOS with RRAM current.          | 65 |

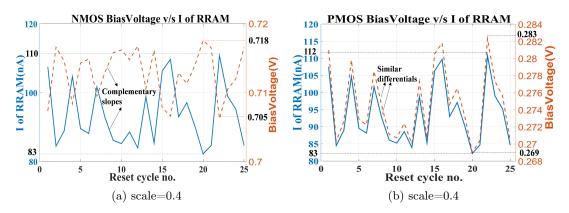

| Figure 5.6 Differential changes due to change in RRAM current with configuration. | 66 |

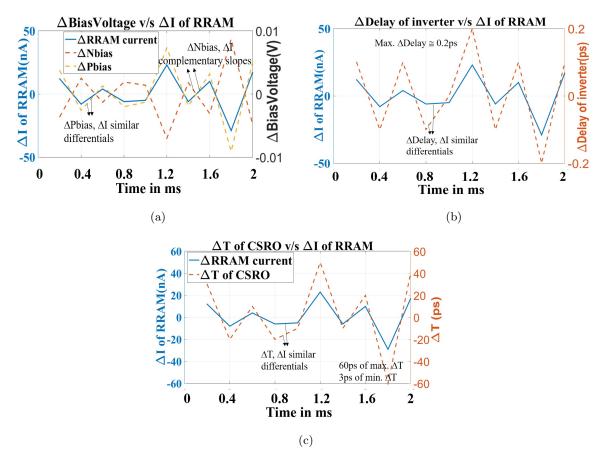

| Figure 5.7 Differential changes due to RTN at $30^{\circ}C$ .                     | 67 |

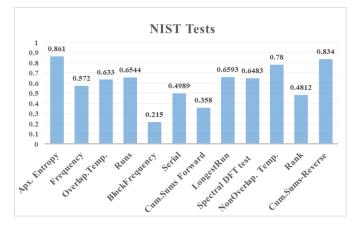

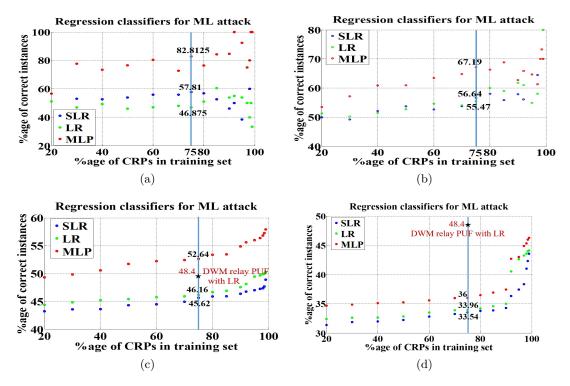

| Figure 5.8 NIST test results on bit stream from 4-bit TRNG.                       | 68 |

| Figure 5.9 Differential change due to RTN at $5^{\circ}$ C.                       | 69 |

| Figure 5.10 NIST tests on 4-bit TRNG within RESET cycle with zero RTN.            | 71 |

| Figure 6.1 CMOS Arbiter PUF.                                                      | 76 |

| Figure 6.2 High level architecture of proposed APUF.                              | 77 |

| Figure 6.3 Conceptual schematic of the proposed APUF.                             | 78 |

| Figure 6.4 Configurability for the number of stages in proposed APUF.             | 81 |

| Figure 6.5 Race firing and sense margin development at differential SA.           | 83 |

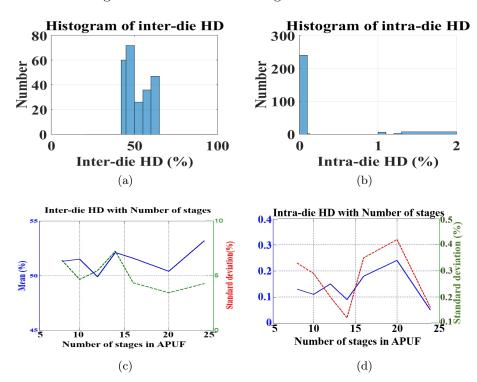

| Figure 6.6 Histogram of the PUF responses such as inter-die HD and intra-die HD.  | 84 |

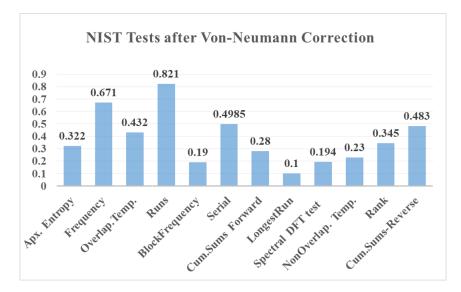

| Figure 6.7 NIST results of eight: (a) 4-stage; and (b) 16-stage APUFs.            | 85 |

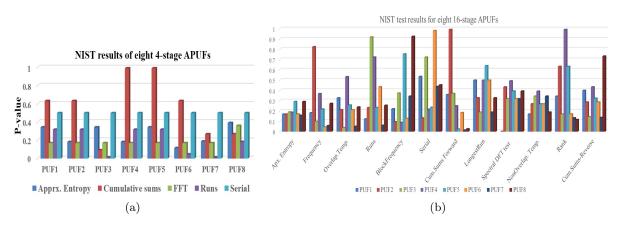

| Figure 6.8 Number of CRPs with and without configurability.                       | 86 |

| Figure 6.9 Performance of regression classifiers on proposed APUF.                | 88 |

| Figure 6.10 Correlation coefficient with number of CRPs.                          | 90 |

| Figure 6.11 RRAM APUF architecture resilient to ML attacks.                       | 91 |

| Figure 6.12 | ML attack on proposed ML resilient architecture. | 92 |

|-------------|--------------------------------------------------|----|

| Figure 6.13 | Sensor nodes and server node in IoT network.     | 94 |

### ABSTRACT

With CMOS technology scaling reaching its limitations rigorous research of alternate and competent technologies is paramount to push the boundaries of computing. Spintronic and resistive memories have proven to be effective alternatives in terms of area, power and performance to CMOS because of their non-volatility, ability for logic computing and easy integration with CMOS. However, deeper investigations to understand their physical phenomenon and improve their properties such as writability, stability, reliability, endurance, uniformity with minimal device-device variations is necessary for deployment as memories in commercial applications. Application of these technologies beyond memory and logic are investigated in this thesis i.e. for security of integrated circuits and systems and special purpose memories. We proposed a spintonic based special purpose memory for search applications, present design analysis and techniques to improve the performance for larger word lengths up to 256 bits. Salient characteristics of RRAM is studied and exploited in the design of widely accepted hardware security primitives such as Physically Unclonable Function (PUF) and True Random Number Generators (TRNG). Vulnerability of these circuits to adversary attacks and countermeasures are proposed. Proposed PUF can be implemented within 1T-1R conventional memory architecture which offers area advantages compared to RRAM memory and cross bar array PUFs with huge number of challenge response pairs. Potential application of proposed strong arbiter PUF in the Internet of things is proposed and performance is evaluated theoretically with valid assumptions on the maturity of RRAM technology. Proposed TRNG effectively utilizes the random telegraph noise in RRAM current to generate random bit stream. TRNG is evaluated for sufficient randomness in the random bit stream generated. Vulnerability and countermeasures to adversary attacks are also studied. Finally, in thesis we investigated and extended the application of emerging non-volatile memory technologies for search and security in integrated circuits and systems.

# **CHAPTER 1 : INTRODUCTION**

CMOS technology has been workhorse of design in electronics industry because of electric field controlled operation and lower power consumption of MOSFETS compared to other semiconductor technologies such as Bipolar Junction Transistors. Constant scaling of CMOS devices has been enabling the semiconductor industry to meet the consumer electronics product market requirements such as smaller size (miniaturization), light weight battery powered gadgets with enormous computing capability comparable to a desktop [4]. Scaling of CMOS itself is driven by Moore's law. Moore's law has been guiding semiconductor industry to push the boundaries of technology and process since past several decades. However, the scaling dictated by Moore's law is exponential and doesn't continue indefinitely due to several technology challenges and practical limitations [5] such as precision in photo lithographic process, electrical limitations due to Short Channel Effects (SCA), Narrow Channel Effects (NCA) and the ever changing needs by applications (memory intensive and longer standby times). This chapter presents a review of technology scaling challenges and the technologies beyond CMOS in exploration to address these challenges.

#### 1.1 Conventional CMOS and Design Challenges

CMOS technology is benefited by the advantages of scaling in terms of performance, dynamic power and area. However, scaling below 65nm leakage power increases exponentially offering new

<sup>&</sup>lt;sup>1</sup>Portions of this chapter were reprinted from Ghosh, Swaroop. "Spintronics and Security: Prospects, Vulnerabilities, Attack Models, and Preventions." Proceedings of the IEEE 104, no. 10 (2016): 1864-1893. Permission is included in Appendix A.

challenges to continuous scaling [6]. Increase in the leakage power due to the effects of short and narrow channel which were not considered earlier become prominent in the feature size below 65nm. Power consumption of a CMOS chip has two major components namely, dynamic and leakage power. Total power in a CMOS circuit is modeled as  $P = fCV^2 + VI_{leakage}$ ; f is the frequency of operation, C is the total load capacitance, V is operating voltage and  $I_{leakage}$  is the leakage current in the active/standby mode.

In addition to Drain Induced Barrier Lowering (DIBL) and increased subthreshold leakage contributing to high leakage power, effects of Hot Carrier Injection (HCI), Time Dependent Dielectric Breakdown (TDDB) and Bias temperature Instability (BTI), high power density, increased soft error probability with scaling of threshold voltage [7],mobility degradation [8] and process variations add the reliability concerns with submicron scaling.

Aside from limitations of CMOS for logics and circuit design CMOS based memories such as Dynamic RAM (DRAM), Static RAM(SRAM) and flash memories have shown several design challenges with technology scaling [9, 10, 11, 12, 13]. Also, finding a single memory technology that caters to the requirements at all levels of memory hierarchy with logic is another motivation to research emerging memory technologies. Such memory is termed as 'Universal memory' technology [14, 15, 16]. STT-RAM and RRAM technology are potential candidates as Universal memory achieved by tuning the characteristics of memory device [15, 17].

With the raising concerns for security the metrics of power, performance and area do not suffice in the IC design for modern applications. In the era of Internet besides sophisticated IC manufacturing process security at the root level in the IC manufacturing and supply chain becomes essential [18]. Various CMOS based security primitives and countermeasures have been proposed in the literature [19]. However, CMOS based designs have demonstrated vulnerability to adversary attacks such as side channel attacks[20, 21] and offer limited features for the design of security primitive. This necessitates the search of emerging technologies for hardware security applications [18].

## 1.2 Emerging Technologies - Beyond CMOS for Memory and Computing

In the wake of ever changing computing needs by modern applications [17] and to overcome the challenges of CMOS technology scaling several non-classical CMOS devices, memory devices and logic devices have been researched [22, 23]. Non-classical CMOS devices include ultra-thin body SOI transistor, band-engineered transistors, FinFET, vertical transistors, high-k/metal gate transistors, ballistic channel transistors [24], Double-gate transistor, and so on.Non Volatile Memory (NVM) technologies explored for both storage and computing within memory include memristor, spintric based memories such as spin valve, Magnetic RAM (MRAM), Spin-Transfer Torque RAM (STT-RAM) using Magnetic Tunnel Junction (MTJ) device and Domain Wall Memory (DWM), Restive Random Access Memory (RRAM) and variants, Phase Charge Memory (PCM), Nano ElectroMechanical (NEM) devices, and so on. MTJ and RRAM based memory cells have proven to be competent and potential replacement candidates to DRAM and SRAM currently used in computing devices [17]. Further, spintronic and RRAM devices can be fabricated in the via space of CMOS layout with fewer additional mask layers in the manufacturing process. Therefore, they are compatible with existing CMOS fabrication process technology.

Advantages of emerging NVM technologies have been exploited for various circuit and architecture design.Computing within memory is an important development with NVM solving the problem of processor-memory communication delay. Adder circuit within memory is proposed and implemented [25, 26]. Neuromorphic, quantum computing and bio-inspired computing have also been realized with emerging NVM technologies. memristor and spintronic memorie are widely researched for logic and circuit design applications.

Memristor was discovered in 1971 and is perceived as a fourth fundamental circuit element, resistor with memory. Resistance of a memristor depends on the history of the voltage applied across its terminals.Since its discovery application of memristor for stateful logic, Boolean logic [27],[28] and implicative circuits has been extensively researched [29].Memristor based multi-state registers, non-volatile processors, memristor based neuron circuit, cross bar array circuits and neuromorphic computing have been proposed [30, 31]. memristor only logic which enables computing within cross bar memory array has been proposed in [32] [33]. These cross bar array based and memristor only based logics lack the sharing of inputs between multiple gate limiting fanout and do not implement XOR/XNOr gates. MAD memristor logic gates [34] implement XOR logic gates and can share the inputs between multiple gates.

Spintronic is another emerging technology extensively researched for its applications for computing [35]. Property of shift in DWM [36] and spin current based switching of MTJ have been greatly exploited for computing. In-memory computing [37], associative computing [38, 39], Boolean logic computing [40], reconfigurable logic based on shift based look-up table [36], big-data computing [41], spin-neurons for non-boolean computation [42], STT-RAM based processor for general purpose [43], MTJ based non-volatile logic computing [44, 45], realization of non-volatile flip flop like storage elements [46, 47, 48], crossbar computing [49, 42, 28] are worth mentioning in this context. Emerging technologies have also demonstrated enormous potential in various areas of computing. Vision of this work is to explore and extend the application of emerging Non-Volatile Memory (NVM) technologies. We researched the application of spintronics based memories such as MTJ and DWM, and resistive memory such as hafnium oxide  $(HfO_x)$  based RRAM for associative memory and hardware security applications.

## 1.3 Hardware Security

In today's highly integrated circuits and systems, satisfying the functionality, frequency, and Thermal Design Power (TDP) requirements are not adequate [19]. It is essential to ensure the security and privacy of the overall system. The contemporary business model involves the *untrusted* third party in every step of Integrated Circuit (IC) manufacturing process- from design, synthesis, layout, and all the way to fabrication and packaging. The trend of integrating third-party Intellectual Property (IP) blocks into the design makes the problem more complex. Broadly, the attacks on hardware could fall under:

- *Malicious modifications* : The hardware Trojans can be inserted in the ICs which cause malfunctioning of IC or leak information for instance.

- *Cloning/Fake IC* : The adversary can imitate the design, fabricate and sell at lower price which lower the market of the genuine IC.

- *Hacking/Eavesdropping* : The adversary eavesdrops the communication channel to crack the secret key for malicious intent.

- *Side Channel Attacks* : Side channels, e.g., current, voltage are monitored to extract the secret information from the device.

- *Reverse Engineering* : IC design details are revealed by peeling off the layers of fabrication process using chemicals and mechanical methods, which reveals the secret design information.

- *IC Recycling* : Unused or barely use ICs are recycled from older PCBs and sold for reduced price compared to genuine new ICs from original manufacturer.

Furthermore, it is worth mentioning that security, trust, and authentication of an electronic system are intertwined with each other. Such an untrusted design environment results in infected hardware that in turn necessitates the authentication of the ICs in the end product. Hardware security primitives such as hardware encryption engine, Physically Unclonable Functions (PUFs), True Random Number Generators (TRNGs), recycling sensors, tamper detection sensors are promising to provide security against the threats such as Hardware Trojan insertion, IC recycling, chip cloning, data snooping and side channel attacks. Furthermore, these primitives are energy-efficient and incurs low area/design overhead. Table 1.1 summarizes the key requirements of hardware security primitives along with the respective features of emerging NVM technologies.

| Table 1.1: Properties offered by emerging NVM technologies   | 1, 2].Hardware security primitives, |

|--------------------------------------------------------------|-------------------------------------|

| key requirements and properties offered by emerging NVM tech | nologies.                           |

| Security Primitive | Key Requirements          | Features Offered by NVM technologies |  |

|--------------------|---------------------------|--------------------------------------|--|

|                    | high process variation    | RRAM device to device                |  |

| PUF                | nonlinearity              | switching variations                 |  |

|                    | nonnneartty               | Nonlinearity in switching resistance |  |

|                    |                           | Noise sensitivity of magnetization   |  |

| TRNG               | High entropy              | stochastic dynamics                  |  |

|                    |                           | Telegraph noise in RRAM current      |  |

| Encryption         | unique and unpredictable  | Unique key generation from           |  |

| Encryption         | identification key        | RRAM device-device variations        |  |

| Recycling Sensor   | Low process variation     | DW nucleation                        |  |

| Recyching Sensor   | High sensitivity to usage | Cycles of endurance in RRAM and MTJ  |  |

It should be noted that CMOS based circuits in security applications have demonstrated the problems of area and power overhead. Further, they are sensitive to environmental fluctuations and have limited randomness and entropy offered by the silicon substrate. The emerging technologies such as magnetic, spintronic and resistive memories have shown promises in bringing an abundance of entropy and physical randomness. Unique identification keys can be generated by extracting spatial, temporal randomness and inherent entropy in a magnetic system and switching variations using custom-designed harvesting circuits. Furthermore, these technologies have also demonstrated robustness, speed and orders of magnitude energy-efficiency compared to their CMOS counterparts [2, 50, 51]. In this work, salient features of  $HfO_x$  based RRAM are exploited for hardware security applications.

Contributions of this dissertation to the literature are described below.

- Design of an associative memory cell termed Ternary Content Addressable Memory (TCAM) cell is proposed. Design selections and analysis including the selection of NMOS devices and MTJ characteristics, effect of PVT variations are presented. Process variation tolerance techniques for reliable search in longer words are also proposed [52, 53].

- 2. We propose an Arbiter Physically Unclonable Function (APUF) using cycle-to-cycle switching variations in resistance states of RRAM. The proposed APUF is realized within one-Transistor one-Resistor (1T-1R) conventional memory architecture with minimal invasive design changes. Proposed APUF is studied for its vulnerability to adversary attacks and design technique to improve the resiliency to machine learning based model building attacks is proposed.

- 3. Random Telegraph Noise (RTN) in the RRAM is exploited for designing a True random Number Generator(TRNG) [54]. Proposed TRNG uses 1T-1R RRAM cell in the bias network of Current Starved Ring Oscillator (CSRO) producing temporal variations in the frequency of CSRO. The CSRO oscillations are sampled to generate true random numbers. In addition,

proposed TRNG is configurable which can be utilized to recover from potential adversary attacks.

## 1.4 Organization of Thesis

Rest of this thesis is organized as follows.

Chapter 2 discusses the basics of spintronic technology and the spintronic memory device MTJ explored in this thesis.

Chapter 3 presents the fundamentals of RRAM memory and its functional operation. Specific features of RRAM exploited in hardware security applications and the details of RRAM device models used for work are also discussed.

Chapter 4 demonstrates an application of MTJ in searchable memory termed as 6T-2MTJ TCAM. Design analysis and techniques to improve the sense margin of proposed TCAM cell are presented.

Chapter 5 presents the realization hardware security primitive TRNG using RRAM memory in the CSRO.

Chapter 6 illustrates another security primitive APUF exploiting the switching variations of RRAM. The chapter Discusses the feature of configurability and architectural changes to leverage proposed APUF to be machine learning attack resilient. Also presents potential application of APUF architecture for data attestation in the Internet of Things (IoTs).

Chapter 7 presents the conclusions and potential future works to extend and enhance the application of NVMs to in the proposed areas.

# **CHAPTER 2 : MAGNETIC TUNNEL JUNCTION DEVICE**

This chapter discusses the basics of spintronic technology, device structure, physics and operation of spintronic based Magnetic Tunnel Junction (MTJ) memory device.

## 2.1 Introduction

Spintronic technology is based on magnetic properties of electron where conventional CMOS computing is based on charge of an electron. Basis of spin devices is magnet. Direction of spin associated with electron is used to encode the logic states for storage and computation. Spintronic devices retain the state due to stable magnetisation direction under the influence of no external field. This property makes the memory based on spintronic non-volatile.

Spintronic devices are realised using magnetic properties of ferromagnetic materials. Three extensively researched spintronic memories are spin valve, Spin Transfer Torque Magnetic Random-Access Memory (STTRAM) and Magnetic Random Access Memory (MRAM). Spintronic device consist of two ferromagnetic layers separated by a spacer layer [55]. The devices differentiate by type of the spacer layer in the device structure and their switching mechanism. Non-magnetic spacer layer between ferromagnetic layers create the effect of magnetoresistance termed as Giant Magnetoresistance (GMR). GMR depends on the relative magnetization orientation of the two ferromagnetic layers and the spacer material used between them (minimum of 3%-8% to maximum

<sup>&</sup>lt;sup>2</sup>Portions of this chapter were reprinted from Ghosh, Swaroop. "Spintronics and Security: Prospects, Vulnerabilities, Attack Models, and Preventions." Proceedings of the IEEE 104.10 (2016): 1864-1893. Permission is included in Appendix A.

of 50%). GMR determines the ratio of the currents in low resistance state to high resistance state through spin device. Higher GMR is required for better readability of a spin device. A very thin layer of insulating, dielectric material can increase the GMR to more than 100%. The new magnetoresistance is termed as Tunnel Magneto Resistance (TMR). Details of the spintronic devices used in this thesis are explained the coming sections.

This chapter presents the details of MTJ as a spintronic device and operation. Also presents an overview of application of MTJ in memory and computing.

#### 2.2 Magnetic Tunnel Junction

MTJ contains a free and a pinned magnetic layer separated by a thin tunneling oxide layer (a schematic is shown in Fig. 2.1a). The equivalent resistance of the MTJ stack is high (low) if the free layer magnetic orientation is anti-parallel (parallel) to that of the fixed layer. Conventionally, the high equivalent resistance is considered as data '1' and low equivalent resistance is considered as data '0'. The magnetic orientation of the MTJ free layer can be changed from Parallel (P) to Anti-Parallel (AP) (or vice versa) to that of fixed layer by either magnetic field-driven or currentdriven techniques. The magnetic field-driven MTJ is the basis for MRAM technology [56] which is promising due to high-density, low standby power, and high-speed operation. On the other hand, STTRAM [57] is an energy-efficient variant of MRAM where the switching of magnetization is based on spin-polarized current.

In MRAM, MTJ lies between a pair of write lines named digit-line and bit-line (Fig. 2.1a). These lines are arranged at right angles to each other, parallel to the cell plane, and one above and one below the cell. An induced magnetic field is created by passing current through the lines.

Figure 2.1: Schematic of (a) MRAM; (b) STTRAM [1].

The induced magnetic field exerts a torque on the free layer magnetic orientation causing it to flip. Therefore, the direction of write current determines the polarity of the torque and thus determines writing '0' or '1'. The isolation (access) transistor is kept off during write. However, during read, the access transistor is turned on, and a voltage is applied across the cell to sense the equivalent resistance. It should be noted that the read current is unidirectional. Other variant of MRAM is thermally Assisted MRAM (TA-MRAM). In TA-MRAM writing by a magnetic field pulse is assisted by temporary heating of the cell produced by tunneling current through the selected cell. TA-MRAM writing consumes less power compared that in filed-written MRAM. In MRAM, depending on the direction of magnetization of reference w.r.t. the plane in ferromagnetic electrodes MTJ devices are classified as In-plane Magnetic Anisotropy (IMA) and Perpendicular Magnetic Anisotropy (PMA) devices. PMA MTJ devices are preferred in the applications requiring longer retention and stability of bit information. It's noteworthy that it is difficult to grow Perpendicularto-plane magnetized materials than in-plane magnetized materials [58]. MRAM devices offer the advantages of reliability, robustness, endurance and resistance to external radiation which are attractive in space and automotive applications [58]. First commercial MRAM chips of 1, 4, 8 and 16Mbit were developed by Everspin Technologies in 2006 followed by Thermally Assisted MRAM (TA-MRAM) chips by Crocus Technology in 2011. Latest reported maturity of MTJ fabrication technology has demonstrated TMR of upto 600% at room temperature with MgO tunnel barrier layer. TMR of 190% has been achieved with flexible MgO-barrier MTJs can be bent to various radii upto 5mm. These flexible MTJs find potential application in high performance and flexible electronics [59].

In STTRAM, each cell has one MTJ and one access transistor in series. The write operation is done by turning the access transistor ON and injecting current from the source-line to the bit-line or vice versa (Fig. 2.1b). STT-writing improves the selectivity and better scalability of cell size compared to MRAM devices. Of-plane STTRAMs require less write current than that in in-plane STTRAMs but with a trade-ff of lesser retention than in-plane counterparts. Thermal assistance can also be employed similar to MRAM. In STTRAM Joule heating produced by the write current through tunnel barrier in MTJ assists the switching of magnetization[58] . However, the read operation of STTRAM is similar to that of MRAM. The dynamics of free layer magnetization for both MRAM and STTRAM is governed by LLG equation [60, 61, 62] as follows:

$$\frac{\partial \vec{m}}{\partial t} = -\gamma \vec{m} \times (H_{eff} + \underbrace{h_{st}}_{stochastic}) - \alpha \gamma \vec{m} \times [\vec{m} \times (H_{eff} + \underbrace{h_{st}}_{stochastic})] \\

+ \underbrace{\frac{I_s \hbar G(\psi)}{2e} \vec{m} \times (\vec{m} \times \vec{e_p})}_{STT}$$

(2.1)

where,  $\vec{m}$  is unit vector representing local magnetic moment,  $\alpha$  represents the Gilbert's damping parameter,  $\gamma$  is gyromagnetic ratio,  $h_{st}$  is field due to stochastic noise,  $I_s$  is spin current,  $G(\psi)$  is the transmission co-efficient,  $\hbar$  is reduced Plank's constant, e is charge of electron and  $\vec{e_p}$  is the unit vector along fixed layer magnetization. In the above expression,  $\overrightarrow{H_{eff}}$  is effective field given by,  $\overrightarrow{H_{eff}} = \overrightarrow{H_a} + \overrightarrow{H_k} + \overrightarrow{H_d} + \overrightarrow{H_{ex}}$ , where  $\overrightarrow{H_a}$  is applied field,  $\overrightarrow{H_k}$  is anisotropy field,  $\overrightarrow{H_d}$  is demagnetization field, and  $\overrightarrow{H_{ex}}$  is exchange field. The retention time of the MTJ, i.e., the time between which the free layer magnetization tends to flip is given by  $T_{ret} = t_0 e^{\Delta}$ , where  $t_0$  attempt time (~1ns), stability factor,  $\Delta = \frac{K_u V}{k_B T}$  where  $K_u$  is the magneto-crystalline anisotropy, V is the volume of the MTJ free layer, T is the operating temperature and  $k_B$  is the Boltzmann constant. By injecting a current (I) through the MTJ having a critical current of  $I_{co}$  (where the direction of the current flips the bit), the retention time can be altered as follows [63]:

$$\Delta = \frac{K_u V}{k_B T} \left(1 - \frac{I}{I_{co}}\right) \tag{2.2}$$

The equations 2.1 and 2.2 are crucial to understanding the factors that can influence the magnetization dynamics and retention time of MTJ.

Application of STTRAM cell is investigated in this thesis. The resistance of MTJ is high when PL and FL are in antiparallel configuration whereas the resistance is low when they are parallel to each other. The value written to the STTRAM bit depends on the direction and the strength of the charge current. Minimum current required to flip the state of the MTJ in a STTRAM bit is called critical current. Bit '1' is written by passing charge current from pinned layer to fixed layer (Fig. 2.1b) and bit '0' is written by the current opposite direction [64]. Tunnel Magneto Resistance (TMR) is the ratio which determines the ratio of electrical resistances of the MTJ structure in parallel and antiparallel polarization states of FL relative to PL magnetization. If  $R_H$  ( $R_L$ ) is the MTJ resistances in antiparallel (parallel) states, the TMR is defined as  $TMR = \frac{(R_H - R_L)}{R_L}$ . In this thesis, MTJ and the transistors in series together is referred as STTRAM while MTJ referred to the MTJ device in the memory cell. Table-2.1 summarizes the parameters of the MTJ device used in this work.

| Parameter                           | Value                    |

|-------------------------------------|--------------------------|

| Saturation Magnetization $(M_s)$    | 800 Oe                   |

| Critical current density $(J_{co})$ | $3.2 \mathrm{MA/c} m^2$  |

| Uniaxial Anisotropy $(K_u)$         | $150150~\mathrm{erg/cc}$ |

| Damping Constant                    | 0.007                    |

| TMR                                 | 125%                     |

| Length and Width                    | 60nmX60nm                |

| Critical Current $(I_{co})$         | 115µA                    |

Table 2.1: Parameters of MTJ used

#### 2.3 MTJ for Memory and Computing

Advent of TMR and STT write mechanisms has enabled application of MTJ device based STTRAM to be potential universal memories. Researchers ventured to deploy spintronic devices in logic computing such as in-memory Boolean computing [65], write spin-current based logic computing [66], majority gates [67, 68] and in neural networks [69]. This section presents a review of application of MTJ in computing.

Logic gates realization proposed in [66] is dependent on the switching critical current of MTJ. Operation of NAND gate can be explained as follows. Inputs to the logic gate are stored in to parallel MTJs in terms of MTJ resistance states. MTJ storing evaluated output is connected in series with the input MTJ network. Output MTJ is initialised to a default low resistance state  $(R_L)$ . When atleast one of the input MTJs are at low resistance state  $R_L$  net current flowing through the output MTJ switched it to  $R_H$ . This evaluates the output of NAND gate to logic state '1'  $(R_H)$ . When the input MTJs are in  $R_H$  state net current through the output MTJ is less than the critical current and state of output MTJ evaluates to logic '0'  $(R_L)$ . Similar technique is extended to realise NOR and inverter universal gates. All Spin Logic (ASL) is another technique of realising logic gates with spintronic based devices.

Proposal of ASL in [65] uses a spin channel between input and output bits unlike in [66] where the charge current was used to evaluate the output. The device used in ASL realization is termed as asl-device. In ASL device input and output magnets are connected and interact via a spin-coherent channel. Spin coherent channel composes of material with high spin flip length, thus conserving the spin of in the channel to manipulate the output bit from the state of input bit. with information storage, communications and evaluation in spin domain ASL is faster, energy and area efficient designs for logic implementation. Also, ASL satisfies the essential characteristics for logic realization and application [65]. Functional extension of ASL gates to realise majority gates, adders, multipliers and complex logic function implementation with majority gates is proposed in [67].

A new type of spin logic device is proposed in [68] called spin torque majority gates (STMG) uses complete spin domain to for logic evaluation. STMG device consists of nanopillars and magnetization of common output free layer is switched by the net current through these nanopillars. Structure is similar to 3 terminal STTRAM. STMG can implement various complex logic functions in terms of majority gates similar to implementation proposed in [67]. However, STMG suffer from low switching speeds and high switching energy compared to ASL majority gates proposed.

Further, application of spintronic devices is explored in neural networks implementation. Deep Neural Networks (DNN) use a large number of hidden layers. DNNs find numerous applications in the fields requiring to learn complex data patterns and data prediction. Spike Neural Networks use bio-inspired design to mimic the functioning of human brain. Spike Timing Dependent synaptic Plasticity (STDP) is one of the desired properties in the synapse connecting the neurons in brain for learning. Programmability and stochastic switching of Spintronic devices by voltage pulse is used to implement synaptic plasticity [69]. MTJ along with heavy metal layer to switch MTJ by spin-Hall effect induced by the current through heavy metal structure provides separate path for programming and spike transmission in neural networks. There are numerous publications exploring the application of spintronic devices such as MTJ and DWM in neuromorphic computing and neural network implementation [70, 71, 72, 73, 74, 42]. Exhaustive discussions on this topic is out of scope of this thesis.

#### 2.4 Summary

Basics of spintronic technology and devices researched in this thesis are discussed in this chapter. Spintronic devices are attractive alternatives to CMOS memory because of their nonvolatility, scalability to sub-nm technology nodes, smaller area, low power consumption and compatibility with CMOS process technology. Further, features of spintronic devices can be exploited to realize logic and special purpose memories competent with their CMOS counterparts. Spintronic memories are potential candidates as universal memories because of their versatile and flexible characteristics with selection of materials in the stack and feature size. Extensive research and innovation is geared towards commercializing spintronic technology in computing.

## CHAPTER 3 : RESISTIVE RANDOM ACCESS MEMORY<sup>1</sup>

#### 3.1 Introduction

RRAM is a disruptive memory device for future NVM applications and a strong memory candidate to challenge flash memory currently used in commercial applications. RRAM based memory cell size of  $6F^2$  is achieved (transistor selector device) and  $4F^2$  cell size is possible with diode as memory selector device in cross-bar array structure. This offers high density memory competitive to DRAM and SRAM. It is designed by sandwiching an oxide material between two metal electrodes i.e., Top Electrode (TE) and Bottom Electrode (BE). RRAM resistive switching is primarily due to the mechanism of oxide breakdown and reoxidation which modifies a Conduction Filament (CF) in the oxide. Fig. 3.1 shows the voltage and current transfer characteristics during the SET and RESET process cycles. The minimum resistance of the filament depends on the current compliance used in the process of forming. The two states of the RRAM in low resistance and high resistance are termed as Low Resistance State (LRS) and High Resistance State (HRS). We have used the expressions from [75, 76, 77] as the basis to model the resistance of Hafnium oxide based RRAM at different voltages applied at the top electrode. The resistance switching of RRAM involves three elementary processes such as formation, SET and RESET.

<sup>&</sup>lt;sup>3</sup>Portions of this chapter was reprinted from 'Govindaraj, R., & Ghosh, S. (2016, October). A strong arbiter PUF using resistive RAM within 1T-1R memory architecture. In Computer Design (ICCD), 2016 IEEE 34th International Conference on (pp. 141-148). IEEE.', 'R. Govindaraj, S. Ghosh and S. Katkoori, "CSRO-Based Reconfigurable True Random Number Generator Using RRAM," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems.doi: 10.1109/TVLSI.2018.2823274.' and 'Puglisi, Francesco Maria, Paolo Pavan, Andrea Padovani, and Luca Larcher. "A compact model of hafnium-oxide-based resistive random access memory." In Proceedings of 2013 International Conference on IC Design & Technology (ICICDT). 2013.', with permission from IEEE Permission is included in Appendix A.

This chapter presents the overview of RRAM operation, device types and details of salient features of RRAM exploited in hardware security applications.

## 3.2 Types of RRAM

RRAM devices are characterized by their switching mechanism, polarity of voltage across electrodes for switching and the materials used in oxide sandwitch and electrodes. Based on polarity of SET/RESET switching voltages RRAM is categorized as unipolar and bipolar. In unipolar type RRAMs switching depends only on the magnitude of the applied voltage across electrodes and independent of the polarity. Switching is interpreted to be due to Joule heating effect in the oxide layer. In bipolar RRAM SET/RESET process is dependent on the polarity of the applied switching voltage between top and bottom electrodes. The switching is due to electrochemical migration of ions and redox reactions which depend on the polarity of operating voltage. Switching model of  $HfO_x$ based bipolar RRAM is used for our research. Details of switching mechanism is discussed below. The forming voltage is applied across the electrodes to create an electric field in the oxide material.

Figure 3.1: RRAM memory device and resistance transfer characteristics.

Oxygen atoms are knocked out of oxide material forming oxygen vacancies under the influence of high electric field, typically as high as 10MV/cm (Fig. 3.2). The conduction through the CF is primarily due to the transportation mechanism of electrons in these oxygen vacancies termed as Trap Assisted Tunneling (TAT). After the process of forming, the resistance of the RRAM is at the lowest (LRS). The resistance in LRS depends on the current compliance as shown in characteristic plot in Fig. 3.1. The SET process is same as forming except that only a part of CF is recovered as compared to forming process (Fig. 3.2). Also, SET is performed following a RESET process and SET voltage depends linearly on the RESET voltage [75, 78]. The process of setting state to HRS state is called RESET process. During RESET the oxygen ions drifted to the anode return to the bulk to combine with the oxygen vacancies or oxidize the metal precipitates. The rate of reoxidation depends on the magnitude of the RESET voltage [75].

Figure 3.2: Forming, SET and RESET switching mechanism in RRAM.

RRAM is further classified as anion and cation type based on resistive switching mechanism. SET process in anion type RRAM is due to formation of oxygen vacancies in the oxide layer and RESET process is due to recombination of oxygen ions back in the oxide layer. Oxygen active electrodes or thin films oxygen reservoirs are required anion type RRAM. Performance and compatibility with CMOS fabrication technology are primary reasons for wide acceptance high-k metal-oxide materials such as  $HfO_x, TaO_x, AlO_x$  in the switching layer of anion type RRAM. Switching process in cation type RRAM is dominated by redox reaction and migration of metal ions, formation of metallic filaments in switching layer. Conductive Bridge RAM (CBRAM) is an example of cation type RRAM. CBRAM devices use Ag or Cu oxidized electrode and an inert electrode. Switching mechanism in CBRAM can be explained as follows. First, Cu atoms oxidize and  $Cu^+$  ions from copper electrode are injected into dielectric layer, then applied negative bias attracts the  $Cu^+$  ions to the bottom electrode to establish a conductive path (low resistance state). On application of positive bias voltage electrochemical reaction due to Joule heating ruptures the conductive path at a maximum power dissipation point (high resistance state). High  $\frac{R_{ON}}{R_{OFF}}$  ratio, longer retention (10<sup>9</sup>) and small operating voltages are attractive features of CBRAM [79].

#### 3.3 **RRAM** for Hardware Security

The resistance of the RRAM after SET and RESET follow probability distribution due to defects in the CF and the thermal voltage fluctuations. The variability in the cycle-to-cycle resistance switching which is a source of randomness can be exploited for security applications. RRAM shows the intra-device temporal variations in switching process. HRS and LRS vary cycleto-cycle [75] and the resistance after switching depends on the generation and recombination of oxygen vacancies. This is stochastic process induced by the electric field and the temperature of the oxide under the applied switching voltage [75, 78]. The resistance switching model is based on TiN/Ti/ $HfO_x$ /TiN RRAM device having a physical oxide thickness  $t_{ox}$  of 5nm. Sources of randomness in the RRAM device and models used in this work are discussed in this section.

$$R_{set} = \rho_{Hf,CF} \times \frac{t_{ox}}{S} \tag{3.1}$$

$$R_{reset} = \rho_{Hf,CF} \times \frac{(t_{ox} - x)}{S} + R_{set} \times (\exp\left\{\frac{x}{k}\right\} - \frac{x}{t_{ox}})$$

(3.2)

$$\frac{dx}{dt} = R_{set} \times C_{xv} \times |V - V_{reset}| \quad ifV > V_{reset}$$

$$\frac{dx}{dt} = 0 \quad otherwise$$

(3.3)

$$I(x,V) = I_0(x) \times \sinh(\frac{V}{V_0})$$

(3.4)

$$I_0(x) = \frac{V_0}{R(x)}$$

(3.5)

$$R(x,T) = R_{set} \times \frac{(t_{ox} - x)}{t_{ox}} + R_{set} \times e^{\frac{x}{k} - 1} \times e^{\frac{E_T}{K_b \times T}}$$

(3.6)

where  $\rho_{Hf,CF}$  is the resistivity of the CF, tox is the hafnium oxide thickness and S is the cross section of the CF.  $\rho_{Hf,CF}$  depends on the current compliance used during forming (Fig.3.1). It is evident that higher current compliance induces a larger CF.  $V_{reset}$  is the function of time and ramp voltage with the peak of 1.3V is applied for RESET.  $C_{xv}$  is the proportionality coefficient.  $V_0$  is experimentally measured quantity.x is the barrier length created by reoxidation of CF by the reset voltage.  $E_r$  is the activation energy,  $K_b$  is Boltzmann constant and T is the temperature of the device.

• *Cycle-to-cycle variation:* We have used the parameters and the equations to model cycle-to-cycle switching variations in RRAM from [75] that are calibrated with experimental data.

Current compliance of 100µA is used for modeling the SET resistance. Eqns. 3.1 to 3.6 are used to model RRAM in Verilog-A. RESET process is performed by negative ramp voltage and the differential barrier length with the voltage modeled by Eqn. 3.3. The current during RESET and SET process is given by Eqn. 3.4. RESET is a thermally activated process. The temperature increases with the electric power and overcomes the activation energy to switch the state of the device. Switching of the device at an applied RESET voltage is probabilistic activity [78, 80] model the variation in the resistance of the RRAM due to defects in the oxide material (Fig. 3.3) we assume Gaussian distribution in the SET resistance of RRAM with the variance of 0.08 [75]. The RESET resistance is calculated using Eqns. 3.4-3.6 by assuming Gaussian distribution of the proportionality coefficient  $C_{xv}$  with variance of 0.034.  $C_{xv}$  models the stochastic variation in the CF rupturing process due to recombination of oxygen vacancies with the ions [75, 81] from cycle-to-cycle. Due to exponential dependence of RESET resistance on the barrier length HRS exhibits lognormal distribution characteristics as shown in Fig. 3.3.

Figure 3.3: LRS and HRS distribution of RRAM. Defects in the CF, cumulative probability distribution plot from [75] and simulated data.

• Random Telegraph Noise: Conduction in the RRAM is explained by TAT of electrons in CF. Due to random distribution in the TAT supporting defects, the current though the RRAM shows stochastic variations with time. The phenomenon responsible for RTN is explained by the researchers [82, 76, 83] as charging and discharging of the traps at or close to the surface of the CF. Also, the frequency of trap charging increases with the bias voltage (voltage across RRAM) and temperature due to local Joule heating of CF. The trapping/emission time of the defects near the CF junction can be modeled as lognormal distribution [82, 83]. RTN results in current fluctuations through the RRAM with time. However, the relation of the trapping/emission times with the current fluctuation is still unclear and is determined to be randomly distributed. Variation of RTN current directly related to the fluctuations of current through RRAM [3]. Essentially, RTN is a multi-level low frequency noise in the RRAM of kHz range. RTN can be characterized by Factorial Hidden Markov Model (FHMM) [84] by superposing the multiple two-level RTNs. However, this doesn't provide a deterministic circuit model that could be adapted for circuit analysis. RTN being a truly random process in RRAM leading to read current fluctuations, exhibits no deterministic behavior which could be modeled without direct access to RRAM. Modeling RTN as normal distribution component in RRAM current is the simplistic model for circuit analysis. It should also be noted that the cycle-to-cycle switching parameter variations and RTN are uncorrelated but concurrent in nature [76].

In this work, multi-level RTN in HRS state (RESET) is modeled as variable current source  $(I_{RTN}$  through RRAM with 20%-30% variation in the steady current in HRS state by fitting in normal distribution curve shown in Fig. 3.4 [76, 83, 3]. This RTN model follows the RTN current measurements in [3]. The frequency of current fluctuation is affected by the temper-

Figure 3.4: RTN current distribution in HRS state of RRAM based on measurement data [3].  $I_{RTN}$  with the frequency of 5kHz is shown in the inset.

ature which is due to longer trapping and emission periods of electron at lower temperature compared to those at higher temperatures [83].

### 3.4 Summary

This chapter presented the basics of RRAM technology, types of RRAM devices. Also, variations in device characteristics that are prominent for application in hardware security are discussed. RRAM is a viable component compatible with CMOS fabrication technology and competent with CMOS DRAM in terms speed and area. However, to make RRAM practical for memory applications stability and uniformity in the switching characteristics for performance need to be improved. Phenomenon of RTN and formation of traps in the oxide layer responsible for RTN need to be completely understood and modeled accurately for study in hardware security applications.

# CHAPTER 4 : 6T-2MTJ TERNARY CAM<sup>2</sup>

#### 4.1 Introduction

Content Addressable Memory (CAM) finds numerous applications in pattern matching, internet data processing, packet forwarding, tag bits storage in processor cache, and as associative memory. The special functionality of the content search in CAM requires a comparison circuitry integrated with the memory cell [85]. The comparator in addition to a memory element adds area and power overhead in CAMs. The need to store and match 'don't care' requires two storage bits which further worsens the area overhead. CMOS CAM is power hungry due to power consumed in Match Line (ML), search line and leakage of the bit cell. In nanometer technologies leakage power constitutes a major fraction of the total power consumed in CAM memory [86]. Non-volatile technologies which are more area efficient than a SRAM and also can provide zero leakage are attractive in such a scenario [85, 87]. Area efficiency and, non-volatility of STTRAM-based ternary CAM is very useful for on-chip CAM applications. Numerous works have demonstrated the realization of CAM using non-volatile memory technologies like memristor [88],nano-electro-mechanical switch [89], Resistive RAM (ReRAM) [90] and spintronic elements such as Domain Wall Memory (DWM), Magnetic Tunnel Junctions (MTJ) and Spin-Torque-Transfer RAM (STTRAM) [91, 92, 93, 94]. Memristor-based NOR TCAM [88] uses a voltage divider network formed by the memristors to enable the discharging

<sup>&</sup>lt;sup>4</sup>Portions of this chapter were reprinted from Govindaraj, R., & Ghosh, S. (2015, July). Design and analysis of 6-T 2-MTJ ternary content addressable memory. In Low Power Electronics and Design (ISLPED), 2015 IEEE/ACM International Symposium on (pp. 309-314). IEEE. and Govindaraj, R., & Ghosh, S. (2017). Design and Analysis of STTRAM-Based Ternary Content Addressable Memory Cell. ACM Journal on Emerging Technologies in Computing Systems (JETC), 13(4), 52.

Permission is included in Appendix A.

path to discharge the match line depending on match/miss. It incurs higher write delay of up to 800ns which hurts the table update performance in the network routers application. ReRAM-based TCAM [90] employs a special clocked self-referenced sensing scheme which complicates the memory system design due to additional reference ML required. An efficient integration of spintronic device with CMOS technology motivates to employ them in TCAM cell design. Also, the principle of bit storage and writing methodologies are different in memristor and ReRAM compared to spintronic device such as MTJ and DWM. This limits the direct extension of memristive and ReRAM TCAMs to design spintronic TCAMs.

Spintronic CAMs using MTJ and DWM suffer from issues such as larger area, unreliable write operation, high search delay and high power consumption compared to CMOS CAMs [86]. The MTJ based TCAM 4T-2MTJ design [95] is area and power efficient however it employs a technique based proportional total current drawn from the ML by bit cells in word. Further, the circuit uses both NMOS and PMOS transistors. In this technique sense margin (SM) decreases significantly as number of bits increase in the worst case search of single bit miss. So, the design is not scalable beyond a certain word length (till 144 bit is presented).DWM based TCAM [93] uses 12 transistors. Therefore, deployment of non-volatile memory in CAM needs effort to achieve smaller footprint and better performance in terms of search delay, write delay, write power and search power.

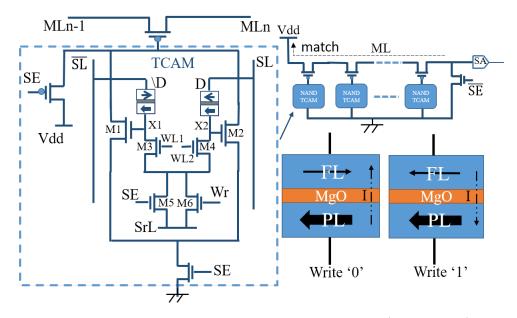

This chapter proposes a NOR type MTJ based TCAM [52] that can support wider CAM words while being tolerant to voltage and temperature variations. However, it is susceptible to poor sense margin due to process variations. Search Enable (SE) modulation to improve the sense margin under inter-die process variation is proposed.Multi- $V_{TH}$  design to improve the sense margin and a NAND type TCAM that exploits the NOR TCAM design are also proposed. The proposed NOR type TCAM employs only 6 transistors and 2 MTJs instead of 16 transistors in CMOS TCAM, and NAND TCAM cell uses 9 transistors and 2 MTJs compared to NAND CMOS TCAM that uses 16 transistors. The following section provides overview of Content Addressable Memory(CAM).

#### 4.2 Content Addressable Memory

CAMs can be divided into two categories depending on the number of states that can be stored in the memory cell namely, Binary CAM (BCAM) and Ternary CAM (TCAM). BCAM stores a binary bit i.e., '0' and '1' whereas TCAM can store three possible values namely, 'don't care' (X), '1', and '0'. CAMs can be further categorized into two topologies namely, NOR and NAND type (Fig. 4.1). The stored bits are compared with the data on the Search Line (SL) and its complement (SL) by XOR operation with the transistor network M1, M2, M3 and M4. To store data in a TCAM cell of NOR type architecture data bit and the complement are stored in two SRAM cells (Fig. 4.1a). Don't care bit can be realized by storing '1' in both SRAM cells i.e.,  $D = \overline{D} = 1$ . In case of match both SL-D and  $\overline{SL} - \overline{D}$  paths are disconnected and the match line remains precharged. In case of miss either of the SL-D or SL - D connect ML to ground which discharges the precharged ML. In a NAND type architecture TCAM cells are connected in series (Fig. 4.1b). Data bit D and D are derived from a single SRAM cell unlike two SRAM cells in NOR type TCAM. The stored bit is masked by using a mask bit (M) in a parallel SRAM cell. In case of match the precharged ML is connected to ground by series TCAM cells of the word by turning the NMOS transistor M1 ON. Storing the mask bit as '1' enables transistor M2 despite match or miss which implements don't care functionality. CMOS TCAM uses two SRAM cells which doubles the area overhead compared to conventional SRAM cell.

Figure 4.1: Conventional CMOS TCAM types. (a) NOR type TCAM; and, (b) Conventional NAND type TCAM. Bit line access transistors are not shown in the figure for simplicity.

#### 4.3 Proposed TCAM Cell

In this Section first we discuss the structure of the proposed TCAM. Next we present qualitative analysis and describe read, write and search operations.

### 4.3.1 NOR TCAM Cell Circuit

Circuit diagram of the proposed TCAM is shown in Fig. 4.2. Two MTJs store D and D respectively. Transistors M1 and M2 form ML discharge network depending on the result of data comparison with the search lines SL and SL. During search transistors M3/M5 and M4/M5 along with MTJ resistance due to TMR make a voltage divider network in which the drain voltages of M3/M4 drive the gates of discharge transistors M1/M2. The cell is designed in such a way that during match the voltage of node X1 and X2 is below the threshold voltage of M1 and M2, and the ML stays precharged. However, during a mismatch the voltage of X1 and X2 rises above the threshold voltage of M1 and M2 respectively discharging the ML. Transistor M3/M4 are the wordline (WL) selection transistors and M6 is the write access transistor that turns ON only during write (WR) operation. Transistor M6 is sized larger to allow sufficient write current. Transistor M5 is driven by Search Enable (SE) signal and, sized to limit the current through STTRAM bit for read

disturb free search operation. Don't care bit can be stored in the cell by storing '1' in both D and  $\overline{D}$  bits. The search bit can be masked by driving  $SL = S\overline{L} = 0$  on the search lines. The Source Line (SrL) is used for two purposes namely, (a) write operation when the SrL is connected to 0 or Vdd depending on the write data to the MTJs; and, (b) search operation when SrL is driven to 0 to allow voltage division.

Figure 4.2: Proposed NOR type TCAM cell.

## 4.3.2 Qualitative Analysis of the Cell Design

There are two match cases namely, (a)  $(D, \overline{D} = (SL, \overline{SL}) = (1, 0)$ ; and, (b)  $(D, \overline{D}) = (SL, \overline{SL}) = (0, 1)$ . Since both cases are identical, we will only explain the first case. For  $(D, \overline{D}) = (1, 0)$  the left side MTJ is in high resistance  $(R_H)$  state whereas the right side MTJ is in low resistance  $(R_L)$  state. Since  $(SL, \overline{SL}) = (1, 0)$ , the voltage at node X1 is

$$V_{X1} = V_{SL} \times \frac{r}{(R_H + r)} = V_M \tag{4.1}$$

and the voltage at node X2 is voltage drop due to current flow from node X1 to SL (detailed analysis is given in Section 4.3.4). In this expression, r is the lumped ON resistance of transistors M3, M4 and M5 (Fig.4.3), and,  $V_{SL}$  is SL voltage. To keep transistor M1 OFF during match,  $V_{X1}$  should be lower than  $V_{TH0}$  (i.e., the threshold voltage of M1 and M2).

Figure 4.3: Equivalent circuit during match and mismatch. (a) Match M1 and M2 are turned ON; and, (b) Mismatch M1 and M2 are OFF as  $V_{d1} < V_{th0}$

For the mismatch, there are two cases namely, (a)  $(D, \overline{D}) = (1, 0)$  and (SL, SL) = (0, 1); and, (b)  $(D, \overline{D}) = (0, 1)$  and (SL, SL) = (1, 0). For the first case the voltage at node X1 is

$$V_{X1} = V_{\bar{SL}} \times \frac{r}{(R_H + r_{eff})} = V_{MM1}$$

(4.2)

where  $r_{eff}$  is the effective resistance of  $R_L, r_3, r_5, andr_4$  resistive network. Whereas, voltage at X2 is

$$V_{X2} = V_{\bar{SL}} \times \frac{r}{(R_H + r)} = V_{MM2}$$

(4.3)

where  $V_{SL}$  is SL) voltage. To keep transistors M1, M2 ON during mismatch,  $V_{MM1}$  and  $V_{MM2}$  should be higher than  $V_{TH0}$ . Similar analysis applies to case (b). From these equations  $V_{MMX} > V_{MX}$  for the two cases as  $R_H > R_L$ . For the design to function properly (i.e., discharge ML during mismatch at a higher speed compared to that of a match case)  $R_H$ ,  $R_L$  and r should be selected such that  $V_{MX} < V_{TH0} < V_{MMX}$ . The following analytical equations can be used to quantify the design parameters.

$$V_{MM} = V_{dd} - I_{MM} \times R_L = V_{\bar{SL}} \times r/(R_L + r) = V_{th0} + \Delta_1$$

(4.4)

$$V_M = V_{dd} - I_M \times R_H = V_{SL} \times r/(R_H + r) = V_{th0} - \Delta_2$$

(4.5)

where  $I_{MM}$  and  $I_M$  are the currents drawn from SL and SL in case of mismatch and match respectively, and,  $\Delta_1$  and  $\Delta_2$  are the offset voltages with respect to  $V_{th0}$ .

Subtracting 4.4 and 4.5 and using  $R_H = R_L \times (1 + TMR)$ , we obtain

$$V_{MM} - V_M = V_{dd} \times \frac{r}{R_L + r} - \frac{r}{R_H + r} = \Delta_1 + \Delta_2$$

(4.6)

$$V_M = V_{dd} \times \frac{r \times R_L \times TMR}{(R_L + r) \times (R_L(1 + TMR) + r)} = \Delta_1 + \Delta_2 \tag{4.7}$$

The optimization of the proposed TCAM revolves around three key requirements: (a) maximizing the difference between mismatch and match voltages i.e.,  $(\Delta_1 + \Delta_2)$ ; (b) maximizing the absolute values of offsets from  $V_{TH0}$  i.e.,  $|\Delta_1|$  and  $|\Delta_2|$  to keep M1/M2 strongly ON or OFF as needed during mismatch and match respectively; and, (c) lowering the search current below critical write current of MTJ.

From 4.7, it can be concluded that higher TMR, higher  $R_H$  and higher r can be employed to enhance  $(\Delta_1 + \Delta_2)$ . Although higher r and  $R_L$  is also good for maximizing  $\Delta_1$ , it minimizes  $\Delta_2$ .

Figure 4.4:  $V_{gs}$  margin diagram illustrating best and worst  $V_M$  and  $V_{MM}$  with  $V_{th0}$ .

A lower  $\Delta_2$  can turn M1/M2 ON during match degrading the sense margin. Fig.4.4 shows pictorial representation of this situation with three operating points. The voltages  $V_{MM1}, V_{MM3}, V_{M1}$  and  $V_{M3}$  provide poor sense margin compared to  $V_{MM2}$  and  $V_{M2}$  even with same magnitude of  $\Delta_1 + \Delta_2$ . The ideal margin is obtained when  $R_H = \infty$  and  $R_L = 0$  which gives  $V_{MM} = V_{dd}$  and  $V_M = 0$ . However, a lower  $R_L$  could be detrimental for read disturb due to high search current. High values of  $R_H$  and  $R_L$  ensure the low search line currents. This in combination with high TMR can provide better  $V_{gs}$  margin i.e.,  $(\Delta_1 + \Delta_2)$  with low search power consumption. The design optimization conducted accounts for the above factors.

### 4.3.3 Write Operation

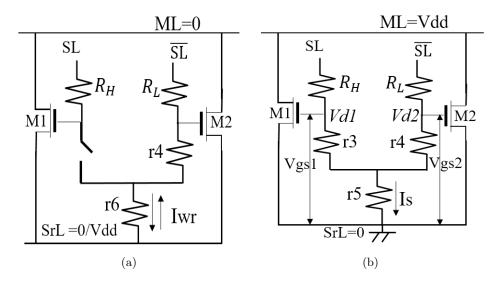

In the proposed TCAM the search lines SL and SL are used to write data to the STTRAM bits. Table-4.1 summarizes the states of control signals in write operation. Writing '1' and '0' consume two cycles to write to the two STTRAMs while 'X' can be written in a single cycle. During write the ML precharge is disabled to avoid power consumption from the ML. This is achieved by pulling the 'precharge' signal high. NMOS transistor M6 is turned ON during write by WR signal. Note that M6 is sized to provide the drain current greater than the critical write current of the STTRAM. The state of search enable signal SE is 'Don't care' as M5 is connected parallel to M6.

Figure 4.5: Equivalent circuit during write and search operation. (a) Write operation, left side STTRAM resistance is  $R_H$  (D='1') and right side STTRAM resistance is  $R_L(\bar{D} = 0')$ ; and, (b) search operation.

For the analysis, we assume that SE is pulled low. The WL is turned ON only for the selected word so that the unselected cells are unaffected. The source line SrL is controlled appropriately to write a '1' or '0'. Fig. 4.5a shows the equivalent circuit of TCAM cell during write. The transistors are replaced with equivalent ON resistances. Resistors r3, r4 and, r6 are equivalent resistors of M3, M4 and, M6 respectively. The write operation is described below. In the first cycle of write operation, writing to D bit is enabled by pulling WL1 to  $V_{dd}$  and  $\overline{D}$  bit path is disabled by pulling WL2 to ground. In the second cycle of write operation, writing to  $\overline{D}$  bit is enabled by pulling WL2 to  $V_{dd}$ and D bit path is disabled by pulling WL1 to ground.

| Table 4.1: States of control | signals NOR TCAM | I memory write operations. | WR= $V_{dd}$ , SE='X' |

|------------------------------|------------------|----------------------------|-----------------------|

|                              |                  |                            |                       |

|           | Writ     | e D-bi     | t (WL1= $V_{dd}$ , WL2=0) | Write $\overline{D}$ -bit (WL1=0, WL2= $V_{dd}$ ) |            |          |  |

|-----------|----------|------------|---------------------------|---------------------------------------------------|------------|----------|--|

|           | SL       | $\bar{SL}$ | SrL                       | SL                                                | $\bar{SL}$ | SrL      |  |

| Write '1' | 0        | Х          | $V_{dd}$                  | Х                                                 | $V_{dd}$   | 0        |  |

| Write '0' | $V_{dd}$ | Х          | 0                         | Х                                                 | 0          | $V_{dd}$ |  |

| Write 'X' | 0        | 0          | $V_{dd}$                  | $\mathrm{WL1}{=}\mathrm{WL2}{=}V_{dd}$            |            |          |  |

- Writing '1': In the first cycle, SrL is pulled high and SL line is pulled to ground. The write current flows from SL writing antiparallel state to the STTRAM storing bit D. There is no current through the other STTRAM bit as the WL2 control signal is grounded. In the second cycle the SrL is pulled low,  $\bar{SL}$  is pulled to  $V_{dd}$  and WL2 is pulled high which programs the other STTRAM storing  $\bar{D}$  to parallel state. There is no current through the other STTRAM bit as WL1 is grounded.

- Writing '0': In the first cycle, the SL is pulled high and the SrL line is pulled low. This cycle writes parallel magnetization state to STTRAM storing D bit. In the second cycle, the SrL is pulled high while SL is at 0, which programs the D bit to antiparallel state.

- Writing 'X': The 'X' state can be stored by writing logic 1 to both D and  $\overline{D}$ . The SrL is pulled to  $V_{dd}$  and the search lines SL and  $\overline{SL}$  are pulled low. The current flows through both the STTRAMs storing antiparallel states to D and  $\overline{D}$ .

#### 4.3.4 Search Operation

Search is a single cycle operation in CAM. The ML is precharged to  $V_{dd}$  and WR is pulled to ground. The SrL is pulled to ground throughout the search operation. Next SE and WL is pulled high to enable the conducting path through M5 and M3/M4 (4.2). Either  $V_{MM}$  or  $V_M$  voltage is developed depending on the match or mismatch respectively at the gate of M1/M2. The search lines SL is pulled to  $V_{dd}$  and SL is pulled low to search a bit '1'. Similarly, SL is pulled low and, SLis pulled to  $V_{dd}$  to search for bit '0'. Both SL and SL are pulled low to search 'X'. Circuit operation in match and mismatch cases are discussed below. Fig. 4.5b shows the equivalent circuit during search operation. • Match: Let  $(D,\overline{D}) = (SL, \overline{D}) = (1, 0)$ . Voltages  $V_{X1}$  and  $V_{X2}$  at the nodes X1 and X2 (Fig.4.2) are given by,

$$V_{X1} = V_{dh} = V_{dd} \times \frac{(r3 + (r5 \parallel (r4 + R_L)))}{R_H + r3 + (r5 \parallel (r4 + R_L))}$$

(4.8)

$$V_{X2} = V_{dl} = V_{dd} \times \frac{((r5 \parallel (r4 + R_L)) \times R_L)}{(R_H + r3 + (r5 \parallel (r4 + R_L)))(r4 + R_L)}$$

(4.9)

Note that  $V_{X2}$  is less than  $V_{X1}$  and appears due to the potential across r5 which results in a current though  $R_L$  even when  $\bar{SL}=0$  (Fig. 4.3a). The transistors M3 and M5 are sized such that  $V_{X1} < V_{th0}$ . So M1/M2 are turned OFF and the ML remains precharged. The other match case i.e.,  $(D,\bar{D}) = (SL,\bar{D}) = (0, 1)$  is similar.

• Mismatch: Mismatch: Let  $(D,\overline{D}) = (1, 0)$  and  $(SL,\overline{SL}) = (0, 1)$ . Then,