# **New Jersey Institute of Technology** Digital Commons @ NJIT

Theses and Dissertations Dissertations

Spring 1969

# Concepts in LSI servo-control-electronics

Alfons Alfred Tuszynski New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations

Part of the Electrical and Electronics Commons

# Recommended Citation

Tuszynski, Alfons Alfred, "Concepts in LSI servo-control-electronics" (1969). Dissertations. 1339. https://digitalcommons.njit.edu/dissertations/1339

This Dissertation is brought to you for free and open access by the Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

# 70-4445

TUSZYNSKI, Alfons A., 1921-CONCEPTS IN LSI SERVO-CONTROL-ELECTRONICS.

Newark College of Engineering, D.Eng.Sc., 1969 Engineering, electrical

University Microfilms, Inc., Ann Arbor, Michigan

(c) Alfons A. Tuszynski 1970

ALL RIGHTS RESERVED

### CONCEPTS IN LSI SERVO-CONTROL-ELECTRONICS

BY

## ALFONS TUSZYNSKI

#### A DISSERTATION

PRESENTED IN PARTIAL FULTILLMENT OF

THE REQUIREMENTS FOR THE DEGREE

OF

DOCTOR OF ENGINEERING SCIENCE

AT

NEWARK COLLEGE OF ENGINEERING

This dissertation is to be used only with due regard to the rights of the author. Bibliographical references may be noted, but passages must not be copied without permission of the College and without credit being given in subsequent written or published work.

Newark, New Jersey

# APPROVAL OF DISSERTATION

BY

CONCEPTS IN LSI SERVO-CONTROL-ELECTRONICS

ALFONS TUSZYNSKI

FOR

DEPARTMENT OF ELECTRICAL ENGINEERING

NEWARK COLLEGE OF ENGINEERING

BY

## FACULTY COMMITTEE

| APPROVED: | <br>Chairman |

|-----------|--------------|

|           |              |

|           |              |

|           |              |

NEWARK, NEW JERSEY

### ABSTRACT

This thesis deals with the engineering aspects of control electronics. It examines modern concepts of servocontrol theory in the light of recent developments in the technology of monolithic circuits. Applicational considerations are slanted towards Aerospace standards of reliability and power-consumption economy.

Conclusions drawn from the discussion of fabrication constraints and performance requirements lead to a preference for digital implementations. Yield probelms on one hand and aging effects on the other greatly reduce the feasibility rating of analog arrays.

Current practice in servo-control electronics revolves around purely analog implementations, sampled-data systems and primitive on-off arrangements. The motivation behind the status quo and the justification of the proposed approach are discussed in detail.

The organization of digital systems is examined in order to demonstrate the feasibility of Large Scale Integration (LST) in servo-control electronics. The questions of hardware versatility and power-dissipation economy are emphasized from technological, economical and applicational standpoints.

Self-Contained loops and Computer-Aided systems are investigated within the ramifications of a functional division into Detectors, Compensators and Drivers. Differential Frequency Modulation is assumed to effect the information

transfer from the Pick-Off coil of the transducer to the Thput ports of the Ratemeter. Pulse Width-Frequency Modulation is employed at the Driver-Torquer interface.

The operation of the Ratameter conforms with classical logic, except for a slope-independent Level-Crossing-Discriminator (LCD), which it designed to provide a time-resolution gain of 3 db. over conventional frequency detectors. Circuit details of the LCD are given in order to illustrate differences between integrated and discrete circuit configurations. Two types of compensators are discussed: canonic pole-zero arrangements with ROM multipliers and Kalman filters with spored-program implementations of covariance equations.

The concept of Pulse-Widen-Fraguency-Modulation (PWFM) is introduced to reconcils the dynamic-range requirements of servo-control drivers with the time-resolution limitations of power transistors. Sumple means of implementation of PWFM are also given; they take the form of a combination of logic-gates and DDA elements, a technique which could be used to advantage in other applications, especially digital dutection and filtration.

Name of student: Alfons A. T. L. junki Degree. Doctor of Engineering Schence Title of dissertation: Concepts in LSI Servo-Control Electronics

Name of Adviser: Dr. J. J. Padalino

## ACKNOWLEDGEMENTS

The writer wishes to acknowledge his indebtedness to the staff of the Newark College of Engineering, in particular to Dr. Phyllis Fox, Dr. A. U. Meyer, Dr. J. J. Padalino, Dr. F. A. Russell and Dr. K. S. Sohn.

# TABLE OF CONTENTS

| INTRO | DUCTION                                            | 1  |

|-------|----------------------------------------------------|----|

| Chapt | er                                                 |    |

| I.    | SERVO-CONTROL-ELECTRONICS, STATUS AND INNOVATIONS  | 3  |

|       | Theory                                             | 3  |

|       | Technology                                         | 4  |

|       | Circuit Design                                     | 8  |

|       | Applications                                       | 11 |

| II.   | ORGANIZATION OF THE ELECTRONIC SUBSYSTEM           | 14 |

|       | Analog Systems                                     | 14 |

|       | Digital Systems                                    | 20 |

|       | The Digital vs. Analog Decision                    | 25 |

| III.  | DIGITAL DETECTORS                                  | 27 |

|       | Principle of Operation                             | 27 |

|       | The Level-Crossing-Discriminator                   | 29 |

|       | The Ratemeter                                      | 32 |

| IV.   | DIGITAL COMPENSATORS                               | 36 |

|       | The Canonical Filter                               | 36 |

|       | The Digital Integrator                             | 43 |

|       | The Z-Transform and the State-Space Representation | 46 |

|       | Digital-Differential-Analyzer Implementations      | 49 |

|       | Realization of Optimal Filters                     | 53 |

| Cha | pter |

|-----|------|

|-----|------|

| V.     | DRIVERS AND PULSE-WIDTH-FREQUENCY-MODULATION 60 |  |

|--------|-------------------------------------------------|--|

|        | Pulse-Width-Modulation 61                       |  |

|        | The Format Converter 65                         |  |

|        | Pulse-Frequency-Modulation 69                   |  |

|        | Limitations of PWM and PFM                      |  |

|        | Pulse-Width-Frequency-Modulation 83             |  |

| CONCL  | USION 90                                        |  |

| RECOM  | MENDATIONS                                      |  |

| Append | dixes                                           |  |

| I.     | EFFICIENCY AND LINEARITY OF DIGITAL DRIVERS 99  |  |

| II.    | ANALYSIS OF PWM EXCITATION 102                  |  |

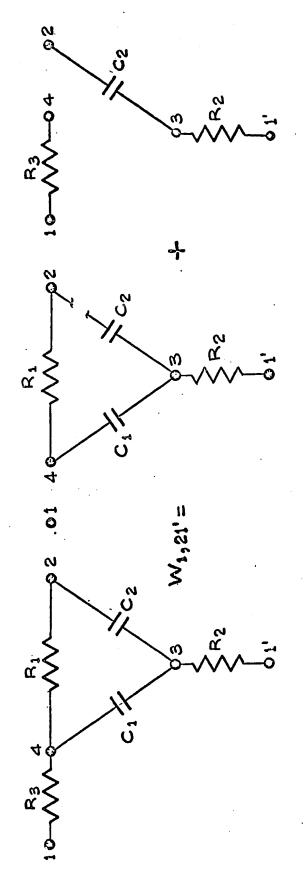

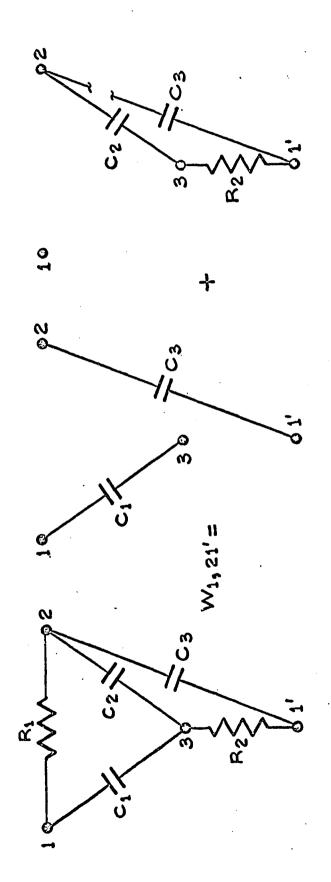

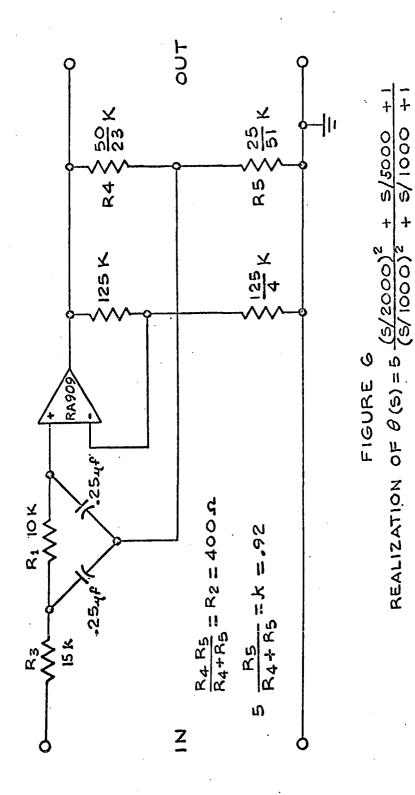

| III.   | ACTIVE ANALOG RC FILTERS 107                    |  |

| REFERI | ENCES                                           |  |

| VTTA   |                                                 |  |

•

# LIST OF FIGURES

| Figure |                                                                       | Page |

|--------|-----------------------------------------------------------------------|------|

| II.1.  | Self-Contained Analog Loop                                            | 1.5  |

| II.2.  | Sampled-Data Systems                                                  | 17   |

| 11.3.  | The Sampling-Process Sequence                                         | 18   |

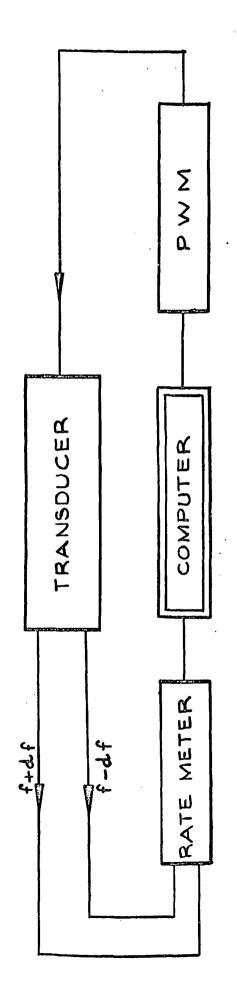

| 11.4.  | Self-Contained Digital Loop                                           | 21   |

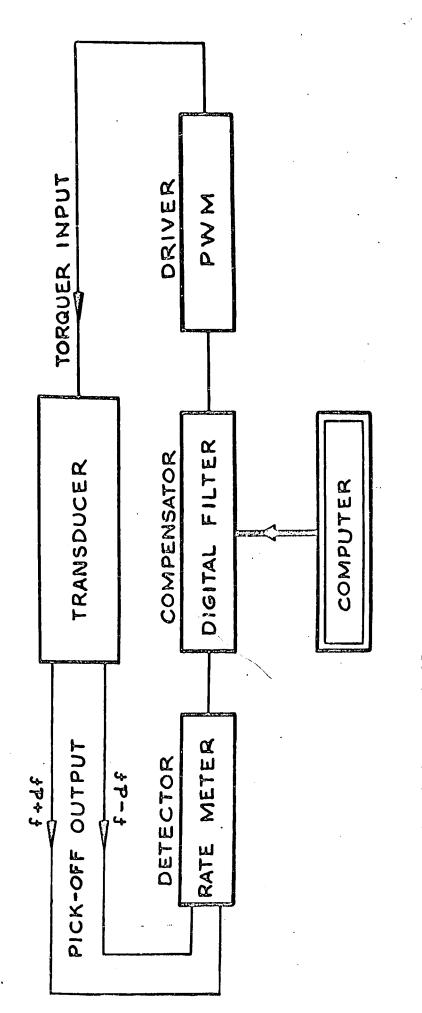

| II.5a. | Computer-Aided Digital Control                                        | 23   |

| II.5b. | Adaptive Loop                                                         | 24   |

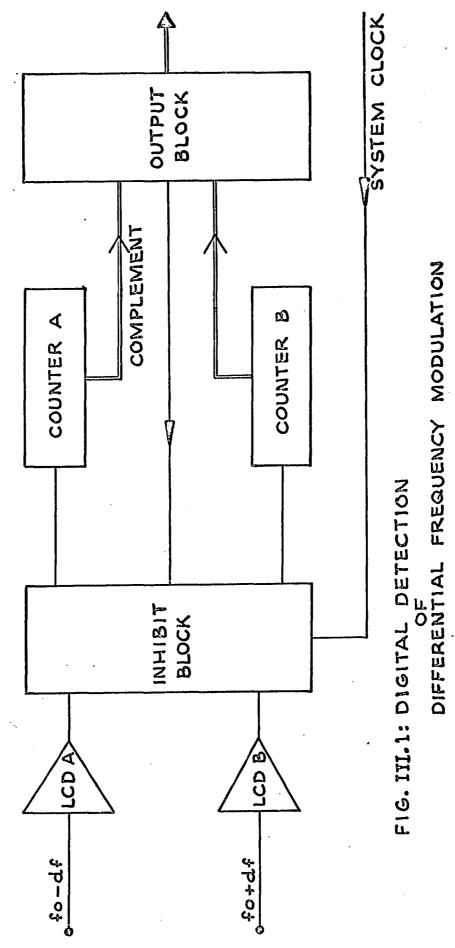

| III.1. | Digital Detection of Differential Frequency Modulation                | 28   |

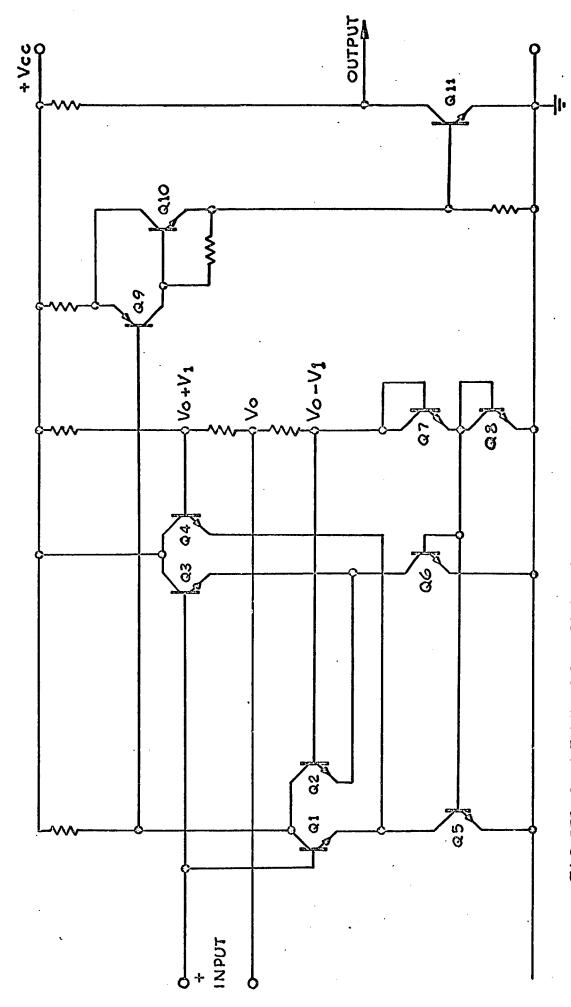

| III.2. | Level-Crossing Discriminator                                          | 30   |

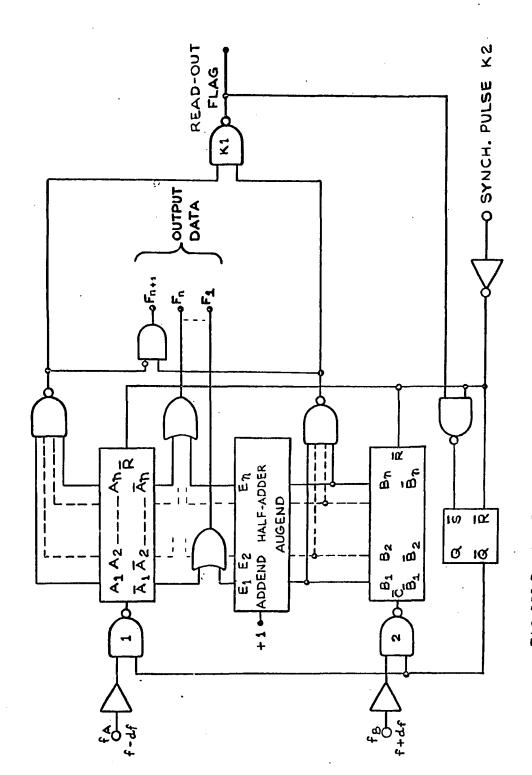

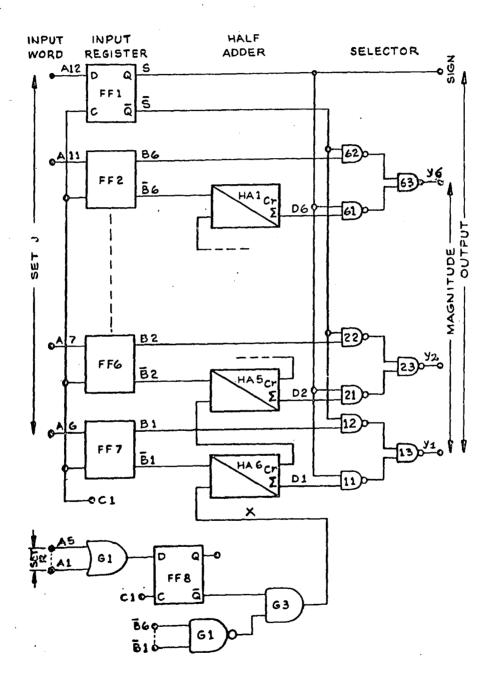

| 111.3. | The Ratemeter                                                         | 33   |

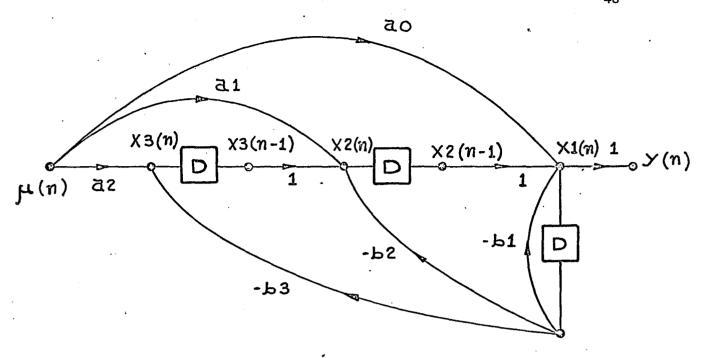

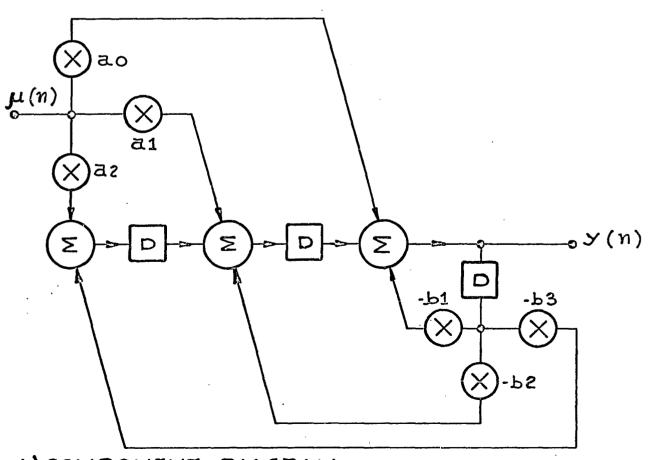

| IV.1.  | Implementation of Equation IV(1)                                      | 37   |

| IV.2.  | Triple Pole/Zero Digital Filter                                       | 39   |

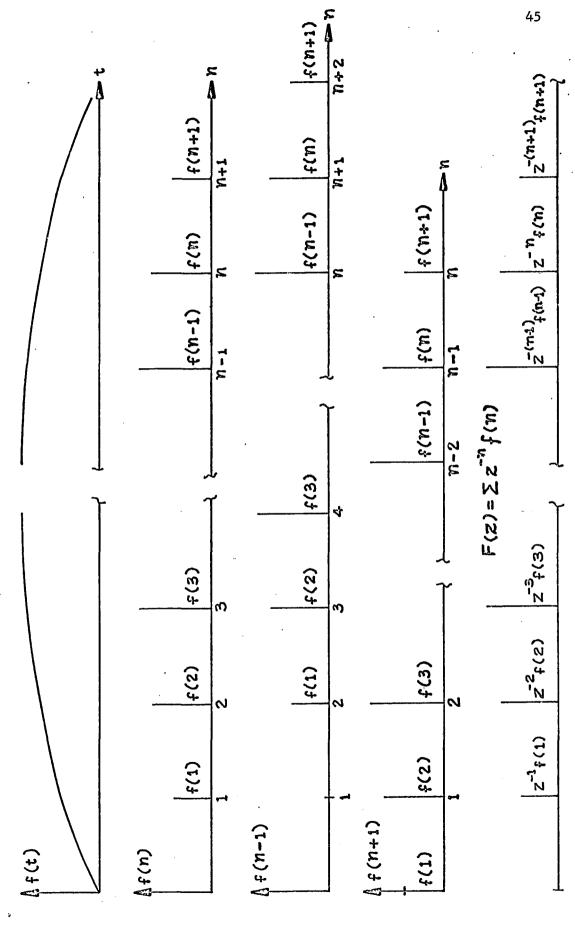

| IV.3.  | Time-Shifting of Discrete Signals                                     | 45   |

| IV.4.  | Equation IV.(25) in State-Space and Component-Diagram Representations | 48   |

| IV.5a. | Implementation of Equation IV.(28)                                    | 51   |

| IV.5b. | Implementation of Equation IV.(28)                                    | 52   |

| IV.6.  | Implementation of Equation IV.(37)                                    | 59   |

| V.1.   | Idealized Response of Pulse Modulators                                | 62   |

| V.2.   | The Basic Pulse-Width Modulator                                       | 64   |

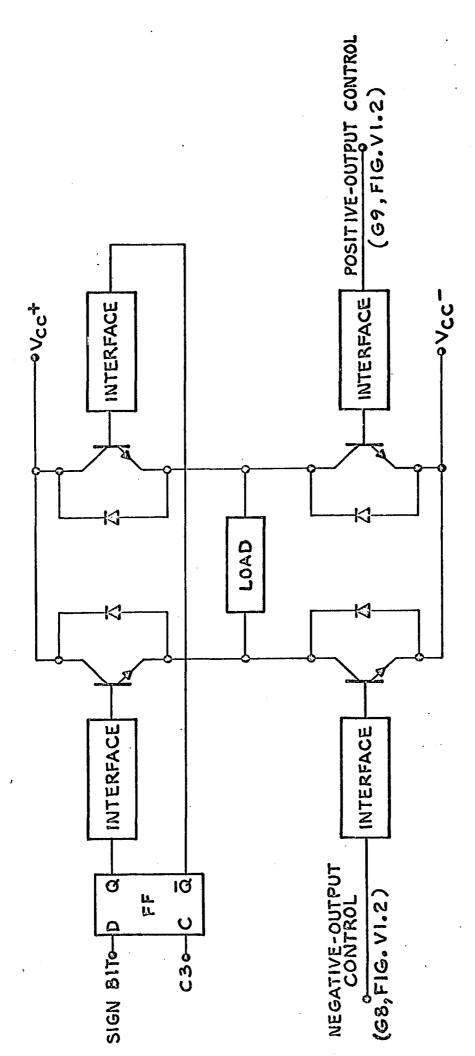

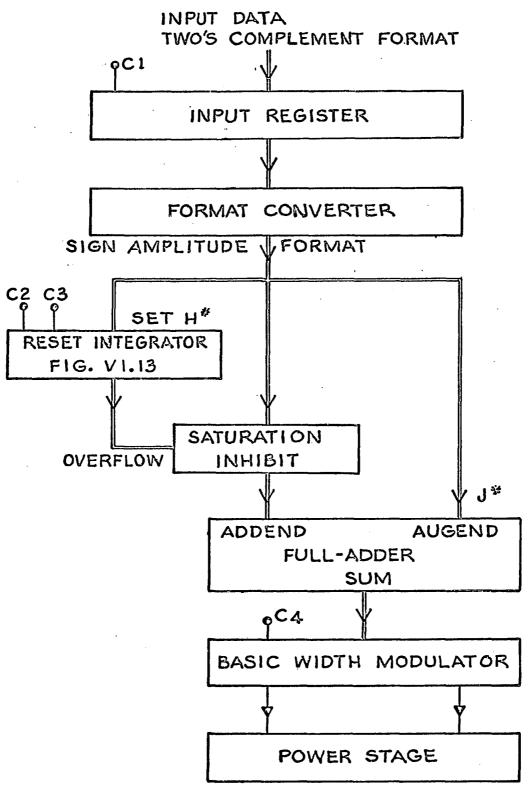

| V.3.   | The Complete Driver                                                   | 66   |

| V.4.   | Format Converter                                                      | 67   |

| 17 E   | Description Chairm                                                    | 40   |

| Figure |                                                                                        |   | Page |

|--------|----------------------------------------------------------------------------------------|---|------|

| V.6.   | Classification of Input Data into Functional Sets .                                    |   | 71   |

| V.7.   | The Reset Integrator                                                                   | • | 72   |

| V.8.   | The Clock Schedule                                                                     | • | 73   |

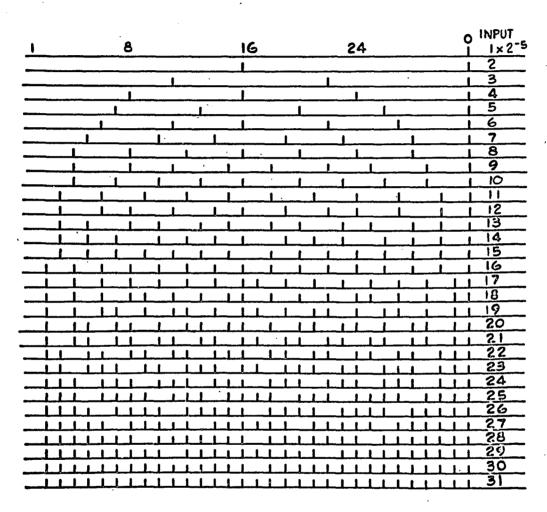

| V.9.   | Response of a 6-bit Reset Integrator                                                   | • | 75   |

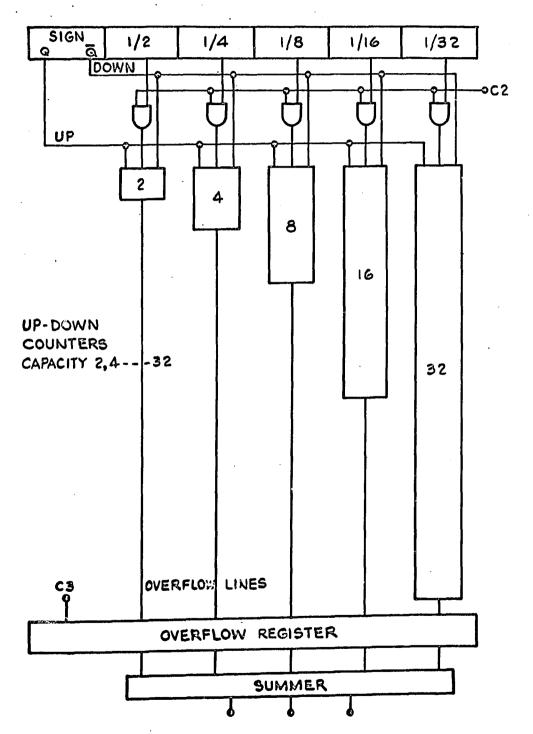

| v.10.  | Alternative Implementation of the Reset Integrator .                                   | • | 78   |

| V.11.  | Output Distortion, Rhombic Approximation                                               | • | 80   |

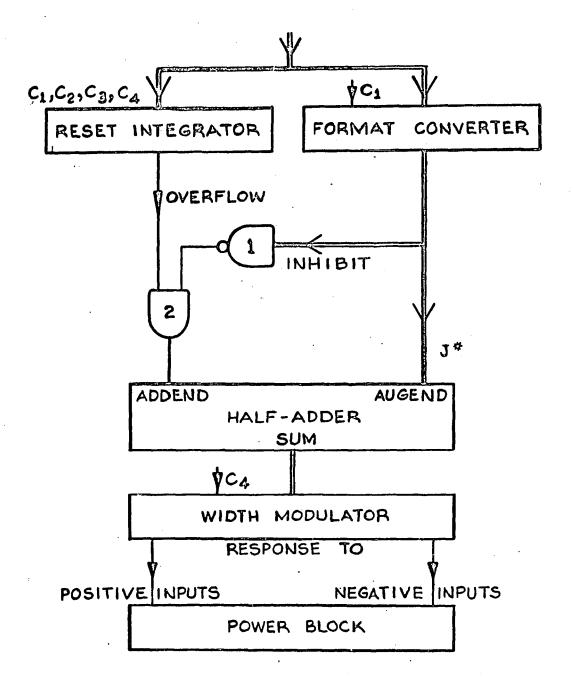

| V.12.  | PWFM Driver                                                                            | • | 85   |

| v.13.  | Alternative Implementation of a PWFM Driver                                            | • | 87   |

|        | Appendix II                                                                            |   |      |

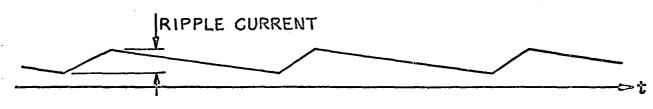

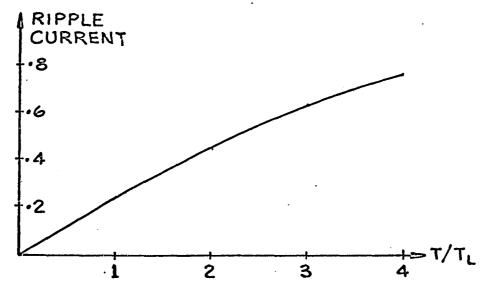

| II.1.  | PWM Excitation of Inductive Loads                                                      | • | 103  |

|        | Appendix III                                                                           |   |      |

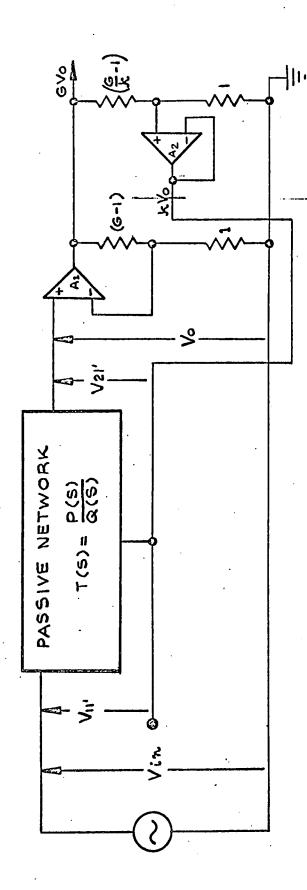

| 1.     | Feedback to the Ground Node of a Passive Network                                       | • | 109  |

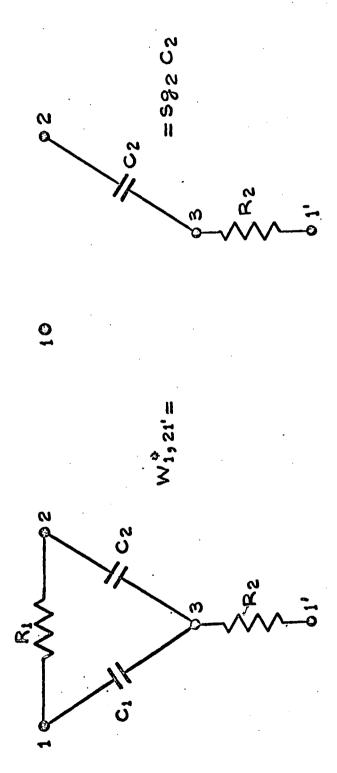

| 2.     | Voltage Transfer Functions of Two-Ports and Three Terminal Networks                    |   | 110  |

| 3.     | The Trial Network                                                                      | • | 113  |

| 4.     | Modification No. 1                                                                     | • | 115  |

| 5.     | Modification No. 2                                                                     | • | 116  |

| 6.     | Realization of $\theta(s) = 5 \frac{(s/2000)^2 + s/5000 + 1}{(s/1000)^2 + s/1000 + 1}$ | • | 117  |

## INTRODUCTION

Confrontation with a significant new device or phenomenon stimulates research in associated sciences and technologies. The ensuing effort is usually directed towards the development of the basic concept, the improvement of the fabrication techniques or the utilization of advantageous characteristics of the given device. Quite frequently disappointment follows because of technological problems, as witnessed in the case of multi-grid gas tubes, or applicatory difficulties, as in the case of tunnel diodes.

Occasionally the utility and feasibility of a discovery may become immediately established, evoking wide-front research into all pertinent aspects of technology and engineering. This has happened in the case of the Junction Transistor, the Integrated-Circuit (IC) and, most recently, in the case of the Large-Scale-Integration (LSI) technology.

The greatest concentration of IC and LSI oriented research is understandably found in areas associated with mass-production items such as digital-computer elements, operational amplifiers and functional modules for TV. Devices of lesser market potential do not receive much attention during the early stages of the evolution of the solid-state technology. There is, however, a noticeable trend towards an unprecedented level of standardization of individual devices and complete systems.

A stalemate situation prevails in the field of Servo-Control hardware. Current practice in Servo-Electronics is confined to analog implementations; there is a slow trend towards Central-Computer processing of all control data.

We intend to explore the implementation of Servo-Control-Electronics in the light of the possibilities presented by the LSI technology, without bias induced by common usage in other applications, but with recognition of the advantages of proper standardization.

We investigate, in Chapters I and II, the theoretical concepts, applicatory requirements and technological limitations of Servo-Electronics, and arrive at a preference for digital, rather than analog, implementations. Digital implementations are compatible with the fabrication constraints of LSI. They also meet the stability requirements of modern control installations. Analog implementations do not fulfill either of the above two requisites.

Organizational concepts and module-level details for the implementation of LSI Control-Electronics are presented in Chapters II through V.

#### CHAPTER I

### SERVO-CONTROL ELECTRONICS--STATUS AND INNOVATIONS

### Theory

The mathematical aspects of control-theory and associated subjects have received a good deal of attention during the last two decades. The "state-space" formulation of differential equations and the "state-transition-matrix" representation (H6, Z1, D3, S2, R8) of dynamic systems have attained the status of classical procedures. Optimization of filters progressed from the Wiener-Kolgomorov theory (L2, P3, W6) to the Kalman-Bucy realization (K3, K2, S12, F1), shifting the interest from the implementation of the Wiener-Hopf Equation to the solution of the Variance Equation. Popularization of topological methods diversified the approach to Active-Filter synthesis (B1, B2, P1), while the development of computerized analysis (H1, K8, D2) lightened the burden of network computations.

Bellman's Principle of Optimality (B4, B5, B6, T6) and Pontryagin's Minimum Principle (P7, T3, A4) led to new concepts of system optimization. Kalman's Theory of Duality (K1, K2, H3) linked stochastic filtration to deterministic optimal-control. The Z-transform became a standard tool of Sampled-Data analysis (F4, K7, L7) and Digital-Filter synthesis (K9, R1, B7). The Fast-Fourier-Transform algorithm (C7, B12, M3) revitalized spectral analysis and strengthened the already prevalent trend towards central-computer processing of all control-data.

Most of the above techniques can be grouped together under the heading of numerical methods in process control. The interest in these techniques has arisen in response to the popularization of digital computers, which have become everyday tools of human and machine operations. The proliferation of digital computers is in turn attributable to recent developments in solid-state physics.

There are applications in which general-purpose computers do not present the best engineering solution. Time-sharing is not a panacea, not even in large installations. Some specialized problems can be solved by relatively modest means. Analog methods are acceptable in many short-duration projects.

It is therefore necessary to investigate which functions can be best performed by analog and which by digital hardware. In the digital domain one must further discriminate between special-purpose hardware and central-computer implementations. We will deal with the above problems within the ramifications of Servo-Control-Electronics.

### **Technology**

The first semi-conductor amplifying device, the point-contact-triode (B3), did not progress beyond the level of a demonstration model, but Shockley's invention of the junction-transistor (S9, S11) has produced practical results. It has also established a principle of lasting value and utility.

The junction-transistor was initially fabricated as a grown-junction device. In an attempt to boost the frequency response and to streamline fabrication techniques, other structures and processes (V1, K6, G3) were tried with various degrees of success. A major innovation by Hoerni led to the planar transistor (H4) and the passivation techniques (P6), which are in general use today. The epitaxial process (C3, B13, M6), a breakthrough in crystal-growth technology, widened the performance horizons of discrete transistors and provided a workable basis for the fabrication of integrated-circuits. A good deal of present-day research is devoted to ion-implantation techniques (L3), which are expected to improve the controlability of the doping process.

Integrated-Circuits are a natural outcome of the planar technology. Contemporary IC's are generally made by the six-masks process (W1). Some new ideas have been introduced to overcome the drawbacks of the bi-polar IC technology: buried-layer diffusion (C2) to reduce the collector-resistance, and lateral-transistors (M8) as well as substrate-collector transistors (S3) to replace conventional pnp devices. Diode isolation continues to maintain a dominant position by virtue of its simplicity and efficacy.

The development of practical field effect devices has been retarded by various surface state problems (M11, W4). Threshold instability and general lack of dependability are still the worst drawbacks of MOS transistors, but steady progress in oxide formation and etching techniques (M7, M1) begins to yield devices which are compatible with LSI concepts and requirements. MOS devices can be

integrated without isolation. One simple structure can be used either as a transistor or a resistor. Slight modification of the pattern gives a capacitor. Multi-Phase logic (K4, Y1) overcomes the speed limitation of RC circuits. Complementary MOS arrangements (R4, L9) produce even better results, admittedly at the expense of technological complications.

Our concept of LSI is predicated on the use of multi-layer interconnect matrices (L10). The first layer interconnects separate devices into logic-elements such as gates, flip-flops, shift-registers, etc. The second layer assembles the logic-elements into modular groups such as counters, adders and multipliers. The third metallization layer, if used, converts modular groups into sub-system blocks at the level of scratch-pad memories, arithmetic-units, canonic filters and ratemeters (L5).

A three-sided comparison between bipolar, complementary MOS and multi-phase MOS implementations would appear to be in order, but an examination of the third technique with regard to long-term objectives reveals the distinct stigma of a stop-gap measure. It is, therefore, advisable to confine our comparison to the bipolar and the complementary MOS technologies.

Bipolar devices have a clean-cut advantage in speed (H2, L10);

LSI blocks of Emitter-Coupled-Logic operate at nano-second clockrates (W7). Furthermore, junction transistors are still more stable

and more reliable than MOS-FETs. Their intrinsically high

transconductance (W2) is useful in sense-amplifier applications.

MOS arrays have excellent speed/power characteristics (A2), facilitating operation of mega-Hertz gates at nano-Watt power levels. They are also very economical in terms of substrate-area (F2).

The choice between the two techniques depends on applicatory factors. In Servo-Control-Electronics speed requirements are modest, but reliability considerations dictate the choice of bipolar techniques. As the stability of MOS devices improves, FET implementations may become preferable because of power-economy considerations.

The LSI technology has its due share of disadvantages. There are power dissipation difficulties, interconnection problems, standardization requirements, tolerance limitations and some economic complications.

The first two disadvantages of LSI are inherent in the miniaturization concept. As we shrink the dimensions of a device, we reduce its power dissipation rating and impose limitations on the size and number of terminals.

Other disadvantages are attributable to the empirical status of the semi-conductor technology. The end result of a series of operations embracing crystal formation and surface preparation as well as a number of etching and diffusion operations cannot be expressed by a mathematical formula. We must therefore rely on conformance with empirically established procedures. Repeatability of device characteristics is the sole criterion of process control.

The reliability of monolithic circuits can be very high (W3, M9) if mass production methods are combined with (1) stringent in-process inspection, (2) far-reaching electrical characterization, and (3) extensive follow-up testing. On the other hand, reliability will be poor, or at best indeterminate, if small-batch lots are produced under conventional laboratory conditions.

Reliability of low-demand items presents a problem which is especially severe in servo-control-electronics. The demand for any particular type of servo-control-hardware is quite low in terms of IC-production quantities. It is therefore necessary to devise a scheme which will embrace a large section of the total servo-control market, and thus create a demand compatible with IC-fabrication economics.

Product standardization plays an important role in LSI science and economics. It boosts the yield and cuts the costs while it improves reliability and electrical performance, but it demands specialization and resourcefulness. Individual circuits must be sufficiently versatile to work in conjunction with a wide variety of other circuits and the performance of generic families must be sufficiently good to meet the requirements of many applications.

### Circuit Design

The last 15 years have witnessed two major evolutions of circuit-design concepts. The first marked the transition from electron-tube to transistor circuits; it reached its peak at the turn of the decade, when it became apparent that the advent of the Silicon-Planar

technology (H4) had produced the best available amplifying device.

Many new circuit-configurations emerged, some utilizing unique advantages, others overcoming unique limitations of the transistor-technology. There was a significant increase in the number of active devices per circuit and a decrease in the number of passive devices.

On the system level, a slight preference for digital implementations became noticeable.

Popularity of thin-film resistor-matrices in the early sixties (T9) brought only minor changes in the approach to circuit design. However, since it coincided with an intensification of research work in Active Filters, it helped to eliminate the use of magnetic components in compensator applications.

The second evolution, much more drastic than the first, was set off by the emergence of the monolithic-circuit technology. Preference for digital implementations moved up another notch and circuit design began to merge with device design.

In analog circuits, some of the new arrangements arose from an observation disclosed by us in 1962 (T8) and extended by Hoffait and Thornton in 1964 (H5). This observation concerns the thermal drift of dual-transistors and states that the thermal coefficient of the offset-voltage is proportional to the offset-voltage itself.

Let  $\Delta V$  be the offset-voltage of two generically similar transistors, then

$$d(\Delta V)/dT = d(V_{be1}-V_{be2})/dT = k(\Delta V)$$

(1)

where,

$$k \approx 3 \text{(microVolts/°C)}$$

per milliVolt of offset, if (2)

$I_{c1} = I_{c2}$  and  $V_{ce1} = V_{ce2}$ .

Practical utilization of this principle in Integrated Circuits is predicated on the intrinsic matching of devices contained within one die. Matching to better than 1/2mV-offset is typical, permitting implementation of simple constant-beta structures (W9, W11) and transistor-controlled current-sources (B10).

In digital circuits, development of multiple-emitter transistors produced the popular TTL gate (L10). Utilization of the predictability of charge-storage ratios brought about the MTTL III family (M10). However, most conspicuous is the abundance of active elements, even in modest-performance circuits. Whereas a discrete component flip-flop may contain 4 to 8 active elements, an integrated flip-flop contains at least 30 transistors. The Level-Crossing-Detector, shown in figure III.2 as an example of IC design, comprises 11 transistors and 8 resistors, or 1.37 transistors per resistor.

Transition to Large-Scale-Integration does not provide any benefits at the circuit level. On the contrary, it imposes a number of design and fabrication constraints. Nevertheless, further circuit-research is required in order to utilize the sub-system advantages of LSI. The speed of digital modules is no longer limited by the parasitic effects of interconnection wires. It is therefore desirable to develop picosecond logic.

### Applications

Microscopic size may be the most spectacular feature of monolithic circuits, but there are other equally important characteristics. Their utility depends on applicatory requirements. To deal with LSI implementations of Servo-Control-Electronics, we have selected Aerospace applications. These applications call for a combination of features such as small size and low power consumption as well as high reliability and long-term stability, and thus display the entire spectrum of the advantages and limitations of molecular electronics (T7, J1, L5).

Current practice in servo-control-electronics is essentially restricted to analog implementations. A typical system may contain 8 integrated amplifiers, 10 discrete transistors, 6 micro-Farads of capacitors and a few discrete resistors. The quality of a set of hardware is determined by its frequency response, gain stability, offset-voltage and offset stability, general reliability, power consumption, mechanical factors and modular organization.

In typical designs, frequency response and gain-stability requirements do not present any difficulties, but offset-voltage and drift specifications do create some serious problems. We have learned to deal with thermal drift (W9, H5, T8), but we are still unable to cope with the offset-voltage and aging problems, except by MOS-chopper stabilization, a bulky and conceptually clumsy technique. Initial errors and aging effects are beyond the control of circuit designers. These are technological problems, the former being

determined by the quality of the passivation techniques (M1, M7) and the latter by the tolerances of the masking and etching processes.

The best available operational amplifiers display offsets of the order of 2 milli-Volts; aging drift of the offset voltage may exceed 5 milli-Volts per year.

Periodic adjustments constitute the only practical but highly objectionable solution of the offset-voltage problem. First, because a military system may be called to instant action after years of storage, and there may not be any time nor opportunity for extensive calibration procedures. Second, because the incorporation of adjustment accessories degrades the reliability of the system, opening a Pandora's box of failure possibilities.

Many malfunctions and catastrophic failures of electronic circuits can be attributed to accidental overloads inflicted during the performance of calibration adjustments (V3). If damage does occur, a chain reaction may follow. Undetected partial damage may induce a catastrophic failure at a later time. Detected damage may bring forth all sorts of complications invariably associated with retrofit operations.

Reliability being the most pressing issue in Aerospace electronics, it is clearly necessary to reduce offset errors to acceptable levels. Initial-offsets could be eliminated, at least in theory, by a yield trade-off, but nothing significant can be done about the long-term drift of analog circuits. At fault is the basic principle of analog circuits, the "principle of voltage proportionality."

To eliminate aging effects we must turn to the "threshold principle" of digital circuits. We can then proceed to realize the full reliability potential of LSI arrays by elimination of all unessential terminals and by provision of short-circuit protection on all interface gates. Where reliability requirements are exceptionally stringent, we can exercise the option of redundance techniques, easily implementable in digital circuits (majority voting) but unfeasible in analog circuits.

#### CHAPTER II.

### ORGANIZATION OF THE ELECTRONIC SUBSYSTEM

### Analog Systems

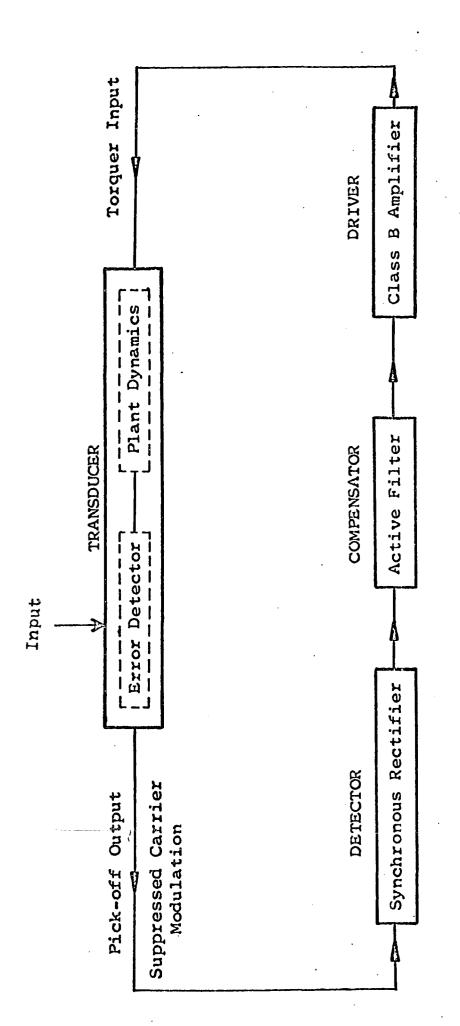

Simplicity is the dominant feature of conventional analog control systems. The electronic subsystem of a typical control-loop (Figure II.1) comprises a Detector, a Compensator and a Driver.

The detector, functionally a phase-sensitive rectifier, usually contains a push-pull amplifier, two chopper transistors, two coupling capacitors and a few discrete resistors.

The compensator may resemble the arrangement of Figure 6 of Appendix III. Its configuration depends both on the order and the values of the coefficients of the transfer function.

The driver is, as a rule, a class B amplifier; discrete power-transistors are generally used in the output section, although an experimental version of a monolithic driver had been fabricated in 1966 (R7).

Refinements may be introduced in one or more modules to comply with requirements of special applications. Where relatively sophisticated control is to be implemented or information interchange between various elements of a major installation is required, recourse can be taken to Sampled-Data techniques.

FIG. II.1: AUTONOMOUS ANALOG SYSTEM.

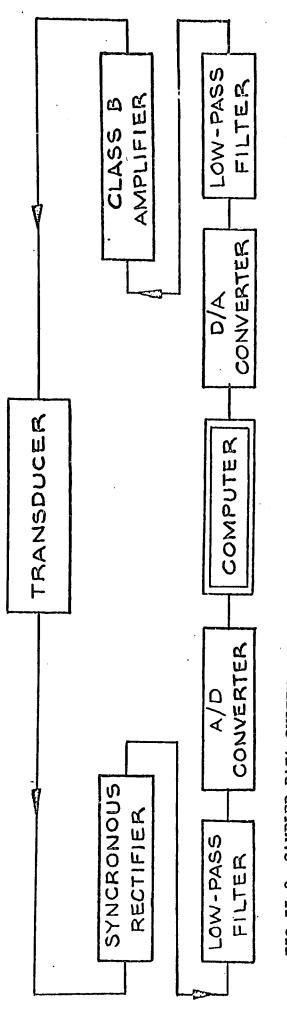

The block-diagram of a Sampled-Data-System is shown in Figure II.2. It is evident that an Analog-to-Digital converter is necessary to translate analog data into the language of the digital computer, but it is not intuitively obvious that a low-pass filter must precede the converter.

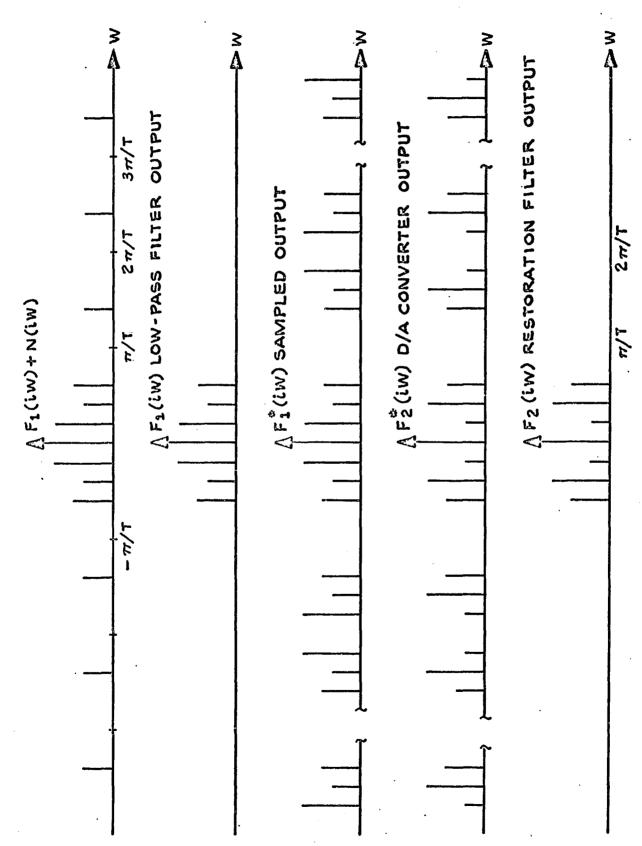

The frequency spectrum of a uniformly sampled signal (R2, P4, J2, F4) is:

$$F^*(jw) = \sum_{r=-\infty}^{\infty} F(jw + j2\pi r/T)$$

(1)

where:

F(jw) = Fourier transform of the original signal,

1/T = Sampling rate,

r = Dummy integer.

Thus, there is a simple relationship between the frequency spectrum of a sampled signal, F\*(jw), and the frequency spectrum of the original, continuous signal, F(jw), if the spectrum of F(jw) is contained within the limits:

$$|w| < \pi/T, \tag{2}$$

in other words if

$$F(jw) = 0$$

for all  $|w| > \pi/T$  (see Figure II.3). (3)

If, however,

$$F(jw) \neq 0 \text{ at any } |w| > \pi/T \tag{4}$$

then F\*(jw) becomes distorted by overlap of excess frequencies. This phenomenon, called "aliasing" (C4), necessitates the use of a low-pass filter.

FIG.II.2: SAMPLED DATA SYSTEM.

FIG. II.3: THE SAMPLING-PROCESS SEQUENCE

Theoretically speaking, the low-pass filter would not be necessary if the input signal was known to be contained within the fundamental band defined by equations (2) and (3). However, in engineering deliberations one must recognize the existence of noise, and look upon equation (1) as a demonstration of noise-susceptibility. Although low-frequency noise is expanded in the same fashion as the signal, aliasing of high-frequency noise increases the noise-energy-content of the fundamental band. It is, therefore, necessary to use the low-pass filter in all practical applications.

The Central Computer of the system, performing the function of a presumably complex compensator, transforms  $F^*(jw)$  into another function  $G^*(jw)$ , in accordance with some predetermined equations.

To examine the restoration process, we observe that elimination from G\*(jw) of all frequencies outside the fundamental band enables us to equate the Fourier-Integral representation (G(jw)) with the corresponding Fourier-Series representation and thus to arrive at the identity:

$$g(t) = \sum_{k=-\infty}^{\infty} g(kT) \frac{\sin \pi (t - kT)/T}{\pi (t - kT)/T}$$

(5)

where:

$$G(jw) = 0 \text{ for all } |w| > \pi/T$$

(6)

G(jw), g(t) are Fourier integral pairs

k = Dummy integer

Equation (5), known as the Sampling-Theorem (S1, S7, L1), explains the need for the restoration filter at the output end of the D/A converter. It contains the essence of all SDS operations, and states that a function g(t) is uniquely represented by its values at uniformly spaced instants, provided that G(jw) complies with equation (6).

The events which take place during the execution of a sampling cycle are portrayed in Figure II.4. A somewhat artificial example has been chosen for the sake of clarity.

Summarizing this section we recall the simplicity and component-economy of self-contained analog control-loops. We also note that extension of analog concepts to Sampled-Data-Control introduces a number of complications, resulting from the basic incompatibility of digital and analog techniques.

# Digital Systems

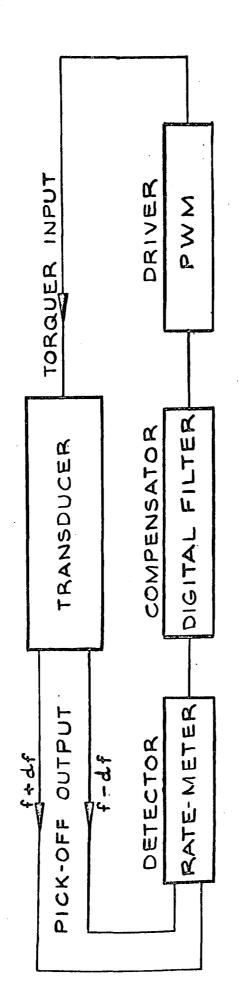

Figure II.4 shows the block diagram of a self-contained digital loop. As in the corresponding analog system, there are three functional modules, a Detector, a Compensator and a Driver. The operation of the three modules is coordinated by a system clock which is usually contained within the central-computer complex.

The circuit arrangement of the electronic detector depends on the principle of operation of the transducer. In some cases the detector can be omitted entirely, in others it may be sufficient to provide a code converter. The error detector of the transducer

FIG.II.4: AUTONOMOUS DIGITAL SYSTEM.

considered in this thesis is assumed to respond in the differential-frequency-modulation mode, generating two signals, one characterized by the frequency  $f_0$  + df and the other by  $f_0$  - df. The electronic detector takes, therefore, the form of a differential ratemeter. Its output is proportional, or nearly proportional, to the deviation ratio  $df/f_0$ .

The configuration of the remaining two modules is independent of the error detection mechanism. The compensator may contain canonical pole-zero elements (D1), or a Kalman filter, or both. The topological complexity of the driver depends on linearity specifications but the proposed PWFM driver will meet all rational requirements.

Structural details of the three modules are discussed in Chapters III to V. Implementation of any one of these modules requires far more components than the implementation of an entire analog system, but the quality of the digital components need not be as high as the quality of the analog components.

The block-diagrams of two computer-aided control systems are given in Figure II.5. In Figure II.5a, all compensation functions are performed by the central computer. In Figure II.5b, the central computer controls the operation of the local compensator by periodic adjustment of its coefficients (Chapter IV).

The simplicity of the computer-aided arrangements stands in striking contrast to the complexity of Sampled Data Systems, which

FIG. II. 5a: COMPUTER AIDED DIGITAL CONTROL.

FIG.II.5b: ADAPTIVE LOOP.

carry the burden of conceptually redundant hardware. All digital modules can be completely compatible. There need not be any difference between Ratemeters for autonomous loops and Ratemeters for computer-aided loops. The same applies to Drivers and other auxiliary equipment.

# The Digital vs. Analog Decision

The main arguments in favor of digital techniques in servocontrol-electronics can be listed as follows:

- 1. Compatibility with the general trend in control theory.

- 2. Reliability and immunity to moderate aging effects.

- Compatibility with the state of the art in Silicon Technology.

- 4. Simplicity of Adaptive-Control implementations.

There are two significant arguments for analog techniques, namely tradition and component economy.

Although some of the disadvantages of analog implementations are sufficiently severe to disqualify analog concepts from all LSI considerations, it would be unwise to overlook the possibility of compromise solutions. We cannot ignore the question of current practice in servo-control electronics. To present a complete argument in favor of digital techniques, we must explain why analog techniques are being used at present.

Component economy is the main reason behind the past and present popularity of analog implementations. The analog double-pole,

double-zero active filter of Figure 6 of Appendix III consists of one amplifier, two capacitors and five resistors. An equivalent 11-bit digital filter would require twenty-two Delay Flip-Flops, two 11-bit, 4-input adders and five 11-bit multipliers; evidently, realization of such filters in terms of discrete transistors is unfeasible, except for demonstration purposes. The choice between digital and analog hardware was only brought about by the emergence of integrated circuits.

The criterion of component economy, which dominated the approach to circuit design until recently, has been deflated by LSI; more important are the questions of component quality, margins against malfunctions and susceptibility to parasitic oscillations (C1, P5).

Where reliability, long-term stability or sophistication are important, digital LSI presents the only rational solution. Analog techniques will be used in various hybrid implementations of non-critical systems for a few years to come, but they will be eventually eliminated by economic factors, even from these applications.

The remainder of this thesis will be devoted to the realization of ratemeters, digital-filters and pulsed drivers, with particular attention to applicatory diversity and modular compatibility.

#### CHAPTER III

# DIGITAL DETECTORS

# Principle of Operation

The digital detector generates a binary output in response to two sinusoidal or square-wave inputs. The output of the detector represents the frequency-deviation-ratio of the input signals.

The principle of operation of the proposed detector is portrayed in Figure III.1.

Two input signals, characterized by frequencies  $f_0$  + df and  $f_0$  - df, are respectively fed into two Level-Crossing Discriminators (LCD-A and LCD-B). The discriminators generate two pulse trains, one at a repetition rate of  $2(f_0 + df)$  and the other at  $2(f_0 - df)$ .

While the Inhibit-Gates (F3, H7) are open, the pulses flow into two counters (P8, G1) until saturation occurs in the counter with the faster input. The saturation event shuts the Inhibit-Gates; it also feeds the complement of the other counter into the Output-Register.

Assuming relaxation of both counters at t = 0, the overflow event will occur at time

$$t_x = \frac{N}{2(f_0 + df)} = \frac{N}{2f_0(1 + x)}$$

(1)

where:

$$N = 2^n - 1 =$$

Capacity of each of the counters. (2)

n = Number of storage elements in each counter.

$$x = df/f_0 = Frequency-deviation ratio.$$

(3)

The state of the other counter at time  $t_{\rm X}$  is

$$m = 2t_x(f_0 - df) = 2t_xf_0(1 - x)$$

$$= N \frac{1-x}{1+x} \tag{4}$$

The complement of m is equal to  $\bar{m}$ ,

$$\bar{\mathbf{m}} = \mathbf{N} - \mathbf{m} \tag{5}$$

$$= 2xN/(1+x) \tag{6}$$

or,

$$x = \frac{\bar{m}}{2N(1 - \bar{m}/2N)} \tag{7}$$

Equations (6) and (7) give the relationship between x, the frequency-deviation-ratio, and  $\overline{m}$ , the output read-out of the detector. At low deviation ratios, the read-out is proportional to x,

$$\bar{m} = kx \qquad (x << 1) \tag{8}$$

Noteworthy is the fact that  $f_0$  appears in equation (6) only in the form of the deviation ratio  $df/f_0$ . This means that the read-out of the ratemeter is independent of  $f_0$ , if the sensitivity of the transducer is independent of  $f_0$ .

# The Level-Crossing-Discriminator

The schematic diagram of a new type of Level-Crossing-Discriminator is presented in Figure III.2.

FIG.III.2: LEVEL CROSSING DISCRIMINATOR

Transistor  $Q_1$  conducts whenever the input voltage exceeds  $V_1$ , transistor  $Q_2$  conducts when the input voltage drops below  $-V_1$ . Thus, the voltage at the common collector of  $Q_1$  and  $Q_2$  is low, except when the input voltage falls within the limits:

$$-v_1 < v_{in} < +v_1 \tag{9}$$

The output voltage  $(V_0)$  conforms, therefore, with the following equations:

$$V_{o} = Low, \text{ when } V_{in} > |V_{1}|$$

(10)

$$V_0 = High, \text{ when } -V_1 < V_{in} < +V_1$$

(11)

Under normal operating conditions, the amplitude of the input signal is considerably larger than  $V_1$ . Consequently, a positive output pulse is produced whenever the input signal crosses zero in either direction. The output pulses are centered on  $V_{in} = 0$ . Their width depends on the amplitude and shape of the input signal.

Compared to conventional Sense-Amplifiers (T1, T2, W10), the proposed LCD has two advantages. It has a better time-resolution, since it generates output pulses both at the positive-going and at the negative-going crossings of the zero-voltage level. Also, it produces pulses of optional width instead of the square-waves associated with Sense-Amplifiers.

The schematic diagram of the LCD discloses a few features which are peculiar to Integrated-Circuit designs. It has 8 resistors and 11 transistors, or less than one resistor per transistor. The common-collector devices  $Q_1Q_2$  and  $Q_3Q_4$  combine surface-area economy

with metallization-pattern simplicity. The current sources  $Q_5$  and  $Q_6$  are controlled by the emitter-collector voltage of a transistor  $(Q_8)$  whose base is shorted to the collector. The compound emitter-follower  $(Q_9 - Q_{10})$  overcomes the beta limitations of lateral pnp transistors.

The above LCD is intended only for operation with sine-wave inputs. In applications utilizing square-wave inputs, the LCD would be omitted or replaced by some pulse-shaping network, if necessary.

#### The Ratemeter

The block diagram of the ratemeter section of the detector is given in Figure III.3. It shows a half-adder (P9), some control logic and two counters.

The operational cycle of the ratemeter can be broken down into three action periods:

- 0,1 The externally controlled "synchronization pulse" resets the counters and enables input gates G1 and G2.

- 0,2 Incoming pulses are fed into the counters.

- 0,3 At  $t = t_x$ , one of the counters saturates (minterm =  $2^n 1$ ), inhibiting the input gates.

- 1,1 At t = T, the "synchronization pulse" initiates the next

operational cycle.

During the time interval from  $t_{\rm X}$  to T, gate Kl is in the "true" state, thus indicating the availability of output data. The Boolean equation of Kl is:

FIG.III.3: THE RATEMETER

$$K1 = \prod_{i=1}^{n} A_i + \prod_{i=1}^{n} B_i$$

(12)

The inhibit flip-flop is controlled by Kl and the external synchronization pulse K2, in accordance with the equations

$$S = K1\bar{K}2 \tag{13}$$

$$R = K2 \tag{14}$$

The half-adder is used for two's-complement coding of negative deviation ratios. To unravel the coding mechanism, assume that df, as shown in Figure IIL 3, is negative.

In a normal operating cycle counter A will saturate first, forcing gate  $F_{n+1}$  into the true state and thus indicating that the deviation ratio is negative.

Gates  $F_1$  to  $F_n$  are then supposed to display the negative equivalent of the complement of the state of counter B. In other words, we want the two's-complement of

$$\overline{B}_n$$

$\overline{B}_{n-1}$   $\overline{B}_{n-2}$  ...  $\overline{B}_2$   $\overline{B}_1$ .

The one's-complement of the above number is obviously given by

$$B_n B_{n-1} B_{n-2} \dots B_2 B_1.$$

To get the two's complement code, we add unity to the minterm of B, and thus obtain:

$$minterm(E) = minterm(B) + 1$$

(15)

The problem of selecting the output information from either channel A or channel B does not exist, since all  $A_i$ s are zero when any of the  $E_i$ s are different from zero, and vice versa. We can thus

combine them by simple "or" gates, operating in accordance with the Boolean equation (T5, S4, C8, F3)

$$F_{i} = \overline{A}_{i} + E_{i} \tag{16}$$

Although  $f_0$  does not enter into equation (6), it is necessary to impose certain restrictions on the values of  $f_0$  and T, in order to ensure proper operation of the ratemeter. Obviously,  $t_X$ , the time to load the counter, must be shorter than T, the period of the synchronization pulses. Hence,

$$T > 2^{n}/f_{o} \tag{17}$$

for ratemeters working in conjunction with conventional sense amplifiers and

$$T > (2^{n-1})/f_0$$

(18)

for ratemeters working in conjunction with the LCD.

The proportionality-error in equation (8) must be considered in relation to the quantization-error, which is equal to the least-significant-bit of the output word. The transient behavior of the ratemeter resembles the behavior of a low-pass filter with a cut-off frequency of 1/T.

The above proposed detector can be used as a mixer-detector of conventional FM data, if a Local Oscillator is added to the arrangement of Figure III.1. The frequency deviation ratio of single channel FM signals is equal to

$$x = \frac{\bar{m}}{N(1 - \bar{m}/N)} \tag{19}$$

#### CHAPTER IV

#### DIGITAL COMPENSATORS

Digital processing resembles the sampling operation. Both techniques are discrete-time procedures which handle data collected at specific instants of time. The clock period of digital systems corresponds to the sampling period of sampled-data systems.

It is, therefore, convenient to apply to digital systems the difference-equation and Z-transform methods, which are generally used in sampled-data systems.

# The Canonical Filter

A difference equation of the type

$$(1 + b_1 E^{-1} + b_2 E^{-2} + \cdots + b_n E^{-n})y = (a_0 + a_1 E^{-1} + \cdots + a_m E^{-m})x$$

where:

$$E^{-1} = Delay Operator$$

(1)

can be implemented as shown in Figure IV.1. It can also be written as

$$y = \frac{A}{B} x \tag{2}$$

and expanded by introduction of an intermediate variable w, such that

$$w = \frac{x}{B}$$

(3a)

$$y = Aw (3b)$$

EQUATION V.1 ր. 0 FIG.IV.1: IMPLEMENTATION

Development of equations (3) and (4) gives

$$w = x - (b_1 E^{-1} + b_2 E^{-2} + \dots b_n E^{-n})w$$

(4)

$$y = (a_0 + a_1 E^{-1} + a_2 E^{-2} + a_m E^{-m})w$$

(5)

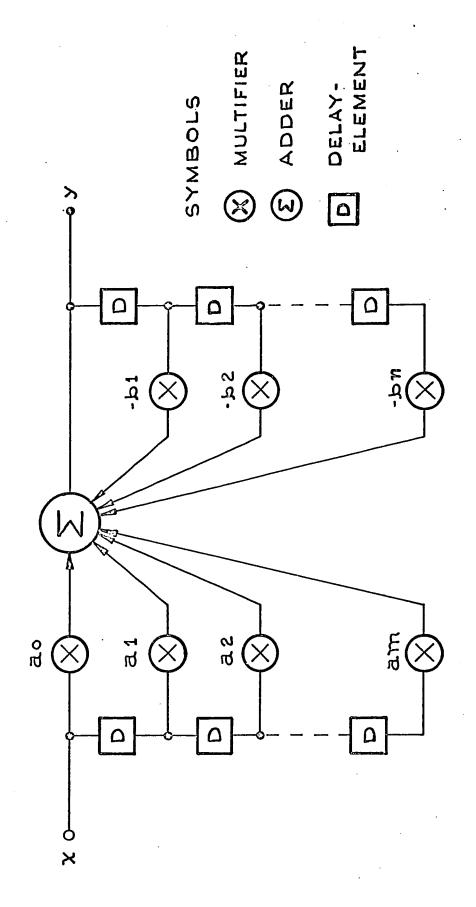

Equations (4) and (5) suggest the implementation of Figure IV2, sometimes called the "canonical filter" (D1, C5) because it employs the minimal number of delay elements.

Examining Figures IV.1 and IV.2, we discern three basic components of digital filters namely delay-elements, multipliers and adders.

There is a good deal of freedom in the design of digital-filter hardware. First, there is the option of series or parallel arithmetic and second, there are many logic elements which, properly combined, will perform the functions of the basic filter-components.

In LSI implementations of small systems, parallel arithmetic is preferable. Thus, a third-order 12-bit filter would comprise thirty-six 1-bit delay elements, two 4-input 12-bit adders and seven 12-bit multipliers.

Shift-registers or flip-flops can be used as the delay-elements of the filter. Any flip-flop will serve the purpose, but D flip-flops offer the convenience of single-line inputs.

The organization of the Adders depends on the speed requirements. Ripple-propagation carry is acceptable in slow machines, but various look-ahead carry-propagation schemes (F3) are employed in

FIG.IV.2: TRIPLE POLE /ZERO DIGITAL FILTER

fast machines. Servo-control electronics generally fall into the former category; ripple-propagation carry should, therefore, suffice.

Multipliers are the most critical components of digital filters. They determine the versatility of the entire filter. Note that the configuration of the filter (Figure IV.2) is independent of the coefficients of the transfer function; it depends only on the order of the transfer function. The coefficients show up in the Multipliers and nowhere else.

It may be advisable to elaborate on this statement with regard to the order of the transfer function. To realize a third order function, we need three Delay-Elements, but a second order function can be generated by the same filter, if we include "zero" among the possible values of a<sub>3</sub> and b<sub>3</sub>. Thus an n-th order filter will take care of all transfer functions of order n and less than n.

The versatility of digital filters stands in vivid contrast to the restrictive nature of analog filters.

Appendix III demonstrates some of the limitations of analog implementations. Equations (14) and (17) of Appendix III state the realizability conditions imposed on the coefficients of the transfer function by the configuration of Figure 6. To be reasonably rigorous, we would have to go one step further and determine the Bode-Sensitivity (B8) as the dependent variable of the coefficients of the transfer function. Sensitivity is in fact one of the reasons

behind the demand for comparative evaluation of alternative realizations of transfer functions (Appendix III and references S5, S6).

Returning to the multipliers we observe that we want the product of a variable and a constant

$$\mathbf{u}_{\mathbf{i}}(\mathbf{n}) = \mathbf{k}_{\mathbf{i}}\mathbf{w}_{\mathbf{i}}(\mathbf{n}) \tag{6}$$

This operation could be easily performed by primitive logic or a few shift-registers in combination with an adder. However, when designing LSI electronics, we must attempt to retain the intrinsic versatility of the digital-filter concept, in order to comply with the mass-production requisites of our technology. We turn, therefore, to "Read-Only-Memories" (ROMs) for the implementation of multipliers.

The fabrication and the principle of operation of solid-state ROMs are discussed in references B11 and N1. These devices are produced in large quantities in the form of "master-dice." Some custom processing of the dice is necessary, but its extent is limited to a metallization operation which determines the contents of the memory.

In our application, we use the independent variable  $w_i(n)$  as the address and obtain the dependent variable  $u_i(n)$  as the output of the memory. The constant multiplier  $k_i$  designates the contents of a given memory. Thus, in response to the address w(n), a ROM labeled  $k_r$  will produce an output  $k_rw(n)$  and a ROM labeled  $k_s$  will produce

the output  $k_Sw(n)$ . To change the transfer function, we simply discard the old set of memories and insert a new one in its place.

The above discussion leads us into the topic of Adaptive-Filter hardware. Reverting to Figure II.5b, we consider the problem of modification of transfer functions under the control of commands from the central computer.

One solution is self-evident: we equip the filter with a few sets of memories and allow the computer to select the appropriate set.

Limited in scope as this method appears to be, it provides an answer to a real problem. As a missile moves through space its dynamics change because of variations in the density of the surrounding atmosphere and because of loss of balast due to expenditure of fuel. It is therefore necessary to have a repertoire of three or four transfer functions of the same basic structure, but slightly different coefficients. The selective-multiplier filter, proposed above, will provide these facilities.

The versatility of the adaptive process can be improved by a different realization of the multipliers. We consider the product

$$u_{\mathbf{i}}(\mathbf{n}) = k_{\mathbf{i}}(\mathbf{n})w_{\mathbf{i}}(\mathbf{n}) \tag{7}$$

where  $w_1(n)$  is the original multiplicand of equation (6), and  $k_1(n)$  is a variable multiplier. To implement equation (7), we provide a compound multiplier to handle two variables and a Multiplier-Register

to store the number  $k_1$ . The contents of the Multiplier-Register can be updated by the central computer, when necessary.

Concluding this section, we observe once more the great versatility of digital-filters. The canonical filter configuration can be used for all rational transfer functions; implementation of adaptive filtration is equally simple.

# The Digital Integrator

Our list of filter elements comprises three basic components, called the Adder, the Delay-Element and the Multiplier. It is expedient to add to this list one derived component, namely the Integrator.

To clarify the meaning of digital integration, let the level of data on a particular line be

$$f(0), f(1), f(2), \dots f(n), \dots$$

(8)

at instants

$$0, 1, 2, \ldots, n, \ldots$$

(9)

Take a function g(n), such that

$$g(n-1) = f(0) + f(1) + f(n-1)$$

(10)

$$g(n) = f(0) + f(1) \dots + f(n-1) + f(n)$$

(11)

$$g(n+1) = f(0) + f(1) + f(n-1) + f(n) + f(n+1)$$

(12)

The function g(n), defined by equation (11), is the digital integral of the sequence f(n).

To attain some proficiency in the manipulation of the digital integral, we refer to Figure IV.3 and write the sequence f(n) as

$$f(n) = f(t)\delta(t) + f(t)\delta(t-1) + ... f(t)\delta(t-m) ...$$

(13)

where:

$\delta(t)$  = Dirac's delta-function.

Equation (13) is equivalent to the expression:

$$f(n) = f(0)\delta(t) + f(1)\delta(t-1) + ... f(m)\delta(t-m) ...$$

(14)

It is, therefore, evident that f(n-1) can be written as

$$f(n-1) = f(0)\delta(t-1) + f(1)\delta(t-2) ... + f(m-1)\delta(t-m) ...$$

(15)

$$= E^{-1}f(n) \tag{16}$$

where:

$E^{-1} =$ The Delay-Operator

In all of the above operations we have tacitly assumed that f(n) is equal to zero at negative values of t. We will obviously design our hardware to behave accordingly; philosophical niceties do not enter into the argument.

The transfer function, H(n), of the integrator can be obtained by subtraction of equation (10) from equation (11):

$$g(n) - g(n-1) = f(n)$$

(17a)

or, in accordance with equation (16),

$$g(n)(1 - E^{-1}) = f(n)$$

(17b)

FIG.IV.3: SHIFTING OF A DISCRETE-TIME FUNCTION

Hence:

$$\frac{g(n)}{f(n)} = H(n) = \frac{1}{1 - E^{-1}}$$

(18)

Utilization of the digital integrator in function generators and frequency modulators will be demonstrated below.

# The Z-Transform and the State-Space Representation

Mathematical details of the Z-transform are discussed in references L7, F4, A3 and practically all textbooks on transform calculus. For our purpose it is sufficient to associate the z-variable with the exponential of the Laplacian s-variable ( $e^{sT}$ ). Let f(t) be a continuous well behaved function and let us expose it to uniform sampling. The sampled function  $f^*(t)$  can be written as:

$$f^*(t) = \sum_{m=0}^{\infty} \int_{0}^{\infty} f(t)\delta(t - mT)dt$$

(19)

where:

$\delta(t)$  = Dirac's delta function

1/T = Sampling rate

m = Integer

The Laplace transform of f\*(t) is:

$$F(s) = \int_{0}^{\infty} f^{*}(t)e^{-st} dt$$

(20)

$$=\sum_{m=0}^{\infty} f(mT)e^{-smT}$$

(21)

Substitution "z" for " $e^{ST}$ ," we obtain the Z-transformation,

$$F(z) = \sum_{m=0}^{\infty} f(mT)z^{-m}$$

(22)

depicted in line 5 of Figure IV.3.

Of immediate interest in filter work is the transform of the delayed function f(t-T). By reference to line 3 of Figure IV.3 and the reasoning employed in the derivation of equation (16), we find that

$$Z[f(t-T)] = z^{-1}F(z)$$

(23)

Comparing equation (23) with equation (16), we conclude that  $z^{-1}$  can be identified with  $E^{-1}$ , for the purpose of digital-filter synthesis.

It does not make any difference whether a rational transfer function is written as  $H(z^{-1})$  or  $H(E^{-1})$ ; any set of components and any configuration which satisfies one of these expressions also satisfies the other.

Flow diagrams in State-Space variables differ from the corresponding block diagrams of digital filters only in symbolism and terminology. A weighted link in the former is a multiplier in the latter, while a node is equivalent to an adder and the delay-elements are the same in both interpretations.

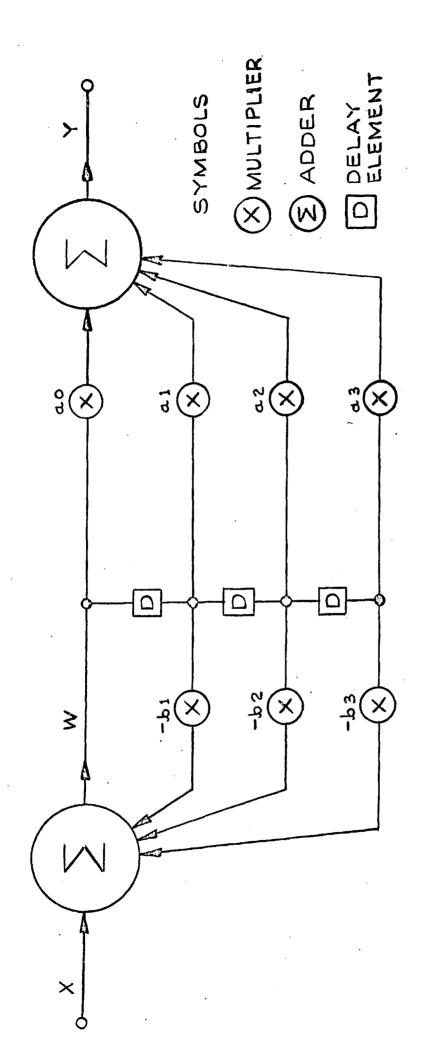

Figure IV.4 shows the flow diagram and the schematic circuit of the equation:

# a) FLOW DIAGRAM

b) COMPONENT DIAGRAM

FIG.IV. 4: EQUATION V.25 IN STATE SPACE AND COMPONENT DIAGRAM REPRESENTATION

$$y(n) + b_1y(n-1) + b_2y(n-2) + b_3y(n-3) =$$

$$= a_0u(n) + a_1u(n-1) + a_2u(n-2)$$

(24)

State-Space interpretations are not unique. As with the previously discussed representations, there are many options. One convenient variation is shown in Figure IV.4. It is based on the following set of matrix equations:

$$\begin{bmatrix} x1(n) \\ x2(n) \\ x3(n) \end{bmatrix} = \begin{bmatrix} -b_1 & 1 & 0 \\ -b_2 & 0 & 1 \\ -b_3 & 0 & 0 \end{bmatrix} \begin{bmatrix} x1(n-1) \\ x2(n-1) \\ x3(n-1) \end{bmatrix} + \begin{bmatrix} a_0 \\ a_1 \\ a_2 \end{bmatrix} u(n)$$

$$y(n) = x1(n)$$

(25)

Although one could standardize State-Space interpretations around Jordan's canonical matrices, no practical advantages would be derived therefrom. It is easier to transform from State-Space to a difference equation and then to the canonical filter of Figure IV.2.

# Digital Differential Analyzer Implementations

Block diagrams of Digital Differential Analyzers (DDAs) resemble Analog Computer diagrams. DDA hardware resembles the digital filter components discussed in the preceding sections of this chapter.

Originally considered to be economical substitutes for regular digital computers, DDAs have been used occasionally as small, special-purpose machines. However, research-work in DDAs has been overshadowed by rapid progress in the development of conventional computers.

The emergence of the LSI technology will stimulate further development of DDA techniques. LSI facilitates decentralization of control-installations and generally favors small-system implementations. In their own right, DDAs have the advantage of compatability with Delta-Modulation (S8, P2, A1), which is increasingly used in aircraft navigation. Furthermore, they can be used to advantage in Kalman Filters, since they are very effective in the solution of linear and non-linear differential equations.

To illustrate the programming of DDAs, let us take Riccati's equation with constant coefficients:

$$y'' + ay' + by^2 = f(x)$$

(28)

Transformation of equation (28) into the form

$$d(\frac{dy}{dx}) = -a(\frac{dy}{dx})dx - by^2dx + f(x)dx$$

(29)

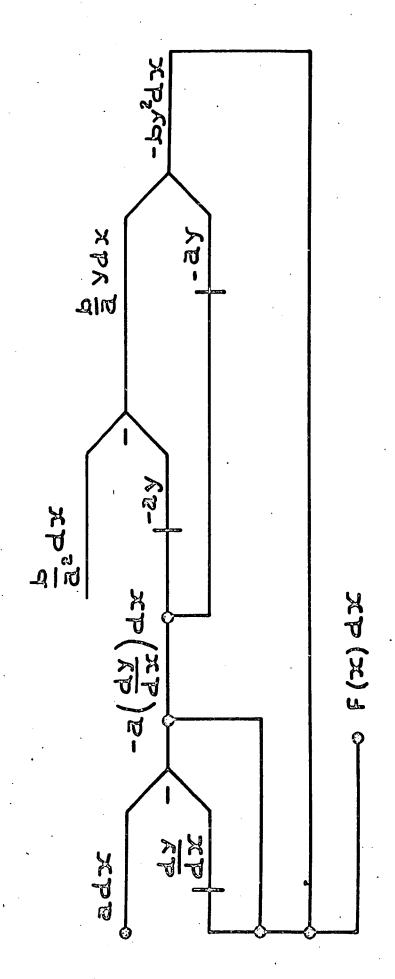

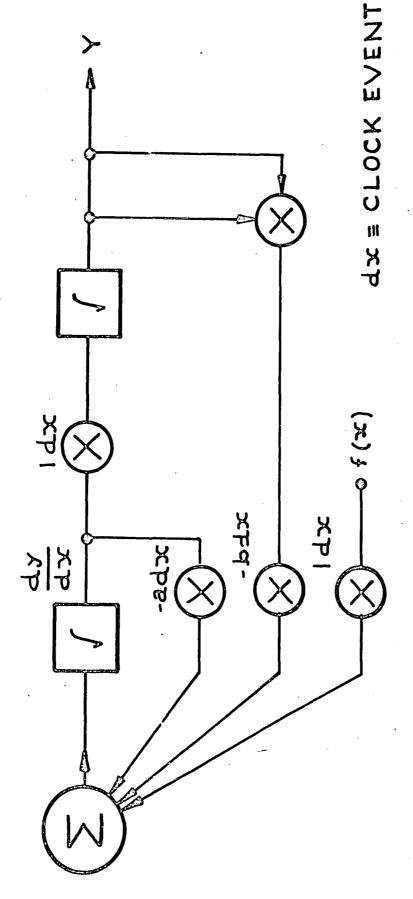

explains the derivation of the block diagram of Figure IV.5a. Figure IV.5b depicts the same equation in the symbolism employed by Monroe (M9).

Monroe and other writers (M4, S8) use DDA blocks of one type only, while we employ the integrator and all basic digital-filter components. The former approach is directed at the user of DDA hardware; our method is clearer and more flexible from the standpoint of the designer of digital-filter components.

The application of Integrators to Pulse-Width-Frequency-Modulation is illustrated in Chapter V. The scaling and design of DDA systems is discussed in reference M4.

FIG.IV. 5a: IMPLEMENTATION OF EQUATION IV.28

WITH DDA ELEMENTS.

FIG.IV.5b: IMPLEMENTATION OF EQUATION 28

WITH STANDARD FILTER COMPONENTS.

# Realization of Optimal Filters

The design of digital electronics generally allows for adequate margins against all reasonable noise phenomena. Nevertheless, some filtration may be necessary to cope with noise generated within the analog section (transducer) of a control system.

In simple cases, noise-effects can be taken into account in the design of the compensator. In complex cases, a separate module, designed around optimal-filtration principles, may be necessary.

Literature on optimal filters is still limited to computer algorithms for the optimization of stochastic data. This does not fulfill our requirements. We must go a step further in order to utilize LSI for the implementation of optimal filters. We will take, therefore, the best known filter algorithm (K1, H3, R5) and attempt to adapt it to our needs. We will examine Kalman's equations in order to: 1) reveal their physical meaning, 2) introduce some engineering simplifications and 3) justify the format of the covariance equation.

The following section is not self-contained. It should be read in conjunction with reference Kl.

Kalman's filtering algorithm is derived in the fifth section (Solution of the Wiener Problem) of his paper. 1

<sup>&</sup>lt;sup>1</sup>R. E. Kalman, "A New Approach to Linear Filtering and Prediction Problems," <u>ASME Transactions</u>, vol. 82, part B, March 1960, pp. 35-45, Ref. K1.

He deals with a dynamic model described by the following set of discrete-time vector-equations:

$$x(t + 1) = \phi(t + 1; t)x(t) + u(t)$$

K(16)

$$y(t) = M(t)x(t) K(17)$$

where:

x(t) = State variables of random process (unobservable).

y(t) = Observable random variables.

$\phi(t + s; t) = Transition matrix (deterministic).$

M(t) = Transformation matrix (deterministic).

The problem of Kalman's paper is formulated as follows: "Given the observed values of  $y(t_0)$ , ..., y(t) find an estimate  $x*(t_1|t)$  of  $x(t_1)$  which minimizes the expected loss."

A partial solution of the problem is given by equations (21) and (22) of the above reference:

$$x*(t + 1|t) = \phi*(t + 1; t)x*(t|t - 1) - \Delta*(t)y(t)$$

K(21)

$$\phi^*(t+1;t) = \phi(t+1;t) - \Delta^*(t)M(t)$$

K(22)

where  $\Delta^*$  is a deterministic matrix which will be determined later.

Some insight into the meaning of the above two equations can be gained by combining them as follows:

$$x^{*}(t+1|t) = \phi(t+1;t)x^{*}(t|t-1) + \Delta^{*}[y(t) - Mx^{*}(t|t-1)]$$

$$= \phi(t+1;t)x^{*}(t|t-1) + \Delta^{*}[y(t) - y^{*}(t|t-1)]$$

(31)

where:

y\*(t|t-1) = Predicted value of y(t); an estimate based on the information available at t - 1.

Equation (31) shows that the estimate of x(t + 1) is given by the sum of two terms. The first term,

$$u = \phi(t + 1; t)x*(t | t - 1)$$

(32)

is the updated value of the previous best estimate, i.e. an estimate of x(t+1) based on information available at t-1. The second term,

$$v = \Delta^*[y(t) - y^*(t|t-1)]$$

(33)

is a correction deducted from the information which became available at event t. It is the weighted difference of the actual reading y(t) and the projected reading y\*(t|t-1).

Equations (31) through (33) deserve some elaboration. Since the transition matrix  $\phi(t+1|t)$  is deterministic, we do not detract from the generality of the stochastic considerations by assumption of a unitary  $\phi$ . We can then write

$$x^*(t+1|t) = x^*(t|t-1) + R[x(t) - x^*(t|t-1)]$$

(34)

where:  $R = \Delta * M$ .

Equation (34) tells us that the best estimate of x(t + 1) after t observations is equal to the best estimate of x(t) after t - 1 observations plus the weighted difference of the observed and estimated values of x(t).

This is an intuitively obvious result. It resembles the conventional procedure for prediction of a stochastic variable on the basis of gradual influx of data. It is closely related to Bellman's Principle of Optimality and Swerling's approach to data-smoothing (S12).

Equation (30) could be taken as the starting point of the derivation

of optimal filters. The essential problem is the derivation of the matrix  $\Delta^*$ , regardless of the preliminary steps.

Returning to Kalman's paper, we note that

$$\widetilde{x}(t+1|t) = \phi * \widetilde{x}(t|t-1) + u(t)$$

K(23)

where:

$\tilde{x}(t_1|t) = \text{Error in the optimal estimate of } x(t_1) \text{ at event time } t.$   $\phi^* = \phi - \Delta^*M$

The covariance matrix P\*(t + 1) is defined as the expectation of the dot product of  $\tilde{x}(t + 1|t)$ :

$$P^*(t+1) = E\tilde{x}(t+1|t)\tilde{x}'(t+1|t)$$

(35)

where:

E(x) = Expectation of x

x' = Transpose of x

Substitution of equation K(23) into equation (35) yields:

$$P^*(t+1) = \phi^*(t+1;t)P(t)\phi^{*'}(t+1;t) + Q(t)$$

(36)

where:

$$Q(t) = Eu(t)u'(t)$$

Kalman's result of the same operation is stated as:

$$P^*(t+1) = \phi^*(t+1;t)P(t)\phi'(t+1;t) + Q(t)$$

K(24)

Subtracting equation K(24) from (35), we obtain the difference V,

$$V = [\phi(t + 1; t) - \Delta^*(t)M(t)]M'(t)\Delta^*'(t)$$

(37)

Since we cannot explain the above discrepancy with the available equations, we proceed to equation K(25) and the derivation of  $\Delta$ \*.

Kalman obtains  $\Delta$ \* from the orthogonality between

$$x(t+1) - \Delta * \tilde{y}(t|t-1)$$

and  $\Delta * \tilde{y}(t|t-1)$ , by writing:

$$E[x(t + 1) - \Delta * \tilde{y}(t | t - 1)] \tilde{y}'(t | t - 1) = 0$$

He thus arrives at:

$$\Delta^*(t) = \phi(t + 1; t) P^*(t) M'(t) [M(t) P^*(t) M'(t)]^{-1}$$

K(25)

Substitution of equation K(25) into (37) discloses the identity V = 0. One can, therefore, assume that Kalman tacitly anticipated equation K(25), in his derivation of P\*(t+1).

The optimal estimate of x(t + 1) can now be expressed as follows:

$$x^{*}(t+1|t) = \phi(t+1;t)\{x^{*}(t|t-1) + R(t)[y(t) - M(t)x^{*}(t|t-1)]\}$$

(37)

$$R(t) = P(t)M'(t)[M(t)P(t)M'(t)]^{-1}$$

(38)

$$P(t+1) = \phi\{P(t) - R(t)M(t)P(t)\}\phi' + Q(t)$$

(39)

The implementation of the above principles must necessarily depend on the complexity of the control installation.

Where there are many observables (y), co-ordination of operations by the Central Computer is necessary. Also, the solution of equations (37) through (39) is fairly complex (f1). One would, therefore, use the Central Computer for the execution of all calculations involved in the above Optimal-Estimate algorithm.

In self-contained loops, similar to those depicted by Figure

II.4, there is only one observable. The matrix M(t) is, therefore,

a row-matrix and the product M(t)P(t)M'(t) is a scalar. This simplifies equation (38) by elimination of the matrix inversion operation.

To detect further simplifications, note that although  $\phi$  and P vary with time, they are not affected by the observable y. The covariance P(t) depends only on time and P(0), a pre-wired estimate of the initial errors. Note also that in practical cases M is a constant matrix, not M(t) as generalized by Kalman.

Thus, it is feasible to use pre-calculated sequences of numbers for  $\phi(t)$  as well as P(t), if the asymptotic values of these quantities can be reached in a reasonable number of steps. A Read-Only-Memory, equipped with a program counter, will supply the necessary data at the appropriate time.

Where the dynamics of the system vary with time as described on page 42, different sets of memories can be selected by commands from the Central Computer.

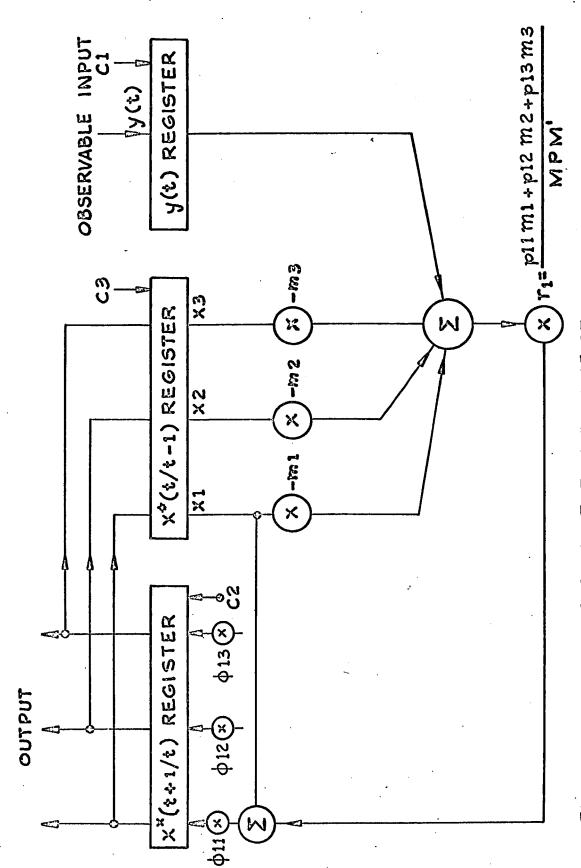

Figure IV.6 depicts the implementation of the xl(t + 1 | t) component of a third order system. Quite a few elements are required. Discrete-transistor hardware would be awkward, but LSI implementations are easily realizable. Thus, single-observable Kalman filters can be implemented without recourse to central-computer calculations; LSI enables us to perform the pertinent operations in situ.

FIG.IV.6: IMPLEMENTATION OF EQUATION V.37

#### CHAPTER V.

#### DRIVERS AND PULSE WIDTH-FREQUENCY MODULATION

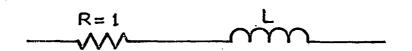

Linearity and efficiency are important characteristics of power-drivers (W8). The linearity of the driver affects the dynamics and the accuracy of the entire system. Efficiency determines the excess power. Low efficiency calls for heat-dissipation accessories, while it imposes unwarranted demands on the batteries and other sources of energy.

Both of the above characteristics are particularly important in Aerospace applications. In a typical mission, the short-duration maneuver requirements are orders of magnitude higher than the prolonged stady-flight torquing-requirements.

In a discussion of efficiency (E), one must be guided by the overall efficiency  $(\bar{E})$ .

$$\tilde{E} = (1/T) \int_{0}^{T} E[i(t)]dt$$

(1)

where: E[i(t)] = Efficiency as a function of load current,

T = Mission time,

or simply ask for high efficiency at all power levels.

Class B modulation is obsolete, by now, because it is inefficient at fractional loads. Modern systems employ Pulse-Frequency-Modulation (PFM) or Pulse-Width-Modulation (PWM). Analog versions of both techniques have been discussed in the literature. Reference M5

is a complete treatise on PFM systems, including analog to PFM conversion techniques of exceptional simplicity and elegance.

Reference R7 provides some details of an Integrated-Circuit implementation of a PWM driver.

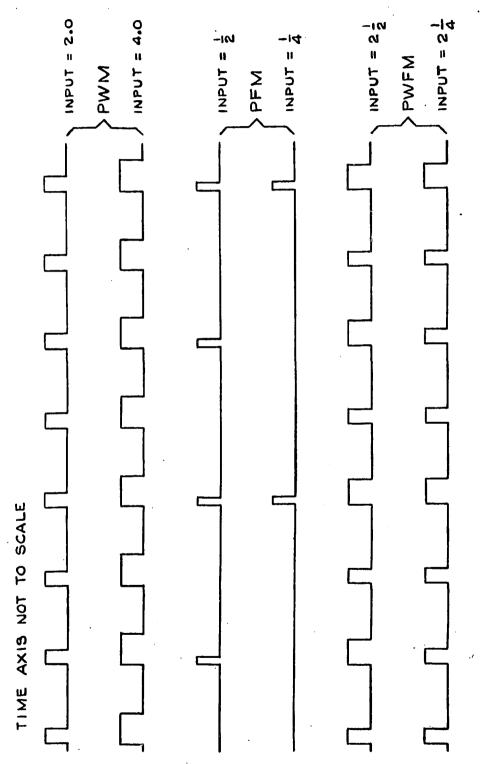

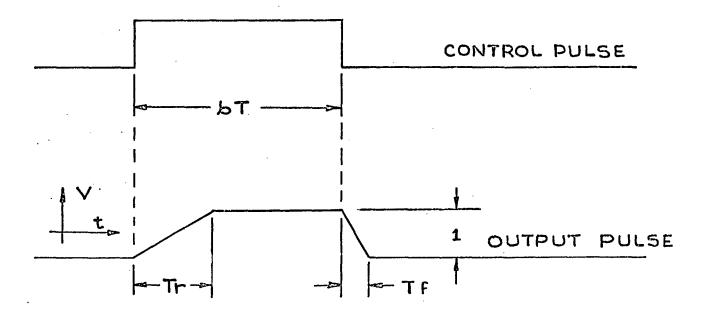

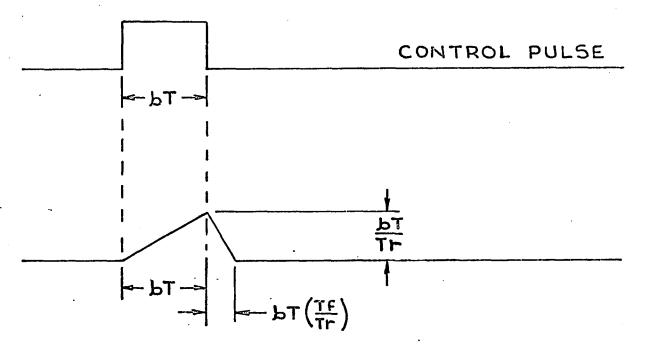

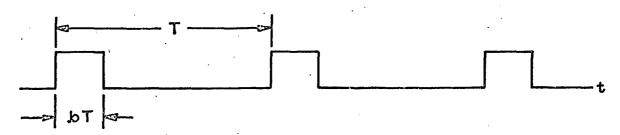

Our own interest lies in digital-input drivers. We present, therefore, all-digital versions of PWM and PFM and, subsequently, introduce the concept of Pulse-Width-Frequency-Modulation (PWFM), developed to overcome the limitations of the older techniques (see Figure V.1). Some component redundance is knowingly accepted, in order to simplify the explanation of PWFM.

#### Pulse Width Modulation

The transfer function of PWM can be expressed by the summation formula:

$$i(t) = \sum_{r=0}^{m} U(t - rT) - \sum_{r=0}^{n} U(t - rT - bT)$$

(2)

where:

Equation (2) displays the proportionality between the width of the

FIG.V.1: IDEALIZED RESPONSE OF PULSE MODULATORS.

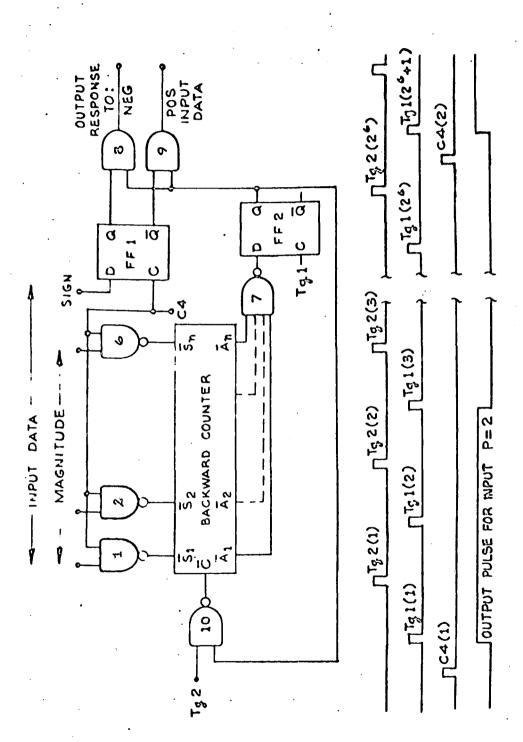

output pulse and the magnitude of the input signal. Implementation of this principle is demonstrated in Figure V.2. The key-element of the basic width modulator is a 6-bit backward counter. The input gates (G1 through G6 and terminal D of FF1) accept a 7-bit word in sign-amplitude format (C8). Output pulses exit through one of two gates (G8 or G9), selected by the "sign" flip-flop FF1.

To examine the operation of the modulator, let a constant positive word of magnitude "p" be applied to the input gates. Also assume that gate G7 is initially in state zero and observe that the repetition rate of the triggers Tg1 and Tg2 is 64 times higher than the clock rate.

Begin with event C4(1), which sets the counter into state p (minterm of the counter equal to p), forcing gate G7 into state "one."

Trigger event Tg1(1) puts FF2 into state "one," marking the beginning of the output pulse and enabling input gate G10. The output pulse exits through gate G9.

Event Tg2(1) feeds a pulse into the counter, reducing its state to p-1.

Tg2(2) sets the counter to p - 2, ... and so on, until event Tg2(p) finally brings the counter to state "zero," forcing G7 into state "zero."

FIG.V.2: THE PULSE WIDTH MODULATOR.

Event Tgl(p + 1) resets FF2, terminating the output pulse and returning the modulator to the state assumed to exist prior to C4(1).

The next operational cycle begins at C4(2).

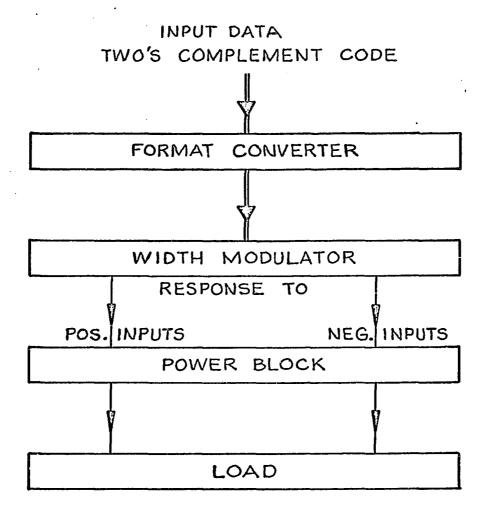

The above width modulator is only one of three elements of a typical power driver. To go from the modulator to the driver, we must add two peripheral units, as shown in Figure V.3: a format converter (Figure V.4) at the input and a power stage (Figure V.5) at the output end of the modulator.

### The Format Converter

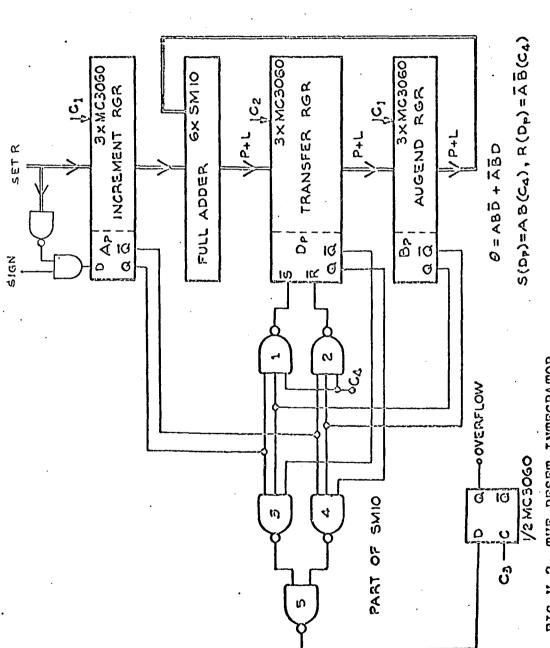

The purpose of the format converter is to reconcile the "two's complement" code of the compensator with the "sign magnitude" code required by the width modulator. In anticipation of PWFM, we assume a 12-bit input to the driver, although we dealt with a 6-bit modulator above.

The input word is divided into various subsets (Figure V.6) whose identity will be clarified as the argument develops. In the present context, the 5 least-significant bits (subset R) are used only for the purpose of proper conversion of negative numbers.

The logic-circuitry of the format converter operates in conformance with the following Boolean equations:

$$x = \prod_{j=0}^{5} \bar{A}_{j} (\sum_{j=6}^{11} A_{j})$$

(3)

$$y_{\underline{i}} = \overline{S}B_{\underline{i}} + SD_{\underline{i}}$$

(4)

FIG.Y.3: COMPLETE DRIVER

FIG.V.4: FORMAT CONVERTER

12-BIT TWO'S COMPLEMENT/7-BIT SIGN AMPLITUDE

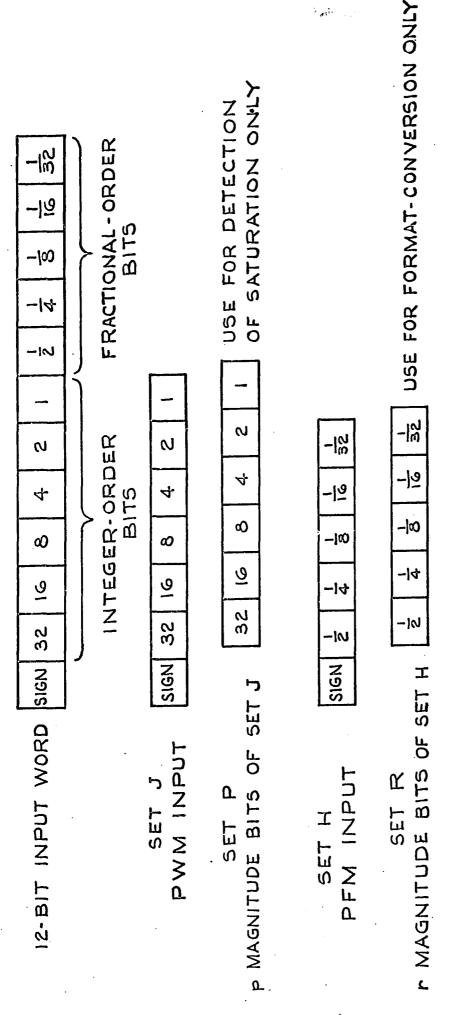

FIG. Y.5: POWER STAGE

#### Pulse Frequency Modulation

Pulse Frequency Modulation (P2, M5) implies proportionality between the magnitude of an input quantity v(t) and the repetition rate f(t) of otherwise uniform output pulses. The output sequence, i(t), can be specified in terms of the Unit Step function U(t):

$$i(t) = \sum_{j=1}^{m} \delta_{mj} \left[ U(t - \sum_{r=1}^{j} T_r) - U(t - x - \sum_{r=1}^{j} T_r) \right]$$

(5)

where:  $\delta_{mj}$  = Kronecker delta

$T_r(t) = t_r - t_{r-1} = Spacing between consecutive pulses at t = t_r$ x = Width of the pulse in seconds.

The delta function representation

$$i(t) = \int_{0}^{\infty} k \sum_{r=1}^{m} \delta(t - t_r) dt$$

(6)

is also legitimate, if its usage is restricted to frequency variation problems.

Analog Reset-Integrator implementations (M5) generally comply with the following equations:

$$f(t) = 1/T \tag{7}$$

$$\int_{t_{m-1}}^{t_m} v(t)dt = k, \text{ a constant}$$

(8)

$$t_{m} - t_{m-1} = T(t)$$

(9)

The proposed configuration of digital-input frequency modulators relies also on the principle of Reset-Integration, generally discussed in conjunction with Digital Differential Analyzers (M4, S8).

Before we examine the operation of the modulator, it should be stressed that we will use set H of Figure V.6 as the input signal. The six integer-order bits (set P) shall be disregarded in the following discussion of PFM.

Returning to set H, we refer to Figure V.7 which presents the block arrangement of the Reset-Integrator and to Figure V.8 which depicts the clock schedule of all Driver elements.

The input word is fed into the Increment-Register by clock C1, while the contents of the Transfer-Register are simultaneously but independently shifted to the Augend Register. The sum of the Increment and Augend words, formed in the Full-Adder block, is clocked into the Transfer-Register by event C2.

An overflow occurs whenever the above sum exceeds the capacity of the registers. This condition is detected by the gate complex G3 through G5, which performs the operation:

$$x = ABD + \overline{ABD}, \qquad (10)$$

The output of G5 is clocked into the Overflow Flip-Flop at clock time C3. Gates G1 and G2 restore the sign-bit of the Transfer-Register to its proper value at C4, in accordance with the equations:

$$S = AB(C4)$$

$$R = \overline{AB}(C4)$$

The polarity of the overflow can be taken from A or B, if required.

It should be noted that the re-setting of the sign-bit does not

CLASSIFICATION OF INPUT-DATA INTO FUNCTIONAL SETS FIG. V.6:

FIG.V.7: THE RESET INTEGRATOR.

affect the remaining 5 bits of the Transfer-Register. The Transfer-Register contains the correct remainder at all times.

The operation of the Reset Integrator can be further clarified by reference to Figures V.1 and V.9. At constant inputs, the modulator behaves like a frequency divider. Thus, with a fixed input of  $1(2^{-r})$ , the output sequence is:

$$\theta(t) = \int_{0}^{\infty} \sum_{k=0}^{\infty} \delta(t - kNT) dt$$

(12)

where:

T = clock period

$$N = 2^r$$