New Jersey Institute of Technology Digital Commons @ NJIT

Theses

**Electronic Theses and Dissertations**

Fall 1-31-1993

# Three dimensional magnetic field sensors and array in BiCMOS technology

Bingda Wang New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/theses

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Wang, Bingda, "Three dimensional magnetic field sensors and array in BiCMOS technology" (1993). *Theses.* 1259. https://digitalcommons.njit.edu/theses/1259

This Thesis is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Theses by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

## ABSTRACT

## Three Dimensional Magnetic Field Sensors and Array in BiCMOS Technology

#### by Bingda Wang

This thesis presents new designs of three dimensional magnetic field sensors in BiCMOS technology. The detailed design of the merged structure device by common diffusion and the high gain transduction circuit are presented. The merged structure has the advantage of less area, less external contacts and less parasitic capacitance. Cross-sensitivity is also eliminated by employing the merged structure. Three active on-chip loads are introduced to improve the sensitivity. The SPICE simulation results show that when a relative change in current  $\Delta I/I$  is 0.001, about 13.6 mV and 8.5 mV can be detected at the output in X(or Y) and Z directions, respectively. The experimental results from a standard (non-merged) BiCMOS magnetic sensor is presented. The 3-D sensor element has been integrated with the signal processing circuits to build a monolithic  $8 \times 8$  sensor array. The detailed SPICE simulation results on the critical path shows the array can be operated with elimination of column-to-column offset voltages under a maximum scanning clock speed of about 0.5MHz. The array structure can find application in precise manufacturing as a position sensor.

# THREE DIMENSIONAL MAGNETIC FIELD SENSORS AND ARRAY IN BICMOS TECHNOLOGY

by Bingda Wang

A Thesis Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Master of Science

Department of Electrical and Computer Engineering

January, 1993

## **APPROVAL PAGE**

#### Three Dimensional Magnetic Field Sensors and Array in BiCMOS Technology

#### by Bingda Wang

Dr. Durga Misra, Thesis Adviser Assistant Professor Department of Electrical and Computer Engineering, NJIT

Dr. Kenneth Sohn, Committee Member Professor Department of Electrical and Computer Engineering, NJIT

Dr. Walter F. Kosonocky, Committee Member Distinguished Professor Department of Electrical and Computer Engineering, NJIT

## **BIOGRAPHICAL SKETCH**

Author: Bingda Wang

Degree: Master of Science in Electrical and Computer Engineering

Date: January, 1993

## **Undergraduate and Graduate Education:**

Master of Science in Electrical Engineering New Jersey Institute of Technology, Newark, NJ, 1993

Master of Science in Information and Electronics Engineering Zhejiang University, Hangzhou, China, 1990

Bachelor of Science in Electrical Engineering, Zhejiang University, Hangzhou, China, 1988

Major: Solid-State Devices and Circuits

This thesis is dedicated to My Parents

## ACKNOWLEDGEMENT

Many people have assisted the auther during this thesis work. In the first, the author would like to thank Dr. Durga Misra, the thesis advisor, for his ever present support and follow up, both technically, and interpersonally. This work could not have been completed without his support.

The author is further indebted to his freinds at NJIT, who gave him their assistance in many ways. The author feels particularly grateful to Zengjing Wu, Elie I. Mourad, Zhu Liu, Chao Ye and Ayyagari V. Subramanyam.

And finally, the author wishes to avail himself of this opportunity to extend his heartfelt thanks to his parents, whose profound concern and great encouragement have always been a major inspiration to the author.

# TABLE OF CONTENTS

| Chapter page                                                                      |

|-----------------------------------------------------------------------------------|

| 1 INTRODUCTION                                                                    |

| 2 PRINCIPLES OF INTEGRATED MAGNETIC FIELD SENSORS AND REVIEW<br>OF PREVIOUS WORKS |

| 2.1 Galvanomagnetic Effects in Semiconductors                                     |

| 2.2 Design Consideration                                                          |

| 2.3 Split-Drain MAGFET12                                                          |

| 2.4 Dual-Collector Magnetotransistors                                             |

| 2.5 3-D MT Based On Bipolar Technology                                            |

| 2.6 3-D Magnetotransistor in CMOS Technology21                                    |

| 3 THREE DIMENSIONAL MAGNETIC SENSOR BASED ON BICMOS TECH-<br>NOLOGY               |

| 3.1 Introduction to BiCMOS Technology25                                           |

| 3.1.1 BiCMOS Technology25                                                         |

| 3.1.2 Overview of the Stanford BiCMOS Technology27                                |

| 3.1.3 Merged Structure in BiCMOS Technology                                       |

| 3.2 3-D Magnetifc Field Sensor in Non-merged Stanford BiCMOS Technology31         |

| 3.2.1 Device Structure and Simulation Results                                     |

| 3.2.2 Layout Design and Experimental Results                                      |

| 3.3 3-D Magnetic Field Sensor in Merged BiCMOS Technology                         |

| 3.3.1 Device Structure and Operation                                              |

| 3.3.2 Sensitivity Analysis                                                        |

| 3.3.3 PISCES Simulation                                                           |

~

| 3.3.4 Circuit Implementation                          | 43 |

|-------------------------------------------------------|----|

| 3.3.5 Layout                                          | 45 |

| 3.3.6 Spice Simulation                                | 47 |

| 4 3-D MAGNETIC FIELD SENSOR ARRAY AND ITS APPLICATION | 54 |

| 4.1 System Operation                                  | 54 |

| 4.2 Circuit Implementation                            | 60 |

| 4.2.1 3-D Merged BiCMOS Magnetic Field Sensor Cell    | 61 |

| 4.2.2 Complementary Merged BiCMOS Gate                | 61 |

| 4.2.3 Dynamic Shift Register                          | 63 |

| 4.3 Layout                                            | 64 |

| 4.4 Spice Simulation                                  | 64 |

| 4.4.1 Simulation of Shift Register                    | 65 |

| 4.4.2 Simulation of 3-D MFS Cell                      | 70 |

| 4.4.3 Simulation of System Delay                      | 72 |

| 4.5 Application Examples                              | 76 |

| 4.5.1 Example One: Position Sensing of Robotic Arm    | 76 |

| 4.5.2 Example Two: Detecting Fringing Magnetic Field  | 81 |

| 5 SUMMARY AND CONCLUSION                              | 83 |

| APPENDIX                                              | 85 |

| REFERENCES                                            |    |

## LIST OF TABLES

,

•

| Table                                                        | Page |

|--------------------------------------------------------------|------|

| 1 Comparison of Bipolar and CMOS                             | 26   |

| 2 Voltage Distribution with MAGFET Gate Connected to Node 4  | 49   |

| 3 Voltage Distribution with MAGFET Gate Connected to Node 10 | 149  |

| 4 Voltage Distribution with MAGFET Gate Connected to Bias2   | 50   |

•

.

## LIST OF FIGURES

| Figu         | re Page                                                       |

|--------------|---------------------------------------------------------------|

| 1.1          | Split-Drain MAGFET 3                                          |

| 1.2.         | Cross-section of a Vertical Magnetotransistor4                |

| 1.3          | Top View of a Sidewall Injection Magnetotransistor5           |

| 2.1          | Example of Hall Effect8                                       |

| 2.2          | Top View of a Vertical Magnetotransistor14                    |

| 2.3          | Top View of a Lateral Magnetotransistor15                     |

| 2.4          | One-dimensional Sensor Magnetic Flux16                        |

| 2.5          | Current Shift in a 2-D Sensor17                               |

| 2.6          | 3-D Magnetic Field Sensor with a 1-D Lateral Device20         |

| 2.7          | The Response of Sensor Channels to a Magnetic Field21         |

| 2.8          | Device Structure of a 3-D Sensor in CMOS Technology22         |

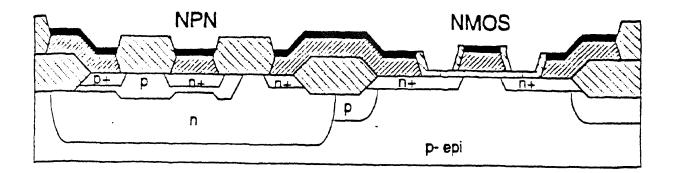

| 3.1          | Cross-sections of NPN and NMOS Transistors26                  |

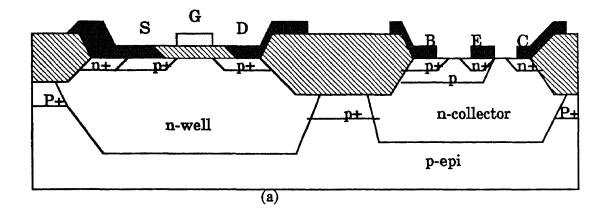

| 3.2          | Cross-sections of the Various PMOS-NPN Configurations30       |

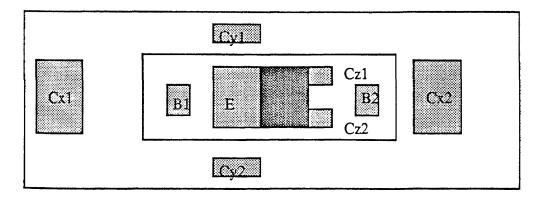

| 3.3          | Top View of Non-merged BiCMOS 3-D MFS 32                      |

| 3.4          | Magic Layout of 3-D Non-merged BiCMOS MFS                     |

| 3.5          | Gummel Plot of the Four Collector NPN in a 3-D MFS 34         |

| 3.6          | Test Results of Sensitivities of 3-D MFS in BiCMOS Process 35 |

| 3.7          | Photomicrography of the Non-merged BiCMOS 3-D MFS 36          |

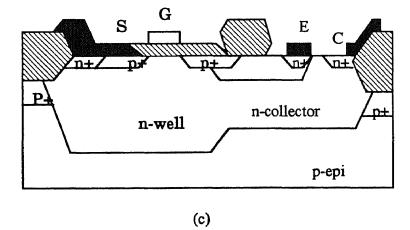

| 3.8          | The BiCMOS Merged Device Structure of 3-D MFS 38              |

| 3.9          | PISCESII Simulation Structure 40                              |

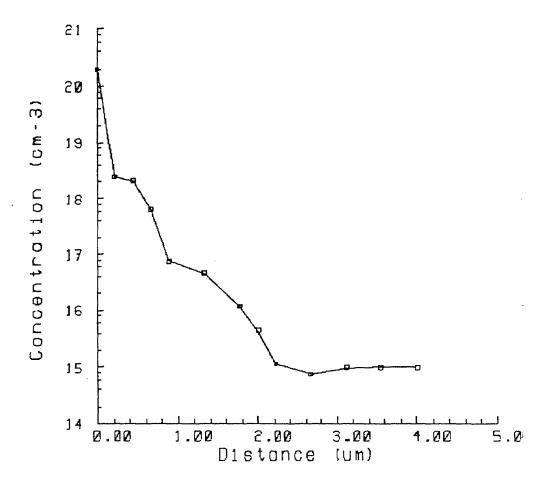

| <b>3.1</b> 0 | Lateral Doping Profile through Y Direction                    |

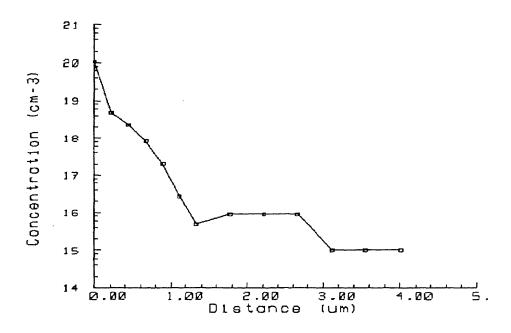

| 3.11         | Vertical Doping Profile through Drain of MAGFET 41            |

| 3.12         | Vertical Doping Profile through Emitter of MAGFET 42          |

| 3.13         | Vertical Doping Profile through Merged Structure              |

## Figure

## Page

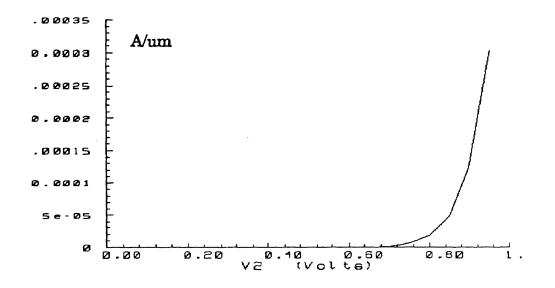

| 3.14 | Base Current vs. Base Voltage for Magnetotransistor 44 |

|------|--------------------------------------------------------|

| 3.15 | Base Current vs. Base Voltage for Magnetotransistor 44 |

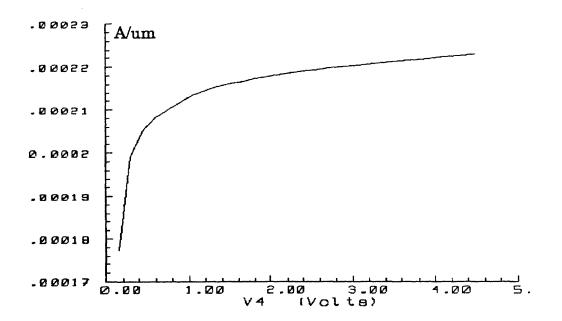

| 3.16 | Threshold Voltage for MAGFET 45                        |

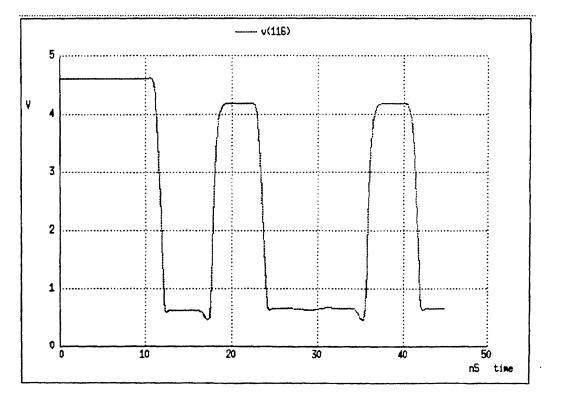

| 3.17 | Circuit of 3-D MFS in Merged BiCMOS Technology         |

| 3.18 | Magic Layout of 3-D MFS with Voltage Output Circuit    |

| 3.19 | SPICE Simulation Results Showing Current Splitting 52  |

| 3.20 | Frequency Response of 3-D Merged MFS Circuit 53        |

| 4.1  | System Structure                                       |

| 4.2  | The Scanning Circuitry with One Mirror Each Column56   |

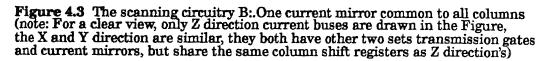

| 4.3  | The Scanning Circuit with One Mirror to All Columns 57 |

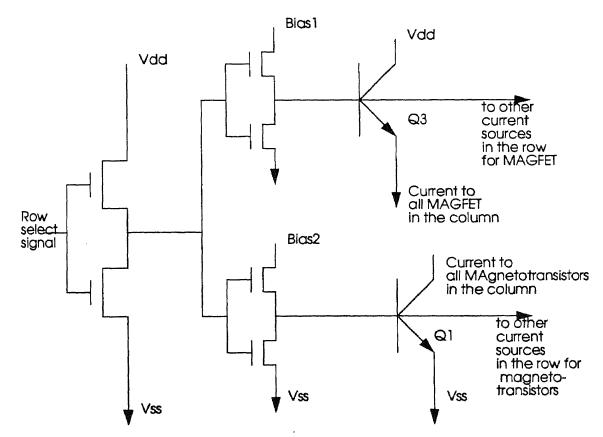

| 4.4  | The Switchable Current Source Supplying 3-D MFS58      |

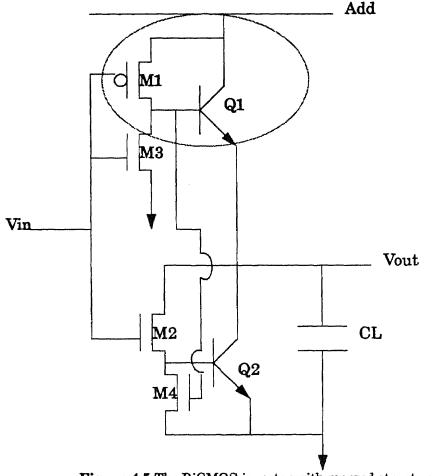

| 4.5  | The BiCMOS Inverter with Merged Structure              |

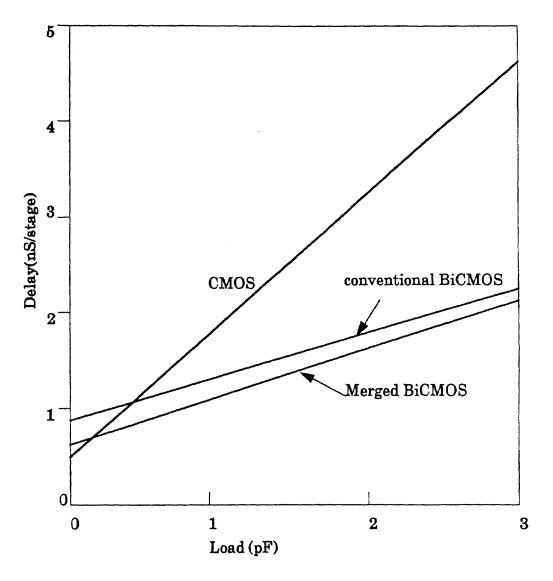

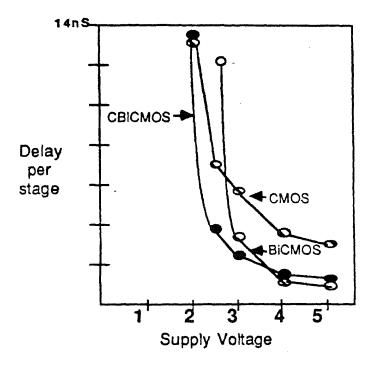

| 4.6  | Measured Delay Comparison62                            |

| 4.7  | Simualtaed Delay Comparison 64                         |

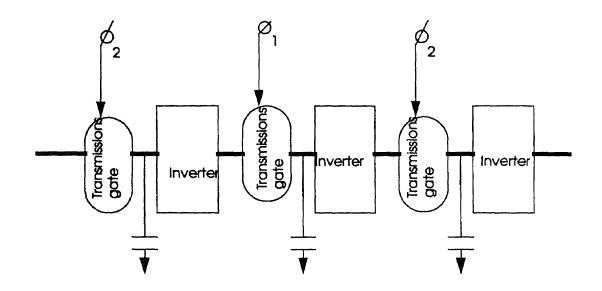

| 4.8  | Simple Dynamic Shift Register                          |

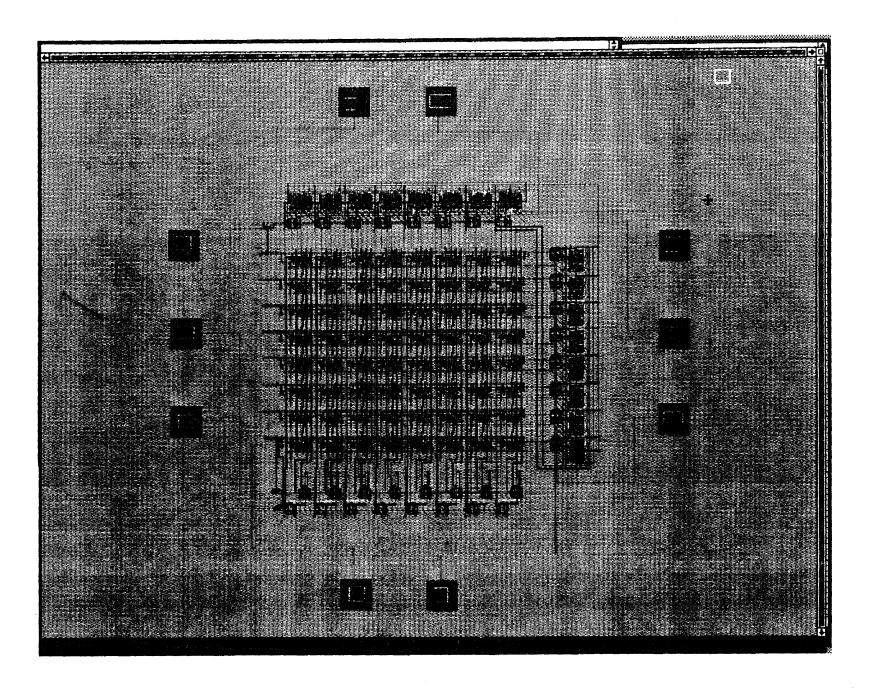

| 4.9  | The Layout of the 8 x 8 Sensor Array 66                |

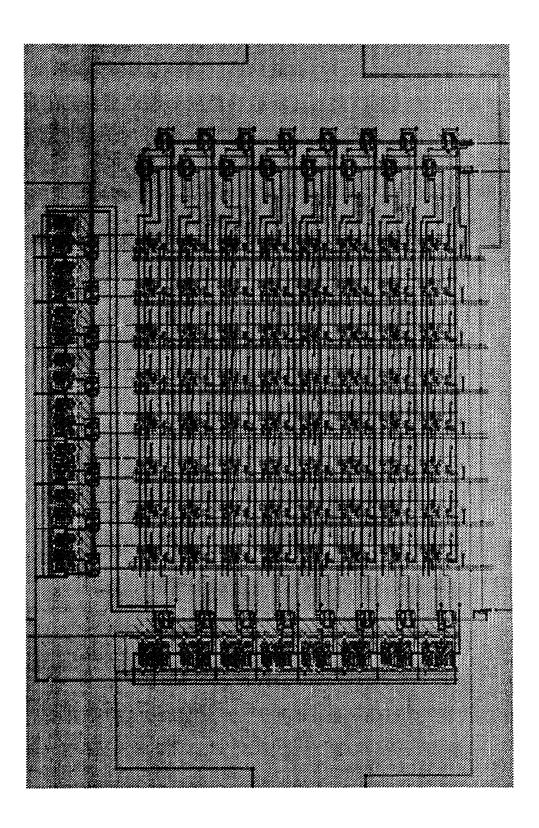

| 4.10 | Simulation Comparison of CMOS and BiCMOS Gates         |

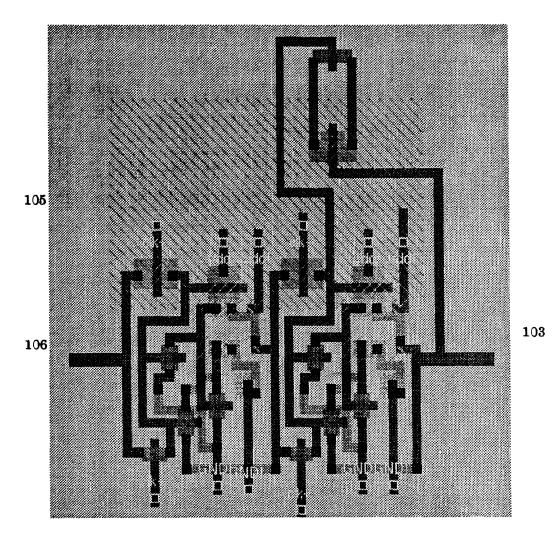

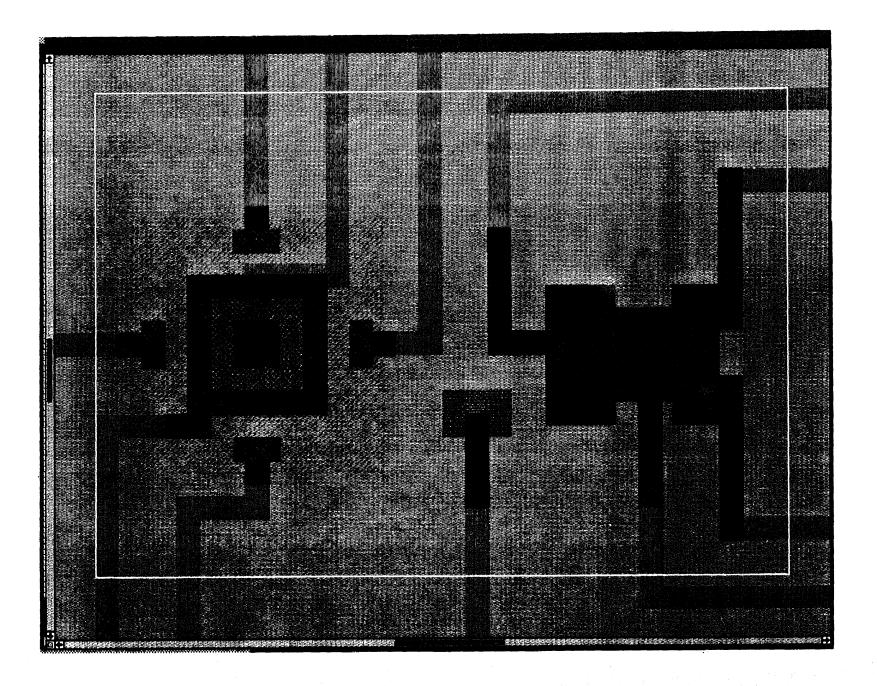

| 4.11 | Magic Layout of Merged BiCMOS Shift Register 68        |

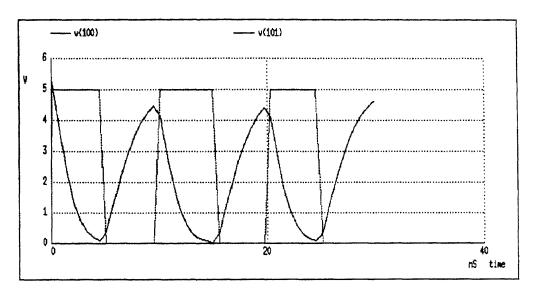

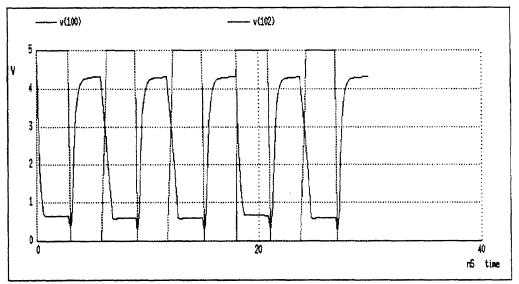

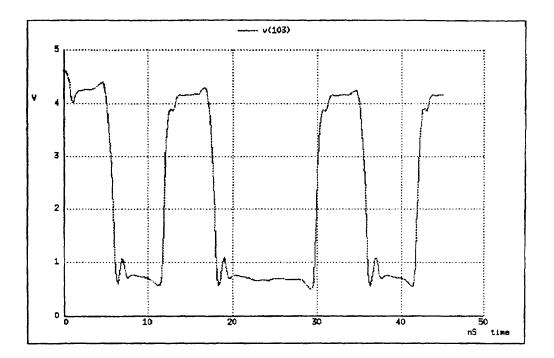

| 4.12 | Simulation Results for Merged BiCMOS Shift Register    |

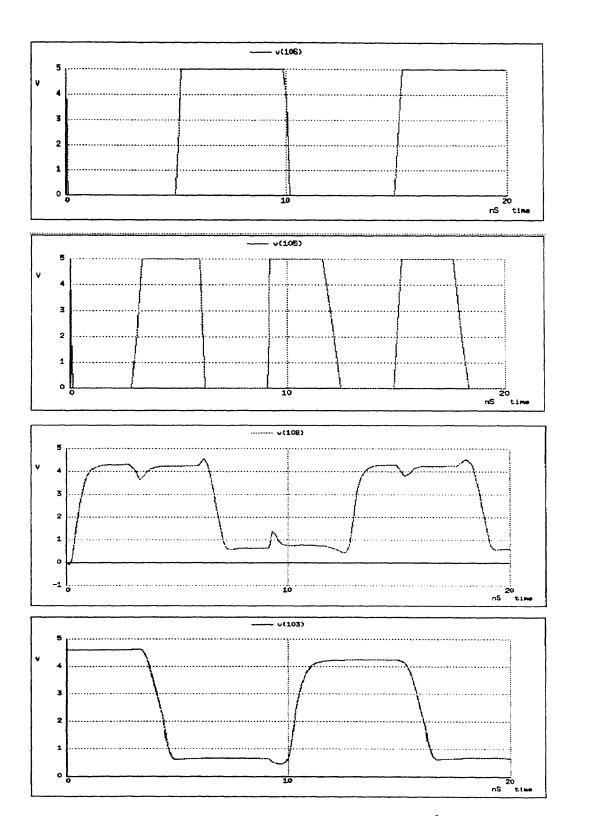

| 4.13 | Two Shift Registers in Chain 70                        |

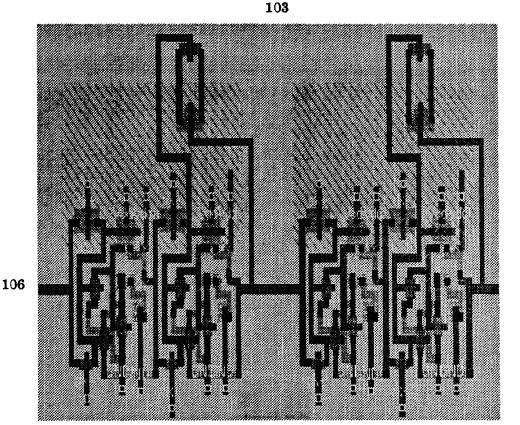

| 4.14 | Simulation Results of Figure 4.1371                    |

| 4.15 | Bus Line Delay Simulation Circuit74                    |

| 4.16 | Simulation Results of System Bus Line Delay            |

| 4.17 | Robotic Position Sensing System                        |

| 4.18 | Position Change Detecting                              |

| 4.18 | Sensing Array Mapping Fringing Field                   |

# CHAPTER 1 INTRODUCTION

Silicon has already revolutionized the way we think about electronics and is now in the process of altering conventional perceptions on sensors and transducers. This holds in particular in the case of magnetic field sensors.

Integrated silicon magnetic field sensors can now be manufactured using standard integrated circuit (IC) processing technologies without invoking additional processing steps such as 'micromachining' or film deposition as in the case of most mechanical or chemical sensors. Integrated sensors are being increasingly developed for a variety of the magnetic field sensitive element together with amplifiers and signal processing circuitry on the same semiconductor chip.

A magnetic field sensors (MFS) is an input transducer that is capable of converting the magnetic field H into a useful electronic signal. A magnetic field sensor is also needed whenever a nonmagnetic signal is detected by means of an intermediary conversion into H ('tandem' transduction), e.g., the detection of a current through its magnetic field or the mechanical displacement of a magnet. Thus we can distinguish two main groups of magnetic field sensor applications.

In direct application case, the magnetic field sensor is part of a magneto-meter. Here are some examples:

- \* Earth magnetic field measurements

- \* Reading of magnetic tapes and disks

- \* Recognition of magnetic ink patterns of banknotes and credit cards

- \* Control of magnetic apparatus

With respect to high-density magnetic recording, some of the recently

1

devised integrated silicon magnetic field sensors are now able to compete with traditional NiFe thin-film magneto-resistor devices.

In indirect Applications case, the magnetic field is used as an intermediary carriers for detection nonmagnetic signals. Examples are as follow:

- \* Contactless switching

- \* Linear and angular displacement detection

- \* Potential-free current detection

- \* Integrated wattmeters

Practical applications require the detection of magnetic fields in the range of micro and millitesla. It can be achieved by the integrated semiconductor sensors. Among the above application, each comes with its specific sensor requirements such as the required sensitivity, field resolution and sensor geometry, etc.

Integrated magnetic field sensors have recently employed various device configurations as a means of detecting the presence of a magnetic field vector. These include vertical magnetotransistors[1],[2] (Figure 1.2), lateral magnetotransistors[3-6], Hall devices[7-9], SD-MAGFETs[10],[11] (Figure 1.1) and Suppressed Side Injection Magnetotransistor[12](Figure 1.3).

Each type has both advantages and disadvantages in one way or another. In general, high absolute sensitivities can be obtained with SD MAGFET when devices operating in the saturation region and drains are connected with high load resistance. In this case, the useful signal is the differential voltage between the two drains. However, SD MAGFETs are onedimensional magnetic field sensors since they are only sensitive to the magnetic field perpendicular to the chip surface.

For the detection of magnetic fields in nanotesla range, Dual-Collector

Figure 1.1 Split-Drain MAGFET

Magnetotransistor with large current gain is desirable. The newly reported Suppressed Sidewall Injection Magnetotransistor displays a range of sensitivities from 0.5/T to 30/T. This sensitivity exceeds by an order of magnitude or more, than the previously reported values for comparable magnetotransistors It can be fabricated by standard CMOS technology. However, from previous report, this kind of magnetic field sensor is still not able to simulatanenously measure more than two components of the magnetic-flus-density vector B.

There are potential applications of three-dimensional magnetic field sensor as in most of the real case the magnetic field is not simply onedimension. Here are some examples of possible 3-D magnetic filed sensor applications :

\* Full magnetic vector measurements on magnetic materials and apparatus

Figure 1.2 Cross section of a vertical magnetotransistor

\* Earth magnetic field measurements for navigational or geological purposes

\* Proximity switches

\* Contactless angular position encoders

Efforts are being made in developing the multi-dimensional magnetic field sensors which enable the detection of the three components of the magnetic field simultaneously. The first fully integrable 3-D magnetic field sensor was proposed by [13] in 1986, which was fabricated in standard bipolar technology. It combines an in-plane 2-D sensor with a lateral magnetotransistor. The device cannot eliminate the cross-sensitivity between x and z, or y and z direction because of the presence of the vertical component in the lateral magnetotransistor[14]. A 3-D vertical Hall magnetic field sensor has been reported recently[9]. The cross-sensitivity between x and z directions disappears, but the cross-sensitivity between x and y directions remains. In our previous work, a 3-D magnetic field sensor fabricated in standard CMOS

Figure 1.3 Top view of a suppressed sidewall injection magnetotransistor

technology has been developed[15]. Although the sensitivity of z direction has been improved by the control of the base surface potential through the biasing of the gate terminal, the cross-sensitivity could not be eliminated completely. In designing a 3-D magnetic sensor, the basic approach is to combine different devices in different orientations on the same chip in a single technology[9],[13]-[16]. However, the 3-D integrable sensors are facing the challenge of implementing the compact sensing structures for all three components of magnetic field on a single plane with relatively lower or no cross-sensitivities.

In this thesis, a three dimensional magnetic field sensor is proposed, using the Stanford merged BiCMOS technology. The design of this BiCMOS 3-D sensor discussed in this work has the following advantages compared to previously reported 3-D magnetic field sensors[9],[13]-[16].

(1). By using the triple diffusion BiCMOS process, the sensor with the four collector vertical npn transistors together with split drain PMOS, as a

single device, is able to eliminate completely the cross-sensitivities which were inherent to the previously reported three dimensional magnetic field sensors in either CMOS or bipolar technology.

(2). The designed BiCMOS sensor can operate in the voltage scale from 0-5V with satisfactory output voltage swings. The device is compatible to the post processing circuits in the BiCMOS technology and can be connected directly without additional voltage transfer. For example, the sensor element can be easily integrated with the signal processing circuitry acting as "smart sensor" in a robotic arm for position detection in a magnetic environment.

(3). In this design, a merged structure from Stanford BiCMOS process is used to reduce the chip area. The advantage of area and number of contacts will become more obvious when the sensing part is used as a building block of a large sensor processing system[17].

Although much effort has been expended in the development of sensors, proportionally less effort has been directed to make integrated arrays of sensors, especially in the multi-dimensional high frequency sensing systems. In this thesis, a development of a 3-D magnetic field sensor array is also presented. The above mentioned 3-D merged BiCMOS magnetic field sensor is used as an individual cell in the processing array system. Such an array has many applications, for example, it can act as the compliant tactile sensor to measure the deformation of a membrane to which small magnetic dipoles are attached[3]. In many cases, the multi-dimensional high frequency response sensing systems can meet the requirements of mapping a quickly varying field. This kind of 3-D magnetic field sensor system can be used in precise manufacturing as a position sensor in a robotic arm in a magnetic source environment which requires that the sensor system not only be capable of detecting absolute positions but also detecting very rapid position changes. Another useful application is the high frequency contactless switching. We often need a tactile sensor which can sample a quickly changing magnetic field. Of course the sensor array can be also used in the general application like determining the fringing fields in an electric motor.

In the following chapters, details about device working principles, design considerations, device and circuit simulations and some test results are presented.

Chapter 2 gives a review of integrated semiconductor magnetic field sensors, describing the physical mechanism basic to the action of the electrons and the main principles about sensitivity, resolution, and technology in typical magnetic field sensors.

Chapter 3 describes the novel 3-D magnetic field sensor designed in Stanford BiCMOS technology with and without the merged structure. The sensors is designed together with output processing circuitry. Design consideration, layouts, PISCES and SPICE simulation and test results are presented.

Chapter 4 gives the design of the 3-D magnetic field array system. The principle of the processing system and optimization through simulation are presented.

Finally the summary and conclusion are provided in chapter 5.

All the computer simulation input data and device layouts for fabrication are presented in Appendix.

## **CHAPTER 2**

## PRINCEPLES AND OF INTEGRATED MAGNETIC FIELD SENSORS AND REVIEW OF PREVIOUS WORK

## 2.1 Galvanomagnetic Effects in Semiconductors

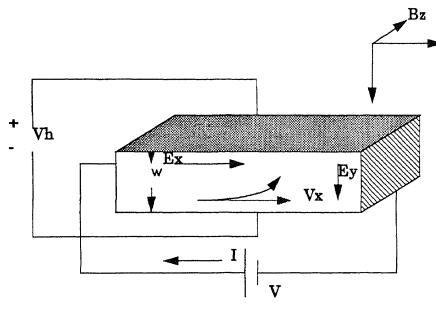

Most MFSs exploit the Lorentz force  $\vec{F} = q\vec{V} \times \vec{B}$  on electrons in a metal, a semiconductor, or an insulator in one way or another, where q denotes the electron charge,  $\vec{V}$  the electron velocity, and  $\vec{B}$  the magnetic induction. A simple example is shown in Figure 2.1.

Figure 2.1 Example of Hall effect

As mentioned in Chapter 1, semiconductor MFSs exploit the galvanomagnetic effects such as Hall voltage, carrier deflection, magnetoresistance and magnetoconcentration, which are due to the action of the Lorentz force on the charge carriers (electrons and holes). In n-type semiconductor material, for instance, the magnitude of the sensor effect is controlled by the product of the electron mobility and the magnetic induction. Hence high electron mobility is crucial for achieving high sensitivity. Thus ntype material is superior to p-type material because of mobility.

The action of the Lorentz force manifests itself in the carrier-transport equations. We assume isotropic n-type material with zero temperature gradient. Let us denote the electron current density for  $\vec{B} = 0$  by  $\vec{J}_{n(0)}$  The diffusion approximation of the Boltzman transport equation leads to

$$\hat{J}_n = \sigma_n \vec{E} + (q D_n \vec{\nabla} n)$$

(2.2)

where  $\sigma_n = q \mu n$  denotes the electronic conductivity for  $\vec{B} = 0$ ,  $\vec{E}$  the electrical field,  $D_n = \mu \kappa (T/q)$  the electron diffusion constant, n the electron density, and  $\mu$  the electron drift mobility. In (2.1) the term  $\sigma_n \vec{E}$  describes the drift current and  $q D_n \nabla n$  the diffusion current. For nonzero magnetic induction  $\vec{B}$ , the electron current density  $\vec{J}_n(B)$  obeys the equation

$$\vec{J}_n(\vec{B}) = \vec{J}(0) - \mu_n^*(\bar{J}(\vec{B}))$$

Where  $\mu_n^*$  is the Hall mobility for electrons. Equation (2.2) can be solved with respect to  $\overline{J}(\overline{B})$  viz.

$$\bar{J}(\vec{B}) = [\bar{J}_n(0) + \mu_n^* \vec{B} \times (\vec{B} \bullet \vec{J}(0)\vec{B})] \left[1 + (\mu_n^* \vec{B})^2\right]^{-1} \quad (2.3)$$

This equation comprises the isothermal galvanomagnetic effects for electrons. It accounts for the direct effects of temperature on carrier concentration, diffusion, and mobility, but does not include thermomagnetic or thermoelectric effects. An analogous equation holds for the hole current density. In general, the electron and hole current equations have to be solved together with the pertinent continuity equations for electrons and holes as well as Poisson's equation. In specific configurations characterized by the device geometry, doping, and boundary and operation conditions, the one or the other galvanomagnetic effect may prevail.

Equation (2.3) induces the action of the Lorentz force on both carrier drift (terms containing  $\vec{E}$ ) and diffusion (terms containing  $\vec{\nabla}n$ ). Diffusion is important in the case of magnetoconcentration or space-charge effects occurring, e.g., in magnetodiodes (injection of both electrons and holes). If carrier concentration gradients can be neglected, as,e.g.,in n-type slabs with ohmic contacts,(2.3) becomes

$$\vec{J}_n(\vec{B}) = \sigma_{nB} \left[ \vec{E} + \mu_n^* (\vec{B} \times (\vec{B} \bullet \vec{E}) \vec{B}) \right]$$

(2.4)

where  $\sigma_{nB} = \sigma_n \left[ 1 + (\mu_n^* \vec{B})^2 \right]^{-1}$ . If  $\vec{B}$  is parallel to  $\vec{E}$ ,  $\vec{B} \times \vec{E} = 0$ leads to  $\vec{J}_n(\vec{B}) = \sigma_{nB}\vec{E} = \vec{J}_n(0)$ : this means that no longitudinal galvanomagnetic field effect is observed in isotropic semiconductors. For  $\vec{B}$ normal to  $\vec{E}$ ,  $\vec{B} \cdot \vec{E} = 0$ , we obtain

$$\vec{J}_n(\vec{B}) = \sigma_{nB} \left[ \vec{E} + \mu_n^* \vec{B} \times \vec{E} \right]$$

(2.5)

This equation describes the transverse galvanomagnetic effects in the case of negligible diffusion. In terms of  $\vec{B} = (0, 0, B)$ ,  $\vec{E} = (E_x, E_y, 0)$  and  $\vec{J}_n(\vec{B}) = (J_{nx}, J_{ny}, 0)$ , (2.5) becomes

$$J_{nx} = \sigma_{nB} (E_x - \mu_n^* B E_y) \underset{\&}{} J_{ny} = \sigma_{nB} (E_y + \mu_n^* B E_x)$$

(2.6)

Two limiting cases are usually distinguished:

1) Hall field:

It is assumed that the current density has only an x-component, i.e.,  $J_{ny} = 0$ . This can be achieved approximately in a long, thin rod sample geometry with current electrodes at the small faces. Then the Hall field

$$E_{y} = -\mu_{n}^{*}BE_{x} = R_{H}J_{nx}B$$

(2.7)

Where

$$R_H = -\mu_n^* / \sigma_n = -\gamma_n / (qn)$$

(2.8)

denotes the Hall coefficient. this results in a rotation of the equipotential lines by the Hall angle  $\theta_H$  with

$$\tan\theta_H = E_y / E_x = -\mu_n^* B = \sigma_n R_H B \tag{2.9}$$

For a long Hall plate of thickness t carrying a current I, the Hall field produces the Hall voltage  $V_H = R_H/t$ . The corresponding Hall sensor has the sensitivity  $V_H/(IB) = R_H/t = \gamma_n/(qnt)$ . Thus high sensitivity requires small carrier concentration n. This explains why semiconductors are more useful here than metals.

2) Carrier deflection:

Now zero Hall field,  $E_y = 0$ , is assumed. This condition can be realized approximately by a short sample of wide cross section with current electrodes at the large faces. The carrier deflection resulting is given by the ratio

$$-J_{ny}/J_{nx} = \mu_n^* B = \tan\theta_H \tag{2.10}$$

#### **2.2 Design Consideration**

Although different applications of magnetic field sensor has different considerations which may emphasize one or two requirements, there are some general design criteria which should be take into account when designing a magnetic field sensor.

First of all, we must consider the availability of technology. Such as standard Bipolar, NMOS, CMOS, and BiCMOS technology. Second, we need to think over total manufacturing cost, which should be as low as possible. Then the environment to which sensor is exposed should also be taken into consideration. This includes temperature, humidity and chemical stress, mechanical stress, vibrations, etc. These conditions will influence the sensor performance.

As to the properties of magnetic field sensor, we should consider the following aspects:

- \* Sensor geometry (H parallel or perpendicular to chip surface)

- \* Sensitivity (absolute sensitivity and relative sensitivity)

- \* Magnetic field resolution signal to noise ratio)

- \* Spatial resolution (device geometry size)

- \* Linearity (response to magnetic field)

- \* Time resolution (frequency response)

- \* Offset, temperature dependance of offset

- \* Power consumption

- \* Stability, reliability, lifetime

#### **2.3 Split-Drain MAGFET**

Split-Drain MAGFET is a MOSFET with two or three adjacent drain regions which share the drain current. A magnetic field perpendicular to the chip surface can cause defection of the current lines in the channel region. By operating the MOSFET in the 'pinch-off' mode  $(V_{DS} > V_{GS} - V_T)$  the output impedance is made very high, so that large output voltage swings may be obtained. Beyond the 'pinchoff' region', the depletion layers formed between drains and channel would prevent voltage changes on the drains from affecting the channel voltages. Since the MOS transistor works as current source, the output impedance would therefore be high and so the device would be capable of producing high output voltages under suitable load conditions. Moreover, this bias condition also ensure that the lateral parasitic npn bipolar formed by two split drains and substrate operates in the cut-off mode [10].

The first magnetic-field sensitive MOS device was the MOS element proposed by Gallagher and Corak [25]. About  $10^3 V/(AT)$  sensitivity can be achieved in this way. The split-drain MOS transistor configuration as proposed by Fry and Hoey [25] shows a much higher sensitivity, viz. about  $10^4 V/(AT)$ , provided load resistors well within magaohm range are applied. The structure of a split-drain MAGFET is shown in Figure 1.1. The separation of the two drains are determined by the minimum spacing of technology. Each drain is L-shaped to provide more drain area, which helps to shape the surface potential for better collection of deflected electrons. The width at the middle of the channel is taken as the minimum width of the device. The length is taken to be the minimum distance covered by the carriers in traveling from the source to the drain [10].

#### 2.4 Dual-Collector Magnetotransistor

Dual-collector Magnetotransistor is a bipolar transistor whose design and operating conditions are optimized with respect to magnetic field sensitivity of the collector current  $I_c$ . Because of the geometrical symmetry, the two collector current should be equal without magnetic field. However, when we apply magnetic field in a particular direction, the current flow will deflect and cause more current in one collector and less current in the other. The first magnetotransistor was proposed by Hudson [6] in 1968. The relative sensitivity was about  $0.05T^{-1}$ . This is the vertical two-collector bipolar transistor, where the magnetic field causes an imbalance in the two collector currents. A lateral magnetotransistor was first described by Davies and Wells [7]. This device was essentially a merged combination of planar Hall plate and a lateral two-collector transistor. The relative sensitivity was about  $0.5T^{-1}$ . A vertical magnetotransistor and a lateral magnetotransistor are shown in Figure 2.2 and Figure 2.3.respectively

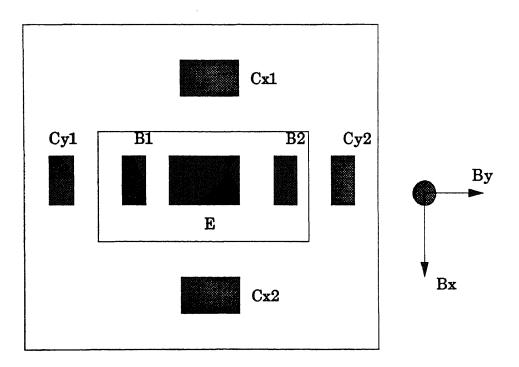

The sensitivity of a vertical 1-D magnetotransistor can be calculated from Figure 2.4. The path of the total collector current  $I_c$  is shifted over a distance  $\Delta y$  under the influence of the lateral magnetic field  $B_x$ . the shift  $\Delta y$ depend on the Hall angle $\theta_H$

$$\tan \theta_H = \mu_H B_x \tag{2.11}$$

Hall mobility of the material  $\mu_{H},$  and the distance L' over which the

Figure 2.2 Top view of a vertical magnetotrasistor

deflection takes place. L' is smaller than the thickness of the epitaxial layer because of the presence of the buried layers, emitter and base diffusions, depletion layers, and current spreading. The shift  $\Delta y$  becomes

$$\Delta y = L' \tan \theta_H \tag{2.12}$$

Figure 2.3 Top view of a lateral magnetotrasistor

$$\Delta y = L' \mu_H B_x \tag{2.13}$$

We assume that current to the left of the central line between the buried layers is collected be collector  $C_x$ , while the current to the right is collected by collector  $C'_x$ . Because of the shift, currents  $I_x$  in collector  $C_x$  and  $I'_x$  in the collector  $C'_x$  are unequal.

$$I_{x} = \left(\frac{1}{2} + \frac{\Delta y}{W_{e}}\right) I_{c}$$

(2.14)

$$I_{x} = \left(\frac{1}{2} - \frac{\Delta y}{W_{e}}\right) I_{c}$$

(2.15)

$W_e$  is the emitter width. The output signal  $\Delta I_x = I_x - I'_x$ , which is the current difference between the two collectors, becomes

$$\Delta I_x = 2I_c \left(\frac{\Delta y}{W_e}\right) \tag{2.16}$$

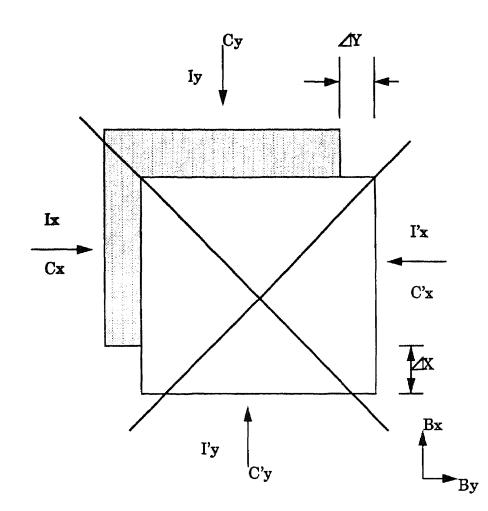

Figure 2.4 One-dimensional sensor-Magnetic-flux density Bx cause a shift in the collector profile

With (2.13) the output signal can be written as

$$\Delta I_x = 2I_c \mu_H B_x \left(\frac{L'}{W_e}\right) \tag{2.17}$$

In the case of a 2-D in-plan sensor Figure 2.4, the sensitivity can be

Figure 2.5 Current shift in a 2-D sensor. Bx and By will shift the injected current profile respectively

calculated similarly. From Figure 2.5 we can see that the in-plane field components  $B_x$  and  $B_y$  cause a shift in the current by  $\Delta y$  and  $\Delta x$

$$I_{x} = I_{c} \left( \frac{1}{4} + \frac{\Delta y}{W_{e}} - \frac{\Delta x \Delta y}{W_{e}^{2}} + \frac{\Delta y^{2}}{2W_{e}^{2}} - \frac{\Delta x^{2}}{2W_{e}^{2}} \right)$$

(2.18)

$$I_{x} = I_{c} \left( \frac{1}{4} + \left( -\frac{\Delta y}{W_{e}} \right) + \frac{\Delta x \Delta y}{W_{e}^{2}} + \frac{\Delta y^{2}}{2W_{e}^{2}} - \frac{\Delta x^{2}}{2W_{e}^{2}} \right)$$

The output signal  $\Delta I_x = I_x - I_x$  of the x channel is

17

(2.19)

$$\Delta I_x = 2I_c \left( \left( \frac{L'}{W_e} \right) \mu_H B_x - \left( \frac{L' \mu_H}{W_e} \right)^2 B_x B_y \right)$$

(2.20)

Currents  $I_y$  and  $I'_y$  in the channel can be calculated in a similar manner, and the output signal  $\Delta I_y$  of the y-collector pair is

$$\Delta I_{y} = I_{c} \left( \frac{2L' \mu_{H} B_{y}}{W_{e}} - \left( \frac{L' \mu_{H} B_{y}}{W_{e}} \right)^{2} - \left( \frac{L' \mu_{H} B_{x}}{W_{e}} \right)^{2} \right)$$

(2.21)

The output signals of the 2-D sensor can be writer for  $|B_y| \ge |B_x|$  as

$$\Delta I_x = 2I_c \left(\frac{L'\mu_H B_x}{W_e}\right) \left(1 - \frac{L'\mu_H |B_y|}{W_e}\right)$$

(2.22a)

$$\Delta I_{y} = 2I_{c} \left( \frac{L' \mu_{H} B_{y}}{W_{e}} \right) \left( 1 - \left( \frac{L' \mu_{H} B_{x}^{2}}{2W_{e} |B_{y}|} \right) - \left( \frac{L' \mu_{H} B_{x}^{2}}{2W_{e} |B_{y}|} \right) \right)$$

(2.22b)

The difference in the form of these equations is caused by the square shape of the current profile. We can see from (13) that both output signals are nonlinear and that they are also dependent on both in-plane field components. In the case of the device used in the experiments with  $W_e = 20 \mu m$ ,  $\mu_H = 0.114 \ (m^2/Vs)$ , and L' smaller than  $8\mu m$ , for magnetic-flux-density values lower than 1T, the contribution of the second-order terms is a factor of 20 lower compared to the first-order terms. Under the above conditions (2.24) can be reduced to

$$\Delta I_x = 2I_c \left(\frac{L' \mu_H B_x}{W_e}\right) \tag{2.23a}$$

$$\Delta I_y = 2I_c \left( L' \mu_H \frac{B_y}{W_e} \right)$$

(2.23b)

#### **2.5 3-D MT Based on Bipolar Technology**

#### **2.5.1 Device Structure and Operation**

We have discussed 1-D and 2-D magnetic field sensors in the previous sections. As in most of the real case, we need to measure the 3-D magnetic field. This can be performed by successively changing the orientation of the one-dimensional sensor and measuring the field component. A simultaneous measurement of all three field components can be achieved by attaching three 1-D sensors to the orthogonal faces of a cube. The spatial resolution of a measurement would not be satisfactory in this case it highly divergent fields were to be measured, nor is the sensor integrable.

A recent report [26] shows that a 3-D magnetic sensor has been designed and fabricated by standard Bipolar technology. As the current flow in a 2-D in-plane magnetotransistor is not completely vertical; there are also significant lateral components of the total current in the n epitaxial collector region. Just as in the case of lateral magnetotransistors, the lateral component of the total collector current can be deflected by  $B_z$ , and this can be used in sensing the last field component. Figure 2.6 shows the structure of the 3-D magnetotransistor.

#### 2.5.2 Sensitivity of the 3-D Magnetotransistor

In general, the output signal of the sensor can be written as

$$\begin{bmatrix} \Delta I_x \\ \Delta I_y \\ \Delta I_z \end{bmatrix} = S \begin{bmatrix} B_x \\ B_y \\ B_z \end{bmatrix}$$

(2.24)

Where  $\Delta I_i$  (i=x,y or z) is the collector-current difference of the

**Figure 2.6** By merging a 2-D in-plane sensor with a 1-D lateral device, a sensor is obtained that is sensitive to all three components of the magnetic field vector

associated channel. S is a  $3 \times 3$  sensitivity matrix, which is not necessarily a diagonal matrix because the output signal  $\Delta I_i$  of the channel i will not only depend on the field component $B_i$ , but also on the other two components. The sensitivity matrix of the structure shown in Figure 2.6 with one z-collector pair is

$$S = \begin{bmatrix} S_{xx} & 0 & 0 \\ 0 & S_{yy} & 0 \\ 0 & S_{xy} & S_{zz} \end{bmatrix}$$

(2.25)

Figure 2.7 The response of different sensor channels to a magnetic filed as a function of the emitter current.

#### 2.6 3-D Magnetotransistor in CMOS Technology

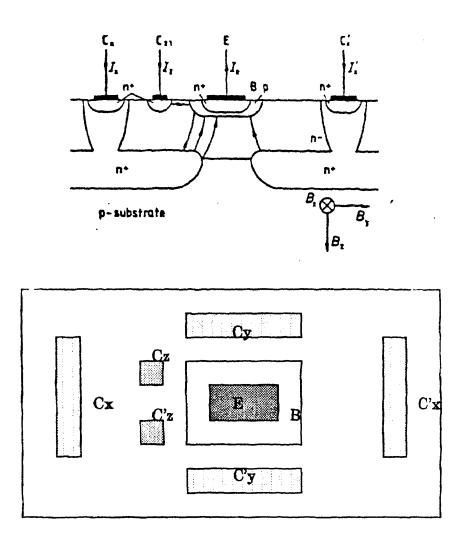

The realization of a 3-D Magnetotransistor in CMOS technology has been accomplished by Ms. Zhang in our Sensor Lab. The device was fabricated in standard 2um CMOS technology. The operation description and test results are given below.

#### 2.6.1 Device Structure and Operation

,

Use of bipolar devices that are reliable with existing CMOS technologies is inexpensive and has wider applications. One possibility is the vertical transistor where the substrate is used as the collector and a separate well as the base. A lateral bipolar transistor can also be formed in the base region. In this section, we first describe the device structure and then analyses its operation.

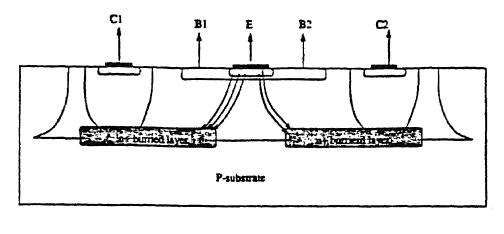

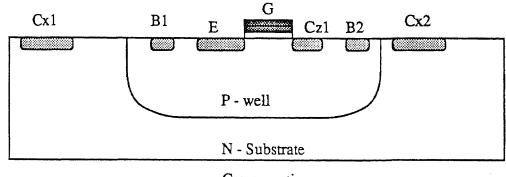

The structure of the new 3-D magnetic field sensor is shown in Figure 2.8. It is basically similar to the conventional 3-D magnetotransistor which has been discussed in last section. The device is situated in a p-well, serving

Cross section

Top view

Figure 2.8 Device structure of 3-D magnetotransistor in CMOS technology

as the base region of the transistor. The substrate serves as collector for the two vertical npn transistors and another lateral bipolar transistor with twocollector pair is formed within the base region. The two vertical magnetotransistor are sensitive to the 2 in-plane magnetic field and the lateral magnetotransistor can measure the magnetic field perpendicular to the chip surface.

However, there are two changes in this new device compared with traditional magnetotransistor. First, two base contacts,  $B_1$  and  $B_2$  are used. This allows the application distribution of collector current. For example, if the device is ideally in geometrical symmetry, each collector current should be equal to corresponding collector pair. However, because the fabrication process may cause asymmetry in device structure which will cause current imbalance even without magnetic field. By applying two slight different voltages to  $B_1$  and  $B_2$ , the imbalance can be dispelled. From Figure 2.8, it is evidenced that additional Z-collector pair partakes of the X- collector current. Adjusting the two base voltages will provide a reasonable distribution of those collector currents.

Second, the device is also similar to a MOS transistor as the base region is covered by the thin oxide and polysilicon gate layers. This was done for two reasons. First, it makes the device fully compatible with a standard CMOS process, so that the emitter and collector can be fabricated as the source and drain of the NMOS transistor, respectively. Second, the gate makes it possible to control the base surface potential. This feature is important for both sensitivity and noise performance of the device. For example, when a magnetic field perpendicularly to the device plane is applied, the electron flux lines are deflected toward the device surface. The two lateral collector currents will be reduced a little because of the recombination at the siliconoxide interface. The MOS structure on top of the base region serves to reduce this recombination. Application of a negative voltage to the gate repels the minority carriers away from interface. As recently demonstrated by Vittoz [6].

To consider the operation, let us assume that the device is biased adequately for the forward active operation, that is the emitter-base junction is forward biased, both collector-base junctions are reverse-biased. Electrons are injected into the base region laterally and vertically and are collected by corresponding collectors. If we apply a magnetic field  $\vec{B}_x$  or  $\vec{B}_y$ , it will cause a change in the two vertical collector pairs due to the deflection of the electron paths. When the field is directed perpendicular to the Figure plane, the Lorentz force on charge carriers will cause an imbalance of collector current in the Z-collector pair.

In the long base region device, because p-well with depth about  $5\mu m$  is used as base region, we must consider the Lorentz force on minority carriers (electrons) as well as that on majority carriers. It is known that the Hall field generated by deflected electrons in silicon is in an opposite direction of the Hall field generated by holes. Therefore, the majority carriers (holes) cancel the Hall field that the minority carrier (electrons) flow would produce, in the same way as they cancel any other space-charge effect. Thus sensitivity can be increased by using minority-carrier deflection in the long-base region. The deflection efficiency is not linked to the device geometry, biasing condition is more related with the device sensitivity. Evidently, this kind of 3-D magnetic field sensor has better performance than those 3-D magnetotransistors discussed previously.

## **CHAPTER 3**

## THREE DIMENSIONS MAGNETIC FIELD SENSOR BASED ON BICMOS TECHNOLOGY

In this chapter, different 3-D MFSs are designed in Stanford BiCMOS technology. The 3-D sensor using merged structure with voltage output circuits is discussed. The device simulations for both non-merged MFS and merged MFS are presented. The SPICE simulation and the test results are also given.

## **3.1 Introduction of BiCMOS Technology**

#### **3.1.1 BiCMOS Technology**

In recent years there has been strong interests in BiCMOS. In the past, however, the cost of more complex process, has restricted such technologies to rather specialized applications. In modern technologies both bipolar and CMOS have shown very similar complexity. By using BiCMOS technology, we can exploit the performance advantages of bipolar and CMOS and at the same time use the higher yield capability of MOS.

Table 1 lists some important properties of bipolar and CMOS transistors in circuits

From table 1 it can be deduced that generally for devices bipolar is in an advantageous position for analog applications because of the better gain and low wideband noise. CMOS obviously is more attractive for digital control and data processing functions because of its low quiescent power, good speed and generally good packing density. The mixture of bipolar and MOS offers unique advantages, however, in both the analog and the digital fields. It features for instance, high-impedance zero dc gate current, high gain

| strengths of Bipolar and CMOS   |                                      |  |  |  |

|---------------------------------|--------------------------------------|--|--|--|

| Bipolar                         | CMOS                                 |  |  |  |

| Large transconductance          | high impedance                       |  |  |  |

| exponential characteristics     | near quaqratic                       |  |  |  |

| low voltage offset              | zero DC dissipation                  |  |  |  |

| low supply voltage              | low narrow band noise                |  |  |  |

| low 1/f noise                   | high slew rate                       |  |  |  |

| fast                            | no second breakdown                  |  |  |  |

| low logic swing                 | self isolating                       |  |  |  |

| good capacitor drive capability | no avalanche breakdown reductionCom- |  |  |  |

| no hot electron limit           | parision of Bipolar and CMOS         |  |  |  |

## **Table 1**Comparison of Bipolar and CMOS

operational opamps, switch capacitor filters and gyrators. Futhermore, precision pairs in mixed AD and DA systems in the field of analog applications are possible. In digital applications mixed sense-amplifiers and buffers can significantly increase the capability of CMOS with regards to speed and compactness.

In the context of electronic advantages it should be noted that some problems can also occur. Because bipolar transistors can inject into the substrate one has to take measures to prevent latch-up. Futhermore CMOS logic generates considerable transient noise which must be prevented from entering into an adjacent sensitive analog part. Both problems can effectively suppressed by proper measure.

## 3.1.2 Overview of the Stanford BiCMOS Process

Stanford BiCMOS process is using a  $2\mu m$  technology. A number of key features include:

\* A single level of polysilicon is used for emitter contacts, base contacts, collector contacts, n- and p-channel gates, and n- and p-channel source/drain contact regions. This allows us to produce high performance polysilicon emitter bipolar transistors coupled with dense, low capacitance contacts to all regions.

\* N+ doped poly is used for emitter contacts, collector contacts, nchannel source/drain contacts, and n-channel gates.

\* P+ doped poly is used for base contacts, p-channel source/drain contacts, and p-channel gate regions. In particular, this avoids problems associated with buried channel p-channel devices which are frequently encountered when n+ polysilicon is used as the gate material for p-channel devices.

\* selective tungsten is used as a strapping layer on top of all polysilicon regions in order to provide a low sheet resistance ( $R < 2(\Omega/(square))$ ) local interconnect layer and to short out any possible n+/p+ diodes occurring in the polysilicon layer.

\* Local oxidation is used to pattern most of the polysilicon regions. In particular, this results in an exceedingly planar surface after all polysilicon processing. This, in turn, greatly eases the task of adding two levels of metallization to this structure. Furthermore, the local oxidation of poly enables us to produce overlapping contact holes (i.e., non-dog-bond poly) between first metal and underlying polysilicon structures further increasing the packing density of this technology.

Figure 3.1 shows a completed cross-section of the vertical NPN

transistor and the NMOS transistor that result from the Stanford BiCMOS process.

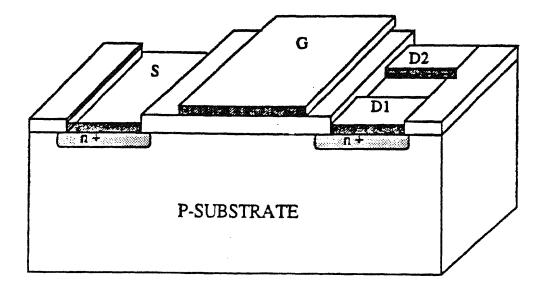

Figure 3.1 Cross-section of the NPN transistor and the NMOS transistor

## Mask Level of Stanford BiCMOS Process

Starting material is p-type <100> boron dopped wafer with 100mm in

diameter. It is a  $2\mu m$  process.

- Mask 1: n-well mask

- Mask 2: collector mask

- Mask 3: active mask

- Mask 4: n-channel field implant mask

- Mask 5: p-channel threshold adjust implant mask

- Mask 6: n-channel threshold adjust implant mask

- Mask 7: active base implant mask

- Mask 8: buried contact mask

- Mask 9: poly oxidation mask

- Mask 10: poly etch mask

- Mask 11: N+ implant mask

- Mask 12: P+ implant mask

- Mask 13: polysilicon resistor mask

- Mask 14: metallization mask, etc.

#### 3.1.3 Merged Structure in BiCMOS Technology

Key device and circuit parameters that require optimization in any application are device density, speed, reliability, and functionality at scaled supply voltages. The merged structure in BiCMOS process focuses on the issue of device density. In standard BiCMOS technology, the PMOS-NPN combination is built as shown in Figure 3.2. The PMOS FET and NPN transistor are built as seprate devices and the drain and base nodes are connected externally with a polysilicon or metal wire. In the merged structure, the external connection is removed and the devices are connected by merging the p-type base and drain in a common diffusion. Two types of merged structures have been built as shown in Figure 3.2. In the first (Figure 3.2b), the devices have been merged, but the contact to the base/drain region is preserved. This contact is often needed in circuit applications. The most compact merged structure is shown in the Figure 3.2c. In this case, there is no contact to the base/drain region. Gate to emitter spacing is determined by process design rules and the space required to isolate n+ and p+ diffusions. It has been demonstrated that the merged structure occupies 35% less area than the equivalent non-merged representations. In Stanford merged BiCMOS process, the layout constrains has been developed to allow latch-free design.

Figure 3.2 Cross-sections of the various PMOS-NPN configurations

## **3.2 3-D Magnetic Field Sensor in Non-merged Stanford BiCMOS** Technology

The 3-D MFS combines magnetotransistor together with MAGFET on a single chip. This combination has great advantages for improving the sensitivity of 3-D magnetic field sensor. The design can eliminate cross-sensitivities completely by using a MAGFET to measure a magnetic field perpendicular to the chip surface instead of the lateral magnetotransistor. The test results of a designed device is presented.

## **3.2.1 Device Structure and Simulation Results**

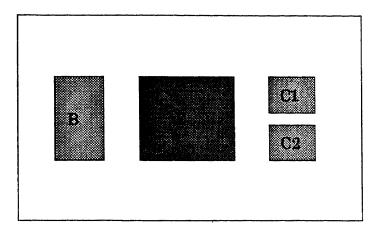

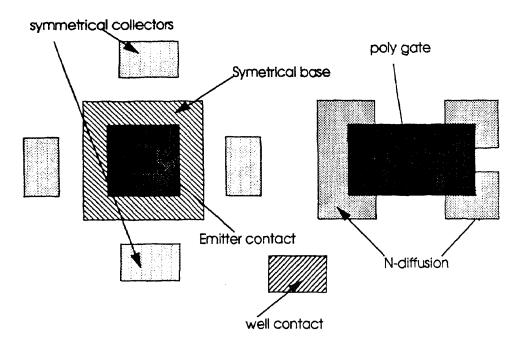

Figure 3.3 shows the top view of the BiCMOS magnetic field sensor. Two dualcollector NPN transistors are used to measure the 2 in-plane magnetic field and one NMOS MAGFET can be sensitive to the third direction. The operation of each kind of sensor is similar to what we have discussed in chapter 2 relevantly.

## **3.2.2 Layout Design and Experimental Results**

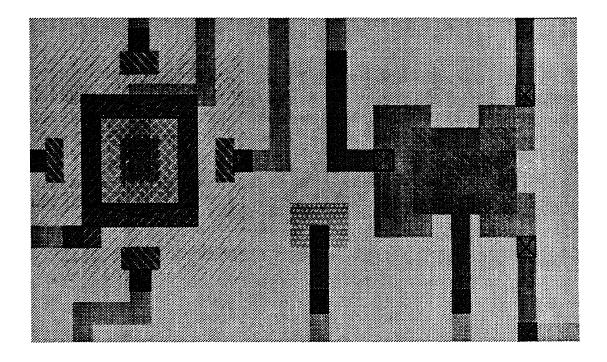

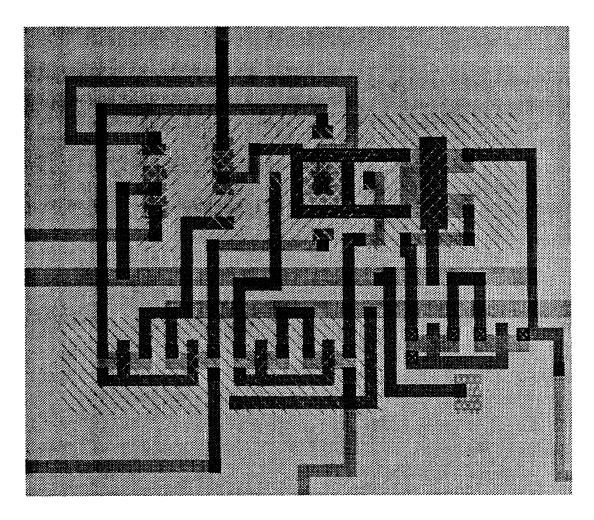

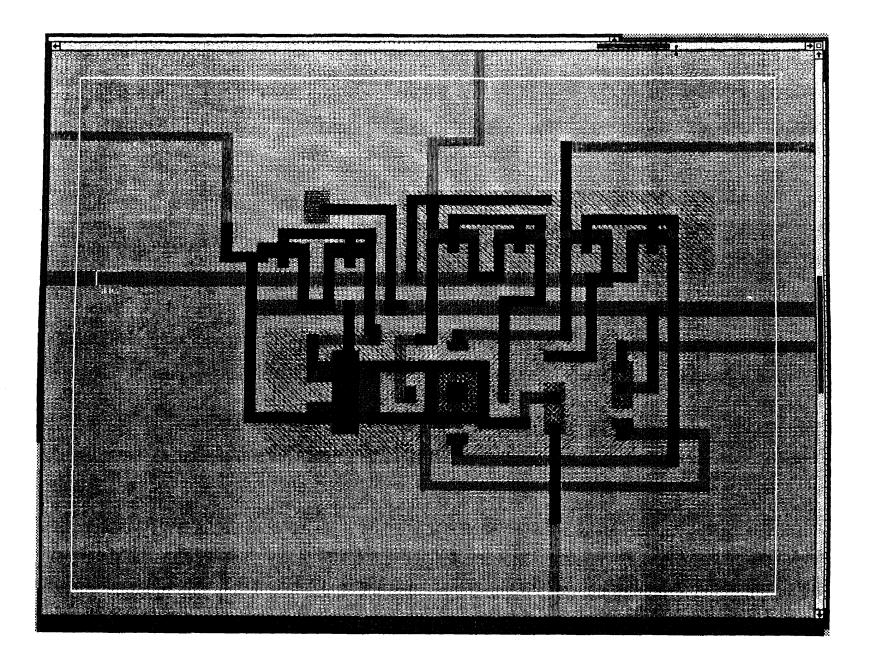

Mask design of this 3-D magnetic field sensor has been done by MAGIC version 6.3 using Stanford  $2\mu m$  n-well BiCMOS technology file. Figure 3.4 shows the final layout.

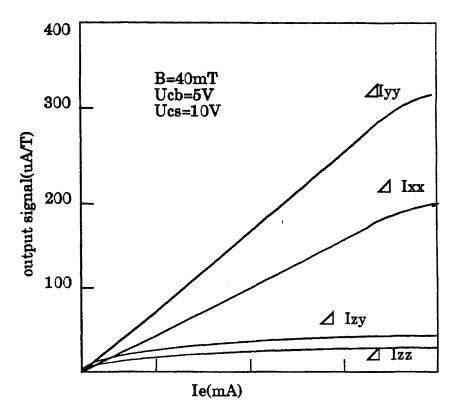

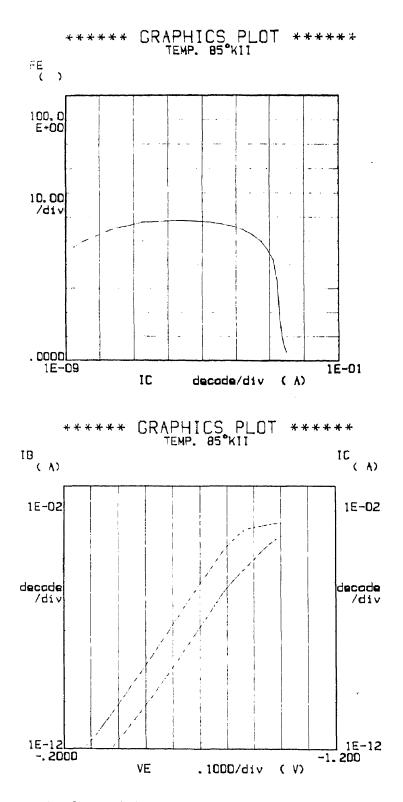

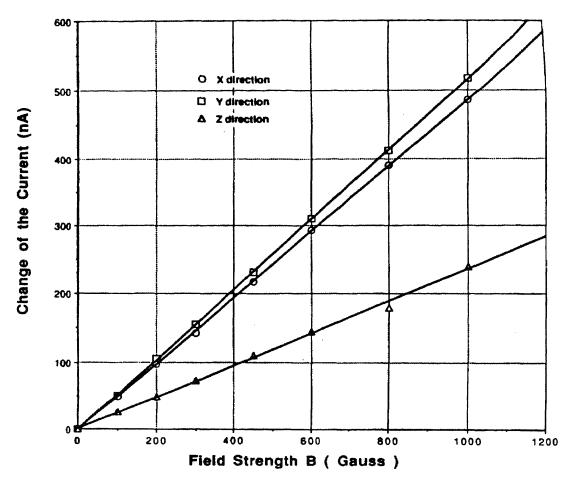

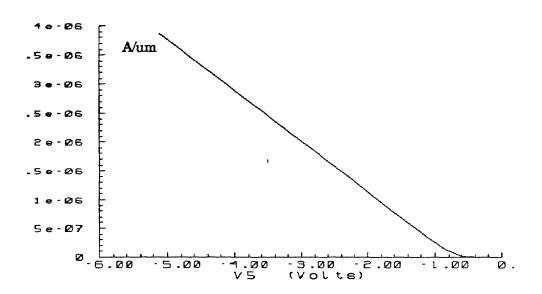

The device has been fabricated in Stanford BiCMOS process by the Integrated Circuits Lab of Stanford University. The Gummel Plots is shown in Figure 3.5. Figure 3.6 shows the measured current changes in the three terminals of the BiCMOS sensor as a function of the applied magnetic field up to 1000 Gauss. The sensor response is basically linear for the range of the field used in this experiment. Because the operating current for the magnetotransistor is greater than that of the MAGFET, we use the relative

Figure 3.3 Top View of Non-merged BiCMOS 3-D MFS

sensitivities, calculated from  $S_{ri} = -\left(\frac{\partial I_i}{\partial B_i}\right)/I_i[22]$  with  $I_i$  indicating the bias current for the different direction (i = X, Y, Z), to evaluate sensitivities of the device in three dimensions. Results show the relative sensitivity in X and Y direction are identified and of  $7.3 \times 10^{-7}/G$  whereas in Z direction it is  $2.8 \times 10^{-6}/G$ . Figure 3.7 shows the photomicrography of the tested chip.

No cross-sensitivity between any two different directions has been found. This is because the n-MOS device and npn transistor are completely isolated in the substrate by p+ isolation between the n-channel MOS device and npn bipolar transistor [20] which was instrumental in eliminating the cross-sensitivity. The disadvantage of this design is that the sensor is not a compact structure. The 3-D sensor with merged structure which is more compact is discussed in the following section.

Figure 3.4 Magic layout of 3-D Non-merged BiCMOS MFS

## 3.3 3-D Magnetic Field Sensor in Merged BiCMOS Technology

In this section, a design of a 3-D magnetic field sensor with merged structure in BiCMOS technology is given. The detailed design of the merged structure by common diffusion as well as the high gain transduction circuit are presented. The merged structure has the advantage of less area, less external contacts and less parasitic capacitance. The area of the sensing part with the merged structure is estimated to be  $25\mu m \times 48\mu m$ . The SPICE simulation results show that when a relative change in current  $\Delta I/I$  is 0.001, about 13.6mV and 8.5mV can be detected at the output in X(or Y) and Z directions, respectively. The cross-sensitivity is eliminated. The designed BiCMOS sensor can operate in the voltage scale from 0-5V with satisfactory output voltage swings. That makes the device compatible to the post signal processing circuits and can be

Figure 3.5 Gummel plot of the four collector NPN in 3-D MFS

connected directly without additional voltage transfer. For example, the sensor element can be easily integrated with the signal processing circuitry acting as

Figure 3.6 Test results of sensitivities of 3-D MFS in BiCMOS process

"smart sensors". The designed sensor has been used as an individual cell of a large sensor processing system( in chapter 4)

## **3.3.1 Device Structure and Operation**

The Stanford  $2\mu m$  BiCMOS technology has the advantage of implementing high gain polyemitter bipolar transistors. The npn-PMOS merged structure[18]-[21] has been developed and used successfully in digital BiCMOS circuits. According to the design rules of the process, in an non-merged structure, the base diffusion of npn and the source of PMOS cannot be

Figure 3.7 Photomicrography of the BiCMOS 3-D magnetic field sensor in non-merged BiCMOS technology

fabricated too closely to each other because the p-diffusion must be at least 5 micron from the edge of the n-well and the n-collector also needs to be at least 4 micron away from the n-well. In the merged structure, however, the p-base of a vertical npn bipolar transistor is merged with the p-diffusion of the PMOS transistor[20],[21], which has the advantage of a more compact device design. Not only there is an area advantage, but also the external contacts between npn and PMOS by polysilicon and metal has been removed to reduce the parasitic capacitances and resistances. A compact structure is extremely important for the design of a 3-D magnetic sensor to avoid any undesired spatial resolution due to the magnetic field gradient. It is therefore necessary to have a uniform field through out the device area.

To achieve uniform sensitivity, proper bias conditions are necessary to keep the npn transistor operating in its linear region and the PMOS transistor in its saturation region. The collector should always be kept at higher potential than that of the source of PMOS because the collector diffusion of npn transistor is in contact with the substrate (n-well) of the PMOS.

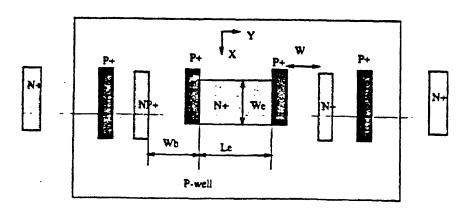

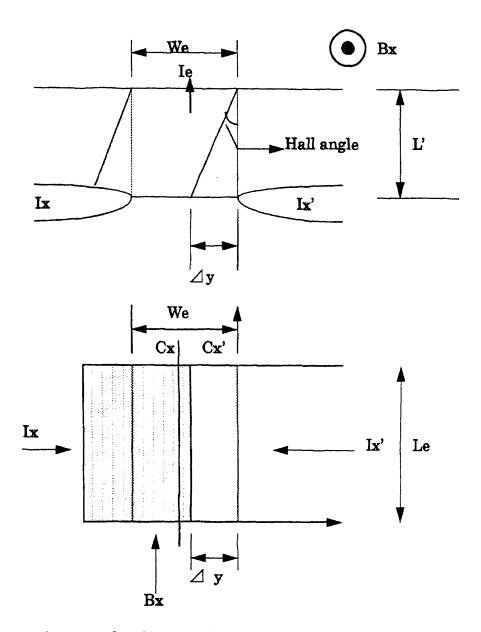

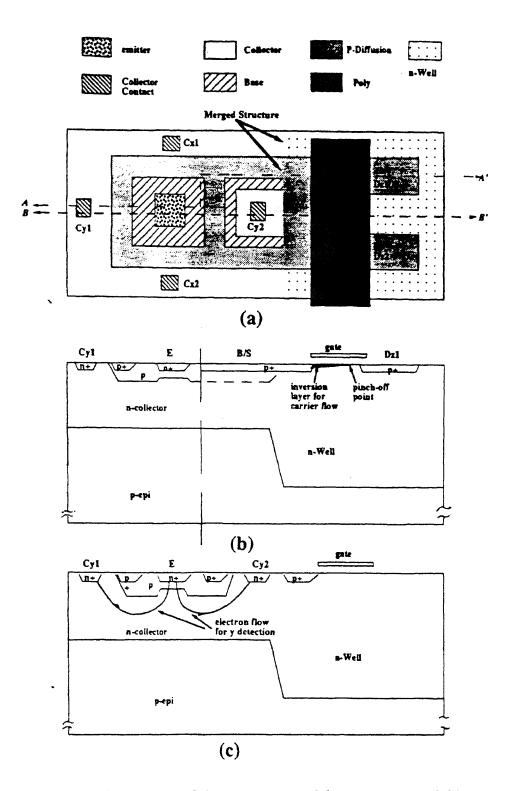

The basic three dimensional BiCMOS magnetic field sensor based on the Stanford merged process is shown in Figure 3.8. The base of the vertical npn transistor is merged with the source of the PMOS through a common p+ diffusion. The four collector contacts  $C_{x1}$ ,  $C_{x2}$ ,  $C_{y1}$ , and  $C_{y2}$  are placed symmetrically with respect to the central emitter. The base contact(p+ diffusion) is also placed symmetrically and merged with the source of the split-drain PMOS. The collector diffusion is connected with the n-well.

The device cross-section through A-A' and B-B' are shown in Figure 3.8(b) and Figure 3.8(c) respectively. The voltage bias of each electrode ensures the operation of the PMOS device in its saturation region and npn transistor in its active region. As we know, when the PMOS is operating in its saturation region, the carrier flow from source to drain is mainly taking place in the inversion layer along the  $SiO_2 - Si$  interface under the gate, as shown in Figure 3.8(b). This lateral flow is responsible for the z component of the magnetic field. When the magnetic field in z direction is absent, i.e.  $B_z$ , the currents flowing through both the drains of PMOS are equal (geometrical symmetry), i.e.  $I_{D1} = I_{D2} = I_D/2$ , where  $I_D$  is the bias current,  $I_{D1}$  and  $I_{D2}$  are the currents flowing in drain1 and drain2 respectively. However, when there is an non-zero magnetic field,  $B_z$ , the carriers flowing in the transistor

**Figure 3.8** The BICMOS merged device structure of the 3-D magnetic field sensor. (a)The top view of the device showing the symmetrical structure: the four collector contacts and the two split drains; (b)the cross-section of the device along the A-A' axis showing the merged base and the source through common p+ diffusion and connection of n-collector with n-well; (c)the cross-section of the device along B-B' axis showing the vertical component of the carrier flow, used to sense By.

are deflected, due to the Lorentz force, which is a vector product of the current and the magnetic field vector. This results in an imbalance in the current flowing through the two drains of the MAGFET. They are in the form of  $I_{D1} = I_D/2 + \Delta I_{ZZ}$  and  $I_{D2} = I_D/2 - \Delta I_{ZZ}$ , where  $\Delta I_{ZZ}$  is the current splitting as a function of  $B_Z$ . The total drain current  $I_{D1} + I_{D2} = I_D$  remains constant.

The y component of the magnetic field is responsible for the deflection of the vertical component of the collector current in the y direction (causing a collector current difference  $\Delta I_{YY}$  between the collector  $C_{y1}$  and  $C_{y2}$ , as shown in the Figure 3.8(c). Similarly the x component of the field is responsible for the deflection of the collector current in the x direction(  $\Delta I_{XX} = I_{Cx1} - I_{Cx2}$ ). The change of the currents due to the field is [14]  $\Delta I_i = 2I_{Ci}L'B_i\mu_H/W_e$  where,  $W_e$  is emitter width; and L' is mean length of the vertical collector current path.

#### **3.3.2 Sensitivity analysis**

In the device structure, since the n-collector, formed by the triple-diffusion process, is in-contact with the n-well of the PMOS(Figure 3.8(b) and Figure 3.8(c)), the cross-sensitivity could be analyzed in the following details. The lateral current in the PMOS device does not have any vertical component, therefore the response of the device to the z component of the magnetic field will be free from the cross-sensitivities from the y or x component of the field. The voltage at the  $C_{y2}$  will be modified when the y component of the field is present. The voltage modification at  $C_{y2}$  will modify the substrate voltage of the PMOS device thereby modifying the threshold voltage. Any modification of the threshold voltage will modify the device current  $I_D$ . Even if the value of the lateral current  $I_D$  is slightly changed because of the change of the substrate

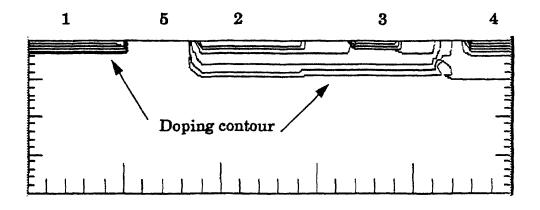

**Figure 3.9** PiscesII simulation structure. Number 1 through 5 presents the position of drain, source(merged with base), emitter, collector and gate.

Figure 3.10 Lateral doping profile through Y direction

voltage during the presence of  $B_y$ , the changes in  $I_{D1}$  and  $I_{D2}$  occur by the same amount, since the device is strictly in geometric symmetry along B-B' axis. The difference of the current between two split drains will be unchanged.

Figure 3.11 Vertical doping profile through drain of MAGFET

The other possibility of current sharing between  $C_{y2}$  and the MOS inversion layer during the presence of  $B_y$  (when  $C_{y2}$  receiving more current) can be ruled out because of the presence of the reverse biased p+ - n junction.

#### **3.3.3 PISCES simulation**

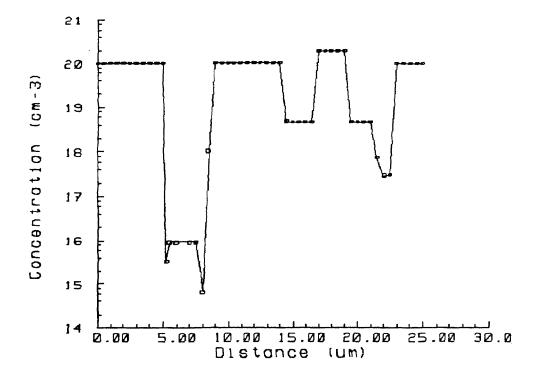

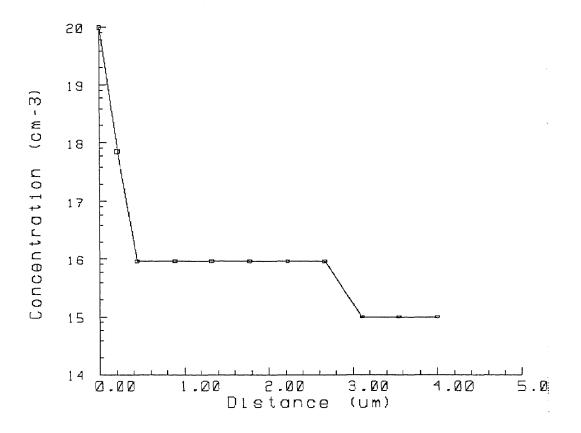

The two dimensional device simulation tool PISCES-IIB[23] has been used for the device optimization. Different sizes and distributions of the base contact

Figure 3.12 Vertical doping profile through the emitter

and emitter were designed to get an optimized geometry for improved electrical characteristics and high current gain. The process parameters such as doping concentration, gate oxide thickness, etc. determine the device response to an applied magnetic field. A fully simulated example is shown in the following Figures. Figure 3.9 shows the simulation structure for the merged 3-D MFS. Figure3.10 to Figure 3.13 show the doping profiles through different crosssections. I-V characteristics are shown in Figure 3.14 to Figure 3.16.

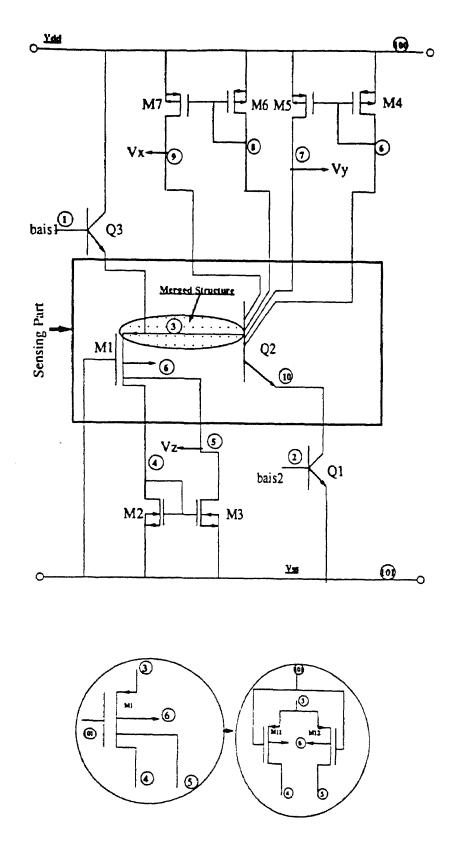

## **3.3.4 Circuit Implementation**

From the above description of the device, a proper circuit has to be designed to ensure that the device operates in an optimized state and to amplify the signals so that high sensitivities can be obtained. Figure 3.17 shows the complete circuit diagram of the 3-D magnetic field sensor. In the Figure, the transistor M1 is a split-drain PMOS whose gate is connected to Vss to ensure its operation

Figure 3.13 Vertical doping profile through the merged structure

in saturation region. This transistor is sensitive to the vertical (Z direction) magnetic field. Q2 is the vertical npn bipolar transistor with two pairs of symmetric collectors, two of them detecting the magnetic field in X direction and the other two in Y direction. Q1 and Q3 act as current sources which can provide constant currents when the biases are adjusted to keep the transistors operating in their deep active regions. Transistors M2-M3, M4-M5 and M6-M7 form the three current mirrors which act as active loads, to three different

directions, for higher impedance thus improves the absolute sensitivities of the

Figure 3.14 Base current vs. base voltage for magnetotransistor

Figure 3.15 Collector current vs. voltage of magnetotransistor

sensor.  $V_x, V_y, V_z$  indicate the outputs in three dimensions.

In the circuit design, the inherent advantages of the BiCMOS

Figure 3.16 Threshold voltage for the MAGFET

technology have been exploited. Since higher current density can be more easily achieved from bipolar transistors, two npn transistors (Q1 and Q3) are used as the current source in order to keep the sensing transistor M1 and Q2 operating in their deep saturation and active regions respectively. Meanwhile the MOSFETs are used to build three pairs of current-mirrors so that a good output voltage swing and less off-set voltage can be obtained due to the high resistive property of the MOSFET. The detailed optimization simulation of the whole 3-D Magnetic field sensor is given in the following section.

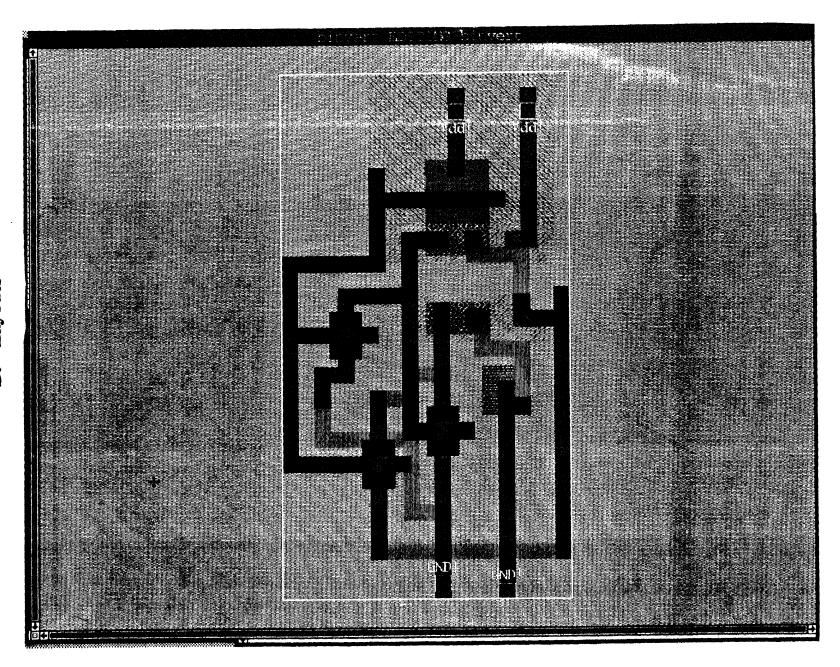

#### 3.3.5 Layout

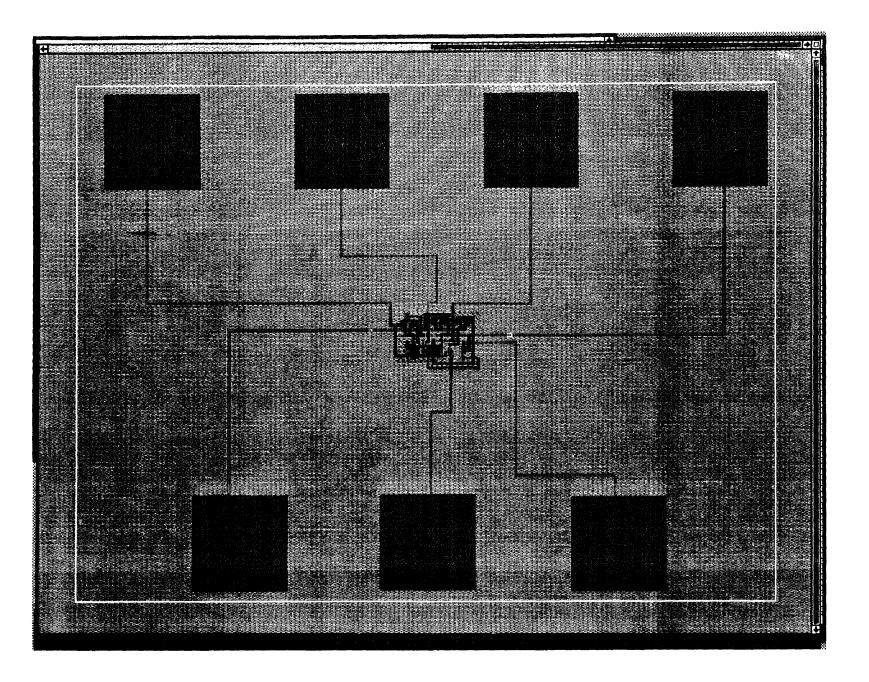

The layout has been implemented with the MAGIC V6 by using the Stanford 2  $\mu m$  BiCMOS technology file(Figure 3.18). The gate length of M1 is  $4\mu m$ , and

Figure 3.17 The circuit diagram of 3-D magnetic field sensor in merged BiCMOS technology. The transistors and the nodes are labeled for SPICE simulation. M12 and M11 are the equivalent transistors to the split-drain MAGFET in the simulatio Vx,Vy and Vz are the outputs.

the width is 12  $\mu m$  with the two symmetric drains whose areas are both 16  $\mu m^2$ . The base of Q2 is a  $12\mu m \times 12\mu m$  square surrounded by four collector contacts symmetrically. The active area of Q2 is selected as  $4\mu m \times 4\mu m$ . Both the active areas of Q1 and Q3 are  $2\mu m \times 2\mu m$ . The aspect ratio of the rest of the transistors, from M3 to M8, is unity so that the total chip area can become as small as possible. The area of the sensing part is  $48\mu m \times 25\mu m$  in the merged structure compared to  $58\mu m \times 30\mu m$  in the non-merged structure (Figure 3.4).

#### **3.3.6 SPICE Simulation**

The designed circuit has been simulated with the SPICE2.G circuit simulation package.We have assumed a linear device response to incorporate the effect of magnetic field for simulation purposes. The effect of the magnetic field manifests itself in the current density distribution in the base-collector region in a bipolar transistor[24] and in the pinch-off region of a split-drain MOSFET. The magnetic field modulation of the emitter injection is assumed negligible and carrier deflection was considered to be the dominant mechanism for the linear magnetic response. Possible nonlinearities in response, due to magnetoconcentration effect[24] is neglected in our SPICE simulation.

The objective of the simulations are:

(1)To determine the DC operating conditions with suitable bias voltages when Vdd=5V,Vss=0V;

(2)to determine the gains with the active load circuits.

(3)to determined the frequency response of the designed 3-D magnetic filed sensor.

The circuit description used for SPICE simulation was directly extracted from the device layout to include all the parasitic capacitance in the

**Figure 3.18** Magic layout of the 3-D magnetic Field sensor with voltage output circuit in merged BiCMOS technology

design. The simulation also uses the most updated Stanford BiCMOS parameter models. The labeled nodes for simulation and the equivalent circuits for the split-drain PMOS and four-collector npn transistor are shown in Figure 3.17.

## 1) Bias Voltages Simulation

The bias conditions were chosen to ensure that all MOSFETs are operating in saturation and all bipolar transistors operating in the forward active regions.

Meanwhile the bias conditions are also optimized to ensure the three outputs have their possibly maximum voltage swing. The detailed simulation results are shown in the following tables. Here the gate of the MAGFET is connected to 0V, node 4 and bias2 respectively. At each case, both bias conditions bias1 and bias2 are set at different values during simulation. The detailed simulation results are listed in following tables respectively. The node voltages are listed for analysis of the DC operation states of every transistors. Obviously, V(4)=V(5), V(6)=V(7)=V(8)=V(9) when no magnetic field appears. So, in the following tables, only V(3), V(4), V(6) and V(10) are listed when different bias conditions are applied.

|        | Bias voltage(v) |        | Node voltage(v) |        |        |        |  |

|--------|-----------------|--------|-----------------|--------|--------|--------|--|

|        | Bias1           | Bias2  | V(3)            | V(4)   | V(6)   | V(10)  |  |

| case 1 | 3.7500          | 0.7800 | 2.9811          | 1.0208 | 3.5043 | 2.2793 |  |

| case 2 | 4.0000          | 0.8000 | 3.2189          | 1.1309 | 3.3866 | 2.4994 |  |

| case 3 | 4.4000          | 0.7800 | 3.6068          | 1.2678 | 3.4879 | 2.9027 |  |

**Table 2** Voltage Distribution with the Gate of the MAGFET(M1) Connected to Node 4

Table 3 voltage distribution with gate of MAGFET (M1) connected to node 101

|        | Bias voltage(v) |        | Node voltage(v) |        |        |        |  |

|--------|-----------------|--------|-----------------|--------|--------|--------|--|

|        | Bias1           | Bias2  | V(3)            | V(4)   | V(6)   | V(10)  |  |

| case 1 | 3.2300          | 0.7800 | 2.4447          | 1.2073 | 3.5187 | 1.7450 |  |

| case 2 | 4.0000          | 0.8000 | 3.1821          | 1.6042 | 3.2202 | 2.4627 |  |

| case 3 | 4.4000          | 0.8000 | 3.4718          | 1.7394 | 3.2102 | 2.7512 |  |

From table 2, in case2, we can see the V(6) is very near V(3), so the Q2

is hardly working in its active region; when we increase the bias1 more, as in case 3, the Q2 is totally cut off. In case 1, we can see, Q2 is working in its active region, and M1 is also working in its saturation region, as we desire, because the voltage drop between drain and source of M1 is greater than 0.8v, which is the threshold voltage value of this PMOS transistor. The other node voltages also show that all the load MOS transistors are working in their saturation region. Meanwhile Q3 and Q1 are both working in their active region which are expected to provide constant currents to M1 and Q2 for detecting of magnetic field vector.

|        | Bias Voltage(v) |        | Node Voltage(v) |        |        |        |  |

|--------|-----------------|--------|-----------------|--------|--------|--------|--|

|        | Bias 1          | Bias2  | V(3)            | V(4)   | V(6)   | V(10)  |  |

| case 1 | 3.5000          | 0.7200 | 2.7360          | 1.6473 | 3.8997 | 2.0734 |  |

| case 2 | 4.0000          | 0.7500 | 3.4956          | 1.4204 | 3.9622 | 2.8395 |  |

| case 3 | 4.5000          | 0.7800 | 3.6852          | 1.5464 | 3.4859 | 2.9807 |  |

**Table 4** Voltage Distribution with the Gate of MAGFET Connected to Bias2

Now let us take a look of the output voltage swings. Under all the transistors work in their required region, from Figure 3.17, we can see the Z direction output voltage can swing from 0.8v to 2.18v(which is calculated from V(3)-Vth), so the swing value is about 2.18-0.8=1.38v. As to the x and y direction, the lowest voltage permitted at node 6 or 7 is 2.2793+1.0000 = 3.2793v (which ensure Q2 still in its required region), so the voltage swing can be 5-0.8-3.2798=0.9202v.

The same analysis can be applied on the table 3 and table 4. For table 3, the circuit configuration set the gate of MAGFET M1 to 0v. That makes the M1 working in more saturation region compared to table 2 case. In table 3, case 2 and case 3 are no good because at these bias conditions, Q2 is nearly not working in the required region. In case 1, the voltage swing in Z direction is 2.4047-0.8-0.8=0.8047v, and the voltage swing in X and Y directions should be 5-2.7450-0.8=1.455v.

In table 4, as calculated, the gate of M1 is connected to bias2, whose voltage is between V(4) and V(101). From the obtained data, we can see, all three bias condition can make the circuit working in required situation. Of course, the bias conditions in case 1 provides best results. At this time, the voltage swing in Z direction is 1.1360v, and the voltage swings in X and Y direction cab be 1.1263v. So the voltage swing in X, Y and Z direction have closer value than in case of table 2 and table 3.

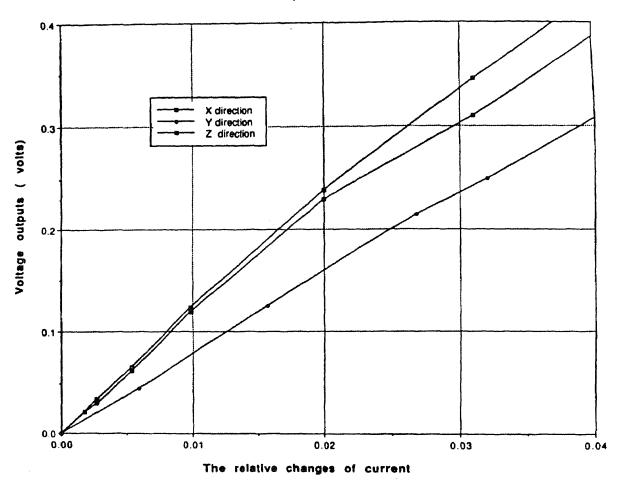

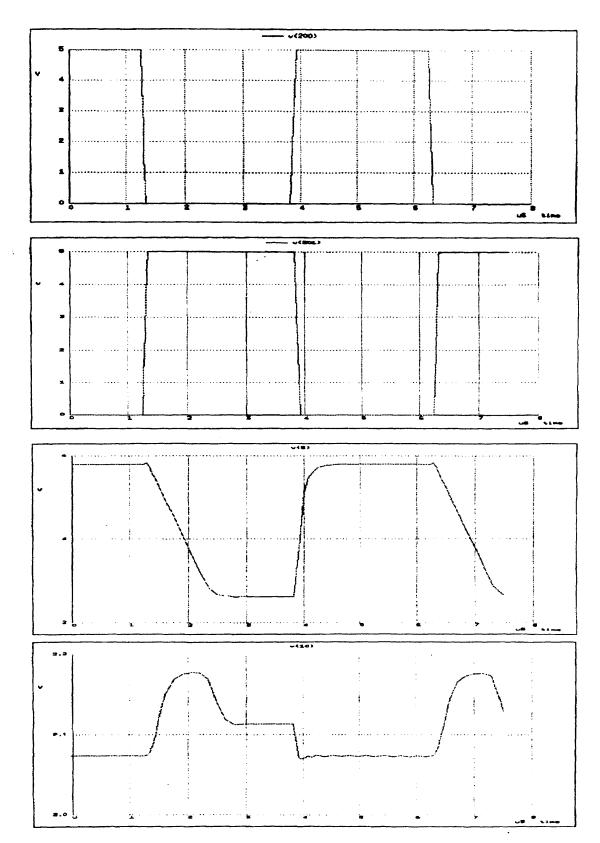

#### 2) Sensitivity gain simulation

Because the SPICE can not simulate the magnetic field parameter directly, in our simulation, a very slight difference between the aspect ratios(W/L) of M12 and M11 in the SPICE input card is made. As the effect of magnetic field is represented by current density distribution[24], it can be taken into account qualitatively through an artificial current asymmetry. The quantitative representation was selected through the experimental results of the device as discussed in previous section. A small change of current  $\Delta I$  between two drains was introduced, i.e.:  $I_{D1} = I + \Delta I, I_{D2} = I - \Delta I$ , which is analogous to the situation caused by the applied magnetic field. A similar procedure has been applied to Q2 by making a very small change of the active areas. The relative sensitivities of X, Y, Z directions are proportional to the relative changes of current,  $\Delta I/I$ , and thereby proportional to  $\Delta V/V$ . The response of the sensor to the magnetic field vector is, therefore represented through the gain of the circuit, as shown in the Figure 3.19. When a relative change in current  $\Delta I/I$

Data from Spice simulation

**Figure 3.19** SPICE simulation results showing the possible current splitting in the 3-D merged BiCMOS sensor circuit.

is 0.001, about 13.6mv and 8.5mv can be detected at the output in X(or Y) and Z directions respectively. The non-linearity in Figure 3.19 is due to the modifications of the dc operating bias conditions of the corresponding nodes where the MOS and bipolar transistors are driven into the linear and saturation region respectively.

## 3) Frequency Response Simulation

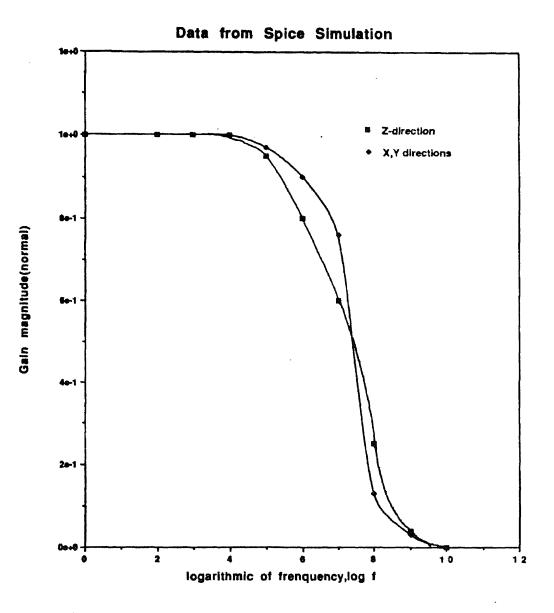

To verify the ability of the circuit to sense a time varying magnetic field, the frequency response has been estimated. All the capacitances simulated, are directly included from the circuit layout. The result is shown in Figure 3.20

Figure 3.20 Frequency response of the 3-D merged magnetic field sensors circuit

# CHAPTER 4 3-D MAGNETIC FIELD SENSOR ARRAY AND ITS APPLICATION

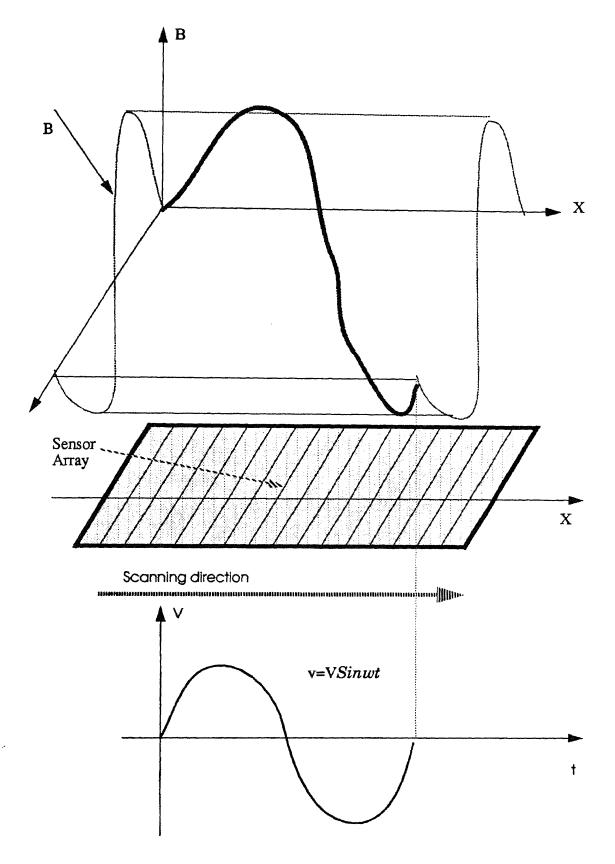

As mentioned in chapter 1, the integration of sensor technology and information processing circuitry is a goal which has great importance in implementation of computer vision system as well as robotic tactile sensing system. This chapter describes the development of a high resolution integrated magnetic field sensor array, where the 3-D merged BiCMOS magnetic field sensor, which has been discussed in last chapter, is used as an individual cell(build block). System architecture and circuit configuration are presented. Two applications of the designed array are described.

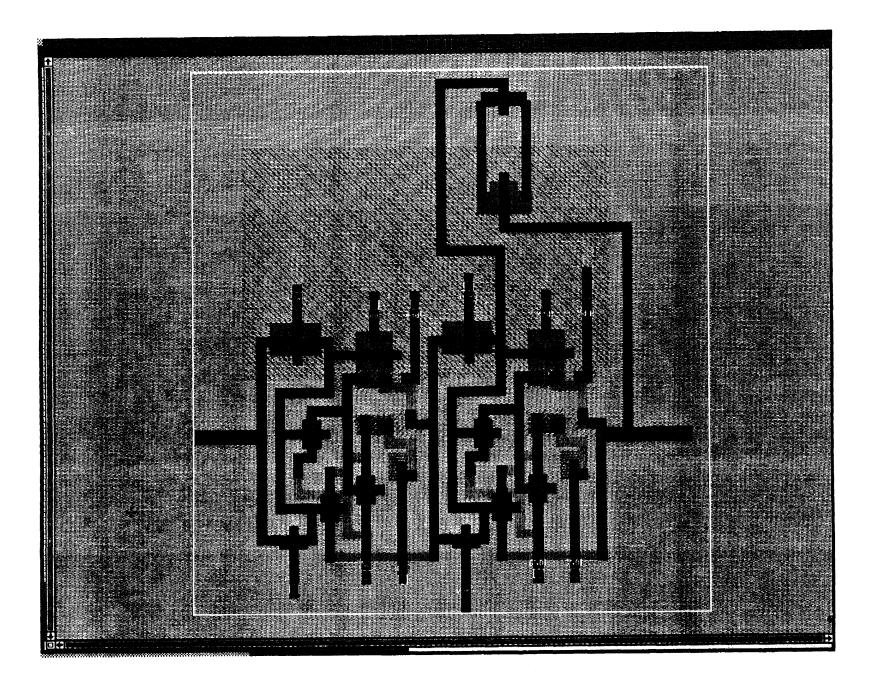

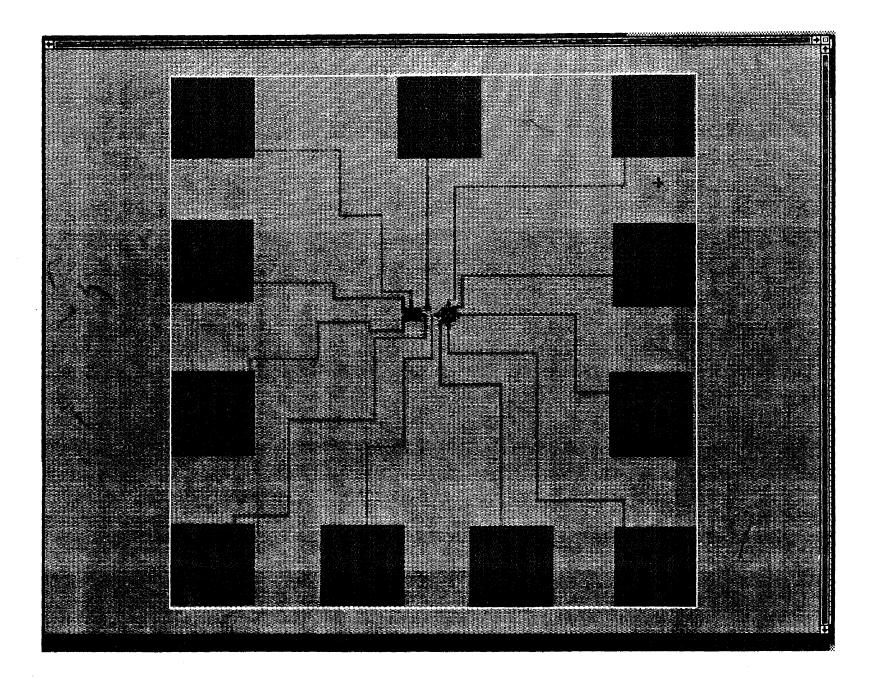

## **4.1 System Operation**

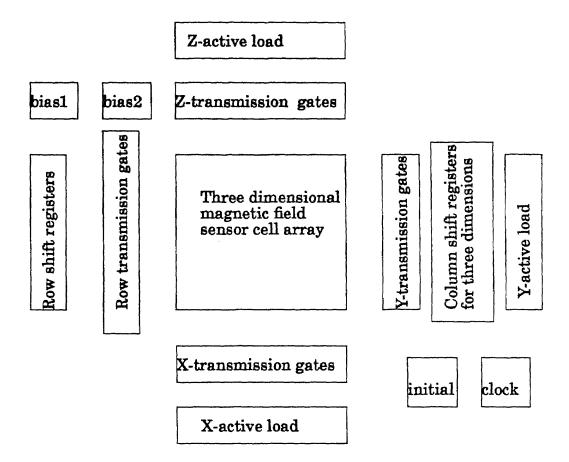

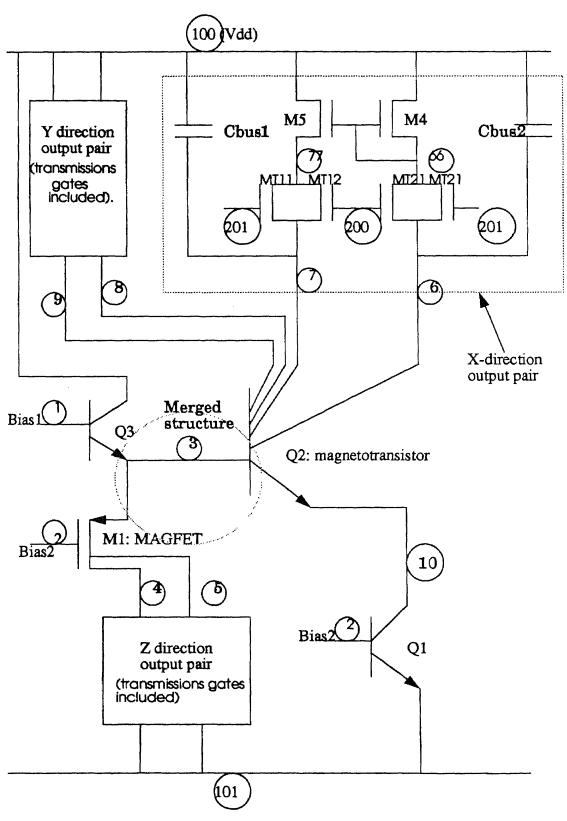

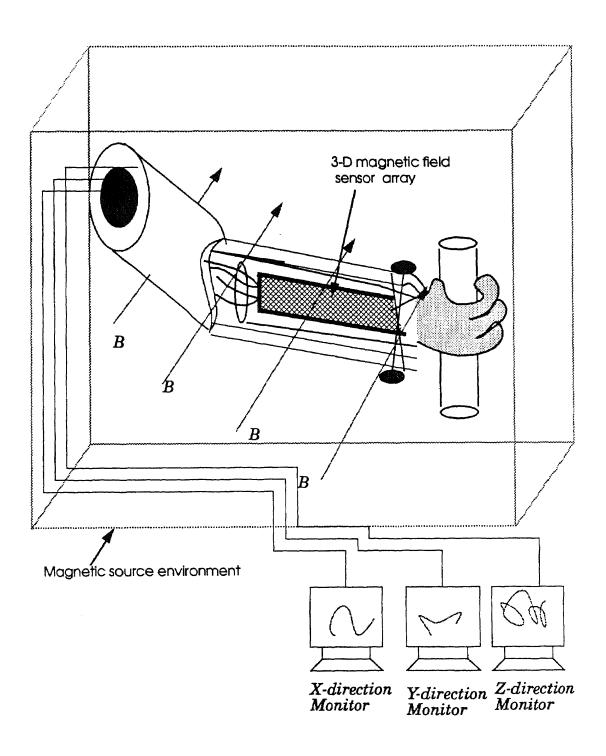

The system architecture is shown in Figure 4.1. It is basically composed the main cell array, one row selection, three column selections ( for three dimensions respectively), active loads and input/output buffers. One column selection circuit is used all three directions x, y and z, because the sensing signals from three dimensions are expected to output simultaneously. The current mirror(CM) is used as the active load, and the 3-D merged BiCMOS magnetic field sensor described in last chapter is used as the cell(MC) in the array(Figure 3.17).

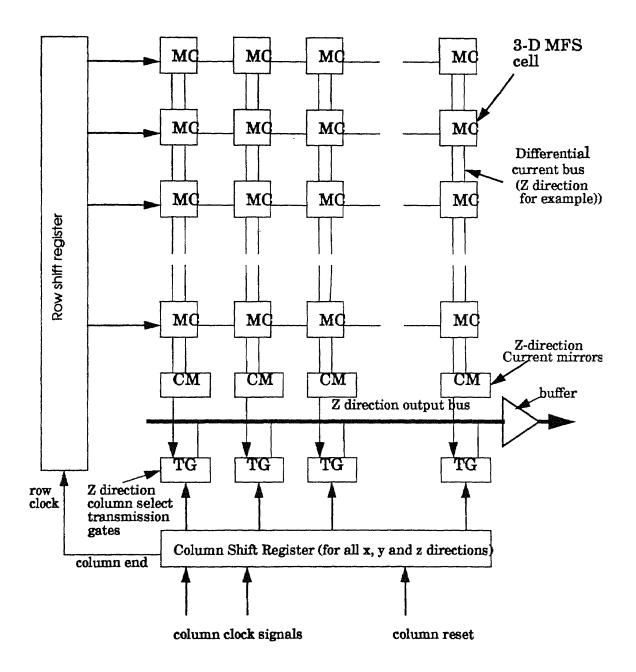

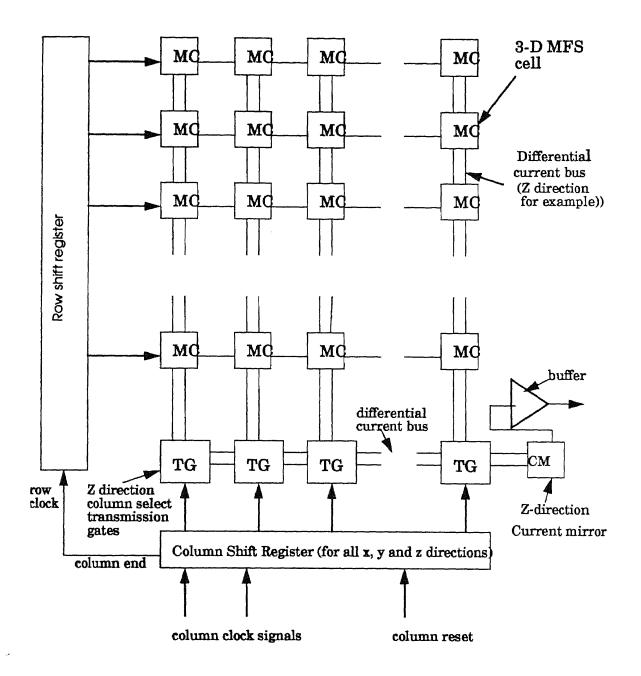

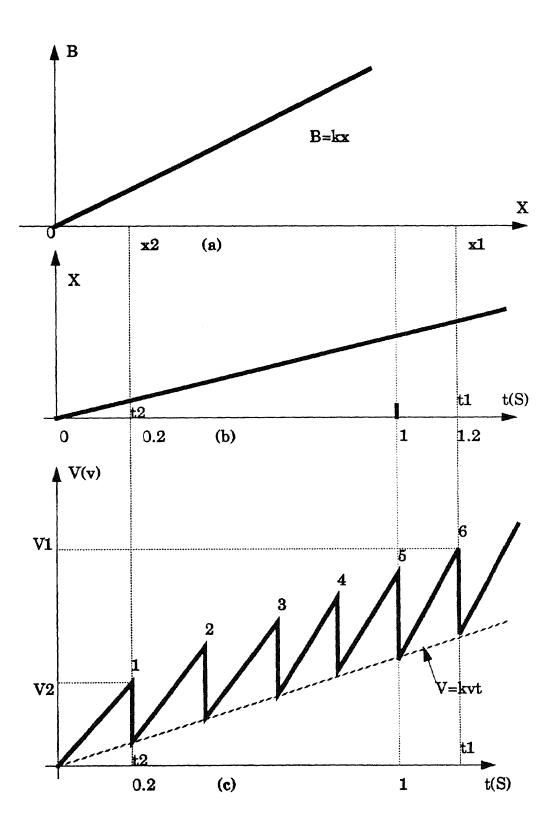

The cell array is scanned in a raster scan fashion. Two slightly different scanning methods are proposed in Figure 4.2 and Figure 4.3, respectively. because the scanning structure are strictly symmetrical in x, y and z direction(Figure 4.2 and Figure 4.3), only one direction in each Figure is

drawn for explanation of the scanning methods.

Figure 4.1 System structure

In both Figures, shift registers along the left-hand side of the circuit shift a single "turn-on" bit, which allows current to flow through all the sensor cells in a single row. The current (actually there are three currents for x, y and z directions respectively, here we can select any one of them for illustration, like Z direction) through a cell is controlled by a switchable current source as shown in Figure 4.4. When the row select buffer is turned on, the bias voltages  $V_{Bias1}$  and  $V_{Bias2}$  are applied to the bases of Q3 and Q1( refer to the cell circuit in Figure 3.17). When the row select buffer is turned off, Vss is

Figure 4.2 The scanning circuitry A:.Each column has current mirror (note: For a clear view, only Z direction current buses are drawn in the Figure, the X and Y direction are similar, they both have other two sets transmission gates and current mirrors, but share the same column shift registers as Z direction's)

applied to the bases of Q1 and Q3, cutting off the flowing current through the 3-D sensor cells in that row.

As the scan proceeds, successive rows are turned on. Only one row at a time is on. Shift registers along the bottom shift a single "column-select" bit, which selects the output of one column at a time. In Figure 4.2, all devices in a given column share a single current mirror transistance amplifier located at the bottom of the column( in x, y directions, the current mirrors are put in the top side and right side respectively, which are not shown in the Figure)Since only one row is on at a time, these current mirrors have current flowing through them from one cell only. The row shift register is shifted only when a

Figure 4.4 The switchable current source supplying the 3-D MFS

complete column scan has been finished. The column shift register is shifted by an external clock signal. The outputs (x, y and z) of the selected cell current is amplified and buffered before it is sent to an analog output pad. The shift registers are initialized by a reset pulse.