# New Jersey Institute of Technology Digital Commons @ NJIT

#### Theses

Theses and Dissertations

Spring 1995

# Radiation damage studies in gate oxides

Sandeep G. Bharathi New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/theses Part of the <u>Electrical and Electronics Commons</u>

#### **Recommended** Citation

Bharathi, Sandeep G., "Radiation damage studies in gate oxides" (1995). *Theses*. 1166. https://digitalcommons.njit.edu/theses/1166

This Thesis is brought to you for free and open access by the Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Theses by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

#### **RADIATION DAMAGE STUDIES IN GATE OXIDES**

Detailed investigation of the effects of Gamma-ray irradiation on the electrical properties such as current-voltage and capacitance-voltage characteristics in thermally grown SiO<sub>2</sub> films in the thickness range of 15 to 120 nm on silicon substrates is presented in this thesis. The structures used in this study are Al/Poly/SiO<sub>2</sub>/Si/Al and Al/SiO<sub>2</sub>/Si/Al MOS capacitors. Based on the electrical characterization studies, we observe that irradiation causes generation of positive charges in the oxide leading to a shift of the high frequency Capacitance-Voltage (C-V) curves. An increase in surface state density at the SiO<sub>2</sub>-Si interface with increase in radiation dose is also observed. Static current-voltage (I-V) characteristics lead to a further insight in the formation of radiation induced oxide traps. Fowler-Nordheim tunneling in irradiated MOS structures is investigated.

by Sandeep G. Bharathi

### A Thesis

Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirement for the Degree of Master of Science in Electrical Engineering

Department of Electrical and Computer Engineering

May 1995

#### APPROVAL PAGE

#### **RADIATION DAMAGE STUDIES IN GATE OXIDES**

Sandeep G. Bharathi

Dr. N. M. Ravindra, Thesis Advisor Associate Professor of Physics, New Jersey Institute of Technology Date

Dr. Walter F. Kosonocky, Committee Member Distinguished Professor Foundation Chair of Optoelectronics and Solid State Circuits New Jersey Institute of Technology

Dr. Marek Sosnowski, Committee Member Associate/Professor of Electrical Engineering, New Jersey Institute of Technology Date

. Date

#### **BIOGRAPHICAL SKETCH**

Ì

| Author: | Sandeep G. Bharathi                         |

|---------|---------------------------------------------|

| Degree: | Master of Science in Electrical Engineering |

| Date:   | May 1995                                    |

#### Undergraduate and Graduate Education

- Master of Science in Electrical Engineering, New Jersey Institute of Technology Newark, New Jersey, 1995

- Bachelor of Science in Electronics Engineering, Bangalore University Bangalore, India, 1992

- Major: Electrical Engineering

This thesis is dedicated to my Parents

#### ACKNOWLEDGMENT

I express my profound gratitude to Dr. N. M. Ravindra for his ingenious contributions, invaluable guidance, and moral support throughout this work and for financial support during my graduate study. His constant counsel and advice to me has been peerless.

I wish to thank Dr. W. F. Kosonocky and Dr. Marek Sosnowski for willing to be on my thesis committee. I also thank Dr. K. R. Farmer for his help during the experimental stage.

I acknowledge the contributions of Michael Metzger and Alex in providing invaluable data required for my research. I would like to thank Arun, Akhila, Bijal, Chetan, Sam, Vivek for all their moral support and their spirits.

I am grateful to Dr. Eng Kie Souw of Brookhaven National Labs for providing the gamma-ray radiation facility. I thank Mike Greico and John Koons of the Microelectronics Research Center, New Jersey Institute of Technology for providing the fabricated devices used in this study.

Last but not least, I am indebted to my aunts Nalini Jayaram and Amba Murthy for their financial and moral support during the entire course of my graduate study.

# TABLE OF CONTENTS

| Cł | hapter                                                    | Page |

|----|-----------------------------------------------------------|------|

| 7  | INTRODUCTION                                              | 1    |

|    | 1.1 Background                                            | 1    |

|    | 1.2 Outline of Remaining Chapters                         | 10   |

| 2  | OXIDATION KINETICS                                        | 11   |

|    | 2.1 Introduction                                          | 11   |

|    | 2.2 Classical Theory of Oxidation of Silicon              | 11   |

|    | 2.3 Chemical Structure of SiO <sub>2</sub>                | 13   |

|    | 2.4 Other Aspects of Thermal Oxidation and CVD Deposition | 17   |

| 3  | FUNDAMENTALS OF MOS STRUCTURE                             | 19   |

|    | 3.1 Introduction                                          | 19   |

|    | 3.2 Ideal MOS Structure                                   | 20   |

|    | 3.3 Effects of Real Surfaces                              | 23   |

| 4  | ELECTRICAL CHARACTERIZATION TECHNIQUES                    | 26   |

|    | 4.1 Introduction                                          | 26   |

|    | 4.2 C-V Measurements                                      | 26   |

|    | 4.3 Oxide charges and their Measurement Methods           | 34   |

|    | 4.3.1 Interface Trapped Charge (Q <sub>it</sub> )         | 34   |

|    | 4.3.2 Quasi Static Method                                 | 34   |

|    | 4.3.3 Conductance Method                                  | 36   |

|    | 4.3.4 Other Methods to Measure D <sub>it</sub>            | 36   |

|    | 4.3.5 Oxide Trapped Charge (Q <sub>ot</sub> )             | 37   |

|    | 4.3.6 C-V Method                                          | 37   |

|    | 4.3.7 Photo I-V Method                                    | 38   |

|    | 4.3.8 Mobile Charge and Fixed Charge                      | 38   |

# TABLE OF CONTENTS (Continued)

| Chapter Pag                                                            | je |

|------------------------------------------------------------------------|----|

| 4.4 I-V Measurements                                                   | 8  |

| 4.4.1 Conduction Process and Breakdown Statistics of Thin Insulators   | 9  |

| 4.4.2 Fowler-Nordheim Tunneling (FNT) in Thin SiO <sub>2</sub> Films   | 0  |

| 5 EXPERIMENTAL PROCEDURE 4                                             | 2  |

| 5.1 Fabrication of the MOS Capacitor                                   | 2  |

| 5.2 Oxide Thickness Measurement                                        | 4  |

| 5.3 Method of Radiation                                                | 4  |

| 5.4 Electrical Measurement Techniques                                  | 5  |

| 6 RESULTS AND DISCUSSION                                               | 6  |

| 6.1 Introduction                                                       | 6  |

| 6.2 Kinetics of Oxidation                                              | 6  |

| 6.3 Capacitance-Voltage Analysis 4                                     | 7  |

| 6.4 Current-Voltage Analysis                                           | 7  |

| 7 CONCLUSIONS 6                                                        | 5  |

| APPENDIX A: High Frequency & Quasi-Static CV Plots                     | 7  |

| APPENDIX B: Interface Trap Density (D <sub>it</sub> ) Plots            | 4  |

| APPENDIX C: Static IV Plots                                            | 8  |

| APPENDIX D: Process Summary                                            | 4  |

| APPENDIX E: Nanospec / AFT Automatic Film Thickness Measurement System | 9  |

| APPENDIX F: Oxide Thickness Versus Time Plots                          | 1  |

| REFERENCES                                                             | 3  |

# LIST OF TABLES

| Tabl | le                                                                                  | Page |

|------|-------------------------------------------------------------------------------------|------|

| 1.1  | Overview of some of the radiation damage studies performed in the past thirty years | 3    |

| 4.1  | Basic conduction process in insulators                                              | 39   |

| 6.1  | Summary of the HF and quasi-static CV characterization on type I device structures  | 49   |

| 6.2  | Summary of the HF and quasi-static C-V on type II device structures                 | 50   |

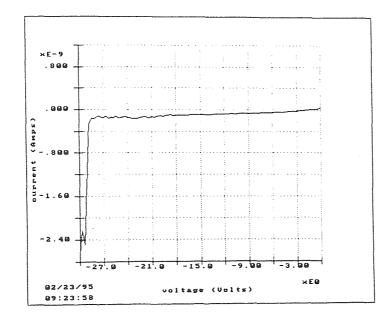

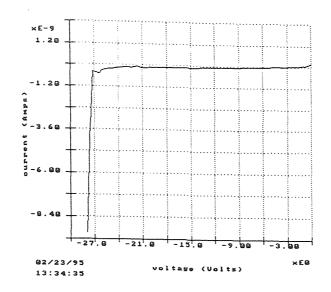

| 6.3  | Summary of the static I-V characterization on type I device structures              | 58   |

| D.1  | Gate1 / LPCVD Polysilicon                                                           | 84   |

| D.2  | Poly doping for type I device structure                                             | 85   |

| D.3  | Aluminum deposition                                                                 | 86   |

| D.4  | Photolithography- Metal                                                             | 86   |

| D.5  | Wet etch aluminum process                                                           | 87   |

| D.6  | RIE- Polysilicon                                                                    | 87   |

| D.7  | Aluminum (front side protect)                                                       | 88   |

| D.8  | Aluminum deposition (back side only)                                                | 88   |

# LIST OF FIGURES

| Figu | re                                                                                                                                                                                                                        | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

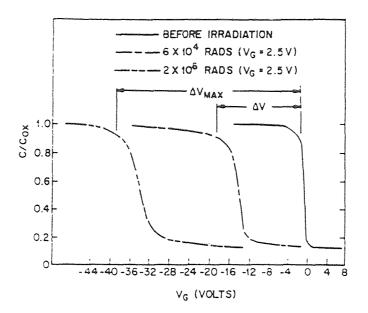

| 1.1  | Shift of MOS capacitor C-V curves for two different doses of radiation under the same positive gate bias                                                                                                                  | 8    |

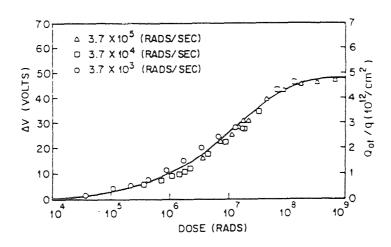

| 1.2  | Shift of C-V characteristics of a MOS capacitor and the coresponding oxide trapped charge for different doses of radiation                                                                                                | 8    |

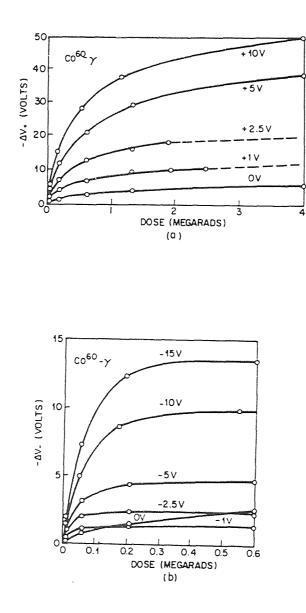

| 1.3  | Shift of C-V curves for a MOSFET along the voltage axis as a function of $\gamma$ ray dose (Co-60) (a) positive aging gate bias; (b) negative aging gate bias                                                             | 9    |

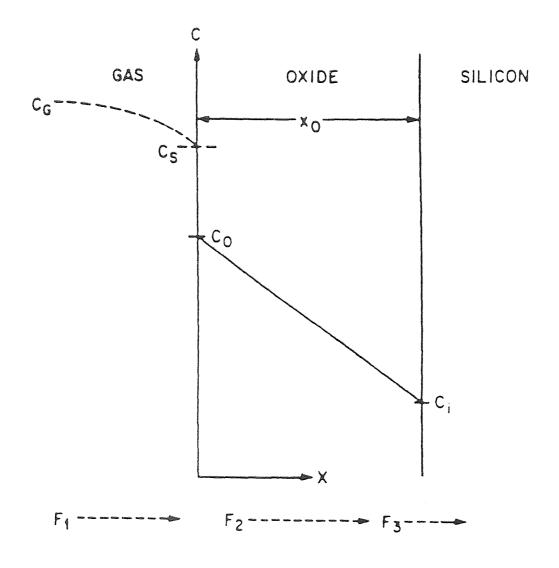

| 2.1  | Cross section of silicon with a growing $SiO_2$ layer illustrating the model for thermal oxidation of silicon. The three fluxes, $F_1$ into the silica, $F_2$ through the silica, and $F_3$ at the $SiO_2$ -Si interface. | 12   |

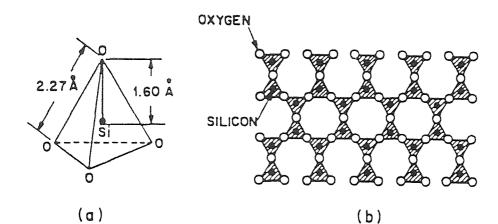

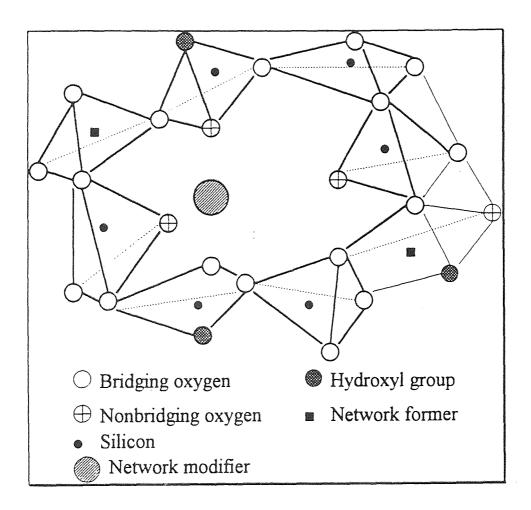

| 2.2  | (a) Basic structural unit of SiO <sub>2</sub> ; (b) Two dimensional representation of a quartz crystal lattice; (c) Two dimensional representation of the amorphous structure of SiO <sub>2</sub>                         | 14   |

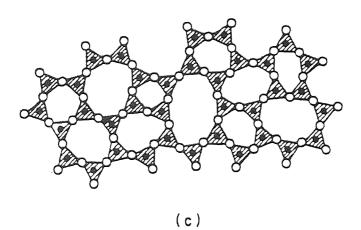

| 2.3  | The structure of fused silica glass                                                                                                                                                                                       | 16   |

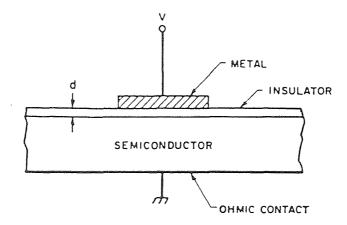

| 3.1  | Metal-oxide-semiconductor (MOS) structure                                                                                                                                                                                 | 19   |

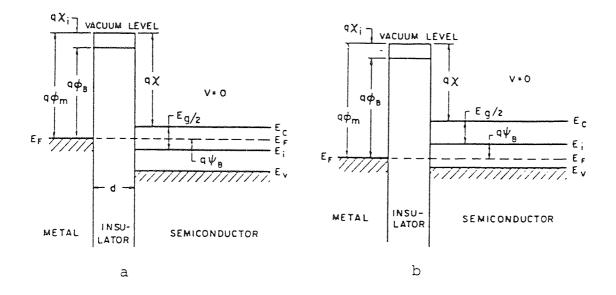

| 3.2  | Energy-band diagrams of ideal MOS capacitors at V=0. (a) n-type semiconductor; (b) p-type semiconductor                                                                                                                   | 20   |

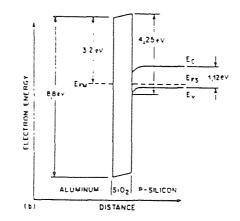

| 3.3  | Energy-band diagram of the MOS capacitor showing the energy barrier between metal and $SiO_2$ and between silicon and $SiO_2$                                                                                             | 21   |

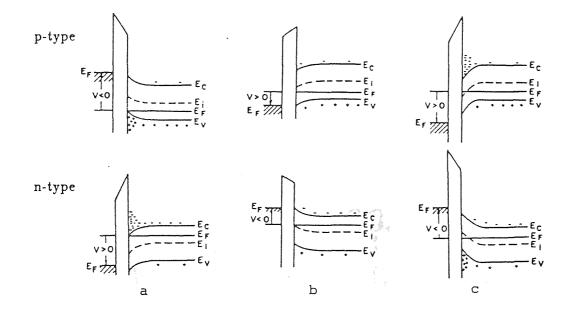

| 3.4  | Energy-band diagrams for ideal MOS capacitor when $V \neq 0$ , for the following cases (a) accumulation; (b) depletion; (c) inversion                                                                                     | 22   |

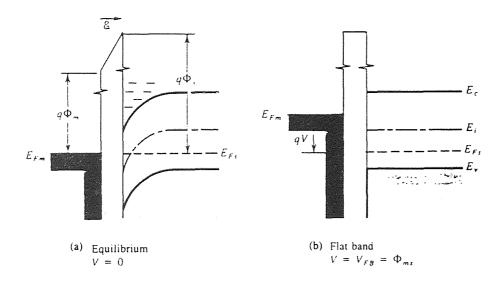

| 3.5  | Energy-band diagrams for negative work function difference. (a) Band bending at equilibrium; (b) Flat band condition for negative applied volatge                                                                         | 23   |

| 3.6  | Charges and their locations for thermally oxidized silicon                                                                                                                                                                | 24   |

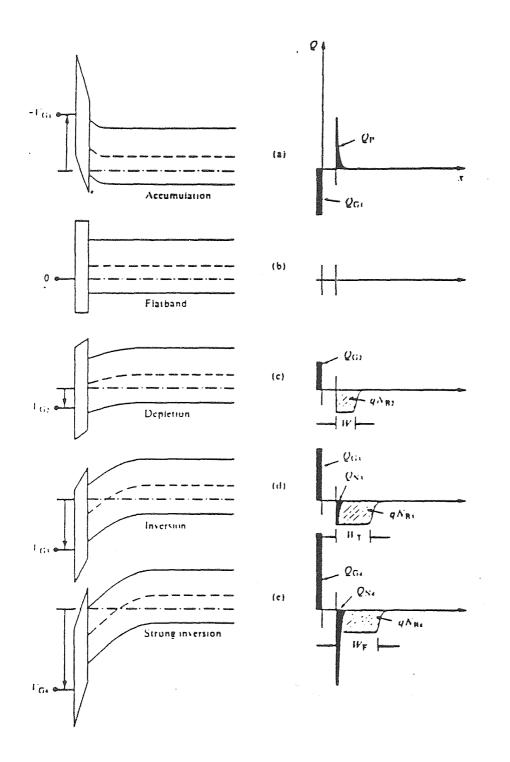

| 4.1  | Energy-band and charge-distribution diagrams for an MOS capacitor on a p-type substrate in (a) accumulation; (b) flatband; (c) depletion; (d) weak inversion and (e) strong inversion                                     | 27   |

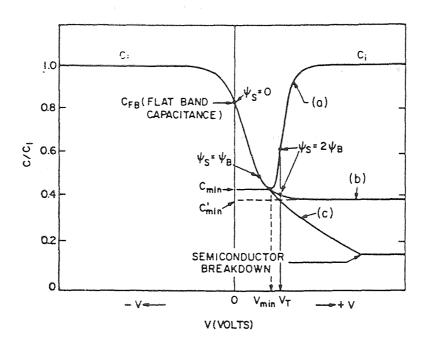

| 4.2  | MOS capacitance-voltage curves: (a) Low frequency; (b) High frequency; (c) Deep depletion                                                                                                                                 | 28   |

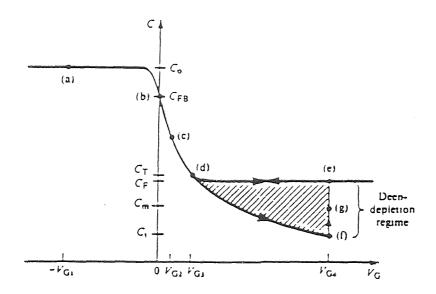

| 4.3  | Capacitance-gate voltage curves for MOS capacitor                                                                                                                                                                         | 28   |

| Figu        | re                                                                                                                   | Page |

|-------------|----------------------------------------------------------------------------------------------------------------------|------|

| 4.4         | Cross section and energy band diagram of an MOS capacitor                                                            |      |

| 4.5         | Capacitances of an MOS capacitor for various bias conditions                                                         |      |

| 4.6         | Quasi-static and High-frequency C-V curves used to determine the surface state density in the depletion region       | 35   |

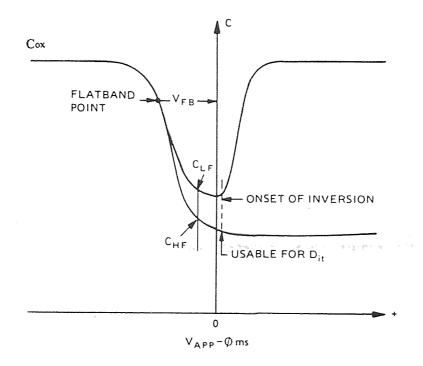

| 5.1         | Process steps for a MOS capacitor array (a) with Al/poly gate, (b) with Al gate only                                 | 43   |

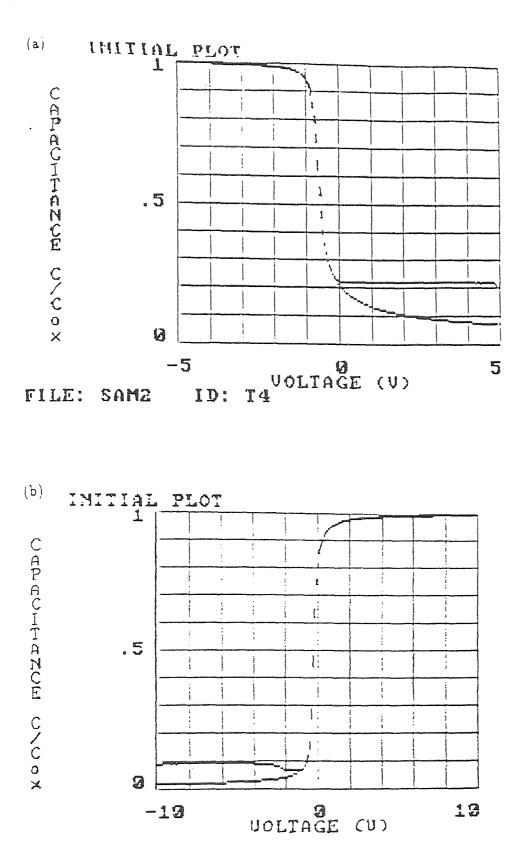

| 6.1         | A representative experimental 1 MHz C-V curve of a MOS capacitor<br>(a) p-type Si substrate; (b) n-type Si substrate | 48   |

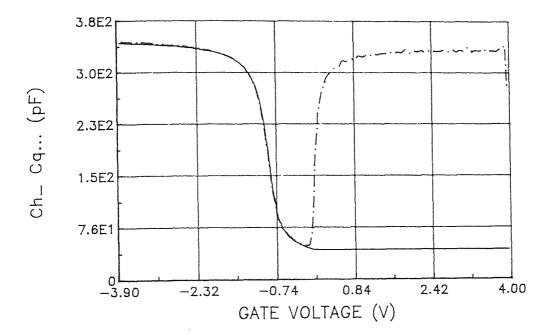

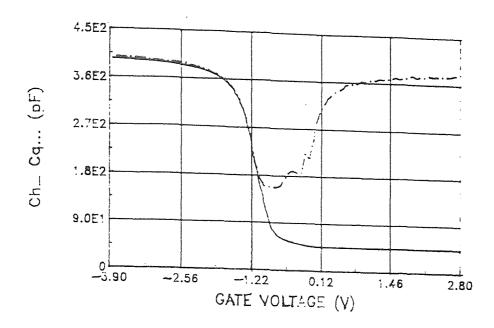

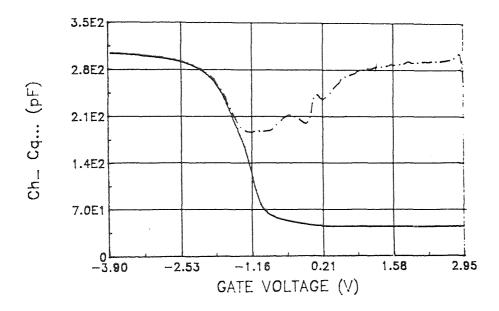

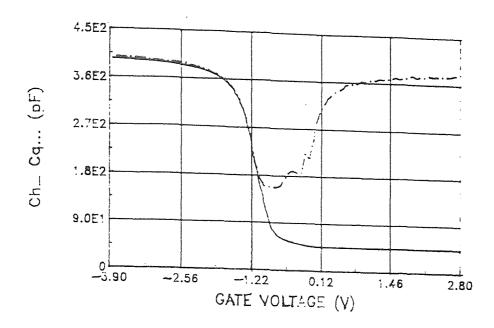

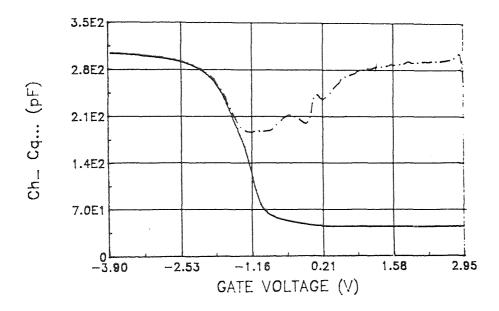

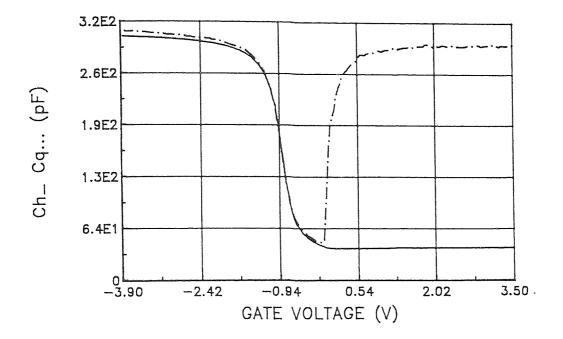

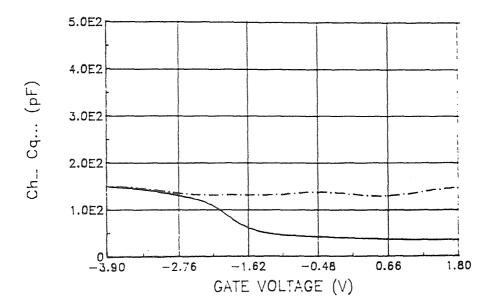

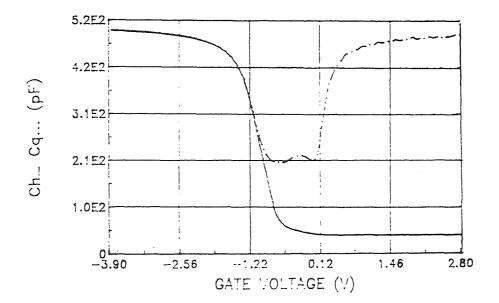

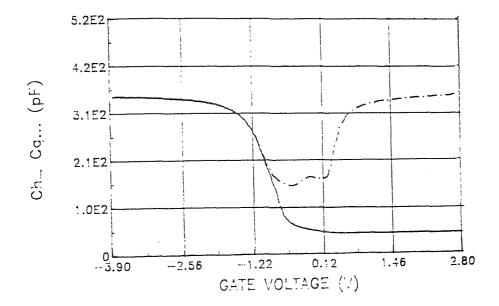

| 6.2         | HF CV and quasi-static curves for type I device structure with $t_{ox} = 19.2 \text{ nm}$ (Control sample)           | 53   |

| 6.3         | HF CV and quasi-static curves for type I device structure with $t_{ox} = 17$ nm (sample irradiated for 30 minutes)   | 54   |

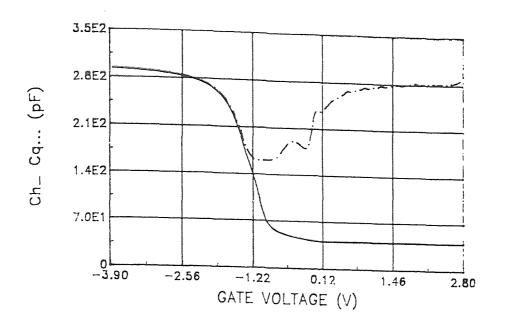

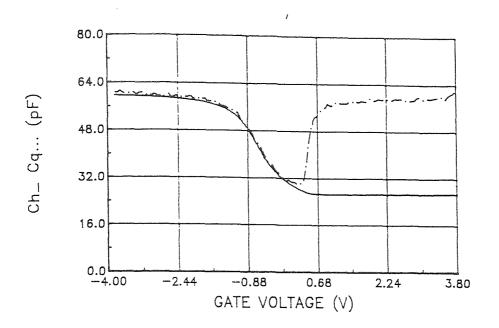

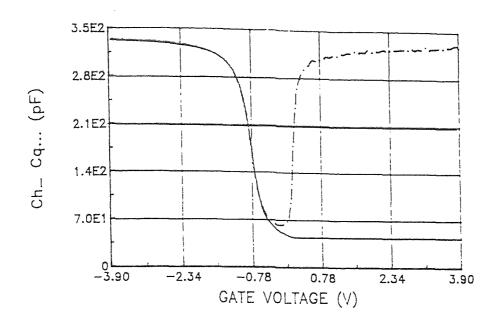

| 6.4         | HF CV and quasi-static curves for type I device structure with $t_{OX} = 20$ nm (sample irradiated for 60 minutes)   | 54   |

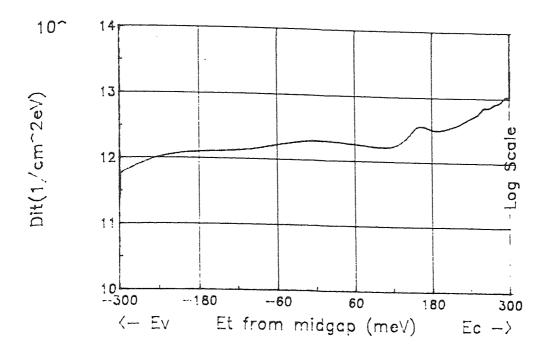

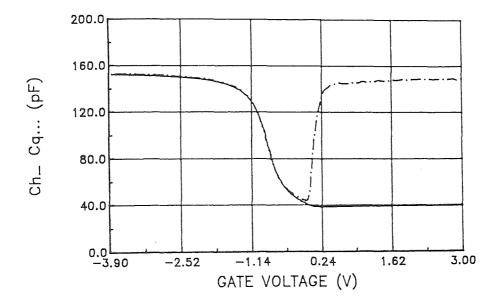

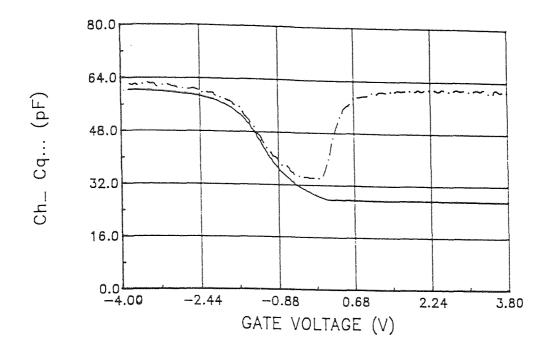

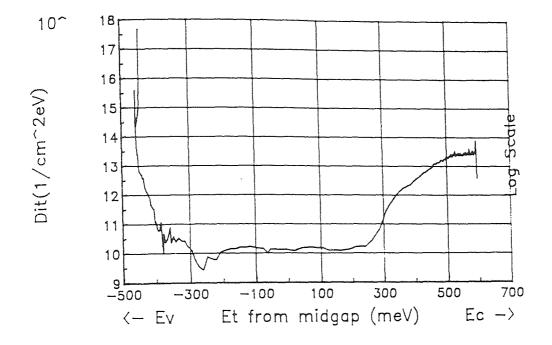

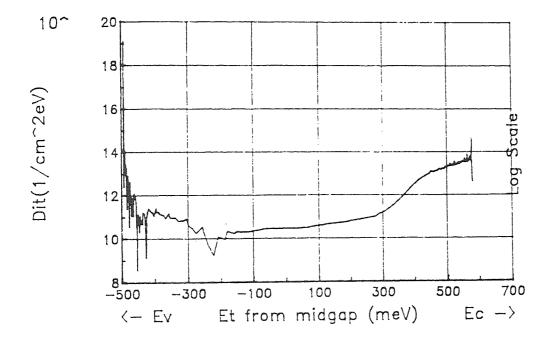

| 6.5         | $D_{it}$ plot for type I device structure with $t_{OX} = 19.2$ nm (Control sample)                                   | 55   |

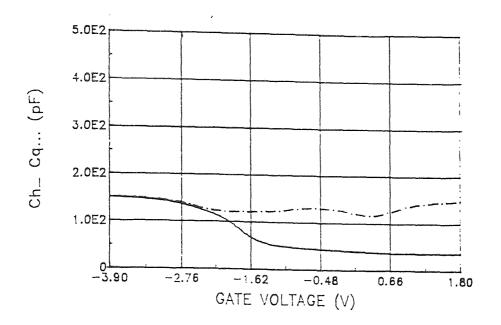

| <b>6</b> .6 | $D_{it}$ plot for type I device structure with $t_{OX} = 17$ nm (sample irradiated for 30 minutes).                  | 55   |

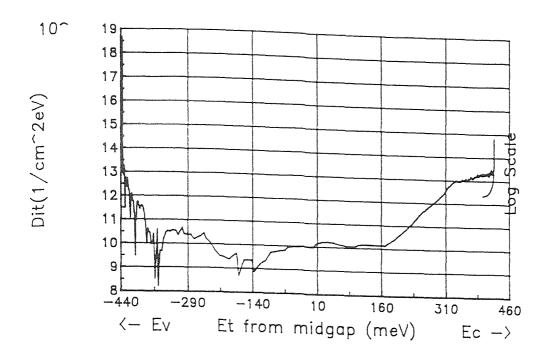

| 6.7         | $D_{it}$ plot for type I device structure with $t_{OX} = 20$ nm (sample irradiated for 60 minutes).                  | 56   |

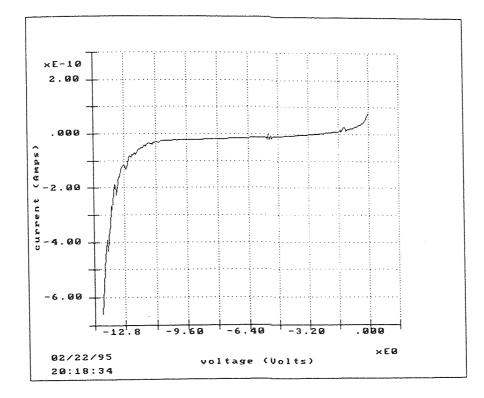

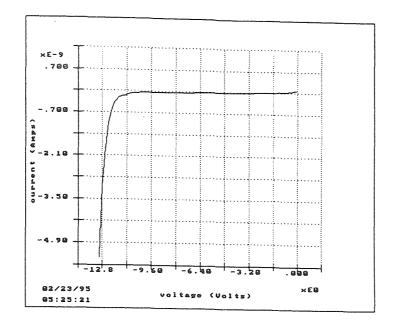

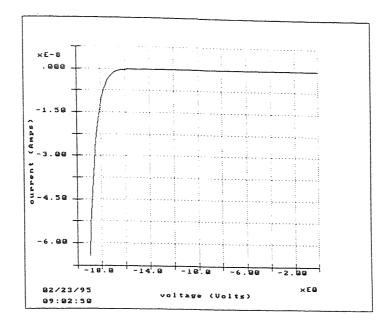

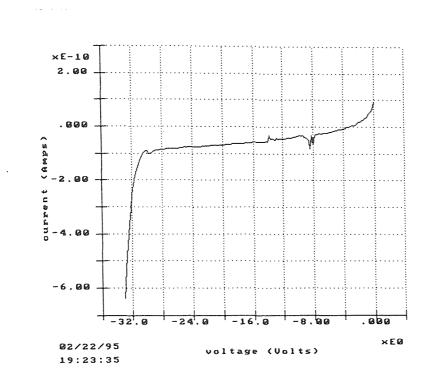

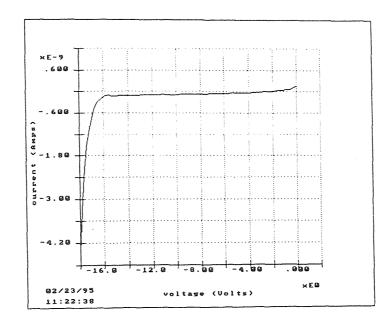

| 6.8         | Static IV plot for type I device structure with $t_{OX} = 17 \text{ nm}$ (Control sample)                            | 59   |

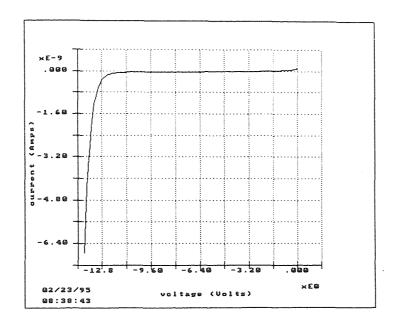

| 6.9         | Static IV plot for type I device structure with $t_{OX} = 17$ nm (sample irradiated for 15 minutes)                  |      |

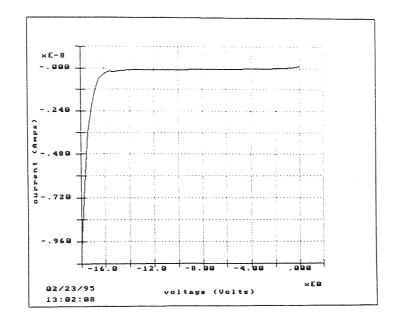

| 6.10        | Static IV plot for type I device structure with $t_{OX} = 17$ nm (sample irradiated for 45 minutes)                  | 60   |

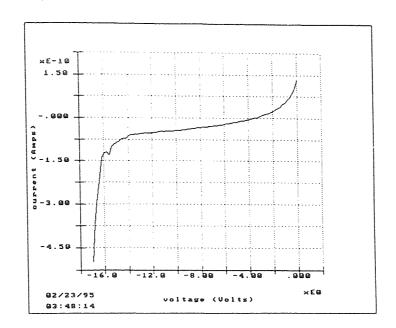

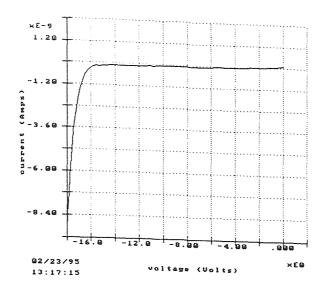

| 6.11        | Static IV plot for type I device structure with $t_{OX} = 23$ nm (Control sample)                                    | 61   |

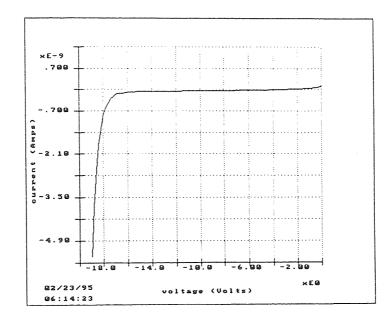

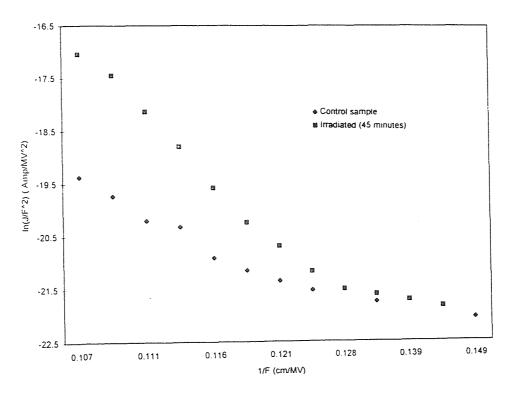

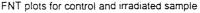

| <ul> <li>6.12 Static IV plot for type I device structure with t<sub>OX</sub> = 23 nm (sample irradiated for 15 minutes)</li> <li>6.13 Static IV plot for type I device structure with t<sub>OX</sub> = 23 nm (sample irradiated for 45 minutes)</li> <li>6.14 Static IV plot for type I device structure with t<sub>OX</sub> = 23 nm (sample irradiated for 90 minutes)</li> <li>6.15 Fowler-Nordheim tunneling plot for type I device structure with t<sub>OX</sub> = 17 nm for control sample and sample irradiated for 45 minutes</li> </ul> |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <ul> <li>irradiated for 45 minutes)</li> <li>6.14 Static IV plot for type I device structure with t<sub>OX</sub> = 23 nm (sample irradiated for 90 minutes)</li> <li>6.15 Fowler-Nordheim tunneling plot for type I device structure with t<sub>OX</sub> =</li> </ul>                                                                                                                                                                                                                                                                           | 61 |

| <ul><li>6.15 Fowler-Nordheim tunneling plot for type I device structure with t<sub>OX</sub> =</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                         | 62 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 62 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| A.1 HF CV and quasi-static curves for type I device structure with $t_{OX} = 22.1$ nm (Control sample)                                                                                                                                                                                                                                                                                                                                                                                                                                          | 67 |

| A.2 HF CV and quasi-static curves for type I device structure with $t_{OX} = 23$ nm (sample irradiated for 30 minutes)                                                                                                                                                                                                                                                                                                                                                                                                                          | 68 |

| A.3 HF CV and quasi-static curves for type I device structure with $t_{OX} = 43.8$ nm (Control sample)                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| A.4 HF CV and quasi-static curves for type I device structure with $t_{OX} = 42.9$ nm (sample irradiated for 30 minutes)                                                                                                                                                                                                                                                                                                                                                                                                                        | 69 |

| A.5 HF CV and quasi-static curves for type I device structure with $t_{OX} = 45.3$ nm (sample irradiated for 60 minutes)                                                                                                                                                                                                                                                                                                                                                                                                                        | 69 |

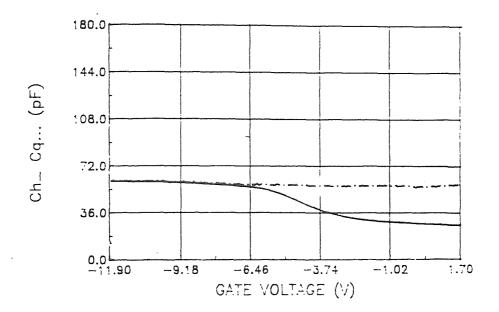

| A.6 HF CV and quasi-static curves for type I device structure with $t_{OX} = 111.8$ nm (Control sample)                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| A.7 HF CV and quasi-static curves for type I device structure with $t_{OX} = 112.3$ nm (sample irradiated for 30 minutes)                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

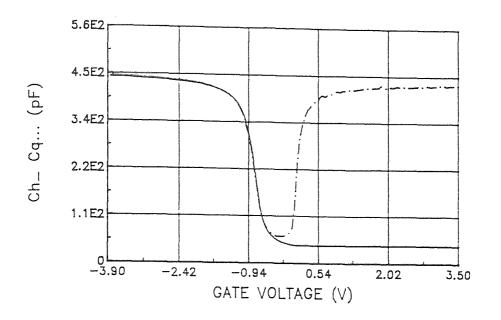

| A.8 HF CV and quasi-static curves for type II device structure with $t_{OX} = 15.1$ nm (Control sample)                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

| A.9 HF CV and quasi-static curves for type II device structure with $t_{OX} = 14.5$ nm (sample irradiated for 60 minutes)                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| A.10 HF CV and quasi-static curves for type II device structure with $t_{OX} = 20$ nm (Control sample)                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| Figu         | re                                                                                                                    | 'age |

|--------------|-----------------------------------------------------------------------------------------------------------------------|------|

| <b>A</b> .11 | HF CV and quasi-static curves for type II device structure with $t_{ox} = 19.3$ nm (sample irradiated for 30 minutes) | 72   |

| <b>A</b> .12 | HF CV and quasi-static curves for type II device structure with $t_{ox} = 110 \text{ nm}$ (Control sample).           | 73   |

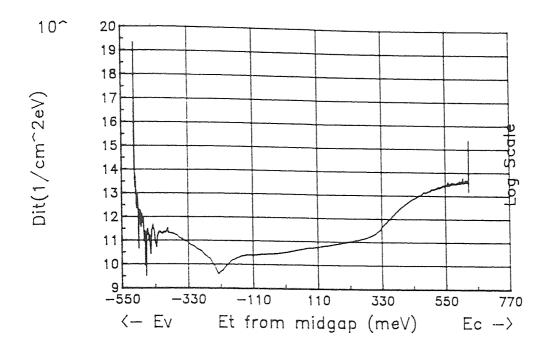

| B.1          | $D_{it}$ plot for type I device structure with $t_{OX} = 22.1$ nm (Control sample)                                    | 74   |

| B.2          | $D_{it}$ plot for type I device structure with $t_{OX} = 43.8$ nm (Control sample)                                    | 75   |

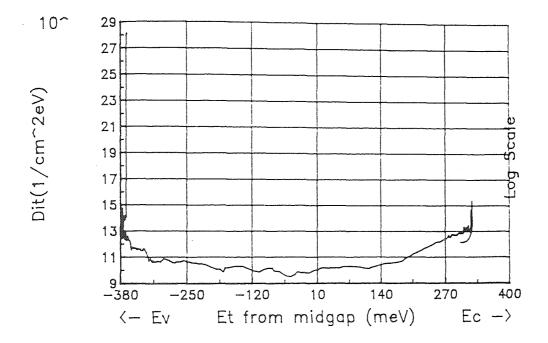

| B.3          | $D_{it}$ plot for type I device structure with $t_{OX} = 111.8$ nm (Control sample)                                   | 75   |

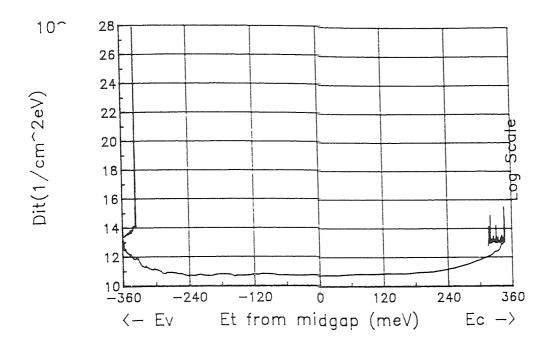

| <b>B</b> .4  | $D_{it}$ plot for type II device structure with $t_{OX} = 17$ nm (Control sample)                                     | 76   |

| B.5          | $D_{it}$ plot for type II device structure with $t_{ox} = 21$ nm (Control sample)                                     | 76   |

| <b>B</b> .6  | $D_{it}$ plot for type II device structure with $t_{OX} = 110$ nm (Control sample)                                    | 77   |

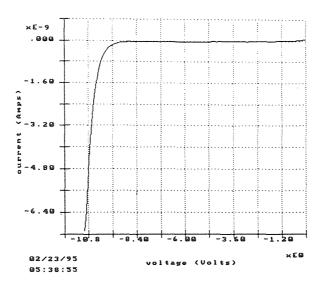

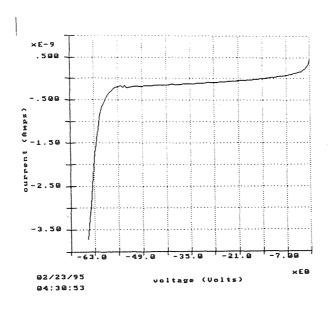

| <b>C</b> .1  | Static IV plot for type I device structure with $t_{OX} = 43$ nm (Control sample)                                     | 78   |

| C.2          | Static IV plot for type I device structure with $t_{OX} = 43$ nm (sample irradiated for 15 minutes)                   | 79   |

| C.3          | Static IV plot for type I device structure with $t_{OX} = 43$ nm (sample irradiated for 45 minutes)                   | 79   |

| C.4          | Static IV plot for type I device structure with $t_{OX} = 43$ nm (sample irradiated for 90 minutes)                   | 80   |

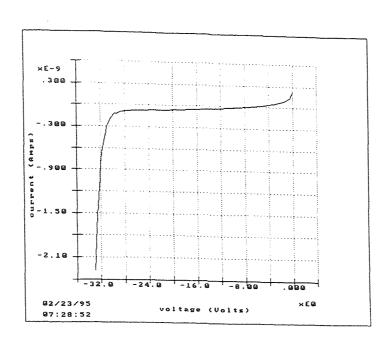

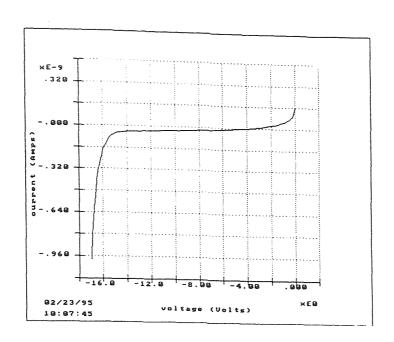

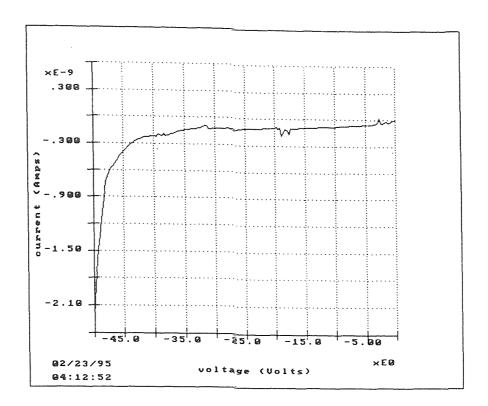

| C.5          | Static IV plot for type II device structure with $t_{ox} = 17$ nm (sample irradiated for 15 minutes)                  | 80   |

| C.6          | Static IV plot for type II device structure with $t_{OX} = 23$ nm (sample irradiated for 45 minutes)                  | 81   |

| Figu | re                                                                                                    | Page |

|------|-------------------------------------------------------------------------------------------------------|------|

| C.7  | Static IV plot for type II device structure with $t_{OX} = 23$ nm (sample irradiated for 75 minutes)  | 81   |

| C.8  | Static IV plot for type II device structure with $t_{OX} = 23$ nm (sample irradiated for 90 minutes)  | 82   |

| C.9  | Static IV plot for type II device structure with $t_{ox} = 118$ nm (Control sample)                   | 82   |

| C.10 | Static IV plot for type II device structure with $t_{ox} = 118$ nm (sample irradiated for 45 minutes) | 83   |

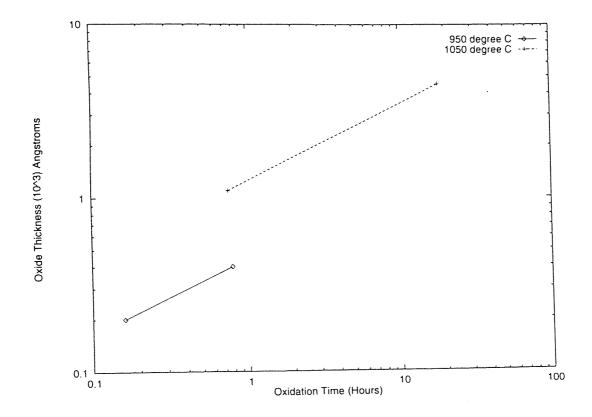

| F.1  | Oxide thickness versus time (our study)                                                               | 91   |

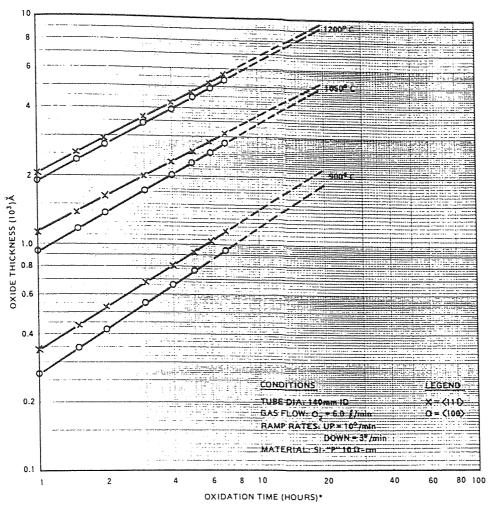

| F.2  | Oxide thickness versus time found in literature                                                       | 92   |

#### CHAPTER 1

#### **INTRODUCTION**

#### 1.1 Background

Scientific research on radiation effects in semiconductors has been conducted for a number of years. The term radiation here is not restricted to photons, but is quite general and includes incident electrons, protons, neutrons and almost any particle that may interact with the material of interest. Our interest is not so much in radiation detection, but changes in material properties due to radiation. In the case of strong radiation, these changes are sometimes deleterious, significantly affecting the electrical conductivity and other electrical characteristics.

The main interest in radiation effects in semiconductors stems from the use of semiconductor devices in industrial, space and military applications in a radiation environment. The effects of radiation are also of considerable importance in device fabrication processes such as electron beam deposition, sputtering, ion etching and ion implantation that expose the device to radiation.

The principle cause of radiation damage varies with the utilization of the device in a particular environment. In general, the irradiating particles involved are classified into three main categories: photons (X-rays and  $\gamma$ -rays), neutrons and charged particles (electrons, protons,  $\alpha$ -particles, heavy ions..). In our study, we confine ourselves to the effect of  $\gamma$ -rays on Al/SiO<sub>2</sub>/p-Si/Al and Al/Poly/SiO<sub>2</sub>/p-Si/Al structures for oxide thicknesses in the range of 125Å - 4500Å..

We shall briefly digress into the history of research performed on radiation induced damage in semiconductor devices and we will present our work in the rest of this thesis. The radiation damage in bulk silicon [1] and in  $SiO_2$  [2] has been studied in order to improve the radiation hardness of microelectronic components. The effects of radiation

include electrical parameter drift such as threshold voltage shift, mobility degradation, increased leakage current and latch up. In both bipolar and MOS transistors, radiation damage in either silicon or the SiO<sub>2</sub> will affect the device characteristics. Szedon and Sandor [3] were among the first to recognize that the change in MOSFET characteristics was caused by the formation of positive charge in the oxide. This led to an intensive study of radiation effects in SiO<sub>2</sub>. In most cases, radiation damage in SiO<sub>2</sub> was the most dominant effect. In this thesis, we confine our study to the radiation induced damage at the SiO<sub>2</sub>-Si interfaces and the oxide in the Metal Oxide Semiconductor (MOS) system.

The MOS capacitor is widely used in the study of radiation effects in  $SiO_2$ . The MOS capacitor is most powerful for investigating the electrical properties of the MOS system. The superiority of MOS capacitor rests on its simple structure, simple fabrication and simplicity of analysis. The simplicity of analysis results because thermal equilibrium conditions are easy to obtain and a one dimensional treatment is accurate. Using the MOS capacitor, nearly all properties of interest in the SiO<sub>2</sub> at the SiO<sub>2</sub>-Si interface and in Si can be measured. The effects of ionizing radiation on metal/oxide/Si structures have been intensively investigated [4-10] and it has been established that irradiation results in trapping of holes (generated by the radiation) in the SiO<sub>2</sub> and creation of interface states at the SiO<sub>2</sub>-Si boundary.

Radiation induced effects have been reported on both p- and n- type substrates with varying oxide thicknesses, orientations, doping concentrations etc. It is difficult to generalize the results of various past experiments. Table 1.1 is an attempt to present a comprehensive summary of the research performed in the past three decades.

The frequency dependent Capacitance-Voltage (C-V) techniques are commonly used to characterize and study the irradiated and control samples. When ionizing radiation passes through a gate insulator, it creates free electrons and holes in the valence and conduction bands of the insulator. The highly mobile electrons are swept out of the

| Device Structure                                    | <ul> <li>Method of<br/>Radiation</li> </ul>                                                                                         | Technique                                                      | T <sub>ox</sub><br>(thickness of the<br>oxide) | Radiation Damage Studied                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AI/SiO <sub>2</sub> /n-Si<br>n - 50Ωcm<br>n - 5 Ωcm | Electron Energies of 10 to 16 KeV.<br>Total electronic charge received by samples was $2-5 \times 10^{-6}$ coul/cm <sup>2</sup> .   | HF CV<br>measurement.<br>Comparison with<br>theoretical curve. | 50Ωcm<br>wafers had<br>1500 Å.                 | Electron bombardment under study conditions<br>introduced added +ve charge which were detected by<br>CV measurements.[3]                                                                                                                                                                                                                                |

| MOS capacitor                                       | $10^{4}$ - $10^{9}$ rads<br>with gate bias of +2 volts applied<br>during irradiation.                                               | HF CV<br>measurement.<br>Comparison with<br>control sample.    | 2000 Å                                         | Shift of CV characteristics along voltage axis for various dose rates. $\Delta V$ saturates above $10^8$ rads.[11]                                                                                                                                                                                                                                      |

| MOFSET                                              | Co-60 $\gamma$ ray doses.<br>(0-4) x 10 <sup>6</sup> rads for +ve gate bias<br>(0-0.6) x 10 <sup>6</sup> rads for -ve gate<br>bias. | HF CV<br>measurement.<br>Comparison with<br>control sample.    | 1600 Å                                         | Shift of CV characteristics corroborates with [11] for<br>positive gate bias and $\Delta V$ saturates for high doses.<br>The same characteristic is exhibited for -ve gate<br>bias too. Saturation voltage shift due to +ve oxide<br>charge build up is much greater for positive bias than<br>for negative gate bias applied during radiation.<br>[12] |

| MOS capacitor<br>p-type                             | $6 \times 10^4$ rads<br>2 x 10 <sup>6</sup> rads<br>with +2.5 volts on gate.                                                        | HF CV<br>measurement.                                          |                                                | Shift of CV characteristics along the voltage axis in<br>MOS capacitor as a result of irradiation at two<br>different dose levels under the same positive gate<br>bias.[13]                                                                                                                                                                             |

| MOS capacitor<br>p-type                             | Radiation with photon energies<br>from well below to well above the<br>bandgap energy.<br>+ve gate bias of 20 volts applied         |                                                                |                                                |                                                                                                                                                                                                                                                                                                                                                         |

# Table 1.1 Overview of some of the radiation damage studies performed in the past thirty years.

# Table 1.1 (Continued)

| Device Structure                                                                                                                                                                                                 | Method of<br>Radiation                                                                                                    | Technique                                                                 | T <sub>ox</sub><br>(thickness of<br>the oxide)                                  | Radiation Damage Studied                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                  | during radiation at $6.7 \times 10^{14}$ photons/cm <sup>2</sup> i.e. 2.4 x $10^8$ rads at 10.2 eV.                       | HF CV and<br>LF CV.                                                       |                                                                                 | CV(curves) HF are shifted to more negative bias<br>corresponding to creation of positive oxide charge. The effect<br>of positive oxide charging in SiO <sub>2</sub> was investigated for high<br>and low photon energies for positive and negative gate bias<br>during irradiation.<br>[14]                                                             |

| p-type MOS<br>$N_a = 1 \times 10^{14}$ , $9 \times 10^{14}$<br>and $5 \times 10^{15}$ / cm <sup>3</sup><br>n-type MOS<br>$N_d = 4 \times 10^{14}$ , $3 \times 10^{15}$<br>/cm <sup>3</sup><br><100> orientation. | 25 KeV electron beam.<br>Irradiation dose was 1 x<br>$10^{-5}$ , 1.6 x $^{-5}$ and 6.6 x<br>$10^{-5}$ C/sq. cm.           | HF CV and<br>quasi-static<br>CV.                                          | 500 Å                                                                           | Interface state generation in MOS capacitors for both p-type,<br>n- type silicon substrates having different doping<br>concentrations were studied.<br>[15]                                                                                                                                                                                             |

| MOS<br>capacitors.                                                                                                                                                                                               | 5 KeV electron beam<br>with +4V gate bias.                                                                                | HF CV and<br>LF CV both at<br>low temperature<br>and room<br>temperature. | 2000 Å<br>About 100<br>variations in<br>fabrication<br>parameters<br>were made. | Interface state generation and oxide charges generation by<br>ionizing radiation were investigated. An attempt to construct<br>atomic models of oxide charges and interface states was<br>made. Randomly located trivalent silicon atoms are shown to<br>account for thermally generated interface states at SiO <sub>2</sub> -Si<br>interface.<br>[16] |

| MOS capacitors,<br>n-channel and p-channel<br>MOSFETs.                                                                                                                                                           | Co-60 gamma ray<br>irradiation of 1 x 10 <sup>6</sup><br>rads. +ve bias was<br>applied for MOSFETs<br>during irradiation. | Temperature<br>bias stress CV<br>curves. HF CV<br>and IV analysis.        | 900 Å, 5600<br>Å and a<br>number of<br>process<br>variables.                    | Reported radiation induced increase of mobile Na <sup>+</sup> ions in<br>MOS capacitors and a bias temperature stress induced<br>relaxation or "annealing" of radiation displaced ion current<br>peak accompanied by small increase in mobile Na in MOS<br>capacitors.[17]                                                                              |

#### **Device** structure Method of Radiation Technique Tox **Radiation Damage Studied** (thickness of the oxide) HF CV plots W - SiO<sub>2</sub> - p-Si 1MeV electron beam 500 Å, Feasibility of using new materials like tungsten instead of poly 670 Å. W - $SiO_2 - n-Si$ of as gate bias and interconnection material for VLSI radiation dose rate 140 rad/sec hardened applications were studied. with +10V [18] bias. MOS capacitors HF CV plots 500 Å Co-60 source. Examination of radiation behavior of high pressure oxides was $1 \times 10^6$ rads with 650 Å <100> quasi-static CV. found to be similar to that of dry and wet atmospheric pressure orientation n-type +10 volts bias. Dry high oxides. Calculation of interface state densities for various Si, SOS n-channel presssamples were done. [19] phosphorous ure oxides. doped poly gate transistors. ESR 1400 Å Effects of bias on radiation induced paramagnetic defects at MOS capacitor, y rays <111> orientation Si/SiO<sub>2</sub> interface were studied with ESR measurements. A 10M rads. n-type Si. large change in density of radiation induced Pb centers with bias was observed. Pb defects were found to account for a large portion of radiation induced defects at the interface.[20] MOS capacitor 0 - 20 eV electron 850 Å Holes and electrons were found to induce formation of trivalent XPS Si centers. Description of bond strain gradient [BSG] model to n type irradiation. 100 wafers. explain interface state build up. [21]

### Table 1.1 (Continued)

# Table 1.1 (Continued)

| Device Structure                                                                                               | Method of<br>Radiation                                                                   | Technique                           | Tox<br>(thickness of<br>the oxide) | Radiation Damage Studied                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOS capacitor.<br><111> orientation<br>n-type<br>2 x 10 <sup>16</sup> /cm <sup>3</sup><br>donor concentration. | X-ray<br>$1.1 \times 10^4$ rads<br>$-10^6$ rads.                                         | HF CV<br>and GV<br>characteristics. | 5000 Å                             | Investigation of flat band voltage shift and<br>generation of surface states for X-ray irradiated<br>samples were done.<br>[22].                                                |

| MOS capacitor.                                                                                                 | Soft X-rays with 1 MV/cm,<br>+ve gate bias, total dose<br>10K rad at low<br>temperature. | Low temperature HF<br>CV curves.    |                                    | A general relationship between location of trapped<br>holes and subsequent generation of interface states<br>were reported.<br>[23]                                             |

| MOS capacitors.                                                                                                | X-rays.                                                                                  | TSC and CV<br>technique.            | 3500 Å                             | Trapped hole annealing was quantitatively<br>estimated by TSC and CV techniques. Models of<br>oxide trap charge buildup and annealing are<br>discussed.<br>[24]                 |

| n-type Si<br><100> orientation<br>MOS capacitor.                                                               | $\gamma$ rays , X-rays $10^3$ to $10^6$ rads.                                            | HF and quasi-static<br>CV.          | 1000 Å -<br>2000 Å<br>thick.       | Change in density of surface states as a result of<br>annealing, irradiation and annealing as a function<br>of temperatures between 300 and 900 K has been<br>studied.<br>[25]. |

oxide by even a small field. However, the holes are trapped usually near the most negative electrode and form a semi-permanent positive space charge. When subjected to ionizing radiation, the accumulation of trapped positive charge is noted as a shift in flat band voltage to more negative values. The amount of this shift will depend on the gate bias during irradiation. For positive gate bias, the holes are trapped closer to silicon resulting in a large flatband shift. For negative bias, they are trapped closer to the metal where they cause a lesser flat band shift.

Figure 1.1 shows the shift along the voltage axis in MOS capacitor C-V characteristics as a result of irradiation at two different dose levels under the same positive gate bias. In p-type silicon used for n-channel transistors, inversion occurs when the Fermi level is close to the conduction band so that the interface states are charged neutral or negative at threshold conditions. With the same argument, n-type silicon used for pchannel transistors have interface states which are charged neutral or positive. In most cases, the positive charge build up dominates at low radiation levels [26]. Figure 1.2 shows shift of the C-V characteristics of an MOS capacitor along the voltage axis and the corresponding oxide trap charge (Qot) as a function of dose with dose rate as parameter. We observe that  $\Delta V$  saturates above a dose of 10<sup>8</sup> rads. Surface state formation is sensitive to radiation doses [26]. Many n-channel devices show a negative shift in threshold voltage for doses less than 10<sup>5</sup> rads and then begin to shift to more positive values for increased dose levels [22]. But p-channel devices usually show a continuous shift to more negative values with increasing radiation dose. Figure 1.3 shows shifts of C-V curves measured between the gate and the substrate of a MOSFET along the voltage axis for positive and negative aging gate bias.

The other notable contributions to this study is Repace's [17] report on mobile Na ions in irradiated MOS capacitors and effect of bias on radiation induced paramagnetic defects at the Si/SiO<sub>2</sub> interface [20]. Models where trapped holes are converted directly to interface traps have been proposed by many authors [21,23,27]. Co-60 irradiation studies

Figure 1.1 Shift of MOS capacitor C-V curves for two different doses of radiation under the same positive gate bias.[13]

Figure 1.2 Shift of C-V characteristics of a MOS capacitor and the corresponding oxide trapped charge for different doses of radiation.[11]

on Aluminum/Tantalum oxide/silicon oxide/silicon capacitors have also been studied [28]. The effect of heat treatment on interface parameters in  $SiO_2$ -Si structures after irradiation opens a whole new field for investigation. With this as the background, we shall discuss at length the findings of our research.

Figure 1.3 Shift of C-V curves for a MOSFET along the voltage axis as a function of gamma-ray dose (Co-60) (a) positive aging gate bias; (b) negative aging gate bias.[12]

#### 1.2 Outline of Remaining Chapters

Chapter Two covers oxidation kinetics and various aspects of oxide growth. Chapter Three deals with the ideal MOS capacitor in terms of its energy band diagrams and also describes the MOS capacitor model under non-ideal conditions. Chapter Four discusses in depth the electrical characterization techniques. Chapter Five describes the experimental procedures used in the fabrication of MOS capacitors and the characterization set up is also outlined. Chapter Six is devoted to the results of the various experiments performed on irradiated MOS capacitors and the effects of radiation on these structures are discussed in detail. Chapter Seven concludes our study of the radiation damage in MOS structures.

#### **CHAPTER 2**

#### **OXIDATION KINETICS**

#### 2.1 Introduction

Oxidation of Silicon is a very important step during the process of fabricating VLSI circuits. A high quality oxide is an absolute necessity in order to ensure the reliability of the devices. Silicon dioxide has several uses: to serve as a mask against implant or diffusion of dopant into silicon, to provide surface passivation, to provide electrical isolation of multi-level metallization schemes, for device isolation and to serve as a dielectric insulator in MOS structures. Several methods of oxidation are currently in use such as vapor phase reaction, plasma anodization, wet anodization and thermal oxidation in both dry and wet environments. In this chapter, we shall discuss the classical theory of oxidation proposed by Deal and Grove [29] and its limitations, the role of non-bridging oxygen at SiO<sub>2</sub>-Si interface and the effects of orientation, temperature and other factors on oxide growth. We will consider the relative differences of dry and wet oxides, thin and thick oxides.

#### 2.2 Classical Theory of Oxidation of Silicon

The macroscopic oxidation of single crystal was first suggested by Deal and Grove. The model is schematically illustrated in Figure 2.1. They proposed that oxidation proceeds by the diffusion of an oxidant (molecular  $H_2O$  or  $O_2$ ) through the existing oxide to the SiO<sub>2</sub>/Si interface. The reactions describing the thermal oxidation of Silicon are given as:

$Si (solid) + O_2 (vapor) \implies SiO_2 (solid)$

Si (solid) +  $2H_2O$  (vapor) ===> SiO<sub>2</sub> (solid) +  $2H_2$

This model proposed by Deal and Grove is valid for oxide thicknesses above 200 Å, oxidation in dry oxygen, oxidant partial pressure of 1 atm or less and temperatures

Figure 2.1 Cross section of silicon with a growing  $SiO_2$  layer illustrating the model for thermal oxidation of silicon. The three fluxes,  $F_1$  into the silica,  $F_2$  through the silica, and  $F_3$  at the SiO<sub>2</sub>-Si interface, are shown. [29]

between 700 and 1300° C. The overall oxidation process based on Figure 2.1 depends on fluxes. After considering the initial oxide layer, various fluxes, gas laws [30] etc., the following relation has been shown to be applicable:

$$x^2 + Ax = B(t + \tau) \tag{2.1}$$

where,

t is the time duration for which the oxidation has taken place,

$\tau$  is the time co-ordinate shift to account for the initial oxide layer,

x is the oxide thickness,

B is the parabolic rate constant and

B/A is the linear rate constant.

Experimentally measured results agree with the predictions of this model over a wide range of oxidation conditions. For wet oxidation, the initial oxide thickness is very small. However for dry oxidation, the extrapolated value of initial oxide thickness is about 200 Å. Therefore Deal and Grove found that there was an initial accelerated growth during oxidation in dry oxygen. A number of different forms and mechanisms have been suggested for the initial thin oxide growth kinetics. The proposals in the literature have included schemes based on enhanced oxidant diffusion, reduced oxidant diffusivity in the oxide, fixed charge effect on the interface reaction rate and micropore diffusion.

#### 2.3 Chemical Structure of SiO<sub>2</sub>

SiO<sub>2</sub> basically has two states: (a) amorphous state termed as glass of fused silica which is extensively used in furnace hardware and (b) crystalline state termed as quartz. The amorphous state of SiO<sub>2</sub> is thermodynamically unstable below 1710° C. Fused silica does not have a long range structure because of its amorphous state but a short range order does exist. The short range order is centered around the structural formula for the material which is SiO<sub>4</sub><sup>4-</sup>. The structure can be described as follows:

The valency of Silicon is four and this Si atom is located at the center of a regular tetrahedron as shown in Figure 2.2a and the oxygen ions are at each of the corners of the tetrahedron. The tetrahedral distance between Si and oxygen ions is 1.60 Å, and the interionic oxygen-oxygen distance is 2.27 Å.

The tetrahedral structures are then joined to each other by an oxygen ion called a bridging oxygen, which is shared between the two touching tetrahedra. This gives rise to a crystalline structure as shown in Figure 2.2b. But for the amorphous state of  $SiO_2$  shown in Figure 2.2c, some of the vertices of the tetrahedra are not shared and this results in the structure having non bridging oxygen ions.

Figure 2.2 (a) Basic structural unit of SiO<sub>2</sub>; (b) Two dimensional representation of a quartz crystal lattice; (c) Two dimensional representation of the amorphous structure of SiO<sub>2</sub>.[31]

The cohesiveness of the glass depends on the ratio of bridging to non bridging oxygen ions. Greater the ratio, the better will be the cohesiveness of the glass. The atomic movement in silica is more likely to occur by the movement of oxygen atoms rather than the silicon atom. The reason for this is the bonding mechanism of the atoms, Si has four bonds to oxygen, as a result four bonds have to be ruptured for the silicon atom to be free whereas the rupture of only two Si-O bonds are required to free a bridging oxygen atom. If the rupture occurs, an oxygen ion vacancy is formed. This vacancy has a net positive charge in the network. Both bridging and non bridging oxygen vacancies may be formed, but the non bridging vacancy is more likely to occur based on binding energy considerations.

SiO<sub>2</sub> films grown by the oxidation of silicon, have an amorphous structure with a random network of polyhedra. The density of thermally grown fused silica (2.25 g/cc) is less than that of the crystalline quartz (2.65 g/cc). The lower density implies a more open structure. This open structure is conducive to the interstitial diffusion of impurities through the network. Impurities in silica alter its properties appreciably. There are two kinds of impurities, substitutional and interstitial. The substitutional impurities (e.g.  $B^{3+} \& P^{5+}$ ) replace Si in the structure and they are also known as network formers. The missing or extra electrons in the tetrahedra, when these materials are added, are accomodated by the elimination or formation of bridging oxygen ions respectively. The elimination of bridging oxygen tend to weaken the network.

Interstitial impurities like the oxides of Na, K, Pb and Ba enter the structure resulting in the metal ions giving up its oxygen to the network, thereby producing two non bridging oxygen ions, which replace the original binding oxygen. The additional non bridging oxygen also tends to weaken the structure facilitating the increased diffusion of other species within the glass. Impurity oxides of this type are termed network modifiers since they do not form glasses themselves. Water vapor is an important impurity in fused silica, and can enter from the atmosphere or be grown-in during wet oxidation. The water vapor combines with a bridging oxygen to form a pair of stable non bridging hydroxyl groups (OH<sup>-</sup>). This reaction can be represented by:  $H_2O + Si-O--Si = Si--OH + OH-Si.$

The increase in non bridging oxygen again tends to weaken the Si network, thereby increasing the diffusivities of many materials in the network. The presence of OH can be detected by IR spectroscopy, since the Si-OH stretching frequency is different than that of Si-O. Figure 2.3 shows the structure of fused silica glass.

#### 2.4 Other Aspects of Thermal Oxidation and CVD Deposition

Oxides grown in pure dry oxygen have the very best electrical properties, but considerably more time is required for growing the same thickness of the oxide at a given temperature in dry oxygen than in water vapor. For relatively thin oxides, such as the gate oxide in a MOSFET, typically lesser than 100 nm thick, dry  $O_2$  oxidation is commonly used. Such a film can be grown very quickly. In many other applications, such as for bipolar transistors and for thick field or isolation oxide (greater than 500 nm) in MOS integrated circuits, oxidation in water vapor or steam is used and provides adequate passivation.

Thin oxides (2.5 nm - 10 nm) are very important in a class of memory devices that use potential wells at the interface between  $SiO_2$  and another insulator to store charge. The potential wells at the insulator-insulator interface are filled and emptied with electrons by tunneling between the wells and the silicon through the thin  $SiO_2$  layer. Another possible application of thin oxides is in semiconductor photovoltaic solar cells, where a thin oxide layer (in the order of 3 nm) between a metal electrode and the semiconductor has been found to increase the output voltage and efficiency of the cell.

The oxidation mechanism is found to depend on the crystallographic orientation of the silicon surface. In particular, the linear oxidation rate is observed to depend on the crystallographic orientation of the silicon surface. The parabolic rate constant (Equation 2.1) is independent of silicon surface orientation, as the parabolic oxidation rate is diffusion limited.

Oxides can also be formed not by oxidation of Si but by CVD deposition at different temperatures. The oxide properties change depending on the temperature at which they were grown. Intermediate temperature (500 - 800° C) oxides may be deposited using pyrolysis of tetraethylorthosilicate,  $(C_2H_2O)_4$ Si, in a hot wall tube furnace reactor [32,33]. Advantages of the intermediate temperature method are a short time cycle, and large numbers of silicon wafers can be handled on a furnace paddle or rack. Intermediate temperature CVD oxides have been used most often as a masking layer for the etching of

silicon nitride films and for diffusion masking of germanium substrates. High temperature deposition of  $SiO_2$  is usually done at temperatures of 850-1100° C using silane diluted to 1% in nitrogen,  $CO_2$ , and hydrogen carrier gas. The high temperature deposition method is most useful for the top masking oxide for etching holes in silicon nitride films. There are a number of advantages to depositing  $SiO_2$  by the pyrolysis of tetraethylorthosilicate at low pressures: less particulates that can deposit on the wafers are generated, up to 200 wafers can be processed at a time, better thickness uniformity across each wafer is obtained, a more specular surface results, less material is used, and this method is less hazardous and lower in cost.

There are still a number of factors that affect the oxidation like nature of the diffusing species, state of water in silica and influence of impurities on oxidation rates. All these factors are discussed by Sze [30] and Ghandhi [34].

#### **CHAPTER 3**

#### FUNDAMENTALS OF MOS STRUCTURE

#### **3.1 Introduction**

The MOS capacitor is the simplest, most reliable device structure for investigation of radiation damage in the oxide and its interface with the semiconductor. Hence it is mandatory to have a thorough knowledge of the physical characteristics of MOS structure under equilibrium and non-equilibrium conditions. In this chapter, we are concerned primarily with the MOS structure shown in Figure 3.1.

Figure 3.1 Metal-oxide-semiconductor (MOS) structure.[35]

We first consider the ideal characteristics of MOS structure and then extend our discussion to include the effects of metal semiconductor work function differences, interface traps, oxide charges etc.

#### 3.2 Ideal MOS Structure

We will consider the energy band diagrams of ideal MOS capacitors for zero applied voltage. Figure 3.2 shows the band diagrams for both n-type and p-type semiconductors. Figure 3.3 shows the energy band diagram quantitatively representing the energy levels.

Figure 3.2 Energy-band diagrams of ideal MOS capacitors at V = 0. (a) n-type semiconductor. (b) p-type semiconductor.[35]

The position of the Fermi level in the gate and in the silicon gives us a very clear picture of the physical device aspect. The forbidden gap in SiO<sub>2</sub> is very large whereas that of silicon is much smaller. At zero applied bias, energy difference between the metal work function and the semiconductor work function is zero or the work function difference [35]  $\phi_{ms}$  is zero. For completeness, we have:

for n-type

$$\phi_{\rm ms} = \phi_{\rm m} - \left(\chi + \frac{E_g}{2q} - \psi_{\rm B}\right) = 0 \tag{3.1}$$

for p-type

$$\phi_{\rm ms} = \phi_{\rm m} - \left(\chi + \frac{E_g}{2q} + \psi_{\rm B}\right) = 0 \tag{3.2}$$

where  $\phi_{\rm m}$  is the metal work function,  $\chi$  is the semiconductor electron affinity,  $\chi_i$  is the insulator electron affinity,  $E_g$  is the bandgap,  $\phi_{\rm B}$  is the potential barrier between the metal and the insulator and  $\Psi_{\rm B}$  is the potential difference between Fermi level  $E_{\rm F}$  and intrinsic Fermi level  $E_i$ . This condition where the energy band is flat when there is no applied voltage is termed as flat band condition (Figure 3.2). The only charges that can exist in the structure under any biasing conditions are those in the semiconductor and those with equal but opposite sign on the metal surface adjacent to the insulator. There is no carrier transport through the insulator under dc biasing conditions or the carrier transport through the insulator under dc biasing conditions or the carrier transport through the insulator under dc biasing conditions or the carrier transport through the insulator under dc biasing conditions or the carrier transport through the insulator under dc biasing conditions or the carrier transport through the insulator under dc biasing conditions or the carrier transport through the insulator under dc biasing conditions or the carrier transport through the insulator under dc biasing conditions or the carrier transport through the insulator under dc biasing conditions or the carrier transport through the insulator under dc biasing conditions or the carrier transport through the insulator under dc biasing conditions or the carrier transport through the insulator is infinite.

Figure 3.3 Energy-band diagram of the MOS capacitor showing the energy barrier between metal and SiO<sub>2</sub> and between silicon and SiO<sub>2</sub>.[2]

When an ideal MOS capacitor is biased with positive or negative voltages, we may examine three cases at the semiconductor surface namely, accumulation, depletion and inversion. These cases are shown in Figure 3.4 for both p-type as well as n-type substrates. The relevance of accumulation, depletion and inversion is also explained with respect to capacitance voltage curves (C-V) in the next chapter. If we apply a negative voltage between the metal and semiconductor, we are effectively depositing a negative charge on the metal. In response, an equal net positive charge accumulates at the surface of the semiconductor. In case of p-type substrate, this occurs by hole accumulation at semiconductor-oxide interface. A positive voltage from metal to semiconductor deposits positive charge on the metal and calls for a corresponding net negative charge at the surface of the semiconductor. Such a negative charge in p-type material arises from depletion of holes from the region near the surface, leaving behind uncompensated ionized acceptors.

Figure 3.4 Energy-band diagrams for ideal MOS capacitor when V≠0, for the following cases: (a) accumulation; (b) depletion; (c) inversion [35]

If we continue to increase the positive voltage, the bands at the semiconductor surface bend down more strongly. Since  $E_i$  is below  $E_F$  and  $E_F >> E_i$  implies a large concentration of electrons in the conduction band, this is the inversion phenomena. The

above discussion applies to n-type substrate devices simply by reversal of polarities of voltages.

#### 3.3 Effects of Real Surfaces

The departure of the physical characteristics of MOS capacitor from the ideal model is due to work function differences and interface charges. As a result, the MOS capacitor happens to be the only semiconductor device that is in equilibrium (considering flat band conditions), when a voltage is applied to it.

The work function of a semiconductor,  $q\phi_s$ , varies with the doping concentration. Hence work function difference,  $q\phi_{ms} = q\phi_m - q\phi_s$ , also varies depending on the doping concentration. Generally,  $q\phi_{ms}$  is not zero as opposed to the ideal case. Considering a p-type semiconductor MOS system, the bands bend down due to the work function difference as shown in Figure 3.5

Figure 3.5 Energy-band diagrams for negative work function difference . (a) Band bending at equilibrium. (b) Flat band condition for negative applied voltage.[36]

Thus the metal is positively charged and the semiconductor surface is negatively charged at thermal equilibrium. To obtain the flat band condition pictured in Figure 3.5b,

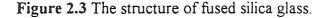

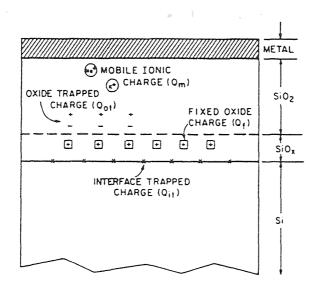

we must apply a negative voltage to the metal  $V_{FB} = \phi_{mS}$ , which is called the flat band voltage. In addition to the work function difference, the equilibrium MOS capacitor is affected by charges in the oxide and at the SiO<sub>2</sub>-Si interface [37]. Figure 3.6 shows charges and their locations for thermally oxidized silicon. There are four general types of charges associated with SiO<sub>2</sub>-Si system. The charges are described as [37]:

Figure 3.6 Charges and their locations for thermally oxidized silicon.[35]

- Fixed oxide charge (Q<sub>f</sub>, N<sub>f</sub>): These are located in the oxide layer less than 25 Å from the SiO<sub>2</sub>-Si interface. The dependency on oxidation ambient temperature, silicon orientation and other related parameters has been clearly explained by Deal [37].

- Mobile oxide charge (Q<sub>m</sub>, N<sub>m</sub>): These are due to ionic impurities such as Na<sup>+</sup>, Li<sup>+</sup>,

K<sup>+</sup> that are mobile within the oxide under bias temperature aging condition.

- (3) Oxide trapped charge (Q<sub>ot</sub>, N<sub>ot</sub>): These may be positive or negative due to holes or electrons trapped in the bulk of the oxide. Trapping may result from any form of ionizing radiation or hot electron injection.

- (4) Interface trapped charge (Q<sub>it</sub>, N<sub>it</sub>, D<sub>it</sub>): These are charges located at the Si-SiO<sub>2</sub> interface with energy states in the silicon forbidden gap. They can possibly be

produced by structural defects, impurities or other defects caused by radiation. Unlike the other three, these can exchange charges with the underlying silicon. These are also referenced as surface states, fast states or interface states in the literature.

Any form of ionizing radiation will affect device structure and characteristics mainly in modifying the charge distributions. In chapter 4, we discuss several characterization techniques to account for radiation induced damage in semiconductor devices.

#### **CHAPTER 4**

# ELECTRICAL CHARACTERIZATION TECHNIQUES

#### **4.1 Introduction**

Radiation hard microelectronics is a vital part of research in the modern day high speed VLSI applications. Therefore the study of radiation induced defects is accomplished by a variety of device characterization techniques. We give importance to electrical characterization methods as they are the most relevant techniques capable of yielding information on device properties. Optical methods are also popular because of their non contacting nature and their high sensitivity is an important advantage. Chemical and physical characterization methods, with their high spatial resolution and ability to identify elements and compounds make them highly indispensable too. A popular technique for characterization of electrical properties of MOS structure is the C-V technique [38].

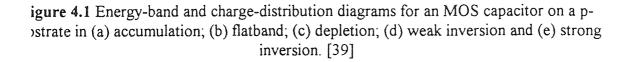

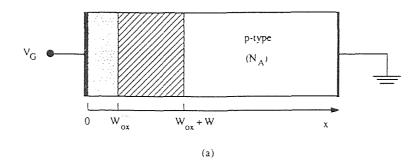

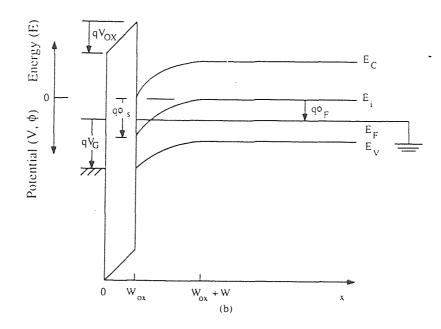

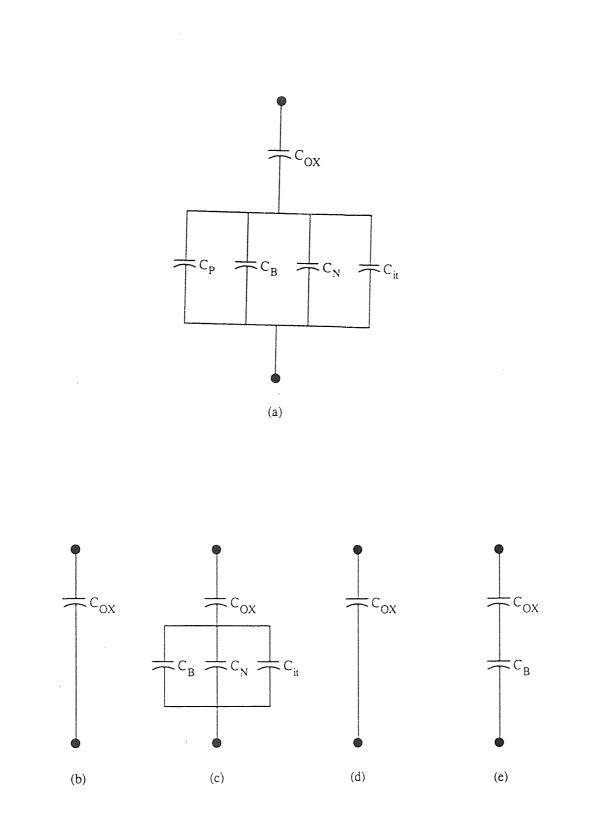

### 4.2 C-V Measurements

Various charges in the MOS system can be measured by the most popular approach of Capacitance-Voltage measurements. Before discussing the measurement methods, we will analyze the effect of gate voltage on MOS capacitances [39]. The energy band and charge distribution diagrams for a MOS capacitor on a p-type substrate for various bias voltages are shown in Figure 4.1. When the gate bias is swept from negative to positive values for a p-type MOS capacitor, the capacitance varies as shown in Figure 4.2 [39]. Figure 4.3 shows the high frequency (HF) curve and the deep depletion regime. We discussed previously accumulation, depletion and inversion with respect to energy bands. The corresponding cases in the C-V plot is shown in Figure 4.3. The C-V curve (a) to (e) in Figure 4.3 is experimentally obtained by sweeping the gate voltage. All the above

Figure 4.2 MOS capacitance-voltage curves: (a) Low frequency; (b) High frequency; (c) Deep depletion. [35]

Figure 4.3 Capacitance-gate voltage curves for MOS capacitor. [39]

the above characteristics are related to p-type silicon substrate and we will limit ourselves to p-type substrate in the rest of the discussion.

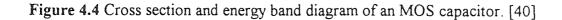

Let us consider a MOS capacitor with the dc gate voltage swept from negative to positive voltages. Superimposed on the dc voltage is a small amplitude ac voltage of typically 10-15 mV amplitude which is necessary to measure the capacitance. The dc voltage determines the bias condition. The three capacitance voltage curves (Figure 4.2) are identical in accumulation and depletion. The energy band diagram of a MOS capacitor on p-type substrate is shown in Figure 4.4 [40].

The capacitance measured [40] between the gate and the substrate is given as:

$$C = \frac{C_{ox}(CP + CB + CN + C_{it})}{C_{ox} + CP + CB + CN + C_{it}}$$

(4.1)

#### where,

Cox is the capacitance due to the oxide charge,

CP is the capacitance due to the hole accumulation charge,

CB is the capacitance due to the space charge region bulk charge,

CN is the capacitance due to the electron inversion charge and

Cit is the capacitance due to the interface trapped charge.

Now we shall discuss the regions of accumulation, depletion and inversion with reference to the C-V plot:

(a) Accumulation: For sufficiently large negative voltages, majority carriers are attracted to the surface of the silicon leading to a p-type surface accumulation layer [41]. Since accumulation charge is very high, the four capacitances shown in Figure 4.5a are neglected and the equivalent capacitance reduces to Figure 4.5b [40]. The high concentration of holes near the Si surface can be thought of as forming the second electrode of a parallel plate capacitor with the gate electrode. Since the accumulation layer is in direct Ohmic contact with the p-type substrate, the capacitance of the structure under accumulation is approximately equal to:

$$C = \frac{A\varepsilon_{0x}}{t_{0x}}$$

(4.2)

where,

Figure 4.5 Capacitances of an MOS capacitor for various bias conditions as discussed in section 4.2. [40]

A is the area of the gate,

$\varepsilon_{\text{ox}}$  is the permittivity of the oxide and

tox is the oxide thickness.

On the C-V plot (Figure 4.3), under negative voltage, the capacitance is the maximum recorded and hence is just the insulator capacitance.

(b) Depletion: When the gate voltage is increased, the surface hole concentration reduces and becomes zero and at this point only a surface depletion region consisting of immobile ionized acceptors will be present (Figure 4.1). In this case, the space charge dominates and the space charge region charge Q<sub>B</sub> is:

$$Q_{\rm B} = -q N_{\rm A} W \tag{4.3}$$

where,

q is the electron charge,

NA is the acceptor concentration and

W is the width of the surface depletion region.

As gate voltages become more positive, both  $Q_B$  and W increase. As the width of the surface depletion region increases, the capacitance from gate to substrate associated with the MOS capacitor structure will decrease which is shown in the equivalent circuit of Figure 4.5c [40]. The total capacitance is the combination of  $C_{ox}$  in series with  $C_B$ , which in turn is in parallel with  $C_{it}$ .  $C_N$  can be neglected in depletion region.

(c) Inversion: With the gate voltages becoming more positive, the surface depletion region will continue to widen until the onset of inversion in which case electrons are attracted up to the silicon surface to form n-type inversion layer. Under weak inversion depicted in Figure 4.1, we apply the equivalent circuit of Figure 4.5c and in this case  $C_N$  is not neglected.

The width of the surface depletion region for a MOS structure in equilibrium will remain essentially constant after the formation of the inversion layer even if the gate voltage is made more positive. For strong inversion,  $C_N$  dominates because  $Q_N$  is very high. Now  $Q_N$  may or may not be able to follow the high frequency small signal ac gate voltage, superimposed on the dc bias and as such the capacitance of the MOS capacitor under inversion conditions is really a function of the frequency of the applied gate ac voltage.

If  $Q_N$  is able to follow the applied ac voltage, the equivalent circuit of Figure 4.5d is a good low frequency approximation and therefore the capacitance is nothing but the oxide capacitance. This is the LF CV curve (Figure 4.2). If  $Q_N$  is unable to follow the ac voltage, the equivalent circuit of Figure 4.5e is the high frequency approximation and therefore capacitance is the series combination of  $C_{OX}$  and  $C_B$ , giving the HF CV curve (Figure 4.2).

(d) Deep depletion: When the dc bias gate voltage is changed rapidly with insufficient time for the generation of inversion charge, then the device is driven into the deep depletion and this is point (f) in Figure 4.3 in the deep depletion curve. Under these conditions, the capacitance is less than the inversion capacitance for obvious reasons.

The three C-V curves (Figure 4.2) are identical in accumulation and depletion but deviate for positive gate voltages because the inversion charge is unable to follow the applied ac voltage for the HF case and does not exist in the deep depletion region. We now discuss charges in the oxide system and their measurement methods.

#### 4.3 Oxide Charges and their Measurement Methods

# 4.3.1 Interface Trapped Charge (Q<sub>it</sub>)

The interface trap charge may arise from irradiation or other similar bond breaking processes [42]. The characteristics of interface trapped charge are briefly outlined in the following paragraphs.