New Jersey Institute of Technology Digital Commons @ NJIT

Theses

**Electronic Theses and Dissertations**

Fall 1-31-1996

# Design and development of four to sixteen channel video multiplexers

Ronan Rahimi New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/theses

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Rahimi, Ronan, "Design and development of four to sixteen channel video multiplexers" (1996). *Theses.* 1116.

https://digitalcommons.njit.edu/theses/1116

This Thesis is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Theses by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

# DESIGN AND DEVELOPMENT OF FOUR TO SIXTEEN CHANNEL VIDEO MULTIPLEXERS

#### by Ronan Rahimi

Video multiplexer series were successfully designed and built for prototype and evaluation both in terms of hardware and software. The hardware platform was designed to accommodate up to sixteen color video input channels for time lapse or real time recording on a single video cassette recorder. This product implements four modes of operation; Live, Record, Playback and Menu mode, which is not a full mode of operation. Menu mode is a series of on-screen programming menus which appears on Live, Record and Playback modes. Menu mode enables the user to program the machine to work under specific modes of application. For Video encoding a new video-capture processor, called Bt819 made by BrookTree, was chosen to minimize the cost and system overhead of adding video input and capture to PC video/graphics systems. This development by Brook Tree employs the firm's time-tested digital Ultralock technology to generate the required number of pixels per line using fixed frequency clock. On-chip pixel buffering and image scaling are provided for our QUAD picture on a monitor. Inter-integrated circuit  $(I^2C)$  communication was chosen to talk to this chip directly. The video syncs were generated from PIC microcontroller using assembly language. This program was designed at 13.5 Mhz (74 nsec) clock rate which follows NTSC CCIR-601 digital video standards. Alarm package design idea came from understanding of link-list programming and was tested on four separate video signals.

# DESIGN AND DEVELOPMENT OF FOUR TO SIXTEEN CHANNEL VIDEO MULTIPLEXERS

by Ronan Rahimi

A Thesis

Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering

Department of Electrical and Computer Engineering January 1996

### APPROVAL PAGE

# DESIGN AND DEVELOPMENT OF FOUR TO SIXTEEN CHANNEL VIDEO MULTIPLEXERS

#### Ronan Rahimi

Dr. Kenneth Sohn, Thesis Advisor Date Professor of Electrical and Computer Engineering and Acting Chairperson for Electrical and Computer Engineering, NJIT

Dr. Edip Niver, Committee Member Associate Professor of Electrical and Computer Engineering, NJIT

Dr. Stanley Reisman, Committee Member Professor of Electrical and Computer Engineering and Associate Chairperson and Graduate Advisor for Electrical and Computer Engineering, NJIT

Date

Date

# **BIOGRAPHICAL SKETCH**

| Author: | Ronan Rahimi                                |

|---------|---------------------------------------------|

| Degree: | Master of Science in Electrical Engineering |

| Date:   | January 1996                                |

# **Undergraduate and Graduate Education:**

- Master of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, New Jersey, 1996

- Bachelor of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, New Jersey, 1992

- Associate of Science in Engineering Science, Bergen Community College, Paramus, New Jersey, 1989

- Major: Electrical Engineering

This Thesis is dedicated to American Dynamics

#### ACKNOWLEDGMENT

I would first like to express my sincerest appreciation to my company American Dynamics at Orangeburg, New York, for their valuable resources and time during preparation of my thesis. I am also grateful to my senior hardware engineer Jimmy McWilliams as well as my senior software manager Frank Hemsing for their helpful effort in preparation, suggestions and discussion of my thesis.

Special thanks to Professors Kenneth Sohn, Edip Niver and Stanley Reisman for serving as members of the committee.

# TABLE OF CONTENTS

| Chapter                                                          |      |

|------------------------------------------------------------------|------|

| 1 INTRODUCTION                                                   |      |

| 2 HARDWARE                                                       |      |

| 2.1 Hardware Components                                          | . 8  |

| 2.1.1 Motorola 68HC11A1                                          | 8    |

| 2.2.2 32k External Rom                                           | 11   |

| 2.2.3 BrookTree (BT 851, YCrCb or RGB to NTSC/PAL Encoder)       | 11   |

| 2.2.4 BT819, Video Capture Processor for TV/VCR Analog Input     | 13   |

| 2.2.5 Alpha Numeric Generator                                    | 13   |

| 2.2.6 MicroChip Processor PIC16C56                               | 14   |

| 2.2.7 I <sup>2</sup> C Bus                                       | 14   |

| 2.2.8 Mitel Switch (MT8806 8 x 6 Analog Switch Array)            | 15   |

| 2.2.9 Dallas Semiconductor (DS1202 Serial Timekeeping Processor) | . 15 |

| 2.2.10 Silicon Gate Cmos 262,144 Words by 8 Bits Multiport Dram  | 16   |

| 3 SOFTWARE                                                       |      |

| 3.1 Modes of Operation                                           |      |

| 3.1.1 Live Mode                                                  | 23   |

| 3.1.2 Play Mode                                                  | 24   |

| 3.1.3 Record Mode                                                | 25   |

| 3.2 Power Loss                                                   | 26   |

| 3.3 Factory Reset                                                | 27   |

| 3.4 Alarm Section                                                | . 30 |

| 3.4.1 Alarm Inputs                                               | 30   |

# TABLE OF CONTENTS (Continued)

| Chapter Pa                                                       | age |

|------------------------------------------------------------------|-----|

| 3.4.2 Alarm Enable/Disable                                       | 30  |

| 3.4.3 Alarm Package                                              | 30  |

| 3.4.4 Alarm List Algorithm                                       | 32  |

| 3.5 Front Panel Input                                            | 33  |

| 3.6 Video Sequences and Switches                                 | 35  |

| 3.6.1 Mitel Switches and Memory Maps                             | 35  |

| 3.6.2 Video Sequencing                                           | 36  |

| 3.7 Video Loss Detection/Automatic Gain Control                  | 37  |

| 3.7.1 Video Loss                                                 | 37  |

| 3.8 AGC Algorithm                                                | 40  |

| 3.9 Time and Date Ic                                             | 44  |

| 3.10 Alphanumeric Output Ic                                      | 50  |

| 3.11 On Screen Menu System                                       | 51  |

| 3.11.1 Order of Menu Appearance                                  | 53  |

| 3.11.2 Appearance of Each ON Screen Menu Based On Default Values | 54  |

| 4 VIDEO CAPTURE PROCESSOR                                        | 62  |

| 4.1 Brooktree Bt819                                              | 62  |

| 5 PIC PROCESSOR                                                  | 67  |

| 6 INTERRUPTS                                                     | 74  |

| 7 SUMMARY AND CONCLUSION                                         | 76  |

| REFERENCES                                                       | 78  |

# LIST OF TABLES

| Table |                                                                | age |

|-------|----------------------------------------------------------------|-----|

| 3.1   | Key Pad Matrix Switches                                        | 34  |

| 3.2   | BT819 Input Value vs DAC Output                                | 42  |

| 3.3   | IRE Level vs ADC Read at Main Processor                        | 43  |

| 6.1   | I/O Port Requirements for Both 4 and 9/16 Channel Multiplexers | 75  |

| Fi   | gure P                                                             | age |

|------|--------------------------------------------------------------------|-----|

| 1.1  | Unit Housing                                                       | 3   |

| 1.2  | System Configuration                                               | 6   |

| 2.1  | Hc11 Interrupt and Timer Block Diagram                             | 9   |

| 2.2  | Hc11 Communication and Memory Block Diagram                        | 10  |

| 2.3  | NMC27C256 Block Diagram                                            | 11  |

| 2.4  | Video Encoder Circuit Diagram                                      | 12  |

| 2.5  | Single Dual Port Dram                                              | 17  |

| 2.6  | Image Storage                                                      | 17  |

| 2.7  | Memory Storage Locations                                           | 18  |

| 2.8  | Horizontal and Vertical Address Map for Formats 1 Through Format 4 | 19  |

| 3.1  | Digital Video Production Diagram                                   | 21  |

| 3.2  | Software Block Diagram                                             | 22  |

| 3.3  | Front Panel in Live Mode                                           | 23  |

| 3.4  | Front Panel in Play Mode                                           | 24  |

| 3.5  | Front Panel in Record Mode                                         | 25  |

| 3.6  | Video Loss Diagram                                                 | 38  |

| 3.7  | AGC Block Diagram                                                  | 40  |

| 3.8  | Serial Steering                                                    | 45  |

| 3.9  | Clock Diagram                                                      | 46  |

| 3.10 | ) Initialization Clock Routine                                     | 47  |

| 3.11 | Send/Receive Realtime Clock Bytes                                  | 48  |

# LIST OF FIGURES

# LIST OF FIGURES (Continued)

| Figure P                             | age |

|--------------------------------------|-----|

| 3.12 Read/Write Realtime Clock Bytes | 49  |

| 4.1 BT819 Block Diagram              | 66  |

| 5.1 Pic Vertical Time                | 68  |

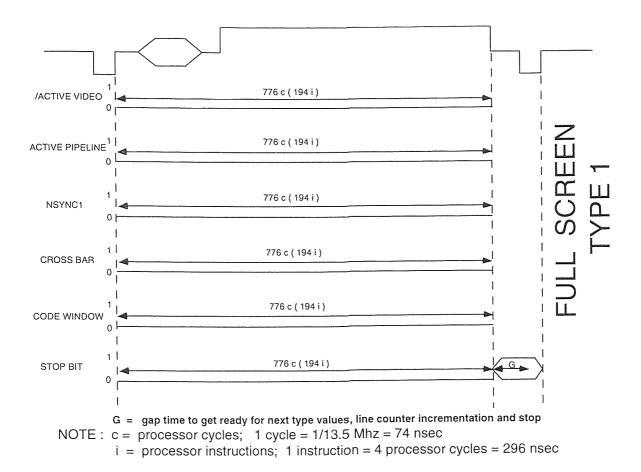

| 5.2 Pic Type1 Signal                 | 69  |

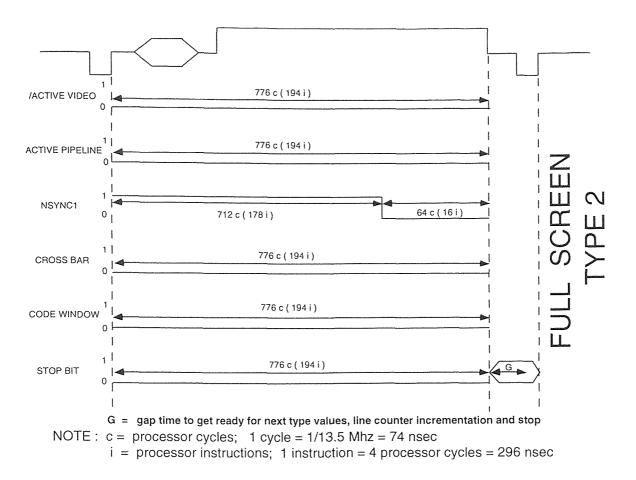

| 5.3 Pic Type2 Signal                 | 70  |

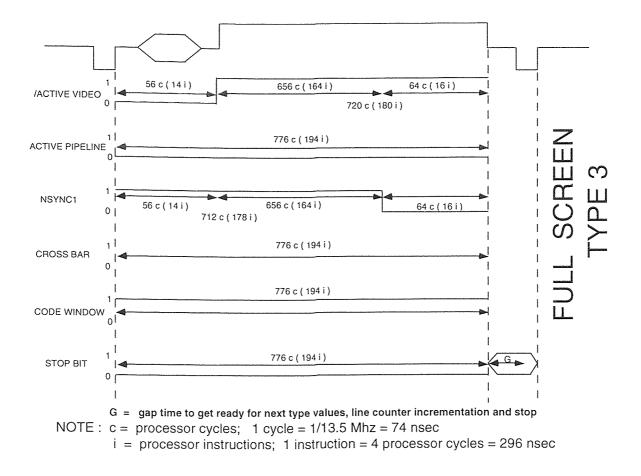

| 5.4 Pic Type3 Signal                 | 71  |

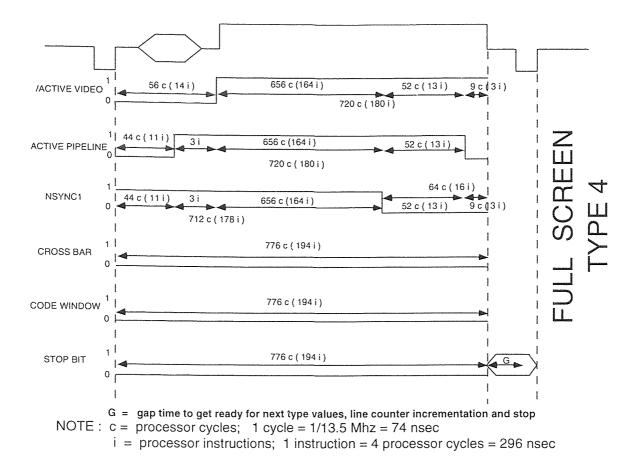

| 5.5 Pic Type4 Signal                 | 72  |

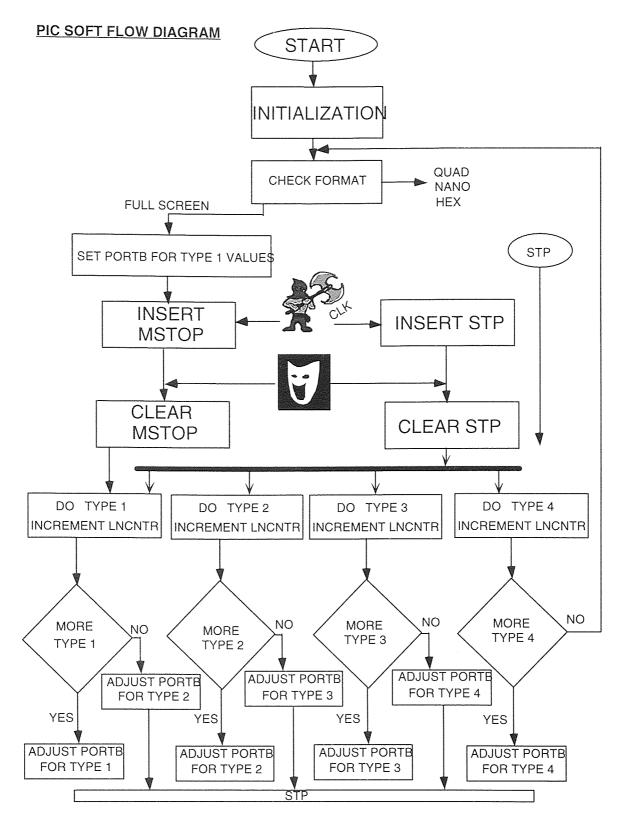

| 5.6 Pic Software Diagram             | 73  |

#### CHAPTER 1

#### INTRODUCTION

The purpose of this document is to provide a unique and summarized description of the Video Multiplexer (V.M.), both in terms of software coding and hardware design.

A time lapse VCR is a proven and valuable tool for documenting video events captured on a single VCR. Applications employing multiple cameras require additional VCRs, sequential switchers or Multi - format displays such as Quads, Nano and Hex. Each of these has its tradeoffs; for example, the VCR is an expensive piece of equipment and requires maintenance. The switcher reduces the rate at which each camera is recorded, and since the switcher output in most cases is non - synchronized and VCR expects to see constant sync, during playback the picture will contain instabilities like "picture flagging".

The video multiplexer technology substitute the use of costly time lapse VCRs for the CCTV customers with small budgets to spend on some expensive VCRs and its maintenance. Therefore, the four channel digital Video Multiplexer (V.M.) is a non-expensive state of art, time base corrected product for those type of customers. This digital Video Multiplexer is designed to fit on a single rack height, half rack cabinet with a desk or rack mount capability. All the hardwares are using surface mount technology with some through hole exceptions.

This product implements three mode of operations which all modes ( Live, Record and Playback ) use the full digital video capability available in this 4 channel

1

multiplexer. Every mode also behaves interactively and separately through user front panel modifications.

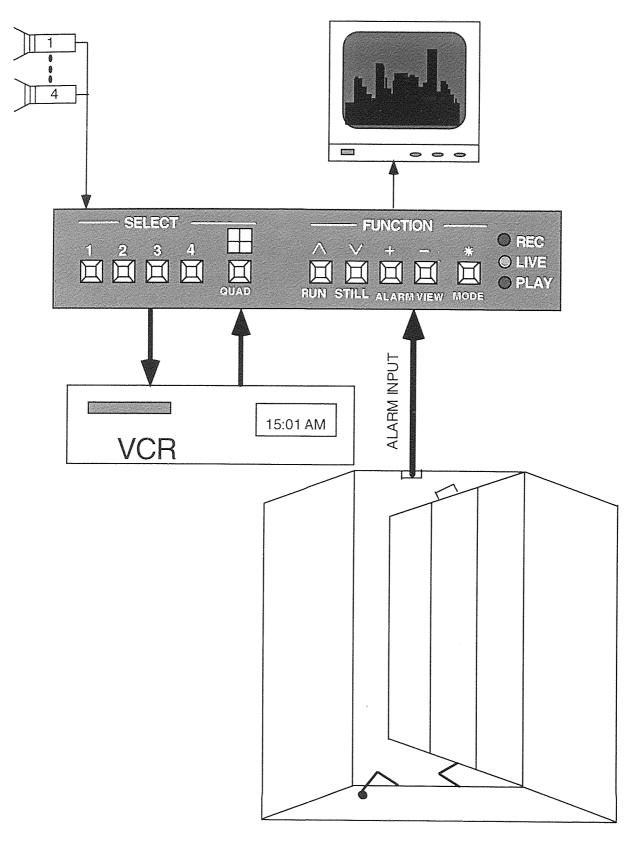

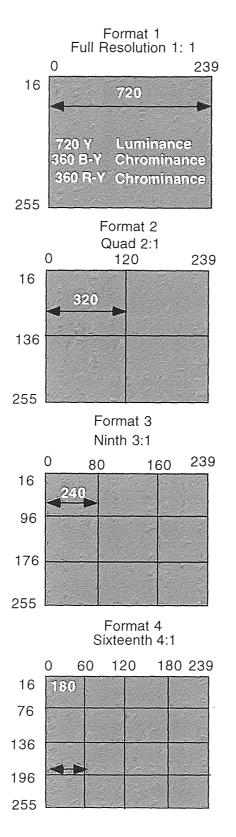

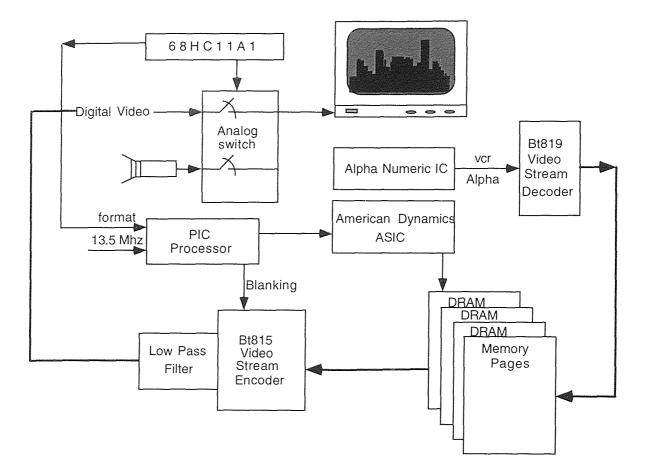

The software and hardware are designed side by side using simulators and real time hardwire bread board prototyping, so the final PC board can be debugged in less time and in more efficient way. This video multiplexer is capable of encoding (recording) up to four cameras on a single time lapse VCR and on the playback decoding these cameras are either displayed in full screen or quad (four digitized pictures) modes. The encoding/decoding for this machine is done through a two powerful encoding/decoding processors made by the Brooktree Corporation, which uses the latest technology in terms of buffering and sampling video signals. These two processors are capable of adjusting the picture for compression and recalibration of video signal in terms of color modulation/demodulation and number of vertical and horizontal syncs. All the encoded video signals are transferred to 12,000,000 dual ram memory cells; 6,000,000 for Chrominance and 6,000,000 for Luminance. The dual ram memory gets loaded with digital video through its parallel ports, and the stored digital video is transferred to the decoder processor via dual ram's serial port. The timing signals for transferring these digital bytes to and out of memory are done through another powerful processor made by American Dynamics known as ASYC controller. This timing processor basically produces the addressing counts for the dual ram's rows and columns as well as video synchronization. All these processors are discussed in more detailed through out the rest of this document.

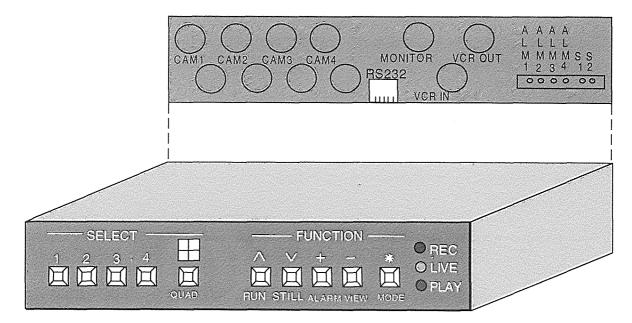

The back of this multiplexer has seven BNC connectors, four for camera inputs, one for VCR output, one for monitor output and one for VCR input during VCR playback and one external connector for four alarm inputs. Each pin on the external connector is used for one camera input, which when activated TAG the associated camera images with VID (Vertical Interval Data), meaning that on the VCR tape before video gets stored on to a tape, we store information about that camera input in this order; camera ID, the field bit indicator and the alarm bit. All the alarms also stored in an ALARM LOG tables, which then presented to the user on the screen in multiple lists. These lists are displayed to the user using an Alpha Numeric processor which uses video sync to mix video with pure ASCII characters. The protocol used to send ASCII characters to this character display processor uses serial communication. The ASCII datas are not stored in the dual ram memory because the alpha numeric processor is sitting in front of the encoding processor (Brooktree Bt819). The unit housing as well front and back panels are illustrated on the diagram below. On the back panel alarms, BNCs and two pins (S1, S2) for future code transfers can be viewed.

Figure 1.1 Unit Housing

Switching video signals are done through an eight by four analog matrix switch, which is also uses serial communication protocol. This analog matrix switch is controlled from front panel keys and all the communications including switching are controlled via Motorola microcontroller MC68HC11A1.

The some of features are;

- High resolution color display, 256-level gray scale over 16 million colors

- Automatic Gain Control (AGC)

- Password -protected setup program with on screen menus

- manual instant STILL button

- Full screen manual call-up of cameras or Quad display

- Automatic Alarm Call-up of full screen display of alarmed cameras

- alarms are tagged on the tape for easy review during playback

- Alarm logging

- Four alarm inputs and RS-232 remote control capability enhance product flexibility

- Multiple alarms can be sequenced

- Sequencing of Quad display with full-screen displays

- Video-Loss Detection on each video input

- On-screen displays include time, date, video loss indication and camera titles

- User-programmed data is saved in nonvolatile memory (EEPROM)

- Compact cabinet design optimizing the available workspace

- Remote control via RS-232 interface

This Video Multiplexer designed to be expanded from 4 camera switch to 9 and then 16 camera switch multiplexers. All theses versions will have the same type of hardware components and software modules to accommodate the design time and expenses for all three products. The main feature of this 4 channel switcher/multiplexer is the use of full scale digital video processing to lower the unit cost.

Figure 1.2 System Configuration

#### CHAPTER 2

#### HARDWARE

The hardware is designed to be housed in a single rack height, half rack cabinet. The unit will be available configured for desk or rack mounting. The new cabinet design in this unit will eliminate the need for separate top and bottom covers and makes the conversion from desk mount to rack mount as simple as possible. The reason for this kind of cabinet design is, historically the test department at American Dynamics has had the requirement to be able to test and examine both top and bottom of the printed circuit board while in its cabinet. However, because of the evolution in ATE (Automatic Test Equipment) and SMT (Surface Mount Technology) at American Dynamics, this requirement is no longer exists. This new cabinet design of Video Multiplexer (V.M.), but will contribute to the cost reduction of existing products that are presently using the old style single rack height, half rack cabinet.

The SMT made us to design the circuit board in four layers. The top layer for surface mount components, the bottom layer for through hole components and middle layer for ground and five volts power supply. The design of this hardware is done on the CAD and the routing of the board is implemented by CAD internal automation and also by CAD operator.

#### 2.1 Hardware Components

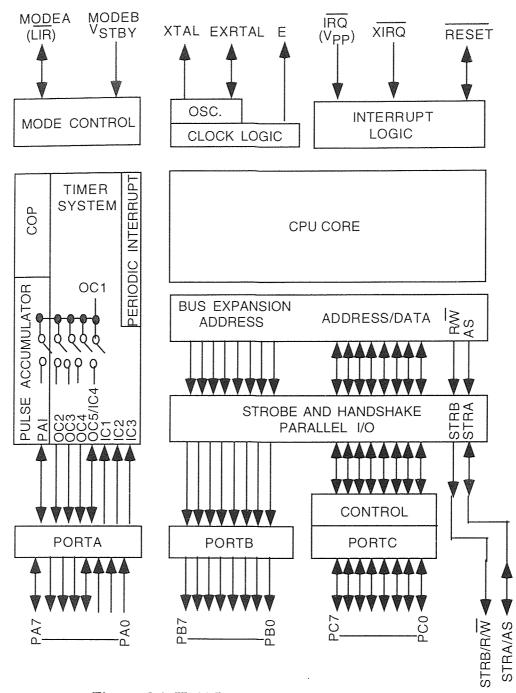

#### 2.1.1 Motorola 68HC11A1

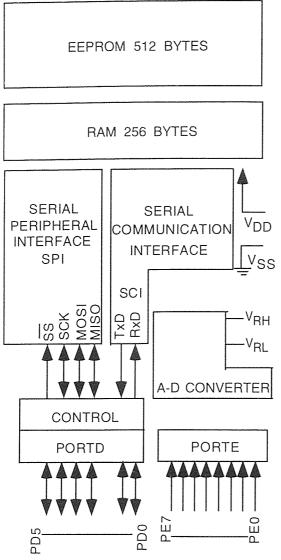

The high-density complementary metal-oxide semiconductor (HCMOS) MC68HC11A1 is an advanced 8-bit MCU with highly sophisticated, on-chip peripheral capabilities. New design techniques were used to achieve a nominal bus speed of 2 Mhz. In addition, the fully static design allows operation at frequencies down to dc, further reducing power consumption.

The HCMOS technology used on the MC68HC11A1 combines smaller size and higher speeds with the low power and high noise immunity of CMOS. On-chip memory systems include 256 bytes of random-access memory (RAM), and 512 bytes of electrically erasable programmable ROM (EEPROM).

Major peripheral functions are provided on-chip. An eight-channel analog-todigital (A/D) converter is included with eight bits of resolution. An asynchronous serial communications interface (SCI) and a separate synchronous serial peripheral interface (SPI) are included. The main 16-bit, free running timer system has three input-capture lines, fine output-compare lines, and real-time interrupt function. An 8-bit pulse accumulator subsystem can count external events or measure external periods.

Self monitoring circuitry is included on-chip to protect against system errors. A computer operating properly (COP) watchdog system protects against software failures. A clock monitor system generates a system reset in case the clock is lost or runs too slow. An illegal opcode detection circuit provides a nonmaskable interrupt if an illegal opcode is detected.

Figure 2.1 Hc11 Interrupt and Timer Block Diagram

Figure 2.2 Hc11 Communication and Memory Block Diagram

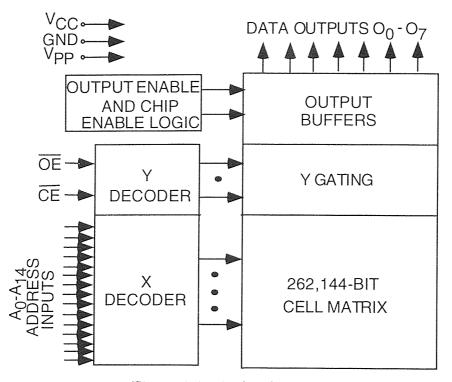

#### 2.2.2 32k External Rom

The NMC27c256 is a high speed 256K UV erasable and electrically reprogrammable CMOS EPROM. The NMC27c256 is packaged in a 28 pin dual inline package with transparent lid. Two of its most important features are TRI-STATE <sup>®</sup> and single 5V power supply.

Figure 2.3 NMC27C256 Block Diagram

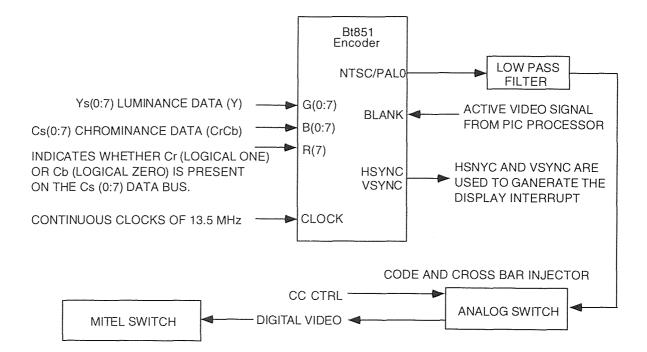

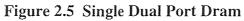

# 2.2.3 Brook Tree (BT851, YCrCb or RGB to NTSC/PAL Encoder)

The Bt851 is designed specifically for video systems requiring the generation of 525-line (M) NTSC or 625-line (B, D, G, H, I) PAL composite or Y/C (S-video) video signals.

The Bt851 generates HSYNC (horizontal sync) and VSYNC (vertical sync) outputs. BLANK is an input and may be externally controlled, this external signal produced from PIC Processor called Active Video (Refer to pic processor section). 24-bit linear RGB data is gamma-corrected and converted to YCrCb. Alternately, 16-bit (4:2:2) YCrCb data may be input directly. The YCrCb is low pass filtered to 1.3 Mhz and modulated. The rise and fall times of sync and the burst envelope are internally controlled.

Analog luminance (Y), and Chrominance (C) information are available on the Y and C outputs for interfacing to S-video equipment. The composite analog video signal is output simultaneously onto both NTSC/PAL analog outputs. This allows one output to provide baseband composite video and another output to drive an RF modulator.

Figure 2.4 Video Encoder Circuit Diagram

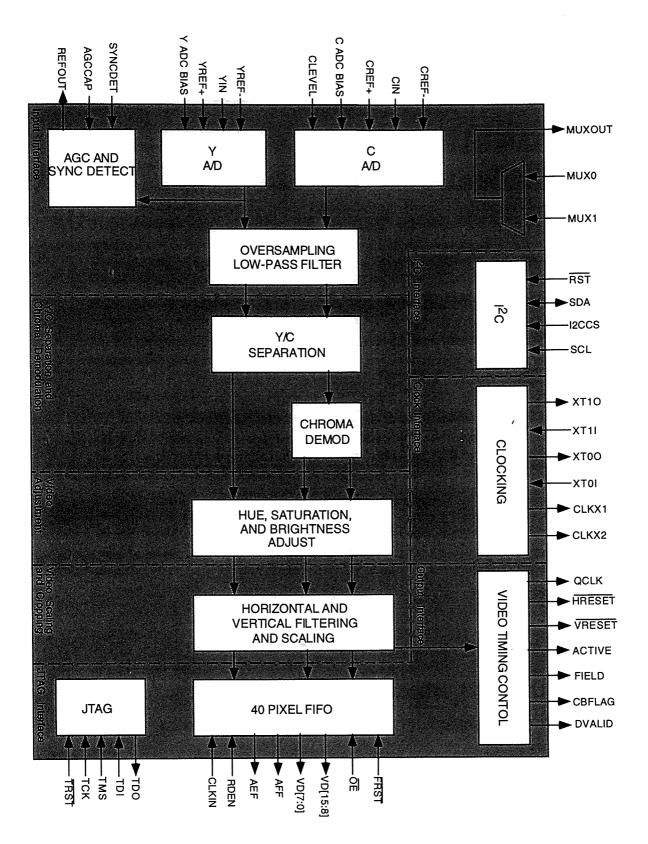

#### 2.2.4 BT819, Video Capture Processor for TV/VCR Analog Input

The Bt819 Video Capture Processor is a fully integrated single-chip decoding and scaling solution for analog NTSC/PAL input signals from TV tuners, VCRs, Cameras, and other sources of composite or Y/C video. It is first front-end input solution for low-cost PC video/graphics systems to deliver complete integration and high performance video synchronization, Y/C separation, filtered scaling and optional FIFOed output pixel data. The Bt819 has all the mixed signal and DSP circuitry required to convert an analog composite waveform into a scaled digital video stream supporting a variety of video formats, resolutions and frame rates (The detailed Architectural are discussed in Bt819 section).

#### 2.2.5 Alpha Numeric Generator

The NEC6450 is on-screen character display CMOS LSI which is combined with microcontroller and used for displaying character strings on the monitor screen. Character format is 12 x 18 dots, and one character enables displaying numbers kanji and hiranaga. Since this LSI has built in video switches, video signals can be input and output by composite video signals, and video signals can be generated internally so that characters can be displayed with no external signals. Only three wires are required to communicate with this character generator: 1- STB (strobe), 2- I/O (data line), and 3- CLK (serial clock). Data can be transferred to this IC one character (1 byte) at a time. For this transferring 72 µsec is a required time.

#### 2.2.6 MicroChip Processor PIC16C56

The PIC16c56 from Microchip Technology is a family low coast, high performance, 8bit, fully static, EPROM based CMOS microcontrollers. It employs RISC like architecture with only 33 single word/single cycle instructions to learn.

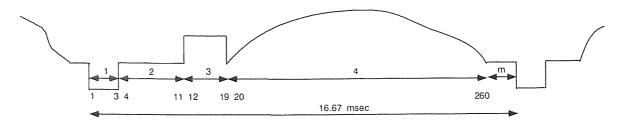

This processor is used in conjunction with other digital Ics to produce signals necessary in digital video to produce digital pictures. One of the conjunction Ics is ASIC processor made by American Dynamics which is basically the production of row and column clocks for DRAM memory. This PIC program basically marks regions of video every 60HZ (16.5 msec) for the hardware; for example the active video portion of the video or the place below active video for storage of data such as alarm bits.

This processor has the ability to synchronize itself with input video signals. This synchronization is accomplished by applying 13.5 Mhz clock to the processor, and on end of each NTSC line the processor clock will be stopped and then restarted at the beginning of each NTSC line. The duration of each NTSC line is  $63.5 \,\mu$ sec, and during this time the PIC processor outputs signals necessary for hardware to produce, store and output digital video.

# 2.2.7 $I^{2}C$ Bus

The I<sup>2</sup>C bus is a multimaster bus. This means that more than one device capable of controlling the bus that can be connected to it. The I<sup>2</sup>C bus is controlled via two lines SDA (serial data line), and SCL (serial clock line). Both SDA and SCL are bi-directional lines, connected to a positive supply voltage via a pull-up resistor. When the line is free both

lines are high. Data on the  $I^2C$  bus can be transferred at a rate up to 100Kbits/s. The bus capacitance is 400pF.

Bit transfer duo to variety of different technology devices (CMOS, NMOS,  $I^2L$ ) which can be connected to the  $I^2C$  bus, the levels of the logical 0(low) and 1(high) are not fixed and depend on the appropriate level of V<sub>DD</sub>. One clock pulse is generated for each data bit transferred. For data to be valid the SDA line must be stable during the high period of the clock. The high or low state of the data line can only change when the clock signal on the SCL line is low.

#### 2.2.8 Mitel Switch (MT8806 8 x 6 Analog Switch Array)

The mitel MT8806 is fabricated in Mitel's ISO-CMOS technology providing low power dissipation and high reliability. The device contains a 8x4 array of crosspoint switches along with 5 to 32 line decoder and latch circuits. Any one of the 32 switches can be addressed by selecting the appropriate five address bits. The selected switch can be turned on or off by applying a logical one or zero to the DATA input. Vss is the ground reference of the digital inputs. The range of analog signal is from  $V_{DD}$  to  $V_{EE}$ . Chip Select (CS) allows the crosspoint array to be cascaded for matrix expansion.

#### 2.2.9 Dallas Semiconductor (DS1202 Serial Timekeeping Processor)

The DS1202 Serial Timekeeping Chip contains a real time clock/calendar and 24 bytes of static RAM. It communicates with a microprocessor via a simple serial interface . The real time clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The end of the month date is automatically adjusted for months with less than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12-hour format with an AM/PM indicator. Interfacing the DS1202 with a

microprocessor is simplified by using synchronous serial communication. Only three wires are required to communicate with the clock/RAM: 1- /RST (reset), 2- I/O (data line), and 3- SCLK (serial clock). Data can transferred to and from the clock/RAM one byte at a time or in a burst of up to 24 bytes. The DS1202 is designed to operate on a very low power and retain data and clock information on less than 1 microwatt.

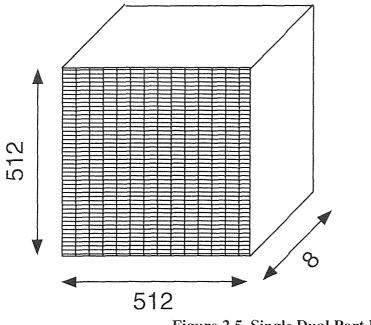

#### 2.2.10 Silicon Gate Cmos 262,144 Words by 8 Bits Multiport Dram

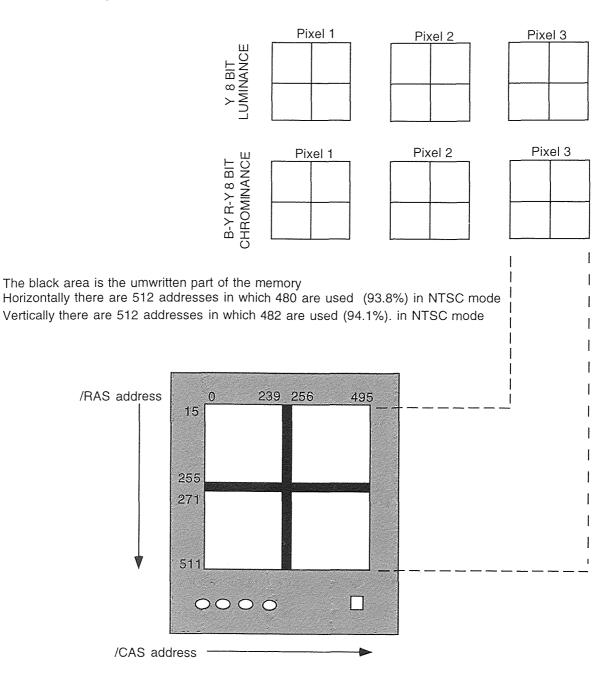

The Tc582257 is a 2M bit CMOS multiport memory equipped with a 262,144 words by 8 bits dynamic random access memory port and a 512 words by 8 bits static serial access memory port (SAM). The TC52857 supports three types of operations; Random access to and from the RAM port, high speed serial access to and from the SAM port and bidirectional transfer of data between any selected row in the Ram and the SAM. The diagrams on the next pages shows the use of this device.

Memory array size is 6 Dual Port Drams = 12,582,912 bits

The memory architecture can either store 4 separate fields or two separate frames.

Figure 2.6 Image Storage

For each physical address there are three corresponding pixels, 240 adresses by 3 pixels = 720 active pixels

Figure 2.7 Memory Storage Locations

Figure 2.8 Horizontal and Vertical Address Map for Formats 1 Through Format 4

#### CHAPTER 3

#### SOFTWARE

Software design in this product is separated into different modules and generalized functions. This software set tried to implement the idea of Object Oriented Programming (Oops) to simplify the use of modules. Module groups are separated to hardware and pure software groups. One of the features of this program is the use of Array of function pointers. The reason is the ability to use the software set for 9 and 16 channel by a few modification to hardware modules. These array of function pointers are based on the functionality of front panel keys in different modes.

Figure 3.1 Digital Video Production Diagram

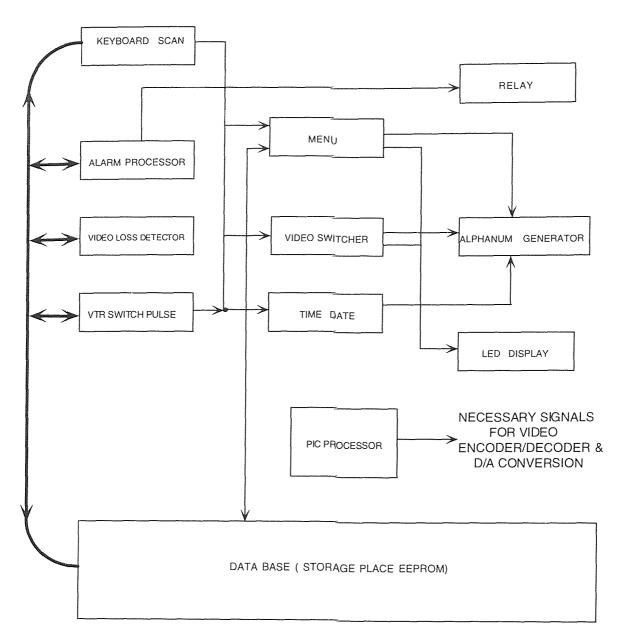

Figure 3.2 Software Block Diagram

# 3.1 Modes of Operation

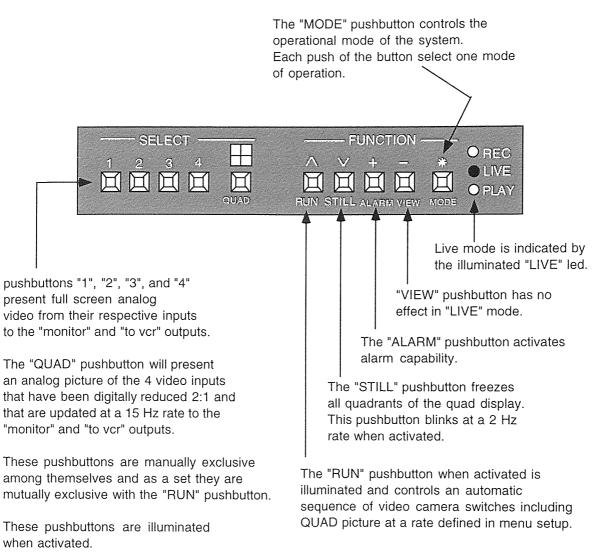

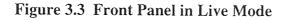

This multiplexer as described earlier has three modes of operation (LIVE, PLAY, and RECORD). These modes are shown in the next few diagrams. PLAY and LIVE modes are similar, except for that fact that in LIVE mode the inputs to the system are from live input cameras, and in the PLAY mode the input is from a video tape recorder.

# 3.1.1 Live Mode

Figure 3.4 Front Panel in Play Mode

## 3.1.3 Record Mode

Figure 3.5 Front Panel in Record Mode

# 3.2 Power Loss

A number of system variables will have to be preserved to survive a power loss. These

variables will all be grouped into a single structure, with a typedef declaring it as a data

type called POWERLOSS. This POWERLOSS data structure will be written to

EEPROM or read from EEPROM as required.

The elements of the POWERLOSS data structure will be :

enum SQUARETYPES { SQ\_FULL, SQ\_FOUR, SQ\_NINE, SQ\_SIXTEEN };

enum OPERATINGMODES { OP\_LIVE, OP\_RECORD, OP\_PLAYBACK };

typedef struct {

unsigned running : 1; /\* Running Camera Sequence \*/

unsigned squares : 2; /\* assigned SQUARETYPES \*/

unsigned opmode : 2; /\* assigned OPERATINGMODES \*/

unsigned alarm\_armed : 1; /\* boolean \*/

unsigned camera\_number : 4; /\* int \*/

} POWERLOSS;

#### 3.3 Factory Reset

The multiplexer can be returned to a condition where all programmable features of the machine can be returned to a default condition. This is called Factory Reset because it is the way the machine is programmed when it is packed for shipping.

A user can factory reset the multiplexer by holding the ALARM button down and cycling AC power. The user can release the ALARM button, 1 second after the power has been applied. The re-programming of the defaults may take longer than 1 second. The reason for this delay is the actual time required for the Factory Table be written to EEProm in Hc11. As indicated below the actual size of this table is array of 397 bytes.

| char const FactoryTabl | e[397] = {                                             |

|------------------------|--------------------------------------------------------|

| /* MENU 10 (01)        | */ 0,1                                                 |

| /* MENU 0 (24)         | */ 20,24,24                                            |

| /* MENU 3 (5)          | */ 21, /****** 3rd entey *****/                        |

| /* MENU 1 (67)         | */ 2,3                                                 |

| /* MENU 2 (823)        | */ 15,15,15,15,15,15,15,15,15,15,15,15,15,1            |

| /* MENU 3 (2425)       | */ 8,11                                                |

| /* MENU 4 (26)         | */ 1                                                   |

| /* MENU 5 (2740)       | */ 'C','A','M','E','R','A',' ','1',' ',' ',' ',4,6     |

| /* MENU 6 (4154)       | */ 'C','A','M','E','R','A',' ','2',' ',' ',' ',4,6     |

| /* MENU 7 (5568)       | */ 'C','A','M','E','R','A',' ','3',' ',' ',' ',' ',4,6 |

| /* MENU 8 (6982)       | */ 'C','A','M','E','R','A',' ','4',' ',' ',' ',4,6     |

| (8396)                 | */ 'C','A','M','E','R','A',' ','5',' ',' ',' ',' ',4,6 |

|                        | */ 'C','A','M','E','R','A',' ','6',' ',' ',' ',' ',4,6 |

| (111124)               | */ 'C','A','M','E','R','A',' ','7',' ',' ',' ',4,6     |

| (125138)               | */ 'C','A','M','E','R','A',' ','8',' ',' ',' ',' ',4,6 |

| (139152)               | */ 'C','A','M','E','R','A',' ','9',' ',' ',' ',' ',4,6 |

| (153166)               | */ 'C','A','M','E','R','A', ','10',' ', ',',',',4,6    |

| (167180)               | */ 'C','A','M','E','R','A',' ','11',' ',' ',' ',4,6    |

| (181194)               | */ 'C','A','M','E','R','A',' ','12',' ',' ',' ',4,6    |

|                        | */ 'C','A','M','E','R','A',' ','13',' ',' ',',',4,6    |

|                        | */'C','A','M','E','R','A','','14','','',',',4,6        |

| (223236)               | */'C','A','M','E','R','A','','15','','',',4,6          |

|                        | */ 'C','A','M','E','R','A',' ','16',' ',' ','4,6       |

|                        | */10                                                   |

| /* MENU 9 (251)        |                                                        |

| /* MENU 10 (252)       | */ 3, /****** 3rd entry *****/                         |

NOTE: This part of the table specify the location of log tables in EEPROM and possible

values to store. In case of no entry the locations should have value of 0x20 (' '). The

values from memory is copied line by line to dwell[0]..dwell[6], dwell[7] holds the value

of pages[1..4] defined at top under MENU 5.

EEPROM start location for log tables = 253

Length of each line = 7 bytes

One line on each page might contain camera number, time and date.

offset from one page to other = 5 \* 7 = 35 bytes

#### PAGE 1:

| (253259) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20 |

|----------|------------------------------------|

| (260266) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20 |

| (267273) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20 |

| (274280) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20 |

| (281287) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20 |

# PAGE 2:

| (288294) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20  |

|----------|-------------------------------------|

| (295301) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20, |

| (302308) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20, |

| (309315) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20, |

| (316322) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20, |

#### PAGE 3:

| (323329) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20, |

|----------|-------------------------------------|

| (330336) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20, |

| (337343) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20, |

| (344350) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20, |

| (351357) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20, |

### PAGE 4:

| (358364) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20, |

|----------|-------------------------------------|

| (365371) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20, |

| (372378) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20, |

| (379385) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20, |

| (386392) | 0x20,0x20,0x20,0x20,0x20,0x20,0x20, |

PASSWD MENU (393..396) 17,17,17,17 };

# 3.4 Alarm Section

# 3.4.1 Alarm Inputs

These inputs are from a latch based on address decoding, called alarm\_latch.

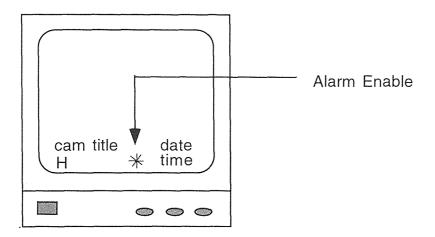

# 3.4.2 Alarm Enable/ Disable

The ability of this multiplexer is to react to alarm conditions can be enabled or disabled by toggling the front panel alarm button. The LED associated with the front panel alarm button will be on when alarms are enabled, and will be off when alarms are ignored. This enabling indicated on the bottom screen by \*

# 3.4.3 Alarm Package

This package is implemented based on American Dynamics main switcher alarm design, which used link list to implement the alarm algorithm. Let us explain this algorithm through examples.

Example 1: Imagine that three alarms read by scan routine and passed on to software alarm algorithm to place for further evaluation. This software routine first ask to see if alarm for particular camera exists or not. If alarm is new places the alarm in the SEQ (sequence) table following Link List algorithm in this manner; If alarm 3, 4 and 6 activated,

example 1.1: alarm 3 activated; last alarm = &seq[3]; sequencer = &seq[3].

alarm 4 activated while 3 on; last alarm = &seq[4]; sequencer =

&seq[4]; seq[3] = 4; seq[4] = 3.

alarm 6 activated while sequencer = &seq[4]; last alarm = &seq[6];

sequencer = &seq[6]; seq[4] = 6; seq[6] = 3;

SEQ[8..16]:

| 0 | 1    | 2 | 3 | 4  | 5    | 6 | 7 | 8    | < Alarm to display      |

|---|------|---|---|----|------|---|---|------|-------------------------|

|   | <br> |   | 4 | 61 | <br> | 3 |   | <br> | < Next alarm to display |

example 1.2: alarm 3 activated; last alarm = &seq[3]; sequencer = &seq[3].

alarm 4 activated while 3 on; last alarm = &seq[4]; sequencer =

&seq[4]; seq[3] = 4; seq[4] = 3.

alarm 6 activated while sequencer = &seq[3]; last alarm = &seq[6];

sequencer = &seq[6]; seq[3] = 6; seq[6] = 4;

SEQ[8..16]:

0

1

2

3

4

5

6

7

8

<----- Alarm to display</td>

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I<

These two examples showed that the property of Link List is maintained and the sequencing and displaying the current alarm is maintained as the new alarm forced into the sequence list.

This algorithm permits us to write separate modules or libraries for future products by simply writing the alarm scan routine part that is customized to individual hardware, and reads individual alarms. In this product these alarms are maintained on an external input latch called Alarm\_Latch.

#### 3.4.4 Alarm List Algorithm

This multiplexer supports an **Alarm Log**. This alarm log is a list of the 20 alarms which have been detected by the machine. Each alarm log entry will be a 7 byte record containing 1 byte of camera number and 6 bytes which contain the packed BCD representation of the time and date of the alarm as read from the on-board time and date chip. This log list is viewable through the menu system. The alpha-numeric display in the multiplexer will allow up to 5 alarm logs per screen, so the alarm log menu will be divided into 4 pages. The next viewable log page can viewed if any data exists on that page, also each page indicates if user can go to next page. The last alarm log display includes an option to **Clear Alarm Log Pages**. This function is available only to last page of the log display. Choosing to clear the alarm list clears all 20 entries in the alarm log and adjust the screen to first alarm list and display empty screen.

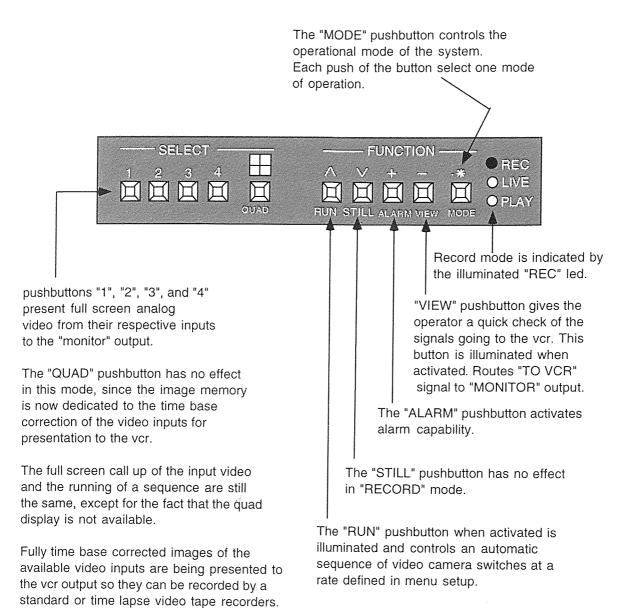

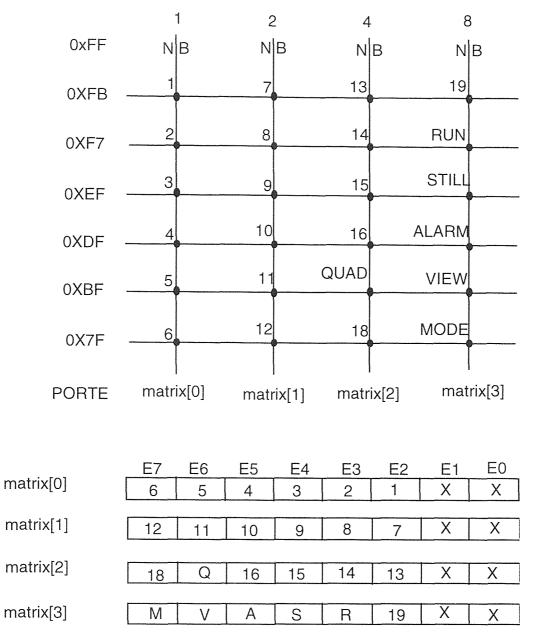

#### **3.5 Front Panel Input**

The front panel of the 4 channel device has 10 pushbuttons and 10 LED's. The front panel of the 9 channel device has 16 buttons and 16 LED's, and the 16 channel device has 23 switches and 23 LED's. The software developed for this system will use a lookup table to map these actual switches to logical key legends which will always have the same index number no matter what device the software is for. The non-changing key legend values will be obtained from the front panel of the proposed 16-channel device, starting at the leftmost button, assigning it the value one, then from left to right, assigning ascending order to each button. This numbering system will then be applied to all the devices, so that for example the QUAD button will always be number 17, even in a device which has only 10 switches. This key number assignment is described in an ENUMerated data type declaration :

```

enum KEYCONSTANTS {

```

KCAM1 = 1, KCAM2, KCAM3, KCAM4, KCAM5, KCAM6, KCAM7, KCAM8, KCAM9, KCAM10, KCAM11, KCAM12, KCAM13, KCAM14, KCAM15, KCAM16, KQUAD, KNINE, KSIXTEEN, KRUN, KSTILL, KALARM, KVIEW,KMODE

};

Table 3.1

Key Pad Matrix Switches

The keyscanning routine will be responsible for returning values in the enumerated set.

#### **3.6** Video Sequences and Switches

#### 3.6.1 Mitel Switches and Memory Maps

The 4 channel device will be using the MITEL MT8806 8 X 4 Analog Switch Array. We will consider the 8 Y pins of the device to be inputs, and the 4 X pins of the device to be outputs. The AD1582 4-channel MUX will have 6 of the Y inputs connected to the D/A video converter, the VCR, and the 4 camera videos, and 3 of the 4 X outputs connected to the A/D video converter, the video loss Sampler, and the user monitor. We can think of the MT8806 as providing a 6 X 3 crosspoint for our purposes.

Memory Mapping: -

The lower 8-bits of the memory map for the Mitel are as follows:

#### xxxAAABB

Where AAA = Input Camera Number and BB = Output Channel Number. The base address is currently 0x3200 and is called /DECODE3. Combining the base address with the lower byte encoding produces the address of the switch required. To close a crosspoint, write a '1' to the address, to clear the crosspoint write a '0'. Since the IC is a crosspoint switch, and the input and output assignments above are only logical concepts, we have to be careful in how the switch is used. The following rules apply when using this crosspoint switch.

1 - A single input can be connected to all 3 outputs. Example: Camera #1 video can be connected to the display monitor, to the videoloss sampler, and to the A/D video converter. 2 - No single output can have more than one input connected. Example:

Camera #1 and camera #2 cannot both be connected to the display monitor. This appears on the monitor as the sum of the two videos.

3 - All requests to connect an input Y to an output X must do it in steps:

- a) check to see if Y is already connected to X.

- b) If Y is not connected to X, the current connection to X must be broken and then the new connection can be made.

- c) If Y is connected already to X, then refuse the request.

4 - A bitmap of the current switch state must be maintained to support the requirements of #3 above.

#### 3.6.2 Video Sequencing

Sequences are automatic camera switches executed by the cpu in the multiplexer based on a timing parameter called a DWELL time. The dwell time is programmed through the menu system. There is one dwell time, which is applied to all cameras in the SEQUENCE LIST. The sequence list in the programming menu is used to include or exclude cameras in the sequence. The sequence can also contain a MULTIVIEW picture. The selection of the type of multiview picture is not programmable, but is chosen by the multiplexer software using an algorithm called Largest\_Viewable\_Multiscreen. This inclusion of the multiview picture is programmed from the menu system.

# 3.7 Video Loss Detection / Automatic Gain Control

Video Loss (VL) and Automatic Gain Control (AGC) will be combined functions which both use data collected from a single source. The data source for these two functions is the A/D conversion of each of the camera video signals available to the machine. The A/D conversion is done in the HC11 using the on-board 8-bit converter. The Vrh of the system will be 5.0 V, and the Vrl of the system will be 0.0 V. The VL/AGC data collection routine will maintain an array of the digitized camera videos ( 8bits ) and use the data to interpret VL and AGC actions.

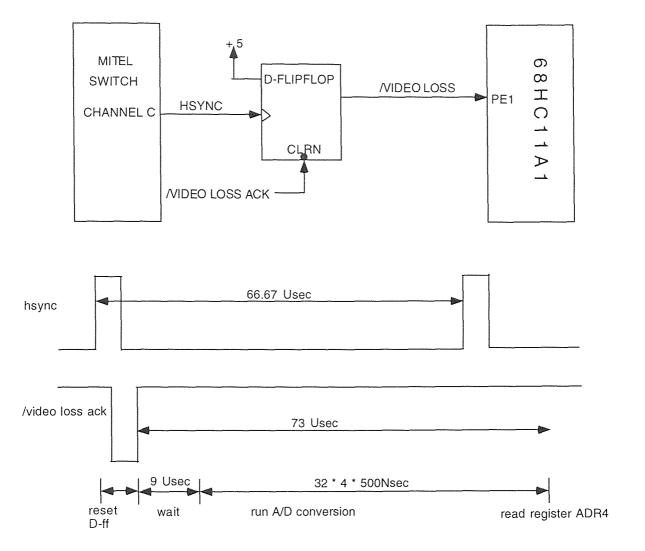

#### 3.7.1 Video Loss

Video Loss is sampled on hc11 portE, channel 1. The rate of sampling is not critical, and once per second is satisfactory.

For each video channel, switch the desired video input to the Video Switch channel C. This connects the desired video to the video loss circuit. The Video Loss Circuit is a sync stripper and an RS flip-flop (RSFF). The microprocessor has an output to the Reset of the RSFF, and an analog input from the Q output of the RSFF. The video loss algorithm is

1- Switch desired video to Video Switch channel 3 output.

2 - Write a zero to the RSFF Reset pin.

3 - Write a 1 to the RSFF output pin.

4 - Perform a A/D conversion on the Q output of the RSFF.

5 - Analyze: If conversion result is > 1/2 Vcc, then assume a video signal is presentElse assume a video signal is absent.

# 6 - Mark a bit in a bit array. Bits == 1 mean Video Is Present

Figure 3.6 Video Loss Diagram

Specific Implementation:

The function for video loss will be called boolean HasVideo( int channelnum )

which will encapsulate this hardware sequence and return TRUE or FALSE.

The specific hardware implementation of this for the 4 channel device is

1- Clear all connections in Mitel switch (/DECODE3 @ 3200). Set the connection for the channel number.

2 - /DECODE12 (u103), D6 = 0; (Hold Reset of FF down)

3 - /DECODE12 (u103), D6 = 1; (release Reset of FF)

4 - convert hc11.porte channel 1;

Report of video loss.

When a report is required,

- The internal raster to character generator will be switched on.

- The Mitel switch will be updated.

- The VIDEOLOSS\_MESSAGE will be written to the display.

### 3.8 AGC Algorithm

The AGC routine will be to sample hc11 portE d0. For the moment, the answers will be stored in an array of 4 characters. To obtain the video, switch the video channel to be sampled to the Video switch output channel A. If you have done a normal switch then this has already been done.

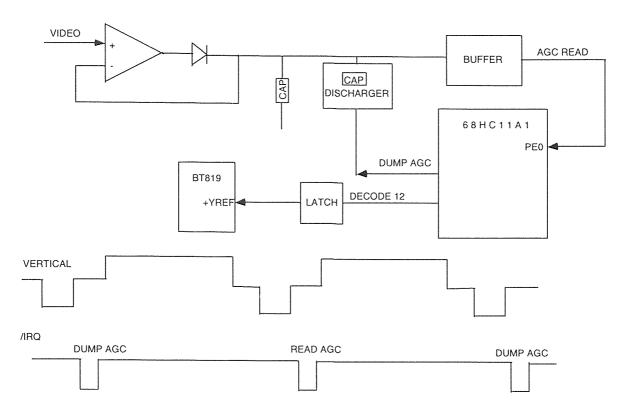

# Figure 3.7 AGC Block Diagram

Experimental IRE values were run and recorded on the tables below. The IRE values are supplied by the signal generator and corresponding ADC and Q0-Q3 values at HC11 and Bt819 were measured.

Dump agc is implemented every 30 msec (every other vertical time) as well as AGC read as shown in the diagram above. Agc read is digitized value of incoming video peak and dump agc is the circuit that resets the peak detector circuit. Values are transferred to

| Q0 - Q3 to BT819 | STEP | DAC out | Delta V |

|------------------|------|---------|---------|

| 0000             | 0    | 0.981   |         |

| 0000             | 1    | 1.042   | 61 mv   |

| 0010             | 2    | 1.097   | 55 mv   |

| 0011             | 3    | 1.158   | 61 mv   |

| 0100             | 4    | 1.233   | 75 mv   |

| 0101             | 5    | 1.294   | 61 mv   |

| 0110             | 6    | 1.349   | 55 mv   |

| 0111             | 7    | 1.410   | 61 mv   |

| 1000             | 8    | 1.458   | 48 mv   |

| 1001             | 9    | 1.519   | 61 mv   |

| 1010             | 10   | 1.574   | 55 mv   |

| 1011             | 11   | 1.635   | 61 mv   |

| 1100             | 12   | 1.710   | 75 mv   |

| 1101             | 13   | 1.771   | 61 mv   |

| 1110             | 14   | 1.825   | 54 mv   |

| 1111             | 15   | 1.887   | 62 mv   |

# Table 3.1 Bt819 Input Value vs DAC Output

| IRE LEVEL | AGC READ VOLTS | Delta V | ADC READ at HC11 |

|-----------|----------------|---------|------------------|

|           |                |         |                  |

| 0         | 0.584          |         | 11               |

| 10        | 0.653          | 69 mv   | 21               |

| 20        | 0.724          | 71 mv   | 30               |

| 30        | 0.795          | 71mv    | 40               |

| 40        | 0.866          | 71mv    | 49               |

| 50        | 0.936          | 70 mv   | 59               |

| 60        | 1.008          | 72mv    | 68               |

| 70        | 1.079          | 71 mv   | 77               |

| 80        | 1.150          | 71 mv   | 87               |

| 90        | 1.222          | 72 mv   | 96               |

| 100       | 1.293          | 71 mv   | 106              |

| 110       | 1.364          | 71 mv   | 115              |

| 120       | 1.435          | 71 mv   | 125              |

| 130       | 1.506          | 71 mv   | 134              |

| 140       | 1.577          | 71 mv   | 144              |

| 150       | 1.648          | 71 mv   | 153              |

| 160       | 1.719          | 71 mv   | 163              |

| 170       | 1.790          | 71 mv   | 172              |

| 180       | 1.861          | 71 mv   | 182              |

Table 3. 2 IRE Level vs ADC Read at Main Processor

## 3.9 Time and Date Ic

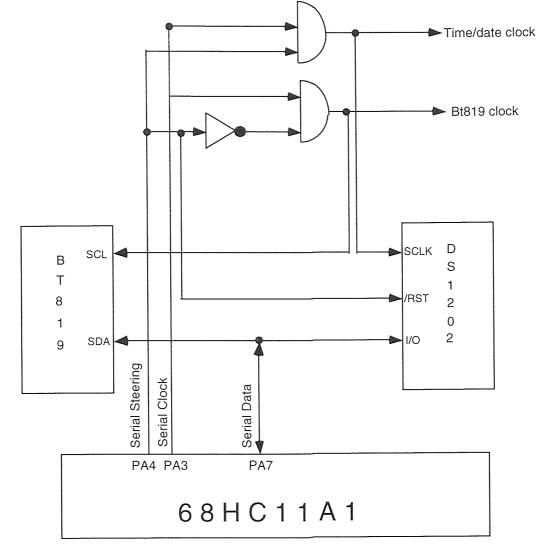

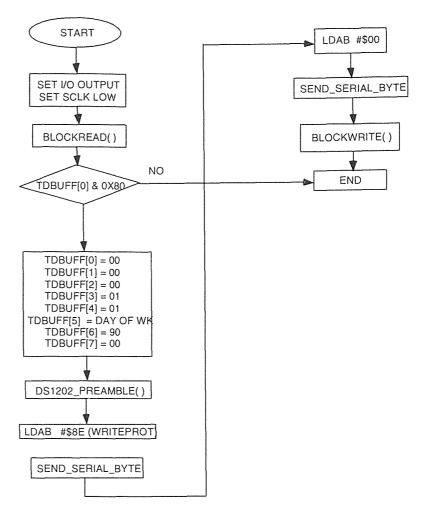

The IC chosen for maintaining time and date is the Dallas DS1202. This device has a bidirectional serial interface. There may be some conflict with other serial devices in the system. The DS1202 has been used in other American Dynamics line of products. The code is written in assembly and contains functions that can be called from C program. Three signals are required to communicate with DS1202; /RST, SCLK, and I/O. These are implemented in the AD1582 as :

| /RST is | PA4 |

|---------|-----|

| SCLK is | PA3 |

| I/O is  | PA7 |

When not communicating with the DS1202, you must hold the /RST signal low. This steers the I/O wire and the SCLK wire to the Brooktree Bt819.

According to Dallas Semiconductor the DS1202 has a software bug such that if the seconds register is initialized to 59, the minutes register will not increment until the seconds has counted through 60 seconds again.

This diagram reroutes sharing of serial clock by changing serial steering bit.

Note: To talk to DS1202 Serial Steering must be high. To talk to BT819 Serial Steering must be low.

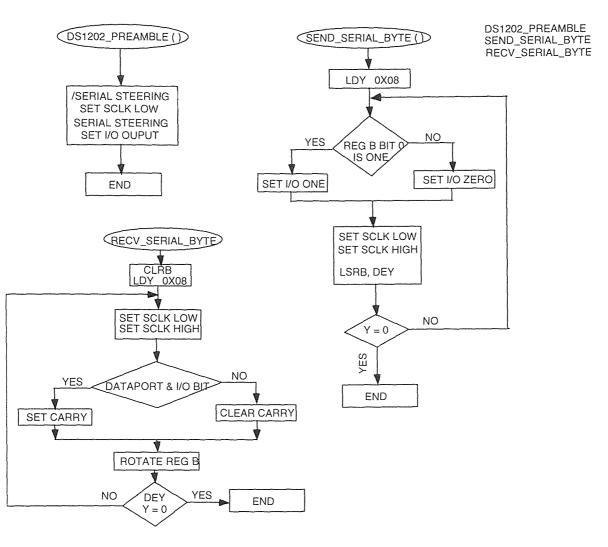

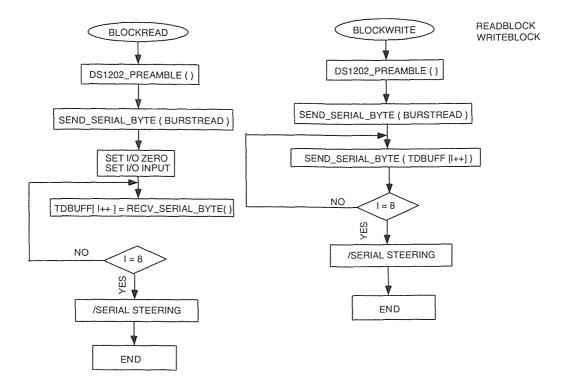

Figure 3.8 Serial Steering

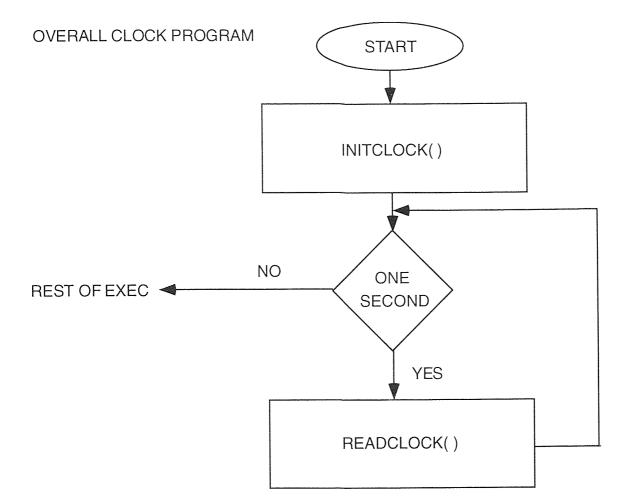

Figure 3.9 Clock Diagram

DS1202 INIT CODE WRITTEN IN ASSEMBLY

Figure 3.10 Initialization Clock Routine

Figure 3.11 Send/Receive Real-time Clock Bytes

Figure 3.12 Read/Write Real-time Clock Bytes

#### 3.10 Alphanumeric Output Ic

This device displays 12 lines of 24 characters, has a raster generator built into it, and is 75% compatible with the NEC 6145 which has been used in a number of projects at AD, but is now discontinued.. This part has an SPI serial connection, unlike the DS1202 and the BrookTree BT819 devices.

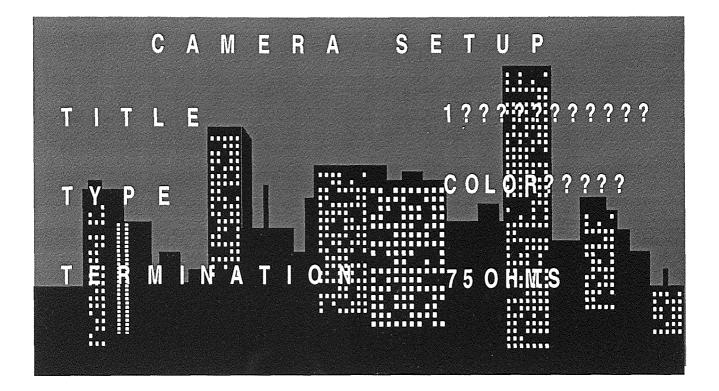

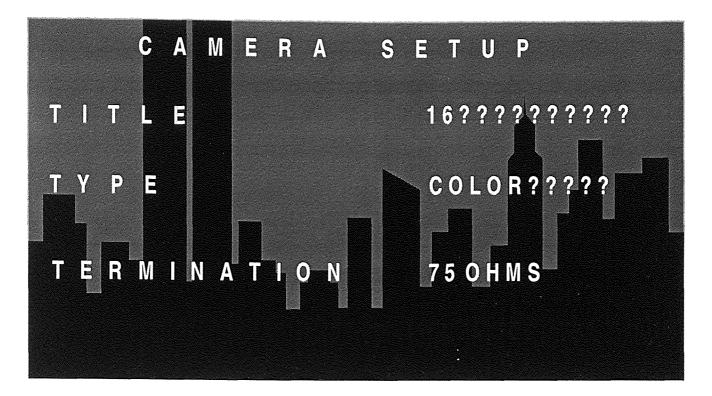

Title information for the cameras is 12 character positions. Camera number is not generated automatically. If a user wants a camera number in the title area, this value must be programmed within the 12 characters allocated.

The default programmed state of the title area is the camera number in the two leftmost positions of the 12 character area. Single digit numbers will be padded with 1 space so that the one's column of each camera number lines up as viewed when switching. This is not an issue with the 4 and 9 channel devices but generalizes the problem for 4,9 and 16 channel units.

#### 3.11 On Screen Menu System

The menu system currently has 9 unique menus. Several of the 9 unique menus are 'paged' (i.e. alarm log menu is 4 pages). The system requirements for menu data and navigation software are currently in the 8K region.

Software menu structures are designed according to the navigation through each menu using front panel keys. Each front led keys represent separate menu functions. All led keys are illuminated during menu mode. Software structures for navigation through each menu are called MENUTASK and they are array of structures, or in another words two dimensional array in which, each array consists of navigation and pointer fields in this manner:

```

typedef struct{

```

unsigned char txtcol; unsigned char row; int txtidx; char edit; unsigned char edcol; char fntn; unsigned arg0; unsigned arg1; unsigned arg2; }MENUTASK;

```

/* Static string column position */

/* Static string row position */

/* Index to static string */

/* Status of string (static, variable, etc.)*/

/* Variable string column position */

/* Numerical or character variable string */

/* RAM variable location */

/* RAM variable location */

/* RAM variable location */

```

Every menu consists of two types of strings, strings that are not effected by the user (static strings) which always get painted on the screen and no need to save their changed values in the eeprom. Other strings (variable strings) which their contents needed to be changed by the user to setup the system based on their applications. Two major routines paints contents of menus to screen one for static strings and other for variable strings.

Variable string routine makes decisions on individual menus and accepts two parameters (current menu number, pointer to beginning of menu structure). Each front panel key has one and only one function during menu mode as listed below:

1) Mode key ( next page menu)

2) Minus key ( decrement field or option)

3) Plus key (increment field or option)

4) Right key ( move to next field or option )

5) Down key (move to next row or row option)

6) Quad key ( quit menu )

7) 1 .. 4 keys used in camera setup menus to go from one camera setup to another.

Menutasks are modified by the above keys and results saved to  $E^2$  prom upon exit or

going to next menu. In this fashion only six bytes allocated in ram for displaying variable

strings in a menu. The below structure enables the programmer to maintain current menu

number and menutask location.

| typedef struct{       |                            |

|-----------------------|----------------------------|

| char curmenu;         | /* current menu number */  |

| MENUTASK *menucursor; | /* pointer to menutasks */ |

| }MENUCTRL;            |                            |

A typical menutasks for a typical menu is shown below:

MENUTASK const Switcher\_Dwell[] = {

| $\sim$ | THOR CONSCONTONOL_DAG |      | 1            |              |    |

|--------|-----------------------|------|--------------|--------------|----|

|        | {MSTRT,MSTRT,MSTRT,   | 0,   | 0, 0,        | 0,0,0},      |    |

|        | { 4, 1, 15,           | 0,   | 0, 0,        | 0,0,0},      |    |

|        | {13, 1, 28,           | 0,   | 0, 0,        | $0, 0, 0\},$ |    |

|        | { 1, 4, 15,           | 0,   | 0, 0,        | 0,0,0},      |    |

|        | {10, 4, 16,           | 2, 1 | 7, R_MLIST   | , 0, 1, 99}, |    |

|        | {20, 4, 17,           | 0,   | 0, 0,        | $0, 0, 0\},$ |    |

|        | { 1, 6, 18,           | 2, 1 | 17, R_SLIST, | 1, 2, 3},    |    |

|        | {MEND,MEND,MEND,      | 0,   | 0, 0,        | 0,0,0}       | }; |

|        |                       |      |              |              |    |

# 3.11.1 Order of Menu Appearance

| if password enabled | Intro menu<br>password menu                                               |

|---------------------|---------------------------------------------------------------------------|

| if password to      | Drrect continue, otherwise quit                                           |

| else                | Intro menu                                                                |

| Ļ                   | 2 seconds time-out                                                        |

|                     |                                                                           |

| Î                   | Vcr Setup                                                                 |

|                     | Switcher option                                                           |

|                     | Alarm inputs                                                              |

|                     | Alarm options                                                             |

|                     | if next page has data display<br>NEXT PAGE, if not display<br>DELETE LIST |

|                     | 1   2   3   4   Alarm log pages     Camera setup 1                        |

|                     |                                                                           |

|                     | Camera setup 16                                                           |

|                     | Time & Date                                                               |

|                     | Security Setup                                                            |

|         |        |          | A        | M      | E        | D      |        | С      |          | N        |          | D | Y | N      | Λ         | M       |          | С        | S        |          |          |          |          |

|---------|--------|----------|----------|--------|----------|--------|--------|--------|----------|----------|----------|---|---|--------|-----------|---------|----------|----------|----------|----------|----------|----------|----------|

|         |        |          | <u> </u> | C      | 0        | R<br>P | Y      | R      | A<br>I   | G        | Η        |   | Y | 1      | A<br>9    | 9       | 5        |          | 3        |          |          |          |          |

|         | A      | D        | 1        | 5      | 8        | 2      |        | N      | Т        | S        | С        |   | V | E      | R         |         | U        | F        | Ρ        | Ρ        | R        |          |          |

|         |        |          |          |        |          |        |        |        |          |          |          |   |   |        |           |         |          |          |          |          |          |          |          |

|         | Ρ      | L        | E        | A      | S        | E      |        | E      | Ν        | Т        | Ε        | R |   | Ρ      | А         | S       | S        | W        | 0        | R        | D        |          |          |

|         |        |          |          |        |          |        |        |        |          | Х        | Х        | Х | Х |        |           |         |          |          |          |          |          |          |          |

| ļ       |        |          |          |        |          |        |        |        |          |          |          |   |   |        |           |         |          |          |          |          |          |          |          |

|         |        |          |          |        |          |        |        |        |          |          |          |   |   |        |           |         |          |          |          |          |          |          |          |

|         |        | ]        |          |        |          |        |        |        |          | <u> </u> | L        |   |   |        | <u> </u>  |         |          |          | <u> </u> |          | <u> </u> |          |          |

| []      |        |          |          | V      | С        | D      |        | R      | E        | С        | 0        | R | D |        | S         | E       | Τ        | U        | Ρ        |          |          |          | <u> </u> |

|         |        |          |          | V      |          | R      |        |        |          |          |          |   |   |        |           | <b></b> |          | 0        | <br>     |          |          |          |          |

| C       | A      | M        | Ε        | R      | A        | S      |        |        |          |          |          |   |   |        |           |         |          |          |          |          |          |          |          |

|         |        |          |          | 1      |          |        |        |        | 2        |          |          |   |   | 3      |           |         |          |          | 4        |          |          |          |          |

|         |        |          |          | 5      |          |        |        |        | 6        |          |          |   |   | 7      |           |         |          |          | 8        |          |          |          |          |

|         |        |          |          | 9      |          |        |        | 1      | 0        |          |          |   | 1 | 1      |           |         |          | 1        | 2        |          |          |          |          |

| <b></b> |        |          | 1        | 3      |          |        |        | 1      | 4        | ļ        | ļ        |   | 1 | 5      |           |         |          | 1        | 6        |          |          |          | ļ        |

|         |        | 0        |          |        |          |        |        |        |          |          |          |   |   |        |           |         | R A      |          |          | <u> </u> |          |          |          |

|         | C      | R        |          |        | Y        | P      | E      |        |          |          | <u> </u> |   |   | F<br>2 | R<br>4    | A       | IVI<br>h |          |          | ├        |          | <u> </u> | <u> </u> |

| V<br>A  | C<br>L | R<br>A   | R        | S<br>M | P        | E<br>S | E<br>P | D<br>E | E        | D        | ┣        |   |   | 2      | 4         |         | h        | r<br>r   | <u> </u> |          |          |          | <br>     |

|         |        | <u> </u> |          |        | <b> </b> |        |        |        | <b>L</b> |          |          |   |   |        | <b>-r</b> |         |          | <u> </u> |          |          |          |          | <u> </u> |

# 3.11.2 Appearance of Each On Screen Menu Based On Default Values

|       |   |   | S | W | response |   | С | Η | E | R |   | 0 | Ρ | T |   | 0 | Ν     | S      |        |   |   | · · · · · · · · · · · · · · · · · · · |

|-------|---|---|---|---|----------|---|---|---|---|---|---|---|---|---|---|---|-------|--------|--------|---|---|---------------------------------------|

| <br>S | W |   | T | С | H        | E | R |   | D | W | E |   |   |   |   |   | 2     |        | S      | E | С |                                       |

|       | N | С | L | U | D        | E |   | M | U | L | Т |   |   |   |   |   | N     | 0      |        |   |   |                                       |

|       | V | E |   | 0 | R        |   | Ρ |   | A | Y |   | M | 0 | D | E | S | Y     | E<br>O | S<br>N | L | Y |                                       |

| <br>  |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   | · · · |        |        |   |   |                                       |

|       |   |   |   |   |          |   |   |   |   |   |   |   |   |   |   |   |       |        |        |   |   |                                       |

|   |   |   |   | А | L | Α | R | Μ |   |          | Ν | Ρ | U | Т | S |   |  |  |  |

|---|---|---|---|---|---|---|---|---|---|----------|---|---|---|---|---|---|--|--|--|

|   |   |   |   |   |   |   |   |   |   |          |   |   |   |   |   |   |  |  |  |

|   | 1 | Ν | / | Ο |   |   |   |   |   |          |   | 2 |   | Ν | / | 0 |  |  |  |

|   | 3 | Ν | / | 0 |   |   |   |   |   | ~        |   | 4 |   | Ν | / | 0 |  |  |  |

|   | 5 | Ν | 1 | 0 |   |   |   |   |   |          |   | 6 |   | Ν | / | 0 |  |  |  |

|   | 7 | Ν | / | 0 |   |   |   |   |   |          |   | 8 |   | Ν | / | 0 |  |  |  |

|   | 9 | N | / | 0 |   |   |   |   |   |          | 1 | 0 |   | Ν | / | 0 |  |  |  |

| 1 | 1 | Ν | / | 0 |   |   |   |   |   |          | 1 | 2 |   | Ν | / | 0 |  |  |  |

| 1 | 3 | Ν | 1 | 0 |   |   |   |   |   | <u> </u> | 1 | 4 |   | Ν | 1 | 0 |  |  |  |

| 1 | 5 | Ν | 1 | 0 |   |   |   |   |   |          | 1 | 6 |   | Ν | / | 0 |  |  |  |

|   |   |   |   |   |   |   |   |   |   |          |   |   |   |   |   |   |  |  |  |

|   |   |   |   |   |   |   | N | 0 | R | M        |   | 0 | Ρ | E | Ν |   |  |  |  |

|       |   |   |   |   | A | L | A | R | Μ |   | 0 | Ρ | Т | I | 0 | Ν | S |   |   |   |   |   |   |

|-------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ~~~~~ |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| C     | L | Ε | А | R | A | Ν | С | Ε |   |   | D | Е | L | Α | Y |   |   |   |   |   |   |   |   |

|       | Н | Ο | L | D | S |   | A | L | Α | R | M | S |   | 2 | 0 |   | S | Ε | С | 0 | Ν | D | S |

|       |   | А | F | Т | E | R |   | Т | Η | Ε |   |   | Ν | Ρ | U | Т |   | С | L | E | А | R | S |

|       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| D     | 1 | S | Ρ | L | A | Y |   |   | S | Ε | Q | U | Ε | Ν | С | Ε |   |   |   |   |   |   |   |

|       |   |   | Μ | 0 | Ν | I | Т | 0 | R |   | S | Ε | Q | U | Ε | Ν | С | E | S |   |   |   |   |

|       |   |   |   | А | L | A | R | Μ | Ε | D |   | С | Α | M | E | R | Α | S |   |   |   |   |   |

|       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| Α     | L | A | R | Μ |   | A | С | Т | 1 | 0 | N |   |   | Ρ | R | 1 | 0 | R | 1 | T | Y |   |   |

|       |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   | Α | L | Α | R | Μ |        | L | 0 | G |   | Ρ | Α | G | E |   | 1 |   |   |   |   |

|---|---|---|---|---|---|---|---|---|--------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |   |        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| С | А | Μ | Ε | R | Α |   |   |   |        |   |   |   | Α | L | Α | R | Μ |   |   |   |   |   |   |

| N | U | Μ | В | Ε | R |   |   |   |        |   | Τ | 1 | Μ | Ε | 1 | D | Α | Т | Ε |   |   |   |   |

|   |   | ? | ? |   |   |   | ? | ? | •      | ? | ? | • | ? | ? |   | ? | ? | / | ? | ? | / | ? | ? |

|   |   | ? | ? |   |   |   | ? | ? | •      | ? | ? |   | ? | ? |   | ? | ? | 1 | ? | ? | / | ? | ? |

|   |   | ? | ? |   |   |   | ? | ? | •      | ? | ? |   | ? | ? |   | ? | ? | / | ? | ? | / | ? | ? |

|   |   | ? | ? |   |   |   | ? | ? | u<br>t | ? | ? | • | ? | ? |   | ? | ? | / | ? | ? | / | ? | ? |

|   |   | ? | ? |   |   |   | ? | ? | 5<br>8 | ? | ? |   | ? | ? |   | ? | ? | 1 | ? | ? | / | ? | ? |

|   |   |   |   |   |   |   |   |   |        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   | D |   | Ν | E | Х | T |   | Ρ      | Α | G | E |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |        |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   | A | L | А | R | M |   | L | 0 | G |   | Ρ | A | G | Ε |   | 4 |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| С | Α | Μ | Ε | R | А |   |   |   |   |   |   |   | А | L | Α | R | Μ |   |   |   |   |   |   |

| Ν | U | Μ | В | Ε | R |   |   |   |   |   | Т | I | Μ | Ε | / | D | A | Т | Ε |   |   |   |   |

|   |   | ? | ? |   |   |   | ? | ? | • | ? | ? | • | ? | ? |   | ? | ? | 1 | ? | ? | / | ? | ? |

|   |   | ? | ? |   |   |   | ? | ? | • | ? | ? | : | ? | ? |   | ? | ? | 1 | ? | ? | / | ? | ? |

|   |   | ? | ? |   |   |   | ? | ? | : | ? | ? | : | ? | ? |   | ? | ? | 1 | ? | ? | / | ? | ? |

|   |   | ? | ? |   |   |   | ? | ? | • | ? | ? | : | ? | ? |   | ? | ? | 1 | ? | ? | / | ? | ? |

|   |   | ? | ? |   |   |   | ? | ? | • | ? | ? |   | ? | ? |   | ? | ? | 1 | ? | ? | / | ? | ? |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   | 4 |   | D | E | L | E | Т | E |   | L | Ι | S | Т |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

|   |   |   |   |   |   |   | Т | 1 | Μ | Ε | / | D | A | Т | Ε |   |   |   |   |   |  |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

|   |   |   |   | Т | l | Μ | E |   |   |   | ? | ? | • | ? | ? | • | ? | ? |   |   |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

|   |   |   |   | D | A | T | Ε |   |   |   | ? | ? | / | ? | ? | / | ? | ? |   |   |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

| Τ | I | Μ | Ε |   | & |   | D | A | Т | Ε |   | D | 1 | S | Ρ | L | A | Y | 0 | Ν |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

|   |   |   |   |   | S | E | С | U | R |   | Т | Υ |   | S | E | T | U | Ρ |   |   |   |   |  |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

| F | R | 0 | Ν | Т | _ | Ρ | А | Ν | Ε | L |   |   |   |   | E | Ν | А | В | L | Ε | D | ? |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   | _ |   |   |   |   |   |   |   |   |   |  |

| Ρ | A | S | S | W | 0 | R | D |   |   |   |   |   |   |   | D |   | S | Α | В | L | Ε | D |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

| N | E | W |   | Ρ | А | S | S | W | 0 | R | D |   |   |   | Ν | 0 |   |   |   |   |   |   |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   | _ |   |   |   |   |   |   |   |   |   |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

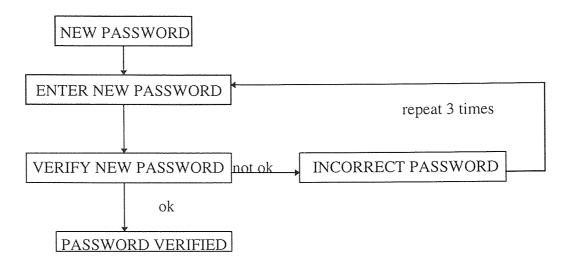

# New password set up. If at above menu new password become YES then

|   |   |   |   |   | S | Ε | С | U | R | Ĭ | Т | Y |   | S | Ε | Т | U | Ρ |   |   |   |   |  |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

| F | R | 0 | Ν | Т |   | Ρ | A | Ν | Ε | L |   |   |   |   | E | Ν | A | В | L | Ε | D | ? |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

| Ρ | A | S | S | W | 0 | R | D |   |   |   |   |   |   |   | D |   | S | А | В | L | Ε | D |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

| Ν | E | W |   | Ρ | А | S | S | W | 0 | R | D |   |   |   | Y | E | S |   |   |   |   |   |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

|   |   |   | Ε | Ν | T | E | R |   | Ν | E | W |   | P | Α | S | S | W | 0 | R | D |   |   |  |

|   |   |   |   |   |   |   |   |   |   | - |   |   |   |   |   |   |   |   |   |   |   |   |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

|   |   |   |   |   | S | E | С | U | R | I | Т | Y |   | S | Ε | Т | U | Ρ |   |   |   |   |  |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

| F | R | 0 | Ν | Т |   | Ρ | A | Ν | Ε | L |   |   |   |   | E | Ν | Α | В | L | Ε | D | ? |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

| P | A | S | S | W | 0 | R | D |   |   |   |   |   |   |   | D | l | S | A | В | L | Ε | D |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

| N | E | W |   | Ρ | Α | S | S | W | 0 | R | D |   |   |   | Y | Ε | S |   |   |   |   |   |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

|   |   | V | E | R |   | F | Y |   | Ν | Ε | W |   | Ρ | А | S | S | W | 0 | R | D |   |   |  |

|   |   |   |   |   |   |   |   |   |   | Х | Х | Х | Х |   |   |   |   |   |   |   |   |   |  |

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |  |

If verification is being correct then we get a message saying PASSWORD VERIFIED then 2 seconds delay and then NEW PASSWORD becomes NO.

If verification is being not correct then we get a message saying INCORRECT PASSWORD then 2 seconds delay and then display ENTER NEW PASSWORD again. If verification failed for the second time third time is given to the user, but after third time if verification still not correct then message PASSWORD NOT CHANGED will be displayed and then NEW PASSWORD becomes NO.

## VIDEO CAPTURE PROCESSOR

#### 4.1 Brooktree Bt819

This part is a composite NTSC/PAL and S-video decoder, which essentially provides color video digitization services to other parts of this machine. The part should be considered as a co-processor which we have to query on a periodic basis. The part uses an Inter-Integrated Circuit bus ( $I^2C$ ) to receive its initial operating parameters and to poll its status.

- Brooktree's VideoStream products (Bt819, Bt851, Bt817) are a family of singlechip, pin and register compatible solutions for processing of analog NTSC/PAL video into digital 4:2:2 YCrCb video. They provide a comprehensive choice of capabilities to enable the feature set and cost to be tailored to different system hardware configurations. All solutions are housed in a 100 QFP package.

- The feature set of the Bt819 supports a video/graphics system partitioning which optimizes the total cost of a system configured both with and without video capture capabilities. This enables system vendors to easily offer products with various levels of video support using single base-system design.

As graphics chip vendors move from graphics-only to video/graphics coprocessors and eventually to single chip video/graphics processor implementations, the ability to efficiently use silicon and package pins to support both graphics acceleration, video playback acceleration and video capture becomes critical. This problem becomes more acute as the race towards

62

higher performance graphics requires more and more package pins to be consumed for wide 64-bit memory interfaces and glueless local bus interfaces. The Bt819 minimizes the cost of the video capture function integration in a number of ways. Recognizing that YCrCb to RGB color space conversion is becoming a required feature of multimedia controllers for acceleration of digital video playback, the Bt819 avoids redundant functionality and allows the downstream controller to perform this task. Secondly, the Bt819 integrates the FIFO which would otherwise be dedicated to feeding a live video stream to the direct memory access engine (DMA) in video controller. Finally, the Bt819 can minimize the number of interface pins required by a downstream multimedia controller in order to keep package costs to a minimum.

Controller systems that are designed to take advantage of these features enable video capture capability to be added to the base system in a modular fashion using only single Integrated Circuit(IC).