## **New Jersey Institute of Technology** Digital Commons @ NJIT

Theses Theses and Dissertations

Spring 1996

# The study of SiGe-channel heterojunction MOS device

Yunchen Qiu New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/theses

Part of the Electrical and Electronics Commons

### Recommended Citation

Qiu, Yunchen, "The study of SiGe-channel heterojunction MOS device" (1996). Theses. 1070. https://digitalcommons.njit.edu/theses/1070

This Thesis is brought to you for free and open access by the Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Theses by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

### **ABSTRACT**

### THE STUDY OF SIGE-CHANNEL HETEROJUNCTION MOS DEVICE

### by Yunchen Qiu

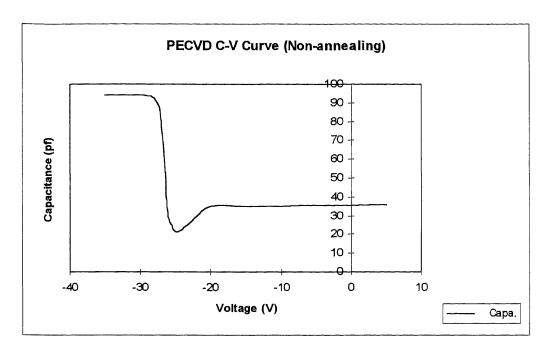

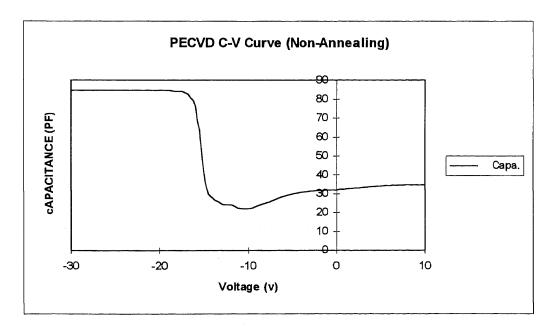

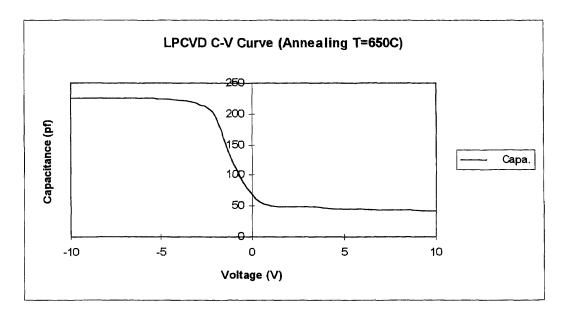

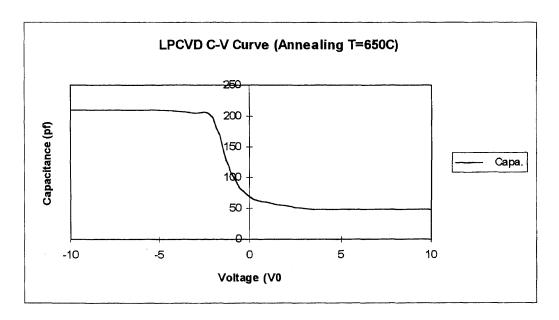

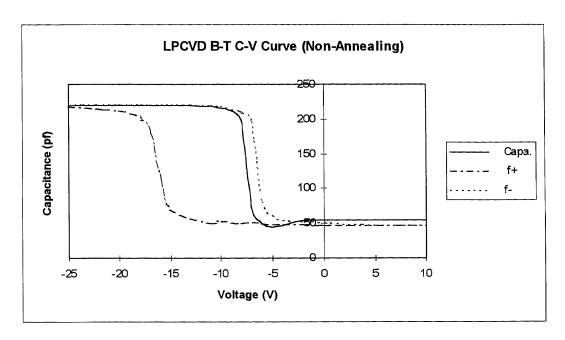

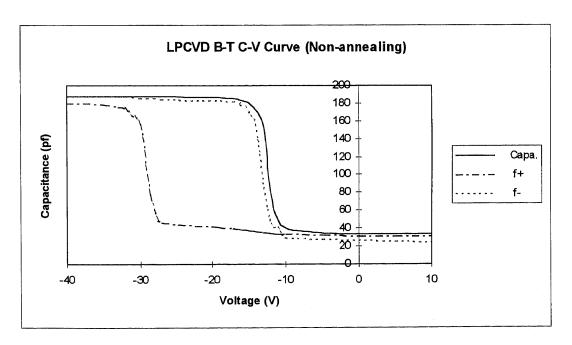

The advances in the growth of pseudomorphic silicon-germanium epitaxial layer combined with the strong need for high-speed CMOS VLSI circuit have led to increased interest in silicon-based heterojunction MOSFET's transistors. The high-performance heterostructure SiGe MOSFET exhibits higher channel mobility than its bulk Si counterpart. The most critical and challenging process for fabricating a SiGe MOSFET device is that for making a gate oxide with sufficient quality for useful conductivity modulation. PECVD methods was employed to deposit the gate oxide and C-V method was used to investigate the electrical characteristics of the film. For PECVD gate oxide, a film refractive index 1.47 were obtained using the deposition rate 125Å/min with a breakdown voltage 4-5 MV/cm, which deposition conditions are optimized as flow rate of DES(12sccm), N2O(172sccm), Helium(850sccm), temperature 300°C, power density  $0.09 W/cm^2$ . The total interface trap and fixed charge density  $N_t = 5.4 \times 10^{12} \text{ cm}^{-2}$  and flatband voltage  $V_{\text{fb}} = \text{-}16V$  for non-annealing MOS capacitor and the total effect of interface trap and fixed charge density  $6.4\times10^{11}$  cm<sup>-2</sup> and flatband voltage -4V were obtained at the oxide thickness dox = 1160Å using annealing at 650 °C for 30 minutes in the ambient of nitrogen. LPCVD silicon dioxide film was obtained at the deposition rate 14.5 Å/min and refractive index 1.46 while  $N_t = 3.9 \times 10^{12} \, \text{cm}^{-2}$  and  $V_{fb} = -8 \, \text{V}$  for nonannealing and  $N_t = 4.9 \times 10^{11}$  cm<sup>-2</sup> and  $V_{fb} = -2V$  for 650 °C annealed MOS capacitor.

### THE STUDY OF SiGe-CHANNEL HETEROJUNCTION MOS DEVICE

by Yunchen Qiu

A Thesis

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Master of Science in Applied Chemistry

Department of Electrical and Computer Engineering

May 1996

### APPROVAL PAGE

## THE STUDY OF SiGe-CHANNEL HETEROJUNCTION MOS DEVICE

# Yunchen Qiu

| Dr. Durgamadhab Misra, Thesis Advisor<br>Associate Professor of Electrical Engineering, NJIT | Date |

|----------------------------------------------------------------------------------------------|------|

| Dr. Kenneth Sohn, Committee Member Professor of Electrical Engineering, NJIT                 | Date |

| Dr. Roy Cornely, Committee Member Professor of Electrical Engineering, NJIT                  | Date |

### **BIOGRAPHICAL SKETCH**

Author: Yunchen Qiu

Degree: Master of Science

**Date:** May 1996

### Undergraduate and Graduate Education:

- Master of Science in Electrical and Computer Engineering, New Jersey Institute of Technology, Newark, New Jersey, 1996

- Master of Science in Electrical Engineering, Fudan University

Shanghai, P. R. China, 1987

- Bachelor of Science in Electrical Engineering, Fudan University Shanghai, P. R. China, 1984

Major: Electrical Engineering

### **ACKNOWLEDGMENT**

I would like to express my deepest appreciation to Dr. Durgamadhab Misra for his guidance, support and encouragement throughout this research. Special thanks are given to Dr. Kenneth Sohn and Dr. Roy Cornely for participating my thesis committee

Special thanks to Dr. Swain and other members in our Lab. for their help and kindness.

Special thanks to Dr. Levy, Dr. Lan Chen. The thesis work would not be completed without their idea, their help and their guidance in the experiment.

Special thanks to J. Grieco, J. M. Koons and K. O'Brien for their help when I worked in NJIT cleanroom.

Special thanks to Mr. Xiaoyi Gu, Yanwei Zhang, Shifeng Zhao, Yongxia Zhang and other friend for their help and kindness.

Finally, I would like to show my sincere gratitude to my best friend Qingping Zheng and Chao Sun for their great support and help during my study period.

## TABLE OF CONTENTS

| Chapter I                                          | Page |

|----------------------------------------------------|------|

| I. INTRODUCTION                                    | 1    |

| 1.1 Overview.                                      | 1    |

| 1.2 Growth of Si/SiGe structure.                   | 2    |

| 1.3 Properties of Si-Ge Layers                     | 8    |

| 1.3.1 Thermal Relaxation.                          | 8    |

| 1.3.2 Oxidation of SiGe layers                     | 9    |

| 1.3.3 Ion-Implantation of SiGe Layer.              | 10   |

| 1.3.4 Etching Effects of SiGe Layer                | 10   |

| 1.4 Application of SiGe Film.                      | 11   |

| 1.5 Objectives of This Thesis                      | 12   |

| 2. EXPERIMENTAL I                                  | 14   |

| 2.1 Capacitor - Voltage Characteristics Technique. | 14   |

| 2.1.1 Measurement of Oxide Charge                  | 15   |

| 2.1.2 Measurement of Mobile and Oxide Fixed Charge | 15   |

| 2.1.3 Measurement of Interface Trap                | 17   |

| 2.1.4 C-V Measurement System                       | 20   |

| 2.2 NJIT Cleanroom.                                | 21   |

| 2.3 Plasma Enhanced Chemical Vapor Deposition      | 24   |

| 2.3.1 Plasma-Enhanced CVD(PECVD)                   | 24   |

| 2.3.2 PECVD of SiO <sub>2</sub>                    | 25   |

# TABLE OF CONTENTS

(Continued)

| Chapter                                     | Page |

|---------------------------------------------|------|

| 2.3.3 PECVD Apparatus.                      | 26   |

| 2.3.4 Helium-diluted PECVD.                 | 26   |

| 2.4 Low Pressure Chemical Vapor Deposition  | 28   |

| 2.4.1 Low Pressure CVD.                     | 28   |

| 2.4.2 LPCVD Apparatus.                      | 29   |

| 3. EXPERIMENTAL II                          | 31   |

| 3.1 The SiGe MOSFET.                        | 31   |

| 3.1.1 The Structure of SiGe MOSFET          | 31   |

| 3.1.2 SiGe-Channel MOSFET Design Parameters | 35   |

| 3.2 Fabrication of SiGe Channel MOSFET      | 43   |

| 3.2.1 Mask of Photolithograph               | 45   |

| 3.2.2 Process Flow Procedure and Chart      | 45   |

| 3.2.3 SiGe-Channel MOSFET Process Traveler  | 46   |

| 4. RESULTS AND DISCUSSIONS                  | 56   |

| 4.1 PECVD SiO <sub>2</sub>                  | 56   |

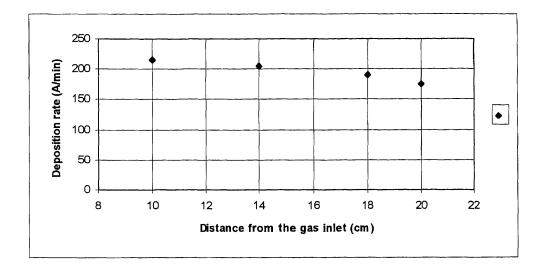

| 4.1.1 Deposition Rate With Distance         | 56   |

| 4.1.2 Temperature Effect                    | 56   |

| 4.1.3 Gas Composition Study                 | 61   |

| 4.1.4 Uniformity of The Film                | 64   |

# TABLE OF CONTENTS

## (Continued)

| Chapter                               |    |

|---------------------------------------|----|

| 4.1.5 The Deposition rate             | 65 |

| 4.1.6 Capacitor - Voltage Measurement | 66 |

| 4.2 LPCVD SiO <sub>2</sub>            | 78 |

| 5. CONCLUSIONS                        | 89 |

| REFERENCES                            | 91 |

## LIST OF TABLES

| Tak | ole de la companya d | Page |

|-----|----------------------------------------------------------------------------------------------------------------|------|

| 3.1 | Theoretical calculation of hole mobility of strained SiGe layer substrate                                      | 34   |

| 3.2 | Experimental low-field channel mobility of SiGe p-MOSFETs                                                      | 35   |

| 4.1 | Uniformity of a 5" wafer versus the flow rate of helium.                                                       | 64   |

| 4.2 | The effect of rf power and the flow rate of helium to deposition rate                                          | 66   |

| 4.3 | Experimental results of C - V measurementFor PECVD                                                             | 69   |

| 4.4 | Deposition rate and uniformity of LPCVD SiO <sub>2</sub>                                                       | 79   |

| 4.5 | Experimental results of C - V measurementFor LPCVD                                                             | 81   |

## LIST OF FIGURES

| Figu | ure                                                                               | Page |

|------|-----------------------------------------------------------------------------------|------|

| 1.1  | A two-dimensional representation of pseudomorphic growth                          | 4    |

| 1.2  | Bandgaps for unstrained bulk SiGe alloys and pseudomorphic SiGe alloys            | 5    |

| 1.3  | Bandgap of SiGe alloys and band alignment                                         | 7    |

| 1.4  | Critical thickness plotted as a function of Ge content.                           | 8    |

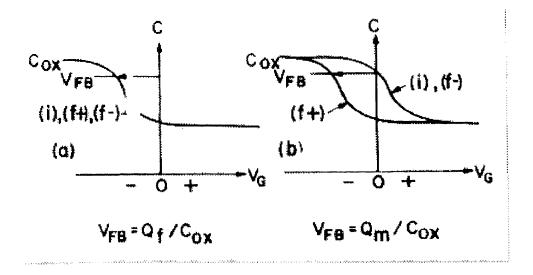

| 2. 1 | High frequency capacitance as a function of gate bias                             | 16   |

| 2. 2 | Diagram illustrating the result of the bias-temperature aging experiment          | 17   |

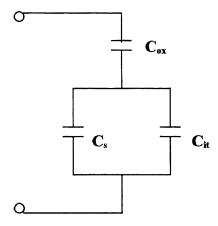

| 2. 3 | Low frequency equivalent circuit of the MOS capacitor                             | 18   |

| 2. 4 | High frequency equivalent circuit of the MOS capacitor                            | 19   |

| 2. 5 | The diagram of Quasi static measurement system.                                   | 22   |

| 2. 6 | The diagram of high frequency C - V measurement system.                           | 23   |

| 2.7  | Schematic diagram of PECVD set-up(a) and the susceptor(b)                         | 27   |

| 2.8  | Schematic of LPCVD reaction chamber.                                              | 30   |

| 3. 1 | Schematic diagram of the layer composition of a p-type GeSi MOSFET                | 32   |

| 3. 2 | 1-D Poisson simulation of the SiGe-channel charges with adjustment                | 37   |

| 3. 3 | 1-D Poisson simulation of the SiGe-channel charges without adjustment             | 39   |

| 3. 4 | N <sup>+</sup> -gate cross-over voltage in the SiGe channel for a flat Ge profile | 41   |

| 3. 5 | 1-D Poisson simulation of charges in a n <sup>+</sup> - gate SiGe p-MOSFET's      | 42   |

| 3. 6 | Ratio of holes flowing in the Si cap layer                                        | 43   |

| 3. 7 | The structure of SiGe channel n-MOSFET                                            | 44   |

| 3 8  | Cross-sectional SiGe MOSFET with field oxide                                      | 48   |

# LIST OF FIGURES (Continued)

| Figu  | re Page                                                                  | е |

|-------|--------------------------------------------------------------------------|---|

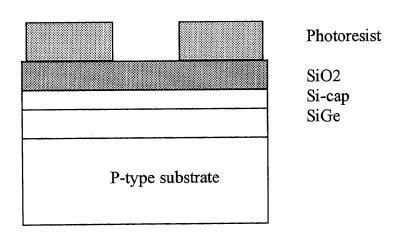

| 3. 9  | Cross-sectional SiGe MOSFET with photoresist                             | 8 |

| 3.10  | Cross-sectional SiGe MOSFET with etched field oxide                      | 9 |

| 3.11  | Cross-sectional SiGe MOSFET with etched field oxide                      | 0 |

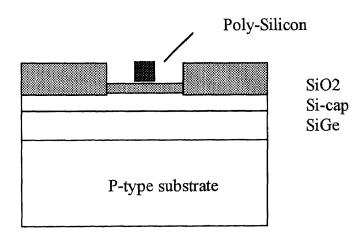

| 3.12  | Cross-sectional SiGe MOSFET with poly-silicon                            | 2 |

| 3.13  | The relation between Aluminum etching rate and temperature5              | 5 |

| 4. 1  | Deposition rate with the distance from the gas inlet                     | 7 |

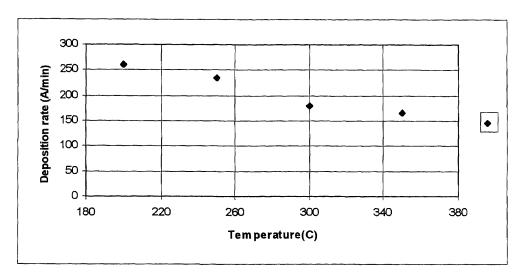

| 4. 2  | Deposition rate as a function of temperature5                            | 8 |

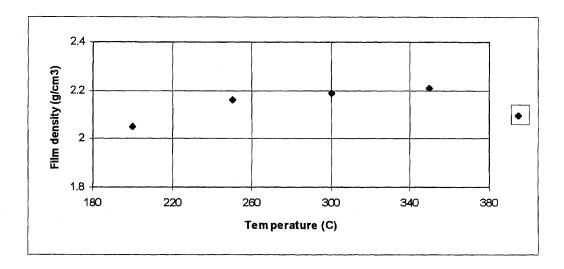

| 4. 3  | Film density as a function of temperature5                               | 8 |

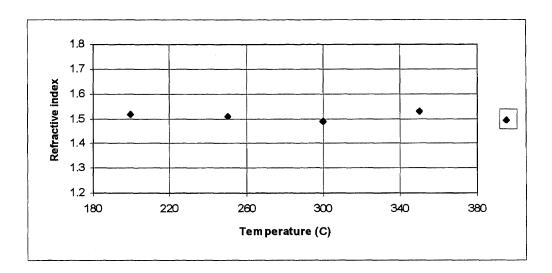

| 4. 4  | Refractive index as a function of temperature60                          | 0 |

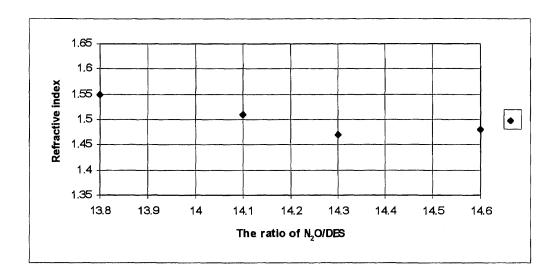

| 4. 5  | Refractive index versus the ratio of N <sub>2</sub> O/DES6               | 1 |

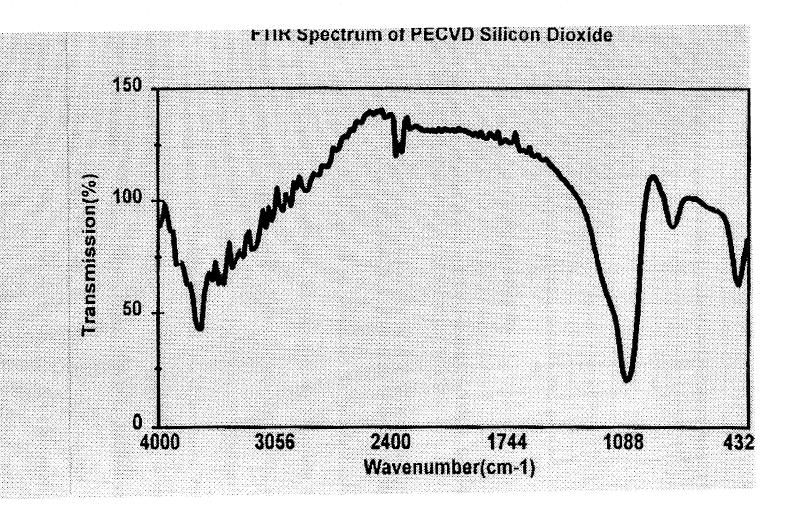

| 4. 6  | Typical FTIR Spectrum of PECVD silicon dioxide                           | 2 |

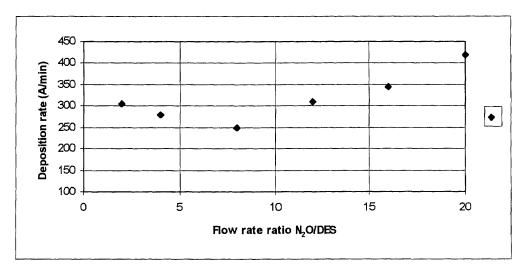

| 4. 7  | Deposition rate as a function of flow rate ratio of N <sub>2</sub> O/DES | 3 |

| 4. 8  | PECVD SiO2 C-V curve (Non-annealing)                                     | 2 |

| 4. 9  | PECVD SiO2 C-V curve (Non-annealing)72                                   | 2 |

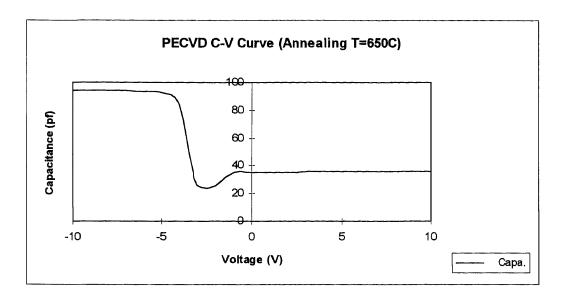

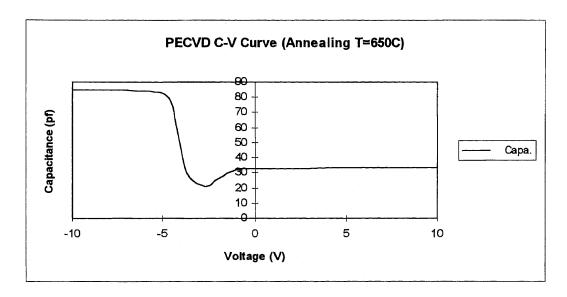

| 4. 10 | PECVD SiO2 C-V curve (T=650°C annealing )                                | 3 |

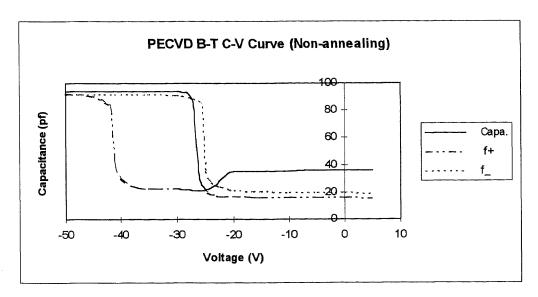

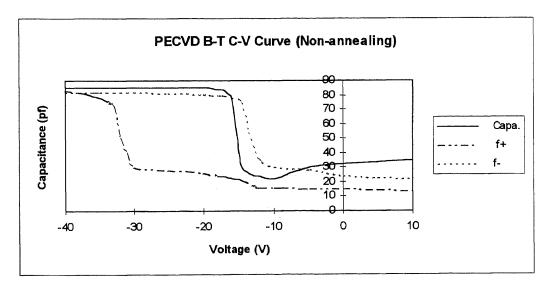

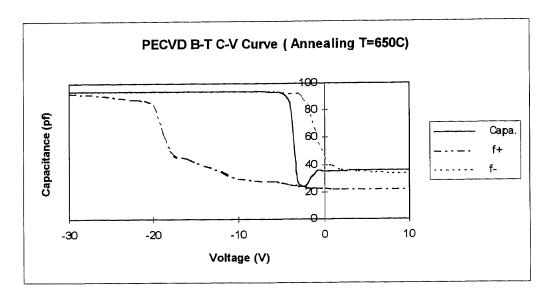

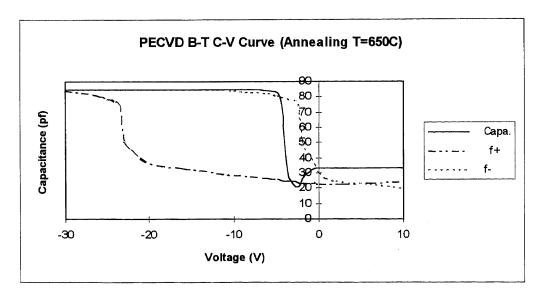

| 4. 12 | PECVD SiO2 B-T C-V curve (Non-annealing)                                 | 4 |

| 4. 13 | PECVD SiO2 B-T C-V curve (Non-annealing)                                 | 4 |

| 4. 14 | PECVD SiO2 B-T C-V curve (T=650°C annealing)                             | 5 |

| 4. 15 | 5 PECVD SiO2 B-T C-V curve (T=650°C annealing)                           | 5 |

# LIST OF FIGURES (Continued)

| Figure                                                   | Page   |

|----------------------------------------------------------|--------|

| 4. 11 PECVD SiO2 C-V curve (T=650°C annealing)           | 73     |

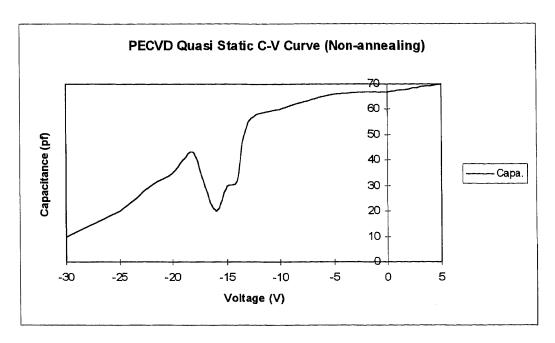

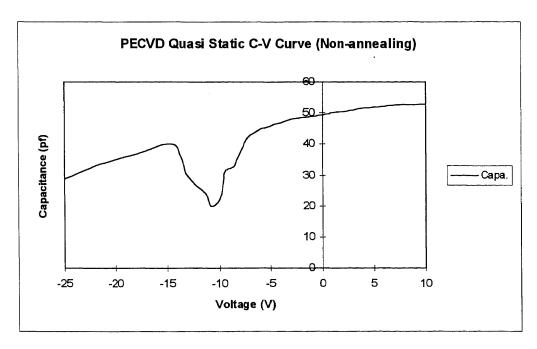

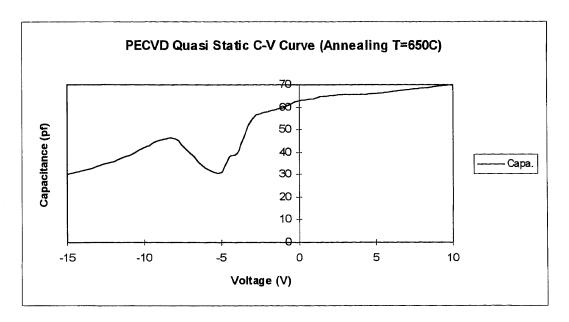

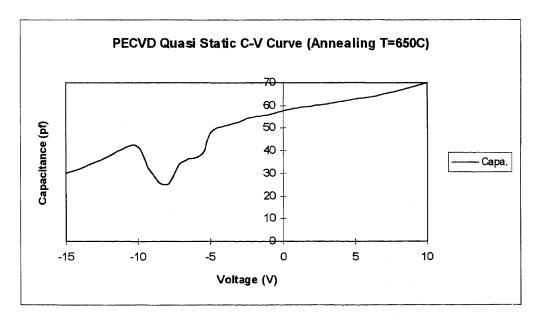

| 4. 16 PECVD SiO2 Quasi Static C-V curve (Non-annealing)  | 76     |

| 4. 17 PECVD SiO2 Quasi Static C-V curve (Non-annealing)  | 76     |

| 4. 18 PECVD SiO2 Quasi Static C-V curve (T=650°C anneali | ing)77 |

| 4. 19 PECVD SiO2 Quasi Static C-V curve (T=650°C anneali | ing)77 |

| 4. 20 LPCVD SiO2 C-V curve (Non-annealing)               | 83     |

| 4. 21 LPCVD SiO2 C-V curve (Non-annealing)               | 83     |

| 4. 22 LPCVD SiO2 C-V curve (T=650°C annealing )          | 84     |

| 4. 23 LPCVD SiO2 C-V curve (T=650°C annealing)           | 84     |

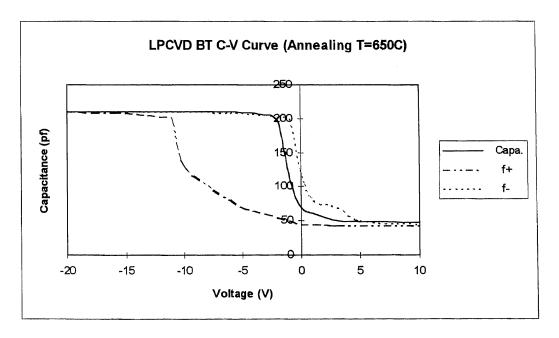

| 4. 24 LPCVD SiO2 B-T C-V curve (Non-annealing)           | 85     |

| 4. 25 LPCVD SiO2 B-T C-V curve (Non-annealing)           | 85     |

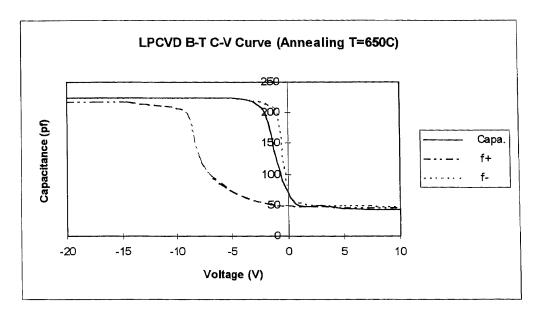

| 4. 26 LPCVD SiO2 B-T C-V curve (T=650°C annealing )      | 86     |

| 4. 27 LPCVD SiO2 B-T C-V curve (T=650°C annealing)       | 86     |

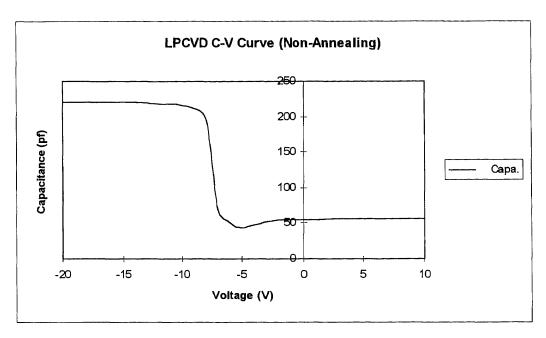

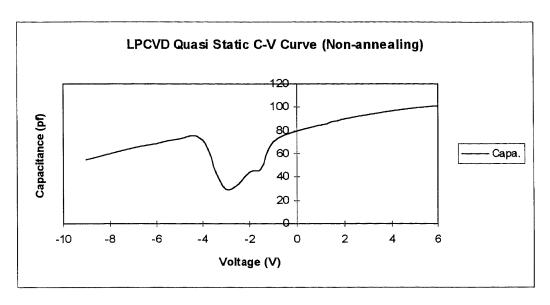

| 4. 28 LPCVD SiO2 Quasi Static C-V curve (Non-annealing)  | 87     |

| 4. 29 LPCVD SiO2 Quasi Static C-V curve (Non-annealing)  | 87     |

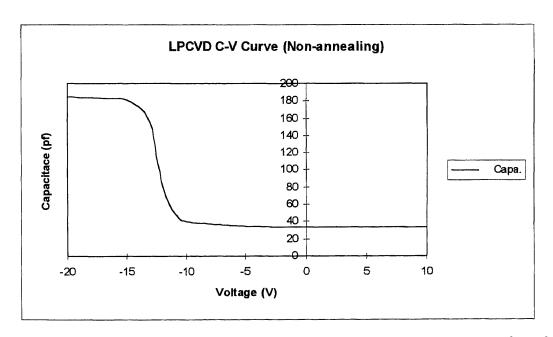

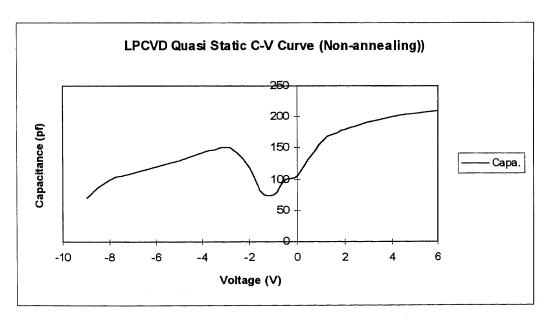

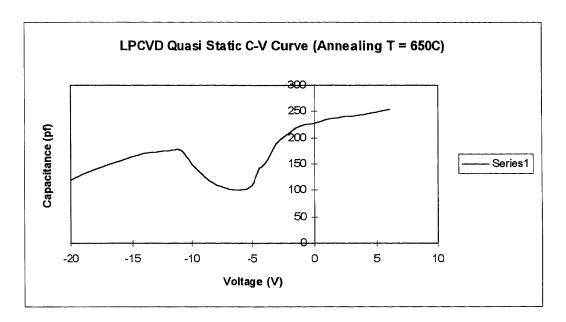

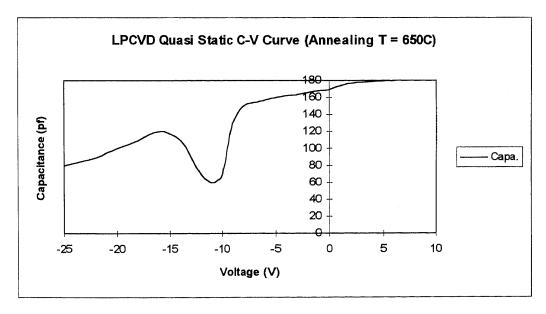

| 4. 30 LPCVD SiO2 Quasi Static C-V curve (T=650°C anneals | ing)88 |

| 4. 31 LPCVD SiO2 Quasi Static C-V curve (T=650°C anneals | ing)88 |

### **CHAPTER 1**

### INTRODUCTION

#### 1.1 Overview

Over the last ten years the significant progress in the application of SiGe layers is attributed to the rapid progress in techniques for the deposition of epitaxial layers of pseudomorphic SiGe epitaxial layers. This progress went through the following phases: material demonstrations, integration, feasibility, intrinsic profile optimization, structural integration and device parasites optimization[1]. Simple mesa structures were used to characterize the quality of the material set from 1983 - 1987[2][3]. This work led to the fabrication of the first SiGe devices in 1987[4]. The feasibility of integrated epitaxial Si and SiGe-base transistors was demonstrated from 1987 - 1989 and led to the generation of SiGe devices with ideal characteristics in 1989[5][6]. Then the sophisticated self-aligned devices[7][8][9] occurred in parallel through 1990 - 1992. The first significant commercial product of fully integrated SiGe bipolar transistors was made in 1994.

The SiGe material set also provides a path to heterojunction device physics and applications within the well established (CMOS dominated) silicon-based semiconductor industry.

The application of the film has became important in many electronics devices because of the ability of these techniques to tailor the band gap of the material. Due to the lattice mismatch between silicon and germanium, the films grown on silicon are strained up to a critical thickness. The narrow band gap of strained Si<sub>1-x</sub>Ge<sub>x</sub> has been used to fabricate

heterojunction bipolar transistors (HBT's)[10][11], modulation-doped field effect transistors (MODFET's)[12][13], long wavelength optoelectronics devices, tunneling and superlattice devices[14], and field-effect transistors (such as MOSFET's). The SiGe HBT's have been demonstrated to have significant performance leverage over advanced bipolar transistors because they offer an enhanced mobility due to selective doping of that material component having the higher energy and edge[15]. In field-effect transistors (FET's), the strained SiGe offers enhanced carrier mobilities which largely improves the device transconductance. This improvement especially demonstrates in CMOS applications in which the interior performance of silicon P-MOSFET's is caused by the field-effect-hole mobility which is typically two to three times lower than the field-effect-electron mobility. Generally Si PMOSFET's are designed with wider gates to minimize asymmetric operation, which obviously affects improving packing density. Hence a high mobility SiGe-channel P-MOSFET's will improve both the circuit speed and the lever of integration.

### 1.2 Growth of Si/SiGe Structure

Making high mobility devices requires the high-quality SiGe films which have good crystalline property. A good quality SiGe films should have the following characteristics: (1) Can be n or p doped up to several orders of magnitude in doping concentration, (2) have a low contamination levels of oxygen, carbon and metals giving a long minority-carrier lifetimes, (3) contain low defect densities, (4) exhibit abrupt interfaces with neighboring layer, and (5) can be deposited selectively.

The most mature growth methods employed today are (1) molecular beam epitaxy (MBE)[16], (2) ultrahigh-vacuum/chemical vapor deposition UHV/CVD[17]. Both methods can be carried out at temperature of about 550°C and can get good quality SiGe layers.

The ability to control the band structure in semiconductors has much potential for the design of high-performance devices. The application of this concept is the heterojunction formed by using materials of differing bandgaps. The narrow-gap Si-Ge alloys shows special promise and is the subject of this thesis. Silicon and germanium are completely miscible over the entire compositional range and give rise to alloys with a diamond crystal structure. The lattice constant of the alloy at room temperature can be determined by Vegard's rule:

$$a_{Si_{(1-x)}Ge_x} = a_{Si} + x(a_{Ge} - a_{Si})$$

(1.1)

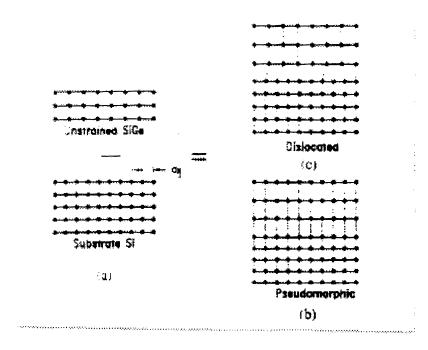

for low atomic concentration (x) of Ge. The lattice mismatch between Ge and Si is 4.17 percent at room temperature and increase only slightly with temperature. Figure 1.1 shows when such an alloy layer is deposited on a thick Si substrate, the mismatch can be in two different ways: 1) tetragonal distortion of the lattices, 2) generation of misfit dislocations at the interface. The distortion of the lattices results in cubic crystal and the films are under biaxial stress. The lattice constant in the plane of the substrate is determined by the substrate. Due to differences in lattices constant of Si, Ge and SiGe, the strain will be created at the surface. This strain is very fundamental property of the devices.

Figure 1.1 A two-dimensional representation of pseudomorphic growth. (a) An unstrained SiGe film is deposited on a silicon substrate. (b) Depending on growth parameter, the growth could be pseudomorphic, with the lattice constant difference accommodated by tetragonal strain or it could be dislocated.

Relaxed or unstrained growth occurs when misfit dislocation are permitted to nucleate. These dislocations may have pure edge components as shown in Figure 1(c) or they may thread through the layers.

It was investigated that the temperature ranges where the two- and three- dimensional growth modes persist using Rutherford Backscattering spectroscopy (RBS) and channeling and cross-sectional transmission microscopy. From this work it can be concluded that good quality layer by layer growth occurs only in the neighborhood of 550 °C for moderate Ge concentrations (up to 15%)[18].

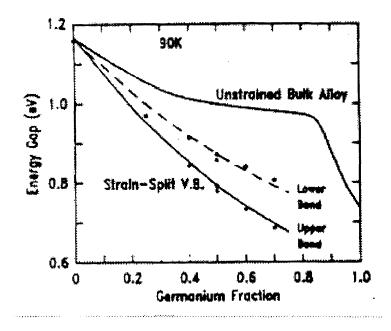

The energy gap value as a function of Ge content is shown in Figure 1.2. The top solid curve shows the bandgap for a bulk alloy layer due to Braunstein et al[19]. The growth of

Figure 1.2 Bandgaps for unstrained bulk SiGe alloys and pseudomorphic SiGe alloys. Both the strain split light and heavy hole bands are shown along with the experimental optical absorption data.

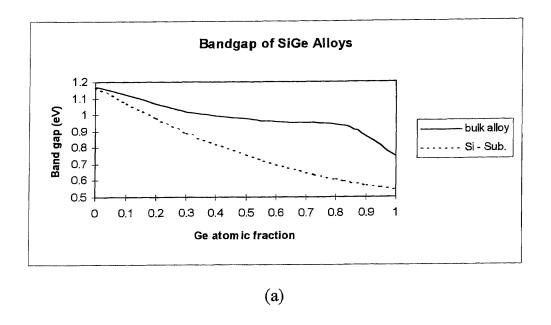

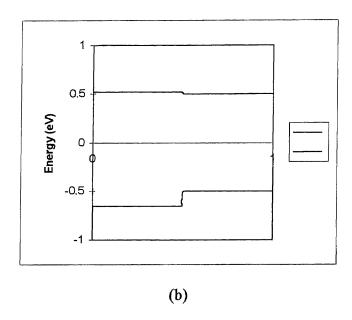

pseudomorphic Si<sub>X</sub>Ge<sub>1-X</sub> on Si substrates causes an even greater shrinkage of the indirect gap as shown in the lower two curves of Figure 1.2. The bandgap shrinkage is significantly increased by the presence of tetragonal strain in the layers. Most of the bandgap difference manifests itself principally in the valence band. Figure 1.3 shows the band alignment for strained Si<sub>X</sub>Ge<sub>1-X</sub> on Si. The gap energy of Si<sub>X</sub>Ge<sub>1-X</sub> layers as a function of x is also summarized in Figure 1.3 for different substrates, which is based on theoretical calculations[4]. The effect of strain on the band structure of pseudomorphic structures provides for a wide range of control of the energy gap depending on the substrate chosen. Clearly, a greater degree of gap adjustment is possible for growth on substrate of different lattice constant. The band offsets are also sensitive to the relative strains in the constituents of the heterostructure.

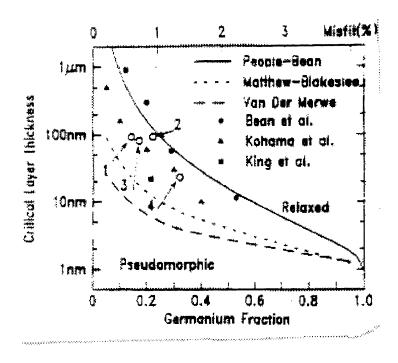

The thickness of the Si<sub>X</sub>Ge<sub>1-X</sub> layer is an important device design consideration. Critical thickness ("maximum thickness) for pseudomorphic growth of Si<sub>x</sub>Ge<sub>1-x</sub> alloys is an important property of the system. The critical thickness  $h_{\text{\tiny c}}$  of an epilayer is a parameter introduced to explain the experimental observation that for an epilayer having a different lattice parameter than its substrate. There is an epilayer thickness below which coherency is preserved, and above which it is not. So if the misfit between substrate Si and growing epilayer  $\mathrm{Si}_{x}\mathrm{Ge}_{1-x}$  is sufficiently small, the first atomic layers which are deposited will be strained such that the in-plane lattice constant of the film matches the substrate lattice parameter and hence a coherent interface will be formed. In this situation, defects could be avoided in growth of Si<sub>x</sub>Ge<sub>1-x</sub> films on Si. The calculation of Mathews et al[21][22] determined the maximum (critical) thickness h<sub>c</sub> of the strained epilayer as: 1) that thickness for which a grown in threading dislocation bows and elongates to form a segment of interfacial misfit dislocation line or 2) those conditions under which nucleation and subsequent growth of a dislocation half-loop would result in interfacial misfit dislocations. In particular, the above models give the following relation between critical thickness h<sub>c</sub> and misfit between film and substrate f where b is the magnitude of the Burger's vector and v is Poisson's ratio, f is the lattice mismatch. The critical thickness as defined either by theory or by experimental resolution does provides a frame of reference and this is summarized in Figure 1.4 for Si<sub>X</sub>Ge<sub>1-X</sub> grown on Si (100) as a function of x.

$$h_c = \left(\frac{1}{f}\right) \left\{ \frac{b}{4\pi (1+\nu)} \right\} \left[ \ln \left(\frac{h_c}{b}\right) + 1 \right]$$

(1.2)

Figure 1.3 (a) Band gap of SiGe alloys (b) The band alignment on Si Substrate

One important property of covalent alloy semiconductors such as Si-Ge is that the onset of relaxation is graduate. This is different from that of pseudomorphic III-V layers in which relaxation is sudden and almost complete once the critical thickness is exceeded.

Figure 1.4 Critical thickness plotted as a function of Ge content.

### 1.3 Properties of SiGe Layers

### 1.3.1 Thermal Relaxation

A key challenge in fabrication of a SiGe HBT is maintenance of a nearly defect free SiGe strained layer on Si. Although Significant bandgap reduction is observed for unstrained SiGe on Si, the presence of an extensive misfit dislocation network in the material would preclude the fabrication of high quality devices. In order to process this material, several restriction are placed due to the metastable nature of pseudomorphic SiGe layers. During thermal annealing, the layers may relax. The mode of relaxation is either via intermixing or via additional misfit dislocation formation. The rapid increase in dislocation density above 850°C is caused by dislocation climb aided by Ge diffusion. It was proposed that

dislocation as a method of strain relaxation is operative only when a large number of them are initially present. Due to enhancement, the structure relaxes with a diffusion coefficient that is higher than normal when few dislocation is present[18]. Hull et al indicated that at low Ge concentration, annealing above 650°C causes significant strain relaxation, but that with large Ge concentration, the relaxation is far more gradual.

Furthermore, all the dislocations in device have electrical effect, this threading helps enhanced impurity diffusion to create a junction leakage. By limiting the processing temperature we can reduced this effect. The tendency of near perfect layers to relax via enhanced diffusion rather than dislocation formation is advantageous from the junction leakage point of view. In fact, relatively high-temperature annealing is also possible without junction degradation for high-quality heterojunctions[18].

### 1.3.2 Oxidation of SiGe Layers

The ability to oxidize exposed regions of silicon to create an insulator is obviously critical to all forms of Si integration and must be preserved when introducing the SiGe material system. The mechanisms of oxide growth on Si are complicated. Recent studies have found that small amounts of Ge could lead to dramatic enhancement in oxidation rates and Ge segregated to the growth interface during oxidation. Since local oxidation is generally used to provide electrical isolation, the Ge "pile-up" effect is likely to lead to high levels of leakage and potential reliability concerns under electrical stress. An general approach to control both of these effects is the use of an all-Si capping layer above the SiGe layer which serves as a sacrificial layer for oxide growth and isolation purposes.

### 1.3.3 Ion-Implantation of Si-Ge Layers

Strained Si/Si<sub>x</sub>Ge<sub>1-x</sub>/Si(100) heterostructure can offer great promise for making high-quality device. In such structures, it is imperative that strain-relieving misfit dislocations and/or threading dislocations be absent from the active device regions. The last thing one should consider doing to an ideal grown strained-layer is introducing significant amounts of lattice damage through implantation. Clearly, implantation damage could provide an ideal source of defect nucleation sites which in turn could lead to deleterious formation of an extensive misfit dislocation network upon annealing. Harame, et al [1] investigated two processes which are likely to cause problems: 1) moderate energy, low dose implants Phosphorous 100 kev, 1x10<sup>13</sup> cm<sup>-2</sup>; 2) high dose, low energy implants Boron 5 kev, 1x10<sup>15</sup> cm<sup>-2</sup>. The results show that the use of both types of implant have been found no significant yield impact for SiGe layers which are clearly within the Matthews and Blakeslee stability criterion. SiGe layer which are mechanically stable are able to undergo implantation and anneal cycles with no additional defect generation or motion beyond that.

### 1.3.4 Etching Effects of SiGe Layers

So far little is known about the dry etching behavior of SiGe alloy and how it differs from that of silicon. Dry etching techniques such as reactive ion etching (RIE), plasma etching (PE) and ion beam etching (IBE) can cause damage in materials. If these damages and contamination effect is not controlled, it can influence material properties and device performance[23]. Dry etching effects can change the surface properties, generation lifetimes, doping activation and diffusion lengths in etched silicon.

The simplest picture of the etching of SiGe is independent removal of Si and Ge atoms by the etchant atoms from the SiGe surface at rates of the species which is more slowly volatilized. The presence of several percent Ge in a SiGe alloy significantly increase the rate of Si atom volatilization of the alloy[24].

The major damages which are considered in dry etching are residues layer formation; impurity contamination, hydrogen permeation and bonding damage. The residue layer is present depends on the etching chemistry. For example, during the CF<sub>4</sub> + O<sub>2</sub> plasma etching, the residue formation maybe neglected. Some groups have detected impurities, particularly metallic impurities such as Fe, Ni, Al, Cr, K, and Zn, on the surface and near-surface region. The bonding damage that results from dry etching exposure has its roots in three distinctly different causes. One is the ion bombardment inherent in at least all current anisotropic dry etching, another is UV radiation, and the third is hydrogen. The effects of dry etching ion bombardment damage are easily seen by C-V characteristics of metal/semiconductor contact made on etching surface.

### 1.4 Application of SiGe Film

The application of silicon/SiGe heterostructures in device has focused on the bipolar and field-effect transistors. In bipolar transistors, the presence of germanium exponentially alters the device characteristics. The SiGe HBT's have been demonstrated to have significant performance leverage over advanced bipolar transistors[25] because they offer an enhanced mobility due to selective doping of that material component having the higher energy band edge [26]. The SiGe HBT offers three key advantages over conventional ion-

implanted bipolar transistor: 1) a reduction in base transit time resulting in higher frequency performance, 2) an increase in collector current density and hence current gain allowing high current gain with low intrinsic base resistance, and 3) an increase in Early voltage at a given cutoff frequency. The first commercial SiGe integrated circuit is the achievement of the application of SiGe technology to the fabrication of a high performance 12-bit DAC.

In the application of Metal-Oxide-Semiconductor field-effect transistor (MOSFET'S), the advantage of using SiGe MOSFET is that it can maximize the device transconductance because the strained SiGe offers enhanced carrier mobilities.

Since the bandgap difference between strained SiGe and unstrained Si appears mostly in valence band, there is large improvement in P-channel MOSFET's hole mobility. This result brings great advantage in CMOS applications because the field-effect hole mobility is typically two to three times lower than the field-effect electron mobility. Usually Si P-MOSFET's are designed with wider gates to minimize asymmetric operation, which affects packing density. Hence a high mobility p-channel FET will improve both the circuit speed and the level of integration.

### 1.5 Objectives of Thesis

The objective of this thesis was to develop a processing technique for fabricating SiGechannel MOSFETs and to use these data as a guide for improving the processing approach. A further objective was to fabricate a SiGe-channel MOSFET and Si-channel MOSFET for comparing the electrical characteristics of the SiGe-channel MOSFET and Si-channel MOSFET, which provides a new heterostructure MOSFET for improving the performance of CMOS VLSI circuit. For fabricating a SiGe-channel MOSFET, a low temperature processing (<650°C), which is a silicon-based heterostructure processing, was investigated because the SiGe layer tends to relax at high temperature(above 650°C). The most important step in this process comparing with the regular Si MOSFET process is how to obtain a good quality gate oxide. Thermal oxidation which is used in Si process (temperature 950°C) is not appropriate to SiGe films. The application of two methods for obtaining insulating gate oxide was investigated: 1) Plasma Enhanced Chemical Vapor Deposition (PECVD) method and 2) Low Pressure Chemical Vapor Deposition (LPCVD) method. The C - V analysis method was employed to study and compare the electrical characteristics of the films deposited by these two methods.

To study the SiGe device, SiGe-channel and Si-channel MOSFETs with different geometry were fabricated with the low-temperature process in NJIT cleanroom.

### **CHAPTER 2**

### **EXPERIMENTAL I**

### 2.1 Capacitor - Voltage Characteristics Technique

The capacitor-voltage characteristics of MOS capacitors have been found to be extremely useful in the evaluation of electrical properties of insulator-semiconductor interfaces.

Uoinigescn shows that the Si/SiGe heterostructure MOS capacitor can become an excellent and thorough characterization vehicle for Si-based heterostructure technology.

There are two basic types of charge in the SiO<sub>2</sub> layer: (1) Interface trap charge; (2) Oxide charge. The feature that distinguishes interface trap charge from oxide charge is that interface trap charge varies with gate bias whereas oxide charge is independent of gate bias. There are three type of oxide charge Q<sub>0</sub>, that are technologically important. (1) Oxide fixed charge Q<sub>f</sub>, which is located at or very near the Si-SiO<sub>2</sub> interface. (2) Oxide trapped charge Q<sub>0t</sub>, which is located either at the metal-SiO<sub>2</sub> interface or at the Si-SiO<sub>2</sub> interface. In some cases, Q<sub>0t</sub> can be distributed within the oxide layer. (3) Mobile ionic charge Q<sub>m</sub>, most commonly is caused by the presence of ionized alkali metal atoms such as sodium or potassium. This type of charge is located either at the metal-SiO<sub>2</sub> interface or at the Si-SiO<sub>2</sub> interface, where it has drifted under an applied field. Drift can occur because such ions are mobile in SiO<sub>2</sub> at relatively low temperatures.

Immobile oxide charge can be distinguished from mobile charge by a bias-temperature aging experiment.

### 2.1.1 Measurement of Oxide Charge

Oxide charge is an important parameter in devices. For example, it can alter the threshold voltage of a MOSFET; alter the silicon surface potential and thereby change reverse surface leakage current in a p-n junction; alter the avalanche breakdown voltage of a p-n junction. The simplest and most widely used method for measuring oxide charge density is to infer this density from the voltage shift of a C-V curve.

The presence of an oxide charge, interface states charge and work function differences are taken into account the flat-band voltage, the amount of gate to substrate voltage which is required to produce zero band-bending at the silicon surface is given by:

$$V_{\rm fb} = \Phi_{\rm ms} - Q_{\rm o}/C_{\rm ox} \tag{2.7}$$

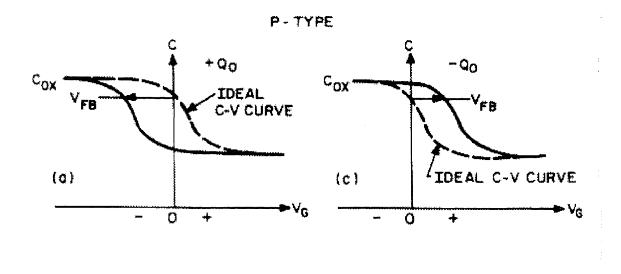

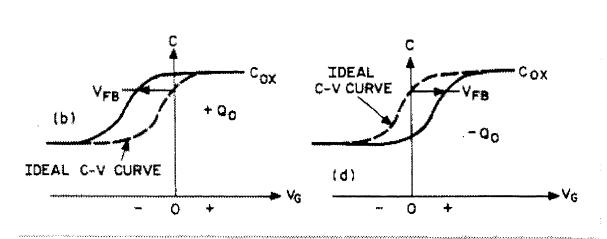

This equation shows that the entire C-V curve is shifted along the voltage axis with respect to the ideal C-V curve by the amount  $V_{fb}$  -  $\Phi_{ms}$ . Figure 2.1 illustrate the shift along the voltage axis of a high frequency C-V curve when positive or negative  $Q_o$  is present in the oxide.

### 2.1.2 Measurement of Mobile and Oxide Fixed Charge

Consider an experiment where the only oxide charge is oxide fixed charge. The initial high frequency C-V curve measurement is labeled (i) in Figure 2.2(a). After heating at 150°C for half an hour with a positive gate bias producing a field of a few million volts per centimeter across the oxide, and cooling back to room temperature, The curve labeled (f<sub>+</sub>)

in figure 2.2(a) is obtained. Repeating the bias-temperature aging with negative gate bias yields curve (f) in figure 2.2(a). So the oxide fixed charge centers are immobile and is given by:

$$V_{fb} = Q_o/C_{ox} \tag{2.8}$$

N - TYPE

Figure 2.1 High frequency capacitance as a function of gate bias showing the effect of oxide charge. The C - V curves marked "ideal" have no oxide charge. (a) Positive oxide charge, p-type; (b) positive oxide charge, n-type; (c) negative oxide charge, p-type; (d) negative oxide charge, n-type.

Figure 2.2 Diagram illustrating how oxide fixed charge, oxide trapped charge, and mobile ionic charge can be distinguished from a bias-temperature aging experiment. The Symbols (i) denotes the initial C - V curve;  $(f_+)$ , after positive bias-temperature aging, and  $(f_-)$ , after negative bias-temperature aging. (a) Oxide fixed charge; (b) mobile ionic charge.

Figure 2.2(b) shows the results of repeating this experiment on an oxide contaminated by mobile ions. Initially  $V_{fb}$  is low, and after positive bias aging it increases. With negative bias aging,  $V_{fb}$  return to its original value. The shift of flat-band voltage is resulted from the movement of mobile charges, which is given by

$$\Delta V_{fb} = Q_m/C_{ox} \tag{2.9}$$

### 2.1.3 Measurement of Interface Trap

The combined high-low frequency capacitance method is used to measure the interface traps. For lower frequencies, interface traps respond to ac gate voltage changes. Therefore

the low frequency equivalent circuit of the MOS capacitor contains an interface trap capacitance, which is not present if there are no interface traps. Figure 2.3 illustrates the equivalent circuit corresponding to equation (4):

$$C_{LF} = \frac{dQ_T}{dV_G} = (C_s + C_{it}) \frac{C_{ox}}{C_{ox} + C_s + C_{it}}$$

(2.10)

C<sub>LF</sub> is the capacitance at the low frequency.

Figure 2.3 Low frequency equivalent circuit of the MOS capacitor.

For high frequency, the interface traps do not follow the ac gate voltage in a high frequency C-V measurement. They contribute no capacitance to the high frequency C-V curve. At high frequency the total capacitance is given by equation (5) with  $C_{it}(\omega) = 0$  (because  $\omega$  is too large for any ac response of interface traps ). The capacitance at high frequency  $C_{HF}$  is given by

$$C_{HF} = \frac{C_s C_{ox}}{C_s + C_{ox}} \tag{2.11}$$

This capacitance corresponds to the equivalent circuit shown in figure 2.4.

Figure 2.4 High frequency equivalent circuit of the MOS capacitor.

The circuit does not contain interface traps explicitly. Therefore, regardless of interface trap level density, the high frequency capacitance of an MOS capacitor will be the same as that of an ideal one without interface traps provided that  $C_s$  is the same.

Castangne and Vapaille were the first to combine high and low frequency C-V curves to obtain a measured C<sub>s</sub>. The step eliminates the need for a theoretical computation of C<sub>s</sub> and for measurement of the doping profile of the device. From equation (4) and (5), C<sub>it</sub> is give by:

$$C_{it} = \left(\frac{1}{C_{IR}} - \frac{1}{C_{gx}}\right)^{-1} - \left(\frac{1}{C_{HR}} - \frac{1}{C_{gx}}\right)^{-1}$$

(2.12)

In this way  $C_{it}$  is obtained directly from the measured C-V curves without the uncertainty introduced by a theoretical  $C_s$  and without uncertainty as to whether  $C_s$  has been calculated for the correct band bending. If we let

$$\Delta C = C_{LF} - C_{HF} \tag{2.13}$$

Then

$$D_{it} = \frac{C_{it}}{q} = \frac{C_{ox}}{q} \left[ \left( \frac{1}{\Delta C / C_{ox} + C_{HF} / C_{ox}} - 1 \right)^{-1} - \left( \frac{1}{C_{HF} / C_{ox}} - 1 \right)^{-1} \right]$$

$$= \frac{\Delta C}{q} \left( 1 - \frac{C_{HF} + \Delta C}{C_{ox}} \right)^{-1} \left( 1 - \frac{C_{HF}}{C_{ox}} \right)^{-1}$$

(2.14)

Hence, the interface density D<sub>it</sub> can be calculated from equation (8).

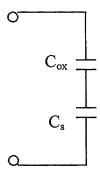

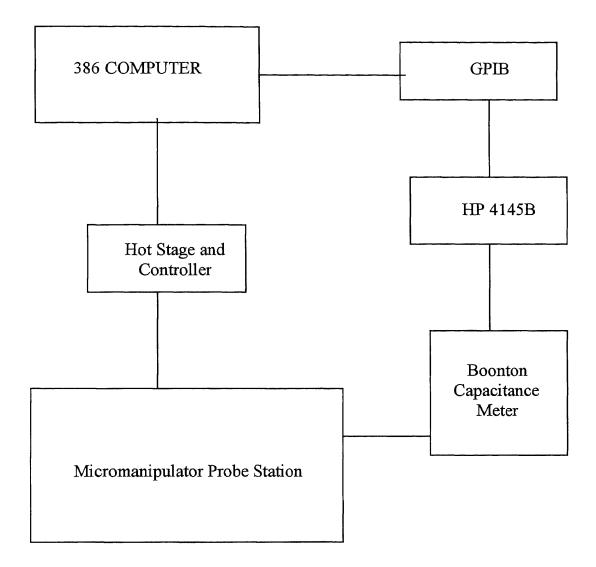

#### 2.1.4 C-V Measurement System

The C-V measurement system is designed to measure the low-frequency C-V, high-frequency C-V and bias-temperature C-V characteristics. This system uses personal computer to control HP4140B which is for quasi static parameter measurement and HP4145B which is used for measurement of high frequency C-V measurement. The components for the system are as follows:

- 1. Supercom 386 IBM/compatible PC

- 2. AT-G.P.I.B. interface card and software NI-488.2

- 3. HP4140B PA Meter / DC Voltage Source

- 4. HP4145B Semiconductor Parameter Analyzer

- 5. Boonton Capacitance Meter Model 72BD

- 6. Micromanipulator Hot Stage and Controller Model HSM

- 7. Micromanipulator Probe Station

- 8. Hewlett-Packard Colorpro Plotter

- 9. Software used: Microsoft Quick Basic Version 4.5 and National Instruments NI-DAQ DOS software version 4.4.

The diagram of Quasi static measurement system is shown in Figure 2.5, which system is designed to make C-V measurement. HP4140B is controlled by 4140 software from 386PC. It can supply desired voltage to DUT on the probe and measure the current or capacitance of the samples. 4140 is an interactive software and the measurement results are shown on the screen. The data are directly stored in a file.

The high frequency C-V measurement system is shown in figure 2.6. HP4145B which is controlled by PC386 software 4145 provides the needed voltage to DUT on the probe. The measurement range can be set through the interactive software. At the same time the HP4145B measures the voltages and currents of the samples and the datas are stored in a file.

#### 2.2 NJIT Cleanroom

Most of our process work was done in NJIT clean-room. NJIT clean-room is a 1200-sq-ft and class 10 fabrication line. It was equipped with all necessary tools for processing wafers up to 150mm in diameter. These equipment include:

Figure 2.5 The diagram of Quasi static measurement system

- 1) Wafer inspection microscope, Dektak profilometer

- 2) Nanometrics optical line width

- 3) Wet chemical station Ultratek mask/wafer scrub

- 4) Semitool spin/rinse dryers

- 5) Karl Suss exposure system

- 6) Nanometrics FTM

Figure 2.6 The diagram of high frequency C-V measurement system

- 7) Inspection microscope

- 8) MTI coat develop system

- 9) Drytek reactive ion etching system

- 10) Leitz MPV FTM

- 11) Varian sputtering system

- 12) BTU diffusion furnace

- 13) BTU LPCVD furnace

- 14) MDA toxic gas monitors

- 15) Tubewash station

- 16) MG Industries gas cabinets

### 2.3 Plasma Enhanced Chemical Vapor Deposition

## 2.3.1 Plasma-Enhanced CVD(PECVD)

Plasma deposition is a combination of a glow discharge process and low pressure chemical vapor deposition in which highly reactive chemical species are generated from gaseous reaction by a glow discharge and interact to form a thin solid film product on the substrate and electrode surface[29]. Since the plasma assists or enhances the CVD reaction, the process is denoted as Plasma-Enhanced CVD (PECVD).

Plasma-enhancement offers an alternative to thermal energy for initiating chemical reactions leading to film deposition. Use of plasma frequently allows deposition at a much lower temperature than could otherwise be achieved, and/or it permits the use of source gases that would ordinarily be considered unreactive. This is the major advantage of PECVD. Radicals, which are predominant species in plasma field, tend to have high sticking coefficients, and also appear to migrate easily along the surface after adsorption. These two factors can lead to excellent film conformality. Desirable film properties such as good adhesion, low pinhole density, good step coverage, adequate chemical properties can

also be obtained by PECVD superior to those of APCVD or LPCVD films. Moreover, the mechanical strength of plasma deposited films is excellent due to their intrinsic compressive stress and high film density[30][31]. However, the complexity of reactions associated with PECVD makes the synthesis of stoichiometric composition difficult. And, as a consequence of the low temperature for film formation, gases are trapped in the films, which frequently causes thermal instability due to outgasing. Though sensitive MOS devices may be damaged by the radiation associated with the plasma discharge, the damage can usually be eliminated by a thermal annealing at the deposition temperature[32]. The main factors which affect the PECVD processes and the thin film properties include plasma power density, frequency as well as the substrate temperature and partial pressure of reactant gases, etc.

#### 2.3.2 PECVD of SiO<sub>2</sub>

The oxidation of silicon in an oxygen plasma allowed the controlled growth of thin, high-quality films of SiO<sub>2</sub> at temperature down to room temperature in a clean vacuum environment. The rate of oxidation and electrical properties may vary greatly depending upon the oxidation conditions. Plasma ion density and sample temperature are the two important factors affecting growth.

In PECVD SiO<sub>2</sub>, siliane (SiH<sub>4</sub>) and nitrous oxide (N<sub>2</sub>O) are used. A typical reaction would be:

$$SiH_4 + N_2O ===> SiO_2 + 2H_2 + 2N_2$$

The process can be carried out between 200 - 400°C. The PECVD SiO<sub>2</sub> films are known to contain hydrogen as well as nitrogen, and to have a high etch rate, high refractive index, low stress and to be oxygen deficient. Conformal coated, low pinhole count and excellent adhesion films were obtained by this technique.

Optimized gas composition of  $N_2O$ / SiH<sub>4</sub> ratio 40/60 and rf power density 0.05W/cm<sup>2</sup> were employed to suppress gas phase reactions and enhance surface reactions. A typical deposition rate of 60 nm/min was readily obtained at 300°C. In our process, the PECVD is employed to deposit electronic quality SiO<sub>2</sub>.

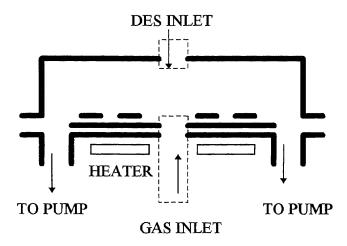

### 2.3.3 PECVD Apparatus

The equipment used for thin film deposition is the Applied Materials AMP 3300IIA PECVD system with an external DES flow control equipment. The scheme of the reactor is given in figure 2.7. The reaction chamber is an aluminum cylinder with aluminum plates on both the top and the bottom, as upper electrode and susceptor, respectively. It has a conventional "radial flow" design and utilizes a mechanical pump/roots blower arrangement for the pumping system. The experimental procedures for deposition are:

1) Wafer loading. 2) Setting deposition conditions. 3) Film deposition.4) Post-deposition procedure. 5) Reactor etching

#### 2.3.4 Helium-diluted PECVD

Thin films of high-quality silicon dioxide is deposited at low temperatures by Heliumdiluted PECVD method, in which the deposition rate much lower than that used in conventional plasma-enhanced processes is found to be crucial in obtaining material with reproducible, good properties. The controlled, slow deposition is achieved by using very low flow rates of reactive gases, together with a much higher flow of inert gas to ensure uniformity.

Figure 2.7 Schematic diagram of PECVD set-up

A typical PECVD reaction is a complex process, in which many variables must be monitored and/or controlled. Although each of these influences the end result to some degree, it is impractical to optimize each one in a given process. Some of these variables are constrained by equipment design, or by simple consideration of uniformity, etc. The most important factor in determining the electrical quality of the deposited material is found to be the rate of deposition. The more important variables which influence this are the total flow of reactive gases, chamber pressure, rf power, and the reactive gas ratio. This ratio of N<sub>2</sub>O to SiH<sub>4</sub> is the primary factor in determining the stoichiometry of the film. To vary the deposition rate in a controlled fashion generally requires a change in

more than one parameter. Increasing the rf power increases the deposition rate but an increase in the reactive gas flow may be necessary to maintain uniformity. For a fixed power level, a decrease in the flow rate generally lowers the deposition rate but may require a decrease in chamber pressure for good uniformity. Moreover, the range of deposition which is possible using these conventional approaches is usually limited by design constraints. It proved difficult to obtain good control at low deposition rate. However, the approach adopted is to use a high flow of inert "carrier" gas (helium) to ensure uniformity and enable a wide range of deposition rate to be achieved simply by varying the reactive gas flow.

#### 2.4 Low Pressure Chemical Vapor Deposition

#### 2.4.1 Low Pressure CVD

The energy to activate and drive the chemical processes can be thermal, supplied by an electric glow discharge plasma, or attained by electromagnetic radiation. According to the type of energy supplied to initiate and sustain the reaction, CVD is classified into (1) Thermally activated reactions at various pressure range such as APCVD and LPCVD; (2) Plasma promoted reaction(PECVD).

In low pressure CVD processes, the reduced gas pressure enhances the mass transfer rate relative to the surface reaction rate, this makes it possible to deposit film uniformly in a relative highly economical close spaced positioning of the substrate wafers in a standup fashion.

The outstanding advantage of LPCVD technique lies in the thickness uniformity of the films and the step coverage which are substantially improved over those obtained in conventional atmospheric pressure CVD reactors. The films have fewer defects, such as particulate contaminants and pinholes, because of the inherently cleaner hot wall operations and the vertical wafer positioning that minimize the formation and codeposition of homogeneously gas phase nucleated particles[33]. These considerations are especially important in VLSI processing where a very high device reliability and high product yield must be achieved.

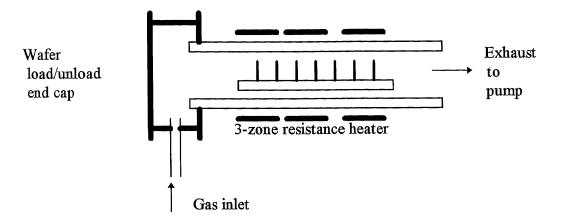

### 2.4.2 LPCVD Apparatus

The equipment used in our cleanroom is computer-controlled BTU LPCVD furnace. The schematic of a LPCVD reaction chamber is shown in Figure 2.8. This is a front-end loading furnace commonly used for operational convenience.

The LPCVD system in our cleanroom is used to deposit the silicon dioxide in low temperature which is 425°C. The films are formed by reacting silane and oxygen.

The chemical reaction proceed as follows:

$$425$$

°C SiH<sub>4</sub> + O<sub>2</sub> ====> SiO<sub>2</sub> + 2H<sub>2</sub>

resulting in high-quality silicon dioxide films. The low deposition temperature of the silane-oxygen reaction makes it a suitable process for low-temperature requirement and also when films must be deposited over a layer of a aluminum.

Figure 2.8 Schematic of LPCVD reaction chamber.

#### **CHAPTER 3**

#### **EXPERIMENTAL II**

At present, the MOSFET is the dominant device used in VLSI circuits. MOSFET technology can be subdivided into NMOS (n-channel MOSFET) technology and CMOS (complementary MOSFET) technology, which provides n-channel and p-channel MOSFET's on the same chip. The performance of CMOS VLSI circuits is being improved steadily by aggressively scaling the device dimensions to the submicron regime. However, the scaling is becoming more and more difficult due to many technological and fundamental limitations. In order to circumvent these difficulties, new device structures and materials based on Si technology have been proposed. The high performance heterostructure SiGe p-MOSFET, which exhibits higher channel mobility than its bulk Si counterpart, was first proposed by Nayak et al[34][35]. The channel mobility in this device is improved by employing a strained Si<sub>0.8</sub>Ge<sub>0.2</sub> layer as the conducting channel. The report[36] showed that high channel mobilities of 240 and 1500 cm<sup>2</sup>/V s at 300 and 77K, respectively, have been achieved for Si<sub>0.5</sub>Ge<sub>0.5</sub> p-MOSFETs. For a short channel (0.25µm) Si<sub>0.8</sub>Ge<sub>0.2</sub> device, a saturation transconductance of 167 mS/mm has been reported[37].

HOW TOURS WILLIAM INCHINE

### 3.1 The SiGe MOSFET

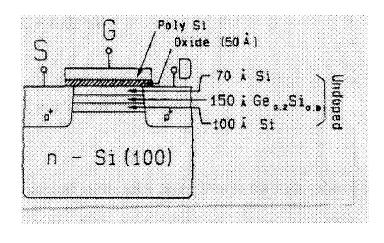

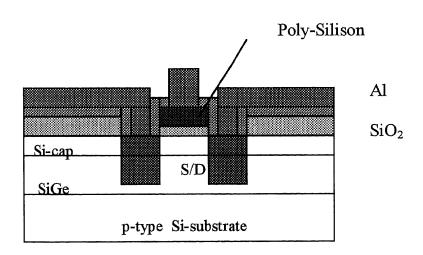

#### 3.1.1 The Structure of SiGe MOSFET

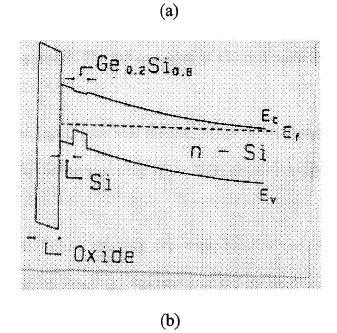

The structure of SiGe device proposed by Nayak[34] is shown in Figure 3.1(a). The

structure is similar to a conventional Si p-MOSFET except that a pseudomorphic SiGe channel is used for channel conduction. Figure 3.1(b) gives the equilibrium band diagram of the above quantum-well structure which corresponds to the condition when the channel of the enhancement-mode p-channel device is inverted. The biaxial compressive stress in

semininger in annihm kasar kah

Figure 3.1 (a) Schematic diagram of the layer composition of a p-type GeSi MOSFET. (b) Equilibrium band diagram of the structure shown in part (a).

SiGe lifts the degeneracy between heavy- and light-hole band, and the spin-orbit band is lowered in energy[38]. This results in a reduced bandgap and high in-plane hole mobility for the SiGe strained layer[39][40][41]. The reduction in bandgap of SiGe compared to bulk Si appears mostly as the valence band discontinuity at the Si/SiGe heterointerface

$$\Delta E_c = 0.02 \text{ eV} \tag{3.1}$$

$$\Delta E_{v} = 0.74x \text{ eV} \tag{3.2}$$

where x is the Ge content in the SiGe layer. Due to the high valance band discontinuity, the number of free holes in the buried SiGe channel (Figure 3.1(b)) will be higher than that in the adjacent Si layers. Therefore, the free carriers (holes in inversion) will be mostly confined in the SiGe channel. The enhancement in channel mobility is due to two main factors:

- (1) Strained-induced high in-plan hole mobility of the SiGe channel.

- (2) Reduced SiO<sub>2</sub>/Si surface scattering as the SiGe channel is separated from gate SiO<sub>2</sub> by the Si cap layer.

There are two factors affecting the strain level in the SiGe channel: (1) Ge concentration, x, in the channel, (2) Thickness of the strained SiGe channel. High Ge content can improve the device performance because strain increases low-field hole mobility and high-field carrier saturation velocity. For a 1.6% strain, an enhancement

factor of 2.5 - 4.5 can be expected. Table 3.1 gives the theoretical calculation of in-plane hole mobility of strained SiGe layer on Si <100> substrate.

Furthermore, for fixed Si cap layer and SiGe channel thickness, hole confinement in the SiGe channel improves with increasing strain[35][43][44]. However, the thermodynamically stable critical thickness of strained SiGe on Si(100) decreases rapidly

**Table 3.1** Theoretical calculation of in-plane hole mobility of strained SiGe layer on Si(100) substrate

| Strain in SiGe<br>(%) | Hole mobility enhancement factor                    |  |  |

|-----------------------|-----------------------------------------------------|--|--|

|                       | (μ <sub>strained-SiGe</sub> /μ <sub>bulk-Si</sub> ) |  |  |

| 0.4                   | 1.2                                                 |  |  |

| 0.8                   | 1.4                                                 |  |  |

| 1.2                   | 1.8                                                 |  |  |

| 1.6                   | 2.4                                                 |  |  |

| 2.0                   | 3.6                                                 |  |  |

| 2.4                   | 5.1                                                 |  |  |

to practically unacceptable values with strain: 80, 40 and 25Å for Si<sub>0.7</sub>Ge<sub>0.3</sub>, Si<sub>0.5</sub>Ge<sub>0.5</sub>, Si<sub>0.3</sub>Ge<sub>0.7</sub>, respectively[45]. For a very thin SiGe channel (<40Å), Si/SiGe interface scattering may limit channel mobility[46]. Experimental results also showed that the channel mobility increases with increasing strain in SiGe which was summarized in Table 3.2. However, when the SiGe channel thickness considerably exceeds the thermodynamically stable critical thickness, degradation of mobility due to strain relaxation has been observed. Severe degradation of channel mobility has been reported for a 100Å channel with 1.6% strain[47] and a 70Å channel with 2.8% strain[36].

Table 3.2 Experimental low-field channel mobility of SiGe p- MOSFETs

| Ref         | Strain in<br>SiGe<br>channel<br>(%) | SiGe<br>Channel<br>thickness<br>(Å) | Temp.<br>(T) | Bulk-Si<br>p-MOS<br>Channel<br>mobility<br>(cm <sup>2</sup> /V s) | Strained-<br>SiGe<br>p-MOS<br>channel<br>mobility<br>(cm <sup>2</sup> /V s) | Improve-<br>ment in<br>mobility<br>(%) |

|-------------|-------------------------------------|-------------------------------------|--------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------|

| [34]        | 0.8                                 | 150                                 | 300          | 122                                                               | 155                                                                         | 27                                     |

| [47,<br>48] | 0.8<br>1.2                          | 100<br>100                          | 300          | 120                                                               | 166<br>186                                                                  | 38<br>55                               |

|             | 0.8<br>1.2                          | 100<br>100                          | 90           | 372                                                               | 573<br>760                                                                  | 54<br>104                              |

| [37]        | 0.8<br>0.8                          | 125-300<br>125-300                  | 300<br>82    | 95<br>250                                                         | 150<br>400                                                                  | 57<br>60                               |

| [49]        | 1.0<br>1.0                          | 200<br>200                          | 300<br>82    | -<br>-                                                            | 220<br>980                                                                  | -<br>-                                 |

| [36]        | 2.0<br>2.8                          | 70<br>70                            | 300          | 141                                                               | 240<br>160                                                                  | 70<br>13                               |

|             | 2.0<br>2.8                          | 70<br>70                            | 77           | 600                                                               | 1500<br>550                                                                 | 150<br>-8                              |

# 3.1.2 SiGe-Channel MOSFET Design Parameters

The SiGe MOSFET design objective is to maximize the device transconductance. This can be achieved by confining high mobility holes in the SiGe channel while reducing the density of low mobility holes which flow at the Si/SiO<sub>2</sub> interface. The following parameters are important for optimization of SiGe MOSFET performance:

- (a) Choice of gate material.

- (b) The method of threshold voltage adjustment.

- (c) The SiGe profile in the channel.

- (d) The Silicon-cap and gate-oxide thicknesses.

The following discussion is based on the investigation with the use of the one-dimensional Poisson simulator HETMOD (HeTerostructure MODeling)[50], which simulated the impact of each of these design parameter on device performance. All simulations assumed that SiGe channel widths exceeding 5nm, neglect of quantum effect, gate oxide 7nm, doping of the n-type substrate  $5 \times 10^{16}$  /cm<sup>3</sup>, the Si/SiGe interface defect free, and the Si/SiO<sub>2</sub> interface density  $5 \times 10^{10}$  /cm<sup>3</sup>.

# A. Choice of Gate Material: n<sup>+</sup> - versus p<sup>+</sup> - doped Polysilicon

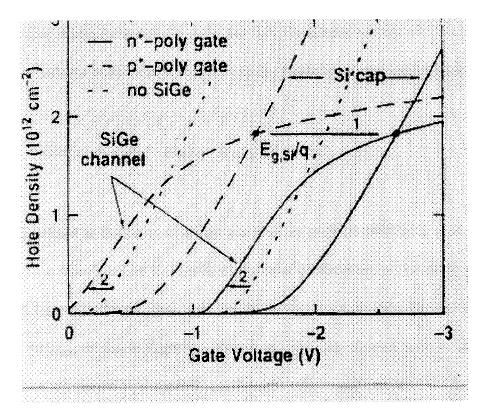

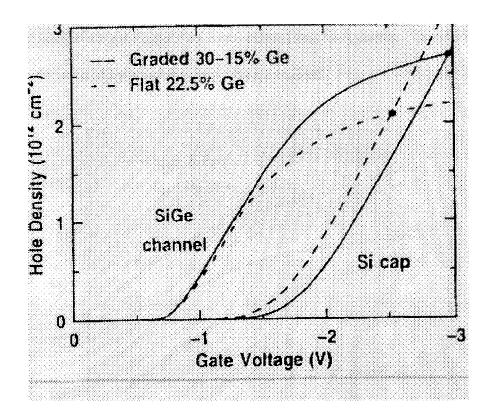

The type of gate material used in the SiGe p-MOSFET strongly influences the degree of the hole confinement to the SiGe channel [49]. HETMOD simulation results plotted in figure 3.2 show the hole densities in the SiGe channel and in the parasitic Si channel at the  $Si/SiO_2$  interface as a function of gate voltage for both an  $n^+$  - and a  $p^+$  - gate SiGe p-MOSFET. The hole distribution in the SiGe p-MOSFET's is compared to the inversion holes present in a silicon  $n^+$  - and a  $p^+$  - gate p-MOSFET. This simulation considers that the vertical channel profile of the SiGe devices consists of a 5-nm Si cap layer and a 9-nm

wide 30% SiGe channel with a uniform n-type doping level of 1x10<sup>15</sup>/cm<sup>3</sup> throughout the Si and SiGe channel. The simulation shows that both SiGe MOSFET's exhibit that

Figure 3.2 1-D Poisson simulation of the Si-cap and SiGe-channel charges for p<sup>+</sup>- and n<sup>+</sup> gate SiGe MOSFET's without threshold voltage adjustment.

SiGe channel turns-on before the parasitic Si cap layer turns-on. The parasitic charge in the Si surface channel exceeds the SiGe-channel charge for gate voltage which is about 1.4 V higher than the turn-on voltage. The cross-over voltage is defined as the gate voltage at which the charges in the SiGe channel and in the Si cap are equal. The  $n^+$  - and  $p^+$  - gate SiGe p-MOSFET's show identical hole confinement, but the difference in workfunction of the gates results in a horizontal shift equal to the silicon bandgap.

The threshold voltage of a SiGe p-MOSFET is defined as the gate voltage at which the total concentration of holes in the Si and SiGe channel equals the concentration of electrons in the n-type substrate[51]. The threshold voltage shift between the Si and SiGe MOSFET's is due to the energy band discontinuity at the Si/SiGe interface. The bandgap narrowing ΔEg is approximately 76 meV per 10% Ge introduced, and 97 % of this offset occurs in the valence band. Analytically, the SiGe threshold voltage can be expressed as:

$$V_{t}(SiGe) = V_{t}(Si) - \Delta E_{v}/q - Q_{channel}/C_{ox} + Q'_{channel}/C_{eq}$$

(3.3)

with V<sub>t</sub>(Si) defined as the onset of strong inversion in a silicon MOSFET. The gate-oxide capacitance  $C_{\text{ox}}$  is replaced by  $C_{\text{eq}}$  which is the series combination of the oxide capacitance and the Si cap capacitance. Q<sub>channel</sub> is the charge in the depletion region of a silicon MOSFET. Q'channel is the background charge in the SiGe channel and in the depleted region underneath the SiGe channel. From the simulation results plotted in Figure 3.2, the n<sup>+</sup>- gate p-MOSFET which has the threshold voltage of -1.2 V needs additional p-type dopants to move  $V_t$  to a lower value. But for the  $p^+$ - gate p-MOSFET which has the threshold voltage of 0 V requires extra n-type dopants to increase V<sub>t</sub>. When the flat channel doping profile is adjusted such that both the n<sup>+</sup> - and p<sup>+</sup> - gate p-MOSFET have identical threshold voltages of -0.6 V, the hole density is shown in Figure 3.3. The hole confinement to the SiGe channel for the n+ - gate design is significantly better than that for the p<sup>+</sup>- gate design since the cross-over voltage for p<sup>+</sup>- gate is as low as -1.1 V and more than -3.0 V for n<sup>+</sup> - gate. Hence, Foe identical Si cap and SiGe channels, the n<sup>+</sup> polysilicon-gate SiGe p-MOSFET can be designed for operation at higher power supply voltages than the p<sup>+</sup> polysilicon-gate SiGe p-MOSFET.

Figure 3.3 1-D Poisson simulation of the Si-cap and SiGe-channel charges for the p<sup>+</sup>- and n<sup>+</sup>- gate SiGe MOSFET's of figure 3.2 but with a -0.6 V threshold voltage.

## B. The Method of Threshold Voltage Adjustment

HETMOD simulation show that shifting the threshold voltage of the  $n^+$ - gate SiGe p-MOSFET to -0.6 V requires boron dose of  $1.5 \times 10^{12}/\text{cm}^2$ . But the high doping level in the SiGe channel leads to ionized impurity scattering which degrades the mobility. This problem can be avoided by using modulation-doping which locates the acceptor atoms outside the SiGe channel, physically separated from the mobile holes. The threshold voltage is independent of whether the boron-doped layer is located above or below the SiGe channel.

When the dopants are located above the SiGe channel, the thickness of the Si cap must increase to locate the dopants in it, therefore reducing the gate-to-channel capacitance. In addition, the parasitic Si surface-channel will turn on at a lower gate voltage than for the undoped Si cap case and also the ionized impurity scattering will affect the hole mobility. The above disadvantages can be avoided by placing the boron-doped layer under the SiGe channel[52]. A thin undoped Si spacer is located between the SiGe channel and the boron-doped layer to avoid ionized impurity scattering. The thickness of this spacer must be small to insure that most of the carriers are transferred to the SiGe channel. This technique is becoming common in state-of-the-art CMOS technologies since placing the dopants underneath the Si channel also improves short-channel effects[53][54].

## C. The Germanium Profile Engineering

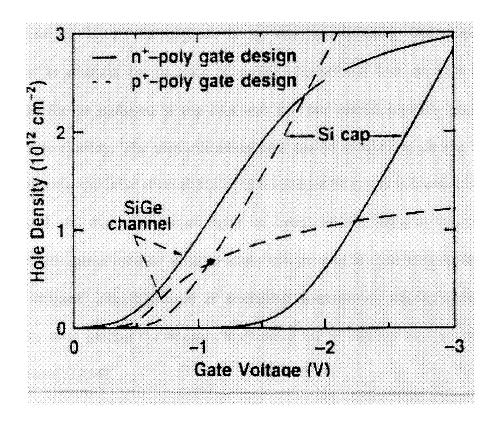

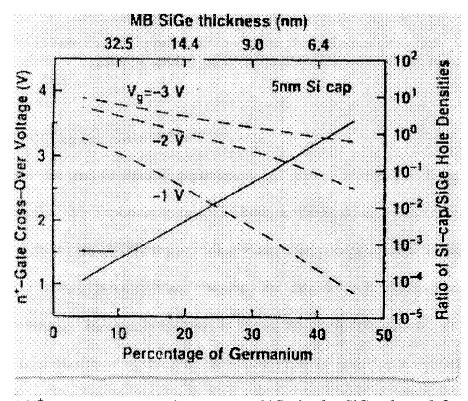

Hole confinement in the SiGe channel is largely dependent on the shape of the SiGe channel. To maximize the hole concentration in the SiGe channel and insure adequate confinement up to high gate voltages, a large valence band discontinuity at the top Si/SiGe films heterointerface is required. However, it is important to keep highly strained SiGe film stable throughout device fabrication. Matthews-Blakeslee gave the critical layer thickness limit on the SiGe thickness which is shown in Figure 3.4. From the results of simulation, the cross-over voltage is linearly proportional to the relative Ge concentration and more carriers flow in the Si cap layer as the gate voltage rises. In order to ensure that

the majority of holes flow in the SiGe channel for gate voltages equal to or more than -3.0 V, the Ge percentage must rise above 30%.

The results of 1-dimension Poisson simulations given in Figure 3.5, which compares a graded Ge profile to a uniform profile for the n<sup>+</sup>- gate p-MOSFET design with identical integrated Ge doses, shows that grading the channel instead of keeping it flat results in a large current drive as the mobility of the holes in the SiGe channel is higher than that of the holes the Si cap layer. In addition, a built-in electric field created in the graded channel forces the holes towards the top surface which can maximize the gate-to-channel capacitance and guiding the holes away from the ionized acceptors.

Figure 3.4 N<sup>+</sup>-gate cross-over voltage versus %Ge in the SiGe channel for a flat Ge profile. The SiGe film thickness is adjusted such that it is stable following Matthews-Blakeslee (MB) stability criterion. No threshold voltage adjustment used in these device.

Figure 3.5 1-D Poisson simulation of the Si-cap and SiGe-channel charges in a n<sup>+</sup>- gate SiGe p-MOSFET's, comparing graded versus uniform SiGe channels with identical total integrated Ge dose.

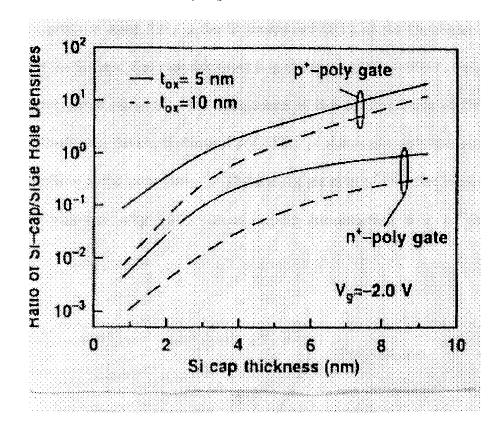

#### D. The Silicon Cap and Gate Oxide Thickness

To maximize the gate-to-channel capacitance and hence increase the SiGe MOSFET transconductance, it is important to minimize both the thickness of the silicon cap and that of the gate oxide. HETMOD simulations indicate that decreasing the Si cap thickness increases the cross-over voltage and reducing the gate oxide thickness decreases the cross-over voltage. This results is shown in Figure 3.6 where the ratio of holes present in the Si cap layer over those confined to the SiGe channel is plotted as a function of Si cap thickness for both the n<sup>+</sup> - and p<sup>+</sup> - gate designs and for two different gate thickness. If the Si cap is too thin, interface scattering will degrade the hole mobility but conversely

increase the channel-to-gate capacitance and hence transconductance. Therefore the Si cap thickness is determined by a mobility/capacitance tradeoff.

Figure 3.6 Ratio of holes flowing in the Si cap layer over those confined in the SiGe versus varying Si cap thickness (Vg = -2 V, T = 300K) for different  $n^+$ - and  $p^+$ -gate designs.

### 3.2 Fabrication of SiGe Channel MOSFET

The fabrication of SiGe MOSFET is carried out in NJIT cleanroom. The process design is based on NJIT cleanroom condition and the properties of SiGe material which is easy to relax in the high temperature procedure. Therefore, a series of low temperature processes are introduced to replace the high temperature processes used in Si MOSFET fabrication.

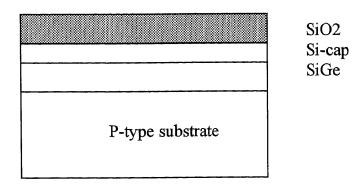

The device structure used in this work is shown in Figure 3.7. For making n-MOSFET, the starting material of SiGe wafer was grown by conventional CVD at atmospheric pressure using SiH<sub>4</sub> as the Si source and GeH<sub>4</sub> as the Ge source. SiH<sub>4</sub> was also used for the Si caps. The caps thickness is in the range 1500 - 1900 Å. Substrate is p-type <100> oriented si wafer. For comparison of the characteristics of SiGe-channel device and Si-channel device, Si-channel MOSFET is also made with the same process designed for SiGe at the same time. The starting material of Si wafer is p-type <100> Si-substrate with resistivity 14-21  $\Omega$ -cm( doping concentration 8 × 10<sup>14</sup>/cm<sup>3</sup> - 1 × 10<sup>15</sup>/cm<sup>3</sup>).

Figure 3.7 The structure of SiGe channel n-MOSFET

In this SiGe n-MOSFET process, there are four lithographic operations, four film-formation operations, two ion implantations and four etching operations.

## 3.2.1 Mask of Photolithograph

The masks used in SiGe n-MOSFET process were designed by Toros. These microelectronics test chip is composed of many device test structures for 2-micro process.

Chip size is 3.58mm  $\times$  3.58mm. The MOSFET transistor structures include:

- 1) Four MOS transistors with  $L=8~\mu m$  and  $W=2~\mu m$ , 4  $\mu m$ , 8  $\mu m$ , 16  $\mu m$ .

- 2) Four MOS transistors with W = 8  $\mu$ m and L = 2  $\mu$ m, 4  $\mu$ m, 8  $\mu$ m, 16  $\mu$ m.

- 3) Four MOS transistors with  $L = W = 1.5 \mu m$ ,  $L = W = 2 \mu m$ ,

$$L = W = 3 \mu m$$

,  $L = W = 4 \mu m$ .

There are four masks for this process which correspond to four different processes:

First mask(#1): Active device area definition.

Second mask(#2): Poly-silicon gate pattern definition.

Third mask(#3): Contact window definition.

Fourth mask(#4): Metal connection layer pattern definition.

#### 3.2.2 Process Flow Procedure and Chart

The main procedures in this process include 18 steps:

- 1. Wafer clean

- 2. LTO SiO<sub>2</sub>

- 3. Photolithograph #1 Mask

- 4. Wet etching Active area

- 5. LPCVD LTO Gate Oxide

- 6. Post LTO Annealing

- 7. Threshold voltage adjustment ion implantation

- 8. Poly-Si deposition

- 9. Photolithograph -- #2 Mask

- 10. RIE Poly-Si

- 11. S/D implantation and Poly-Si doping

- 12. Post-annealing

- 13. LTO SiO<sub>2</sub>

- 14. Photolithograph #3 Mask

- 15. RIE LTO

- 16. Aluminum deposition

- 17. Photolithograph

- 18. Aluminum etching

- 19. Aluminum alloy annealing

#### 3.2.3 SiGe-Channel MOSFET Process Traveler

In this section, the process is introduced step by step with calculation and explanation.

#### Step 1: Wafer clean

The first step for starting the process is always the wafer cleaning. The purpose is to remove the organic and inorganic contamination which exist on the surface of the wafer.

The wafer clean used in NJIT cleanroom is p-clean followed by rinsing of deionized water.

P-clean is consisted of three steps:

1) clean in the mixture of 5:1 H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> with 110°C and 10 minutes.

- 2) rinse with hot deionized water for 10 minutes.

- 3) rinse with cold deionized water for 5 minutes. Then spin the wafer dry.

## Step 2: LPCVD LTO SiO<sub>2</sub> (field oxide)

This step is to form the oxide isolation region. The oxide is deposited by the LPCVD LTO method. Before the wafer is sent into the furnace, the furnace pre-clean procedure has to be done by  $100:1::H_2O:HF$  for 1 minute. The deposition rate is about  $15\text{\AA}/\text{min}$  and the temperature is  $425^{\circ}C$ . The source is 300sccm SiH<sub>4</sub> and 75 sccm O<sub>2</sub> with pressure of 500m Torr. The film thickness is determined by many factors: (1) For 2  $\mu$ m process, the thickness of field oxide is typically 0.5 to 1  $\mu$ m.(2) serve as a mask for S/D ion implantation( 120keV,  $3 \times 10^{15}\text{/cm}^2$ ). Refer to Step 9 for detail. (3) the step of oxide. Since this is not the localized oxidation of silicon(LOCOS) process, after the formation of active area, the step is the same height of the oxide. If it is too high, the poly-silicon gate opening may occur at the corner of the step. (4) the oxide thickness loss during the process. Because the LPCVD LTO SiO<sub>2</sub> structure is loose and every furnace pre-clean will etch 530 Å approximately in 1 minute. Considering above factors, the film thickness is designed as 8000 Å in this process. Figure 3.9 show the cross-sectional view of SiGe MOSFET with formation of field oxide.

#### Step 3: Photolithograph - #1 Mask

This step defines the active device area which is patterned by mask #1. To do the the photolithograph, the first thing to do is to apply Photoresist which thickness is about 1.2 \( \mu \) m determined by the revolution (4000 rpm) and time (20 seconds). Then bake the photoresist in bake box oven at temperature 115°C for 20 minutes. Third step is to do the

Figure 3.8 Cross-sectional SiGe MOSFET with field oxide

alignment and exposure, followed by developing. Finally, the film of photoresist has to be baked again to make it hard enough for etching. Figure 3.10

# Step 4: Wet etching - Active area

The wet-etching of field oxide is done in the 7:1 BOE etchant with HF:H<sub>2</sub>O:NH<sub>4</sub>F. The

Figure 3.9 Cross-sectional SiGe MOSFET with photoresist

etching rate for LPCVD LTO SiO<sub>2</sub> is about 3300 Å/min. Since the wet chemical etching is isotropic, it should be very careful to control the ending time to avoid over-etching that will result in the larger active area than patterned area. After etching, photoresist is removed by p-strip solution (same as p-clean). Then clean the wafer for next step. Figure 3.11 is the cross-section of the formation of active area.

Figure 3.10 Cross-sectional SiGe MOSFET with etched field oxide

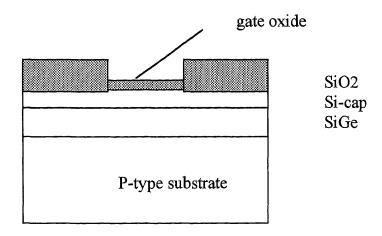

#### Step 5: LTCVD LTO gate oxide

In this process, the gate oxide is made by the deposition of LPCVD LTO which is introduced in step 2. The thickness of gate oxide is 435 Å according to 2-Micron process MOSIS parameters. This is a low temperature process, the quality of the oxide film is not as good as thermally grown oxide. Figure 3.12 shows cross-sectional SiGe MOSFET with gate oxide.

#### Step 6: Post-LTO annealing

Post-LTO annealing is necessary because it can reduce interface density which is brought by LPCVD deposition. Annealing is carried out in nitrogen at 600-650°C for 30 minutes.

Figure 3.11 Cross-sectional SiGe MOSFET with etched field oxide

## Step 7: Threshold voltage adjustment ion implantation

The experimental result shows that the flat-band voltage of Al-Si(p-type substrate) MOS structure is about -2 V after post-LTO annealing. But in this process, the gate material is poly-silicon. The difference of work function of poly-silicon and aluminum to p-type substrate is about -0.15 V. Hence the flat band voltage applied for poly-silicon to p-type substrate is about -2.15 V. The Threshold voltage is

$$_{t}(Si) = V_{fb} + 2\Psi_{B} + \frac{\sqrt{2\varepsilon_{s}qN_{A}(2\Psi_{B})}}{C_{o}}$$

(3.4)

where

$$\Psi_B = \frac{kT}{q} \ln \left[ \frac{N_A}{n_i} \right] = 0.0259 \times \ln \left[ \frac{1 \times 10^{15}}{1.45 \times 10^{10}} \right] = 0.29V$$

(3.5)

$$C_o = \frac{\varepsilon_{ox}}{d} = \frac{3.9 \times (8.85 \times 10^{-14})}{435 \times 10^{-8}} = 7.93 \times 10^{-8} \, F \, / \, cm^2 \tag{3.6}$$

Hence

$$V_t(Si) = -2.15 + 0.58 + 0.175 = -1.4 V$$

(3.7)

From equation (2), x = 0.2,  $\Delta E_V = 0.74x \text{ eV} = 0.15 \text{ eV}$ . So

$$V_t(SiGe) = V_t(Si) - \Delta Ev/q = -1.4 - 0.15 = -1.55 V$$

(3.8)

To adjust the threshold voltage of the device to 0.9 V,  $\Delta$  V<sub>t</sub>(SiGe) = 2.45 V and the p-type Boron ion implantation is required. The Boron charge causes a flat-band shift of

$$\Delta V_{t}(SiGe) = qF_{B}/C_{o}$$

(3.9)