New Jersey Institute of Technology Digital Commons @ NJIT

Theses

**Electronic Theses and Dissertations**

Summer 8-31-1998

# Telephone-accessed controller using CEBus for device control over power line

Gerald Aska New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/theses

Part of the Electrical and Electronics Commons

## **Recommended Citation**

Aska, Gerald, "Telephone-accessed controller using CEBus for device control over power line" (1998). *Theses.* 898. https://digitalcommons.njit.edu/theses/898

This Thesis is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Theses by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

## TELEPHONE-ACCESSED CONTROLLER USING CEBUS FOR DEVICE CONTROL OVER POWER LINE

#### by

## Gerald Aska

The CEBus standard has made it possible for devices developed by different manufacturers to communicate over the power line. Further, the standard allows analog adjustments of devices besides transmitting and receiving binary information. This Controller extends the distance from which these devices can be controlled.

To extend the distance of communication with a device, a telephone line interface was developed that allows the user to communicate with a CEBus device via the Controller. The Controller responses to Central Office signaling and opens its communication channel to allow the user to provide it with the commands by using the telephone keypad. The Controller interprets these commands and sends the appropriate information over the power line to the device specified in the command.

To make the Controller user friendly a voice circuit has been included. This circuit provides all the prompts and responses to guide the user for proper operation of the Controller.

## TELEPHONE-ACCESSED CONTROLLER USING CEBUS FOR DEVICE CONTROL OVER POWER LINE

by Gerald Aska

A Thesis Submitted to the Faculty of New Jersey Institute of Technology in Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical Engineering

Department of Electrical and Computer Engineering

August 1998

## **APPROVAL PAGE**

## TELEPHONE-ACCESSED CONTROLLER USING CEBUS FOR DEVICE CONTROL OVER POWER LINE

## by Gerald Aska

| Dr. Constantine N. Manikopoulos, Thesis Advisor                  | Date |

|------------------------------------------------------------------|------|

| Associate Professor of Electrical and Computer Engineering, NJIT |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

|                                                                  |      |

| Dr. Stanley S. Reisman, Committee Member                         | Date |

| Professor of Electrical and Computer Engineering, NJIT           |      |

Dr. Yun-Qing Shi, Committee Member Associate Professor of Electrical and Computer Engineering, NJIT

Date

## **BIOGRAPHICAL SKETCH**

Author: Gerald Aska

**Degree:** Master of Science

Date: August 1998

## Undergraduate and Graduate Education:

- Master of Science in Electrical Engineering, New Jersey Institute of Technology, Newark, NJ, 1998

- Bachelor of Science in Engineering Technology, New Jersey Institute of Technology, Newark, NJ, 1996

Major: Electrical Engineering

To my dear wife, Pauline, and mother-in-law, Cynthia, for their invaluable support during my studies at NJIT. To my daughter, Abigail, from whom time was taken so that I could complete my studies.

.

## ACKNOWLEDGMENT

There are a number of persons that I must give special thanks for their contribution to my success in completing this thesis. I thank Dr. Constantine N. Manikopoulos for allowing me to work under his supervision and for providing me with the information that gave me the basic understanding of CEBus. Thanks to Dr. Stanley S. Reisman and Dr. Yun-Qing Shi for consenting to be committee members. Special thanks also to Christopher Onjian for his responsiveness to my questions on CEBus-related issues.

## TABLE OF CONTENTS

| Cł | napter Page                                  |

|----|----------------------------------------------|

| 1  | INTRODUCTION1                                |

|    | 1.1 Objective                                |

|    | 1.2 Background Information                   |

| 2  | SPREAD SPECTRUM                              |

| 3  | HARDWARE DESCRIPTION                         |

|    | 3.1 Power Line Interface                     |

|    | 3.2 Telephone Line Interface                 |

|    | 3.3 Ring Detector                            |

|    | 3.4 Tone Detector                            |

|    | 3.5 Voice Module                             |

| 4  | SOFTWARE IMPLEMENTATION                      |

|    | 4.1 Bank Memory Implemention                 |

|    | 4.2 Software Development                     |

|    | 4.3 CEBus Message Transfer using CEBench     |

|    | 4.3.1 Layers Definitions                     |

|    | 4.3.2 CEBench Modifications                  |

| 5  | USER INTERFACE                               |

| 6  | CONCLUSION AND FUTURE IMPROVEMENTS65         |

| Al | PPENDIX A CONTROLLER APPLICATION SOURCE CODE |

| Al | PPENDIX B CONTROLLER APPLICATION FLOWCHARTS  |

## TABLE OF CONTENTS (Continued)

| Chapter    |                           | Page |

|------------|---------------------------|------|

| APPENDIX C | COMPILE BATCH FILE        | 113  |

| APPENDIX D | CONTEXTS, OBJECTS AND IVS | 114  |

| APPENDIX E | ALTERA SOURCE CODE        | 120  |

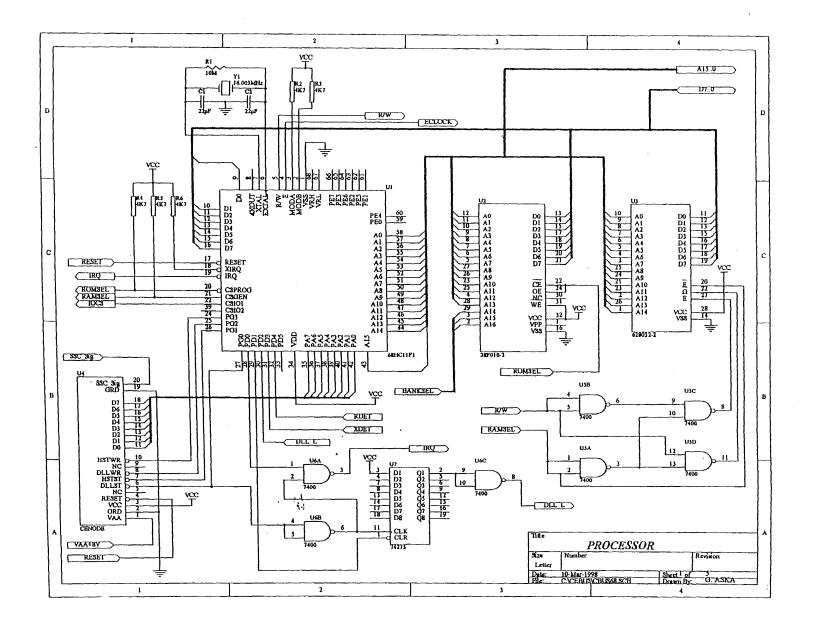

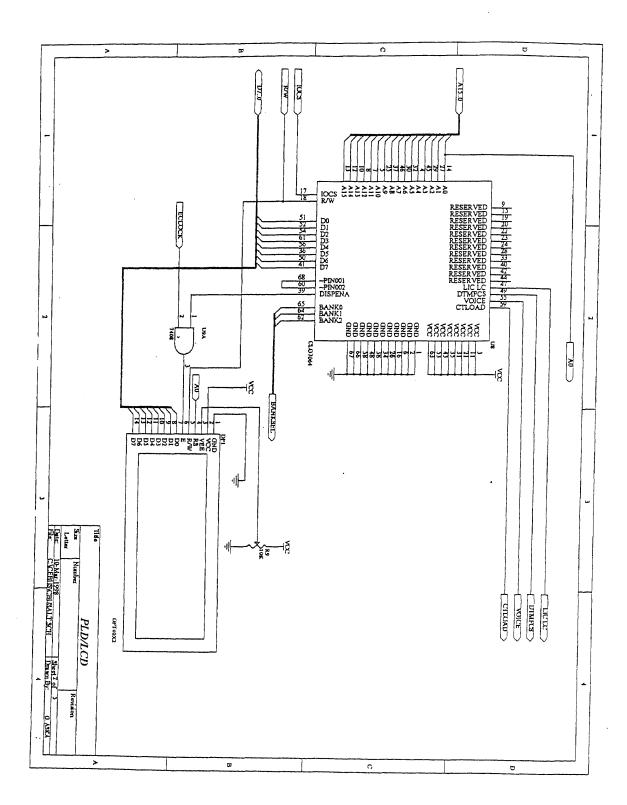

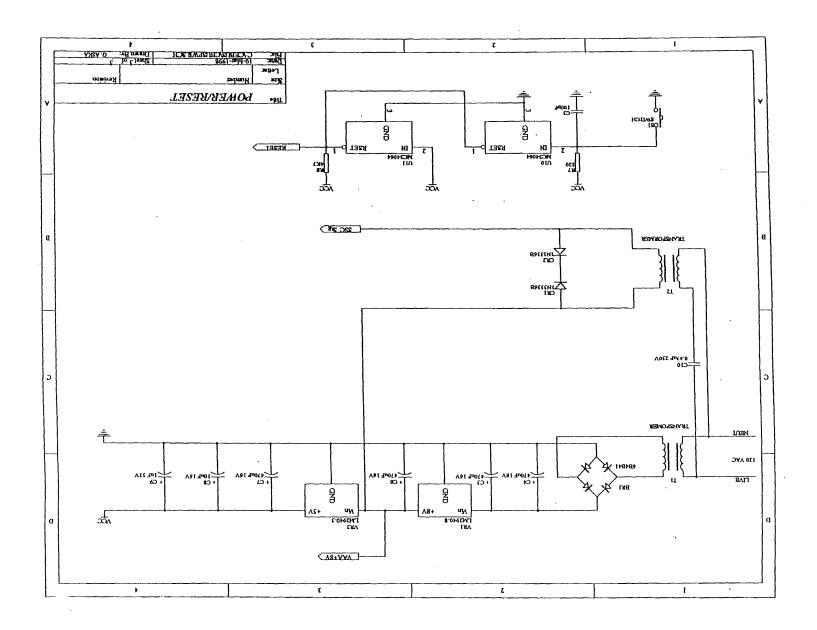

| APPENDIX F | SCHEMATIC DIAGRAMS        | 122  |

| APPENDIX G | PARTS LIST                | 128  |

| REFERENCES |                           | 132  |

.

## LIST OF TABLES

| Table | Page                                                     |

|-------|----------------------------------------------------------|

| 2.1   | Spread spectrum symbol code6                             |

| 3.1   | DLL functions implemented by CEThinx part of CENode PL13 |

| 3.2   | CENode/Host processor commands14                         |

| 3.3   | I/O lines and their uses15                               |

| 3.4   | U.S. telephone line operating parameters and limits      |

| 3.5   | Truth table of Multivibrator                             |

| 3.6   | Status register bit description                          |

| 3.7   | Functional encode/decode table                           |

| 3.8   | Control logic to access registers                        |

| 3.9   | Sythesizer Phonemes                                      |

| 3.10  | Phonemes Attribute Tokens40                              |

| 3.11  | V8600 command summary41                                  |

| 4.1   | Data transfer between modules in hierarchical program    |

| 5.1   | Valid and Invalid conditions for a command code62        |

## LIST OF FIGURES

| Figur | e Page                                                     |

|-------|------------------------------------------------------------|

| 2.1   | Spread spectrum signal for a 1 bit                         |

| 2.2   | Representation of two consecutive 1 bits7                  |

| 2.3   | Bit representaion for the preamble                         |

| 2.4   | Preamble and preamble EOF signaling                        |

| 2.5   | Beginning of data using $\phi 1$ and $\phi 2$ for symbols  |

| 3.1   | High-level block diagram of Controller10                   |

| 3.2   | Second-level block diagram of Controller11                 |

| 3.3   | CENode PL block diagram13                                  |

| 3.4   | Timing diagram of Attention Sequence17                     |

| 3.5   | Timing diagram of read Command Sequence17                  |

| 3.6   | Timing diagram of write Command Sequence18                 |

| 3.7   | Ringing cadence at Tip and Ring21                          |

| 3.8   | Ringing cadence at output of DAA                           |

| 3.9   | Telephone Line Interface Circuit                           |

| 3.10  | Multivibrator used in Ring Detector Circuit24              |

| 3.11  | Counter circuit used in Ring Detector Circuit              |

| 3.12  | Timing relation of Multivibrator and ring cadence of DAA27 |

| 3.13  | Tone Detector Circuit                                      |

| 3.14  | V8600 logic symbol                                         |

## LIST OF FIGURES (continued)

| Figure | 3                                                          | Page |

|--------|------------------------------------------------------------|------|

| 3.15   | V8600 status flags                                         | 36   |

| 3.16   | Microprocessor interface example                           | 36   |

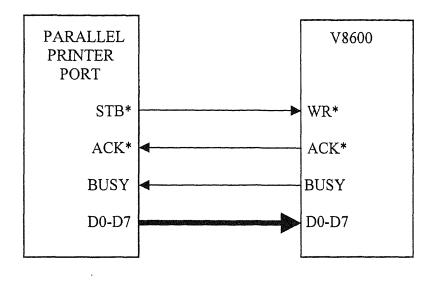

| 3.17   | Parallel Printer Port interface example                    | 37   |

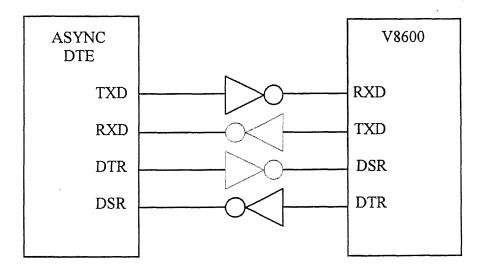

| 3.19   | RS-232 Serial interface example                            | 37   |

| 4.1    | Altera bank memory implementation program (part1)          | 44   |

| 4.1    | Altera bank memory implementation program (part 2)         | 45   |

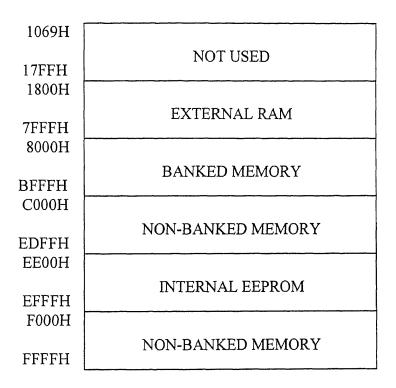

| 4.2    | Address range of each bank in memory chip.                 | 46   |

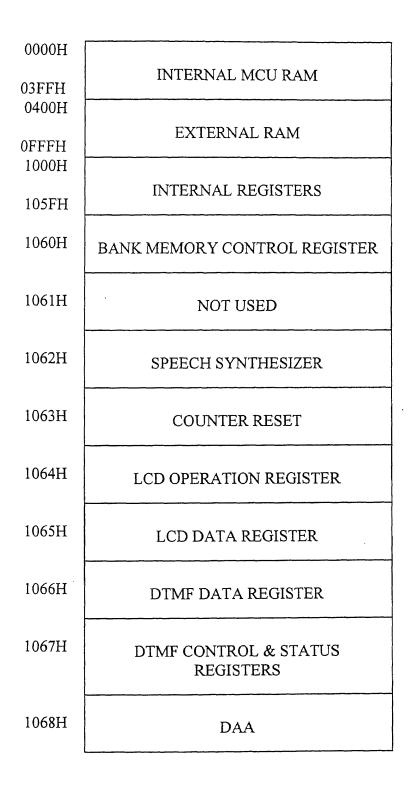

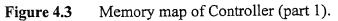

| 4.3    | Memory map of Controller (part 1)                          | 47   |

| 4.3    | Memory map of Controller (part 2)                          | 48   |

| 4.4    | Hierarchical arrangement of software program               | 50   |

| 4.5    | CEBench components of CEBus device.                        | 53   |

| 4.6    | Contexts, Objects and IVs used for the Controller (part 1) | 56   |

| 4.6    | Contexts, Objects and IVs used for the Controller (part 2) | 57   |

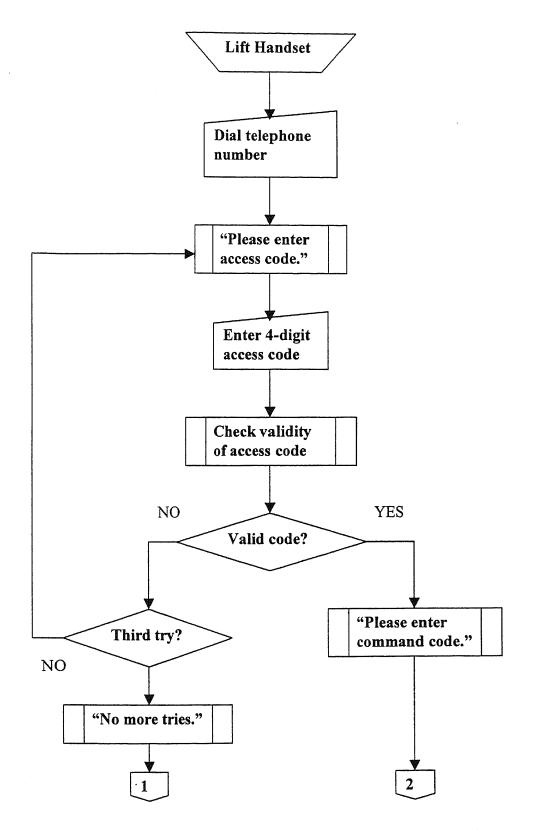

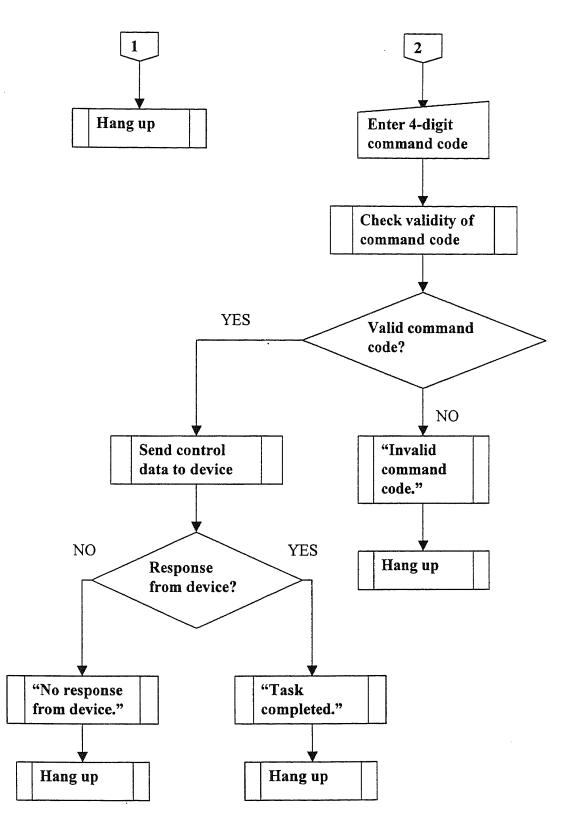

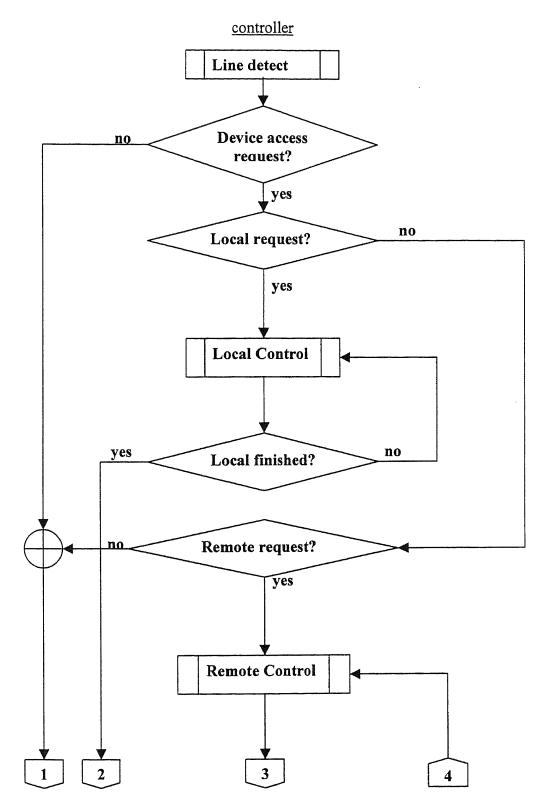

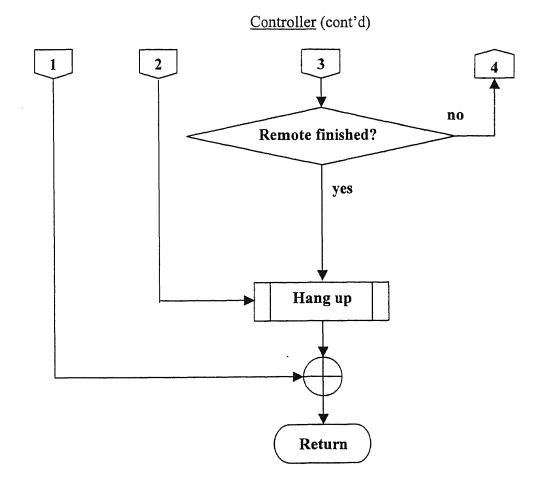

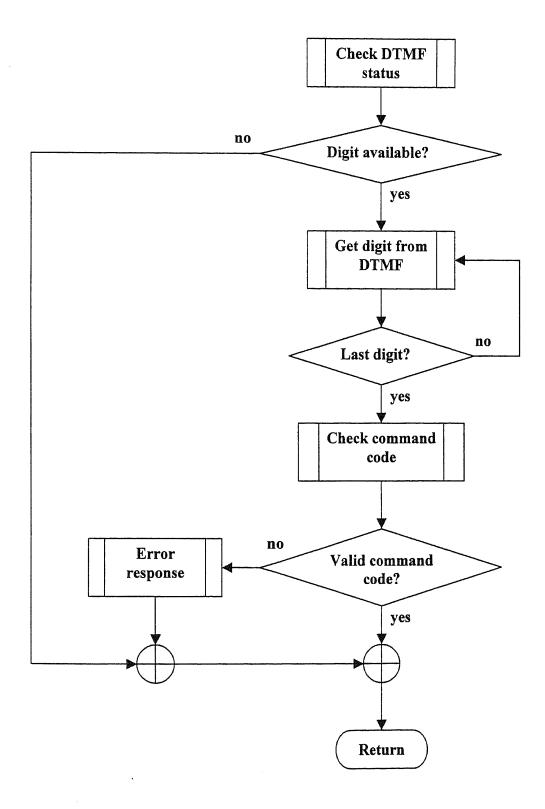

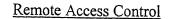

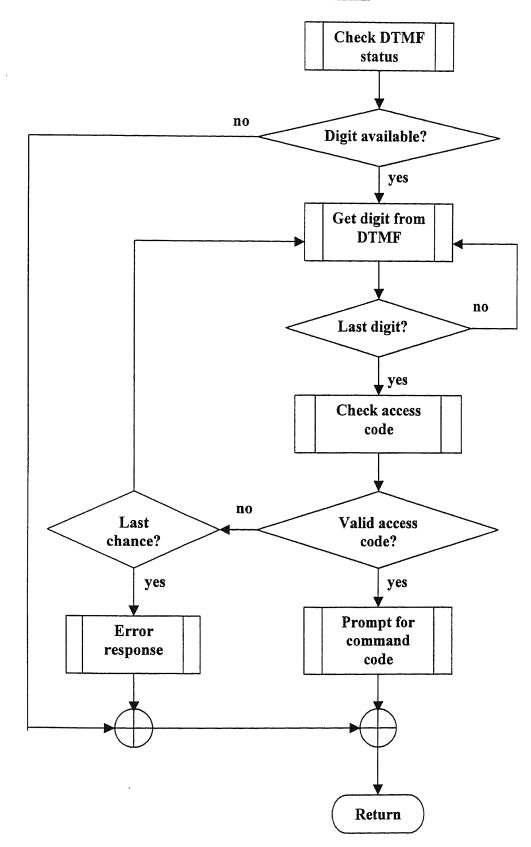

| 5.1    | Operation flowchart of Controller (part 1)                 | 63   |

| 5.1    | Operation flowchart of Controller (part 2)                 | 64   |

.

## CHAPTER 1

#### **INTRODUCTION**

#### 1.1 Objective

The objective of this thesis is to present the design and implementation of a Controller that is accessible from the telephone line and send control signals via the power line to a controlled device.

Since the CEBus standard is moving towards becoming a popular standard it will be inevitable that users will need a device that allows them to be able to control devices in the home from a remote location. Currently, X-10 allows remote control of device in the home. The problem is that X-10 is a proprietary standard and only a few devices can communicate using this standard. CEBus on the other hand is an open standard and because it flexibility and capability, that exceeds that of X-10, it is expected that many manufactures will either start or developing home automation devices, using CEBus, adding to the number of existing manufacturers. The Controller, that has been developed, satisfies the need for users to be able to communicate with any CEBus device from a remote location.

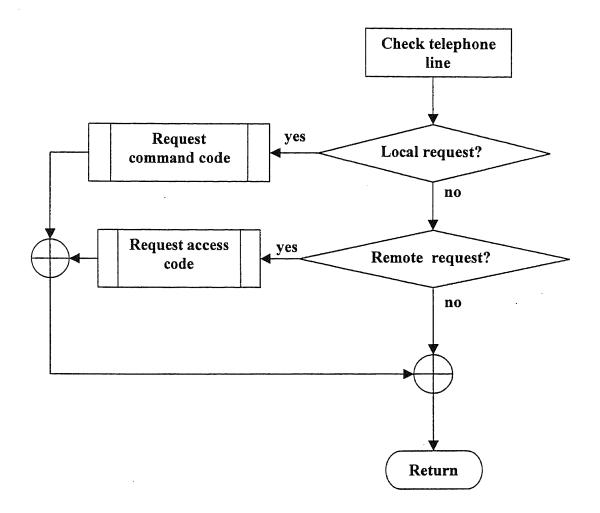

In the process of designing the Controller five stages were developed. The first stage is the Telephone Line Interface. It is responsible for line impedance matching and generating and receiving central office signaling. All user code entered from a telephone keypad enters this Interface. The Ring Detector forms the second stage of the Controller. It detects the ring signal from the Telephone Line Interface after it has been reformatted. This circuit determines the number of rings the Controller will allow before responding. The third stage is the Voice Module, which sends synthesized voice prompts and responses to the user. These prompts and responses guide the user through the operation of the Controller. The fourth stage is the Tone Detector, which detects the code the user enters from the telephone keypad. The dual-tone signal is then converted to a 4-bit digital code so that the microcontroller can interpret it. The final stage of the Controller is the Power Line Interface. This stage is responsible for converting digital-coded information to spread spectrum format in the transmitting mode and from spread spectrum to a digital format in the receiving mode. Spread spectrum is the technology used for power line communication. Since no device currently exist that allows remote control of CEBus devices the design was started from an high-level block diagram and proceeded to the component level design and implementation. Also, the software started with a high-level flowchart to the writing of many lines of code.

An important consideration used in the development of this device is the ease of use. This is the reason for including a synthesized voice feedback to the user. The user knows when to enter a code and receives a feedback on what happen when it was processed. The Controller receives four-digit access and command codes. It was also designed to allow the user to be able to use an extension to control a device that may be in another room of the house that the user is in. This feature was also implemented.

#### 1.1 Background Information

As the market for home automation increases more manufacturers will become involved in developing home automation devices. To avoid the confusion and hardship for consumers to find devices that are compatible to those that may already be in the home it became important to develop a standard among home automation manufacturers. The standard developed by the Electronics Industries Association (EIA) for home automation is the Consumer Electronic Bus (CEBus) standard. Since it was develop by a standard organization it will facilitate the interoperation of CEBus devices from various manufacturers.

The Controller presented in this thesis incorporates the CEBus standard making it possible to communicate with a CEBus device from a remote location.

.

#### CHAPTER 2

#### SPREAD SPECTRUM

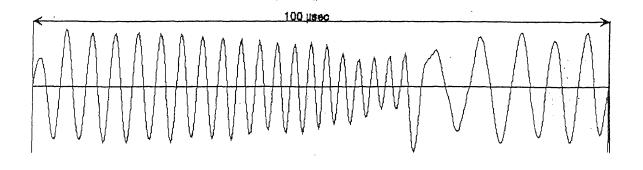

The spread spectrum waveform is a 100kHz to 400kHz bandeaus-filtered signal used in CEBus for communication over the power line. A 1 bit is represented by the waveform shown in Figure 2.1. The waveform starts at 200kHz and sweeps to 400kHz then suddenly changes to 100kHz and sweeps to 200kHz. The total sweep from 200kHz through to 200kHz again takes 25 cycles and a duration of 100µsec. This sweep is called a chirp. To meet FCC standard the out of band frequency above 400kHz must have an amplitude of less than 1mV. This is to ensure that the signal does not affect any AM radios that might be connected to the power line. The amplitude of the signal less than 100kHz must be less than 5mV to prevent interference with air and marine radio navigation.

The symbols, 1 and 0, are transmitted along the power line using SUPERIOR and INFERIOR states. Before any packet of data is transmitted on the power line a preamble must precede it. The SUPERIOR state of the preamble is that shown in Figure 2.1 and the INFERIOR state is the absence of the SUPERIOR state. In other words, the type of modulation used for the preamble is Amplitude Shift Keying (ASK). The preamble is a series of ones and zeros used in the sensing of the presence of another node transmitting. The physical layer does this by receiving its own signal. When it sends a signal (SUPERIOR state) it expects to get back a signal and when it does not send a signal

4

(INFERIOR state) it does not expect to receive a signal. However, if it gets a signal during its INFERIOR state it is an indication that another node is transmitting and that it

Figure 2.1 Spread spectrum signal for a 1 bit.

must back off. This detection method is called carrier sense multiple access (CSMA). If after all the eight bits of the preamble has be transmitted and no other node has been detected this node sends a preamble EOF (End of Frame) signal to let the other nodes know that it is about to transmit data.

In the data portion of the packet symbols are represented by two SUPERIOR states (phase 1 and phase 2). The signal shown in Figure 2.1 is called SUPERIOR phase 1 ( $\phi$ 1). SUPERIOR phase 2 ( $\phi$ 2) is 180° out phase with SUPERIOR  $\phi$ 1. Therefore the modulation method used in the data portion of the packet is Phase Reversal Keying (PRK). In the data portion of the signal there can be no absence of the signal as in the preamble. When the receiver detects a valid signal it then locks on to the signal for the duration of the packet. If the signal became absent the receiver would assume that it has

received the whole packet. However, the packet would eventually be discard after processing.

What is important in spread spectrum to represent a bit is the duration of the signal and not the phase. Table 2.1 shows the duration of the signal to represent 0, 1, End

| SYMBOL | PREMBLE |        | DATA |        |

|--------|---------|--------|------|--------|

|        | UST     | Timing | UST  | Timing |

| 1      | 1       | 114µs  | 1    | 100µs  |

| 0      | 2       | 228µs  | 2    | 200µs  |

| EOF    | 8       | 800µs  | 3    | 300µs  |

| EOP    | N/A ·   | N/A    | 4    | 400µs  |

**Table 2.1**Spread spectrum symbol code.

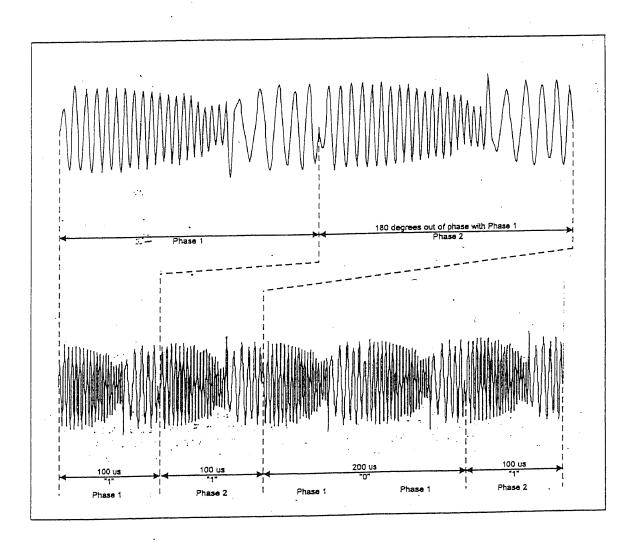

of Frame (EOF), and End of Packet (EOP) for different parts of a packet. A 100 $\mu$ s duration of the signal is called a Unit Symbol Time (UST). Earlier, it was mentioned that a 1 bit is represented by the signal shown in Figure 2.1, however an inverted or 180° out of phase signal may also represent a 1 bit provided that the duration of the signal is 100 $\mu$ s. This inverted symbol is called a INFERIOR or SUPERIOR  $\phi$ 2 (phase 2) state and the non-inverted SUPERIOR state is called the SUPERIOR  $\phi$ 1 state. Spread spectrum alternates between these phases to represent a series of 1 bits. Figure 2.2 shows the spread spectrum signal to represent two consecutive 1 bits. Note that after the first 100 $\mu$ s signal the phase is reversed to represent the next 1 bit. This phase alternating also applies to the 0 symbol which has a duration of 200 $\mu$ s. Also for a 0 bit, whichever phase is representing the signal that phase is continued for the duration of the symbol. The chirp will just be repeated.

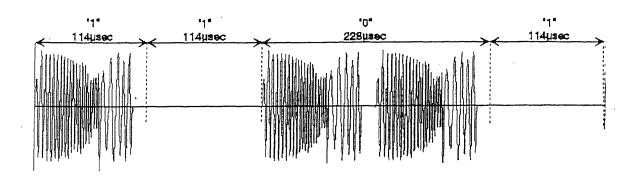

As shown in Table 2.1, the duration of the signal that represent a symbol for the preamble is different from that of the data portion. Since a chirp last for only 100 $\mu$ s there is an absence of signal even before the end of the symbol. The states are alternated just as in the data portion of the packet. Also, to represent a 0 bit there are two consecutive absences of the signal. The pattern is shown in Figure 2.3.

Figure 2.2 Representation of two consecutive 1 bits.

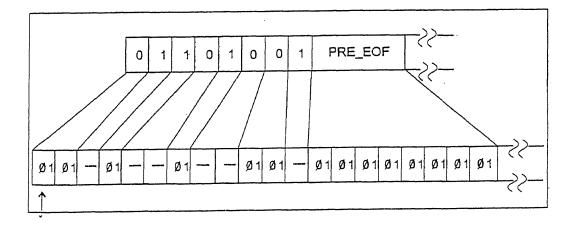

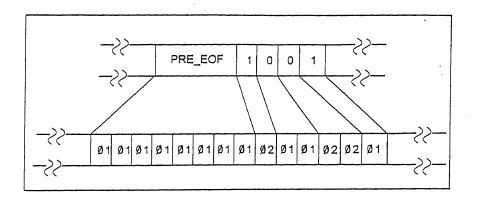

Figure 2.4 shows an example of preamble and the states used to represent the series of bits (01101001). The preamble EOF (PRE\_EOF) is a series of eight ones and is represented by eight SUPERIOR states. The SUPERIOR state is represented by  $\phi 1$  and the INFERIOR state by "---" in the preamble. After the PRE\_EOF has been transmitted the data portion of the packet follows. This is shown in Figure 2.5.

Figure 2.3 Bit representation for the preamble.

Figure 2.4 Preamble and preamble EOF signaling.

8

**Figure 2.5** Beginning of data using  $\phi 1$  and  $\phi 2$  for symbols.

## **CHAPTER 3**

## HARDWARE DESCRIPTION

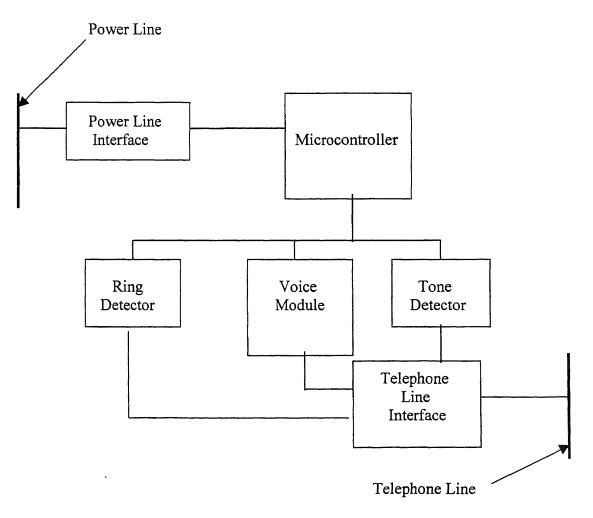

The high-level block diagram of the Controller is shown in Figure 3.1. The Telephone Line Interface receives signaling information from the telephone company central office and DTMF code from the user at the other end of the line. The Ring Detector counts the number of rings. When the set number of rings are detected the circuit signals the microcontroller. The microcontroller then accesses the telephone line and sends data to

Figure 3.1 High-level block diagram of Controller.

Figure 3.2 Second-level block diagram of Controller.

)\_\_\_\_\_1

the voice module. The Voice Module transmits an intelligible audio prompt to the user requesting some action. The user responses by pressing appropriate keys on the telephone keypad. The Tone Detector decodes these entries. The inputs to the Tone Detector are DTMF tones. The decoded tones are analyzed by the microcontroller to determine the action to take. The tones must provide information as to which device to operate and what kind of operation to perform. This communication between the controller and the controlled device takes place over the power line. The interface to the power line is provided by the Power Line Interface. Figure 3.2 shows a more detailed block diagram of the Controller. Refer to Appendix F for schematic diagrams. The following sections provide details of the functions of the hardware.

#### 3.1 **Power Line Interface**

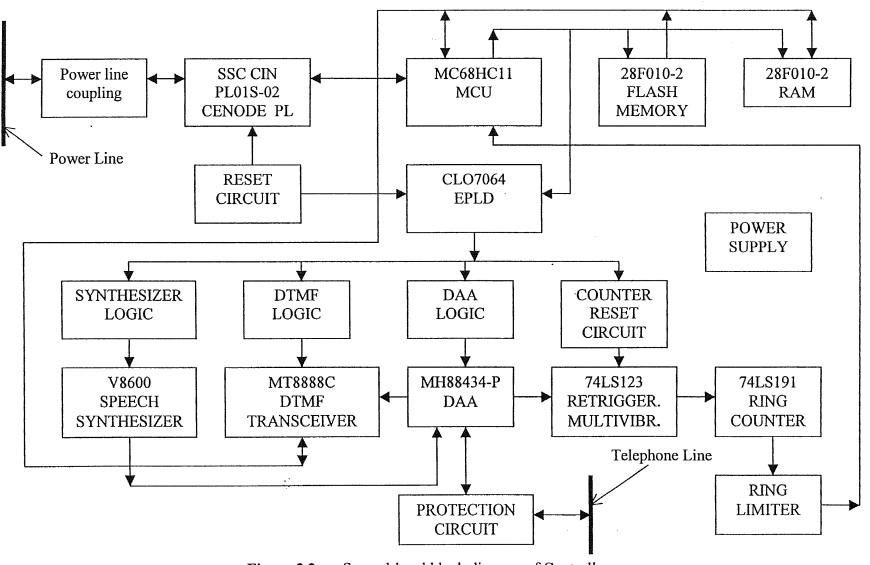

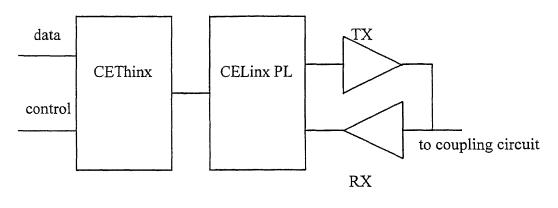

The Power Line Interface consist of a toroid impedance matching transformer, a 60 Hz blocking capacitor, two clamping diodes and the CENode PL Network Interface Card (SSC CIN PL01S-02) made by Intellon. The CENode PL Network Interface Card contains all of the circuitry and processing to implement EIA-600 Data Link Layer and Physical Layer of the CEBus Power Line Specification.

A block diagram of the CENode PL is shown in Figure 3.3. The CENode PL contains the CEThinx that implements the Data Link Layer and the CELinx PL that implements the Physical Layer of the Controller. The CELinx generates and detects spread spectrum waveform. In the detection mode of the CELinx PL the received spread spectrum is compared to an internal representation of the signal. Once a match is detected

the receiver locks on to the signal. This is why no absence of the signal can occur in the information portion of a packet. The receiver can detect signals of amplitudes between 5mV and 7V in the presence of power line noise.

Figure 3.3 CENode PL block diagram.

The DLL part of the CENode PL is implemented by the CEThinx. The table below (Table 3.1) lists the functions of CEThinx in both transmitting and receiving modes [5]:

**Table 3.1**DLL functions implemented by CEThinx part of CENode PL.

| CETHINX FUNCTIONS                      |                                    |  |

|----------------------------------------|------------------------------------|--|

| TRANSMITTING MODE                      | RECEIVING MODE                     |  |

| Generate preamble                      | Separate packet fragments          |  |

| Compress data using leading zero       | Detect packet errors               |  |

| suppression                            |                                    |  |

| Generate FCS for error checking        | Compare received and generated FCS |  |

| Generate acknowledgement packet        | Recognize System and MAC addresses |  |

| Access the power line medium using the | Reject duplicate packets           |  |

| CSMA/CDCR protocol                     |                                    |  |

The CENode to Host interface supports 15 commands. The development software used for the Controller sends these commands to the CENode. Table 3.2 shows these commands [4].

| Command | Command | Command Name    | Description                                   |  |

|---------|---------|-----------------|-----------------------------------------------|--|

| Value   | Code    |                 |                                               |  |

| 00H     | FIE     | Force Interface | Used by Factory Testing ONLY.                 |  |

|         |         | Error           |                                               |  |

| 01H     | RST     | Reset           | Host interface reset of CENode.               |  |

| 02H     | LR      | Layer Manage-   | Layer management read of configuration        |  |

|         |         | ment read       | information.                                  |  |

| 03H     | LW      | Layer Manage-   | Layer management write of configuration       |  |

|         |         | ment write      | information.                                  |  |

| 04H     | IR      | Interface Read  | Host read of interface flags.                 |  |

| 05H     | CW      | Control Wrote   | Host write to data link control parameters.   |  |

| 06H     | SR      | Status Read     | Host read of transmit, receive and statistics |  |

|         |         |                 | status information.                           |  |

| 07H     |         | Reserved        | Reserved.                                     |  |

| 08H     | PR      | Packet Receive  | Host read of received CENode packet.          |  |

| 09H     | PT      | Packet Transmit | Host write of CENode packet.                  |  |

| 0AH     | RRI     | Read Receive    | Host read of buffered received packet         |  |

|         |         | Information     | NDPU field from CENode.                       |  |

| 0BH     | WTI     | Write Transmit  | Host write of transmit NDPU field to          |  |

|         |         | Invoke          | CENode.                                       |  |

| 0CH     | RRH     | Read Receive    | Host read of data link NPDU header            |  |

|         |         | Header          | information from received.                    |  |

| 0DH     | WTH     | Write Transmit  | Host write of the NDPU header                 |  |

|         |         | Header          | information for subsequent transmit           |  |

|         |         |                 | packets.                                      |  |

| 0EH-45H |         | Reserved        | Reserved.                                     |  |

| 46H     | WR46    | Write Register  | Host write of data link communications        |  |

|         |         | 46              | access control parameters.                    |  |

| 47H-83H |         | Reserved        | Reserved.                                     |  |

| 84H     | RR4     | Read Register 4 | Host read of receive status flags.            |  |

| 85H-FFH |         | Reserved        | Reserved.                                     |  |

.

Table 3.2CENode/Host processor commands.

.

The logical interface between the Host processor and the CENode uses 13 I/O lines. Eight are bi-directional data lines, four are handshaking, and one is the Reset input. These 13 lines and their uses are listed in Table 3.3 [4].

| Mnemonic | Name          | Üse                                                                                                                                                                                                                                                                                                                                                      |  |

|----------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D0-D7    | Data pins     | Bi-directional data lines. In high impedance state when not in use for transfer.                                                                                                                                                                                                                                                                         |  |

| HSTST*   | Host Strobe   | Falling edge active strobe from host to CENode.<br>Used by host to initiate transfer of command to<br>CENode in conjunction with HSTWR* signal, and<br>used to indicate data byte available in host write<br>mode, and to acknowledge data byte transfer in host<br>read mode.                                                                           |  |

| HSTWR*   | Host Write    | Active low. Used to indicate a write mode in<br>conjunction with a Host Strobe signal. HSTWR*<br>inactive (high) with HSTST* indicates end of host<br>write mode, and end of any write command transfer.                                                                                                                                                 |  |

| DLLST*   | CENode Strobe | Falling edge active. (Falling edge active interrupt or<br>latched flag at host). Used in conjunction with<br>DLLWR* by CENode to get host attention and<br>request a command sequence. Also used to indicate<br>data available to host during a host read mode (with<br>DLLWR* active), and to acknowledge the data byte<br>transfer in host write mode. |  |

| DLLWR*   | CENode Write  | Active low. Used to indicate an attention request to<br>the host in conjunction with a DLLST* signal if no<br>transfer in progress. DLLWR* inactive (high) with<br>DLLST* indicates the end of read command data<br>transfer.                                                                                                                            |  |

| Reset    | CENode Reset  | Reset signal line for CENode. The host may assert<br>this line low (open collector drive) to provide a<br>hardware reset to the CENode.                                                                                                                                                                                                                  |  |

**Table 3.3**I/O lines and their uses.

The time allowed to service a DLLST\* signal from the CENode with a HSTST\* signal from the host is up to 1msec. Beyond this time duration the CENode will time-out. The exception to this rule occurs when DLLST\* is asserted for an Attention Sequence. In this case the HSTST\* response cannot be timed out. The DLLST\* is a fixed pulse of approximately 6µsec duration. The maximum supported transfer rate between the CENode and the host processor is approximately 40Kbytes per second.

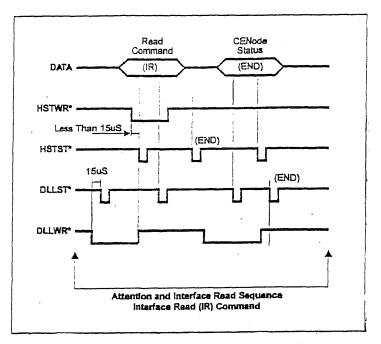

The CENode uses an Attention Sequence to cause the host to execute a command sequence. To prevent a race condition, the CENode executes a non-interruptible Attention Sequence by first asserting DLLWR\* and then waiting approximately 15µsec while checking for a HSTST\* signal. If a HSTST\* is seen during the time, DLLWR\* is dropped and the host command sequence is performed. If after approximately 15µsec, no HSTST\* has been seen, the CENode asserts a DLLST\* signal. The next HSTST\* is then interpreted as an acknowledgement of the Attention Sequence. The HSTWR\* should be asserted prior to this time by the host and the CENode will drop the DLLWR\* signal in response to the HSTST\* signal. Figure 3.4 shows the timing diagram for the Attention Sequence.

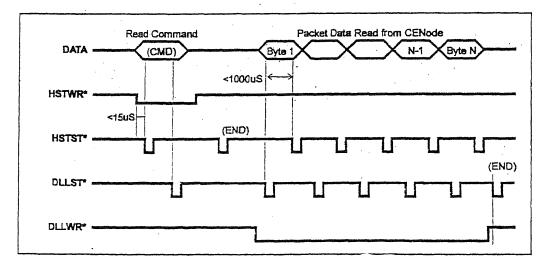

Although the CENode can cause the host to initiate a command sequence, the host can do it independently and asynchronously. In either case, the host starts a command sequence by putting the command on the data bus and asserting HSTWR\*. If the host is not responding to an Attention DLLST\* it must, in a non-interruptible sequence lasting not more than 15µsec, check that DLLWR\* is not asserted before asserting HSTST\*. If DLLWR\* is asserted it must wait for the Attention DLLST\*, then with a HSTST\*

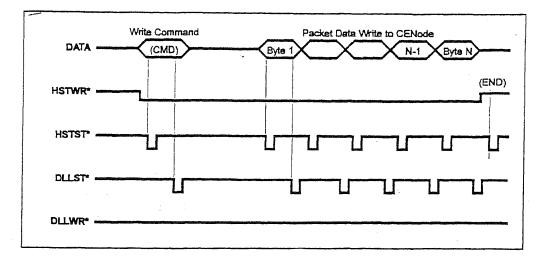

acknowledge it and indicate a command on the data bus and continue with the command sequence. The host may have to wait up to 5µsec for the initial DLLST\* acknowledging the command. Figures 3.6 and 3.7 show the timing diagrams for the read and the write command sequences respectively [4].

Figure 3.4 Timing diagram of Attention Sequence.

Figure 3.5 Timing diagram of read Command Sequence.

Figure 3.6 Timing diagram of write Command Sequence.

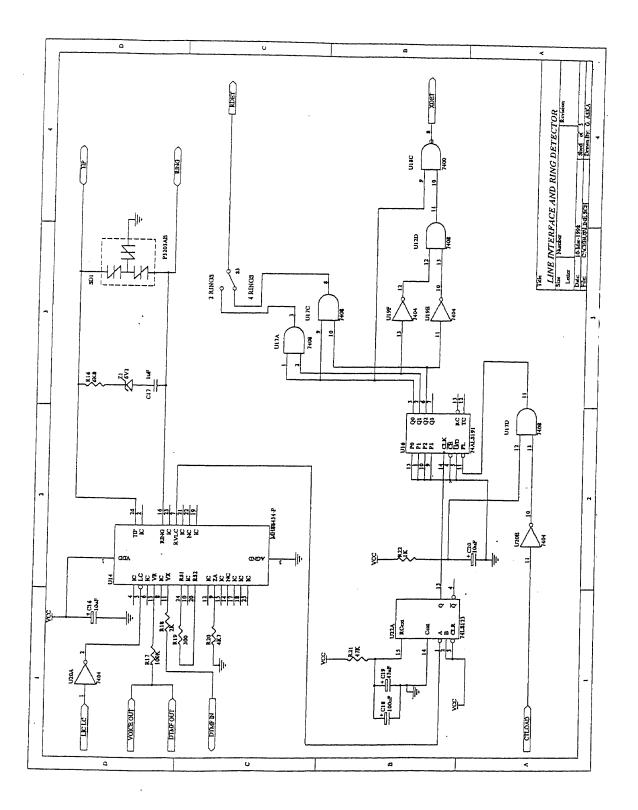

## 3.2 Telephone Line Interface

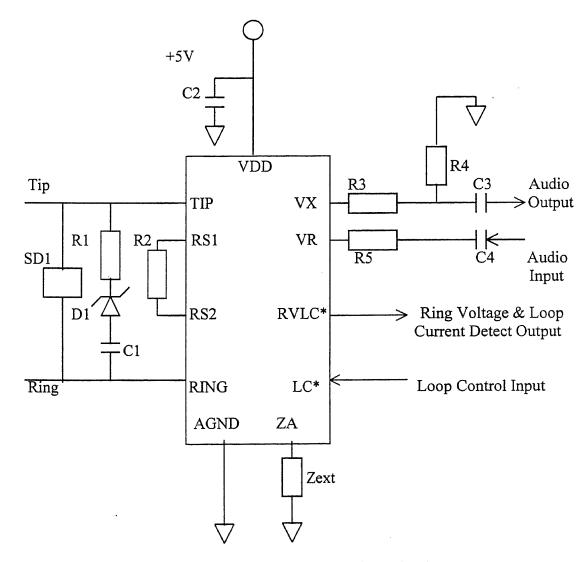

The Telephone Line Interface is an MH88434-P Data Access Arrangement (DAA) manufactured by Mitel. The device provides isolation to comply with North American standards -- FCC Part 68.304 and DOC CS03 2.2 [1]. Table 3.4 lists the operating parameters and limits for telephone equipment in the United States [16].

To protect the device from damage due to over voltage a P3203AB sidactor (SD1) is connect across Tip and Ring as shown in Figure 3.9. Damaging transient voltage may occur due to lightning surges of up to 1000 volts and induced voltages from, or short circuits to, utility electrical power lines. The sidactor is a very fast clamping device. When it senses high voltages on the line it provide a low impedance in a matter of nanoseconds to protect communication equipment. It will hold the line voltage low until the high voltage that triggered the device reaches a safe level.

| PARAMETER                    | Typical Values  | Limits               |

|------------------------------|-----------------|----------------------|

| Common Battery Voltage       | -48 V dc        | -47 to 105 V dc      |

| Operating Current            | 20 to 80 mA     | 20 to 120 mA         |

| Subscriber Loop Resistance   | 0 to 1300 ohms  | 0 to 3600 ohms       |

| Loop Loss                    | 8 dB            | 17 dB                |

| Distortion                   | -50 dB total    | N/A                  |

| Ringing Signal               | 20 Hz, 90 V rms | 16 to 60 Hz,         |

|                              |                 | 40 to 130 V rms      |

| Receive Sound Pressure Level | 70 to 90 dBspl* | 130 dBspl            |

| Telephone Set Noise          |                 | less than 15 dBrnC** |

**Table 3.4**U.S. telephone line operating parameters and limits

\*dBspl = dB sound pressure level.

\*\*dBrnC = dB value of electrical noise referenced to -90dBm measured with C message weighting frequency response.

A resistor, zener diode and capacitor in series are connected across Tip and Ring as a dummy ringer. Its purpose is to provide a load across Tip and Ring.

When Loop Control (LC\*) is at logic 0, a line termination is applied across Tip and Ring. At this logic level the device is in the off-hook state and DC loop currents will flow through the DAA from the central office. The line termination consists of a DC line termination and an AC input impedance. The DC termination is dependent on the loop current and is approximately  $300\Omega$ . Zext represents the additional impedance required for proper impedance matching of the DAA to the line impedance. The following formula was used to calculate the value of Zext:

Input impedance

$$Zin = \frac{Zext + Zint}{10}$$

(3.1)

Where Zint is the internal impedance of the DAA and is equal to  $1.3k_{\Omega}$ . Zin (the impedance of the telephone line) is equal to  $600_{\Omega}$ .

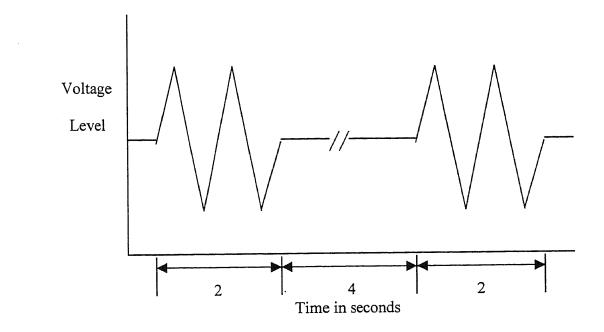

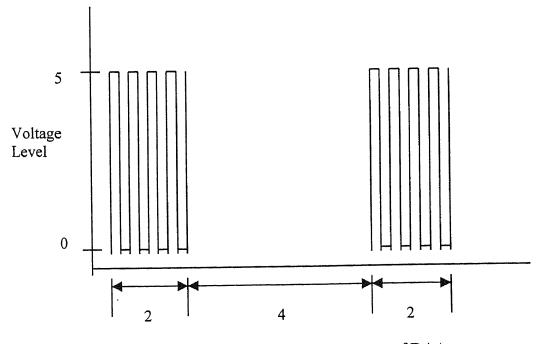

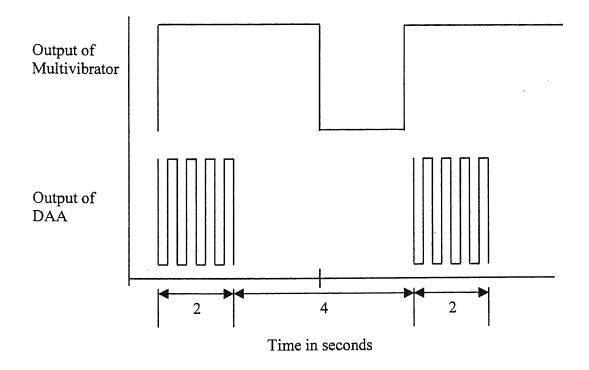

The resistor R2 sets the sensitivity of the ring voltage detection circuit. Using a  $300k_{\Omega}$  resistor sets the sensitivity to approximately 20Vrms. The ring signal from the central office is typically 90Vrms. The ring frequency from the central office is between 16Hz and 60Hz. However, the frequency is doubled (32Hz to 120Hz) when it comes out of the DAA at the Ring Voltage/Loop Current (RVLC\*) pin. This output ring voltage is at TTL level. Another consideration of the ring signal is the ringing cadence. The ringing cadence for the United States and Europe is 2 seconds ring and 4 seconds silence. Figure 3.7 shows the ring signal from the central office and Figure 3.8 shows the ring voltage at the output of the DAA.

The DAA converts the balanced two-wire input at Tip and Ring to a groundreferenced signal at VX. It also converts the ground-referenced signal at VR to a balanced two-wire signal across Tip and Ring. The transmit (VX) and receive (VR) signals are biased at 2.5V. During full duplex transmission an internal cancellation circuit prevents the signal sent out on TIP and Ring from re-entering on VX.

The transmit gain of the DAA is the gain from the differential signal across Tip and Ring to the ground referenced signal at VX. Resistors R3 and R4 alters the gain of

Figure 3.7 Ringing cadence at Tip and Ring.

Figure 3.8 Ringing cadence at output of DAA.

the device. The gain of the device was reduced by 50% (3dB) using a voltage divider consisting of two  $2k\Omega$  resistors. The receive gain of the device is the gain from the ground referenced signal at VR to the differential signal across Tip and Ring. The input resistance at VR (to ground) is  $47k\Omega$ . A  $100k\Omega$  resistor was used to reduce the gain by 50% (3dB).

Figure 3.9 Telephone Line Interface Circuit.

The DAA shown in Figure 3.9 is capable of monitoring the line condition across Tip and Ring. The Ring Voltage/Loop Current (RVLC\*) detect pin indicates the status of the device. The output is a logic 0 when loop current flows indicating that the device is in the off-hook state. The pin will also go low when an extension phone goes off-hook. This feature was used to implement the extension phone mode of the Controller. In the dial-up mode the RVLC\* pin will output ringing voltage which distinguishes it from the extension mode.

When the Controller is on-hook, 48V is across Tip and Ring. When the line is accessed (LC\* low) a low DC impedance of 100 to  $400_{\Omega}$  causes a loop current to flow. At the time the ring signal is present no loop current flows.

### 3.3 Ring Detector

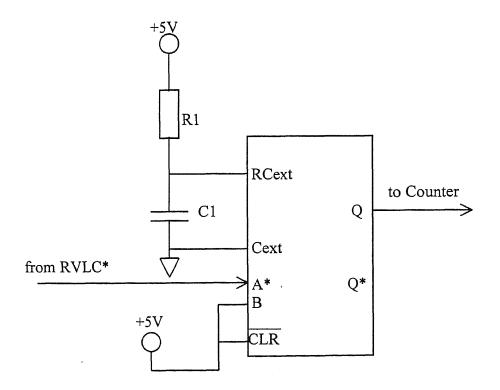

The major components of the ring detector are the 74LS123 retriggerable monstable multivibrator and the 74LS191 Up/Down Binary Counter. Figure 3.10 shows the circuit diagram for the multivibrator and Table 3.5 shows its truth table [17]. Resistor R1 and capacitor C1 essentially determines the basic output pulse duration. For C1 less than or equal to 1000pF the pulse duration is calculated from:

$$t_w = K * R1 * C1$$

(3.2)

When C1 is greater than or equal to  $1\mu$ F, the output pulse duration is calculated from:

$$t_{\rm w} = 0.33 * R1 * C1 \tag{3.3}$$

For the given equations, as applicable:

K is the multiplier whose value depends on the expected pulse duration. This value was obtained from the data sheet.

R1 is in  $K\Omega$

C1 is in pF

t<sub>w</sub> is in ns

Connecting the Cext pin to ground gives maximum noise immunity even though the device is connected to ground internally. Due to the timing scheme used by the device, a switching diode is not required to prevent reverse biasing when using electrolytic capacitors [17].

Figure 3.10 Multivibrator used in Ring Detector circuit.

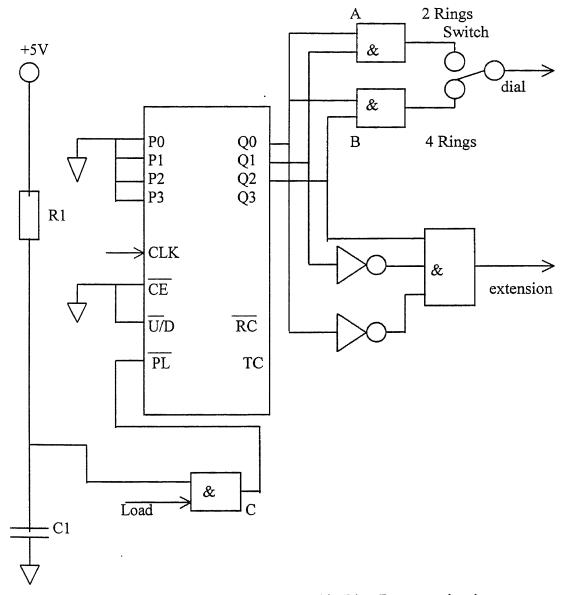

A pulse of 2sec was calculated for the Controller. This duration was used so that the pulsed would reflect the ringing cadence. Each time the ringing signal is present the output of the 74LS123 goes to logic 1 to increment the count. Doing so we can set the number of times the Controller will "ring" before seizing the telephone line. As Figure 3.11 shows the number of rings can be set to either 2 or 4 using AND gates. We will get back to the detail of this circuit a little late. For now we want to look at the response of the multivibrator circuit in relation to the ringing cadence at the output off the DAA. Recall that the multivibrator used is retriggerable. Therefore when the ring stops and the silent period begins the output of the multivibrator will be at logic 1 for 2 more seconds after the ring stops (although it rose to logic 1 at the beginning of the ring). Figure 3.12 shows

| INPUTS |   |   | OUTPUTS |    |  |

|--------|---|---|---------|----|--|

| CLEAR  | A | В | Q       | Q* |  |

| L      | X | X | L       | Н  |  |

| х      | Н | Х | L       | Н  |  |

| х      | x | L | L       | Н  |  |

| Н      | L |   |         |    |  |

| Н      |   | Η | Л       |    |  |

| ·      | L | Η |         | Ţ  |  |

**Table 3.5**Truth table of Multivibrator.

this timing relation. The 74LS191 counter has a positive edge clock. When counter receives a positive-going edge from the multivibrator it will increment at the beginning of each ring.

The counter begins to operate at power-up. Since at power-up the capacitor has no charge the upper plate of the capacitor is virtual zero. The Load input of AND gate C in

Figure 3.11 Counter circuit used in Ring Detector circuit.

Figure 3.11 is also initialized to zero. Therefore the input on the PL\* pin of the 74LS191 counter will be zero. This will cause the inputs on pins P0, P1, P2 and P3 to be loaded into the counter setting the output of counter (Q0, Q1, Q2 and Q3) to zero. When "ringing" begins it causes the counter to increment. Note the dial and extension outputs of the counter circuit. The extension output is low when the count is 1. This will indicate to the microcontroller that there is a request for access to the Controller. The microcontroller will then seize the telephone line to begin communication.

**Figure 3.12** Timing relation of multivibrator output (top) and ringing cadence at output of DAA (bottom).

There was one problem here that needed to be solved. The extension output of Figure 3.11 should only be active when an extension phone is off-hook. However, it does

become active even in the dial-up mode since the counter will eventually reach a count of 1. If this problem is not solved then we will never get to a count beyond 1 and there will be no distinction between dial-up access and extension phone access. That is, the telephone line will be seized at the count of one. This will cause the ringing signal from the central office to stop, ending the count at one. What makes this problem serious is that for extension access no access code is required and anyone can have access to any device in the home although the user would be using a remote telephone for access. To solve this problem a twelve-second software delay was added. Since only the extension phone can cause the RVLC\* pin to be at logic 0 for 12 seconds then the microcontroller cannot be confused as to which mode of access to provide. In other words, the count of 1, using a remote telephone, will not remain at 1 long enough for the Controller to accept it as a local access. After each access to the Controller the microcontroller resets the counter by setting the Load input on AND gate C to a logic 0.

Because of the timing relation between the multivibrator output and the DAA output, setting the number of dial-up rings was not straightforward. To set the Controller to "ring" 2 times the counter had to be set for a count of 3. To explain the reason for this we must look back at Figure 3.12. Note that the first high output of the multivibrator occurs when the ring signal goes to logic 0 causing the counter to immediately go to a count of 1. The output then goes low for 2 seconds before the next ring. After the first silent period of the ring signal and at the beginning of the second ring the counter will go to a count of 2 because of the second high at the output of the multivibrator. A count of 3 will occur just at the start of the third ring. In fact the microcontroller will respond to this

count of 3 so fast that the ring signal will be cut off before it can even make a complete cycle. Therefore only 2 rings actually occur for a count of 3 at the output of the counter.

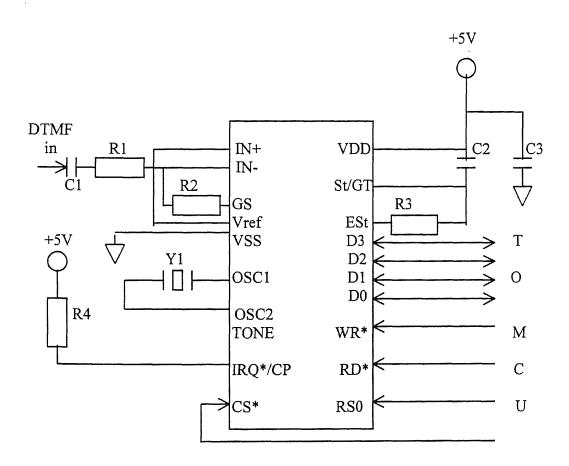

### 3.4 Tone Detector

The MT8888C Integrated DTMF Transceiver is responsible for detecting and converting DTMF tones. Figure 3.13 shows the Tone Detector circuit diagram used in the Controller. The MT8888C detects a valid dual tone by a steering circuit. Before loading the Receive Data Register (RDR) with the corresponding 4-bit data the steering circuit in conjunction with the C2 and R3 checks the duration of the tone. This is done so that voice tones (which are of shorter duration) are not interpreted as valid tone pairs. When a valid tone pair is received Est goes to logic 1 which in turn drives St/GT to logic 1. Provided that the signal is maintained for the valid period, St/GT will reach the threshold voltage of the steering circuit. This is enough time for the steering logic to register the corresponding code in the register. After the code is registered GT outputs a logic 1 which will remain as long as Est stays at logic 1. There will be a short delay to allow the output latch to stabilize. After this delay the steering output flag goes to logic 1 indicating that a valid tone pair has been received and registered. The condition of a valid tone pair detection can be obtained by reading a logic 0 on bit b3 of the status register. Table 3.6 [1] shows the representation of each bit in the status register. Although the steering circuit rejects signals that are too short to be considered valid, it will tolerate signal interruptions too short to be considered a valid pause [1].

The input signal, from the DAA, enters the MT8888C on IN-. In Figure 3.13 the input is connected in the single-ended mode. Capacitor C1 and resistors R1 and R2

determine the gain of the input amplifier and GS provides the feedback path. Capacitor C1 also provides dc voltage blocking.

Figure 3.13 Tone Detector Circuit.

The MT8888C is capable of generating sixteen standard DTMF tone pairs with low distortion and high accuracy. All frequencies are derived from crystal Y1 that must be 3.579545 MHz. The sinusoidal waveforms for the individual tones are digitally synthesized using a row and column programmable divider and switched capacitor D/A converters. The standard set for the tolerance of the individual tones in North America is Register. The individual tones generated are referred to as low group (LOW FREQ.) and

| BIT | NAME                                           | STATUS FLAG SET                                                            | STATUS FLAG<br>CLEAR                                                |

|-----|------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------|

| ь0  | IRQ                                            | Interrupt has occurred .<br>Bit 1 (b1) or bit 2 (b2) is<br>set.            | Interrupt is inactive.<br>Cleared after Status<br>Register is read. |

| b1  | TRANSMIT DATA<br>REGISTER (BURST<br>MODE ONLY) | Pause duration has<br>terminated and transmitter<br>is ready for new data. | Cleared after Status<br>Register is read.                           |

| b2  | RECEIVE DATA<br>REGISTER                       | Valid data is in the<br>Receive Data Register.                             | Cleared after Status<br>Register is read.                           |

| b3  | DELAYED STEERING                               | Set upon the valid<br>detection of the absence<br>of a DTMF signal.        | Cleared upon the<br>detection of a valid<br>DTMF signal.            |

**Table 3.6**Status register bit description.

Table 3.7Functional Encode/Decode Table.

•

| LOW   | HIGH  | DIGIT | D3 | D2 | D1 | D0 |

|-------|-------|-------|----|----|----|----|

| FREQ. | FREQ. |       |    |    |    |    |

| 697   | 1209  | 1     | 0  | 0  | 0  | 1  |

| 697   | 1336  | 2     | 0  | 0  | 1  | 0  |

| 697   | 1477  | 3     | 0  | 0  | 1  | 1  |

| 770   | 1209  | 4     | 0  | 1  | 0  | 0  |

| 770   | 1336  | 5     | 0  | 1  | 0  | 1  |

| 770   | 1477  | 6     | 0  | 1  | 1  | 0  |

| 852   | 1209  | 7     | 0  | 1  | 1  | 1  |

| 852   | 1336  | 8     | 1  | 0  | 0  | 0  |

| 852   | 1477  | 9     | 1  | 0  | 0  | 1  |

| 941   | 1336  | 0     | 1  | 0  | 1  | 0  |

| 941   | 1209  | *     | 1  | 0  | 1  | 1  |

| 941   | 1477  | #     | 1  | 1  | 0  | 0  |

| 697   | 1633  | A     | 1  | 1  | 0  | 1  |

| 770   | 1633  | В     | 1  | 1  | 1  | 0  |

| 852   | 1633  | С     | 1  | 1  | 1  | 1  |

| 941   | 1633  | D     | 0  | 0  | 0  | 0  |

.

high group (HIGH FREQ.) tones. Typically, the high group to low group amplitude ratio is 2dB to compensate for high group attenuation on long loops.

In certain telephony applications it is required that DTMF signals generated are of a specific duration determined either by the particular application or by any one of the exchange transmitter specification currently existing. Standard DTMF signal timing can be accomplished by making use of the burst mode. The transmitter is capable of issuing symmetric bursts/pauses of predetermined duration. This burst/pause duration is 51 ms±1 ms, which is a standard interval for auto-dialer and central office applications. After the burst/pause duration expires the appropriate bit is set in the Status Register which indicates that the transmitter is ready for more data. The timing described above is available when the DTMF mode is selected in Control Register A (CRA).

The MT8888C is capable of transmitting single tones from either the low or high group. To accomplish this bit b2 of Control Register B (CRB) must be set to logic 1 and the device must be in DTMF mode.

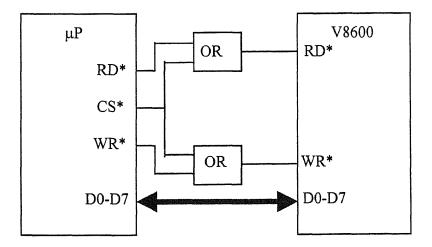

The MT8888C incorporates an Intel microprocessor interface that is compatible with a 16 MHz 80C51 microcontroller. However, this device was interfaced to the Motorola MC68HC11 in which additional logic had to be use for RD\* and WR\* signaling. The MC68HC11 microcontroller has only one pin for both the read and write signals in which a high indicates a read and a low for write. The MT8888C however has two pins, one for read and the other for write. Hence the use of addition logic. This chip was used due to availability. The DTMF chip for the MC68HC11 is the MT8880C.

The microprocessor interface of the MT8888C provides access to five internal registers. The read-only Receive Data Register contains the decoded output of the last valid DTMF digit received. Data entered into the write-only Transmit Data Register will determine which tone pair will be transmitted. Transceiver control is accomplished with two control registers – CRA and CRB – which have the same address. CRB can be accessed only when a logic 1 is written to bit b3 of CRA. The following control register write will be to CRB. The third control register write will be to CRA again. If CRB needs to be accessed again then a logic 1 must be written to b3 of CRA again. Table 3.8 shows the logic levels on the control pins to access the registers. These control levels must accompany a logic 0 on pin CS\*.

**Table 3.8**Control logic to access registers.

| RS0 | WR* | RD* | FUNCTION                        |  |

|-----|-----|-----|---------------------------------|--|

| 0   | 0   | 1   | Write to Transmit Data Register |  |

| 0   | 1   | 0   | Read from Receive Data Register |  |

| 1   | 0   | 1   | Write to Control Register       |  |

| 1   | 1   | 0   | Read from Status Register       |  |

A software reset must be included at the beginning of the program to initialize the control registers after power-up. The initialization procedure should be executed 100 ms after power-up. The initialization process must follow the sequence below [1]:

|                              | RS0 | WR* | RD* | D3 | D2 | D1 | D0 |

|------------------------------|-----|-----|-----|----|----|----|----|

| 1. Read Status Register      | 1   | 1   | 0   | Х  | Х  | Х  | х  |

| 2. Write to Control Register | 1   | 0   | 1   | 0  | 0  | 0  | 0  |

| 3. | Write to Control Register | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

|----|---------------------------|---|---|---|---|---|---|---|

| 4. | Write to Control Register | 1 | 0 | 1 | 1 | 0 | 0 | 0 |

| 5. | Write to Control Register | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

| 6. | Read Status Register      | 1 | 1 | 0 | Х | Х | Х | Х |

After this initialization sequence the control registers can be configured according to the users choice of operation. The following sequence was used to configure the control registers of the Controller:

|    |                             | RS0     | WR* | RD* | D3 | D2 | D1 | D0 |

|----|-----------------------------|---------|-----|-----|----|----|----|----|

| 1. | Write to Control Register A | 1       | 1   | 0   | Х  | Х  | Х  | Х  |

|    | (tone out, DTMF, IRQ*, Sele | ect CRI | B)  |     |    |    |    |    |

| 2. | Write to Control Register B | 1       | 0   | 1   | 0  | 0  | 0  | 0  |

|    | (burst mode)                |         |     |     |    |    |    |    |

The tone out, IRQ\* and burst mode were not needed for the Controller since it only operated in the receive mode.

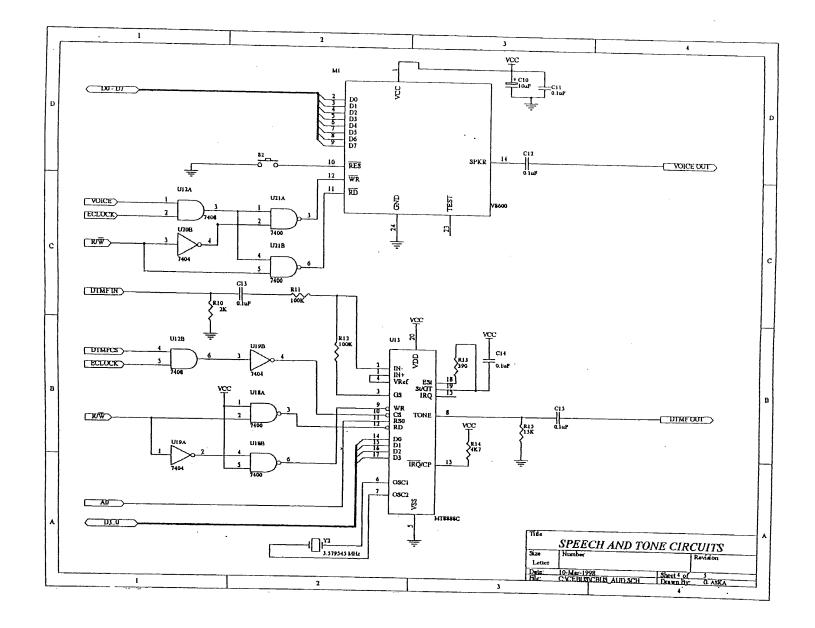

### 3.5 Voice Module

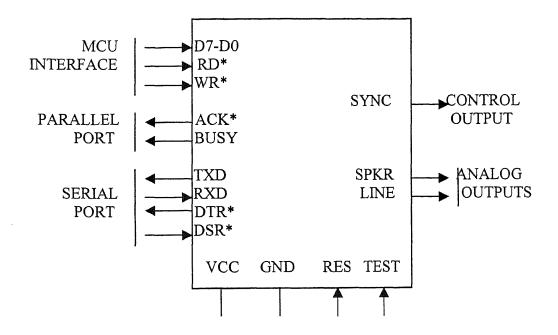

The V8600 Speech Synthesizer, developed by RC Systems was used for the voice prompts and responses of the Controller. It has the capability to convert ASCII text into a high quality male voice. However the module can be programmed for a female voice if the programmer so desires. Figure 3.14 shows the logic symbol of the V8600. It consist

of a  $131,072 \times 8$  ROM which contains the text to speech algorithms. The V8600 supports 524,288 bytes of ROM for storing customization programs such as pre-recorded PCMencoded speech. An  $8,192 \times 8$  RAM provides storage for the exception dictionary, a 4K FIFO buffer for the DAC (Digital to Analog Converter) and tone generators, and the input text/command buffer. The input buffer and the exception dictionary share approximately 2600 bytes of the RAM.

Figure 3.14 V8600 logic symbol.

The module supports three types of interfaces namely, microprocessor, parallel and serial. An example of each interface is shown in Figures 3.16, 3.17 and 3.18 respectively. The microprocessor's read and write signals control the data direction between the microprocessor and the V8600. The CS\* signal can be derived from an address decoder. In the microprocessor configuration, the host processor can read the V8600 status flags. The bit definitions of the status byte are shown in Figure 3.15. When the SYNC bit is set to 1 the synthesizer is either talking or sending out data from the tone generator. It goes to 0 immediately after output ceases. SYNC2 is similar to SYNC but drops to 0 up to 0.5 seconds earlier. The RDY (Ready) is set to 1 when the V8600 is ready to accept data. AF (Almost Full) is set to 1 when less than 300 bytes are available in the text/command input buffer. AE (Almost Empty) is set to 1 when less than 300 bytes are occupied in the text/command input buffer

| 0 | SYNC | SYNC2 | RDY | AF | AE | 0 | 0 |

|---|------|-------|-----|----|----|---|---|

|   |      |       | · . |    |    |   | L |

Figure 3.15 V8600 status flags.

Figure 3.16 Microprocessor interface example

In the printer port example, the STB\* output from the computer's parallel printer port connects directly to the V8600's WR\* pin. The V8600's ACK\* and busy outputs

Figure 3.17 Parallel Printer Port interface example.

Figure 3.18 RS-232 Serial interface example

serve as handshaking signals with the port. In most cases it is not necessary to utilize both The V8600's asynchronous serial port provides the means to operate with a handshaking signals as they essentially convey the same information. In this configuration, the host computer simply prints the text to be spoken to the V8600 remote computer's communications port. The port operates with 8 data bits, one or more stop bits and no parity. Baud rate selection is automatic. The V8600 currently does not use the TXD or DSR pins for any purpose, and may be left unconnected. In this configuration, the host computer simply prints the text to be spoken to the V8600. Because the V8600's serial port I/O pins operate at TTL levels, the addition of (at most) two RS-232 line drivers and receivers are necessary

The baud rate of the serial port is determined automatically from the first character received on the RXD pin which is usually CR (0Dh). Since this is done by measuring the duration of the start bit, the first data bit (D0) must be a logic 1 for proper detection of the end of start bit. The first character is then discarded. The baud rate is reset only when the V8600 is reset.

The V8600 has four addressing modes namely Text, Character, Phoneme and PCM. The modes can be changed at any time, even within the same string of text. In the Text mode all text sent to the V8600 is spoken as complete sentences. Punctuation is also taken into consideration by the intonation generation algorithms. The V8600 will not begin translating text until it receives a CR (0Dh) or Null (00h) character -- this ensures that sentence boundaries receive the proper inflection.

The Character mode causes the V8600 to translate input text on a character-bycharacter basis. In other words text are spelt instead of spoken as words. The V8600 does not wait for a CR/Null in this mode.

The Phoneme mode is useful for creating customized speech, when the normal text-to-speech (Text) mode is inappropriate for producing the desired voice effect. Phoneme mode is used when it is important for the correct stress and emphasis be placed

on certain words in a phrase. This detailed modification is not possible with text mode since changes are only allowed at word boundaries whereas phoneme mode allows changes within words. Table 3.9 lists the phonemes that can be produced by the V8600 and Table 3.10 lists the attribute tokens. For example in text mode a sentence, in C language, would be sent to the V8600 as follows:

printf("How dare you speak to me like that way!");

In phoneme mode the same sentence could sent as shown below:

prinf("70H AW -/D>/EH R +<//YY UW S P/IY K T UW /M IY DH AE T -/W EY .+/");

| Phoneme | Example  | Phoneme | Example      | Phoneme | Example    |

|---------|----------|---------|--------------|---------|------------|

| Symbol  | Word     | Symbol  | Word         | Symbol  | Word       |

| AA      | father   | H       | hire         | SH      | Dish       |

| AE      | bat      | IH      | sit          | Т       | Tip        |

| AH      | cut      | IX      | relative     | TH      | Thick      |

| AO      | lawn     | IY      | meet         | TX      | Mistake    |

| AW      | cow      | ЛН      | jet          | UH      | Pull       |

| AX      | about    | K       | cute         | UW      | Tool       |

| AY      | kite     | KX      | s <b>k</b> i | V       | Give       |

| В       | bird     | L       | long         | W       | Went       |

| СН      | cheese   | М       | mug          | WH      | When       |

| D       | dare     | Ν       | new          | YY      | You        |

| DH      | either   | NX      | ru <b>ng</b> | Z       | Zero       |

| DX      | computer | OW      | tone         | ZH      | Leisure    |

| EH      | set      | OY      | boy          | space   | variable   |

| ER      | were     | Р       | past         |         | pause      |

| EY      | bake     | PX      | spot         | ,       | medium     |

| F       | fact     | R       | ring         |         | pause      |

| G       | give     | S       | some         |         | long pause |

#### Table 3.9Synthesizer Phonemes

| Symbol | Function                   |

|--------|----------------------------|

| nn     | Set pitch to 'nn' (0 – 99) |

| · /    | Increase pitch 10 steps    |

| \      | Decrease pitch 10 steps    |

| +      | Increase speed 1 step      |

| -      | Decrease speed 1 step      |

| >      | Increase volume 1 step     |

| <      | Decrease volume 1 step     |

**Table 3.10**Phonome Attribute Tokens.

In PCM mode data sent to the V8600 is written to the digital to analog converter FIFO buffer. The results in a very high data rate, and provides the capability to produce the highest quality speech. This mode also provides sound effects that are not possible in the text mode.

The V8600 interprets a list of commands that are used to change the synthesizer's attributes, such as volume or pitch. A list of these commands is shown in Table 3.11.

The output of the V8600 (SPKR pin) was connected to the DAA so that the audio could travel along the telephone line to the user. A resistor was connected between the V8600 and the DAA as recommended by the manufacturer. A  $0.1\mu$ F capacitor blocked the 2.5V on the VR pin from reaching the V8600. A logic circuit connected to WR\* and RD\* provides selection of the Speech Synthesizer only when its address was specified on the address bus. This logic was necessary since the V8600 does not have a chip select pin [18].

| Command | Function                    | Range n | Default |

|---------|-----------------------------|---------|---------|

| NB      | Punctuation level           | 0 - 7   | 6       |

| NC      | Character mode/delay        | 0 - 31  |         |

| D       | Phoneme mode                | -       |         |

| E       | Enable intonation           | -       |         |

| NF      | Format frequency            | 0-9     |         |

| J       | Tone generator              | -       |         |

| L       | Load exception dictionary   | -       |         |

| M       | Disable intonation          | -       |         |

| NP      | Pitch                       | 0 - 99  |         |

| R       | Clear                       | -       |         |

| NS      | Speed                       | 0 - 9   |         |

| NT      | Text mode/delay             | 0 - 15  |         |

| U       | Enable exception dictionary | -       |         |

| NV      | Volume                      | 0 - 9   |         |

| NX      | Tone                        | 0 - 1   |         |

| NY      | Timeout delay               | 0 - 15  |         |

| Z       | Zap command                 | -       |         |

| @       | Reinitialize                | -       |         |

| n#      | PCM mode                    | 0 - 99  |         |

Table 3.11V8600 command summary.

#### CHAPTER 4

### SOFTWARE IMPLEMENTAION

This chapter contains all the relevant information pertaining to the development of the software for the Controller. This includes the development software configuration for the banked memory mode which was used to allow the 16-bit address lines of MC68HC11 microcontroller access 128 bytes of memory. The structure of the device application program that allows the proper operation of the Controller in relation to CEBus internal function is described in section 4.2. Also included is the configuration of the CEBench software to allow correct interfacing of software and hardware for communication over the power line.

### 4.1 Bank Memory Implementation

The file cstartup.s07 contains the routine to configure the hardware after a power-up or manual reset. The user to comply with the current hardware design can modify this file. One important area of configuration is to allow memory to operate in banked memory mode. As mentioned earlier this allow the MC68HC11 microcontroller which has 16 address lines (with address space of 64Kbytes) to access 128Kbytes of memory. When the banked memory compiler option is selected the designer must assign a memory location to store the bank number. This assignment should be made in both the cstartup.s07 and 109.s07 configuration files. The location 1060H was used for this memory location as shown below in the cstartup.s07 file:

IOPORT EQU \$1060

42

### CLR IOPORT

The foregoing instruction switches the bank to bank 0. The 109.s07 file was modified to include the following assembly code :

| IOPORT | EQU  | \$1060 |

|--------|------|--------|

|        | LDAA | IOPORT |

|        | PSHA |        |

|        |      |        |

|        |      |        |

|        |      |        |

|        | STAA | IOPORT |

|        | PULA |        |

|        | STAA | IOPORT |

The second instruction loads the current bank number into the accumulator. The second stores this number on the stack. After obtaining the new bank number from the X register it is stored in location 1060H (third to last instruction). After the program, in the selected bank, has executed the old bank number is pull of the stack then stored in location 1060H (second to last and last instructions).

The Altera PLD is responsible for putting the bank number onto the memory address lines. Figure 4.1 shows a copy of the bank-switching program used in the Altera. The Altera chip outputs the bank number to the memory chip when the instruction

is executed. The bank number to the memory chip is determined by the following "if" statement in the Altera PLD:

IF (addr[14]) THEN

bank[2..0] = 7;

# ELSE IF (!addr[14]) THEN

```

TITLE "68HC11 Banked Memory";

```

# Subdesign banked

(

| data[70]           | :bidir;  |

|--------------------|----------|

| addr[15], iocs, rw | :input;  |

| bank[20]           | :output; |

)

```

Variable

```

| bankreg[20] | :dff; |

|-------------|-------|

|             |       |

set, baddr, bnum[7..0] :node;

# BEGIN

baddr = (addr[] == H"1060" & !iocs);

set = baddr & rw;

data0 = tri(bnum0, set);

Figure 4.1 Altera bank memory implementation program (part 1).

data1 = tri(bnum1, set);

data2 = tri(bnum2, set);

data3 = tri(bnum3, set);

data4 = tri(bnum4, set);

data5 = tri(bnum5, set);

data6 = tri(bnum6, set);

data7 = tri(bnum7, set);

bankreg[2..0].d data[2..0];

bankreg[].clk = !(baddr & !rw);

IF (addr[14]) THEN

Bank[2..0] = 7;

ELSEIF (!addr[14]) THEN

Bank[2..0] = bankreg[2..0].q;

END IF;

IF (baddr & rw) THEN

bnum[2..0] = bankreg[2..0];

bnum[7..3] = GND;

END IF;

Figure 4.1 Altera bank memory implementation program (part 2).

When address line 14 is low the content of the bank register determines which bank is selected. If the bank register clock is not activated then the accessed location in memory may be the non-banked location (bank 7) or the current banked location. The non-banked location is always selected when address line 14 is high. The address range of each bank is shown in Figure 4.2 and the memory map showing the addresses used for banked and non-banked memory for the MC68HC11 is shown in Figure 4.3. Figure 4.3 also shows

| 00000H  |            |

|---------|------------|

| AAPPETT | BANK 0     |

| 03FFFH  |            |

| 04000H  |            |

|         | BANK 1     |

| 07FFFH  |            |

| 08000H  |            |

| 0000011 |            |

| 0BFFFH  | BANK 2     |

|         |            |

| 0C000H  |            |

|         | BANK 3     |

| 0FFFFH  |            |

| 10000H  |            |

|         | BANK 4     |

| 13FFFH  | Diddir i   |

| 14000H  |            |

| 1100011 |            |

| 17FFFH  | BANK 5     |

|         |            |

| 18000H  |            |

|         | BANK 6     |

| 1BFFFH  |            |

| 1C000H  |            |

|         | NON-BANKED |

| 1FFFFH  |            |

|         |            |

Figure 4.2 Address range of each bank in memory chip.

the total memory map of the Controller. More will be said about this memory map in the next section. Each bank contains 16kbytes. The total number of bytes on the memory

Figure 4.3 Memory map of Controller (part 2).

chip used for the Controller is 128kbytes. The address range 8000H to BFFFH of the MC68HC11 is used to access the banked portion of memory. Switching to the different banks is done as outlined above. The non-banked area of memory is addressed from C000H to EDFF and F000H to FFFFH of the microcontroller. These addresses are directly mapped to non-banked memory.

### 4.2 Software Development

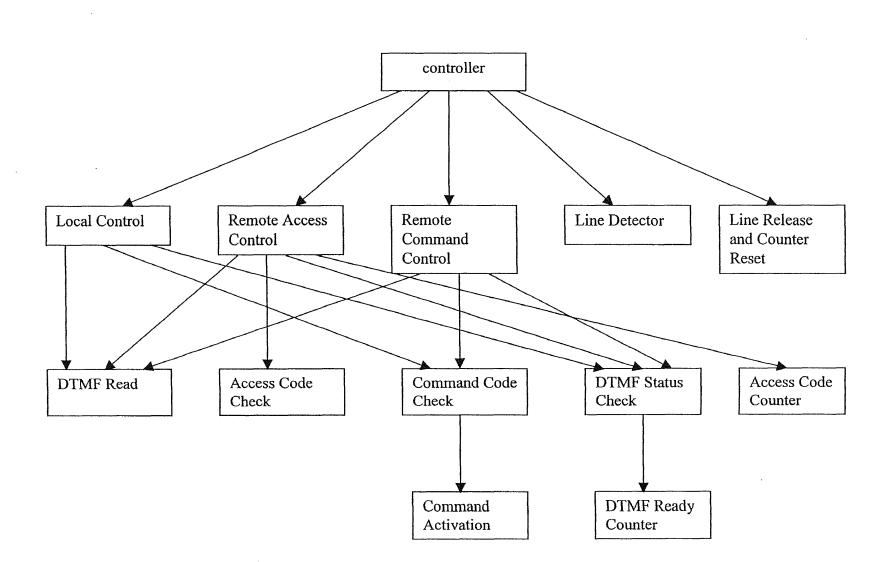

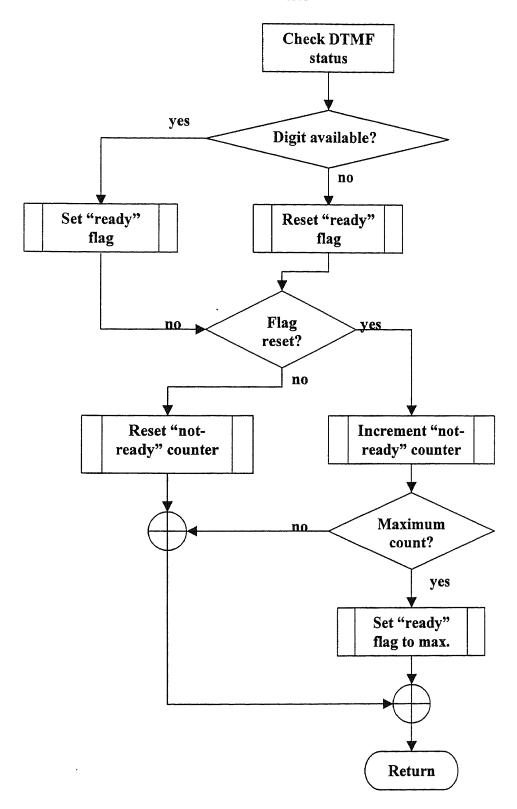

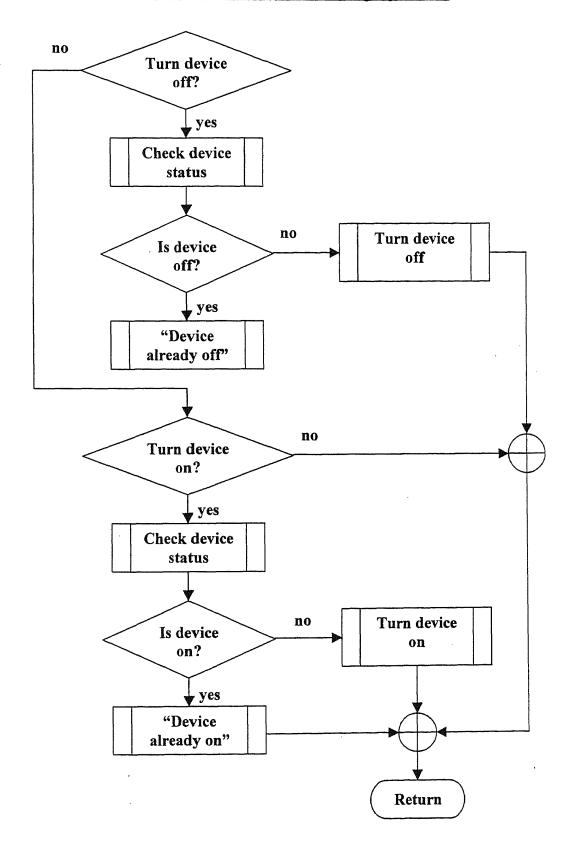

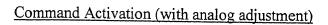

The software program was designed in a hierarchical arrangement to facilitate the limited timing for the program and for ease of debugging. This hierarchical arrangement is shown in Figure 4.4. Lower level modules are controlled by the upper layer modules. However, data may flow from the lower layers to the upper layers as well as from the upper layers to lower layers. Table 4.1 shows the data transfer between the control and controlled modules. So as not to be confused, the controller in the first column of the Table refers to one of the software module and not the entire unit. (We used a capital "c" when referring to the unit and a lower case "c" for the software module.) This first module is called the controller since it determines when the other modules execute. The column list the module that initiates the execution of other modules. The second column lists the called modules. The last column shows the data that the called module returns to the calling module. This data is the result of the module's execution.

Figure 4.3 shows the memory map as seen by the MC68HC11 microcontroller. The MC68HC11 only has 16 address lines and therefore can only address 64kbytes (0000H to FFFFH) of memory. The Controller required much more memory than this to perform all its functions. The memory was therefore increased to 128kbytes (00000H to 1FFFF) using banked addressing mode. The microcontroller's address range 8000H to BFFF was used to address each bank of memory. These addresses provided the offset in each memory bank while the bank selection was done by the Altera PLD, as was outline earlier. The flowcharts for the device-level programs are in Appendix B.

Figure 4.4

Hierarchical arrangement of software program.

50

| Control Module | Data Sent         | Controlled Module | Data Returned       |

|----------------|-------------------|-------------------|---------------------|

| controller     | Void              | Local Control     | 0 = Not finished    |

|                |                   |                   | 1 = Finished        |

| controller     | Void              | Remote Access     | 0 = Not finished    |

|                |                   | Control           | 1 = Finished        |

| controller     | Void              | Remote Command    | 0 = Not finished    |

|                |                   | Control           | 1 = Finished        |

| controller     | Void              | Line Detector     | 0 = Line not active |

|                |                   |                   | 1 = Local access    |

|                |                   |                   | request             |

|                |                   |                   | 2 = Remote access   |

|                |                   |                   | request             |

| controller     | Void              | Line Release and  | Void                |

|                |                   | Counter Reset     |                     |

| Local Control  | Void              | DTMF Read         | Digit               |

| Local Control  | Command code      | Command Code      | 0 = Incorrect       |

|                |                   | Check             | 1 = Correct         |

| Local Control  | Void              | DTMF Status Check | 0 = Not ready       |

|                |                   |                   | 1 = Ready           |

|                |                   |                   | 2 = Not-ready       |

|                |                   |                   | counter at max.     |

| Remote Access  | Void              | DTMF Read         | Digit               |

| Control        |                   |                   |                     |

| Remote Access  | Access code       | Access Code Check | 0 = Incorrect       |

| Control        |                   |                   | 1 = Correct         |

| Remote Access  | Void              | DTMF Status Check | 0 = Not ready       |

| Control        |                   |                   | 1 = Ready           |

|                |                   |                   | 2 = Not-ready       |

|                |                   |                   | counter at max.     |

| Remote Access  | 0 = Reset counter | Access Code       | 0 = Not maximum     |

| Control        | 1 = Increment     | Counter           | count               |

|                | counter           |                   | 1 = Maximum         |

|                |                   |                   | count               |

| Command Code   | Command code      | Command           | 0 = Code out or     |

| Check          |                   | Activation        | range for addressed |

|                |                   |                   | device              |

|                |                   |                   | 1 = Code accepted   |

| DTMF Status    | 0 = Reset counter | DTMF Ready        | 0 = Not maximum     |

| Check          | 1 = Increment     | Counter           | count               |

|                | counter           |                   | 1 = Maximum         |

|                |                   |                   | count               |

# Table 4.1 Data transfer between modules in hierarchical program

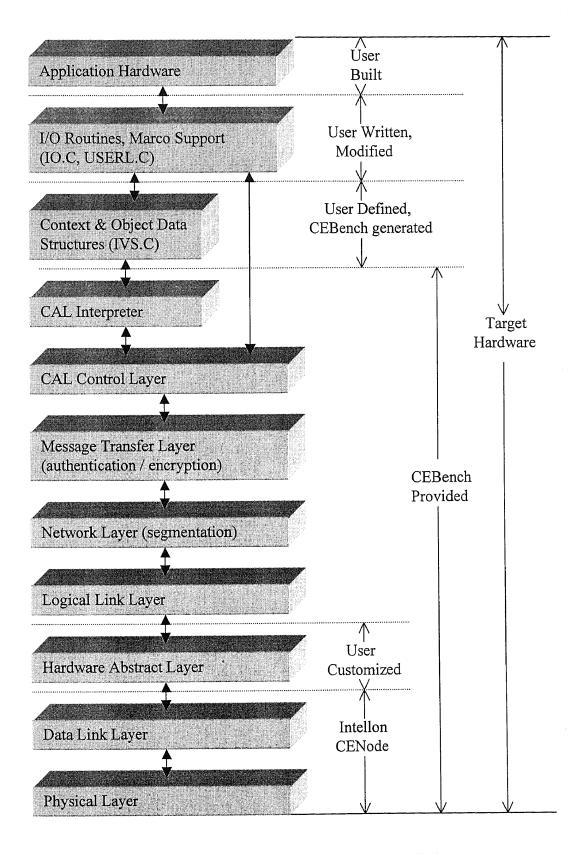

## 4.3 CEBus Message Transfer using CEBench

CEBus message transfers were made possible by configuring the CEBench software to suit the Controller's application. The CEBench software consists of Contexts, Objects and Instance Variables (IVs) that may be written to or read from. They provide the interface, in conjunction with the IO.C source file, between the user written program and the power line hardware. The IO.C was modified to transfer data to and from specified IVs so that CEBus messages could be sent at the appropriate times. Another file that was modified was the HC11HAL.C, used to configure the MC68HC11. Figure 4.5 shows the components of CEBench used to construct a CEBus device. It also specifies the files to be modified by the user and the file that must be developed by the user [2].

### 4.3.1 Layer Definitions

This section defines the layers relevant to the development of a CEBus device from a developer's point of view.

The CAL Control Layer consist of two parts, namely the definition of a data structure that models a products operation and a command syntax that defines the operation of a set of methods on the data structure. The CAL is actually responsible for what products say to each other.

The CAL interpreter is responsible for CEBus message origination and the receiving and parsing of CEBus messages. It is an element of the application layer. It provides services to the application including resource allocation and control functions.

Figure 4.5 CEBench components of CEBus device

The IVS.C file defines the CEBus Contexts, Objects and IVs, their initialization, and their associations to the IO.C source file. It consists of tables generated by CEBench from user specifications. This file must not be modified since the target libraries are written to interface to this file as it is generated by CEBench. Modifying this file may result in incorrect or non-operation of the target executable file.

The IO.C is a template file to be modified by the user. It provides the connection between the Contexts, Objects IVs and the associated target system hardware. This association is implemented by using a series of case statements in which each case number corresponds to a number placed in the I/O column of the Context. When the CEBus execution cycle reaches this I/O number the of the Context the corresponding series of code will execute.

The USERL.C file allows the user to implement customized CEBus functionality. It provides user access to CAL control indications of CEBus functions such as macros, and result messages and also allows user access to the message transfer layer for sending CAL messages [2].

Another important file that is not included in Figure 4.5 is MAIN.C. This file implements the overall target program flow. It is responsible for calling the subroutines to initialize the CON Control, Message Transfer, Network, Logical Link and the Hardware Abstract Layers. After the initialization of these layers it then calls the CEBus executive entry point – CEBus\_Proc(). This in turn initiates the execution of the CON Control, Message Transfer and Network Layers. Since this entry point is in a while loop these layers are repeatedly executed.

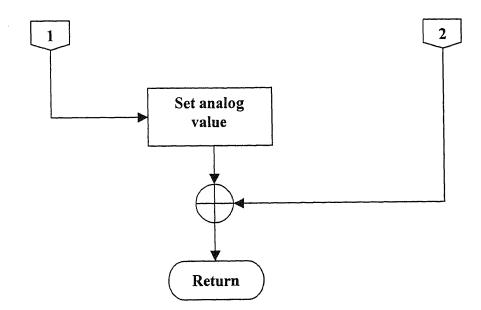

54