## New Jersey Institute of Technology

# Digital Commons @ NJIT

**Theses**

**Electronic Theses and Dissertations**

Summer 8-31-1999

# Study of the effects of deuterium implantation upon the performance of thin-oxide CMOS devices

Sumit Kishore New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/theses

Part of the Chemical Engineering Commons

#### **Recommended Citation**

Kishore, Sumit, "Study of the effects of deuterium implantation upon the performance of thin-oxide CMOS devices" (1999). Theses. 855.

https://digitalcommons.njit.edu/theses/855

This Thesis is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Theses by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

# **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### **ABSTRACT**

# STUDY OF THE EFFECTS OF DEUTERIUM IMPLANTATION UPON THE PERFORMANCE OF THIN-OXIDE CMOS DEVICES

#### by Sumit Kishore

The use of ultra thin oxide films in modern semiconductor devices makes them increasingly susceptible to damage due to the hot carrier damage. Deuterium in place of hydrogen was introduced by ion implantation at the silicon oxide-silicon interface during fabrication to satisfy the dangling bonds. Deuterium was implanted at energies of 15, 25 and 35 keV and at a dose of  $1 \times 10^{14} / \text{cm}^2$ . Some of the wafers were subjected to  $N_2O$  annealing following gate oxide growth. It was demonstrated that ion implantation is an effective means of introduction of deuterium. Deuterium implantation brings about a clear enhancement in gate oxide quality by improving the interface characteristics.  $N_2O$  annealing further improves device performance. A reduction of electron traps with deuterium was also observed. A combination of deuterium implantation at 25 keV and a dose of  $1 \times 10^{15} / \text{cm}^2$ , followed by annealing in  $N_2O$  was observed to have the most positive influence on device behavior.

Concurrently, MEMS microheaters being fabricated for an integrated VOC sensor were also tested for their temperature response to an applied voltage. Different channel configurations and materials for the conducting film were compared and the best pattern for rapid heating was identified. Temperature rises of upto 390 °C were obtained. The temperature responses after coating spin-on glass in the microchannels were also measured.

# STUDY OF THE EFFECTS OF DEUTERIUM IMPLANTATION UPON THE PERFORMANCE OF THIN-OXIDE CMOS DEVICES

by Sumit Kishore

A Thesis

Submitted to the Faculty of

New Jersey Institute of Technology

in Partial Fulfillment of the Requirements for the Degree of

Master of Science in Chemical Engineering

Department of Chemical Engineering, Chemistry and Environmental Science

August 1999

### APROVAL PAGE

# STUDY OF THE EFFECTS OF DEUTERIUM IMPLANTATION UPON THE PERFORMANCE OF THIN-OXIDE CMOS DEVOCES

### Sumit Kishore

| Dr. Durgamadhab Misra, Thesis Advisor<br>Associate Professor,<br>Department of Electrical and Computer Engineering, NJIT |      |  |  |

|--------------------------------------------------------------------------------------------------------------------------|------|--|--|

|                                                                                                                          |      |  |  |

|                                                                                                                          |      |  |  |

|                                                                                                                          |      |  |  |

| Dr. Somenath Mitra, Committee Member                                                                                     | Date |  |  |

| Associate Professor of Chemistry,                                                                                        |      |  |  |

| Department of Electrical and Computer Engineering, NJIT                                                                  |      |  |  |

|                                                                                                                          |      |  |  |

|                                                                                                                          |      |  |  |

|                                                                                                                          |      |  |  |

| Dr. Norman W. Loney, Committee Member                                                                                    | Date |  |  |

| Associate Professor of Chemical Engineering,                                                                             |      |  |  |

| Department of Electrical and Computer Engineering, NJIT                                                                  |      |  |  |

#### **BIOGRAPHICAL SKETCH**

Author:

Sumit Kishore

Degree:

Master of Science

Date:

August 1999

### Undergraduate and Graduate Education:

Master of Science in Chemical Engineering New Jersey Institute of Technology, Newark, New Jersey, 1999

Bachelor of Technology (Honors) in Chemical Engineering, Indian Institute of Technology, Kharagpur, Kharagpur, India 1997

Major:

Chemical Engineering

#### Presentations and Publications:

S. Kishore and D. Misra, "Thin-Gate Oxides Grown on Light Deuterium Implanted Silicon Substrate", *Poster Session, Electrochemical Society 195<sup>th</sup> Meeting*, Seattle, WA, May 1999.

#### **ACKNOWLEDGMENT**

I would like to express my deep sense of gratitude to Dr. Durgamadhab Misra for his constant guidance, support and encouragement throughout the research.

My special thanks to Dr. Somenath Mitra for participating on my thesis committee and for his invaluable assistance regarding this project and otherwise, throughout the duration of this project.

I would like to take this opportunity to extend my sincere gratitude to Dr. Norman W. Loney for serving on my thesis evaluation committee. I would also like to thank Dr. Dentcho Ivanov and Ken O' Brien for assisting me throughout my work in the cleanroom.

Finally, my thanks to Pradnesh, Minhee, Jason, Kevin and Narahari for their invaluable help at various times during the project.

This thesis is dedicated to my parents

## TABLE OF CONTENTS

| Cł | napter                                                         | Page |

|----|----------------------------------------------------------------|------|

| 1  | INTRODUCTION                                                   | 1    |

|    | 1.1 Overview                                                   | 1    |

|    | 1.2 Objective                                                  | 3    |

| 2  | BACKGROUND                                                     | 5    |

|    | 2.1 Overview of CMOS Technology                                | 5    |

|    | 2.2 MOS Capacitors                                             | 7    |

|    | 2.3 Oxide Formation                                            | 7    |

|    | 2.4 Silicon Dioxide-Silicon Interface                          | 8    |

|    | 2.4.1 Hot Electron Effects                                     | 9    |

|    | 2.4.2 Oxide Charges and Traps                                  | 9    |

|    | 2.4.3 Tunneling                                                | 11   |

|    | 2.5 Oxide Characterization                                     | 11   |

|    | 2.6 Literature Review                                          | 14   |

|    | 2.6.1 Damage Characterization                                  | 14   |

|    | 2.6.2 Incorporation of Nitrogen in Oxide and at Interface      | 16   |

|    | 2.6.3 Implantation as a Means of Incorporation of Species      | 17   |

|    | 2.6.4 Substitution of Hydrogen with Deuterium at the Interface | 17   |

|    | 2.7 Motivation for Current Work                                | 19   |

| 3  | FABRICATION                                                    | 20   |

| Chapte | r                                                              | Page |

|--------|----------------------------------------------------------------|------|

| 3      | .1 Introduction                                                | 20   |

| 3      | .2 Outline of the Process Steps for Fabrication                | 20   |

|        | 3.2.1 Process Flow Description                                 | 21   |

|        | 3.2.1.1 Starting.Materials                                     | 21   |

|        | 3.2.1.2 Denuding                                               | 21   |

|        | 3.2.1.3 Sacrificial Oxide Growth                               | 22   |

|        | 3.2.1.4 Deuterium Implantation                                 | 22   |

|        | 3.2.1.5 Sacrificial Oxide Strip                                | 24   |

|        | 3.2.1.6 Gate Oxide Growth                                      | 25   |

|        | 3.2.1.7 Annealing in N <sub>2</sub> O Ambient                  | 26   |

|        | 3.2.1.8 Measurement of Oxide Thickness                         | 27   |

|        | 3.2.1.9 Deposition of Polysilicon                              | 27   |

|        | 3.2.1.10 Implantation of Phosphorus                            | 28   |

|        | 3.2.1.11 Photolithography to Pattern Polysilicon               | 29   |

|        | 3.2.1.12 Etching of Polysilicon                                | 31   |

|        | 3.2.1.13 Photoresist Strip                                     | 32   |

|        | 3.2.2 Flow Chart for Fabrication of the Device                 | 32   |

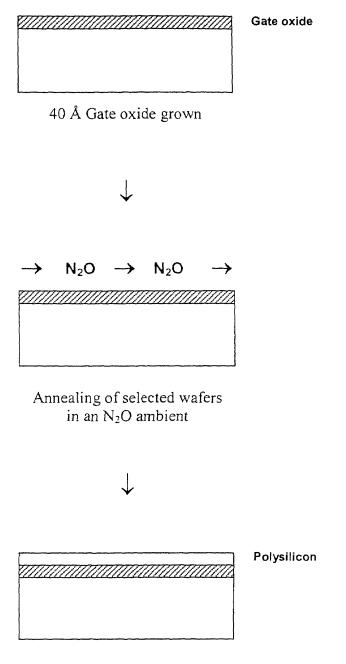

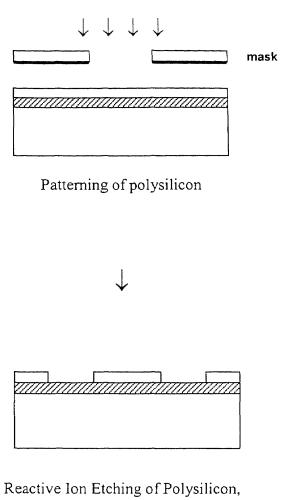

|        | 3.2.3 Schematic Representation of the Device Fabrication Steps | 33   |

| 4 RE   | SULTS AND DISCUSSIONS                                          | 37   |

| 4      | .1 Overview                                                    | 37   |

| Cha | pter |                                        |                           | Page |

|-----|------|----------------------------------------|---------------------------|------|

|     | 4.2  | Methodology                            |                           |      |

|     | 4.3  | Measurements                           |                           | 39   |

|     |      | 4.3.1 Device Breakdown Characteristic  | s                         | 39   |

|     |      | 4.3.2 Leakage Current with and without | t Implantation, Annealing | 41   |

|     |      | 4.3.3 Comparison of Implantation Ener  | gies                      | 42   |

|     |      | 4.3.4 Voltage Stress under Gate and Su | bstrate Injection         | 44   |

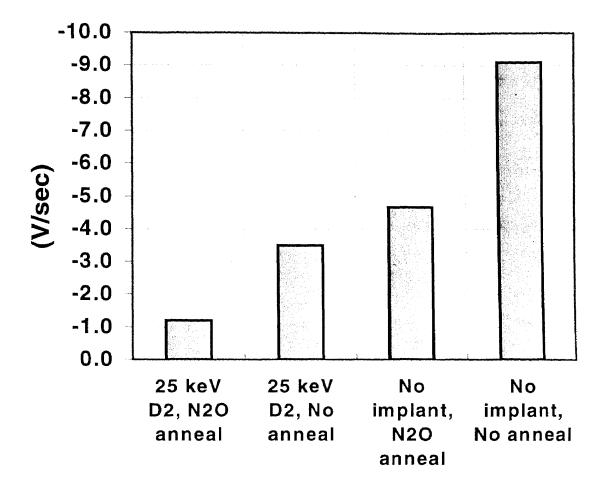

|     |      | 4.3.5 Initial Electron Trapping Slope  |                           | 46   |

| 5   | CON  | CLUSIONS                               |                           | 49   |

|     | 5.1  | Introduction                           |                           | 49   |

|     | 5.2  | Future Scope                           |                           | 50   |

| 6   | REV  | IEW OF MEMS HEATER                     |                           | 51   |

|     | 6.1  | Background                             |                           | 51   |

|     | 6.2  | Introduction                           |                           | 51   |

|     | 6.3  | Objective                              |                           | 53   |

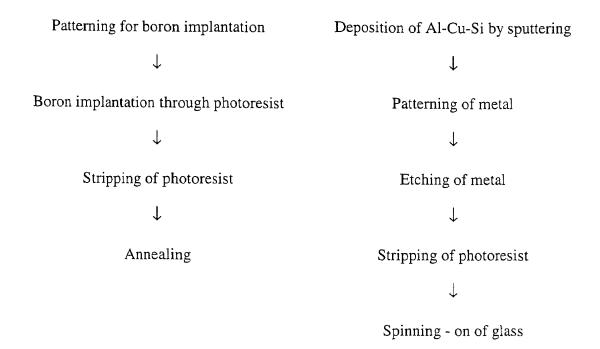

|     | 6.4  | Fabrication                            |                           | 54   |

|     |      | 6.4.1 Process Flow                     |                           | 54   |

|     |      | 6.4.2 Simulations                      |                           | 55   |

|     | 6.5  | Measurements                           |                           | 58   |

|     |      | 6.5.1 Measurement Methodology          |                           | 58   |

|     |      | 6.5.2 Experimental Results             | •••••                     | 60   |

| Cha | pter  |        |            |                                                                                 | Page |

|-----|-------|--------|------------|---------------------------------------------------------------------------------|------|

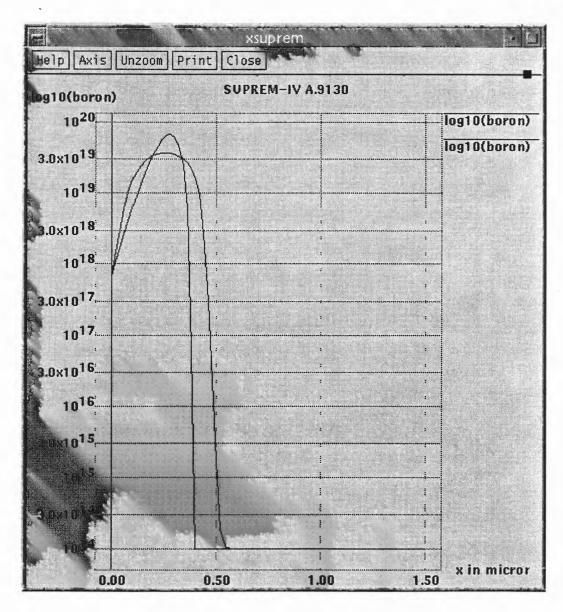

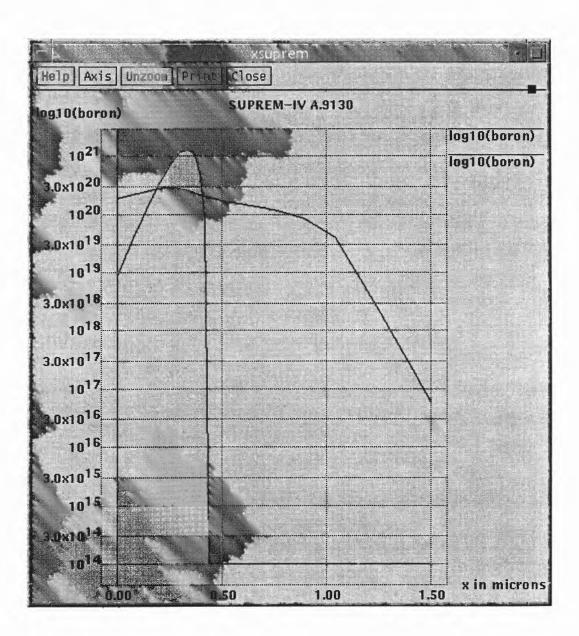

|     |       |        | 6.5.2.1    | Comparison of Boron Implanted and Metal Deposited Microconcentrators            | . 60 |

|     |       |        | 6.5.2.2    | Comparison of Channel Configurations                                            | 61   |

|     |       |        | 6.5.2.3    | Temperature Profile for Metal-deposited Channels with and without Spin-on Glass | 63   |

|     |       | 6.5.3  | Voltage    | Dependence of Temperature Rise                                                  | 64   |

|     |       | 6.5.4  | Resistan   | ice and Power Calculations                                                      | 66   |

|     | 6.6   | Concl  | lusions    |                                                                                 | 68   |

| APF | PENDI | ХА     | LPCVD '    | THEORY AND DEPOSITION CONDITIONS                                                | 70   |

|     | A.1   | LPC    | VD React   | or                                                                              | 70   |

|     | A.2   | Flow   | Chart Sh   | owing Oxide Deposition                                                          | 71   |

| В   | POLY  | /SILIC | CON DEF    | POSITION AND DOPING METHODS                                                     | 73   |

|     | B.1   | Meth   | ods of Po  | lysilicon Deposition                                                            | 73   |

|     | B.2   | Flow   | Chart for  | Polysilicon Deposition                                                          | 74   |

|     | B.3   | Flow   | Chart for  | Polysilicon Doping                                                              | 75   |

| C   | SPUT  | TERI   | NG         |                                                                                 | 76   |

|     | C.1   | Sputt  | ering      |                                                                                 | 76   |

|     | C.2   | Flow   | Chart Sh   | owing the Sputter Deposition Process                                            | 77   |

| D   | PHO   | TOLIT  | HOGRA      | PHY                                                                             | 78   |

|     | D.1   | Intro  | duction    |                                                                                 | 78   |

|     | D.2   | Desc   | ription of | Lithographic Process                                                            | 79   |

| Ch | napter                                    | Page |  |

|----|-------------------------------------------|------|--|

| Е  | E ETCHING                                 |      |  |

|    | E.1 Introduction                          | 81   |  |

|    | E.2 Wet Etching Terminology               | 83   |  |

|    | E.3 Dry Etching.                          | 84   |  |

|    | E.4 Description of the Reactor for RIE    | 86   |  |

| F  | SIMULATIONS                               | 88   |  |

|    | F.1 SRIM Simulations                      | 88   |  |

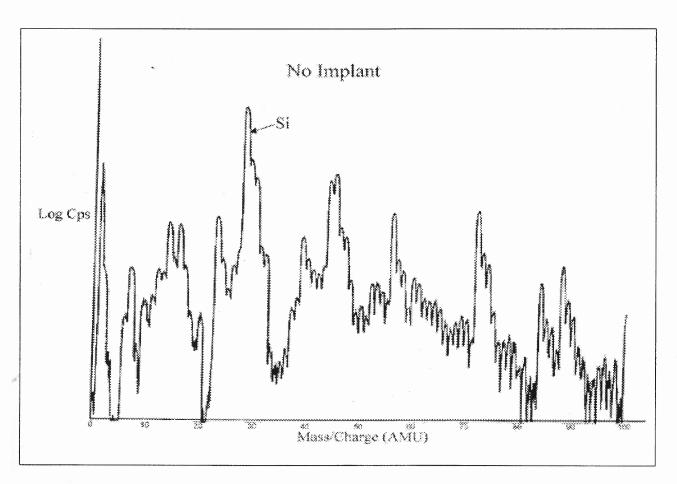

| G  | SIMS Analysis                             | 90   |  |

|    | G.1 SIMS Analysis in Absence of Deuterium | 90   |  |

| RE | EFERENCES                                 | 91   |  |

## LIST OF TABLES

| Table |                                                                       | Page |

|-------|-----------------------------------------------------------------------|------|

| 3.1   | Sacrificial Oxide Growth Conditions                                   | 22   |

| 3.2   | Deuterium Implantation Parameters                                     | 24   |

| 3.3   | Gate Oxide Growth Conditions                                          | 25   |

| 3.4   | N <sub>2</sub> O Anneal Parameters                                    | 26   |

| 3.5   | Wafer Thickness Measurements                                          | 27   |

| 3.6   | Polysilicon Deposition Conditions                                     | 28   |

| 3.7   | Phosphorus Implantation Parameters                                    | 29   |

| 3.8   | Polysilicon Etch Conditions                                           | 31   |

| 4.1   | Fabrication Scheme for the Wafers                                     | 39   |

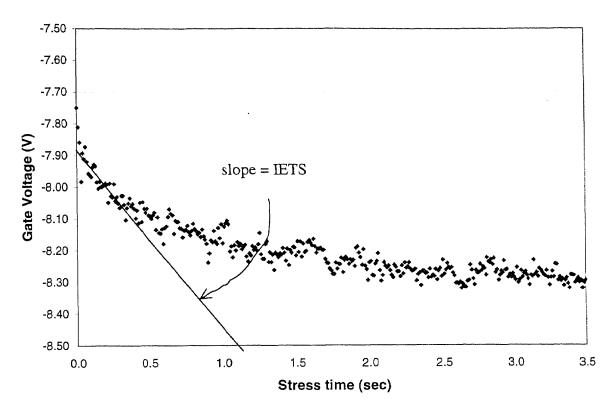

| 4.2   | IETS values for Gate Current Injection on 100 Å Capacitors            | 48   |

| 6.1   | Initial Implantation Schedule                                         | 56   |

| 6.2   | Second Implantation Schedule                                          | 58   |

| 6.3   | Microconcentrator Channel L/W Ratios                                  | 59   |

| 6.4   | Maximum Temperature Rise Measured for All Channels At 40 V            | 61   |

| 6.5   | Maximum Temperature Rise At 40 V with and without Spin-on Glass       | 62   |

| 6.6   | Calculated and Measured Resistances and Power for Individual Channels | 68   |

## LIST OF FIGURES

| Figure |                                                                                                               | Page |

|--------|---------------------------------------------------------------------------------------------------------------|------|

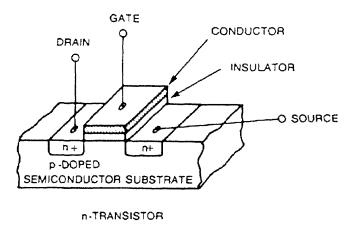

| 2.1    | nMOS Transistor Structure                                                                                     | 6    |

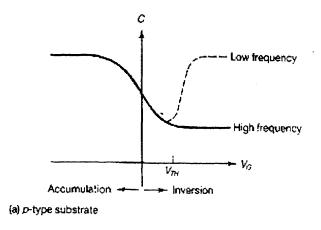

| 2.2    | Ideal C/V curve for p-type MOS capacitor                                                                      | 13   |

| 2.3    | Ideal C/V Curve for n-type MOS Capacitor                                                                      | 13   |

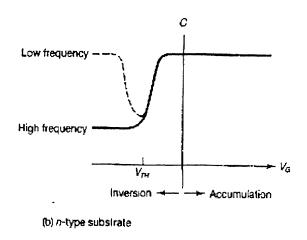

| 2.4    | Effect of a positive oxide charge on the C/V response of a MOS capacitor unit                                 | 14   |

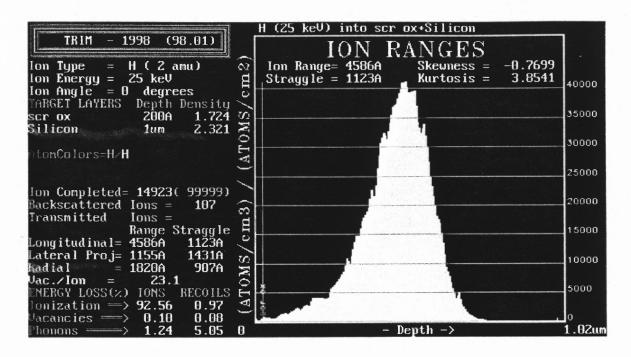

| 3.1    | SRIM simulation of implantation of <sup>2</sup> H <sub>1</sub> at 25 keV, 1x10 <sup>14</sup> /cm <sup>2</sup> | 24   |

| 3.2    | SIMS analysis result for the wafer implanted with $D_2$ at 25 keV, $1 \times 10^{14} / \text{ cm}^2$          | 26   |

| 3.3    | Pattern of Capacitors on wafers                                                                               | 29   |

| 3.4    | Schematic Diagram of Process Fabrication Steps                                                                | 36   |

| 4.1    | Leakage Current Density Characteristics at Breakdown                                                          | 40   |

| 4.2    | Leakage current density vs. gate voltage for wafers with and without implant, annealing.                      | 42   |

| 4.3    | Leakage current density vs. gate voltage for wafers at different implantation energies                        | 43   |

| 4.4    | Time-dependent gate current at constant voltage (5 V) under gate injection                                    | 44   |

| 4.5    | Time-dependent gate current at constant voltage (-5 V) under substrate injection                              | 45   |

| 4.6    | The voltage-time curve for current stress under gate injection with IETS displayed                            | 47   |

| 4.7    | Bar chart of average IETS values for different wafers upon gate Injection                                     | 48   |

| 6.1    | Boron concentration profile in silicon after implantation and annealing                                       | 56   |

# LIST OF FIGURES (Continued)

| Figure |                                                                                                                         | Page |

|--------|-------------------------------------------------------------------------------------------------------------------------|------|

| 6.2    | Boron concentration profile in silicon following implantation and Annealing; alternative implantation regime            | 57   |

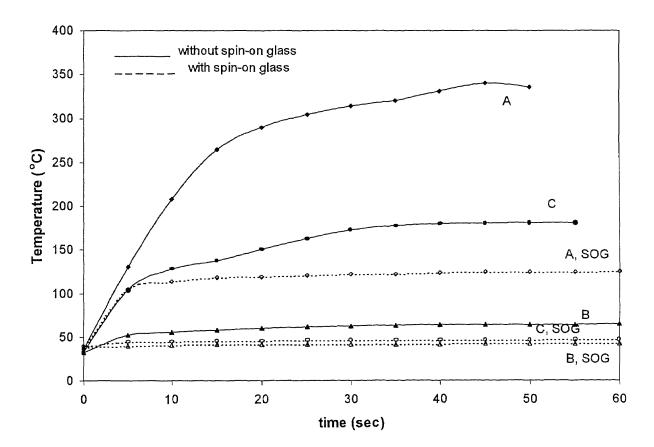

| 6.3    | Initial temperature rise for channels A,B and C with and without Spin-on glass deposition at an applied voltage of 30 V | 63   |

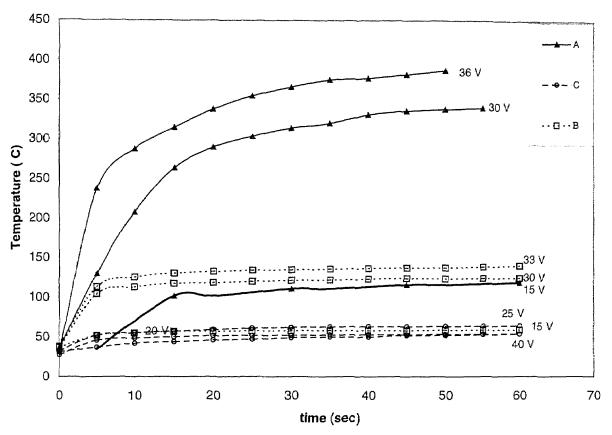

| 6.4    | Initial temperature rise for channels A,B and C without spin-on glass as a function of applied voltage                  | 65   |

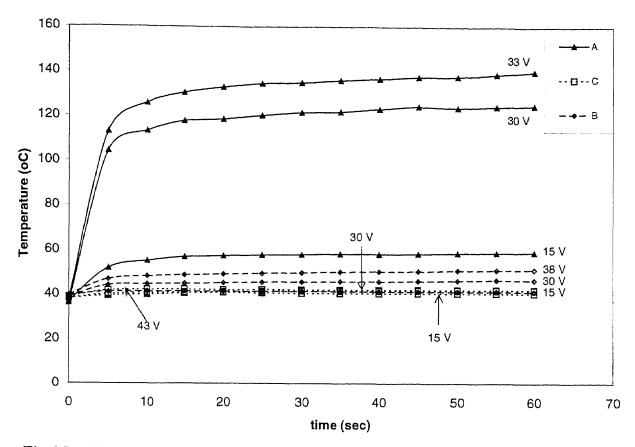

| 6.5    | Initial temperature rise for channels A,B and C with spin-on glass deposited as a function of applied voltage           | 66   |

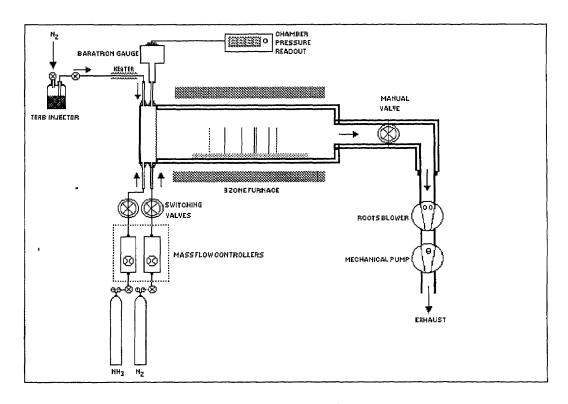

| A.1    | Schematic representation of the LPCVD reactor                                                                           | 70   |

| E.1    | Anisotropic etch profile                                                                                                | 82   |

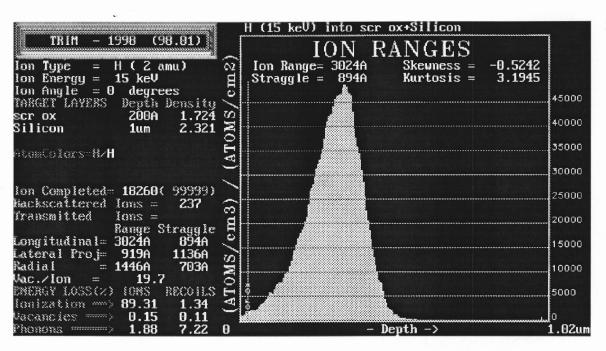

| F.1.1  | SRIM simulation of implantation of <sup>2</sup> H <sub>1</sub> at 15 keV, 1x10 <sup>14</sup> /cm <sup>2</sup>           | 88   |

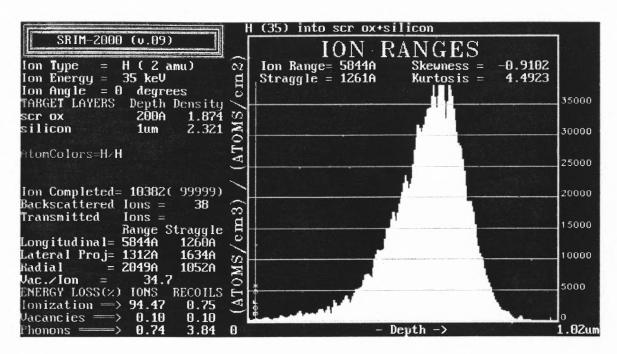

| F.1.2  | SRIM simulation of implantation of <sup>2</sup> H <sub>1</sub> at 35 keV, 1x10 <sup>14</sup> /cm <sup>2</sup>           | 89   |

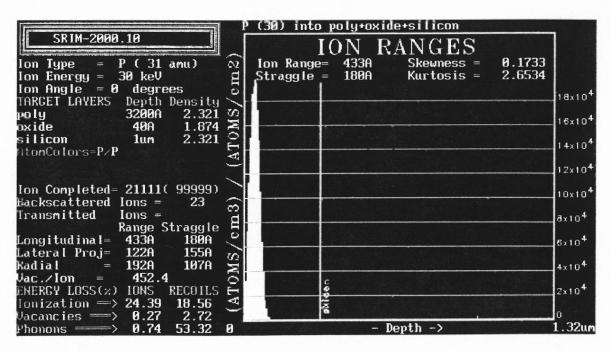

| F.2.1  | SRIM simulation of P <sup>15</sup> implantation of polysilicon at 30 keV, $1x10^{14}$ /cm <sup>2</sup>                  | 89   |

| G.1    | SIMS analysis for wafer with no deuterium implanted                                                                     | 90   |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Overview

The trend in electronics is towards continuous scaling down of semiconductor devices into the submicrometer range. This in turn calls for the use of very thin gate oxides in these devices. For most MOS (Metal Oxide Semiconductor) applications, the primary dielectric is silicon dioxide. The reliability of very thin gate oxides thus becomes an important concern. The smaller thickness of these oxide films results in higher operating fields and larger direct-tunneling currents. Also, very thin oxides have a higher tendency towards anomalous degradation and quasi- to soft breakdown.

The performance and characteristics of MOSFET (MOS Field Effect Transistor) devices, containing an oxide layer as an integral part of the device, are intimately related to the nature of the silicon-silicon oxide interface. This interface represents the transition from the tetrahedral structure of silicon to the polyhedral structure of silicon dioxide. The interface is commonly characterized by a number of dangling bonds, because they represent positions in the silicon lattice where the silicon valencies are unfulfilled. These dangling bonds degrade the performance of the device. There also exist at the interface a number of charged states due to fixed and mobile charges. All of these result in undesirable behavior of thin-gate oxides, particularly under conditions of high current, voltage or temperature stress.

In general, during device fabrication a number of steps are taken to reduce the defects associated with the oxide-silicon interface and the oxide film itself. Commonly, the number of dangling bonds is reduced by annealing the device in a hydrogen ambient, usually forming gas, following oxide growth. The hydrogen atoms diffuse through the silicon dioxide to take up positions in the crystal lattice represented by dangling bonds.

Annealing the devices in a nitrogen ambient also has been observed [1] to reduce the number of fixed and mobile charges associated with the oxide. Heat treatment in a nitrogenous ambient leads to improved stoichiometry at the interface. Nitrogen incorporated in the oxide also serves to act as a barrier against the movement of dopant impurities into the oxide.

Recent studies [2,3,4] have included the investigation of ion implantation as opposed to heat treatment as a method of introduction of nitrogen into the silicon oxide lattice. Implantation offers a better way to introduce low doses of species into the body of the device with greater control over the concentration profile, and does not require the high temperatures required for diffusion. In other studies [5,6,7,8], nitrous oxide  $(N_2O)$  has been used during annealing in place of ammonia.

The use of deuterium [9,10] in place of hydrogen in annealing to reduce the number of dangling bonds has also been the subject of recent study. The larger mass of deuterium compared to hydrogen makes it more difficult to remove it from place under hot electron bombardment. However, it is necessary to anneal the wafers in deuterium ambient for hours to see any significant result in integrated circuits with multilevel dielectric/metallization layers [10]. This happens because deuterium is heavier than

hydrogen and the shadowing effect of multilevel metallization can make it really difficult for deuterium to reach the gate-oxide/silicon interface.

#### 1.2 Objective

This thesis seeks to investigate the characteristics of thin gate oxide MOS devices with oxide grown on the silicon substrate upon implantation of deuterium into the substrate, in order to observe its effect on device performance and lifetime. The study takes the following novel approaches:

- (a) the use of deuterium to reduce the number of dangling bonds at the silicon dioxidesilicon interface.

- (b) implantation as opposed to annealing as a method of introduction of the deuterium at the interface.

- (c) to combine these studies with the use of an ultra-thin (40 Å) gate oxide.

This thesis deals with the fabrication and testing of thin oxide MOS capacitors to establish the appropriate implantation process for incorporation of deuterium for this purpose.

The aim of this thesis was to fabricate the test structures to evaluate the behavior of thin gate oxides grown on silicon substrate implanted with deuterium. For this purpose, MOS capacitors of varying surface areas were fabricated on lightly doped silicon wafers. Different implantation energies of deuterium were tried out to arrive at the optimum energy level. To compare the results obtained with those resulting from annealing in nitrous oxide, wafers with and without deuterium implanted on them were annealed in

nitrous oxide ambient. A control wafer without deuterium or N<sub>2</sub>O annealing was also prepared.

This and the following chapter present a general idea of MOS devices, the nature of the silicon dioxide-silicon interface and the problems associated with the oxide film in these devices. A literature review is also presented. The third chapter describes in detail the various process steps used in the fabrication of the device. The fourth chapter presents the results obtained from the tests carried out on the wafers. The fifth chapter summarizes the conclusions from the tests. The simulations carried out for the experiment are reported in the appendix.

The process was simulated using SRIM and SUPREM IV. The fabrication was carried out in the cleanroom at the Microelectronics Research Center, NJIT. The device was tested using HP4140 and HP4145B Semiconductor Parameter Analyzer to evaluate device parameters.

This project was carried out simultaneous with another project, involving the fabrication of a MEMS heater as part of a larger project on the construction of semiconductor microsensor for detection of organic molecules, in which the author was an active participant. The final chapter presents the background of and discusses the results obtained for that project.

#### **CHAPTER 2**

#### BACKGROUND

### 2.1 Overview of CMOS Technology

Over the past decade, Metal-Oxide-Semiconductor (MOS) technology has played an increasingly important role in the global integrated circuit industry. This is because of a number of reasons: their self-isolation makes it easy to place devices side-by-side on a chip; they can be made considerably smaller than their bipolar counterparts; they can be made in bulk silicon, thus avoiding costly epitaxial growth; they require lesser process steps and they have lower power dissipation. For a combination of these reasons, MOS technology is a prime candidate for large-scale integration purposes in device fabrication.

Silicon forms the basic starting material for a large class of integrated circuits. A MIS (Metal-Insulator-Semiconductor) structure is created by superimposing several layers of conducting, insulating, and transformer-forming materials to create a sandwich-like structure. These structures are created by a series of chemical processing steps involving oxidation of silicon, introduction of impurities into the silicon to give it certain conduction characteristics, and deposition and etching of aluminum (or other conducting material) on the silicon to provide interconnections. Of the various insulating films used in MIS devices, by far the most important is silicon dioxide, so that the name MOS is extensively used for MIS devices utilizing silicon dioxide as the insulator, and the silicon dioxide is commonly referred to as gate "oxide" only.

After the fabrication steps, the typical MOS structure includes distinct diffusion (doped silicon), polysilicon and aluminum layers, separated by layers of insulating material i.e. oxide.

Physically, a typical MOS transistor consists of regions of heavily doped semiconductor formed in lightly doped semiconductor substrate. The dopant impurities in these regions, called the source and drain respectively, and the substrate are of the opposite types. The source and drain are separated on the surface by the insulating layer. If the substrate is p-doped (excess holes) and the source and drain regions are n-doped (excess electrons), an n-type transistor is formed. With the opposite doping, a p-type transistor results. The structure of an nMOS transistor is shown in Fig. 2.1.

Fig 2.1 nMOS Transistor Structure

A CMOS (Complementary Metal Oxide Semiconductor) transistor is formed by laying an n-type and a p-type transistor side-by-side on the same wafer.

#### 2.2 MOS Capacitors

The core of the MOSFET is the sandwich of metal, silicon dioxide insulator, and silicon semiconductor. This sandwich behaves electrically like a capacitor. While the actual transistor behavior of the MOSFET depends on the channel formed between the source and drain in the semiconductor, and the voltages applied at the gate and the source/drain, the behavior of this metal-oxide-semiconductor sandwich is crucial to the performance and lifetime of the device. For this reason, the MOS capacitor is the subject of much materials research. Accordingly, the current project focussed on the fabrication and testing of MOS capacitors, with the aim of possible extension of results obtained to transistors. As discussed later, a number of tests evaluate and characterize the quality of the oxide in terms of the behavior of this capacitor.

#### 2.3 Oxide Formation

The surface of silicon is covered at all times by a layer of silicon dioxide. This is true even of freshly cleaved silicon, which upon exposure to air gets covered with a few monolayers (≈15-20 Å) of oxide, and gradually thickens with prolonged exposure to an upper limit of about 40 Å. Most silicon microcircuit applications require much thicker oxide films. These oxide films are grown on the wafer by maintaining it in an elevated temperature in an oxidizing ambient, usually dry oxygen or water vapor.

Wet oxidation processes are in general more rapid, but result in relatively lowdensity silicon dioxide films. The use of live steam leads to poor grades of oxides. Hence wet oxidation is usually accomplished by flowing a carrier gas, generally oxygen or an inert, through a water bubbler whose temperature is maintained below the boiling point to prevent its undue depletion.

Oxides grown in dry oxygen are extremely dense, and have a relatively low concentration of traps and interface states. Consequently, gate oxides for MOS-based circuits are exclusively made by this process.

#### 2.4 Silicon Dioxide-Silicon Interface

The exact nature of the  $Si-SiO_2$  interface is not completely understood. A somewhat simplified picture of the interface, formed as a result of thermal oxidation, is a single-crystal silicon followed by a monolayer of  $SiO_x$ , i.e. incompletely oxidized silicon, then a strained region of  $SiO_2$  roughly  $10\sim40$  Å deep, and the remainder stoichiometric, strainfree, amorphous  $SiO_2$ .

In an ideal MOS device the oxide film is assumed to have zero conductance because of the absence of any charge carriers. However, for any practical MOS diode, interface traps and oxide charges will exist at the interface, which will, one way or the other, affect the ideal MOS characteristics. They could cause a shift in the normal transistor characteristics with repeated use, or reduce the lifetime of the device, or begin conducting under conditions of strong electric fields or high currents. Some of the primary defects associated with the oxide film leading to degradation in performance are discussed here. The phenomena which lead to anomalous behavior under stressed conditions are also presented.

#### 2.4.1 Hot Electron Effects

The barrier height at the silicon-silicon dioxide interface is about 3.2 eV, sufficiently low so that electrons or holes, generated in silicon by device action, can occasionally have enough energy to surmount this barrier and get trapped in the silicon dioxide layer. This phenomenon of hot carrier trapping is often encountered in high-field regions.

Hot electron effects result in a change in the breakdown voltage of the device, and also the breakage of some of the satisfied silicon bonds at the silicon surface, further increasing the interface trap density. Hot electron effects are of increasing importance in VLSI because of the use of ultra-thin gate oxides and short channel lengths.

### 2.4.2 Oxide Charges and Traps

These traps and charges can be further classified into

(a) Interface trapped charges: the regular crystal lattice in the silicon bulk is interrupted at the interface with silicon dioxide, as the latter is amorphous. A bare silicon surface carries one unsatisfied charge per atom (1 C/m²). Even with a good oxide film after annealing, this charge remains at about 10<sup>-5</sup> C/m². The atoms at this interface have energy states in the Si forbidden gap and can exchange charges with silicon in short time. These so-called fast states are responsible for both generation and recombination effects at the surface. They give rise to a number of time-varying phenomena.

The number of these interface states is generally reduced by a wet hydrogen anneal of the surface at temperatures of about 450 °C.

- (b) Fixed oxide charge: a layer of charge also exists within the oxide film close to the surface. These are primarily caused by excess silicon ions present within the oxide layer. They are essentially immobile under an applied field.

- (c) Trapped oxide charge: these are defects within the SiO<sub>2</sub> layer that could be created, for example, upon x-radiation or hot-electron injection.

These together represent the slow charge states. They do not enter directly into the electronic process, but do so indirectly by establishing a surface potential, thus reducing the surface carrier mobility and altering the surface conductance.

Slow surface states can be minimized by processing the samples so as to reduce the excess ionic silicon in the oxide. This could be effected by high-temperature oxidation in dry oxygen, or, more commonly, by a relatively lower temperature anneal in a dry nitrogen ambient.

(d) Mobile ionic charge: impurities, notably sodium and potassium, can be present in the oxide as positively charged ions. These are primarily introduced as a result of contamination of the oxidation furnace. They can move about within the oxide film in response to applied voltages, leading to a drift in threshold voltage.

Mobile charges can be minimized by oxidizing in dry oxygen ambient, maintaining ultra-cleanliness during the oxidation process, coating a cover layer of silicon nitride as a barrier to ion transport, and, during gate oxidation, using chlorine bearing species to capture sodium ions.

#### 2.4.3 Tunneling

For ultra-thin oxides or under a very high electric field (10<sup>6</sup> V/m for Si), tunneling will occur. This is a quantum electrical effect, wherein current conduction occurs by band-to-band tunneling process. Oxides with thickness in the range of 20~25 Å are more prone to direct tunneling. Though tunneling is possible at the thickness range used in the present work, it is not likely to be a very significant effect.

#### 2.5 Oxide Characterization

The most useful ways to characterize oxide layers for their suitability to device performance all involve electrical techniques. The simplest measurement is the breakdown voltage. In this test, a capacitor is made by forming a conducting electrode (metal/polysilicon) on top of the oxide. The voltage of the capacitor is increased while the electrical current through the oxide film is measured. At smaller electric fields, the only current is leakage current, which is ordinarily too small to measure. When a sufficiently high electric field (about 12 MV/cm for thermal oxide) has been reached, a current will be detected which will rise exponentially with voltage, signaling an irreversible rupture of the oxide.

Another variant of the simple breakdown tests is the charge-to-breakdown test. In this test, the oxide is stressed to a point just below its breakdown field. The stress could be constant current, constant voltage or ramped current or voltage modes. The current vs. time profile shows an increase in current due to trapping of electrons in the bulk of oxide, until breakdown occurs due to accumulation of trapped positive charge near the interface.

Very thin oxides show little evidence of bulk electron trapping, and very large charge to breakdown values.

More sensitive methods of oxide evaluation use capacitance-voltage measurements. A voltage is applied between the capacitor gate and the substrate and ramped from negative to positive values, while the capacitance of the oxide is measured. The capacitance  $C_{ox}$  is given by

$$C_{ox} = \frac{\varepsilon_o \varepsilon_{ox} \cdot A}{t_{ox}} \tag{2.1}$$

where  $C_{ox}$  = capacitance of oxide film

$\varepsilon_o$  = permittivity of vacuum

$\varepsilon_{ox}$  = dielectric constant of oxide

$t_{ox}$  = thickness of oxide film

A =area of gate.

Ordinarily, for a p-type doped substrate, a negative voltage at the gate draws holes to the Si-SiO<sub>2</sub> interface, resulting in a condition known as accumulation. As the voltage is ramped, the measured capacitance decreases, because the change in sign of the field repels the charge directly beneath the gate. The resulting capacitance of the depletion region is in series with the gate oxide capacitance and effectively increases the overall capacitance.

The capacitor is said to go through the conditions of accumulation, depletion and inversion. Ideal C-V plot for a p-type capacitors is shown in Fig. 2.2.

Fig. 2.2 Ideal C/V curve for p-type MOS capacitor

At high frequencies, the inversion layer carriers can't change their numbers fast enough, and the capacitance is frozen at its minimum value. The profile for an n-type semiconductor, shown in Fig. 2.3, shows the same behavior, except for a change in polarity.

Fig. 2.3 Ideal C/V Curve for n-type MOS Capacitor

The presence of each of fixed oxide charges, mobile ionic charges and interface states, discussed earlier, affects the C-V curve by causing lateral shifts from the ideal curve in characteristic ways, as shown in Fig. (2.4).

Fig. 2.4 Effect of a positive oxide charge on the C/V response of a MOS capacitor.

This in turn changes the threshold voltage at which the MOS transistor turns on. For a net positive oxide charge, the C-V curve shifts to lower values of  $V_g$  and for negative charges, towards higher values of  $V_g$ .

#### 2.6 Literature Review

The investigation of new materials and methodologies to reduce the anomalous effects associated with the oxide film in MOS devices is the subject of a large body of research. This research assumes more significance in light of the increasing use of ultrathin oxide films in such devices as a result of overall miniaturization.

#### 2.6.1 Damage Characterization

B. E. Weir *et al.* [11] have reported that soft breakdown becomes more likely for thinner oxides and for oxides stressed at lower voltages or current densities. The differences between hard and soft breakdowns of oxide are evident from post-stress I-V curves, with hard breakdown resulting in resistive I-V behavior, while gate current still has an exponential dependence on  $V_g$  following soft breakdown. At thicknesses below 20 Å. increase in gate noise becomes only way to observe breakdown. They have estimated

that oxides should undergo hard breakdown at voltages above ~6.5V and soft breakdown below ~5V. In modeling devices with ultra-thin dielectrics, gate noise, which is characteristic of soft breakdown, must be included. Soft breakdown degrades device performance by introduction of noise.

C.T. Liu et al. [12] have related hard and soft breakdowns to charge traps in the oxides. They used oxides from 23-38 Å in thickness, and measured tunneling currents through the gate to characterize the oxide. They found tunneling current to be the predominant charge transport mode at these thicknesses.

Koji Eriguchi and Masaaki Niwa [13] investigated the time-dependent dielectric breakdown of thin gate oxides. They grew gate oxides of thicknesses 40, 60, 100 Å at a temperature of 850 °C. Injected hot electrons break Si-H bonds and liberate H-related species near the interface. The released species diffuse through the oxide and react with precursor defect sites to create traps. The number of hot electrons generated as a function of temperature upon current or voltage stress was found to be dependent on stress polarity. They reported that a gate injection increases the number of hot electrons, while substrate injection diminishes it.

K.P. Cheung et al. [14] used gate leakage current as a measure for damage. Gate leakage current is not dependent on trapped charges. For gate oxides thinner than 50 Å, measurements relying on trapped charges no longer reliably work due to efficient detrapping by tunneling. Most thin oxide damage analysis studies are sensitive to trapped charges. Their data supported the conclusion that charging damage does not decrease with thinner oxide. This is thought to be due to larger charge-to-breakdown for very thin

oxides, as it helps the oxide withstand charging current better. Nowadays the use of highcurrent, low voltage plasma supplies renders oxides more prone to charging damage.

#### 2.6.2 Incorporation of Nitrogen in Oxide and at Interface

Nitrogen is commonly incorporated into the gate oxide to reduce interface state generation and to increase the resistance to dopant diffusion. Traditionally a postoxidation anneal in NH<sub>3</sub> has been used for this purpose. J. Ahn, W. Ting and D.L. Kwong [6] have investigated the use of nitridation during thermal oxidation using N<sub>2</sub>O as a nitriding medium. They reported improved initial performance and enhanced device reliability due to increased resistance to dopant diffusion and reduced interface state generation. Previously, other approaches have involved the rapid thermal oxidation of silicon in N<sub>2</sub>O [7] and rapid thermal nitridation of thermal SiO<sub>2</sub> in an N<sub>2</sub>O ambient [15]. However, rapid thermal processes have been shown [8] to exhibit thickness and compositional non-uniformities. Furnace oxidation produces very uniform N<sub>2</sub>O oxides across the wafer. Not only does this strengthen the oxide structure, but also acts as an oxidant diffusion barrier thus reducing oxidation rate and hence providing superior thickness control in the ultrathin range. Ahn et al. [6] also reported significantly improved resistance to charge trapping and interface state generation under hot-electron stressing. The oxide in their research was grown at 850 °C and nitrided at 950 °C for 20 min, followed by a nitrogen anneal for 5 min. They reported tighter distribution and higher endurance in t<sub>BD</sub> tests, particularly under substrate injection tests. This was probably due to the nitrogen-rich layer near the Si-SiO<sub>2</sub> interface, with nitrogen replacing strained Si-O bonds with Si-N bonds.

G.Q. Lo et al. [16] have reported improved hot-carrier immunity in CMOS devices with  $N_2O$  nitrided oxides. Z.A. Ma et al. [5] showed suppressed boron penetration as a result of  $N_2O$  nitridation.

#### 2.6.3 Implantation as a Means of Incorporation of Species

C.T. Liu *et al.* [3] have discussed implantation of nitrogen before the oxide growth as a method of incorporation into the oxide. They reported an improvement in gate oxide's resistance to plasma-charging damage. Both electron trapping and hole trapping was found to be suppressed effectively. However, their earlier work with higher doses damaged the substrate and created dislocation loops after subsequent thermal cycles. The implanted nitrogen was also found to inhibit oxide growth. In a subsequent paper [4], they reported successful results with nitrogen implanted at low doses of 5x10<sup>13</sup>-5x10<sup>14</sup>/cm<sup>2</sup> and an energy of 25 keV, through a 200 Å screen oxide.

### 2.6.4 Substitution of Hydrogen with Deuterium at the Interface

Low-temperature post-metallization anneals in hydrogen ambients are critical to CMOS fabrication technologies in reducing Si-SiO<sub>2</sub> interface trap charge densities by hydrogen passivation. I.C. Kizilyalli, J.W.Lyding and K. Hess [9] have shown that using deuterium in place of hydrogen improves the hot carrier reliability of NMOS transistors by up to an order of magnitude. This phenomenon was explained in terms of a kinetic isotope effect. Chemical reaction rates involving heavier isotopes are reduced, and consequently, under hot electron stress, bonds to deuterium are more difficult to break than bonds to protium. However, the static chemical binding is evidently the same for both isotopes. Both are

equally effective in reducing interface trap charge densities. Also, transistor function for protium and deuterium post-metal anneal devices are identical. SIMS analysis reveals that at anneal temperatures of 400-450°C, deuterium diffuses more rapidly through oxide to accumulate at the Si-SiO<sub>2</sub> interface.

As per established theory, degradation of MOS performance results from channel hot electrons due to their stimulating the desorption of hydrogen from the Si-SiO<sub>2</sub> interface [18]. Post-metallization anneal at low temperatures improves device function by passivating the otherwise electrically active interface traps, but sets the stage for subsequent hot electron degradation. But the role of reactive hydrogen that actually participates in the interface states and trapped oxide charges has been difficult to quantify because of the difficulty in distinguishing them from the background concentration of chemically stable hydrogen in the oxide. Heungsoo Park and C.R. Helms [10] used deuterium in place of hydrogen for the annealing in order to distinguish it from background hydrogen. They also studied the effect of annealing in N2 and D2 ambient at temperatures from 400-900°C. They showed that in a Si-SiO<sub>2</sub> system, at temperatures of 600 and 800 °C, the implanted deuterium is released from Si-D and Si-OD bonds respectively. Thus the deuterium concentration in silicon decreases with annealing temperature and drops to background levels at about 900 °C. This is an important finding as most thermal oxidation processes are carried out at temperatures in excess of this temperature.

Gale et al. [17] have shown that there was a difference in the kinetics of bulk electron trapping between oxides diffused in H<sub>2</sub>O and D<sub>2</sub>O ambients.

#### 2.7 Motivation for Current Work

As stated in the Objective (Sec. 1.2), the study investigates the use of ion implantation as a means of introduction of the deuterium at the silicon-silicon dioxide interface. While annealing in deuterium ambient has been shown to improve device characteristics, it is not suitable for complex integrated circuits with multilevel interconnections. Implantation also offers a much greater level of control over the precision of placement and dosages, which makes it more suitable for modern devices.

Also, thin gates are increasingly used in modern devices because of the tendency towards increasing miniaturization. The current study uses an oxide thickness (40Å) near the current limit of practical device fabrication. Since these thin-oxide devices are more susceptible to hot electron damage, the use of deuterium and other species in reducing hot electron effects is an important subject of study.

### **CHAPTER 3**

#### FABRICATION

#### 3.1 Introduction

In this chapter the detailed fabrication sequence is presented. The brief process flow is described below. An introduction to the particular process step is detailed in the beginning of each process and the conditions maintained during the fabrication are given following this. All the defects and problems encountered during each of the processing step are discussed at the end of that particular process and the ways in which to overcome these problems are also presented. The process steps, except for ion implantation, were all carried out at the NJIT Microelectronics Research Center. The deuterium implantation was carried out at IICO (Santa Clara, CA), while the polysilicon gate implant was carried out at Ion Implant Services (Sunnyvale, CA). The different deuterium implantation schedules were simulated using the SRIM (Stopping and Range of Ions in Matter) simulation package.

## 3.2 Outline of the Process Steps for Fabrication

An outline of the processing steps that were followed is presented. This includes a detailed description of each of the process steps, including the conditions maintained during the fabrication and a discussion of its significance and problems associated with it. This is followed by a flow chart for the fabrication of the device, and a schematic representation of the fabrication process.

## 3.2.1 Process Flow Description

3.2.1.1 Starting Materials: The starting material for the process was p-type (boron doped), <100> oriented CMOS grade silicon wafers, with a sheet resistivity of 1.25-2.0  $\Omega$ -cm.

3.2.1.2 Denuding: Each wafer was scribed on the back for identification. An oxide layer of approximate thickness 1000 Å was grown by steam oxidation at 950 °C performed for 40 minutes. This oxide layer was subsequently stripped using 6:1 BOE (buffered oxide etch). This step helped in the removal of impurities and contaminants from the wafer surface prior to actual processing.

Impurities can degrade the performance of circuits or even cause failure. This is even truer of very large scale integrated circuits, with extremely small devices operating at low voltages and the thin films used in them. Hence for high yield and device reliability, it becomes imperative to eliminate all possible sources of contamination. Surface cleaning is especially important prior to high temperature processes because impurities react and diffuse at much higher rates at elevated temperatures. Thus a surface cleaning is performed at the beginning and before any furnace processing. The most commonly used wet chemical cleaning technology is based on hot alkaline or acidic peroxide (H<sub>2</sub>O<sub>2</sub>) solutions. These are used to remove chemically bonded films from the wafer surface prior to critical steps. RCA cleans, another commonly used process, are based on a two-step process with the wafer etched in succession in two solutions, SC-1 followed by SC-2. Both these solutions incorporate the strong oxidizing capability of H<sub>2</sub>O<sub>2</sub>. SC-1 is an aqueous alkaline solution which removes organic films, while SC-2 is

an acidic mixture used to remove alkali ions & cations and metallic contaminants. SC-1 is typically a 5:1:1 solution of DI water, "unstabilized" (30%)  $H_2O_2$  and ammonium hydroxide (27%). SC-2 typically consists of a 6:1:1 solution of water,  $H_2O_2$  and hydrochloric acid (37%). The processing temperature is maintained at 80 °C.

**3.2.1.3** Sacrificial Oxide Growth: A thin (~200 Å) oxide was grown on the denuded wafer surface prior to implantation of deuterium. This was needed as implantation typically provides a dopant profile with a peak dopant concentration at a certain depth within the substrate. The use of a sacrificial oxide layer thus helps achieve a peak deuterium concentration near the silicon surface. This not only permits doping the wafer while still keeping its surface passivated, it also allows greater control of the charge at the Si-SiO<sub>2</sub> interface.

The conditions for sacrificial oxide growth were

Table 3.1 Sacrificial Oxide Growth Conditions

| Туре        | Steam Oxidation |

|-------------|-----------------|

| Oxygen      | 7.5 SLM         |

| Bubbler     | 530 scm         |

| Temperature | 1050 °C         |

| Time        | 12 min          |

3.2.1.4 Deuterium Implantation: Low doses of deuterium were implanted through the sacrificial oxide film. Ion implantation is a process in which energetic, charged atoms or

molecules are directly introduced into a single-crystal substrate. It is ordinarily carried out with ion energies in the range 50-500 keV. An ion source, which can be any ionizable compound of the atom, is vaporized and ionized by passing it through a hot or cold electronic discharge. The ions released by electronic bombardment are extracted and fed to an accelerator column. Mass separation processes are used to generate a monoenergetic, highly pure beam of atoms.

Implantation has a number of advantages over diffusion as a means of introducing impurities in semiconductor technology. A very pure beam, free of contamination, of the dopant can be generated. A wide variety of doses, from  $10^{11}$  to  $10^{17}$  can be delivered, and controlled to within  $\pm 1\%$  over this range. The process can be carried out at room temperature. By controlling the energy and dosage of implant, a wide variety of dopant concentration profiles can be obtained. However, implantation is a costly process and results in damage to the crystal structure. A high-temperature anneal can, however, erase most of the damage.

The conditions to be used for the implantation were derived from simulations performed using the SRIM package. The simulation result for implantation carried out at an incident ion energy of 25 keV is presented in Fig. 3.1. From the figure, it is observed that the peak of the as-implanted deuterium concentration distribution is at an approximate depth of 0.5µm within the body of the silicon substrate. The simulation results at the other implantation energies used are presented in Appendix F (Figs. F.1.2, F.1.3). The conditions used for the implantation along with the approximate depth of implantation peak are summarized in Table 3.2.

Fig. 3.1 SRIM simulation of implantation of  ${}^{2}H_{1}$  at 25 keV,  $1x10^{14}/cm^{2}$ .

|   | Tuble 3.2 Deaterrain in | npramati | 011 1 | arameters  |

|---|-------------------------|----------|-------|------------|

|   |                         |          |       |            |

| , | <sup>2</sup> Deuterium. | Denth    | of    | implantati |

Table 3.2 Deuterium Implantation Parameters

| Species | <sup>2</sup> Deuterium <sub>1</sub> | Depth of implantation peak (from SRIM simulation) |

|---------|-------------------------------------|---------------------------------------------------|

| Energy  | 15 keV                              | 0.50 μm                                           |

|         | 25 keV                              | 0.35 μm                                           |

|         | 35 keV.                             | 0.65 μm                                           |

| Dose    | $1 \times 10^{14} / \text{cm}^2$    |                                                   |

# **3.2.1.5 Sacrificial Oxide Strip:** The sacrificial oxide film was stripped using 6:1 BOE.

The process details are the same as for stripping of the denuding oxide.

3.2.1.6 Gate Oxide Growth: The actual thin gate oxide was grown by dry oxidation at 800 °C for 15 minutes. While steam oxidation is generally faster, it is not suitable for the growth of very thin oxide films. Also, dry oxidation results in oxide of higher density and generally better quality with a lower concentration of traps and interface states. For this reason gate oxide is almost exclusively grown by the dry oxidation method. Prior to the oxidation, the furnace was cleaned with a mixture of oxygen and HCl, followed by a nitrogen purge and cool down. This step was necessary to ensure high purity of the gate oxide layer grown. The conditions maintained for the gate oxidation were:

**Table 3.3** Gate Oxide Growth Conditions

| Туре        | Dry Oxidation |

|-------------|---------------|

| Oxygen      | 7.5 SLM       |

| Temperature | 750 °C        |

| Time        | 30 min        |

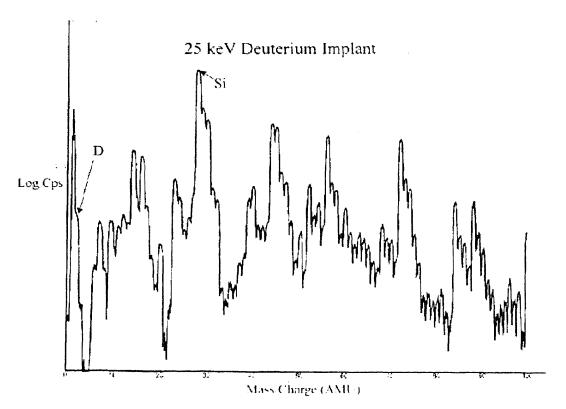

After growing the gate oxide, Secondary Ion Mass Spectrometry (SIMS) analysis was performed on the wafers to establish the presence of deuterium at the interface. The analysis result for the wafer implanted with deuterium at 25 keV, 1 x 10<sup>14</sup> / cm<sup>2</sup> is presented in Fig. 3.2. The peak labeled as "D" indicated by the arrow in the figure corresponds to deuterium. Thus the presence of deuterium in the substrate is borne out by the analysis. The SIMS analysis for the wafer without any deuterium implanted is shown in the appendix, Fig. G.1 and lacks a peak corresponding to deuterium.

Fig. 3.2 SIMS analysis result for the wafer implanted with  $D_2$  at 25 keV,  $1x10^{14}/\,\mathrm{cm}^2$ .

3.2.1.7 Annealing in  $N_2O$  Ambient: Control wafers with and without deuterium implanted on them were annealed in nitrous oxide. The conditions used for the process were:

Table 3.4  $N_2O$  Anneal Parameters

| Species     | N <sub>2</sub> O |

|-------------|------------------|

| Flow Rate   | 7.5 SLM          |

| Temperature | 800 °C           |

| Time        | 24 min           |

3.2.1.8 Measurement of Oxide Thickness: Because of the very low thickness of the oxide film used, it was imperative to minimize the exposure of the wafers with the thin gate oxide to air, as even a short duration exposure would result in the formation of native oxide film on top of the wafer surface. At the low thickness of the gate oxide being used, even a small amount of native oxide could prove sufficient to alter the nature of the oxide film significantly. Accordingly, wafers for oxide thickness measurement were specially marked out and separated at this stage. The thickness was determined by ellipsometry using an Olympus ellipsometer. Ellipsometry is the only reliable method for thickness determination of such thin films. The thicknesses were determined at 12 points on the wafers, which were averaged to arrive at the final thickness. These readings are summarized in Table 3.5.

Table 3.5 Wafer Thickness Measurements

| No. of Wafers      | 5      |

|--------------------|--------|

| Points/wafer       | 12     |

| Mean Thickness     | 42.3 Å |

| Standard Deviation | 5.21 Å |

**3.2.1.9 Deposition of Polysilicon:** The gate oxidation was immediately followed by the deposition of polysilicon. The polysilicon was deposited by LPCVD at 600 °C. The conditions maintained during the process are summarized in this table:

**Table 3.6** Polysilicon Deposition Conditions

| SiH <sub>4</sub> | 300 sccm    |

|------------------|-------------|

| Temperature      | 600 °C      |

| Pressure         | 400 mTorr   |

| Time             | 2 hr 25 min |

**3.2.1.10 Implantation of Phosphorus:** The polysilicon was doped with phosphorus to increase its conductivity. A high implantation dosage and energy, equivalent to a source-and-drain implant, was used.

Undoped polysilicon has a high resistivity of about 500  $\Omega$ -cm, and is essentially self-insulating. Doping with either boron or phosphorus results in a sharp reduction in the resistivity of the polysilicon film, making it conducting. For use as gates in MOS transistors, the polysilicon is heavily doped to form n+ or p+ regions. This can be done by diffusion processes, but for heavy doses ion implantation methods are preferred. The implantation turns the film amorphous, and an annealing step is required to recrystallize the film and for dopant activation.

Implantation was used as the doping method in this study. The conditions to be used for the implantation were arrived at by performing simulations using SRIM. These simulations are presented in Appendix F (Fig. F.2.1). The implantation specifications are summarized in Table 3.7.

Table 3.7 Phosphorus Implantation Parameters

| Species | Phosphorus <sup>15</sup>         | Depth of implantation peak (from SRIM simulation) |

|---------|----------------------------------|---------------------------------------------------|

| Energy  | 30 keV.                          | 0.1 μm                                            |

| Dose    | $1 \times 10^{16} / \text{cm}^2$ |                                                   |

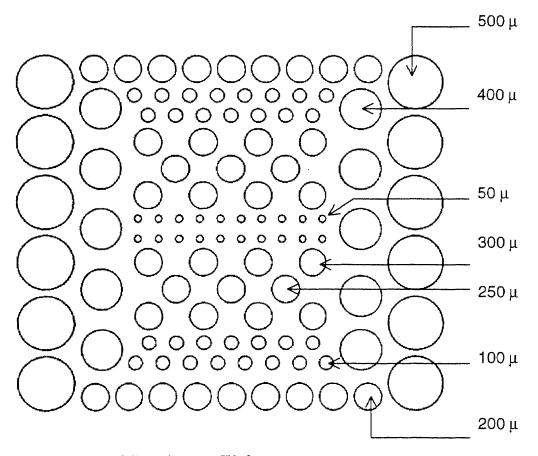

3.2.1.11 Photolithography to Pattern Polysilicon: the mask HMM 3-0520-03 (Device:2  $\mu$ m MOS tester; Layer: Circles) was used to pattern the wafer with a pattern of circular capacitors of diameters ranging from 50 to 500  $\mu$ m. The pattern shown in Fig. 3.3 was repeated throughout the surface of the wafers.

Fig 3.3 Pattern of Capacitors on Wafers

In photolithography, a layer of polymeric photoresist (PR) is applied as a thin film to the substrate and subsequently exposed through a mask. The mask contains clear and opaque features that define the patterns to be created in the PR layer. The areas in the PR exposed to the light are made either soluble (for positive photoresist) or insoluble (for negative photoresist) in a specific solvent known as developer. Negative PR was used in the current thesis. To start with the wafer was primed with a pre-resist coating of a material designed for better photoresist adhesion. The wafers were then ready to be coated with photoresist. Spin coating is the most widely used technique to apply a uniform and adherent film of desired thickness. This procedure was carried out by dispensing the resist solution on the wafer surface, and then rapidly spinning the wafer until the resist was essentially dry. After the wafers were coated with resist, they were subjected to a temperature step, called soft-bake (or pre-bake). This step accomplishes several important purposes, including driving off solvent from the spun-on resist and improving adhesion of the resist. After the wafer had been coated with resist and suitably soft-baked, it was ready to be exposed to some form of radiation in order to create an image on the resist. The degree of exposure was adjusted by controlling the energy impinging on the resist. Following exposure, the resist film was made to undergo development in order to leave behind the image, which would serve as the mask for etching. The wafer was then spindried and transported to the post-bake module. Following development, an inspection was performed. The purpose was to insure that the steps of the PR process up to this point had been performed correctly and to within the specified tolerance. Any inadequately processed wafers detected by this inspection could have their resist stripped and reworked. Post-baking was then performed just prior to etching. Its chief purposes include the removal of residual solvents, improvement of adhesion, and to increase the etch resistance of the resist.

## 3.2.1.12 Etching of Polysilicon:

The polysilicon was etched by using Drytek Phantom etch station.

Etching in microelectronics fabrication is a process by which material is removed from the silicon substrate or from thin films on the substrate surface. When the mask layer is used to protect specific regions of the wafer surface, the goal of etching is to precisely remove the material which is not covered by the mask.

The theory of wet and dry etching is detailed at length in Appendix H.

The conditions used during the etching were

Table 3.8 Polysilicon Etch Conditions

| Туре                      | Phantom Dry Etch |

|---------------------------|------------------|

| Temperature               | 25 ℃             |

| Time                      | 60 sec           |

| Pressure                  | 250 mTorr        |

| SF <sub>6</sub> flow rate | 40 sccm          |

At these conditions, the polysilicon etch rate was 3400 Å/min.

**3.2.1.13 Photoresist Strip:** the remaining photoresist was stripped off using an m-pyrol strip. This is a two-stage process involving immersion into a primary followed by a secondary m-pyrol bath.

## 3.2.2 Flow Chart for Fabrication of the Device

Silicon Wafer

J

Deposition of denuding oxide

1

Stripping of denuding oxide

$\downarrow$

Deposition of sacrificial oxide

1

Ion implantation of deuterium

$\downarrow$

Stripping of sacrificial oxide

$\downarrow$

Deposition of gate oxide

1

Annealing of selected wafers in  $N_2\text{O}$

Measurement of oxide thickness

J

Deposition of polysilicon

J

Source and Drain implantation of phosphorus

$\downarrow$

Drive - in

$\downarrow$

Photolithography to pattern polysilicon

Reactive Ion Etching of polysilicon

J

Stripping of photoresist

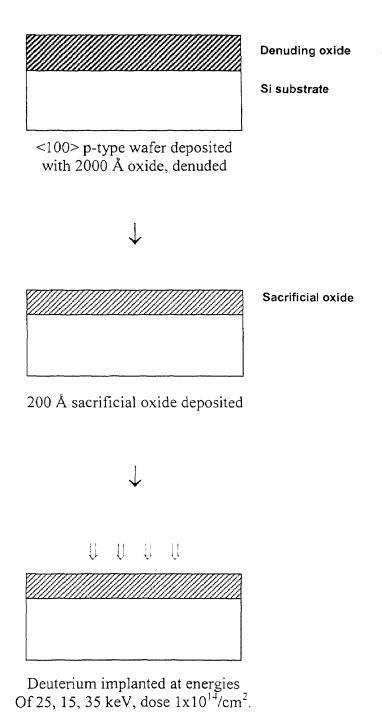

# 3.2.3 Schematic Representation of the Device Fabrication Steps

The cross sections of the wafers at different processing steps are shown schematically by means of cut-away profiles of the devices, along with a brief explanation of the step(s) involved.

Deposition of polysilicon, S-&-D implantation of phosphorus

Photoresist strip

Fig. 3.4 Schematic Diagarm of Process Fabrication Steps

### **CHAPTER 4**

#### RESULTS AND DISCUSSIONS

#### 4.1 Overview

The results from the various tests carried out on the wafers are presented in this chapter.

A discussion of the results is also included.

The capacitors were tested using the HP-4145B Semiconductor Parameter Analyzer. The HP 4145B has four SMUs (Source Monitor Unit), two voltage monitors (V<sub>m</sub>) and two voltage sources (V<sub>s</sub>). Connections are defined according to the device being measured. However, there are certain basic testing programs already defined like the FET, diode, BJT that can be modified as desired.

The HP-4145B Semiconductor Parameter Analyzer is capable of applying a wide range of currents and voltages through each of the SMU channels and measuring the time-varying or voltage- or current-dependent measurements at different points on the wafer. A probe with tip size of about 50  $\mu$ m was used to place the probe on the capacitors.

To carry out the tests, a pattern consisting of circular capacitors of different cross sectional areas was formed on the wafers. The capacitor sizes ranged from 50  $\mu$ m to 500  $\mu$ m. The pattern shown in Fig. 3.3 was repeated over the entire surface of the wafers. The capacitance depends on the cross sectional area as

$$C_o = \left(\frac{\varepsilon}{t}\right) A \tag{4.1}$$

where

$$A = \text{area of gate}$$

= 1.963 x 10<sup>-5</sup> cm<sup>2</sup> to 1.963 x 10<sup>-3</sup> cm<sup>2</sup>

$t = thickness of dielectric \approx 40 Å$

and

$$\varepsilon_{\text{SisO2}}$$

= dielectric constant  $\approx 3.5 \times 10^{-13} \text{ F/cm}$

Using these values, the average unstressed capacitance of the devices works out to be between 17.18 pF (for 50 µm wafers) and 1718 pF (for 500 µm wafers).

# 4.2 Methodology

Based on simulations carried out using SRIM, an implantation energy of 25 keV and a dose of  $1x10^{14}$  atoms/cm<sup>2</sup> was selected. However, implantation was carried out on some wafers at energies above and below this energy to arrive at the optimum value. A total of 11 wafers were processed. Improvements in device performance have earlier been reported upon annealing in N<sub>2</sub>O. To compare results with annealing, some of the implanted wafers were annealed in N<sub>2</sub>O. The scheme for fabrication is given in Table 4.1.

As explained earlier, a silicon surface left exposed to air for even short duration tends to grow a native oxide layer on top of it, or as a thin layer over the previously thermally grown oxide. Native oxide has very undesirable characteristics for MOS devices. In addition, because of the small thickness of gate oxide used, even a small layer of native oxide on the gate could have a significant effect. Hence some wafers were marked out for measurement of the oxide thickness and were separated from the remaining wafers, which were directly processed after growth of the gate oxide.

Table 4.1 Fabrication Scheme for the Wafers.

| Wafer | Implant scheme                                   | Anneal scheme                | Other details                    |

|-------|--------------------------------------------------|------------------------------|----------------------------------|

| 1.    | $25 \text{ keV}, 1 \times 10^{14} / \text{cm}^2$ | Annealed in N <sub>2</sub> O | No gate oxide grown.             |

| 2.    | $25 \text{ keV}, 1 \times 10^{14} / \text{cm}^2$ | Annealed in N <sub>2</sub> O |                                  |

| 3.    | $25 \text{ keV}, 1 \times 10^{14} / \text{cm}^2$ | None                         | Taken for thickness measurements |

| 4.    | 15 keV, 1x10 <sup>14</sup> /cm <sup>2</sup>      | Annealed in N <sub>2</sub> O |                                  |

| 5.    | 15 keV, 1x10 <sup>14</sup> /cm <sup>2</sup>      | None                         | Taken for thickness measurements |

| 6.    | 35 keV, 1x10 <sup>14</sup> /cm <sup>2</sup>      | Annealed in N <sub>2</sub> O |                                  |

| 7.    | 35 keV, 1x10 <sup>14</sup> /cm <sup>2</sup>      | None                         | Taken for thickness measurements |

| 8.    | $35 \text{ keV}, 1 \times 10^{14} / \text{cm}^2$ | None                         |                                  |

| 9.    | None                                             | Annealed in N <sub>2</sub> O |                                  |

| 10.   | None                                             | None                         | Taken for thickness measurements |

| 11.   | None                                             | None                         |                                  |

## 4.3 Measurements

The primary test applied to compare the wafers was the leakage current density through the capacitor gate when a ramped voltage was applied at the gate. This test was repeated at several different locations and different capacitor sizes on the wafers.

# 4.3.1 Device Breakdown Characteristics

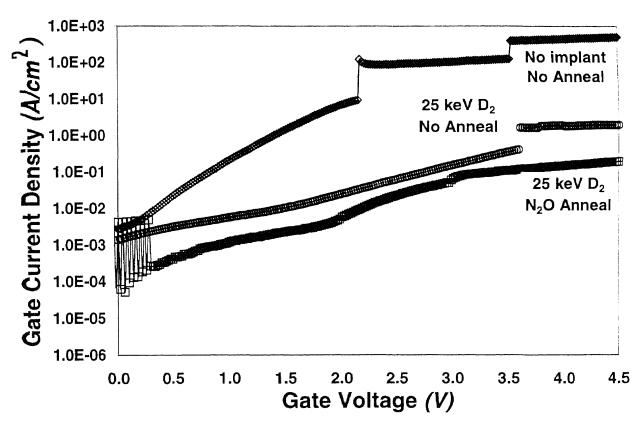

Typical breakdown characteristics of the wafers with and without deuterium implantation and annealing are presented in Fig. 4.1.

The curve for the implanted and annealed wafer shows close to ideal characteristics. The control wafer (without implant and anneal) breaks down earlier than the ones implanted with deuterium.

Breakdown characteristics of devices are an important indicator of device lifetime. A breakdown is characterized by a sharp increase in the current through the oxide and indicates an irreversible damage to the oxide structure. A broken-down device

Fig. 4.1 Leakage Current Density Characteristics at Breakdown.

is rendered unusable. The breakdown performance is generally reported in terms of charge-to-breakdown and time-dependent dielectric breakdown, which are statistically

generated from the breakdown current and potential difference respectively under extended voltage or current stress.

Unfortunately, breakdown could not be consistently observed across all wafers in sufficient numbers to generate statistical data. Most of the device characteristics were indicative of post-stress breakdown, and the leakage current was high for a device of this nature.

At extremely low gate oxide thicknesses, there is a greater tendency for devices to exhibit soft rather than hard breakdown. A soft breakdown is characterized by increase in circuit noise near the point of breakdown and lack of a sharply defined current increase. Thus breakdown becomes more difficult to observe. Fig. 4.1 shows two distinct cases of sharply defined breakdowns. This indicates the lowering of interface trap-enhanced breakdown with deuterium implantation. The lack of other breakdown curves could be attributed to the tendency of the devices to break down by soft mechanisms.

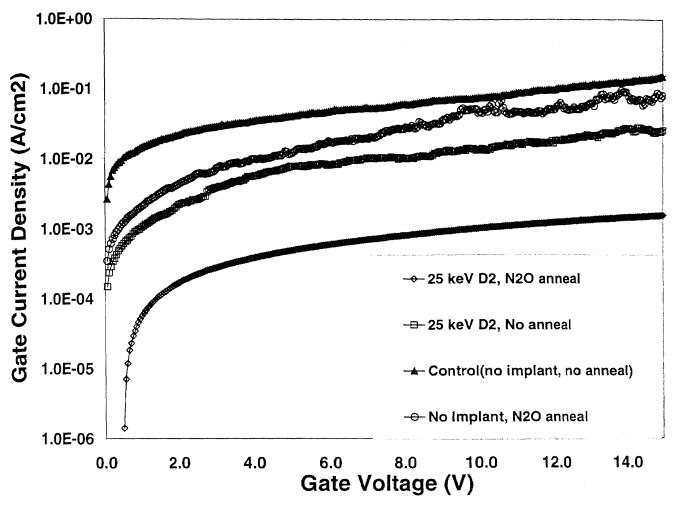

## 4.3.2 Leakage Current with and without Implantation, Annealing

Fig. 4.2 compares the results for the various  $N_2O$  annealed wafers. It is seen that all wafers exhibit some leakage current even at low voltages. This could be attributed to the extremely small thickness of the gate oxide.

The results clearly show that the leakage current is the lowest for devices implanted with deuterium at 25 keV with N<sub>2</sub>O annealing. The wafer shows no appreciable leakage current until at an applied voltage of 3 V, at which point there is a small leakage current. The difference between wafers without implantation, and with implantation but no annealing was not very large, which suggests that a carefully selected

Fig. 4.2 Leakage current density vs. gate voltage for wafers with and without implantation, annealing.

regime of implantation and annealing is the best for improving device performance. The wafers without any implantation or annealing in general showed the worst characteristics.

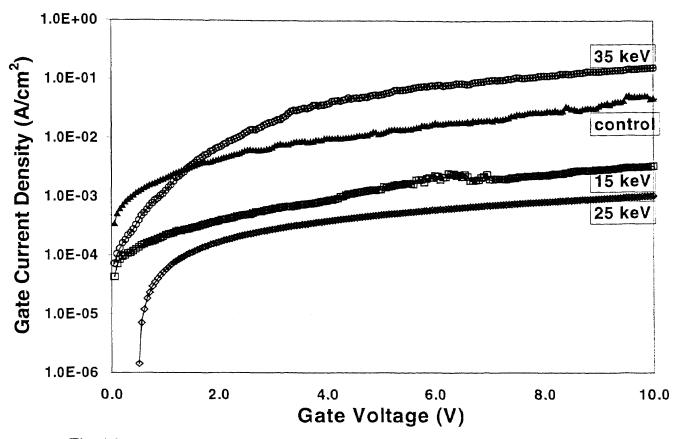

# 4.3.3 Comparison of Implantation Energies

Fig. 4.3 compares the results for the wafers implanted with deuterium at different source energies. The experiments are in agreement with the selected design, as the devices implanted with deuterium at 25 keV show the least leakage current. Wafers implanted

Fig. 4.3: Leakage current density vs. gate voltage for wafers at different implantation energies.

with 15 keV deuterium show slightly worse leakage, while the current is much higher for 35 keV implanted wafer.

Ion implantation typically results in a dopant profile with a peak concentration some depth into the target material. A higher energy of implantation (35 keV) causes amore substrate damage, leading to higher leakage current, that results in a deeper implant peak. On the other hand, a lower energy (15 keV), means that the implant peak is shallow, making the deuterium more susceptible to diffuse out during oxide growth.

A post-implant anneal is commonly used to even out the distribution of implanted ions at the interface, but in this case, because of the risk of outdiffusion of deuterium at

high temperatures, the annealing was limited to the gate oxide growth temperature. The trade-off could be reduced efficiency of redistribution of ions upon annealing.

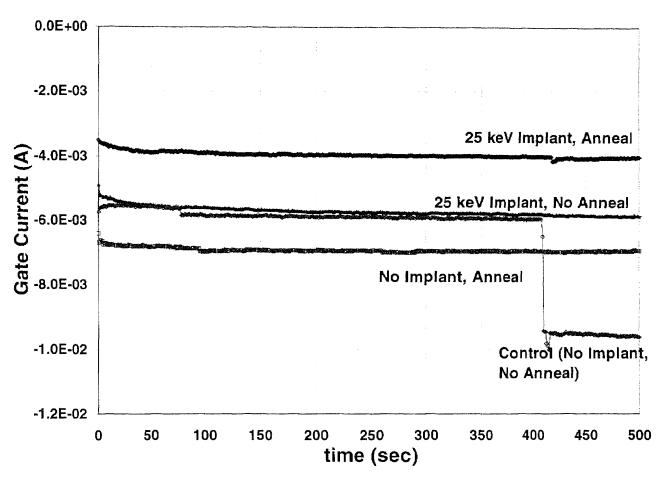

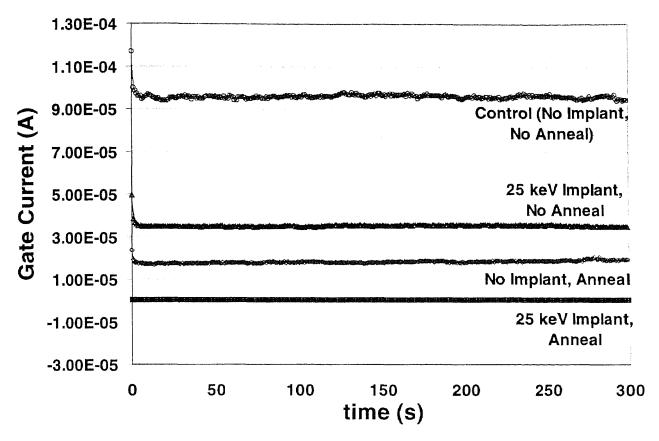

# 4.3.4 Voltage Stress under Gate and Substrate Injection

Fig. 4.4 Time-dependent gate current at constant voltage (5 V) under gate injection.

The time-dependent behavior of the leakage current was measured under Gate Injection i.e. with a positive voltage with respect to the substrate applied to the gate electrode, and under Substrate Injection i.e. with the substrate positive with respect to the gate.

Fig. 4.5 Time-dependent gate current at constant voltage (-5 V) under substrate injection.

A constant voltage stress near the breakdown voltage of the dielectric is applied to the capacitor to get a measure of the stability of the device under continuous voltage stress.

Under conditions of both Substrate injection, shown in Fig. 4.4, and Gate injection, shown in Fig. 4.5, the leakage currents through the devices on the wafer implanted with deuterium and annealed in  $N_2O$  was found to be the lowest, and in fact was very small for substrate injection, indicating the reduction in the number of dangling bonds. For the case of gate injection, the leakage current for the control wafer was