New Jersey Institute of Technology Digital Commons @ NJIT

Dissertations

**Electronic Theses and Dissertations**

Spring 5-31-1992

# Process technology and characterization for field emission devices

Jong Min Kim New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Kim, Jong Min, "Process technology and characterization for field emission devices" (1992). *Dissertations*. 1157. https://digitalcommons.njit.edu/dissertations/1157

This Dissertation is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

### **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

### **INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps. Each original is also photographed in one exposure and is included in reduced form at the back of the book.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality 6" x 9" black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

# U·M·I

University Microfilms International A Bell & Howell Information Company 300 North Zeeb Road. Ann Arbor, MI 48106-1346 USA 313/761-4700 800/521-0600

Order Number 9235730

Process technology and characterization for field emission devices

Kim, Jong Min, Ph.D.

New Jersey Institute of Technology, 1992

•

Copyright ©1993 by Kim, Jong Min. All rights reserved.

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

.

### Process Technology and Characterization for Field Emission Devices

by Jong Min Kim

Dissertation submitted to the Faculty of Graduate School of New Jersey Institute of Technology in partial fullfillment of the requirement for the degree of Doctor of Philosophy in Electrical Engineering 1992

Title of Thesis:

Process Technology and Characterization for Field Emitter Devices

Name of Candidate:

Jong Min Kim Doctor of Philosophy, 1992

Thesis and Abstract Approved:\_\_\_\_\_\_Date  $\frac{2/14/22}{Dr}$ . William N. Carr

Professor Department of Electrical and Computer Engineering

Signature of other members of the thesis committee.

Dr. Robert J. Zeto US Army ET&DL Fort Monmouth, New Jersey

\_\_\_\_\_Date \_\_\_\_\_ Dr. Robert B. Marcus

**Bell Communications Research** Red Bank, New Jersey

Dr. Kenneth S. Sohn Professor Department of Electrical and Computer Engineering

\_\_\_\_\_Date \_\_\_\_\_ Dr. Marek Sosnowski Associate Professor Department of Electrical and Computer Engineering

\_\_\_\_\_Date \_\_\_\_\_ Dr. Durga Misra Assistant Professor

Department of Electrical and Computer Engineering

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

### ABSTRACT

### Title of Thesis: Process Technology and Characterization for Field Emission Devices

Author: JONG MIN KIM, Doctor of Philosophy in Electrical Engineering, 1992 Thesis directed by: DR. WILLIAM N. CARR

Vacuum microelectronics is a new research field which applies semiconductor process technology to the fabrication of micron-dimensioned electron devices. Vacuum microelectronics is made possible by advances in microstructures and nanofabrication technology. Vacuum microelectronic devices are further characterized by a wide operating temperature range, nuclear radiation immunity, higher emission current density potential, and lower power consumption than that of thermionic emitters. The low mass of the electron provides a higher carrier mobility than GaAs or any solid state device. These features offer the potentials for wide variety of applications.

In this dissertation, electron field emission structures applicable to a variety of vacuum microelectronic devices have been fabricated and characterized. The cathodes are micromachined of N-type silicon and tungsten using a combination of ultraviolet liftoff lithography and reactive ion etching. A minor emphasis has been placed on micromachining surface-grooved structures for applications that include both vacuum microelectronics and optical microsystems. Optimized processing, device modeling, and physical/electrical characterization are key elements in the research described.

The control of sidewall angle, cavity depth, and apex radius for ridge structures in silicon has been a major focus of this thesis. Reactive ion etching techniques have been studied for sidewall angles up to  $45^{\circ}$  and ridge apex radii of approximately 40nm.

A fluorine-based chemistry  $(CF_4/O_2)$  with oblique angles (tilted wafers) for the incident beam electric field and overetching is used in separate experiments. The use of deep UV-hardened photoresist and image- reversal aluminum liftoff for reactive ion etching masking are compared. Aluminum as a shadow mask for reactive ion etching micromachining has the advantage of lower etch/sputtering rates and higher temperature tolerance compared to photoresist in the  $CF_4/O_2$  system. Typical etch conditions used were  $CF_4/O_2$  flow rates of 20/2 sccm, pressure 10 to 40 mTorr, and etch duration 30 min. This thesis is one of the first detailed studies of reactive ion etching comparing tilted and untilted wafer substrates.

A new process technology for vacuum microelectronic diodes is shown, and device design with a knife-edge cathode and a lateral electron trajectory is implemented as a characterization tool. The cathode structure for these devices consists of a titanium:tungsten /tungsten film sandwich overlaying an aluminum adhesion and sacrificial film. The aluminum film is partially sacrificed to achieve the necessary sharp edge of tungsten metal surface for field emission. The tung-

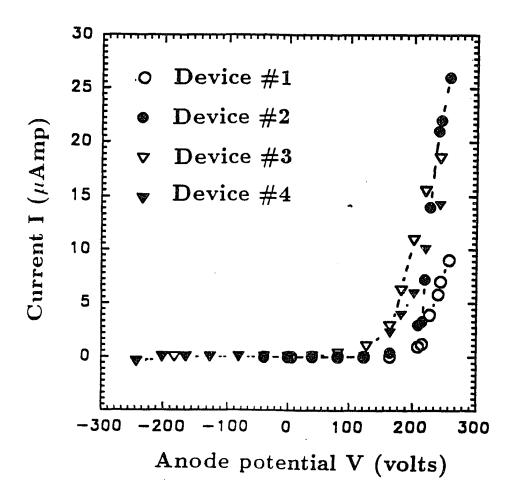

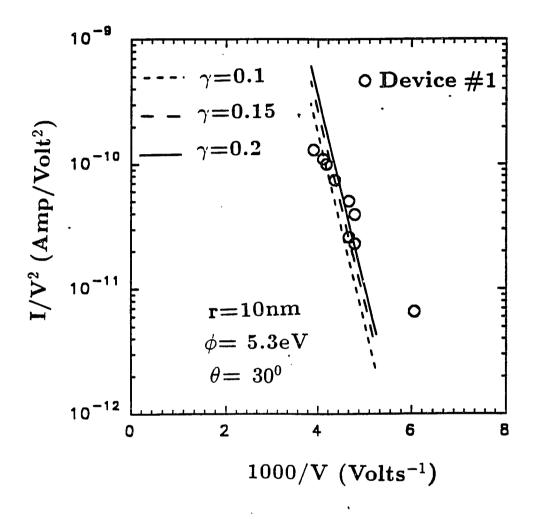

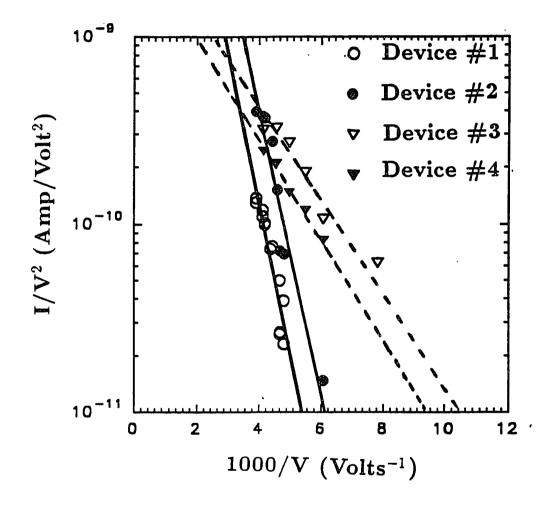

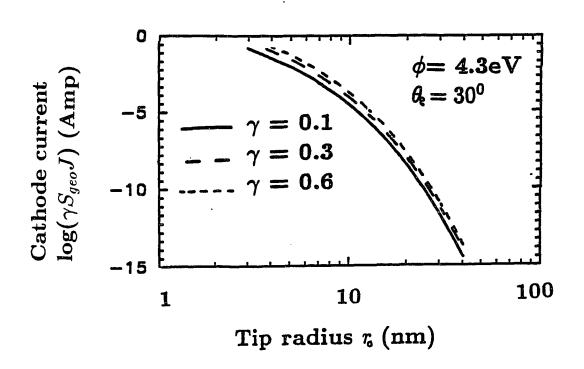

sten and titanium metals are deposited by dc magnetron sputtering followed by liftoff lithography and thermal annealing. Selected devices with a cathode to anode spacing of 0.8  $\mu$ m are electrically characterized in 2 to 5  $\times 10^{-9}$  Torr vacuum. A maximum static current of 26  $\mu$ A current is obtained. The I-V characteristics of lateral trajectory devices with a knife-edge cathode are compared with Fowler Nordheim theory. Good agreement occurs if the cathode apex radius is approximately 10nm. Based on a Fowler Nordheim model the effective fraction  $\gamma$  of the knife-edge emitting electrons is in the range 3 to 80%.

This research includes the first experimental verification of the effect of deflection electrodes to confine the electron beam. Characterization and modeling comparisons for vacuum microelectronic devices with a knife-edge cathode and lateral electron trajectory are described for the first time.

#### ACKNOWLEDGMENT

Many people have assisted me during my thesis work. I am very grateful to my graduate advisor Dr. William N. Carr, Editor-in- Chief of J. M & M and Director of Microelectronics Research Center, whose inspiration and guidance benefited me significantly; without his support this work could not have been finished.

I also thank the co-advisor Dr. Robert J. Zeto, Branch Chief at U.S. Army ET & DL, Fort Monmouth, N.J. for every bit of excellent comments and helps. I also thank Dr. Kenneth Sohn for unconditional helps to my study for 7 years, and thank Dr. D. Misra and Dr. Sosnowski for the nice advises.

Thanks to Dr. Robert Marcus, I achieved my RIE etching career and applied that technology to vacuum microelectronics. His pioneering work on vacuum microelectronics cheered me up greatly.

I would also like to express my appreciation to my colleques, R. Piekarz, J. Conrad, C. Mulford, W. Windsor, L. Poli, C. Kondek, J. Perna, A. Ballekdjian, B. Widuta, E. Zakar and Dr. Daeshik Woo at U.S. Army, ET & DL, Fortmonmouth, N.J. who gave me their assistance in many ways.

I feel particularly grateful to my brother Jongoon Kim, sister-in-law Bobae Lee, my lovely nephew and niece, Ian and Elin in U.S. who helped and loved me greatly.

I really want devote this thesis to my late brother-in law Joosuk Do died at the age of 38 years.

Many thanks go to my mother, brothers and sisters in Korea.

### VITA

### Jong Min Kim

#### Education

| 1987-1991 | New Jersey Institute of Technology,<br>Newark, N.J.<br>Ph.D in EE |

|-----------|-------------------------------------------------------------------|

| 1984-1986 | New Jersey Institute of Technology,<br>Newark, N.J.<br>MSEE       |

| 1976-1980 | Hongik University,<br>Seoul, Korea.<br>BSEE                       |

#### **EXPERIENCES:**

Aug., 1989 Research Associate:

to Microelectronics Center at US Army LABCOM Electronics Technology and Device Lab-Present oratory, Fort Monmouth, NJ: Development of semiconductor vacuum microelectronic device with the consortium of U.S. Army ETDL and NJIT. This project includes semiconductor vacuum microelectronics device development with submicron IC process technology, test and applications for switching devices, microwave amplifiers, sensors and flat panel displays. Semiconductor vacuum microelectronics devices are being fabricated with the submicron silicon IC technology, in a class 10 clean room-micromachining by wet and dry etching, planarization by reactive ion etching(RIE), multilevel submicron lithography for making bridge and cantilever micromechanics. and submicron patterning by RIE, photo and e-beam lithographic liftoff process.

#### Mar., 1988 Research Assistant:

to Microelectronics Center at NJIT: Installation of MRC RIE-51 reactive ion etcher and operation Jul., 1989 for micromachining Si, silicides, metal and dielectrics, also for trench formation, planarization. Plasma diagnosis for RIE by Quadrupole Mass Spectroscopy. Design and installation of UHV test chamber for vacuum microelectronic devices.

#### Apr.,1985 Research Assistant:

to The design and fabrication of the fiber optics for CO<sub>2</sub> laser high power transmission funded by Dec., 1986 New jersey State- This was a joint project with General Fiber Optics Inc., Cedar Grove, NJ and Omega Opticals Inc., Brattle Borough, Vermont.-Development of ZnS, ZnSe, CdTe and hollow metallic waveguide fabrication.

#### Jan., 1982 Computer System Engineer

to Gold Star Electronics Co., Seoul, Korea, Computer H/W system design and pilot product test Aug., 1984 engineering.

### Contents

| 1 | Inti                                  | roduction                                                     | 1  |  |

|---|---------------------------------------|---------------------------------------------------------------|----|--|

| 2 | 2 Theoretical review and applications |                                                               |    |  |

|   | 2.1                                   | Theory of electron emission                                   | 2  |  |

|   | 2.2                                   | Quantitative analysis of emission mechanism                   | 4  |  |

|   | 2.3                                   | Field emission from semiconductors                            | 5  |  |

|   | 2.4                                   | Field emission through dielectric layer                       | 9  |  |

|   | 2.5                                   | Design of a field emitter                                     | 10 |  |

|   | 2.6                                   | Factors governing field emitter operation                     | 11 |  |

|   | 2.7                                   | Modeling factors for the device integration                   | 11 |  |

| 3 | Fun                                   | damentals of RIE                                              | 14 |  |

|   | 3.1                                   | The concepts of RIE system                                    | 14 |  |

|   | 3.2                                   | Etch variables                                                | 17 |  |

|   | 3.3                                   | Selection of etchant gases and etching mechanism              | 17 |  |

| 4 | RI                                    | E techniques for silicon sidewall angle control in microengi- |    |  |

|   | neering 2                             |                                                               |    |  |

|   | 4.1                                   | Overview                                                      | 21 |  |

|   | 4.2                                   | Experimental Procedures                                       | 24 |  |

|   | 4.3                                   | Results and discussion                                        | 25 |  |

1

i

|   |                 | 4.3.1 Overetching with photoresist mask at $\theta_t = 0^0 \ldots \ldots$ | 25 |

|---|-----------------|---------------------------------------------------------------------------|----|

|   |                 | 4.3.2 Wafer inclination with photoresist mask                             | 29 |

|   |                 | 4.3.3 Sidewall angle results with Al liftoff mask                         | 35 |

|   |                 | 4.3.4 Trench etch rates with Al liftoff mask                              | 40 |

|   | 4.4             | Summary                                                                   | 43 |

| 5 | Мо              | del of lateral vacuum microelectronic devices with a cusp                 |    |

|   | catl            | hode                                                                      | 44 |

|   | 5.1             | Device Modeling                                                           | 45 |

|   | 5.2             | Experimental procedures for the recessed lateral diode of cusp cath-      |    |

|   |                 | ode with two deflecting grids                                             | 53 |

|   |                 | 5.2.1 Selection of materials and technology                               | 53 |

|   |                 | 5.2.2 Device fabrication and discussion                                   | 57 |

|   | 5.3             | Results and discussion for the electrical measurements $\ldots$ .         | 64 |

|   | 5.4             | Summary                                                                   | 70 |

| 6 | $\mathbf{Fiel}$ | d emission diode with a tungsten wedge cathode and lateral                |    |

|   | elec            | tron trajectory                                                           | 71 |

|   | 6.1             | Previous publications                                                     | 72 |

|   | 6.2             | Electrostatic design                                                      | 74 |

|   | 6.3             | Fowler Nordheim Modeling                                                  | 80 |

|   | 6.4             | Device Fabrication                                                        | 82 |

|   |                 | 6.4.1 Cathode processing                                                  | 82 |

|   |                 | 6.4.2 Anode processing                                                    | 87 |

|   |                 | 6.4.3 Final processing                                                    | 87 |

|   | 6.5             | Electrical Characterization                                               | 90 |

|   | 6.6             | Summary                                                                   | 98 |

ii

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

. . . . . . . . . .

۱

..

÷

| 7            |                                                                        | 99  |

|--------------|------------------------------------------------------------------------|-----|

| 7.1          | Summary and conclusions                                                | 99  |

| 7.2          | Applications of field emitters in state-of-the-art technology $\ldots$ | 103 |

|              | 7.2.1 Microwave applications                                           | 103 |

|              | 7.2.2 Flat panel displays                                              | 103 |

| 7.3          | Other applications                                                     | 104 |

| References 1 |                                                                        | 105 |

| App          | endix A 1                                                              | .19 |

### List of Figures

١

....

| <b>2.1</b> | The surface potential barrier seen by an electron in a field emission         | 3  |

|------------|-------------------------------------------------------------------------------|----|

| 2.2        | Diagram illustrating field emission from a semiconductor (a) with-            |    |

|            | out field penetration, (b) with field penetration                             | 7  |

| 2.3        | Field emission vertical microtriode model [Ref.2-14]                          | 12 |

| 3.1        | Schematic representation of $(a)$ reactive ion etching system and $(b)$       |    |

|            | plasma potential distribution between anode and cathode $\ldots$ .            | 16 |

| 4.1        | Definition of sidewall angle $\theta_s$ and wafer tilt angle $\theta_t$       | 23 |

| 4.2        | SEM micrograph of etch profile of N-type substrate at normal in-              |    |

|            | cidence angle (a) and etch profile with respect to time (b) $\ldots$          | 27 |

| 4.3        | SEM micrograph of ridge cross section with resist mask and normal             |    |

|            | incidence (a) N-type (b) P-type silicon wafer                                 | 28 |

| 4.4        | Reference notations defined (a) Reference locations defined on the            |    |

|            | wafer (b) Cross section of tilted wafer in chamber                            | 32 |

| 4.5        | SEM micrograph(left) and corresponding cartoon view (right) show-             |    |

|            | ing sidewall profile at $\theta_t = 20^0$ (a) etch location #1 , (b) etch     |    |

|            | location #3, (c) etch location #5. $\ldots$                                   | 33 |

| 4.6        | Sidewall angle definition $\theta_s$ as a function of etch location $\#$ with |    |

|            | resist mask (a) notation defined, (b) cross section drawing. Data             |    |

|            | is fitted to a linear best fit.                                               | 34 |

iv

•

,

| 4.7  | SEM micrographs of ridge formation with annealed and unannealed                                     |    |

|------|-----------------------------------------------------------------------------------------------------|----|

|      | Al masks at various tilt angle (a) unannealed at $\theta_t = 0^0$ , (b) an-                         |    |

|      | nealed at $\theta_t = 0^0$ , (c) unannealed at $\theta_t = 20^0$ , (d) annealed at                  |    |

|      | $\theta_t = 20^0$ , (e) unannealed at $\theta_t = 45^0$ , $\ldots$ $\ldots$ $\ldots$                | 36 |

| 4.8  | Sidewall angles $\theta_{s1}$ and $\theta_{s2}$ as a function of tilt angle $\theta_t$ with Al mask | 39 |

| 4.9  | Silicon etch rate as a function of etch location using unannealed Al                                |    |

|      | mask with tilt angle $	heta_t$ as a parameter $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$          | 41 |

| 4.10 | Silicon etch rate as a function of wafer tilt angle $\theta_t$ using unannealed                     |    |

|      | Al mask with etch location as a parameter                                                           | 42 |

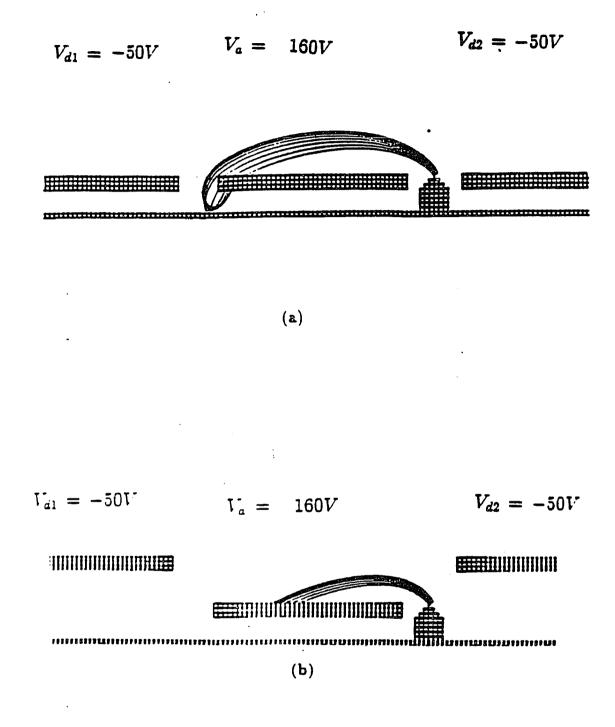

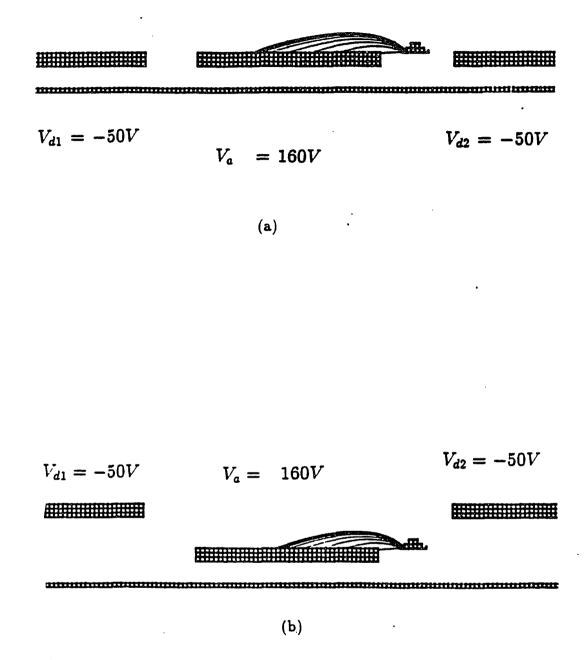

| 5.1  | Wedge cathode for (a) planar and (b) recessed structures with de-                                   |    |

|      | flector $bias(V_{d1,2})$ and anode $bias(V_a)$                                                      | 47 |

| 5.2  | Knife-edge emitter for (a) planar and (b) recessed structures with                                  |    |

|      | deflector $bias(V_{d1,2})$ and anode $bias(V_a)$                                                    | 48 |

| 5.3  | Cusp cathode for (a) planar and (b) recessed structures with de-                                    |    |

|      | flector $bias(V_{d1,2})$ and anode $bias(V_a)$                                                      | 49 |

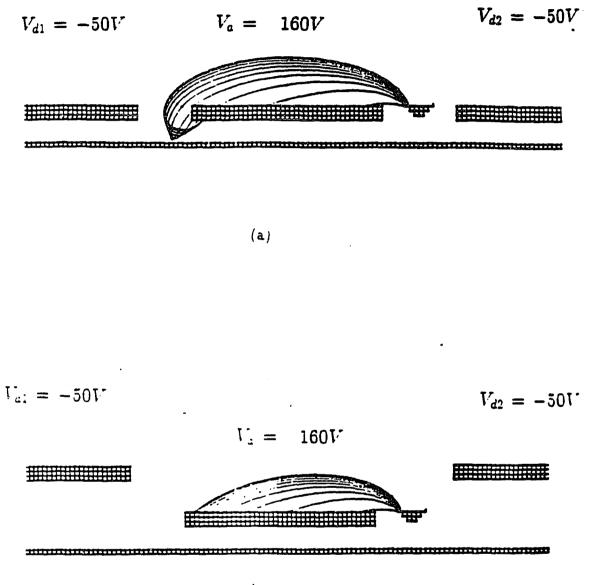

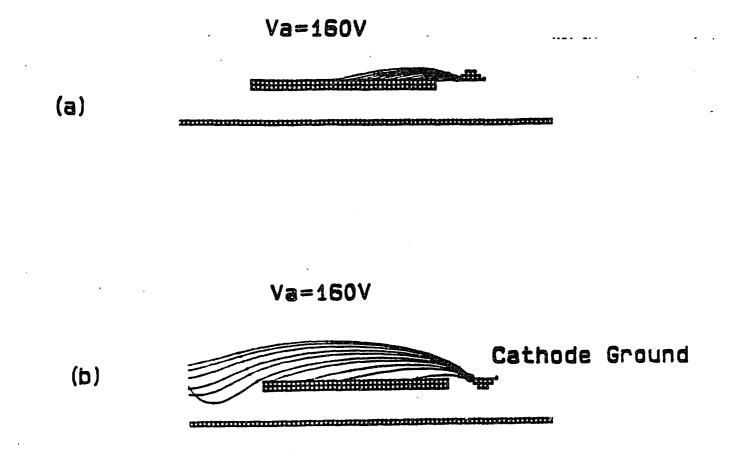

| 5.4  | Electron trajectories without deflecting grid for (a) knife-edge cath-                              |    |

|      | ode (b) cusp cathode                                                                                | 51 |

| 5.5  | Potential distributions without deflecting grid for (a) knife-edge                                  |    |

|      | cathode (b) cusp cathode                                                                            | 52 |

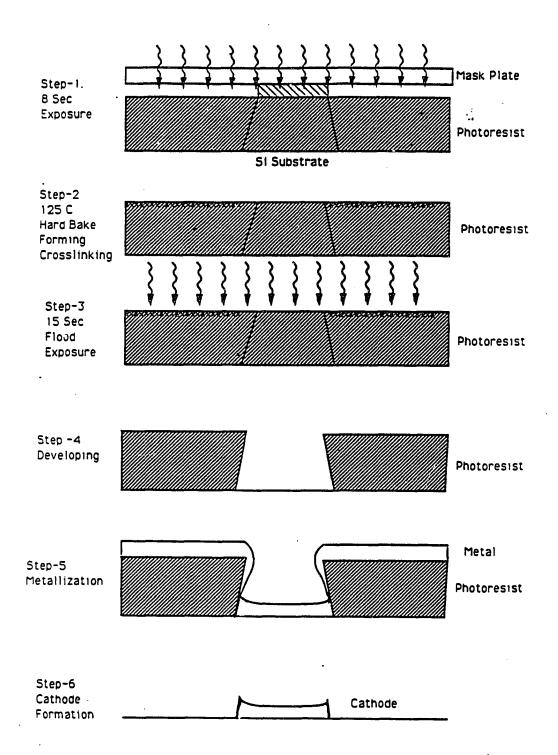

| 5.6  | AZ 5214E reverse image process for cusp edge cathode                                                | 56 |

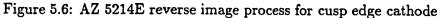

| 5.7  | (a) Layout of the recessed lateral diode, (b) mask#1 (recessed oxide                                |    |

|      | well), (c) mask#2 (cusp cathode), (d) mask#3 (anode and deflector                                   |    |

|      | electrodes)                                                                                         | 58 |

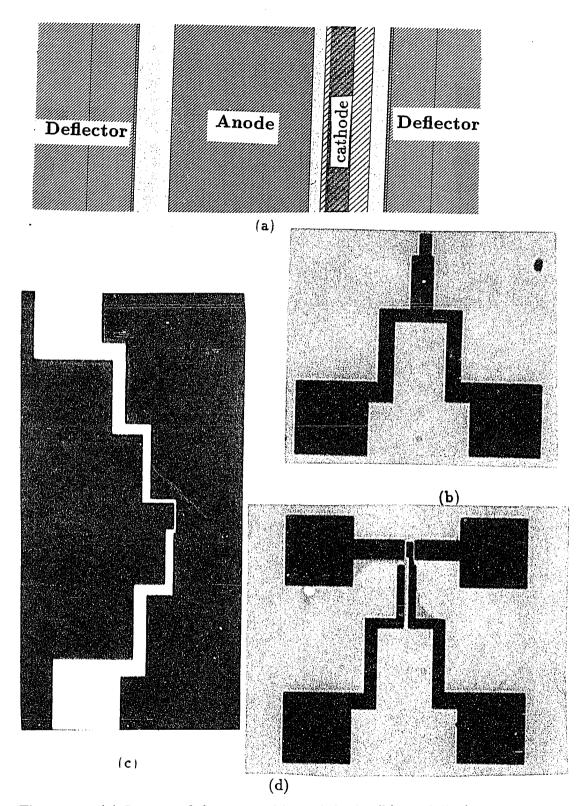

| 5.8  | Sidewall of (a) AZ 5214E photoresist after reverse image process                                    |    |

|      | (b) SEM view of the cusp cathode after liftoff                                                      | 60 |

| 5.9  | Packaged single device                                                                              | 62 |

·

.

٠

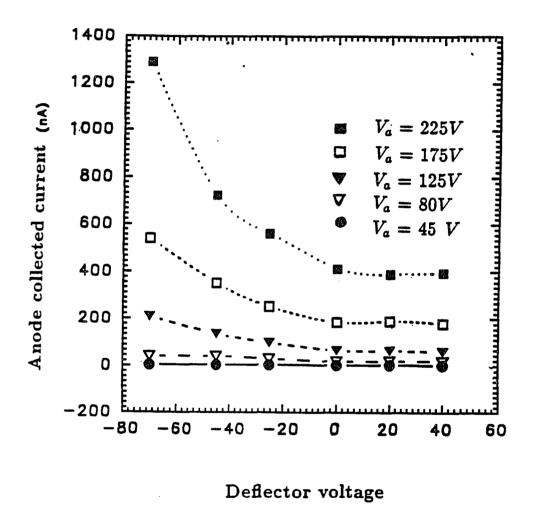

|     | 5.10 | The I-V characteristics of the anode current vs. deflector voltage            |    |

|-----|------|-------------------------------------------------------------------------------|----|

|     |      | as a function of the anode voltage                                            | 65 |

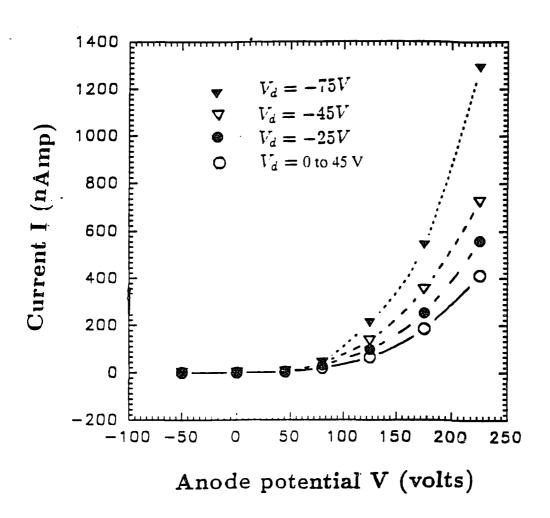

|     | 5.11 | The I-V characteristics of the anode current vs. anode voltage as             |    |

|     |      | a function of deflector voltage                                               | 66 |

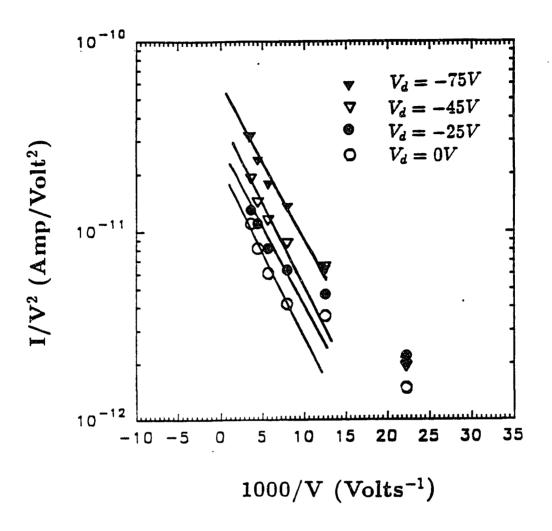

|     | 5.12 | Fowler-Nordheim plot for cusp cathode device                                  | 69 |

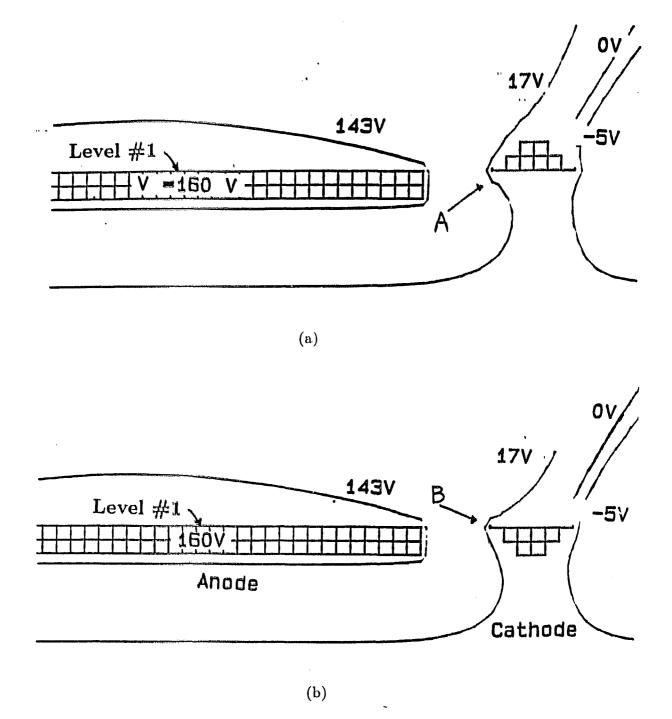

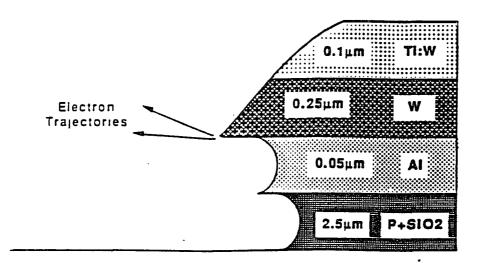

|     | 6.1  | Field emission cathode cross section                                          | 73 |

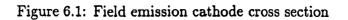

|     | 6.2  | SEM top view of processed device                                              | 76 |

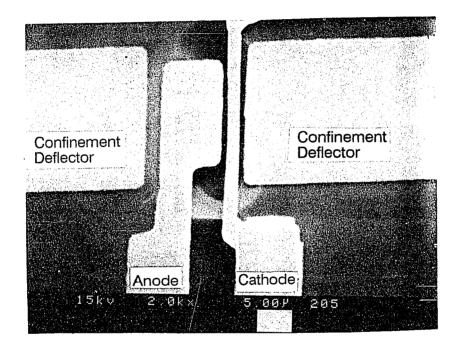

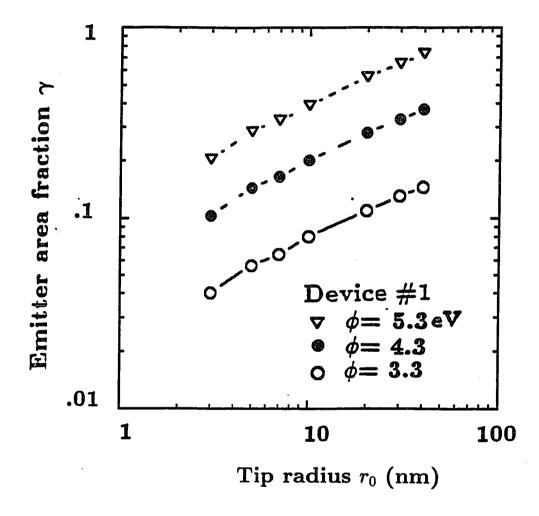

|     | 6.3  | Representive simulation geometry for $E_{max}$ calculations                   | 77 |

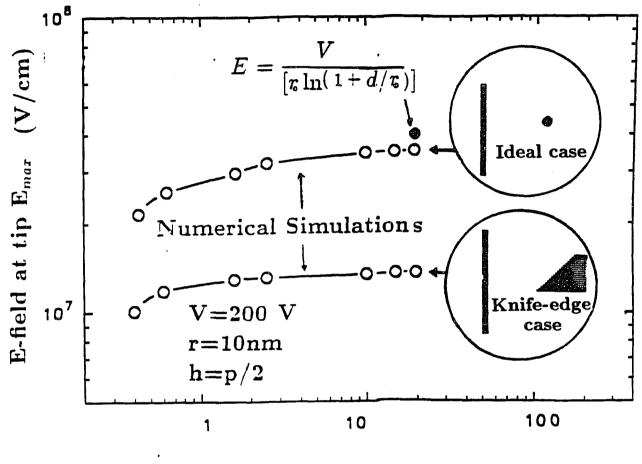

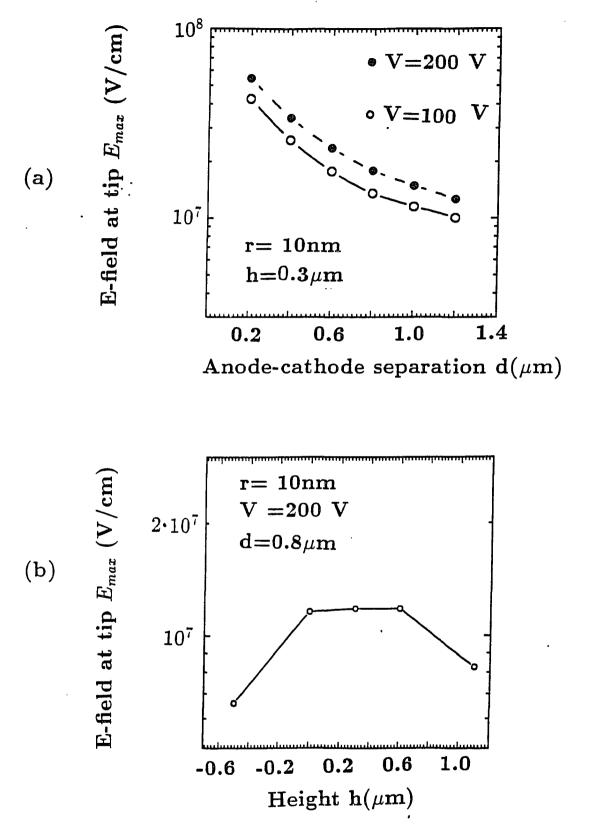

|     | 6.4  | Maximum cathode field $\mathbf{E}_{max}$ as a function of anode thickness $p$ | 78 |

|     | 6.5  | Maximum cathode field $E_{max}$ as a function of (a) cathode height $h$       |    |

|     |      | and (b) anode-to-cathode separation $d$                                       | 79 |

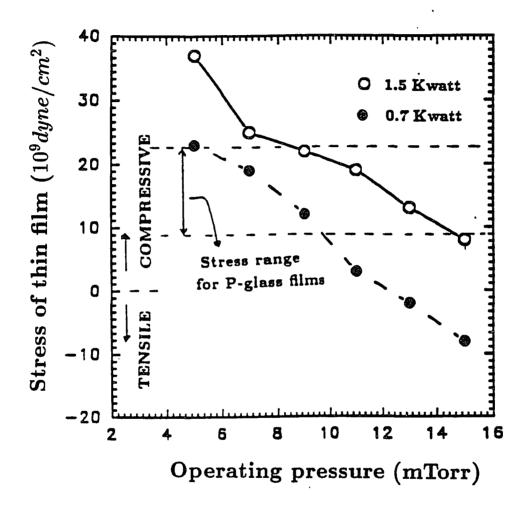

|     | 6.6  | Internal Ti:W stress as a function of sputter chamber pressure fol-           |    |

|     |      | lowing $400^{\circ}$ C anneal                                                 | 84 |

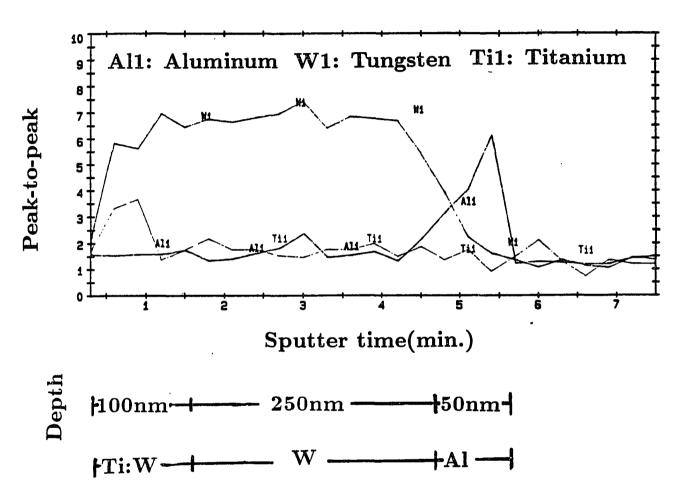

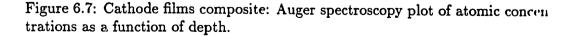

|     | 6.7  | Cathode films composite: Auger spectroscopy plot of atomic con-               |    |

|     |      | centrations as a function of depth.                                           | 85 |

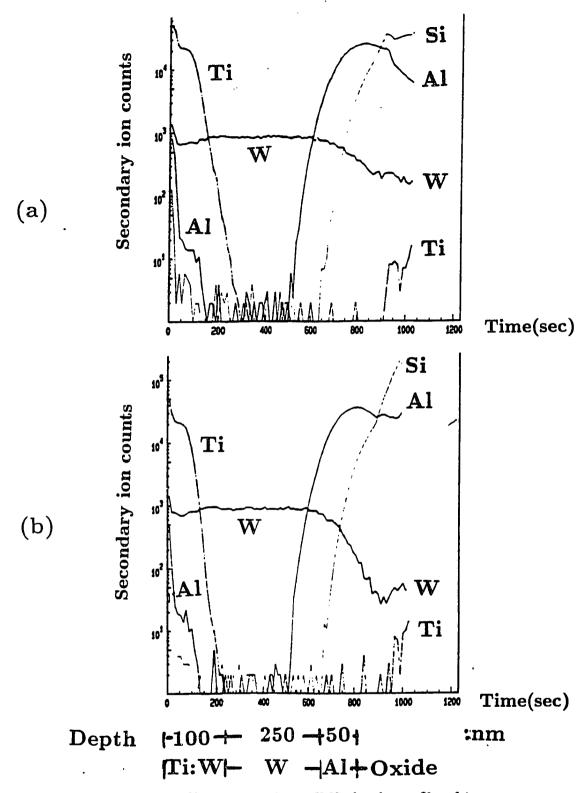

|     | 6.8  | Cathode films composite: SIMS depth profile of ion counts as a                |    |

|     |      | function of depth (a) before annealing (b) after $400^{\circ}C$               | 86 |

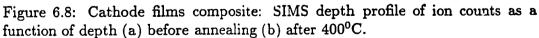

|     | 6.9  | SEM views obtained with a fully processed device $(a)$ oblique angle          |    |

|     |      | view of entire device (b) sideview showing anode-cathode section              |    |

|     |      | and (c) oblique angle view of cathode only                                    | 89 |

|     | 6.10 | Characteristic IV plots for selected diodes $#1-#4$                           | 92 |

|     | 6.11 | Analytical and experimental IV plots in Fowler Nordheim format                |    |

| • . |      | for device $\#1$                                                              | 93 |

|     | 6.12 | IV plots in Fowler-Nordheim formats for device $#1-#4$                        | 94 |

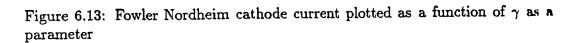

|     | 6.13 | Fowler Nordheim cathode current plotted as a function of $\gamma$ as a        |    |

|     |      | parameter                                                                     | 95 |

•

. . . .

۱

4.

| 6.14 | 4 Emitting area fraction $\gamma$ plotted as a function of knife-edge radius |    |  |  |  |  |

|------|------------------------------------------------------------------------------|----|--|--|--|--|

|      | $r_0$                                                                        | 96 |  |  |  |  |

vii

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

• • •

### List of Tables

- 6.1 Parameters used for specifying surface emitting fraction factor  $\gamma$  . 97

- 7.1 Recently published field emission cathode characteristics . . . . . 102

viii

## Chapter 1 Introduction

Vacuum microelectronics is a new field made possible by advances in microstructures and nanofabrication technology. Vacuum microelectronic devices are further characterized by a wide operating temperature range, nuclear radiation immunity, higher emission current density potential, and lower power consumption than of the thermionic emitters. The low mass of the electron provides a higher carrier mobility than GaAs or any solid state device. These features offer the potential for wide variety of applications.

In Chapter 2, the recent trends of applications are described and concepts of device physics and integration are discussed. In Chapter 3, fundamentals of RIE are presented. Chapter 4 describes the applications of silicon micromachining to the formation of vacuum microelectronics. Detailed qualitative and quantitative descriptions are given for different mask layers.

Chapters 5 and 6 describe the new processing technology for the fabrication of unique field emission tips for lateral electron trajectories. Chapter 5 gives an analysis and new technology for the recessed diode with cusp cathode and two deflecting control grids. Chapter 6 describes processing and characterization of the tungsten knife-edge emitter. Chapter 7 presents the summary and conclusions of this research together with a table of published field emission tip results.

1

### Chapter 2

# Theoretical review and applications

### 2.1 Theory of electron emission

Field emission is dependent upon the shape and work function of emitting material or vacuum environments which affects the work function.

Work function for field emission is modeled by (1) a close packed surface, and by (2) a loosely packed surface [Ref.2-1]. If the extrinsic species are adsorbed into the surface, the work function may increase or decrease by the amount of  $\Delta \phi = 2\pi P_i N_s \theta$  where  $P_i$ ,  $\theta$ ,  $N_s$  are the dipole moment, the fraction of filled surface sites and the number of ad-sites, respectively.

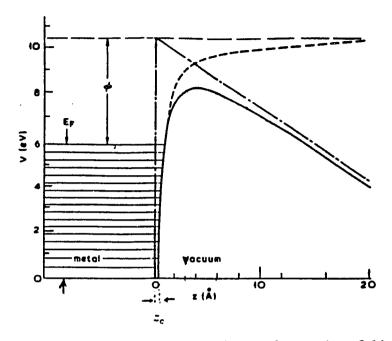

For a strong electrical field, the field emission barrier may be sufficiently reduced in width so that the excited electrons can tunnel out into the vacuum. The surface potential barrier profile from Gomer and Modinos [Ref.2-1, 2-2] is shown in Fig.2.1 for a metal surface.

Figure.2.1. The surface potential barrier seen by an electron in a field emission experiment(solid line). The contribution of the image potential and of the applied field (F = 0.3V/Å) are shown by the broken and the broken-solid line, respectively [Ref.2-2]

A infinitely-deep metal surface from  $-\infty$  to 0 in z axis is assumed in Fig.2.1. An electron situated at a distance z from a plane surface of perfect conductor is affected by the image force. Therefore, the potential energy of electrons on the vacuum side of the metal -vacuum interface, is given by

$$V(z) = E_F + \phi - \frac{e^2}{4z}$$

(2.1)

where  $E_F$  is Fermi level and  $\phi$  is work function (see Fig.2.1) and is valid for  $z \ge 3$ Å. The units of V(z),  $E_F$  and  $\phi$  are eV.

For  $z \leq 3$ Å, the detailed shape of the potential barrier also depends on the metal surface [Ref.2-2]. When the external electrical field F is applied, the electron potential energy is given by

$$V(z) = E_F + \phi - \frac{e^2}{4z} - eFz, \quad (z \ge z_c)$$

$$V(z) = 0, \quad (z \le z_c) \tag{2.2}$$

3

where  $z_c$  is determined by  $V(z_c) = 0$ .

The transmission coefficient and reflection coefficient for electron emission are obtained by WKB method from the Schrödinger equation with the variations of above mentioned potential energy [Ref.2-3]. A general emission current density equation which is known as the **Fowler -Nordheim equation** derived using the WKB approximation [Ref.2-4] is at low temperature,

$$J(F) = A'F^2 \exp(-B'\phi^{3/2}/F)$$

(2.3)

where,

$\begin{aligned} A' &\equiv e^3 / [16\pi^2 \hbar \phi t^2 [\frac{(e^3 F)^{1/2}}{\phi}]] \\ B' &\equiv (4/3e) (2m/\hbar)^{1/2} v [\frac{(e^3 F)^{1/2}}{\phi}] \end{aligned}$

$t(y) \equiv v(y) - \frac{2}{3}y \frac{dv}{dy}$ , where v and y are numerically defined from the derivations [Ref.2-4]. This Eq(2.3) is the most important equation in field emission theory that is describing the relationships between current emission and work function.

### 2.2 Quantitative analysis of emission mechanism

From the field emission current given by Eq.(2.3),  $\ln(J/F^2)$  versus 1/F may be plotted. The plot has straight line whose slope is given by

$$S_{FN} = \frac{d\ln(J/F^2)}{d(1/F)} \equiv -0.683s(\frac{g.79\sqrt{F}}{\phi})\phi^{3/2}$$

(2.4)

where  $0.3V/\mathring{A} \leq F \leq 0.5V/\mathring{A}$  and  $s(y) = v(y) - y/2\frac{dv}{dy}$ .

While in principle work function could be determined from a measurement of slope, the surface potential barrier due to the image force and local effect such as adsorption prohibits the absolute value of work function from being determined[Ref.2-2].

The emission current with image force is at least 10 times lower than that without image force. [Ref.2-5]. The slope of the related FN plot with image force included is changed by less than 5 % from the slope of the FN plot without the image force.

The potential barrier is lowered by the external electrical field. The work function is partly determined by lattice structure, temperature and adsorption of other species. Chemisorbed atoms form a strong electrostatic bond and dipole layer at the surface. Electropositive atoms like thorium and barium are adsorbed as positive ions and make it easier for electrons to tunnel out into the vacuum, by lowering the work function. Electronegative atoms like oxygen and fluorine make it difficult for an electron to escape by increasing the work function.

### 2.3 Field emission from semiconductors

Processing steps may leave an adsorbed layer on the semiconductor surface. The adsorption layer, like ionic bonding on a semiconductor surface, forms surface states with a sharply defined electron dipole layer. This is analogous to the work function increment resulting from adsorption on a metal surface. If there is no surface charge, the penetration of the applied field increases and work function is reduced. If the electronegative surface charge is high enough, charge is densified and field penetration is difficult increasing the work function.

The effective work function  $\phi$  for electron emission into a vacuum results from the sum of several potential barriers existing at the surface.

$$\phi = \phi_i + E_g \pm \phi_F + \phi_s \tag{2.5}$$

where  $\phi_i, E_g, \phi_F$  and  $\phi_s$  are the intrinsic work function, the energy band gap, the energy barrier variations due to Fermi energy level penetration, the energy barrier variations due to doping density. For a lightly doped N-type semiconductor without surface states, the effective work function is  $\phi = \phi_i$  corresponding to a near-intrinsic, low field condition. For a lightly doped P-type semiconductor the

work function increases by the amount of the energy band gap to  $\phi = \phi_i + E_g$ . For a heavily doped P-type semiconductor, the work function increases further by the amount of Fermi energy penetration  $\phi_F$  into the valence band to  $\phi = \phi_i + E_g + \phi_F$ . For heavily doped N-type is decreased by the amount of Fermi energy level penetration  $\phi_F$  into the conduction band to  $\phi = \phi_i - \phi_F$ . When the semiconductor bulk doping is small, the electric field penetrates into the semiconductor and the surface space charge layer widens. Thus the work function component  $\phi_s$  is increased further. For instance, in a heavily doped N-type semiconductor  $\phi = \phi_i - \phi_F + \phi_s$ where  $\phi_s$  is the additional energy barrier due to N-type doping density  $N_D$  where a narrow surface charge layer forms. From Poisson's equation, the additional energy barrier due to the electric field penetration into the semiconductor is

$$\phi_s = \frac{2\pi N_D e l^2}{K} \tag{2.6}$$

where  $N_D$ , e, l, and K are the donor doping density, the charge of electron, the thickness of the surface state, and the dielectric constant, respectively.

The effect of additional surface positive charge ( for example, thorium and cesium) is to reduce the thickness of the surface space charge barrier and thus lower the work function for N-type material. Similarly, the effect of electronegative surface charge ( for example, fluorine or oxygen) is to increase the width l of the surface space charge region and thus increase the work function component  $\phi_s$ .

For the emission from the conduction band from the Fowler Nordheim theory, the current density is given by

$$J = \frac{2neKT}{(\pi m\phi)^{1/2}} \exp(-6.8 \times 10^{7} \phi^{3/2} / F)$$

(2.7)

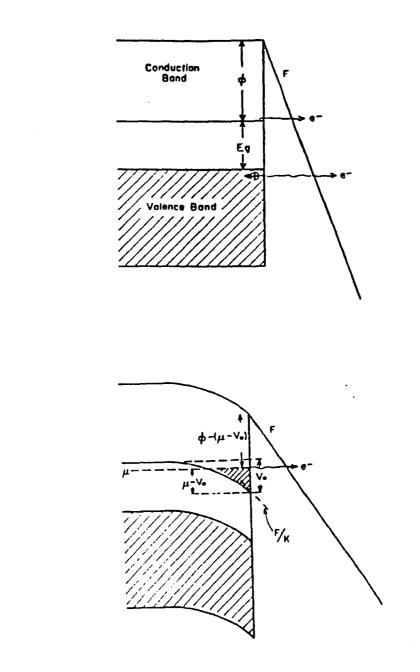

where n, e, K, T, m, and F are the number of electrons per  $cm^3$  in the conduction band, the charge of electron, the dielectric constant, the temperature of field emitter, the mass of electron, and the surface electric field, respectively [Fig.2.2].

6

(a)

(b)

Figure2.2. (a) Diagram illustrating field emission from a semiconductor; Emission from the valence band results in creation of positive hole there. (b) Field emission from semiconductor with field penetration:  $\mu$ =Fermi level,  $\phi$ =ionization energy,  $V_0$ =lowering of the conduction band at the surface due to field penetration,  $\phi - (\mu - V_0)$ =effective work function, F=applied field, F/K=field in semiconductor at surface. [Ref.2-1].

7

When the field penetration without surface state effects is assumed [Fig.2.2.b], the emission current density is obtained by multiplying J in Eq.(2.5) with  $e^{-V_0/kT}$ , since the energy lowering  $V_0$  of the conduction band at the surface due to field penetration is induced.

The total emission current density for semiconductor can include components of electron emission from energy levels in both the conduction and valence bands. For instance, a P-type semiconductor emitter operating at a high temperature can have appreciable electron population in the conduction band and thus a strong  $J_c$  component:

$$J_c = e \int_0^\infty j_c(\epsilon_s) d\epsilon_s$$

$$J_v = e \int_{-\infty}^{-E_g} j_v(\epsilon_s) d\epsilon_s$$

where  $\epsilon_s$ , e, and  $E_g$  are the energy distribution, the magnitude of electronic charge, and the energy gap between conduction band and valence band, respectively. The parameters in the  $j_c$ ,  $j_v$ , are total energy distributions of the electron from the conduction band, and the valence band, respectively [Ref.2-6]. The integration limit (0 in the above eq's) reference potential is at the bottom the conduction band.

A similar analysis applies to the case of metallic emitters. For the case of metallic emitters of course the only valid case refers to extremely heavily doped N-type bulk material without any energy band gap. For the case of metals, the effective work function for tunneling electrons simplifies to  $\phi = \phi_i + \phi_s$  consistent with the above discussion. In the case of both semiconductors and metals, the presence of significant surface charge species  $Q_s$  can very significantly raise or lower the overall work function by affecting  $\phi_s$ .

The previous discussion of the effect of surface charge  $Q_s$  has been simplified. A more precise discussion follows.

### 2.4 Field emission through dielectric layer

There are two types of adsorption which form surface dielectric layers; physical adsorption and chemical adsorption. Physical adsorption has Van Der Waals force coupling, and chemical adsorption has tight bonding for one or more atomic layers. Chemical adsorption is generally a type of covalent bonding instead of ionic bonding. Typically, the maximum thickness of an adsorbed layer film on semiconductor and metal is 20-30 Å. Tunneling through an adsorbed dielectric layer is affected in that (1) the field within dielectric shell (reduced by 1/K where K is the dielectric constant), (2) the image potential is reduced by 1/K, (3) the potential energy of electrons in the dielectric layer is reduced by an average polarization energy, (4) each inert gas atom such as Ar, Kr, and Xe is electropositive and represents a short range but deep attractive potential for electrons. Factors 1) and 2) contribute to an increase, while 3) and 4) contribute to a decrease of effective work function, respectively.

The potential energy of an electron in an electron emission on the vacuum side of adsorbate covered surface is given by

$$V(z) = E_F + \phi_{ad} - \left(\frac{eF}{K}\right)l - eFz - \frac{(K-1)e^2}{(K+1)4z} - \frac{2e^2}{(1+K)4(z+l)}$$

(2.8)

where  $E_F$ ,  $\phi_{ad}$ , F, and l are Fermi level, work function of the adsorbed layer, external applied field, and thickness of dielectric layer, respectively [Ref.2-6]. Equation (2.8) is for  $z \ge z_c$  as in Fig.2.1 with the adsorbed layer. Eq.(2.2) also represent the potential energy of electron for  $z \ge z_c$  as in Fig.2.1 with the clean surface. The effects of a surface oxide to increase the work function were shown recently by Yang et al [Ref.2-7].

An additional case, for the tunneling through oxide, including MIM (metalinsulator-metal), MOMOM(metal-oxide-metal-oxide-metal) and MOMVM(metaloxide-metal-vacuum-metal) surface film has been reported by Ref.2-8.

When the metallic adsorbate on tungsten is considered, the work function is normally reduced, except for Au on tungsten where the work function increases [Ref.2-9]. This depends on the properties of metal/material at the metal/vacuum interface. However, the nature of these phenomena is not clearly understood [Ref.2-9].

### 2.5 Design of a field emitter

Dyke et al [Ref.2-10] reported the relationships between the emission current density and the electric field for a diode (emitter and anode). This reference expresses the electric potential at a tip:

$$V = \left[\frac{V}{R^n}\right] \left[r^n - r_0^{2n+1} r^{-n-1}\right] P_n(\cos\theta)$$

(2.9)

in spherical coordinates -r and  $\theta$ , and where  $R, V, r_0, P_n(\cos\theta)$  and  $\theta$  are the emitter-to-anode distance, applied potential, radius of emitter sphere, Legendre polynomials and cathode sidewall angle with respect to the vertical axis for vertical type cathode, respectively.

A typical field at the tip is  $10^7 \leq F \leq 10^8$  V/cm. As  $\theta$  increases, the electric field rapidly decreases and the emission current also decreases. McCord et al [Ref.2-11] used the spherical model in the method of images to get an improved calculation for STM applications. His results show field distributions similar to those obtained by Dyke [Ref.2-10]. To achieve the maximum emission current, the tip radius should be as small as possible. The sharpest tip with an atomic range radius has been reported by Marcus et al [Ref.2-12].

Factors limiting the maximum current density of a field emitter array (FEA) for a various tips was described by Utsumi [Ref.2-13]. One fundamental limit for current density in an FEA is thermal instability due to Joule ( $I^2R$ )

loss) heating by electrical current flow in a nano scale emitter. The field emission current is approximated by  $I = Jr_0^2$  where J and  $r_0$  are the field emission current density at the emitter and the emitter radius, respectively [Ref.2-13]. If I is too high, Joule heating effect becomes serious and the emitter tip may be metallurgically damaged. Utsumi [Ref.2-13] calculated the maximum emission current density before melting to be  $J_{max} = 10^6 \frac{\sqrt{2T_M \sigma K}}{h} A/cm^2$ , where  $\sigma, K, T_M, h$  are electrical conductivity  $(\Omega \text{cm})^{-1}$ , thermal conductivity, melting point  $({}^0C)$  and emitter height (cm) from the substrate, respectively, simply assuming a simple cone shape emitter pedestal.

### 2.6 Factors governing field emitter operation

Electrical breakdown strength, the tip thermal stresses, and the maintenance of a clean emission surface are factors limiting maximum emitter current over a period of time. For this purpose, an ultra high vacuum (UHV) system is required. However, the operation of these devices in vacuum at pressures as high as  $10^{-3}$ Torr atmosphere has been demonstrated. [Ref.2-14,15].

### 2.7 Modeling factors for the device integration

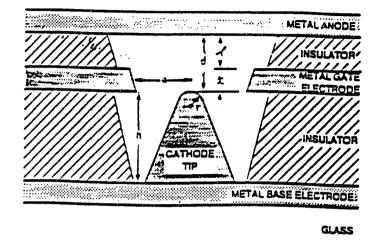

Spindt et al [Ref.2-16,17] have reported simple design models for devices with a vertical (normal to substrate) electron trajectory. Referring to their data, the distance between grid and emitter, and the height of the tip must be considered. For a wider gap between anode and cathode, a higher voltage bias is required. Reduced anode-cathode separation d in Fig.2.3 reduces the bias voltage needed. At a larger bias voltages the device dielectric layer can be broken down electrically. In order to avoid these problems, the careful design techniques are required. With small bias voltage, the smaller emitter radii ( $r_0$  in Fig.2.3) and the higher tips (h in

Figure 2.3: Field emission vertical microtriode model [Ref.2-14]

Fig.2.3) are preferred. From Brodie [Ref.2-14],  $d = 0.5 \mu m$ ,  $h = 1.5 \mu m$ ,  $V_a = 20V$ ,  $V_g = 10V$  are feasible for the field emission without electrical breakdown where  $V_a$  and  $V_g$  are anode and gate bias, respectively from Fig.2.3.

Orvis et al[Ref.2-18] has also presented the design rules for vertical devices. According to Orvis et al, for P -type material, the electrical field will create a depletion region on the silicon tip that will significantly reduce the field enhancement and the field emission rate. Heavily doped N-type (more than  $10^{17}$  atom/ $cm^{-3}$ ) is a superior material. It does not form a depletion layer and works like a metal surface. The electric field effect at the grid is important, since the emission from the electron extraction (positive bias) electrode may occur. This secondary emission effect represents undesirable leakage current from the extraction electrode to the anode in 3-element devices.

Electron trajectories and design descriptions have been published for a

lateral device modeled by Carr et al [Ref.2-19] with a SIMION\*.

\* Simulation program from the Idaho National Engineering Center

13

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

۰

# Chapter 3 Fundamentals of RIE

### 3.1 The concepts of RIE system

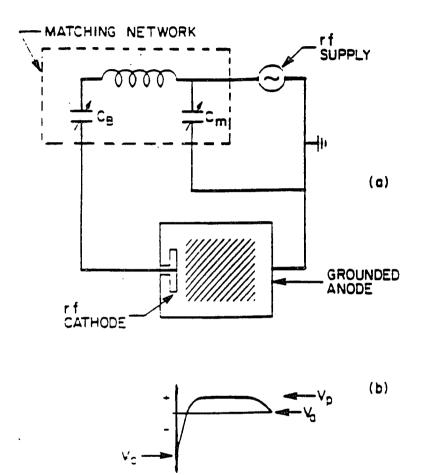

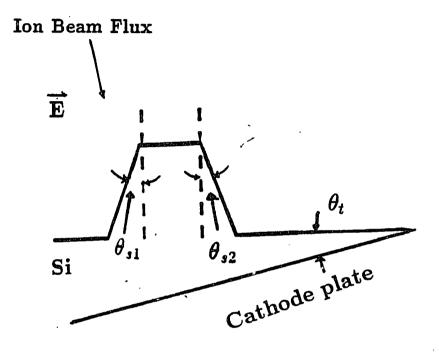

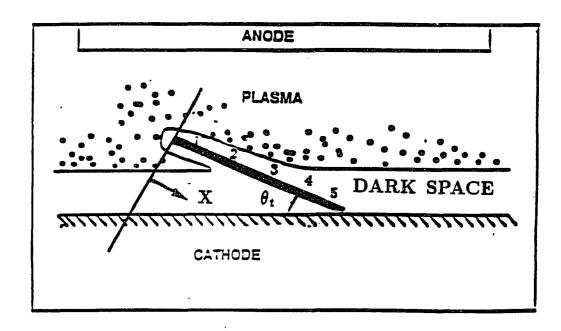

A reactive ion etching system is shown in Fig 3.1(a) with voltage potential distributions between the anode and the cathode in Fig.3.1(b). Fig.3.1(a) shows the block diagram of typical reactive ion etcher. This system has an asymmetrical electrode structure. Between electrode and plasma, a Crooke's dark space is formed[Ref.3-1]. This dark space is also called the sheath area. A detailed description and analysis of the dark space is given by Brown [Ref.3-2].

Positive ions are created and accelerated primarily in the dark space. The potential difference across the dark area is an important parameter for the ion etching and is given by

$$V_p - V_{fi} = \frac{kT_e}{2e} ln \frac{M_i T_i}{M_e T_e}$$

(3.1)

where  $V_p$ ,  $M_e$ ,  $M_i$ ,  $V_{fi}$ ,  $T_e$ , and  $T_i$  are plasma potential, mass of electron and ion, substrate potential and temperature of electrons and ions respectively [Ref.3-3].

Since the plasma has a very low electric field, the space within the plasma is essentially equipotential at  $V_p$ . If an isolated substrate is inserted into the plasma, the substrate takes on a "floating potential"  $V_{fi}$ . The plasma potential  $V_p$  is always greater than the floating potential  $V_{fi}$ . This potential  $V_p - V_{fi}$  drives ions up against the substrate and enhances ion etching process.

Fig.3.1.b shows the potential distributions with  $V_a$  and  $V_c$  which are the anode and the cathode potentials, respectively. The substrate is mounted on the cathode with  $V_c$ . The potential difference between the cathode and plasma plays a major role of the acceleration of the ions and the electrons in the system.

In order to provide maximum rf power delivery in the system, the capacitance for impedance matching should be adjusted in Fig.3.1.[Ref.3-4].

16

....

#### **3.2** Etch variables

There are several variables of RIE that strongly affect the etching process. Control variables are as follows: the residence time of the etchant gases, the conductance of the pumping system, chamber operating pressure, rf power of the RIE, rf frequency of the RIE, electrode spacing, and area of electrodes.

As each substrate etches through different etching mechanisms, flow rate for different etchant gases must be carefully selected for different substrates. The following detail analysis refers to Chapman and Vossen et al [Ref.3-5,6].

## 3.3 Selection of etchant gases and etching mechanism

The precise mixtures for etchant gases should be decided empirically. Generally, Al and III-V compound semiconductors are etched with chlorine-based etchants, while dielectrics and silicon /silicides are etched with fluorine-based gases. Refractory metals including W and Mo are also generally etched with fluorine-based gases as the sublimation temperature of the W and Mo with fluorine gases is lower than that with the chlorine-based gases.

For silicon etching, oxygen gas is typically mixed with  $CF_4$ , because oxygen increases the etch rate and prohibits polymer formation during etching. The maximum etch rate of silicon is obtained when the flow ratio of  $O_2/CF_4$  is 0.15-0.20 [Ref.3-7,8].

The etching mechanism for the silicon with these gases  $(CF_4 \text{ with } O_2)$  is given as follows: when  $CF_4^0$  is bombarded with electrons, major ion species for etching such as  $CF_3^+$  are generated. This  $CF_3^+$  sputters the silicon surface and breaks the Si-Si bonds. This results in the highly reactive radicals such as  $CF_3^0$ or  $F^0$  reacting with the dangling Si surface bonds, and forming the volatiles such

as SiF<sub>4</sub> which can be exhausted. The role of the oxygen molecule in this step is that it removes carbon atom by forming  $CO_2$  gas, and increases net atomic  $F^0$ concentration. The increased  $F^0$  radical induces the high etch rate by forming SiF<sub>4</sub>. If the  $O_2$  concentration is too high, the Si etch rate decreases because oxygen reacts with  $F^0$  and reduces the amount of the  $F^0$  radical. If the  $O_2$  concentration are too low, the polymer layer can be easily formed [Ref.3-9].

To control the etching of SiO<sub>2</sub>,  $H_2$  gases are normally mixed with  $CF_4$ . Since  $H_2$  removes  $F^0$  radical, the density of  $C^0$  radical increases. The  $C^0$  radical reacts with the oxide to form volatile CO<sub>2</sub>. At high H concentration, the ratio of F/C decreases and  $(CF_2)_n$  polymer is formed. It is caused by the association of fluorocarbon radicals on the surface at high pressure [Ref.3-9]. This polymer passivates Si surface and hinders it from being etched.

In either silicon or silicon dioxide, the addition of Ar gas to fluorine gas increases enormously the etch rate because  $Ar^+$  ions sputter the surface with a higher yield compared with other positive ions [Ref.3-10]. Detailed thermodynamic mechanisms and surface reaction chemistry are explained in Ref.3-10.

In order to predict the etch rate of any specific reactive ion etching process, three mechanisms must be considered: (1) sputter etch, (2) chemical etch and (3) ion assisted chemical etch. The etch rate of silicon by these three mechanisms can be calculated as follows:[Ref.3-11]

1) Sputter etch rate is given by (unit;  $\dot{A}$ /min):

$$ER_p = \frac{\Gamma_{ion}Y_p}{N} \tag{3.2}$$

where  $\Gamma_{ion}$ ,  $Y_p$ , and N are the ion flux, the sputter yield of ions at ion energy under investigation and the atomic density of the substrate, respectively;

2) Chemical etch rate(does not require an initial sputtering):

$$ER_c = \frac{\Gamma_n Y_n}{N} \tag{3.3}$$

where  $\Gamma_n$ , and  $Y_n$  are the radical flux and the reaction probability of radicals with substrate, respectively;

3) Ion assisted chemical etch rate (requires an initial sputtering):

$$ER_i = \frac{n\Gamma_{ion}Y_n}{N} \tag{3.4}$$

for  $\Gamma_{ion} n \leq \Gamma_n$ , and

$$ER_i = \frac{\Gamma_n Y_n}{N} \tag{3.5}$$

for  $\Gamma_{ion} n \geq \Gamma_n$ ,

where n and  $Y_n$  are the number of adsorbed radicals activated by incident ion and the chemical sputter yield of the ion at ion energy, respectively. The detail chemistry of etch process (3) is a combination of (1) and (2).

## Chapter 4

# RIE techniques for silicon sidewall angle control in microengineering

This chapter describes RIE techniques with silicon substrates for initial processing of semiconductor field emitter array cathodes for vacuum microelectronics. A secondary focus is process research for optical reflecting gratings for opto- and micromechanical devices. These applications each require control of the sidewall angle and apex radius. In this chapter, we describe micromachining control of trenches with remainder sidewall angles varying from 15 to 60<sup>0</sup> and resulting apex ridge radii of as small as 40nm. A fluorine-based chemistry  $(CF_4/O_2)$  with oblique angles for the incident beam (tilted substrates) and overetching is used. The use of both deep UV-hardened photoresist and aluminum as RIE shadowmasks is compared. Unannealed aluminum as a shadowmask for RIE micromachining has the advantage of lower etch/sputtering rates and higher process temperature tolerance compared to photoresist in the  $CF_4/O_2$  RIE system. Etch environments in the pressure range 30 to 80 mTorr with  $CF_4/O_2$  flow rates of 20/2 sccm, rf power 100 to 200 watts, and etch duration 30 min. are described. Both tilted and untilted substrates mountings were studied. Under these conditions, the surface erosion is primarily a combination of ion milling and chemical etch mech-

anisms. Both P-type and N-type substrates of 100nm diameter wafers were used. Relatively sharp single- and double-ridged silicon structures were obtained using the photoresist shadowmask on untilted substrates. The photoresist shadowmask provides an advantage over Al only for the sidewall orientation  $\theta_t = 20^0$  where we were able to specify a condition for obtaining a smooth optically reflective surface. The more vertical sidewall angles obtainable with the unannealed Al shadowmask should permit fabrication of field emitter cone or ridge cathodes on pedestals with higher height-to-width ratios. A field cathode pedestal with a more vertical sidewall results in a higher electric field at the electron emission tip or ridge.

#### 4.1 Overview

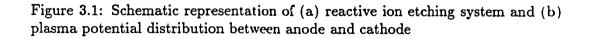

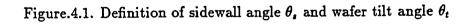

The results described in this chapter are applicable to the initial processing of semiconductor cathodes for vacuum microelectronics devices [Ref.4-1,2,3] and to the controlling the blaze angle for optical diffraction gratings [Ref.4-4,5]. Each of these applications require control of the sidewall angle  $\theta_s$  in Fig.4.1. Similar structures also have application for some trench capacitors and several specialized microelectromechanical devices. RIE as a tool for microengineering has been used for shaping sidewalls for laser mirror facets [Ref.4-6] and for SAW (surface acoustic wave) devices [Ref.4-7,8]. Related RIE studies describe sidewall control in trench structures including electrical device isolation and capacitors [Ref.4-9,10,11,12]. The effects of RIE processing on surface topography with both experimental results and modeling data have been reported for several VLSI circuit fabrications [Ref.4-13,14,15,16,17,18].

Previous work with RIE systems has established that the wafer tilt angle  $\theta_t$ in Fig.4.1 and etch environment greatly affects the resulting sidewall angle  $\theta_s$ . In this chapter, we compare the use of photoresist versus aluminum as a shadowmask in the RIE etching process for controlling the sidewall angle and apex sharpness. Generally, the maximum etching anisotropy is obtained at maximum beam energy and lowest pressure under conditions generally described as ion beam milling. Ion beam milling becomes significant at pressure levels of less than 10 mTorr and totally dominates the etching process at pressure levels of 0.1 mTorr and less. The striations and general roughness of the ion beam milled surface , however, are unacceptable for our applications.

At pressures higher than 10 mTorr, the density of neutral chemical etchants becomes significant and a smoother, more isotropically etched surface results. We have etched at higher pressures ranging from 30 to 80 mTorr in order to obtain a more desirable surface smoothness and also to increase the etch rate. In this chapter, the ridged structures created by etching with both resist and metallic in situ shadowmasks for tilted substrates are compared with results for conventional etching of untilted wafers. The primary objective for this work is to develop and further understand the RIE process which permits control of the sidewall angle and the sidewall smoothness in the situations selected.

23

### 4.2 Experimental Procedures

Etching is done with an MRC RIE-51 system using  $CF_4$ ,  $O_2$ , and Ar sources. The chamber base pressure was  $2x10^{-5}$  Torr. The controlled operating pressures were in the 30 to 80 mTorr range during  $CF_4/O_2$  flow. The 13.56 MHz power source of 100 to 250 watts provided 500 to 800 volt rf peak-to-peak voltage levels across the plasma diode. The reactor anode-cathode separation was 6 cm. Untilted wafers  $(\theta_t = 0^0)$  are positioned flat against the cathode. Stainless steel wedges were used to tilt the wafer on the cathode for the etching at angles of  $\theta_t = 20$  and 45°. Wafers of [111] orientation, 100 mm diameter, heavily doped with arsenic or boron of less than 0.003  $\Omega$ cm resistivity were used. The wafers were patterned with four shadow films: (a) deep UV-hardened positive AZ1518 photoresist, (b) same resist not deep UV-hardened, (c) annealed Al, and (d) non-annealed Al. Processes (a) and (d) were found to be superior for our applications. Wafers were patterned using  $1.23\mu$ m linewidth and  $4.0\mu$ m pitch photomask which results in positive and negative final shadow "top hat" images for positive photoresist and Al, respectively. For the photoresist processes (a) and (b), a 1.8  $\mu$ m thick resist was applied at 5000 rpm(40 sec.), preceded by HMDS (Hexamethyldisilazane: 10% in Xylene) spincoating at 6000 rpm (30 sec). The UV lithography exposure was preceded by a soft bake at  $110^{\circ}C(1 \text{ min})$ . The exposed wafer was developed with Shipley MIF312 (50%  $H_2O$ ) followed by a hard bake at 125°C (1 min). A final deep UV (flood exposure) hardening was accomplished while ramping the temperature from 125 to 180 °C (6 min).

The above mentioned processes (c) and (d) use an Al liftoff image-reversal technique for RIE-shadowing. An underlying 1.4  $\mu$ m film of AZ 5214E resist was hardbaked at 125°C for 1 min. and UV floodexposed at 365 nm wavelength. Following development in MIF 312 (50%H<sub>2</sub>O), a 0.22 $\mu$ m e-beam deposition of Al

was made. The AZ 5214E sacrificial layer under the Al is next lifted off with an acetone rinse and ultrasonic agitation. The Al shadowmask now serves as an in situ "top hat" shadowmask for RIE micromachining. In our F-based RIE process an etch rate selectivity of 18X was observed for Si substrate versus the unannealed Al shadowmask. For comparison the Al film was annealed at  $350^{\circ}$ C (30 min). The Al is etched with CF<sub>4</sub>/O<sub>2</sub> (20/2 sccm) at 30 mTorr using a 200 watt power level. Following RIE the remaining Al was removed by  $H_2SO_4$ :  $H_2O_2$ (1:1) solution.

#### 4.3 **Results and discussion**

## 4.3.1 Overetching with photoresist mask at $\theta_t = 0^0$

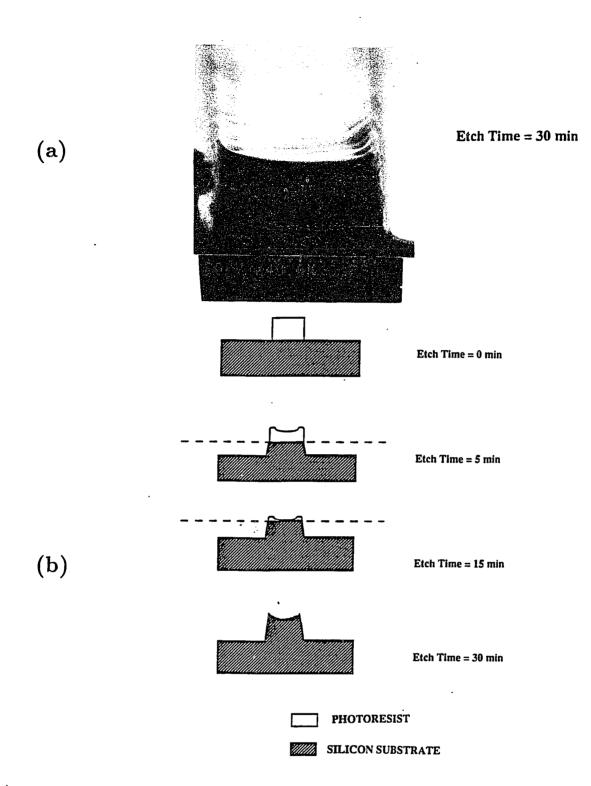

Figure 4.2(a) is the SEM cross section view of a structure obtained by two-step RIE etching with a deep UV-hardened AZ 1518 mask on untilted wafers. RIE in this experiment continues even after the photoresist was completely etched away. This is referred to as "heavy overetching" in this experiment. This figure shows symmetrical sidewalls for a wafer oriented for normal incidence (tilt angle  $\theta_t = 0$ ). A two-step etching sequence was used at a 100 watt power level. The first step at 80 mTorr(CF<sub>4</sub>= 10 sccm) for 15 min. creates a ridge structure with rounded sidewalls. During the second step, pressure was reduced to 40 mTorr (CF<sub>4</sub>/O<sub>2</sub>= 30/7 sccm) for 15 min. and sharp sidewalls are created. The first step creates a smooth surface topography. The second step creates a more abrupt sidewall although the sidewall striations increase. The process etch profile for an untilted wafer etched with for different periods of time is shown in Fig.4.2(b). The "top hat" photoresist has been exposed to more incident photon energy near the sidewalls during the lithography process. This result of photo-diffraction in turn causes the photoresist to be more retardant to RIE etching near the sidewall

also.

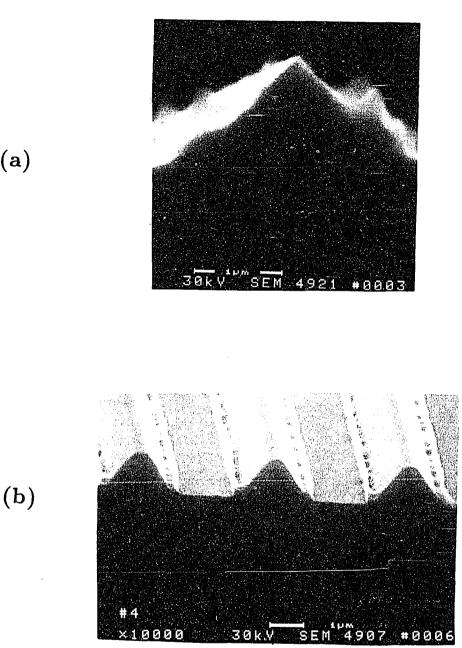

In Fig.4.3(a) and (b), a single-step process is used to define ridge structures with N-type and P-type wafers, respectively. A sharp edge at the apex of the ridge is more readily obtained with the N-type substrate in Fig.4.3(a) compared with the P-type case of Fig.4.3(b). The debris on the left and right sidewall in Fig.4.3(a) is photoresist polymer. Flow rates of  $CF_4/O_2=20$  / 2sccm at 30 mTorr for 30 minutes were used for N- and P-type substrates using power levels of 200 and 150 watt, respectively. The resulting apex radii of 40nm for the Ntype and 300nm for the P-type material are estimated from SEM cross sections as in Fig.4.3(a) and Fig.4.3(b), respectively. N-type material provides the lower work function for field emission cathodes and is usually preferred for vacuum microelectronics.

The ridge structures of Fig.4.3 using a single-step process described above can be oxidized to fabricate Marcus-type field emission cathodes for devices with vertical electron trajectories [Ref4-19,20,21]. The double-ridge structure of Fig. 4.2 obtained with the two-step process may prove useful for obtaining cathode tips oriented at an oblique angle more useful for field emission devices with a lateral electron trajectory [Ref.4-22].

For the optical grating application, the P-type substrate resulted in a more planar sidewall (desirable) compared with the N-type starting material. The onestep process of Fig.4.3 is used for the optical structure.

Figure.4.2. SEM micrograph of ridge cross-section with resist mask and normal incidence  $\theta = 0^{\circ}$ .

(a) N-type [111] with photoresist mask under  $CF_4/O_2=20$  sccm/2 sccm at 30 mTorr, 200 watts with aceton cleaning. (b) P-type [111] under the same etching condition except 150 watts and Piranah cleaning.

$\mathbf{27}$

(a)

(a) N-type [111] with photoresist mask under  $CF_4/O_2=20sccm/2sccm$  at 30 mTorr, 200 watts with aceton cleaning. (b) P-type [111] under the same etching condition except 150 watts and Piranah cleaning.

$\mathbf{28}$

#### **4.3.2** Wafer inclination with photoresist mask

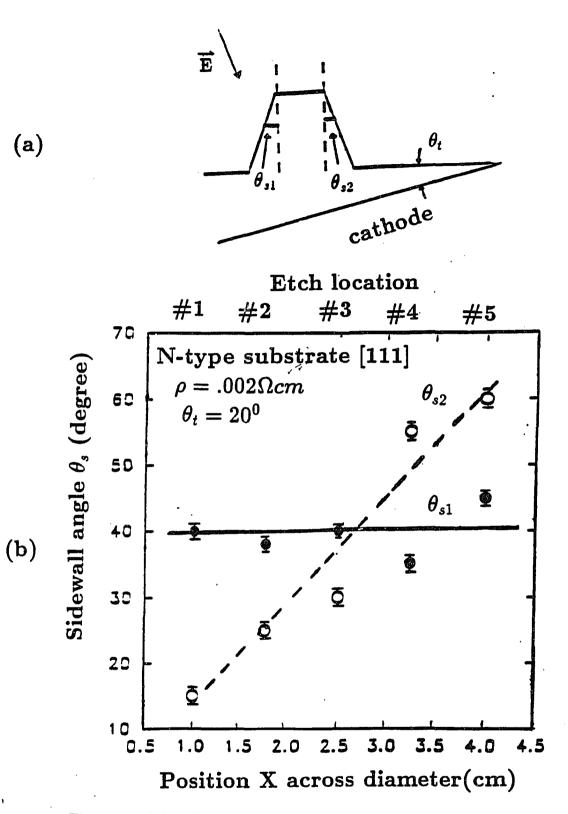

A series of experiments with heavily doped N-type substrates were performed using deep UV-hardened photoresist as the only mask for defining trench structures. The sidewall angles  $\theta_{s1}$  and  $\theta_{s2}$  defined in Fig.4.1 are controlled by tilting the silicon wafer with respect to the plane of the cathode. Fig.4.4 shows a wafer tilted at an angle  $\theta_t$  during the etch process with positions #1 through #5 defined along a diameter. The tilted wafer exhibits an increasing dark space thickness along the wafer diameter from position #1 to #5. The kinetic energy for ions colliding with the wafer surface increases from position #1 to position #5. The milling rate due to the ion also generally increases from position #1 to position #5 for tilted wafers corresponding to the increased energy of the incident ions as will be detailed in next section. The less dominant but important etching mechanism is that of the chemical reaction at the silicon surface. The chemical etch rate due to unmasked free radical generally decreases from position #1 to #5.

For untilted wafers  $\theta_t = 0^0$  the dark space thickness is a uniform 1.5 cm. For a tilt angle  $\theta_t = 20^0$  illustrated in Fig.4.4(b), the dark space thickness ranges from 1.5 cm at the cathode surface (position #5) to 0.5 cm at the wafer position near the anode edge (position #1). The dark space always forms on the wafer surface adjacent to the plasma glow.

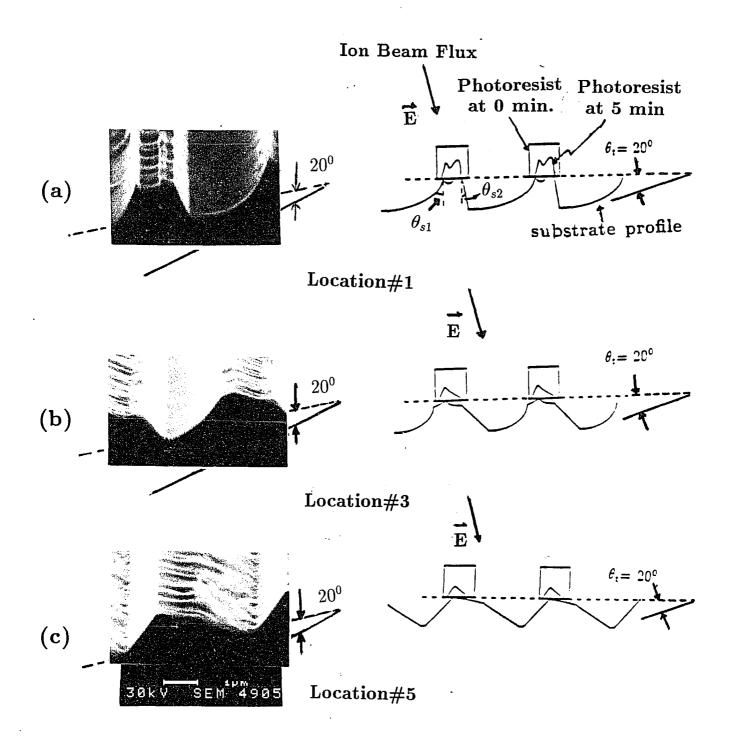

Figure 4.5 shows three SEM cross section photo views and the corresponding drawn cross sections to show the photoresist shadowmask. The Fig.4.5 SEM views at position #1, #3, and #5 are all obtained with the wafer tilted  $\theta_t = 20^0$ and with 30 min. of etching. Figures 4.5 (a), (b), and (c) show cross sections at position #1, #3, and #5, respectively. In Figure 4.5, the drawn cross sections each include an insert view of the photoresist shadowmask at t=0 and t=5 minutes. At the start of etch t=0, the photoresist shadowmask is rectangular in cross section as shown. Following a 5 minute etch the photoresist has eroded substantially as shown. The etching of the photoresist continues until it is entirely removed within approximate 15 minutes.

The sidewall angles  $\theta_{s1}$  and  $\theta_{s2}$  defined in Fig.4.1 vary with position along the diameter of the tilted wafer as shown in Fig. 4.5. The dominant surface removal mechanisms that can affect the sidewall formation are (1) ion milling due to physical ion bombardment, and (2) formation of volatile silicon compounds by neutral species. Also surface topography can be affected by buildup occurring when the volatile silicon compounds are redeposited on an adjacent sidewall by a local reactive redeposition. In addition, components of the photoresist "top hat" can be sputtered onto a sidewall and thus reduce the etch rate on the sidewall.

In Fig.4.5(a), the sidewalls are asymmetrical indicating an isotropic etching process at location #1. At this position the dark space has minimal thickness and the ions impinge upon the wafer surface with lower kinetic energy. The silicon surface here is closer to the plasma and should contain a higher density of free (un-ionized) radicals which are known to etch isotropically. In this case sidewalls of approximately  $40^{\circ}$  and  $15^{\circ}$  are observed for  $\theta_{s1}$  and  $\theta_{s2}$ , respectively.

In Fig.4.5(c) the maximum asymmetry is observed at location #5. The shadowed surface shows the striations characteristic of kinetic impacts from the incident ion stream. The maximum sidewall angle  $\theta_{s2} = 60^{\circ}$  is observed for this case. The smooth surface of sidewall  $\theta_{s1}$  is not characteristic of ion milling although a strong ion beam flux exists at location #5. The clean  $\theta_{s1}$  surface in Fig.4.5(a) shows no evidence of sputtered photoresist debris. We believe the most likely mechanism accounting for the  $\theta_{s1}$  surface smoothness is reactive redeposition excited by the ion beam. The sidewall topography shown in Fig.4.5(b) is intermediate between the (a) and (c) cases and thus is a mix of these same pro-

cesses. This technique provides the optical gratings with the desirable sidewall at position #1 and #5. There is a yield problem in that the most desirable sidewalls do not occur at all wafer positions #1-5.

Fig.4.6 summarizes the sidewall angle observations obtained from a series of SEM photos including those of Fig.4.5. A photoresist "top hat" or shadowmask is used in Fig.4.6 with a 30 min. etch and an N-type substrate tilted  $\theta_t = 20^{\circ}$ . This plot clearly indicates the complex nature of the erosion mechanisms as the sidewall angles  $\theta_s$  vary across the wafer diameter. The sidewall angle  $\theta_{s2} = 60^{\circ}$ obtained at location #5 is primarily due to the ion milling. If the shadowmask would remain intact and the etch time extended, we expect that  $\theta_{s2}$  at location #5 will eventually equal to  $20^{\circ}$  in alignment with the incident ion beam. At location #1, the smooth sidewall  $\theta_{s2} = 15^{\circ}$  observed is dominated by a chemical etching assisted by the directional ion beam. The fact that sidewall  $\theta_{s1}$  is an almost constant  $40^{\circ}$  across the wafer diameter from location #1 to #5 is only fortuitus considering the complex interplay of surface erosion mechanisms. At other tilt angles  $\theta_t = 20^{\circ}$  we do not expect the sidewall  $\theta_{s1}$  to remain constant across the diameter.

(a)

(b)

Figure 4.4: Reference notations defined (a) Reference locations defined on the wafer (b) Cross section of tilted wafer in chamber

Figure.4.5 SEM micrograph (left) and corresponding cartoon view (right) showing sidewall profiles obtained with an N-type substrate using a photoresist mask  $\theta_t=20^{\circ}$ , CF<sub>4</sub>/O<sub>2</sub>=20 sccm/2 sccm, 30 mTorr, 200 watt for 30 min . (a) etch location #1. (b) etch location #3 (c) etch location #5

33

٠.

Figure 4.6: Sidewall angle definition  $\theta_s$  as a function of etch location # with resist mask (a) notation defined, (b) cross section drawing. Data is fitted to a linear best fit.

#### 4.3.3 Sidewall angle results with Al liftoff mask

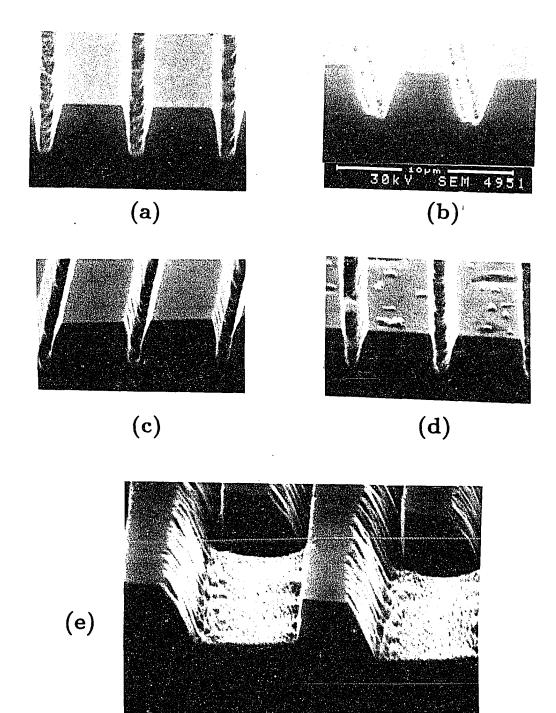

Unannealed aluminium etches a factor of 30x more slowly in the  $CF_4/O_2$  system compared with photoresist. We have taken advantage of this differential in defining an Al liftoff process for creating deep trench structures on Si substrates. The RIE etch rate for Al with a  $CF_4/O_2$  flow of 20/2 sccm and a 200 watt rf power level is 50Å/min ( $\theta_t = 0^0$ ). This compares with an etch rate of  $880\text{\AA}/\text{min}$  for Si under the same conditions. The annealed Al mask withstands the RIE flux for 30 minutes, compared to 15 min for the photoresist and thus permits deeper substrate trenching compared with the previous case for the photoresist shadowmask.

A series of SEM views obtained using an Al "top hat" shadowmask are shown in Fig.4.7. These SEM cross section views are obtained at location #3. All trenches in Fig.4.7 are approximately  $3.3 \ \mu m$  in depth. The mask used for the Al process is the reverse of that used for the previously described process in Fig.4.2,4.3, and 4.5. The Al shadowmask is defined using the mentioned liftoff lithography process. The sampled figures are obtained from the middle of the wafer at location #3.

Figure 4.7(a) and (b) compare the trenching structure at  $\theta_t = 0^0$  for unannealed and annealed Al shadowmasks, respectively. The aspect ratios, sidewall angles and trench depths were uniform over the entire wafer for this  $\theta_t = 0^0$  case. While the annealed Al of Fig.4.7(a) survived the 30 min etch, the annealed Al mask was etched away at the periphery prior to the end of etch in (b). The increased size of Al grains which results from the thermal treatment accounts for the faster etch rate observed in the annealed Al film. The edge loss of the faster-etching annealed Al film during RIE resulted in the creation of the wider trench of Fig.4.7(b) compared to (a).

Figure.4.7 SEM photo micrographs of ridge formation with Al shadowmask on N-type substrate -  $CF_4/O_2 = 20sccm/2sccm$ , 200 watt, 30 mTorr for 30 minutes. (a) unannealed mask at  $\theta_t = 0^{\circ}$ , (b) annealed mask at  $\theta_t = 0^{\circ}$ , (c) unannealed mask at  $\theta_t = 20^{\circ}$ , (d) annealed mask at  $\theta_t = 20^{\circ}$  and (e) unannealed mask at  $\theta_t = 45^{\circ}$ . All views are at wafer location #3

36

#0001

Й

Reproduced with permission of the copyright owner. Further reproduction prohibited without permission.

50

The sidewall cross section with the wafer inclined with a tilt angle  $\theta_t = 20^0$  is shown in Fig.4.7(c) and (d), without and with annealing, respectively. For the  $\theta_t = 0$  case, the annealed Al etch rate is faster compared to  $\theta_t = 20^0$ . The residue of annealed Al on the silicon surface in the case of Fig.4.7(d) compared to 4.7(b) is a consequence of the slower etch rate in (d). In Fig.4.7(e) with  $\theta_t = 45^0$  at location #3, the texture of the  $\theta_{s2}$  sidewall surface indicates that ion milling is dominating the erosion process and indicates a relatively small isotropic chemical etch component. In (e) the Al mask at the edge totally etched away and the the trench is widened considerably.

Chapman[Ref.4-23] reports that the etch rate increases approximately linearly as a function of the tilt angle  $\theta_t$  for ion sputtering (milling), over the range  $0 \le \theta_t \le 45^0$  at pressure levels of less than 1 mTorr. Our results cannot be compared directly since we have a much higher chamber pressure and use chemical reaction by free radicals with ion milling simultaneously. Our sidewall in Fig.4.7 shows only a partial striated surface characteristic of ion milling.

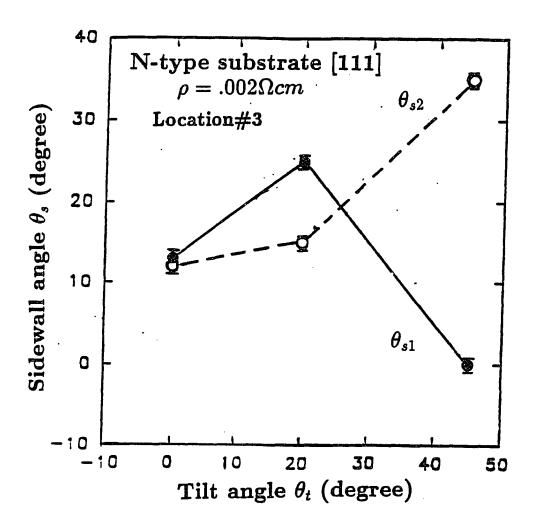

The sidewall angles  $\theta_{s1}$  and  $\theta_{s2}$  are plotted in Fig.4.8 as a function of the wafer tilt angle  $\theta_t$  using the Al unannealed shadowmask. The sidewall angles  $\theta_{s1}$  and  $\theta_{s2}$  are approximately 12° for tilt angle of  $\theta_t = 0°$  and again cross at approximately  $\theta_t = 28°$  for the RIE parameters used. The sidewall angle  $\theta_{s1}$  is maximum at an intermediate value as seen in Fig.4.8. The sidewall angle  $\theta_{s2}$  is seen to increase constantly in Fig.4.8 with the tilt angle  $\theta_t$ , where ion milling effects are especially important. In Fig.4.8, the sidewalls at  $\theta_t = 0°$  are of course symmetrical. As the substrate is tilted and etched at  $\theta_t = 20°$ , one observes that sidewall  $\theta_{s2}$  steadily increases with the tilt angle as expected with a strong ion milling anisotropy component. A very different etch mechanism is operative in Fig.4.8 on  $\theta_{s1}$ . The vertical sidewall angle  $\theta_{s1} = 0°$  at  $\theta_t = 45°$  is quite smooth

37

and results from a combination of both erosion and deposition mechanisms.

These complex erosion effects are the result of more than the two fundamental mechanisms operating independently: (1) milling by primary ions and (2) chemical etching by neutrals. The additional mechanisms to be considered are (3) formation of C-F polymer on the sidewalls[Ref.4-24,25], (4) sputtering of Si from one surface downstream to either  $\theta_{s1}$  or  $\theta_{s2}$  sidewalls, (5) downstream sputtering of atomic layers of the Al shadowmask onto an adjacent sidewall  $\theta_{s1}$ , and (6) secondary ions reflected from one sidewall resulting in milling of an adjacent sidewall. Among these six(6) mechanisms, only the etching by neutrals (2) is isotropic. Each of the other mechanisms is anisotropic contributing sidewall striations and strong variations of sidewall  $\theta_s$  with substrate tilt  $\theta_t$ . Here both primary and secondary ion milling by reflected  $CF_3^+$  ions in addition to smooth etching by fluoride neutrals may be dominant. We do not understand the detail etch/deposition mechanisms operative for  $\theta_t \geq 15^0$  on sidewall  $\theta_{s1}$ .

The etch rate for the P-type wafers is reduced compared to the N-type case primarily due to the difference in Coulombic forces between the reactant F (chemisorbed singly-ionized negative charge state) and the dopant impurities. The  $F^-$  ion at the surface is attracted into the positively charged donor bonds of N-type silicon and thus the etch reaction rate is enhanced. Similarly, the  $F^-$  ion at the surface is repulsed from the negatively charged acceptors in P-type silicon and the etch reaction rate is reduced[Ref.4-26].

Figure 4.8 Sidewall angles  $\theta_{s1}$  and  $\theta_{s2}$  at location #3 for a N-type substrate as a function of tilt angle  $\theta_{t}$ - N-type substrate (Data obtained from average of 3 sampled values from 3 wafers).

#### 4.3.4 Trench etch rates with Al liftoff mask

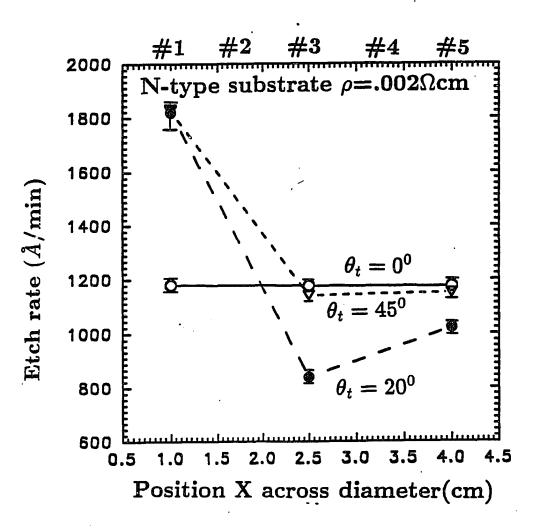

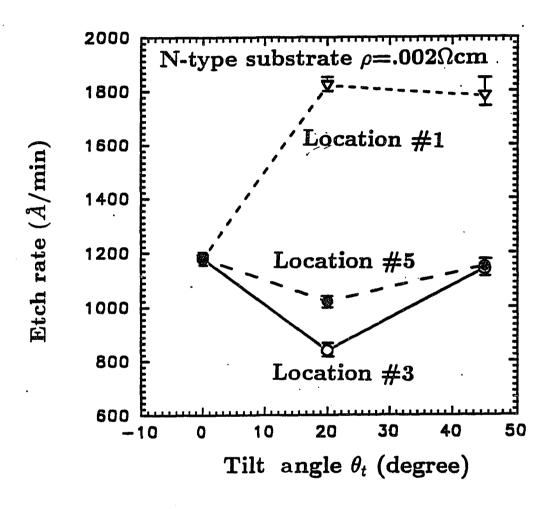

The etch rates plotted in Fig.4.9 are obtained from the Alphastep-200 surface profilometer for SEM photos of trenches on wafers with the Al shadowmask. The untilted  $\theta_t = 0^0$  wafer is etched at 1180 Å/min with our process. Thus, the 30 min etch results in trenches of depth  $3.5\mu$  depth for the case  $\theta_t = 0^0$  using the Alphastep-200 surface profilometer. In Fig.4.9, the dominance of the faster etch rate of the neutral radicals is seen at location #1. As the observed etch site moves away from location#1 the effect of ion sputtering increases and the erosion rate decreases at location #3. However, as one moves from the location#3 to location#5 in Fig.4.9 the complexity of the process is further indicated when the etch rate is seen to increase somewhat. Additional etch rate data which includes that of Fig.4.9 is shown in Fig. 4.10. The etch rate tilt angle dependency at location #1 in Fig.4.10 shows highly nonlinear characteristics. Additional studies will be required to understand this observation at location #3 and #5 is seen to be more constant with substrate tilt  $\theta_t$  compared with that of location #1.

The observed dependencies cannot be fully explained as being entirely indicates due to the (1) physical erosion of the surface by the primary ion beam and (2) chemical etching by neutral radicals alone as independently acting mechanisms. The basic ion sputtering of the sidewalls is an electrodynamic process that can be described with a ballistic model [Ref.4-27]. The basic chemical etching with neutral fluoride radicals should proceed approximately independently of the ion sputtering process. However, both primary processes are clearly supplemented by the four secondary processes mentioned probably the buildup of monolayer polymers and redeposition of the substrate material on the sidewalls.

40

## **Etch Location**

Figure.4.9 Silicon etch rate as a function of etch location using unannealed Al as a shadowmask. Tilt angle  $\theta_t$  is the plot parameter:  $\theta_t = 0$ , 20 and 45°. N-type substrate. (Data obtained with the Alphastep-200: each data point is the average of three samples)

41